# General Release Specification - MC68HC68VBI

no;

# **List of Sections**

| Section 1. General Description 15            |

|----------------------------------------------|

| Section 2. Memory 33                         |

| Section 3. Phase-Locked Loop (PLL)           |

| Section 4. VBI Data Extraction Module        |

| Section 5. Multiplexed Expansion Bus         |

| Section 6. Serial Peripheral Interface (SPI) |

| Section 7. Electrical Specifications         |

| Section 8. Mechanical Specifications         |

| Section 9. Ordering Information              |

| , cc                                         |

MC68HC68VBI -- Rev. 3.0

List of Sections

General Release Specification

vatasheethu.com

# PAGE(S) INTENTIONALLY BLANK

----

**General Release Specification**

4

MC68HC68VBI - Rev. 3.0

List of Sections

MOTOROLA

# **Table of Contents**

# Section 1. General Description

| 1.1    | Contents                               |

|--------|----------------------------------------|

| 1.2    | Introduction                           |

| 1.3    | Features                               |

| 1.4    | Functional Overview                    |

| 1.4.1  | VBI Data Extraction Module17           |

| 1.4.2  | Expanded Interface                     |

| 1.4.3  | Serial Peripheral Interface (SPI)      |

| 1.5    | Pin Assignment                         |

| 1.6    | Internal Structure                     |

| 1.7    | Functional Pin Description             |

| 1.7.1  | PAR/SER                                |

| 1.7.2  | <u>CS</u>                              |

| 1.7.3  | CSA                                    |

| 1.7.4  | AD0/SCLK                               |

| 1.7.5  | AD1/SDATA                              |

| 1.7.6  | AD2/SWIN                               |

| 1.7.7  | AD3:AD7                                |

| 1.7.8  | SDI/AS                                 |

| 1.7.9  | SDO/RW                                 |

| 1.7.10 | •••••=•••••••••••••••••••••••••••••••• |

| 1.7.11 |                                        |

| 1.7.12 |                                        |

| 1.7.13 |                                        |

| 1.7.14 |                                        |

| 1.7.15 |                                        |

| 1.7.16 |                                        |

| 1.7.17 |                                        |

|        |                                        |

| 1.7.19 | 9 OSC1                                 |

MC68HC68VBI - Rev. 3.0

**General Release Specification**

MOTOROLA

Table of Contents

# Table of Contents

| OSC2                                       |

|--------------------------------------------|

| V <sub>DD1</sub>                           |

| V <sub>SS1</sub>                           |

| V <sub>DD3</sub>                           |

| V <sub>SS3</sub>                           |

| V <sub>DD2</sub>                           |

| V <sub>SS2</sub>                           |

| de Selection                               |

| ed Frequency Oscillator                    |

| Ceramic or Crystal Resonator               |

| External Clock                             |

| Oscillator Frequency (f <sub>OSC</sub> )32 |

|                                            |

## Section 2. Memory

| 2.1 | Contents                        |

|-----|---------------------------------|

| 2.2 | Introduction                    |

| 2.3 | MC68HC68VBI Memory Map          |

| 2.4 | Control Registers \$00-\$1835   |

| 2.5 | Status/Data Registers \$80-\$DD |

# Section 3. Phase-Locked Loop (PLL)

| 3.1 | Contents                        |

|-----|---------------------------------|

| 3.2 | Introduction                    |

| 3.3 | Line Number Definitions         |

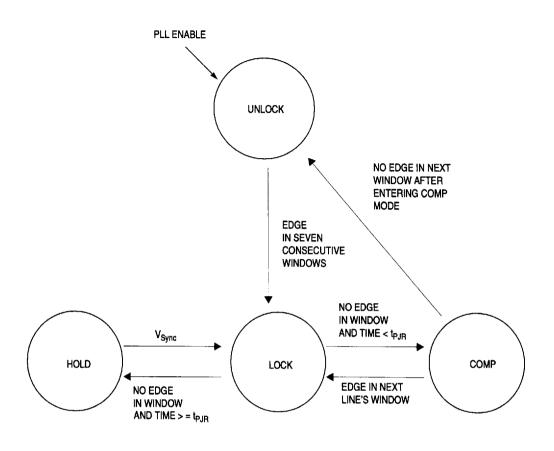

| 3.4 | PLL State Description           |

| 3.5 | Sampling Clock Control Register |

| 3.6 | Extraction PLL Divider          |

| 3.7 | Sync Control/Status             |

| 3.8 | Miscellaneous Register          |

#### Section 4. VBI Data Extraction Module

| 4.1 | Contents          |

|-----|-------------------|

| 4.2 | Introduction      |

| 4.3 | General Operation |

| 4.4 | Signal Connection |

| 4.5    | Data Slicer Output Signals61                   |

|--------|------------------------------------------------|

| 4.6    | BUSY Signal                                    |

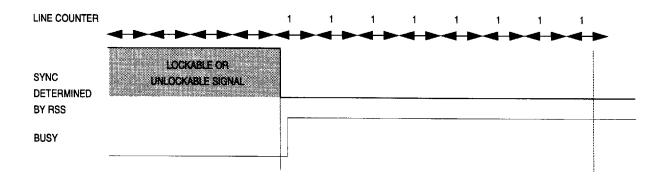

| 4.6.1  | Register Readability During BUSY               |

| 4.7    | Quasi-Horizontal Sync Detection                |

| 4.8    | Field Detection                                |

| 4.9    | Data Extraction Input Signal Description       |

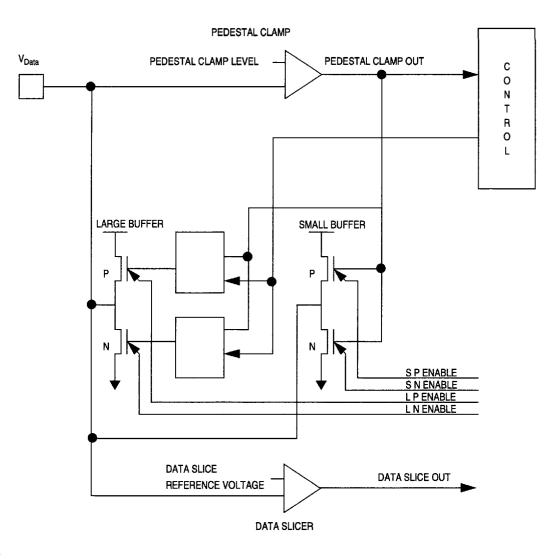

| 4.9.1  | Pedestal Clamp and Data Slicer Circuit Diagram |

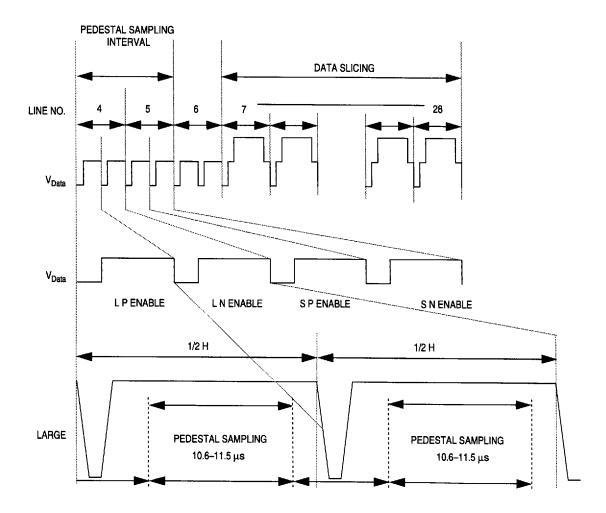

| 4.9.2  | Pedestal Clamp Timing Diagram                  |

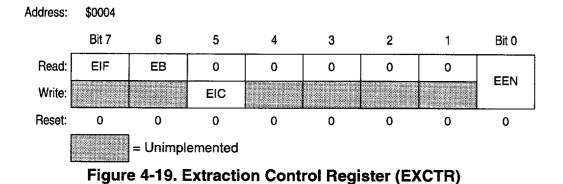

| 4.10   | Extraction Control Register                    |

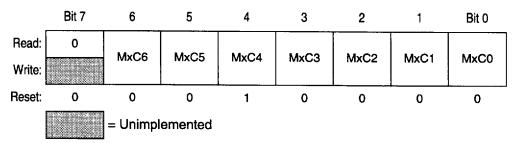

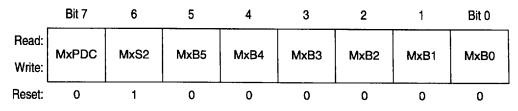

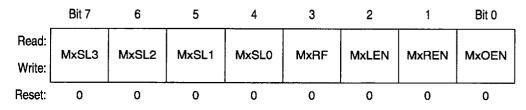

| 4.11   | Mode Description Registers                     |

| 4.12   | Teletext Hamming Decoder                       |

| 4.13   | PDC Mode                                       |

| 4.13.1 | Framing Code Synchronization                   |

| 4.13.2 | 8/30 Magazine and Row Address Group Match      |

| 4.13.3 | Format 2 Designation Code Match                |

| 4.14   | Line Control Registers                         |

| 4.15   | Field Sync Line 7 Sync Registers               |

| 4.16   | Quasi-Sync Line Count Registers                |

| 4.17   | PDC Address Register                           |

| 4.18   | Read Data x Registers                          |

|        | _                                              |

.....

# Section 5. Multiplexed Expansion Bus

| 5.1 | Contents     | .91 |

|-----|--------------|-----|

| 5.2 | Introduction | .91 |

# Section 6. Serial Peripheral Interface (SPI)

| 6.1 | Contents          |

|-----|-------------------|

| 6.2 | Introduction      |

| 6.3 | SPI Memory Access |

# Section 7. Electrical Specifications

| 7.1 | Contents                       |

|-----|--------------------------------|

| 7.2 | Introduction                   |

| 7.3 | Maximum Ratings102             |

| 7.4 | Operating Temperature Range102 |

| MC68HC68VBI — Rev. 3.0 | General Release Specification |   |

|------------------------|-------------------------------|---|

| MOTOROLA               | Table of Contents             |   |

|                        | Table of Contents             | / |

----

\_\_\_\_\_

| Thermal Characteristics                     |

|---------------------------------------------|

| 5.0 V DC Electrical Characteristics         |

| Data Extraction Characteristics             |

| Data Slicer Output Characteristics          |

| Serial Peripheral Interface Characteristics |

| Phase-Locked Loop Characteristics           |

|                                             |

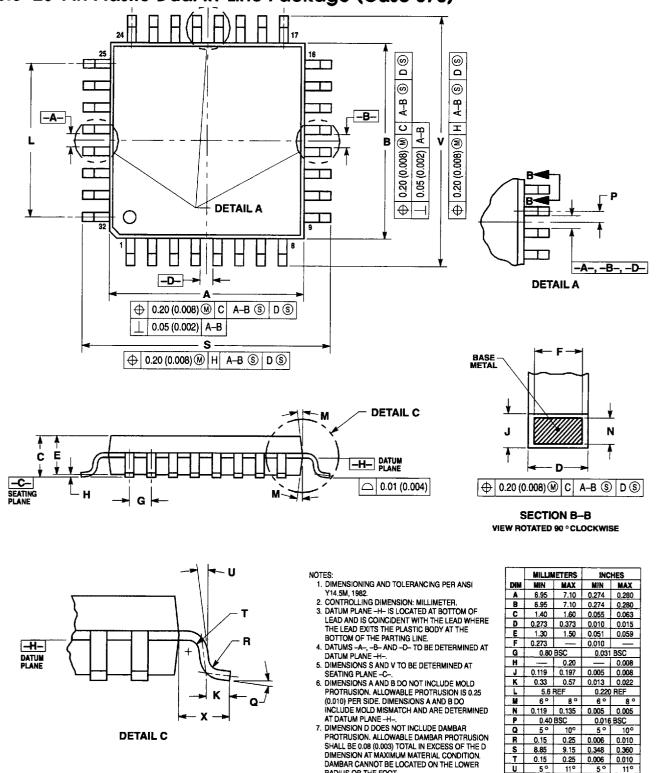

# Section 8. Mechanical Specifications

| 8.1 | Contents                                       | .107  |

|-----|------------------------------------------------|-------|

| 8.2 |                                                | . 107 |

| 8.3 | 28-Pin Plastic Dual In-Line Package (Case 873) | .108  |

# Section 9. Ordering Information

| 9.1 | Contents                |

|-----|-------------------------|

| 9.2 | Introduction            |

| 9.3 | MC Ordering Information |

8

# **List of Figures**

| Figure | Title                                         | Page |

|--------|-----------------------------------------------|------|

| 1-1    | Example of Expanded or Serial Communication   | 20   |

| 1-2    | 32-Pin QFP PinoutFigure                       | 24   |

| 1-3    | MC68HC68VBI Block Diagram                     | 25   |

| 1-4    | Oscillator Connections                        | 31   |

| 2-1    | MC68HC68VBI Memory Map                        | 34   |

| 2-2    | MC68HC68VBI Control Registers Description     |      |

| 2-3    | Control Register \$00:\$0F                    |      |

| 2-4    | Control Register \$10:\$18                    |      |

| 2-5    | MC68HC68VBI Status/Data Registers Description | 38   |

| 2-6    | Status/Data Register \$80:\$8F                |      |

| 2-7    | Status/Data Register \$90:\$9F                | 41   |

| 2-8    | Status/Data Register \$B0:\$BF                | 42   |

| 2-9    | Status/Data Register \$C0:\$CF                | 43   |

| 2-10   | Data/Status Register \$D0:\$DD                | 44   |

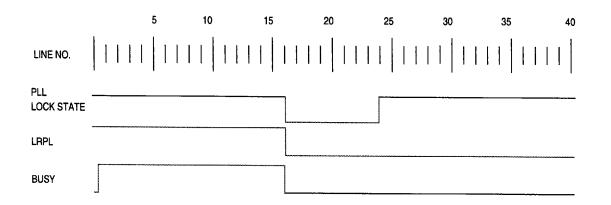

| 3-1    | PLL Block Diagram                             | 46   |

| 3-2    | LRPL Bit Timing Example                       | 47   |

| 3-3    | PLL Clock Signal Distribution                 | 48   |

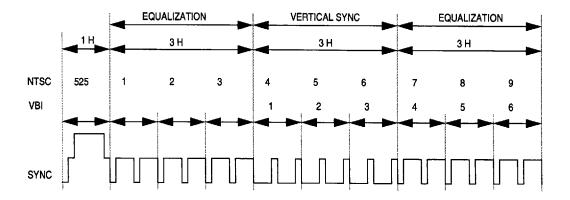

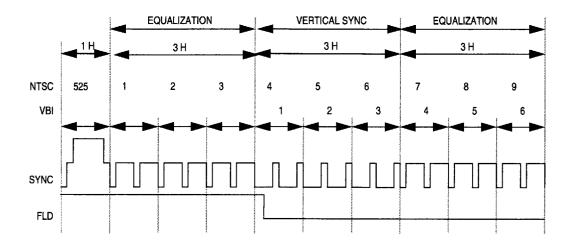

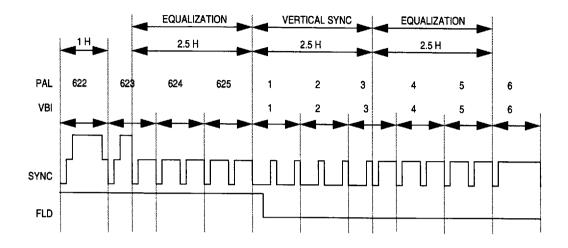

| 3-4    | NTSC First Field                              | 49   |

| 3-5    | NTSC Second Field                             | 49   |

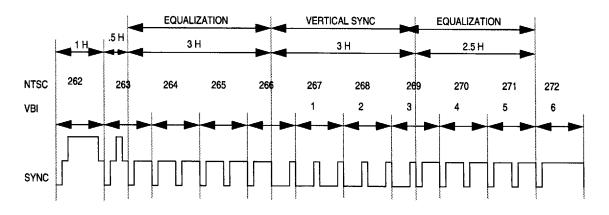

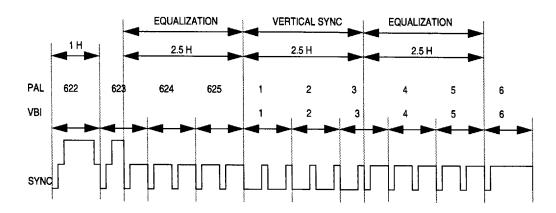

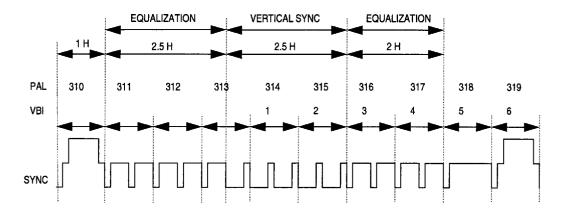

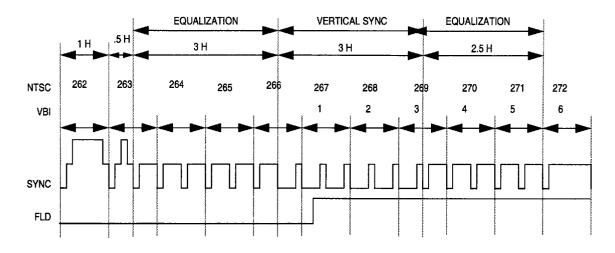

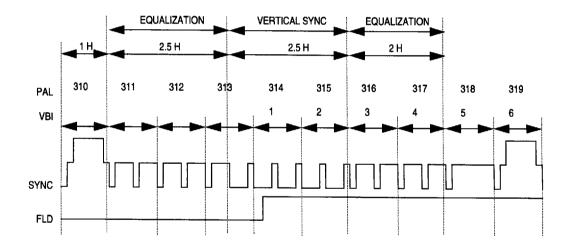

| 3-6    | PAL First Field                               | 49   |

| 3-7    | PAL Second Field                              | 50   |

| 3-8    | PLL State Diagram                             | 51   |

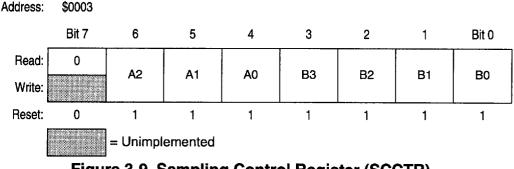

| 3-9    | Sampling Control Register (SCCTR)             | 52   |

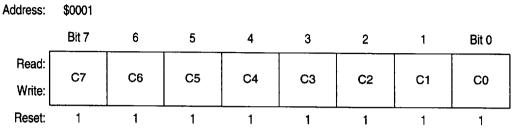

| 3-10   | Extraction PLL Divider (EPLLD)                | 53   |

MC68HC68VBI - Rev. 3.0

# List of Figures

| Figure | Title                                               | Page |

|--------|-----------------------------------------------------|------|

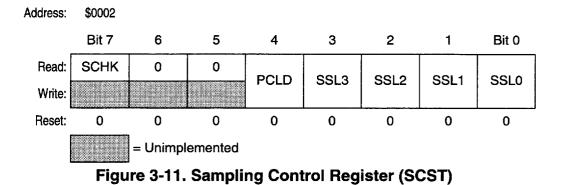

| 3-11   | Sampling Control Register (SCST)                    | 54   |

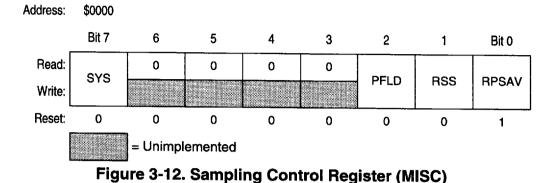

| 3-12   | Sampling Control Register (MISC)                    | 55   |

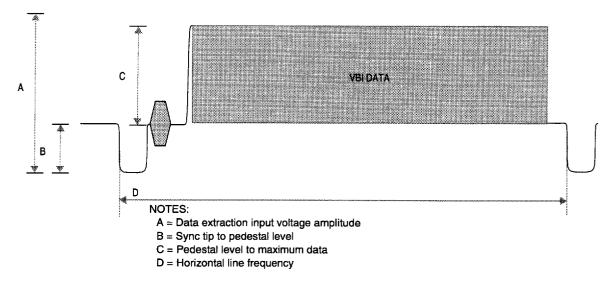

| 4-1    | Data Extraction Timing Diagram.                     | 60   |

| 4-2    | External Video Signal Connections                   | 61   |

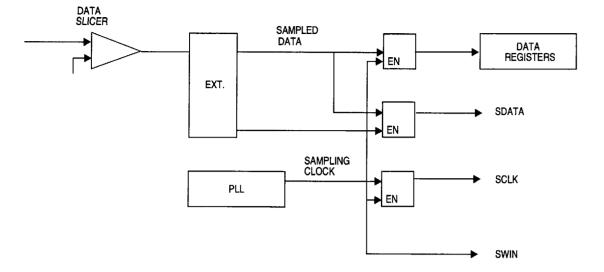

| 4-3    | Data Slicer Output Signal Block Diagram             | 62   |

| 4-4    | Data Slicer Output Signal Timing Diagram            | 63   |

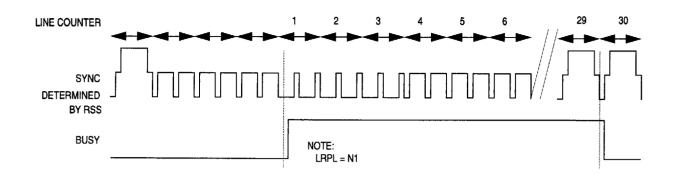

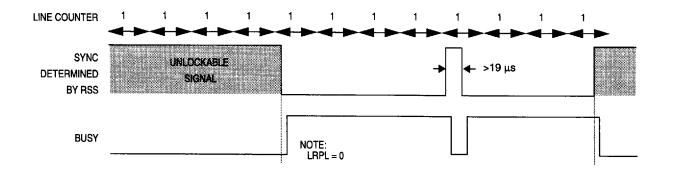

| 4-5    | BUSY Timing Diagram for Normal Sync Condition       | 64   |

| 4-6    | BUSY Timing Diagram for PLL Unlocked Condition 1.   | 64   |

| 4-7    | BUSY Timing Diagram for PLL Unlocked Condition 2 .  | 65   |

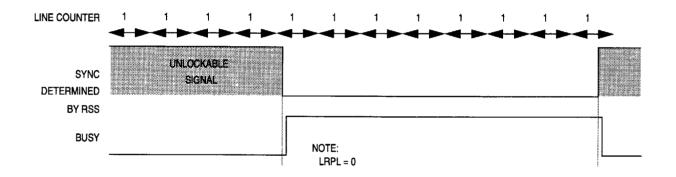

| 4-8    | BUSY Timing Diagram for No Signal Condition         | 65   |

| 4-9    | Register Readability During BUSY                    | 66   |

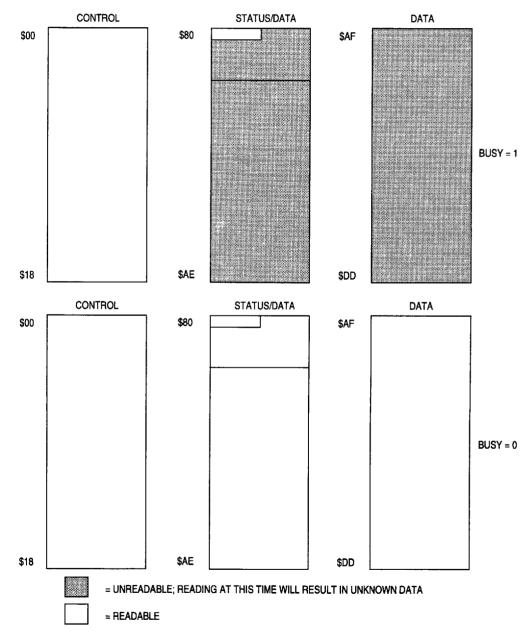

| 4-10   | Quasi-H Sync Timing for NTSC First Field            | 67   |

| 4-11   | NTSC First Field                                    | 68   |

| 4-12   | NTSC Second Field                                   | 68   |

| 4-13   | PAL First Field                                     | 69   |

| 4-14   | PAL Second Field                                    | 69   |

| 4-15   | Data Extraction Input Line Description              | 70   |

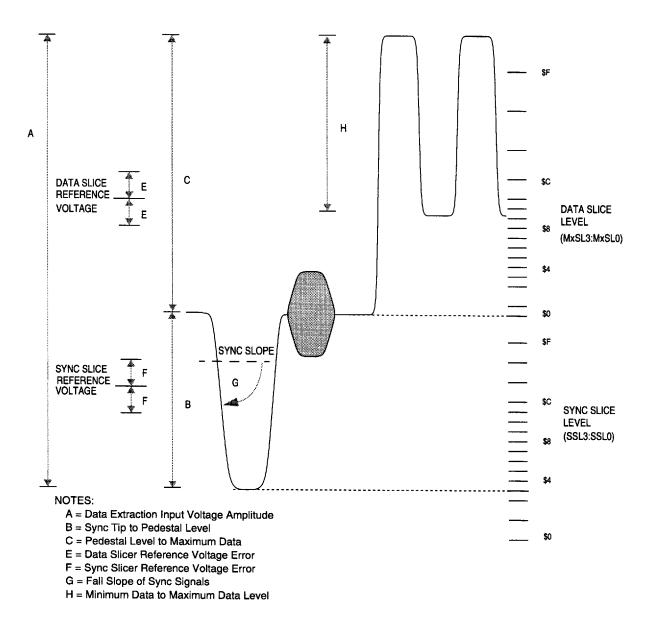

| 4-16   | Data Extraction Slice Level Description             | 71   |

| 4-17   | Pedestal Clamp and Data Slicer                      | 74   |

| 4-18   | Pedestal Clamp Timing                               | 75   |

| 4-19   | Extraction Control Register (EXCTR)                 | 76   |

| 4-20   | Mode Description Register 0 (MxD0, MxD1, and MxD2)  | 77   |

| 4-21   | Mode Description Register 1 (MxD1)                  | 77   |

| 4-22   | Mode Description Register 2 (MxD2)                  | 78   |

| 4-23   | Clock Synchronization Edge                          | 79   |

| 4-24   | Digital Low Pass Filter Block Diagram               | 80   |

| 4-25   | PDC Mode Teletext Hamming Decode Enable Diagram     | 83   |

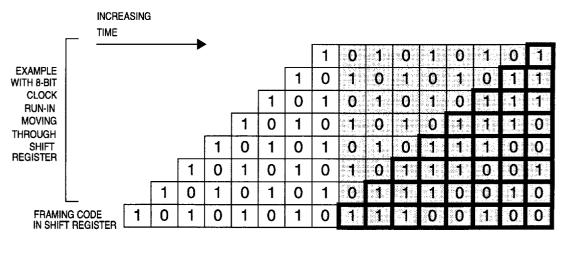

| 4-26   | Operation of Framing Code Synchronization           | 84   |

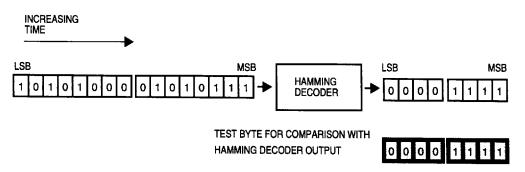

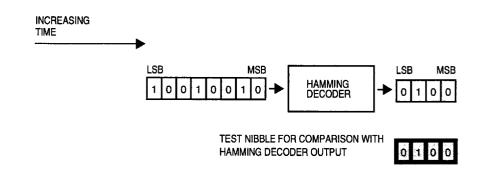

| 4-27   | Operation of 8/30 MRAG Comparison                   | 85   |

| 4-28   | Operation of Format 2 Designation Code Comparison . | 86   |

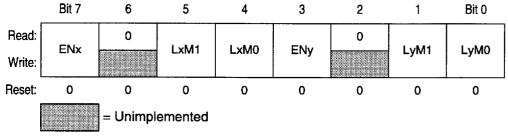

| 4-29   | Line Control Registers x/y (LCRx/LCRy)              |      |

| General | Release | Specification |

|---------|---------|---------------|

|---------|---------|---------------|

MC68HC68VBI - Rev. 3.0

÷

| Figure | Title Page                                   |

|--------|----------------------------------------------|

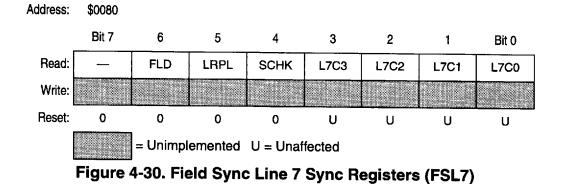

| 4-30   | Field Symp Line 7 Syme Devictory (FO) 7)     |

|        | Field Sync Line 7 Sync Registers (FSL7)87    |

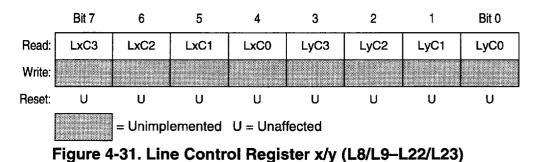

| 4-31   | Line Control Register x/y (L8/L9–L22/L23)88  |

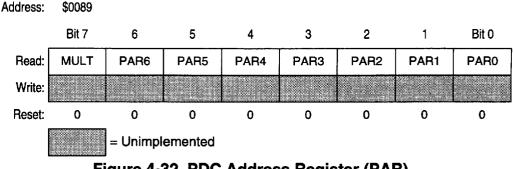

| 4-32   | PDC Address Register (PAR)88                 |

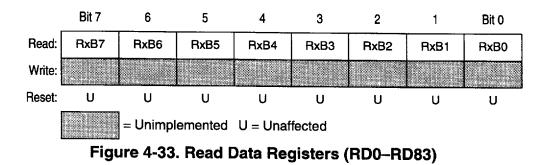

| 4-33   | Read Data Registers (RD0–RD83)               |

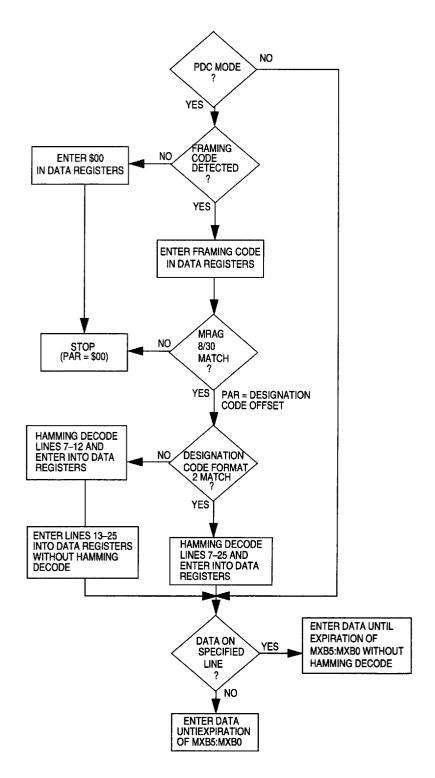

| 4-34   | Data Entry Flow Diagram                      |

|        |                                              |

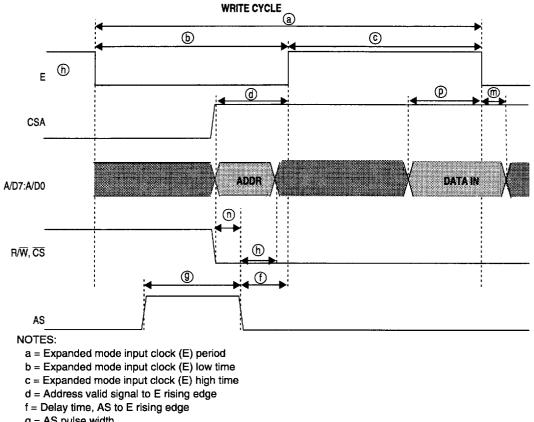

| 5-1    | Multiplexed Expansion Bus Write Cycle Timing |

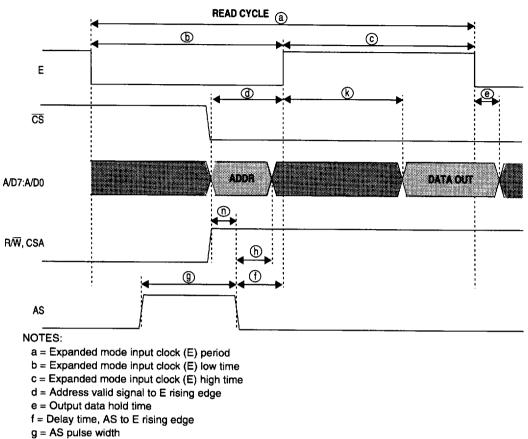

| 5-2    | Multiplexed Expansion Bus Read Cycle Timing  |

|        |                                              |

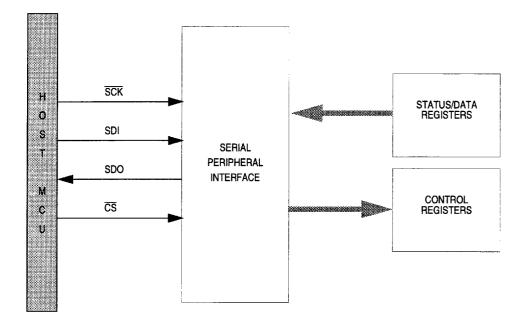

| 6-1    | SPI Block Diagram                            |

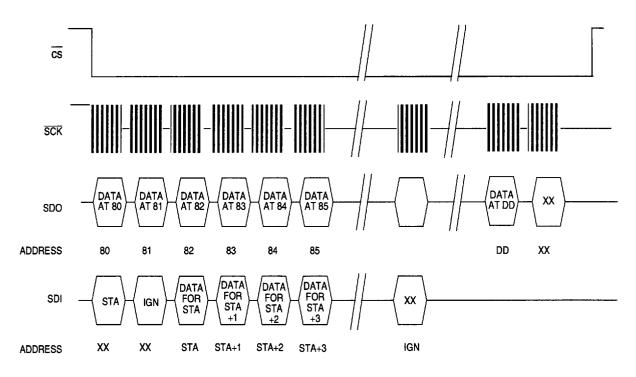

| 6-2    | SPI Interface Description                    |

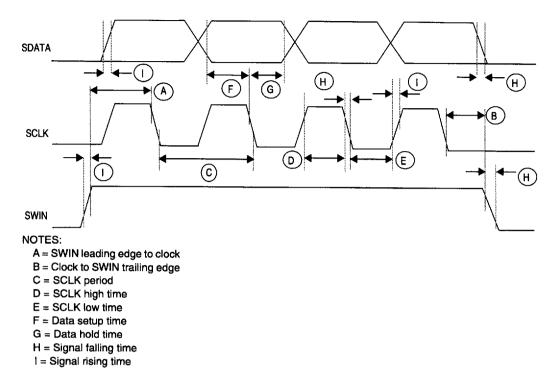

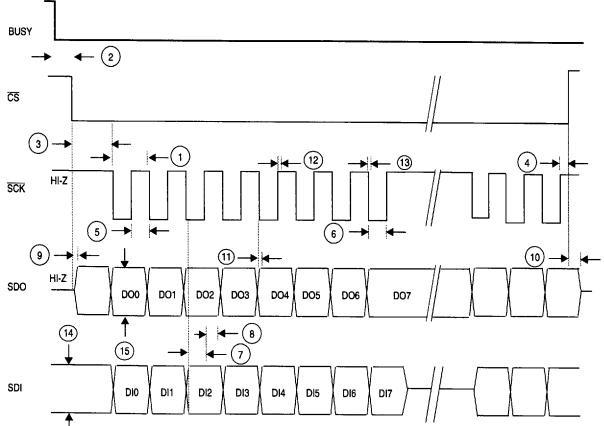

| 6-3    | SPI Timing Diagram                           |

MC68HC68VBI -- Rev. 3.0

-----

MOTOROLA

# PAGE(S) INTENTIONALLY BLANK

**General Release Specification**

12

MC68HC68VBI - Rev. 3.0

List of Figures 6367248 0164292 641 🎟 MOTOROLA

# General Release Specification — MC68HC68VBI

# List of Tables

| Table      | Title                                               | Page |

|------------|-----------------------------------------------------|------|

| 1-1<br>1-2 | MC68HC68VBI Pin Assignments<br>Mode Selection Table |      |

| 3-1        | PLL Output Frequency Examples                       | 47   |

| 4-1        | Sync Slice Levels                                   | 72   |

| 4-2        | Data Slice Levels                                   | 73   |

| 4-3        | Teletext Hamming Decoder                            | 82   |

| 9-1        | MC Order Numbers                                    |      |

----

MC68HC68VBI - Rev. 3.0

**General Release Specification**

-----

# PAGE(S) INTENTIONALLY BLANK

**General Release Specification**

MC68HC68VBI - Rev. 3.0

List of Tables 6367248 0164294 414

MOTOROLA

# Section 1. General Description

# 1.1 Contents

| 1.2                                                                | Introduction                                                                                                                                                                                                          |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3                                                                | Features                                                                                                                                                                                                              |

| 1.4<br>1.4.1<br>1.4.2<br>1.4.3                                     | Functional Overview       .17         VBI Data Extraction Module       .17         Expanded Interface       .20         Serial Peripheral Interface (SPI)       .21                                                   |

| 1.5                                                                | Pin Assignment                                                                                                                                                                                                        |

| 1.6                                                                | Internal Structure                                                                                                                                                                                                    |

| 1.7<br>1.7.1<br>1.7.2<br>1.7.3<br>1.7.4<br>1.7.5<br>1.7.6<br>1.7.7 | Functional Pin Description       .26         PAR/SER       .26         CS       .26         CSA       .26         AD0/SCLK       .26         AD1/SDATA       .27         AD2/SWIN       .27         AD3:AD7       .27 |

| 1.7.8                                                              | SDI/AS                                                                                                                                                                                                                |

| 1.7.9<br>1.7.10<br>1.7.11                                          |                                                                                                                                                                                                                       |

| 1.7.12                                                             |                                                                                                                                                                                                                       |

| 1.7.13                                                             |                                                                                                                                                                                                                       |

| 1.7.14                                                             | 22.2                                                                                                                                                                                                                  |

| 1.7.15                                                             |                                                                                                                                                                                                                       |

| 1.7.16                                                             |                                                                                                                                                                                                                       |

| 1.7.17                                                             |                                                                                                                                                                                                                       |

| 1.7.18                                                             |                                                                                                                                                                                                                       |

| 1.7.19                                                             | 9 OSC1                                                                                                                                                                                                                |

MC68HC68VBI - Rev. 3.0

**General Release Specification**

MOTOROLA

General Description

| 1.7.20 | OSC2                                     |

|--------|------------------------------------------|

| 1.7.21 | V <sub>DD1</sub>                         |

| 1.7.22 | V <sub>SS1</sub>                         |

| 1.7.23 | V <sub>DD3</sub>                         |

| 1.7.24 | V <sub>SS3</sub>                         |

| 1.7.25 | V <sub>DD2</sub>                         |

| 1.7.26 | V <sub>SS2</sub>                         |

| 1.8 N  | Node Selection                           |

| 1.9 F  | Fixed Frequency Oscillator               |

| 1.9.1  | Ceramic or Crystal Resonator             |

| 1.9.2  | External Clock                           |

| 1.9.3  | Oscillator Frequency (f <sub>OSC</sub> ) |

|        |                                          |

#### 1.2 Introduction

The Motorola MC68HC68VBI is a low-cost HCMOS video peripheral capable of decoding user-definable vertical blanking interval (VBI) data formats from National Television System Committee (NTSC), phase alternating line system (PAL), or sequential color and memory system (SECAM) video signals. A fully duplexed serial peripheral interface (SPI) or Motorola 68HC(7)11 multiplexed expansion bus enables interface with the host processor. A functional block diagram of the MC68HC68VBI is shown in **Figure 1-1**.

#### 1.3 Features

- Low Cost, HCMOS Technology

- 32-Pin Quad Flat Pack (QFP) Package

- Input Data Extraction

- Closed Caption, Extended Data Service

- Video Identification

- Moji Tajuu, Japanese Closed Captioning in Kanji

- Video Programming System (VPS)

**General Release Specification**

- Program Delivery Control Mode (PDC)

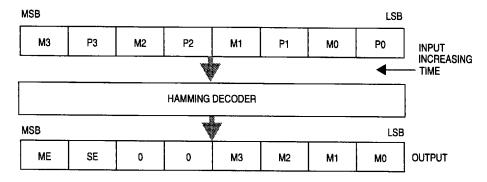

- Hamming Decoder

- Packet 8/30 Format 1 and Format 2

- Serial Peripheral Interface (SPI)

- Motorola 68HC(7)11 Multiplexed Expansion Bus

- Internal Phase-Locked Loop (PLL) Frequency Generator

- **Quasi-Horizontal Sync Detection**

#### 1.4 Functional Overview

The MC68HC68VBI contains three major functional blocks. They are:

- 1. SPI

- 2. VBI data extraction module

- 3. Multiplexed expansion bus

During communication with the host device, an input clock is needed. A single 5-volt  $\pm 10\%$  power supply is required as well as a fixed-frequency resonator or input signal. All other timing and reference voltage signals are generated on chip.

#### 1.4.1 VBI Data Extraction Module

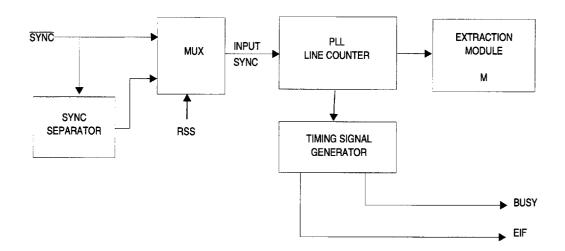

The VBI data extraction module extracts data from the composite video signal according to the programming supplied by the host. Since critical parameters of the input signal to be extracted are programmable, extraction of most data formats is possible.

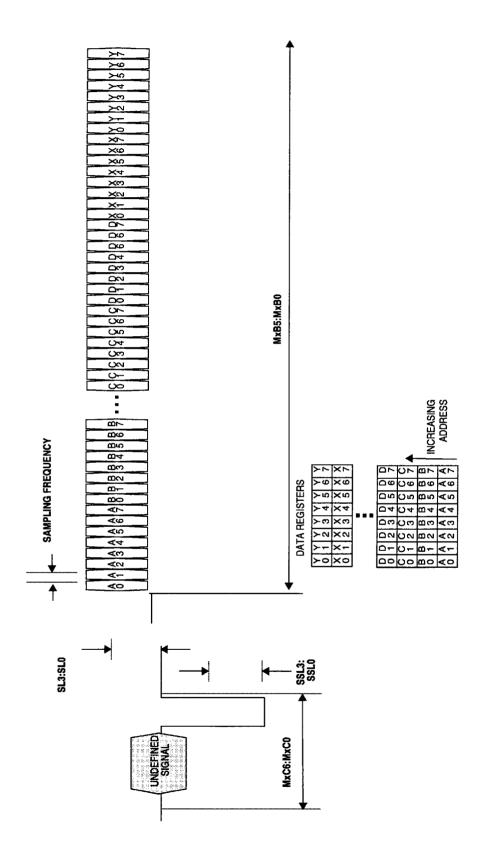

The VBI data extraction module is capable of extracting data of up to three modes from any line in the vertical blanking interval. A maximum of 84 8-bit bytes can be extracted and stored by this module in each field. This data is passed to the host MCU through the serial or expanded interface.

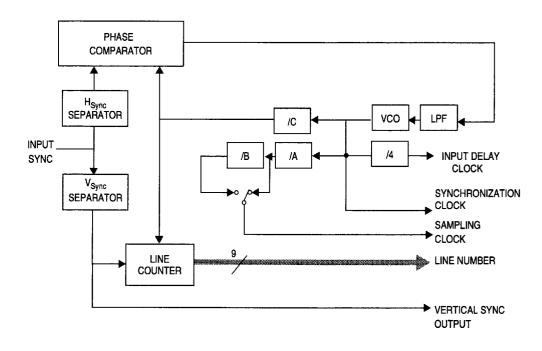

The data extraction module uses a PLL system with three programmable dividers for generation of suitable sampling clocks. Appropriate divide

| MC68HC68VBI - Rev. 3.0 |                     | General Release Specification |  |  |

|------------------------|---------------------|-------------------------------|--|--|

| MOTOROLA               | General Description |                               |  |  |

#### **General Description**

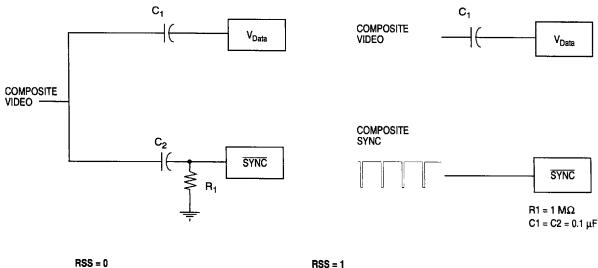

ratios must be chosen and programmed by the user for generation of the sampling clocks. The clock switch may be used to switch between related clocks without re-stabilizing the PLL or for lower clock frequencies. External composite sync or internally separated sync pulses can be selected using the read sync select bit, RSS, in the MISC register.

The mode description memory is used to define the characteristics of the data formats to be extracted. These registers are organized into four groups of three registers.

Data to be extracted is described by:

- Clock delay, the number of output delay clocks from the horizontal sync leading edge until the first data

- PDC mode or not

- Number of bytes to be sampled per line

- PLL clock switch

- Data slice level

- Clock synchronization on rising or falling edge

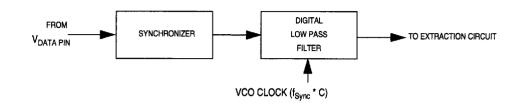

- Digital LPF enable

- Resynchronization enable

- Output enable

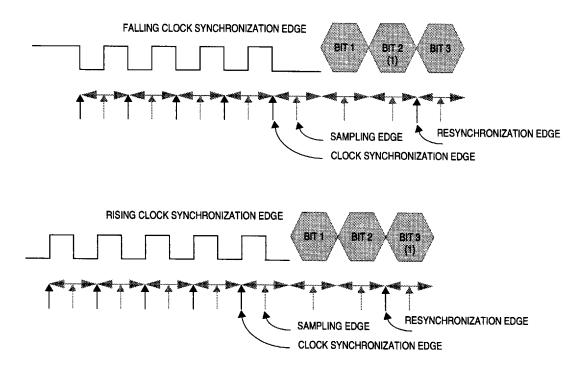

The clock synchronization edge is used for initial clock synchronization and maintenance of clock synchronization. It is determined by MxRF. If this bit is clear, the clock will be resynchronized on the rising edge of the data contained in the video signal, and if it is set, on the falling edge.

The clock delay register is intended to allow the user to start data acquisition at the appropriate time. Prior to expiration of the count in the clock delay register, the data contained in the video signal will not be sampled. When the count in the clock delay register expires, the data acquisition module will synchronize the sampling clock to the first selected edge (depending on selection of MxRF) of the video signal.

For those data types with start bits, the clock delay register should expire after the last transition of the signal before the rising edge of the start bit. For those data types with a run-in clock but no start bit, the clock delay register should expire after the last transition of the signal before the rising edge of the run-in clock. In this way, proper clock synchronization of all data types can be achieved. The run-in clock can be used by software to verify proper synchronization.

Following expiration of the clock delay register, the sampling clock will re-establish synchronization at every selected edge of the input video signal. If several like data bits occur, the clock will detect these bits accurately until resynchronizing at the next edge.

When the number of bytes to be sampled has been entered into the internal memory, the data acquisition module will terminate data sampling. This allows the user to determine the beginning and end of each line's samples.

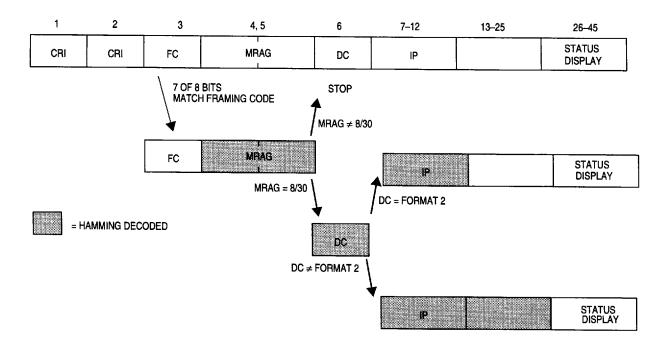

A specialized PDC mode has been included to allow selection of sampled data. When this mode is enabled, only those PDC lines with a magazine and row address group matching the 8/30 format code will be read into the internal data registers. If a PDC line with a different magazine and row address group is encountered, only the framing code is captured. If no data is detected, \$00 is entered into the data registers.

Once the modes have been described, the user can read data of one of the three described modes using the line control registers. Data may be read from lines 7 through 28. The line control registers contain an enable bit and two bits to indicate the mode number desired for that line.

MC68HC68VBI - Rev. 3.0

MOTOROLA

**General Release Specification**

19

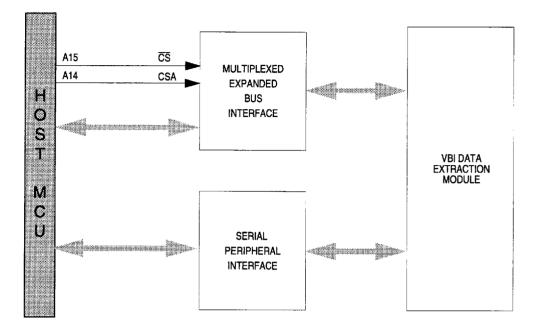

Figure 1-1. Example of Expanded or Serial Communication

#### 1.4.2 Expanded Interface

The expanded interface provides high-speed access between Motorola 68HC(7)11 multiplex expansion MCUs and the control and data registers of the data extraction module. This is accomplished using the multiplex expansion mode of devices such as the 'HC11E9 or 'HC11A8.

The expanded interface is designed to require a minimum of interface hardware and to provide direct access to the control and data registers of the data extraction module. Using the configuration in **Figure 1-1**, VBI registers can be accessed by the software in exactly the same way as the 'HC11's internal memory locations. The VBI memory can be accessed using any high order addresses between \$40XX and \$7FXX. In its default state, the HC11E9 has no other memory in this range. Control signals are provided to coordinate communication with the HC11 MCU.

**General Release Specification**

#### 1.4.3 Serial Peripheral Interface (SPI)

A full-duplex serial peripheral interface (SPI) links the host device with the control and data registers of the data extraction module.

The SPI is designed to access the registers once between each vertical blanking interval. It is recommended that this be done some time during the display portion of the video output. Data can be read from and written to the registers simultaneously. Starting at address \$80, all or part of the data can be read. Simultaneously, all or a single contiguous group of control registers may be written.

After chip select is asserted, the first two bytes clocked into the SPI are the write start and write ignore (stop) address. Thereafter, data is clocked into the registers starting from the start address. At the ignore address, data is no longer entered into the memory. Clocks must be applied for a full byte at the ignore address to enter the previous data into the register. Control signals are provided to coordinate communication with the host MCU.

Starting from the first clock used to clock in the start address, data is clocked out of the read-only registers from address \$80. Even after the ignore address has been reached, data from the read-only registers will be clocked out. When the last byte is reached, \$FF will be clocked out.

MOTOROLA

#### 1.5 Pin Assignment

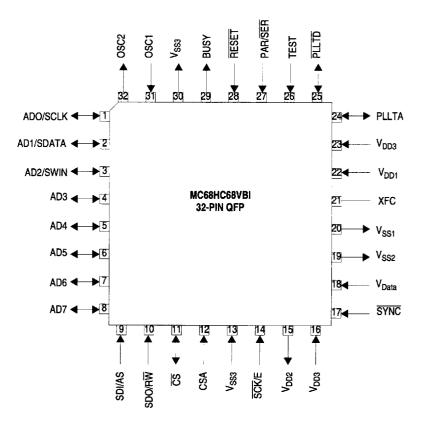

The MC68HC68VBI is available in a 32-pin QFP. The pin assignment for this package is shown in **Table 1-1**.

| Pin | Name              | Expanded Mode |          |               | Serial Mode       |        |          |               |                   |

|-----|-------------------|---------------|----------|---------------|-------------------|--------|----------|---------------|-------------------|

| No. |                   | I/O           | CMOS/TTL | Open<br>Drain | Func-<br>tion     | 1/0    | CMOS/TTL | Open<br>Drain | Func-<br>tion     |

| 1   | AD0/<br>SCLK      | I/O           | CMOS     | No            | AD0               | 0      | CMOS     | No            | SCLK              |

| 2   | AD1/<br>SDATA     | 1/0           | CMOS     | No            | AD1               | 0      | CMOS     | No            | SDATA             |

| 3   | AD2/<br>SWIN      | I/O           | CMOS     | No            | AD2               | 0      | CMOS     | No            | SWIN              |

| 4   | AD3               | 1/0           | CMOS     | No            | AD3               | 0      | Note 4   |               | —                 |

| 5   | AD4               | I/O           | CMOS     | No            | AD4               | 0      | Note 4   |               | _                 |

| 6   | AD5               | 1/0           | CMOS     | No            | AD5               | 0      | Note 4   |               |                   |

| 7   | AD6               | I/O           | CMOS     | No            | AD6               | 0      | Note 4   |               | _                 |

| 8   | AD7               | Note 2        | CMOS     | No            | AD7               | 0      | Note 4   | —             |                   |

| 9   | V <sub>DD3</sub>  | I             | _        |               | _                 | Note 2 |          | _             |                   |

| 10  | SDI/AS            | 1             | CMOS     | No            | AS                | 1      | TTL      | No            | SDI               |

| 11  | SDO/RW            | I             | CMOS     | Yes           | RW                | 0      | CMOS     | Yes           | SDO               |

| 12  | SCK/E             | I             | CMOS     | No            | E                 | I      | TTL      | No            | SCK               |

| 13  | <u>CS</u>         | I             | CMOS     | No            | CS                | I      | TTL      | No            | CS                |

| 14  | CSA               | Note 2        | CMOS     | No            | CSA               | 1      |          | —             | Note 5            |

| 15  | V <sub>SS3</sub>  | Note 2        |          | _             | _                 | Note 2 |          | —             | —                 |

| 16  | V <sub>DD2</sub>  | 1             |          | _             |                   | Note 2 | _        |               | —                 |

| 17  | SYNC              | I             | Note 1   | No            | SYNC              | I      | Note 1   | No            | SYNC              |

| 18  | V <sub>Data</sub> | Note 2        | Note 1   | No            | V <sub>Data</sub> | I      | Note 1   | No            | V <sub>Data</sub> |

| 19  | V <sub>SS2</sub>  | Note 2        | _        |               |                   | Note 2 | _        | _             | _                 |

| 20  | V <sub>SS1</sub>  | Note 3        |          |               | —                 | Note2  | _        | —             | _                 |

| 21  | XFC               | Note 2        | Note 1   | No            | XFC               | Note 3 | Note 1   | No            | XFC               |

Table 1-1. MC68HC68VBI Pin Assignments

**General Release Specification**

| Pin<br>No. |                  | Expanded Mode |          |               | Serial Mode   |        |          |               |               |

|------------|------------------|---------------|----------|---------------|---------------|--------|----------|---------------|---------------|

|            | Name             | ١/O           | CMOS/TTL | Open<br>Drain | Func-<br>tion | 1/0    | CMOS/TTL | Open<br>Drain | Func-<br>tion |

| 22         | V <sub>DD1</sub> | Note 2        | _        | _             |               | Note 2 |          | —             |               |

| 23         | V <sub>DD3</sub> | 1/0           |          |               | _             | Note 2 |          |               | _             |

| 24         | PLLTA            | I/O           |          | No            | Test          | 1/0    |          | No            | Test          |

| 25         | PLLTD            | I             |          | No            | Test          | I/O    |          | No            | Test          |

| 26         | TEST             | I             | CMOS     | No            | Test          | 1      | CMOS     | No            | Test          |

| 27         | PAR/SER          | I             | CMOS     | No            | Parallel      | I      | CMOS     | No            | Serial        |

| 28         | RESET            | 0             | TTL      | No            | Reset         | I      | TTL      | No            | Reset         |

| 29         | BUSY             | Note 2        | CMOS     | Yes           | Busy          | 0      | CMOS     | Yes           | Busy          |

| 30         | V <sub>SS3</sub> | I             |          |               | -             | Note 2 | _        |               |               |

| 31         | OSC1             | 0             | CMOS     | No            | OSC1          | 1      | CMOS     | No            | OSC1          |

| 32         | OSC2             | I/O           | CMOS     | No            | OSC2          | 0      | CMOS     | No            | OSC2          |

#### Table 1-1. MC68HC68VBI Pin Assignments (Continued)

NOTES:

1. Defined separately

2. Power supply or ground pin

3. Connection for external capacitor

4. Pulled down weakly; does not affect circuit operation in serial mode

5. No function

MC68HC68VBI - Rev. 3.0

#### **General Description**

Figure 1-2. 32-Pin QFP Pinout

**NOTE:** A line over a signal name indicates an active-low signal. Any reference to voltage, current, or frequency specified in the following sections will refer to the nominal values. The exact values and their tolerance or limits are specified in **Section 7. Electrical Specifications.**

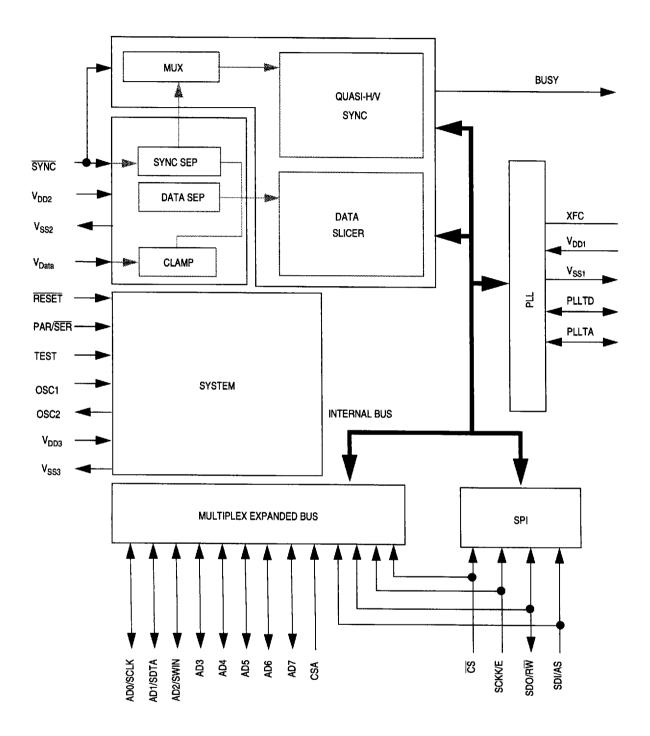

#### 1.6 Internal Structure

A block diagram of the MC68HC68VBI is shown in Figure 1-3.

General Release Specification

MC68HC68VBI --- Rev. 3.0

MOTOROLA

24

# Figure 1-3. MC68HC68VBI Block Diagram

| MC68HC68VBI - Rev. 3.0 | C68HC68VBI — Rev. 3.0 Gen |    |

|------------------------|---------------------------|----|

| MOTOROLA               | General Description       | 25 |

|                        | 🖬 6367248 O1643O5 O2T 🛲   |    |

## **General Description**

#### **1.7 Functional Pin Description**

#### 1.7.1 PAR/SER

This input-only pin activates either expanded or serial interface with the host controller. When this pin is at a low-voltage level, the serial communication interface is activated. When this pin is at a high-voltage level, the expanded interface is activated.

#### 1.7.2 CS

This input-only pin is the chip select for both the serial and expanded interfaces, depending on PAR/SER. When serial is activated and this pin is at a high-voltage level, the serial interface is deselected. When it is at a low-voltage level, the serial interface is selected. The first SCK following the falling edge of  $\overline{CS}$  clocks data.

When expanded is activated and this pin is a high-voltage level, the expanded interface is deselected. When it is a low-voltage level and CSA is a high-voltage level, the expanded interface is selected.

When the serial interface is activated, TTL input levels are used. When the expanded interface is activated, CMOS input levels are used.

#### 1.7.3 CSA

This input-only pin is the alternate chip select for the expanded interface. When serial is activated, this pin has no affect. When expanded is activated and this pin is a high-voltage level and  $\overline{CS}$  is a low-voltage level, the expanded interface is selected. To disable this pin, connect to low-voltage level.

#### 1.7.4 AD0/SCLK

When the expanded mode is activated, this bidirectional pin is AD0 of the address/data bus of the expanded interface. When the serial mode is activated, this pin is the data slicer sampling clock output. When in

| General | Release | Specification | n |

|---------|---------|---------------|---|

|         |         |               |   |

reset, this pin is high impedance. When the expanded interface is deactivated, this pin is weakly pulled down (about 100 k $\Omega$ ).

#### 1.7.5 AD1/SDATA

When the expanded mode is activated, this bidirectional pin is AD1 of the address/data bus of the expanded interface. When the serial mode is activated, this pin is the data slicer sampled data output. When in reset, this pin is high impedance. When the expanded interface is deactivated, this pin is weakly pulled down (about 100 k $\Omega$ ).

#### 1.7.6 AD2/SWIN

When the expanded mode is activated, this bidirectional pin is AD2 of the address/data bus of the expanded interface. When the serial mode is activated, this pin is the data slicer window output. When in reset, this pin is high impedance. When the expanded interface is deactivated, this pin is weakly pulled down (about 100 k $\Omega$ ).

#### 1.7.7 AD3:AD7

These bidirectional pins make up the remainder of the address/data bus of the expanded interface. While in reset, these pins are high impedance. When the expanded interface is deactivated, these pins are weakly pulled down (about 100 k $\Omega$ ).

#### 1.7.8 SDI/AS

When the expanded interface is enabled, this input-only, TTL-level (transistor-transistor logic) pin functions as the expanded interface address strobe. When the serial communication interface is enabled, this pin is the serial communication data input pin.

When the serial interface is activated, TTL input levels are used. When the expanded interface is activated, CMOS input levels are used.

MC68HC68VBI - Rev. 3.0

# **General Description**

#### 1.7.9 SDO/RW

When the expanded interface is enabled, this open drain, input/output pin determines read from memory or write to memory. When the serial communication interface is enabled, this pin is the serial communication data output pin and an external pullup resistor should be attached. While in reset, this pin is high impedance.

#### 1.7.10 SCK/E

This input-only, TTL-level dual function pin is the clock input for both the expanded interface or the serial interface. When serial mode is selected, an external pullup resistor should be connected to this pin to control the pin state during idle periods.

When the serial interface is activated, TTL input levels are used. When the expanded interface is activated, CMOS input levels are used.

#### 1.7.11 SYNC

This input-only pin accepts synchronization signals from the video source. These signals may be a composite video signal or digital level composite sync. If composite video is input, a series capacitor should be used. If composite sync is input, direct coupling should be used and RSS should be set.

#### 1.7.12 V<sub>Data</sub>

This pin accepts the video input signal for determination of the pedestal level and data extraction. Synchronization signals are input at the SYNC pin.

#### 1.7.13 XFC

This pin is used for connection to external passive components used to determine the characteristics of PLL. Typical passive component is 0.1  $\mu$ F capacitor and might be sourced to V<sub>SS</sub>1.

| General Release Specification |                         | MC68HC68VBI — Rev. 3.0 |

|-------------------------------|-------------------------|------------------------|

| 28                            | General Description     | MOTOROLA               |

|                               | ■ 6367248 O164308 839 ■ |                        |

| MOTOROLA               | General Description 29                                                                                                                                |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC68HC68VBI — Rev. 3.0 | General Release Specification                                                                                                                         |

|                        |                                                                                                                                                       |

|                        | This output-only pin is the output for the fixed-frequency oscillator.                                                                                |

| 1.7.20 OSC2            |                                                                                                                                                       |

|                        |                                                                                                                                                       |

|                        | This input-only pin is the input for the fixed-frequency oscillator.                                                                                  |

| 1.7.19 OSC1            |                                                                                                                                                       |

|                        | a low level.                                                                                                                                          |

|                        | this signal is high, the registers may be busy. The signal on this pin is<br>referenced to the sync selected by RSS. While in reset, this pin outputs |

|                        | This open-drain output-only pin is high during lines 1 through 29. When this signal is low, it is safe to access the extraction data registers. When  |

| 1.7.18 BUSY            |                                                                                                                                                       |

|                        | This input-only TTL-level pin resets the peripheral to a known state.                                                                                 |

| 1.7.17 <b>RESET</b>    |                                                                                                                                                       |

|                        |                                                                                                                                                       |

|                        | This input-only pin is for factory use only and should always be connected to V <sub>SS3</sub> .                                                      |

| 1.7.16 TEST            |                                                                                                                                                       |

|                        | It is reserved for factory use and should always be connected to $V_{\mbox{SS3}}$ .                                                                   |

|                        | This input/output pin is the analog test pin for the extraction module PLL.                                                                           |

| 1.7.15 PLLTA           |                                                                                                                                                       |

|                        | It is reserved for factory use and should always be connected to $V_{\text{SS3}}.$                                                                    |

|                        | This input/output pin is the digital test pin for the extraction module PLL.                                                                          |

| 1.7.14 PLLTD           |                                                                                                                                                       |

-----

-----

# **General Description**

| 1.7.21 | V <sub>DD1</sub> | This is the analog power supply pin for PLL1.                             |

|--------|------------------|---------------------------------------------------------------------------|

| 1.7.22 | V <sub>SS1</sub> | This is the analog ground pin for PLL1.                                   |

| 1.7.23 | V <sub>DD3</sub> | This is the digital power supply pin for logic circuits.                  |

| 1.7.24 | V <sub>SS3</sub> | This is the digital ground pin for logic circuits.                        |

| 1.7.25 | V <sub>DD2</sub> | This is the digital power supply pin for noise-sensitive analog circuits. |

| 1.7.26 | V <sub>SS2</sub> | This is the digital ground pin for noise-sensitive analog circuits.       |

## 1.8 Mode Selection

Modes are selected per the information in Table 1-2.

| Table 1-2. Mode | Selection Table |

|-----------------|-----------------|

|-----------------|-----------------|

| Mode     | Test | PAR/SER         | CS         | CSA         |

|----------|------|-----------------|------------|-------------|

| Serial   | 0    | 0               | Active Low | Inactive    |

| Expanded | 0    | 1               | Active Low | Active High |

| Test     | 1    | Factory Test Me |            | e           |

General Release Specification

MC68HC68VBI - Rev. 3.0

■ 6367248 0164310 497 **■**

**General Description**

MOTOROLA

Ł

#### 1.9 Fixed Frequency Oscillator

A fixed-frequency oscillator is included for generation of timing signals when a stable PLL frequency is not available.

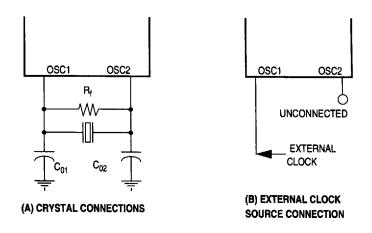

The OSC1 and OSC2 pins are the connections for the 2-pin on-chip oscillator. The OSC1 and OSC2 pins can accept these two sets of components:

- A crystal or ceramic oscillator as shown in Figure 1-4(a)

- An external clock signal as shown in Figure 1-4(b)

#### 1.9.1 Ceramic or Crystal Resonator

The circuit in **Figure 1-4** shows a typical 2-pin oscillator circuit for a ceramic or crystal resonator. The crystal manufacturer's recommendations should be followed, as the resonator's parameters determine the external component values required to provide maximum stability and reliable startup. The load capacitance values used in the oscillator circuit design should include all stray capacitances. The crystal and components should be mounted as close as possible to the pins for startup stabilization and to minimize output distortion.

Figure 1-4. Oscillator Connections

| MC68HC68VBI - F | Rev. 3.0 |

|-----------------|----------|

|-----------------|----------|

#### **1.9.2 External Clock**

An external clock from another CMOS-compatible device can be connected to the OSC1 input, with the OSC2 input not connected, as shown in **Figure 1-4**. This configuration is possible regardless of oscillator connection or not.

#### 1.9.3 Oscillator Frequency (f<sub>OSC</sub>)

When SYS = 0 (525-line system), a frequency of 3.57954 MHz (NTSC  $f_{OSC}$ ) must be used. When SYS = 1 (625-line system), a frequency of 4.43362 MHz (PAL  $f_{OSC}$ ) must be used. This oscillator must always be connected to ensure proper operation. Vertical sync signals detected using the fixed-frequency oscillator must be longer than 63 times the duration of one fixed-frequency clock period to be considered vertical sync signals.

**General Release Specification**

# Section 2. Memory

# 2.1 Contents

| 2.2 | Introduction                    |

|-----|---------------------------------|

| 2.3 | MC68HC68VBI Memory Map34        |

| 2.4 | Control Registers \$00–\$1835   |

| 2.5 | Status/Data Registers \$80-\$DD |

#### 2.2 Introduction

Information concerning the MC68HC68VBI memory map and its control registers and status/data registers are found in this section.

MC68HC68VBI - Rev. 3.0

# 2.3 MC68HC68VBI Memory Map

The MC68HC68VBI has 119 active bytes of registers as shown in **Figure 2-1.**

|                               | \$0000<br>5 DVTF0   |

|-------------------------------|---------------------|

| EVERACTION AND DUE DECISIONED | 5 BYTES             |

| EXTRACTION AND PLL REGISTERS  | ↓                   |

|                               | \$0004              |

|                               | \$0005<br>11 BYTES  |

|                               |                     |

| LINE CONTROL REGISTERS        | •                   |

|                               | \$000F              |

|                               | \$0010<br>9 BYTES   |

| MODE DESCRIPTION REGISTERS    | 3 DT 123            |

| MODE DESCRIPTION REGISTERS    |                     |

|                               | \$0018              |

|                               | \$0019<br>103 BYTES |

| UNUSED                        | ↓                   |

| ONOCLD                        | \$007F              |

|                               | \$0080              |

|                               | 10 BYTES            |

| SYNC STATUS REGISTERS         | 4                   |

|                               | \$0089              |

|                               | \$008A              |

|                               | 84 BYTES            |

| DATA REGISTERS                | Ļ                   |

|                               | \$00DD              |

|                               | \$00DE              |

|                               | 26 BYTES            |

| UNUSED                        | Ļ                   |

|                               | \$00F7              |

|                               | \$00F8              |

|                               | 8 BYTES             |

| RESERVED                      | $\downarrow$        |

|                               | \$00FF              |

| l                             | 400i l              |

#### Figure 2-1. MC68HC68VBI Memory Map

# 2.4 Control Registers \$00-\$18

| Addr | Name                            |  |

|------|---------------------------------|--|

| \$00 | Miscellaneous Register          |  |

| \$01 | Extraction PLL Divider Register |  |

| \$02 | Sync Status/Control Register    |  |

| \$03 | Sampling Clock Control          |  |

| \$04 | Extraction Control Register     |  |

| \$05 | Line Control 7/8 Register       |  |

| \$06 | Line Control 9/10 Register      |  |

| \$07 | Line Control 11/12 Register     |  |

| \$08 | Line Control 13/14 Register     |  |

| \$09 | Line Control 15/16 Register     |  |

| \$0A | Line Control 17/18 Register     |  |

| \$0B | Line Control 19/20 Register     |  |

| \$0C | Line Control 21/22 Register     |  |

| \$0D | Line Control 23/24 Register     |  |

| \$0E | Line Control 25/26 Register     |  |

| \$0F | Line Control 27/28 Register     |  |

| \$10 | Mode 0 Description 1 Register   |  |

| \$11 | Mode 0 Description 2 Register   |  |

| \$12 | Mode 0 Description 3 Register   |  |

| \$13 | Mode 1 Description 1 Register   |  |

| \$14 | Mode 1 Description 2 Register   |  |

| \$15 | Mode 1 Description 3 Register   |  |

| \$16 | Mode 2 Description 1 Register   |  |

| \$17 | Mode 2 Description 2 Register   |  |

| \$18 | Mode 2 Description 3 Register   |  |

#### Figure 2-2. MC68HC68VBI Control Registers Description

# Memory

| Addr | Register Name                     |                 | Bit 7 | 6  | 5     | 4     | 3    | 2    | 1     | Bit 0 |

|------|-----------------------------------|-----------------|-------|----|-------|-------|------|------|-------|-------|

| \$00 | Miscellaneous (MISC)              | Read:           | SYS   | 0  | 0     | 0     | 0    | PFLD | RSS   | RPSAV |

|      |                                   | Write:<br>Read: |       |    |       |       |      |      |       |       |

| \$01 | Extraction PLL Divider (EPLLD)    | Write:          | C7    | C6 | C5    | C4    | Сз   | C2   | C1    | C0    |

| \$02 | Sync Control/Status (SCST)        | Read:           | SCHK  | 0  | 0     | PCLD  | SSL3 | SSL2 | SSL1  | SSL0  |

|      |                                   | Write:          |       |    |       |       |      |      |       |       |

| \$03 | Sampling Clock Control (SCCTR)    | Read:<br>Write: | 0     | A2 | A1    | AO    | B3   | B2   | B1    | B0    |

| \$04 | Extraction Control (EXCTR)        | Read:           | EIF   | EB | 0     | 0     | 0    | 0    | 0     | EEN   |

| φ01  |                                   | Write:          |       |    | EIC   |       |      |      |       |       |

| \$05 | Line Control 7/8 (LCR7/LCR8)      | Read:<br>Write: | EN7   | 0  | L7M1  | L7M0  | EN8  | 0    | L8M1  | L8M0  |

| \$06 | Line Control 9/10 (LCR9/LCR10)    | Read:<br>Write: | EN9   | 0  | L9M1  | L9M0  | EN10 | 0    | L10M1 | L10M0 |

| \$07 | Line Control 11/12 (LC11/LCR12)   | Read:<br>Write: | EN11  | 0  | L11M1 | L11M0 | EN12 | 0    | L12M1 | L12M0 |

| \$08 | Line Control 13/14 (LCR13/LCR14)  | Read:<br>Write: | EN13  | 0  | L13M1 | L13M0 | EN14 | 0    | L14M1 | L14M0 |

| \$09 | Line Control 15/16 (LCR15/LCR16)  | Read:<br>Write: | EN15  | 0  | L15M1 | L15M0 | EN16 | 0    | L16M1 | L16M0 |

| \$0A | Line Control 17/18 (LCR17/LCR18)  | Read:<br>Write: | EN17  | 0  | L17M1 | L17M0 | EN18 | 0    | L18M1 | L18M0 |

| \$0B | Line Control 19/20 (LCR19/LCR20   | Read:<br>Write: | EN19  | 0  | L19M1 | L19M0 | EN20 | 0    | L20M1 | L20M0 |

| \$0C | Line Control 21/22 (LCRR21/LCR22) | Read:<br>Write: | EN21  | 0  | L21M1 | L21M0 | EN22 | 0    | L22M1 | L22M0 |

| \$0D | Line Control 23/24 (LCR23/LCR24)  | Read:<br>Write: | EN23  | 0  | L23M1 | L23M0 | EN24 | 0    | L24M1 | L24M0 |

| \$0E | Line Control 25/26 (LCR25/LCR26)  | Read:<br>Write: | EN25  | 0  | L25M1 | L25M0 | EN26 | 0    | L26M1 | L26M0 |

| \$0F | Line Control 27/28 (LCR27/LCR28)  | Read:<br>Write: | EN27  | 0  | L27M1 | L27M0 | EN28 | 0    | L28M1 | L28M0 |

U = Unimplemented

#### Figure 2-3. Control Register \$00:\$0F

General Release Specification

MC68HC68VBI - Rev. 3.0

MOTOROLA

| Addr | Register Name               |                 | Bit 7 | 6     | 5     | 4     | 3    | 2     | 1     | Bit 0 |

|------|-----------------------------|-----------------|-------|-------|-------|-------|------|-------|-------|-------|

| \$10 | Mode 0 Description 0 (M0D0) | Read:<br>Write: | 0     | M0C6  | M0C5  | M0C4  | M0C3 | M0C2  | M0C1  | MOCO  |

| \$11 | Mode 0 Description 1 (M0D1) | Read:<br>Write: | MOPDC | M0S2  | M0B5  | M0B4  | M0B3 | M0B2  | M0B1  | MOBO  |

| \$12 | Mode 0 Description 2 (M0D2) | Read:<br>Write: | M0SL3 | M0SL2 | M0SL1 | MOSLO | MORF | MOLEN | MOREN | M0OEN |

| \$13 | Mode 1 Description 0 (M1D0) | Read:<br>Write: | 0     | M1C6  | M1C5  | M1C4  | M1C3 | M1C2  | M1C1  | M1C0  |

| \$14 | Mode 1 Description 1 (M1D1) | Read:<br>Write: | M1PDC | M1S2  | M1B5  | M1B4  | M1B3 | M1B2  | M1B1  | M1B0  |

| \$15 | Mode 1 Description 2 (M1D2) | Read:<br>Write: | M1SL3 | M1SL2 | M1SL1 | M1SL0 | M1RF | M1LEN | M1REN | M10EN |

| \$16 | Mode 2 Description 0 (M2D0) | Read:<br>Write: | 0     | M2C6  | M2C5  | M2C4  | M2C3 | M2C2  | M2C1  | M2C0  |

| \$17 | Mode 2 Description 1 (M2D1) | Read:<br>Write: | M2PDC | M2S2  | M2B5  | M2B4  | M2B3 | M2B2  | M2B1  | M2B0  |

| \$18 | Mode 2 Description 2 (M2D2) | Read:<br>Write: | M2SL3 | M2SL2 | M2SL1 | M2SL0 | M2RF | M2LEN | M2REN | M2OEN |

U = Unimplemented

Figure 2-4. Control Register \$10:\$18

MC68HC68VBI - Rev. 3.0

# 2.5 Status/Data Registers \$80-\$DD

| Addr | Name                            |

|------|---------------------------------|

| \$80 | Field Sync/Line 7 Sync Register |

| \$81 | Line 8/Line 9 Sync Register     |

| \$82 | Line 10/Line 11 Sync Register   |

| \$83 | Line 12/Line 13 Sync Register   |

| \$84 | Linbe 14/Line 15 Sync Register  |

| \$85 | Line 16/Line 17 Sync Register   |

| \$86 | Line 18/Line 19 Sync Register   |

| \$87 | Line 20/Line 21 Sync Register   |

| \$88 | Line 22/Line 23 Sync Register   |

| \$89 | PDC Address Register            |

| \$8A | Data Register 0                 |

| \$8B | Data Register 1                 |

| \$8C | Data Register 2                 |

| \$8D | Data Register 3                 |

| \$8E | Data Register 4                 |

| \$8F | Data Register 5                 |

| \$90 | Data Register 6                 |

| \$91 | Data Register 7                 |

| \$92 | Data Register 8                 |

| \$93 | Data Register 9                 |

| \$94 | Data Register 10                |

| \$95 | Data Register 11                |

| \$96 | Data Register 12                |

| \$97 | Data Register 13                |

| \$98 | Data Register 14                |

| \$99 | Data Register 15                |

| ·····   |

|---------|

|         |

|         |

|         |

|         |

|         |

|         |

| <u></u> |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

|         |

#### Figure 2-5. MC68HC68VBI Status/Data Registers Description

**General Release Specification**

| Addr | Name             |

|------|------------------|

| \$9A | Data Register 16 |

| \$9B | Data Register 17 |

| \$9C | Data Register 18 |

| \$9D | Data Register 19 |

| \$9E | Data Register 20 |

| \$9F | Data Register 21 |

| \$A0 | Data Register 22 |

| \$A1 | Data Register 23 |

| \$A2 | Data Regiser 24  |

| \$АЗ | Data Register 25 |

| \$A4 | Data Register 26 |

| \$A5 | Data Register 27 |

| \$A6 | Data Register 28 |

| \$A7 | Data Register 29 |

| \$A8 | Data Register 30 |

| \$A9 | Data Register 31 |

| \$AA | Data Register 32 |

| \$AB | Data Register 33 |

| \$AC | Data Register 34 |

| \$AD | Data Register 35 |

| \$AE | Data Regiser 36  |

| Addr | Name             |

|------|------------------|

| \$C9 | Data Register 63 |

| \$CA | Data Register 64 |

| \$CB | Data Register 65 |

| \$CC | Data Register 66 |

| \$CD | Data Register 67 |

| \$CE | Data Register 68 |

| \$CF | Data Register 69 |

| \$D0 | Data Register 70 |

| \$D1 | Data Register 71 |

| \$D2 | Data Register 72 |

| \$D3 | Data Register 73 |

| \$D4 | Data Register 74 |

| \$D5 | Data Register 75 |

| \$D6 | Data Register 76 |

| \$D7 | Data Register 77 |

| \$D8 | Data Register 78 |

| \$D9 | Data Register 79 |

| \$DA | Data Register 80 |

| \$DB | Data Register 81 |

| \$DC | Data Register 82 |

| \$DD | Data Register 83 |

Figure 2-5. MC68HC68VBI Status/Data Registers Description (Continued)

MC68HC68VBI - Rev. 3.0

**General Release Specification**

ł

## Memory

| Addr        | Register Name             |                 | Bit 7 | 6         | 5     | 4      | 3      | 2      | 1     | Bit 0 |

|-------------|---------------------------|-----------------|-------|-----------|-------|--------|--------|--------|-------|-------|

| \$80        | Field Sync/Line 7 (FSL7)  | Read:           | 0     | FLD       | LRPL  | SCHK   | L7C3   | L7C2   | L7C1  | L7C0  |

| φου         |                           | Write:          |       |           |       |        |        |        |       |       |

| \$81        | Line 8/Line 9 (L8/L9)     | Read:           | L8C3  | L8C2      | 8LC1  | L8C0   | L9C3   | L9C2   | L9C1  | L9C0  |

| • - ·       |                           | Write:          |       |           |       |        |        |        |       |       |

| \$82        | Line 10/Line 11 (L10/L11) | Read:           | L10C3 | 10C2      | L10C1 | L10C0  | L11C3  | L11C2  | L11C1 | L11C0 |

|             | · · · · ·                 | Write:          |       |           |       |        |        |        |       |       |

| \$83        | Line 12/Line 13 (L12/L13) | Read:           | L12C3 | L12C2     | 12LC1 | L12C0  | L13C3  | L13C2  | L13C1 | L13C0 |

|             |                           | Write:          |       |           |       |        |        |        |       |       |

| \$84        | Line 14/Line 15 (L14/L15) | Read:           | L14C3 | L14C2     | L14C1 | L14C0  | L15C3  | L15C2  | L15C1 | L15C0 |

|             |                           | Write:          | 14000 | 1 4 9 9 9 |       | 1 1000 | 1.1700 | 1.1500 |       |       |

| \$85        | Line 16/Line 17 (L16/L17) | Read:           | L16C3 | L16C2     | L16C1 | L16C0  | L17C3  | L17C2  | L17C1 | L17C0 |

|             |                           | Write:          | L18C3 | 11000     | 11001 | 11000  | 1.1000 | 11000  | 14004 | 14000 |

| \$86        | Line 18/Line 19 (L18/L19) | Read:<br>Write: | L1003 | L18C2     | L18C1 | L18C0  | L19C3  | L19C2  | L19C1 | L19C0 |

|             |                           | Read:           | L20C3 | L20C2     | L20C1 | L20C0  | L21C3  | L21C2  | L21C1 | LC210 |

| \$87        | Line 20/Line 21 (L20/L21) | Write:          | 12000 | 12002     | L2001 | 12000  |        | LZIUZ  | 12101 | L0210 |

|             |                           | Read:           | L22C3 | L22C2     | L22C1 | L22C0  | L23C3  | L23C2  | L23C1 | L23C0 |

| \$88        | Line 22/Line 23 (L22/L23) | Write:          |       |           |       |        |        |        |       |       |

|             |                           | Read:           | MULT  | PAR6      | PAR5  | PAR4   | PAR3   | PAR2   | PAR1  | PAR0  |

| \$89        | PDC Address (PAR)         | Write:          |       |           |       |        |        |        |       |       |

| <b>A</b> -1 |                           | Read:           | R0B7  | R0B6      | R0B5  | R0B4   | R0B3   | R0B2   | R0B1  | R0B0  |

| \$8A        | Read Data 0 (RD0)         | Write:          |       |           |       |        |        |        |       |       |

| ¢oD         | Deed Date 4 (DD4)         | Read:           | R1B7  | R1B6      | R1B5  | R1B4   | R1B3   | R1B2   | R1B1  | R1B0  |

| \$8B        | Read Data 1 (RD1)         | Write:          |       |           |       |        |        |        |       |       |

| \$8C        | Read Data 2 (RD2)         | Read:           | R2B7  | R2B6      | R2B5  | R2B4   | R2B3   | R2B2   | R2B1  | R2B0  |

| φOC         | neau Dala 2 (ND2)         | Write:          |       |           |       |        |        |        |       |       |

| \$8D        | Read Data 3 (RD3)         | Read:           | R3B7  | R3B6      | R3B5  | R3B4   | R3B3   | R3B2   | R3B1  | R3B0  |

| <b>40</b> D |                           | Write:          |       |           |       |        |        |        |       |       |

| \$8E        | Read Data 4 (RD4)         | Read:           | R4B7  | R4B6      | R4B5  | R4B4   | R4B3   | R4B2   | R4B1  | R4B0  |

| +           | ······ Dulu ((104)        | Write:          |       |           |       |        |        |        |       |       |

| \$8F        | Read Data 5 (RD5)         | Read:           | R5B7  | R5B6      | R5B5  | R5B4   | R5B3   | R5B2   | R5B1  | R5B0  |

|             | ·/                        | Write:          |       |           |       |        |        |        |       |       |

U = Unimplemented

## Figure 2-6. Status/Data Register \$80:\$8F

**General Release Specification**

MC68HC68VBI - Rev. 3.0

-

\_\_\_\_

| Addr | Register Name       |        | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1            | Bit 0 |

|------|---------------------|--------|-------|-------|-------|-------|-------|-------|--------------|-------|

| \$90 | Read Data 6 (RD6)   | Read:  | R6B7  | R6B6  | R6B5  | R6B4  | R6B3  | RB2   | R6B1         | R6B0  |

| ψυυ  |                     | Write: |       |       |       |       |       |       |              |       |

| \$91 | Read Data 7 (RD7    | Read:  | R7B7  | R7B6  | R7B5  | R7B4  | R7B3  | R7B2  | R7B1         | R7B0  |

| ΨΟΙ  |                     | Write: |       |       |       |       |       |       |              |       |

| \$92 | Read Data 8 (RD8)   | Read:  | R8B7  | R8B6  | R8B5  | R8B4  | R8B3  | R8B2  | R8B1         | R8B0  |

|      |                     | Write: |       |       |       |       |       |       |              |       |

| \$93 | Read Data 9 (RD9)   | Read:  | R9B7  | R9B6  | R9B5  | R9B4  | R9B3  | R9B2  | <b>R9B</b> 1 | R9B0  |

|      |                     | Write: |       |       |       |       |       |       |              |       |

| \$94 | Read Data 10 (RD10) | Read:  | R10B7 | R10B6 | R10B5 | R10B4 | R10B3 | R10B2 | R10B1        | R10B0 |

| ÷• · |                     | Write: |       |       |       |       |       |       |              |       |

| \$95 | Read Data 11 (RD11) | Read:  | R11B7 | R11B6 | R11B5 | R11B4 | R11B3 | R11B2 | R11B1        | R11B0 |

| •    |                     | Write: |       |       |       |       |       |       |              |       |

| \$96 | Read Data12 (RD12)  | Read:  | R12B7 | R12B6 | R12B5 | R12B4 | R12B3 | R12B2 | R12B1        | R12B0 |

|      | ,                   | Write: |       |       |       |       |       |       |              |       |

| \$97 | Read Data 13 (RD13) | Read:  | R13B7 | R13B6 | R13B5 | R13B4 | R13B3 | R13B2 | R13B1        | R13B0 |

|      | · · ·               | Write: |       |       |       |       |       |       |              |       |

| \$98 | Read Data 14 (RD14) | Read:  | R14B7 | R14B6 | R14B5 | R14B4 | R14B3 | R14B2 | R14B1        | R14B0 |

|      | · · · ·             | Write: |       |       |       |       |       |       |              |       |

| \$99 | Read Data 15 (RD15) | Read:  | R15B7 | R15B6 | R15B5 | R15B4 | R15B3 | R15B2 | R15B1        | R15B0 |

|      | 、 <i>、</i> ,        | Write: |       |       |       |       |       |       |              |       |

| \$9A | Read Data 16 (RD16) | Read:  | R16B7 | R16B6 | R16B5 | R16B4 | R16B3 | R16B2 | R16B1        | R16B0 |

|      | · · ·               | Write: |       |       |       |       |       |       |              |       |

| \$9B | Read Data 17 (RD17) | Read:  | R17B7 | R17B6 | R17B5 | R17B4 | R17B3 | R17B2 | R17B1        | R17B0 |

|      |                     | Write: |       |       |       |       |       |       |              |       |

| \$9C | Read Data 18 (RD18) | Read:  | R18B7 | R18B6 | R18B5 | R18B4 | R18B3 | R18B2 | R18B1        | R18B0 |

|      |                     | Write: |       |       | _     |       |       |       |              |       |

| \$9D | Read Data 19 (RD19) | Read:  | R19B7 | R19B6 | R19B5 | R19B4 | R19B3 | R19B2 | R19B1        | R19B0 |

|      |                     | Write: |       |       |       |       |       |       |              |       |

| \$9E | Read Data 20 (RD20) | Read:  | R20B7 | R20B6 | R20B5 | R20B4 | R20B3 | R20B2 | R20B1        | R20B0 |

|      |                     | Write: |       |       |       |       | _     |       |              |       |

| \$9F | Read Data 21 (RD21) | Read:  | R21B7 | R21B6 | R21B5 | R21B4 | R21B3 | R21B2 | R21B1        | R21B0 |

|      |                     | Write: |       |       |       |       |       |       |              |       |

U = Unimplemented

## Figure 2-7. Status/Data Register \$90:\$9F

MC68HC68VBI - Rev. 3.0

**General Release Specification**

Memory 6367248 0164321 272 Memory

| Addr          | <b>Register Name</b>                  |        | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

|---------------|---------------------------------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$B0          | Read Data 38 (RD38)                   | Read:  | R38B7 | R38B6 | R38B5 | R38B4 | R38B3 | R38B2 | R38B1 | R38B0 |

| φου           |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B1          | Read Data 39 (RD39)                   | Read   | R39B7 | R39B6 | R39B5 | R39B4 | R39B3 | R39B2 | R39B1 | R39B0 |

| ΨUΤ           |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B2          | Read Data 40 (RD40)                   | Read:  | R40B7 | R40B6 | R40B5 | R40B4 | R40B3 | R40B2 | R40B1 | R40B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B3          | Read Data 41 (RD41)                   | Read:  | R41B7 | R41B6 | R41B5 | R41B4 | R41B3 | R41B2 | R41B1 | R41B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B4          | Read Data 42 (RD42)                   | Read:  | R42B7 | R42B6 | R42B5 | R42B4 | R42B3 | R42B2 | R42B1 | R42B0 |

| <b>4-</b> 1   |                                       | Write: |       |       |       |       |       |       |       |       |

| \$ <b>B</b> 5 | Read Data 43 (RD43)                   | Read:  | R43B7 | R43B6 | R43B5 | R43B4 | R43B3 | R43B2 | R43B1 | R43B0 |

| <b>400</b>    |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B6          | Read Data 44 (RD44)                   | Read:  | R44B7 | R44B6 | R44B5 | R44B4 | R44B3 | R44B2 | R44B1 | R44B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B7          | Read Data 45 (RD45)                   | Read:  | R45B7 | R45B6 | R45B5 | R45B4 | R45B3 | R45B2 | R45B1 | R45B0 |

| • = ·         |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B8          | Read Data 46 (RD46)                   | Read:  | R46B7 | R46B6 | R46B5 | R46B4 | R46B3 | R46B2 | R46B1 | R46B0 |

| ,<br>         |                                       | Write: |       |       |       |       |       |       |       |       |

| \$B9          | Read Data 47 (RD47)                   | Read:  | R47B7 | R47B6 | R47B5 | R47B4 | R47B3 | R47B2 | R47B1 | R47B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$BA          | Read Data 48 (RD48)                   | Read:  | R48B7 | R48B6 | R48B5 | R48B4 | R48B3 | R48B2 | R48B1 | R48B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$BB          | Read Data 49 (RD49)                   | Read:  | R49B7 | R49B6 | R49B5 | R49B4 | R49B3 | R49B2 | R49B1 | R49B0 |

| ·             |                                       | Write: |       |       |       |       |       |       |       |       |

| \$BC          | Read Data 50 (RD50)                   | Read:  | R50B7 | R50B6 | R50B5 | R50B4 | R50B3 | R50B2 | R50B1 | R50B0 |

|               | · · · · · · · · · · · · · · · · · · · | Write: |       |       |       |       |       |       |       |       |

| \$BD          | Read Data 51 (RD51)                   | Read:  | R51B7 | R51B6 | R51B5 | R51B4 | R51B3 | R51B2 | R51B1 | R51B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

| \$BE          | Read Data 52 (RD52)                   | Read:  | R52B7 | R52B6 | R2B5  | R52B4 | R52B3 | R52B2 | R52B1 | R52B0 |

|               | · · · · · · · · · · · · · · · · · · · | Write: |       |       |       |       |       |       |       |       |

| \$BF          | Read Data 53 (RD53)                   | Read:  | R53B7 | R53B6 | R53B5 | R53B4 | R53B3 | R53B2 | R53B1 | R53B0 |

|               |                                       | Write: |       |       |       |       |       |       |       |       |

U = Unimplemented

## Figure 2-8. Status/Data Register \$B0:\$BF

General Release Specification

MC68HC68VBI - Rev. 3.0

-

| SC0         Read Data 54 (RD54)         Read:         R64B7         R64B6         R54B3         R54B2         R54B1         R54B0           SC1         Read Data 55 (RD55)         Read:         R55B7         R55B6         R55B3         R55B2         R55B1         R55B2         R55B1         R55B2           SC1         Read Data 55 (RD55)         Read:         R55B7         R55B6         R55B4         R55B3         R55B2         R55B1         R55B0         R55B2         R55B1         R55B2         R55B1         R55B2         R55B1         R55B3         R55B2         R55B1         R55B2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Addr     | Register Name       |        | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------|--------|--------|--------|--------|--------|--------|--------|-------|------------------------|