MC68HC908QF4

Data Sheet

M68HC08 Microcontrollers

> MC68HC908QF4 Rev. 1.0 6/2004

# MC68HC908QF4

#### **Data Sheet**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://motorola.com/semiconductors/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

# **Revision History**

Freescale Semiconductor, Inc.

| Date             | Revision<br>Level | Description                                                        | Page<br>Number(s) |

|------------------|-------------------|--------------------------------------------------------------------|-------------------|

| October,<br>2003 | N/A               | Initial release                                                    | N/A               |

| June,            |                   | Removed references to MC68HC908QF3, MC68HC908QF2, and MC68HC908QF1 | Throughout        |

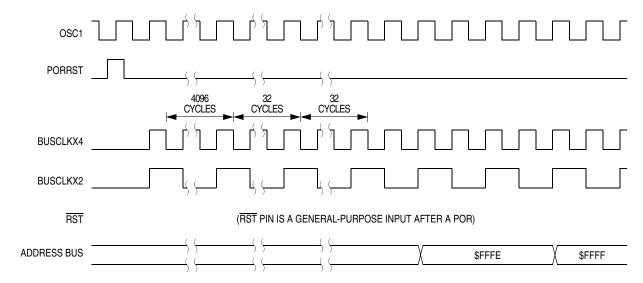

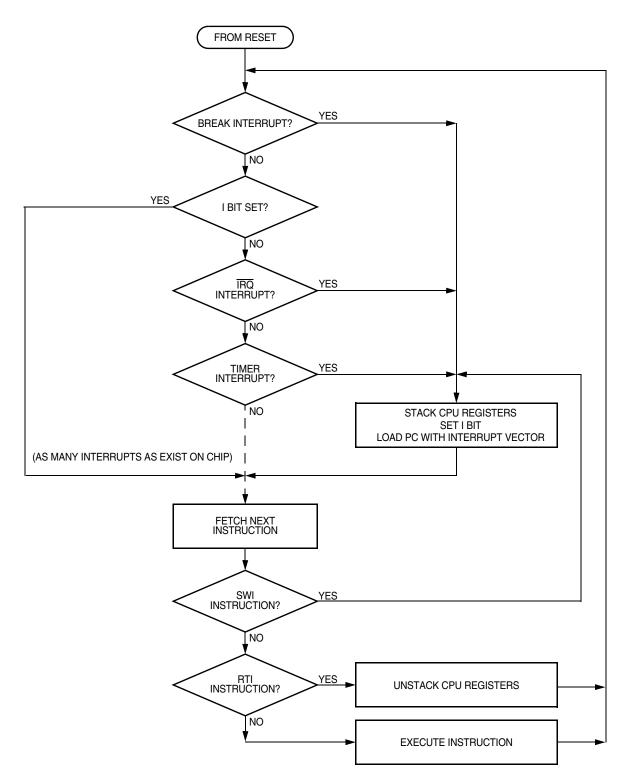

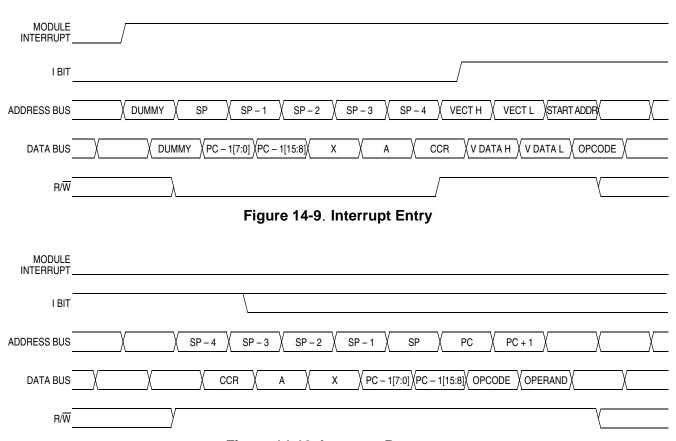

| 2004             | 1.0               | 17.4 Thermal Characteristics — Updated 32-pin TQFP value           | 176               |

|                  |                   | 18.2 MC Order Numbers — Updated table entries for MC order numbers | 193               |

**Revision History**

## Data Sheet — MC68HC908QF4

# **List of Sections**

| Section 1. General Description15                                  |

|-------------------------------------------------------------------|

| Section 2. Memory                                                 |

| Section 3. Analog-to-Digital Converter (ADC)                      |

| Section 4. Auto Wakeup Module (AWU)                               |

| Section 5. Configuration Register (CONFIG)5                       |

| Section 6. Computer Operating Properly (COP)55                    |

| Section 7. Central Processor Unit (CPU)59                         |

| Section 8. External Interrupt (IRQ)73                             |

| Section 9. Keyboard Interrupt Module (KBI)79                      |

| Section 10. Low-Voltage Inhibit (LVI)87                           |

| Section 11. Oscillator Module (OSC)9                              |

| Section 12. PLL Tuned UHF Transmitter Module10                    |

| Section 13. Input/Output (I/O) Ports11                            |

| Section 14. System Integration Module (SIM)119                    |

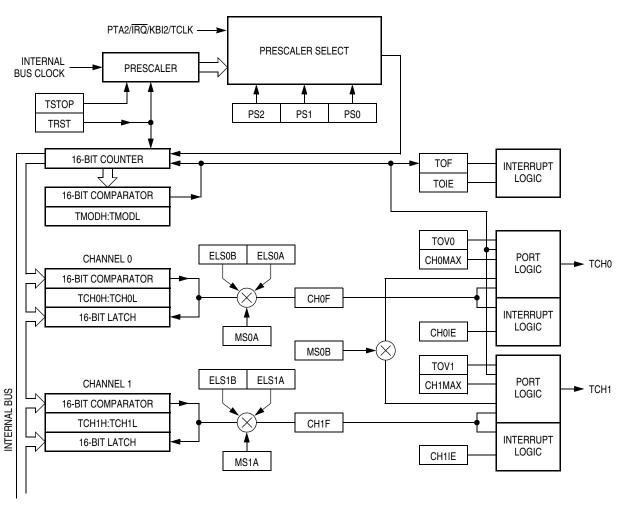

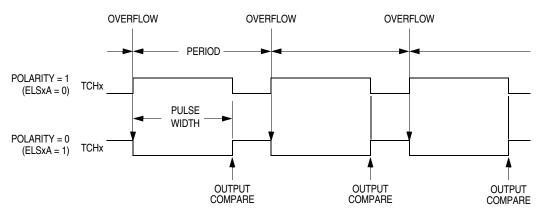

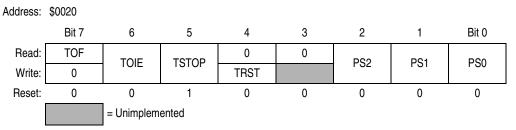

| Section 15. Timer Interface Module (TIM)137                       |

| Section 16. Development Support155                                |

| Section 17. Electrical Specifications                             |

| Section 18. Ordering Information and Mechanical Specifications193 |

MC68HC908QF4 — Rev. 1.0 Data Sheet

Go to: www.freescale.com

**List of Sections**

## Data Sheet — MC68HC908QF4

# **Table of Contents**

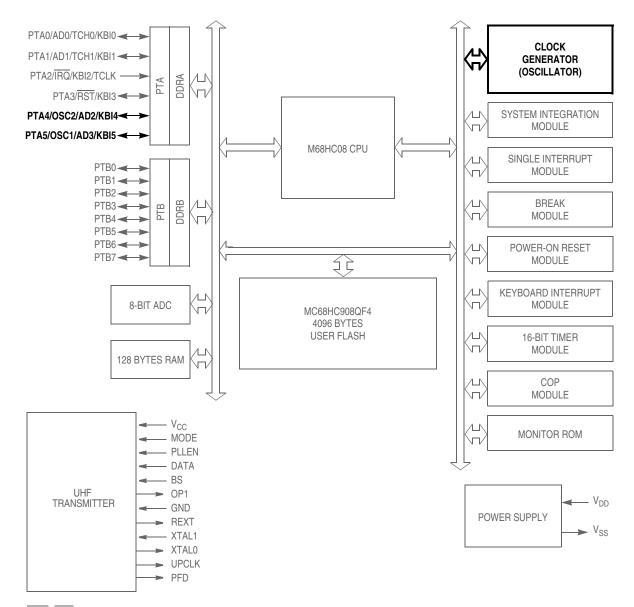

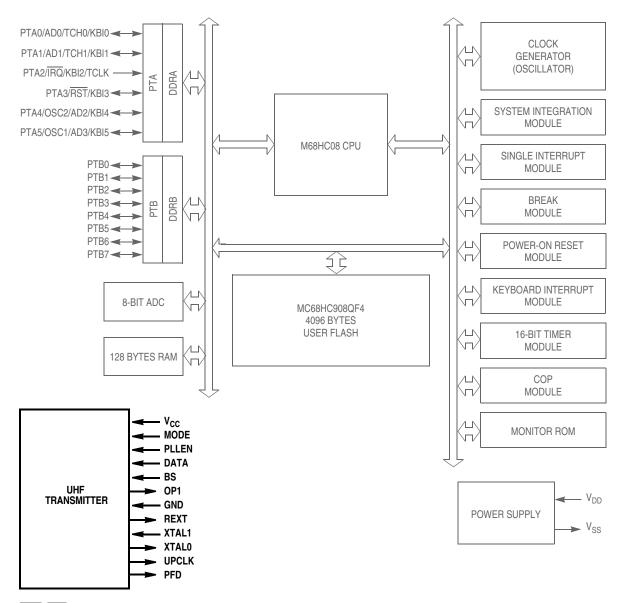

**Section 1. General Description**

| 1.1                                              | Introduction                                                                                                                                      |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                              | Features                                                                                                                                          |

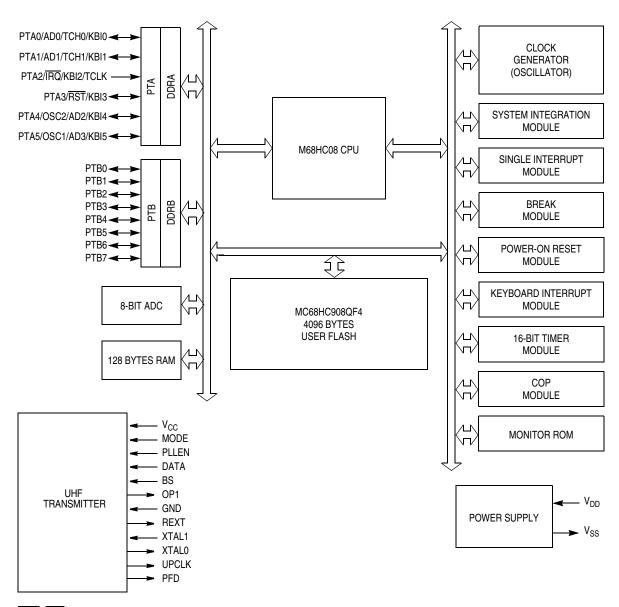

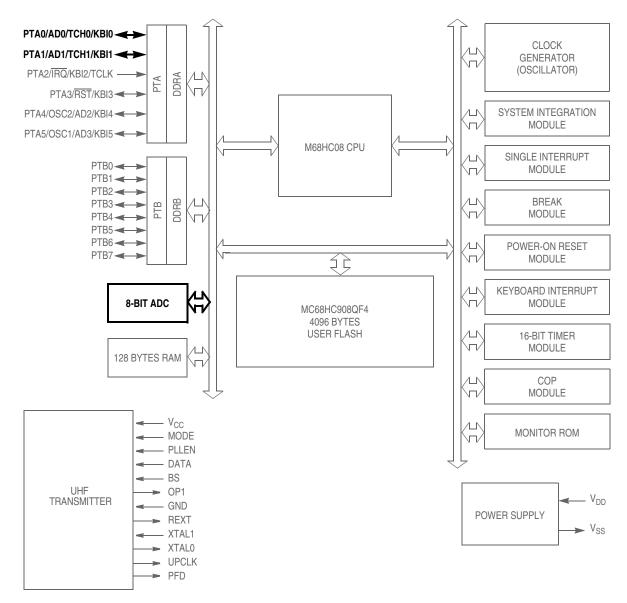

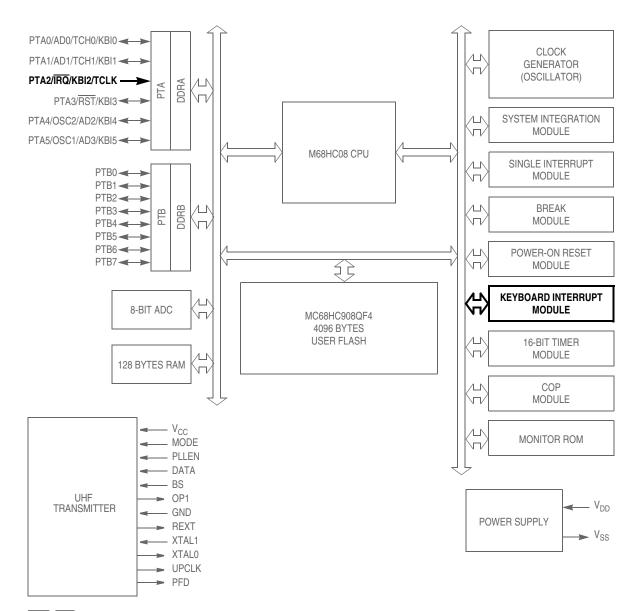

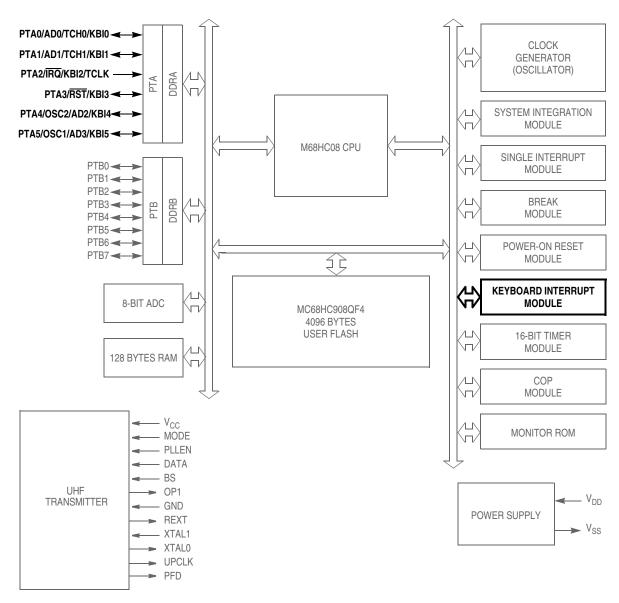

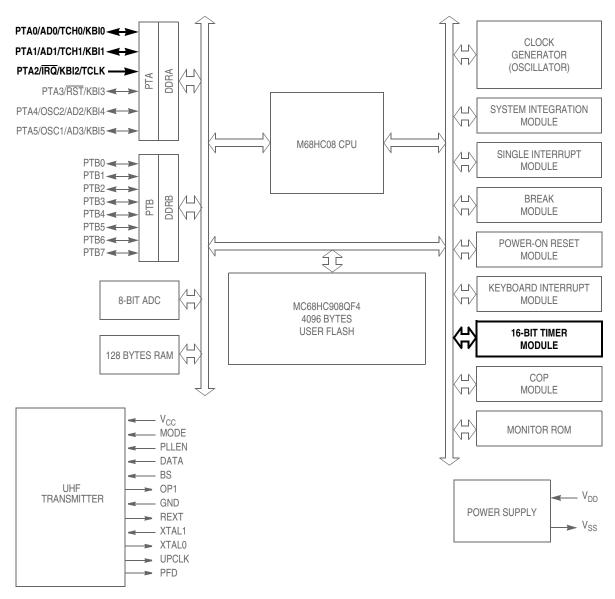

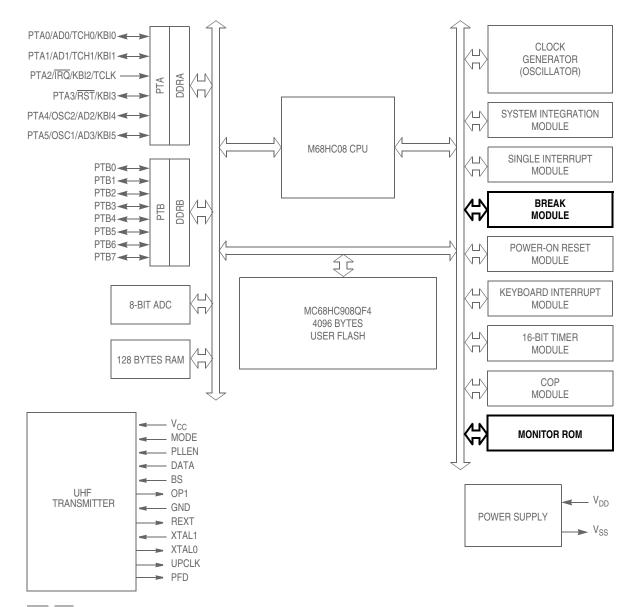

| 1.3                                              | MCU Block Diagram                                                                                                                                 |

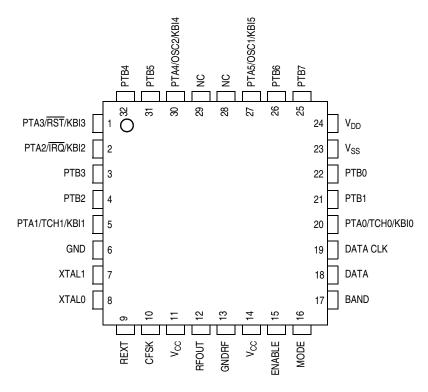

| 1.4                                              | Pin Assignments                                                                                                                                   |

| 1.5                                              | Pin Functions                                                                                                                                     |

|                                                  |                                                                                                                                                   |

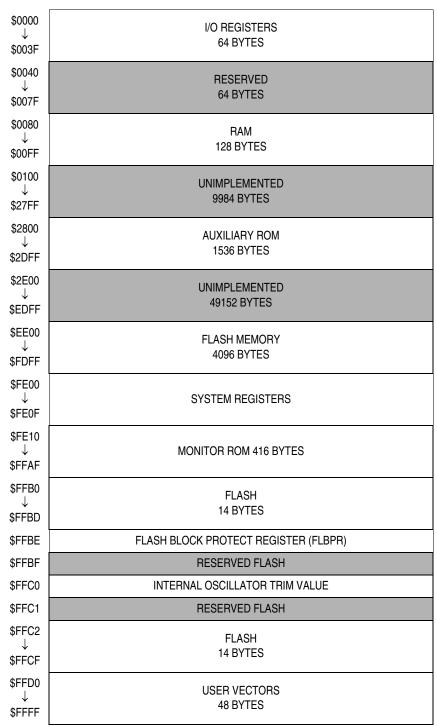

|                                                  | Section 2. Memory                                                                                                                                 |

| 2.1                                              | Introduction                                                                                                                                      |

| 2.2                                              | Unimplemented Memory Locations                                                                                                                    |

| 2.3                                              | Reserved Memory Locations                                                                                                                         |

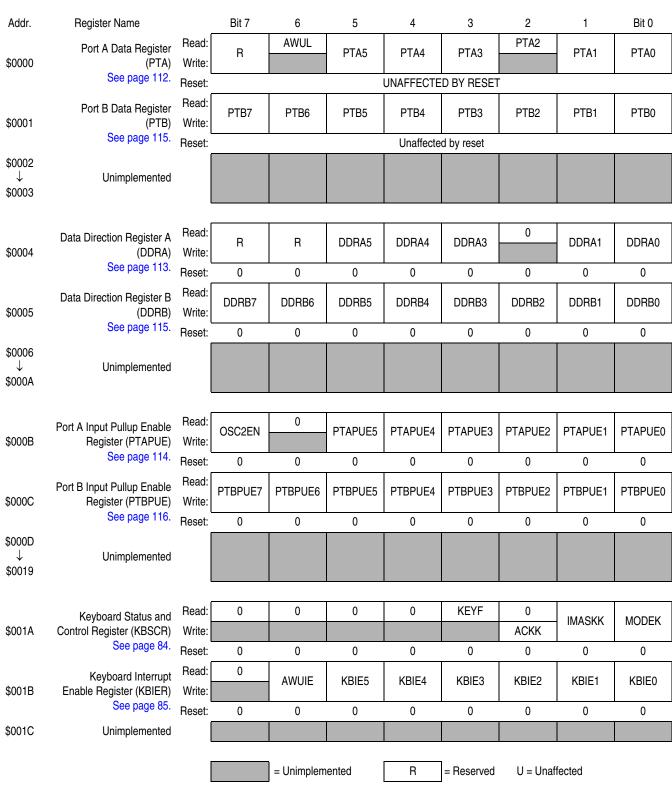

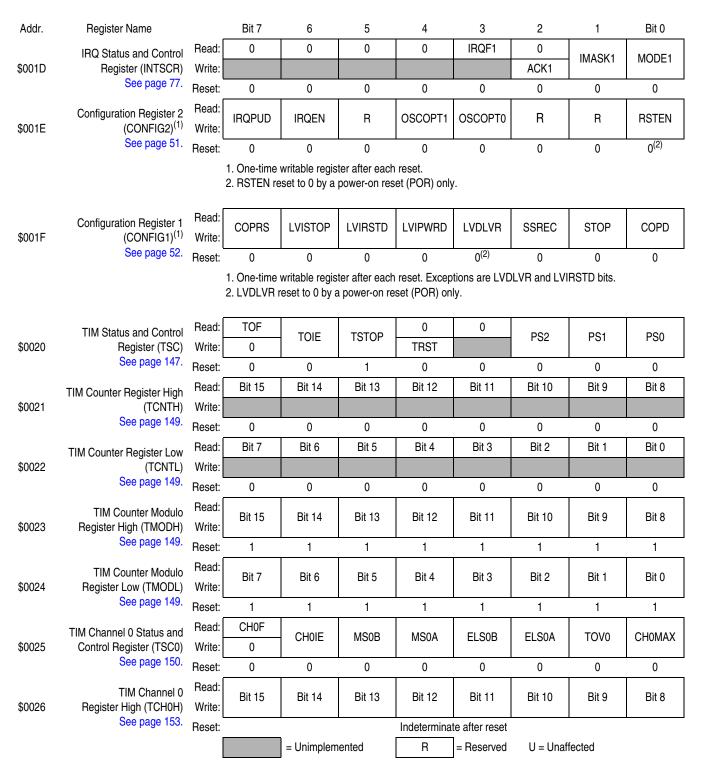

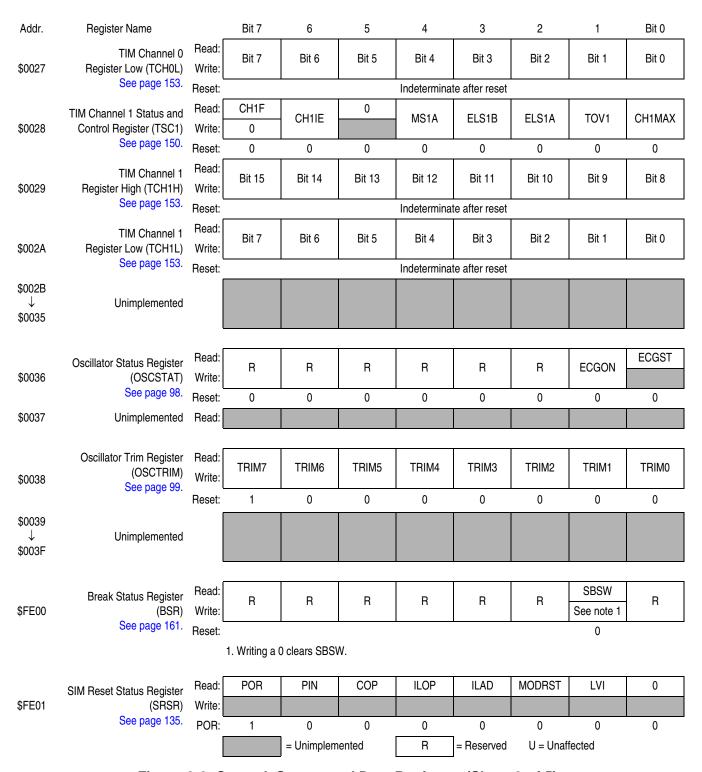

| 2.4                                              | Input/Output (I/O) Section                                                                                                                        |

| 2.5                                              | Random-Access Memory (RAM)                                                                                                                        |

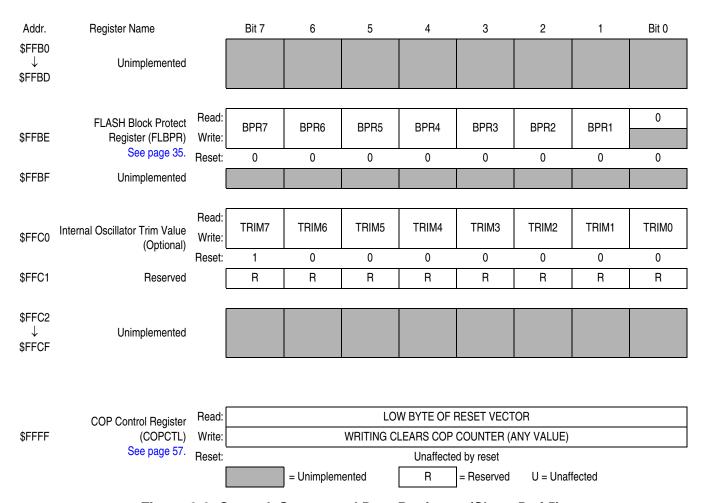

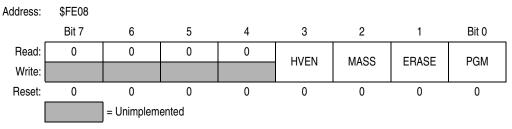

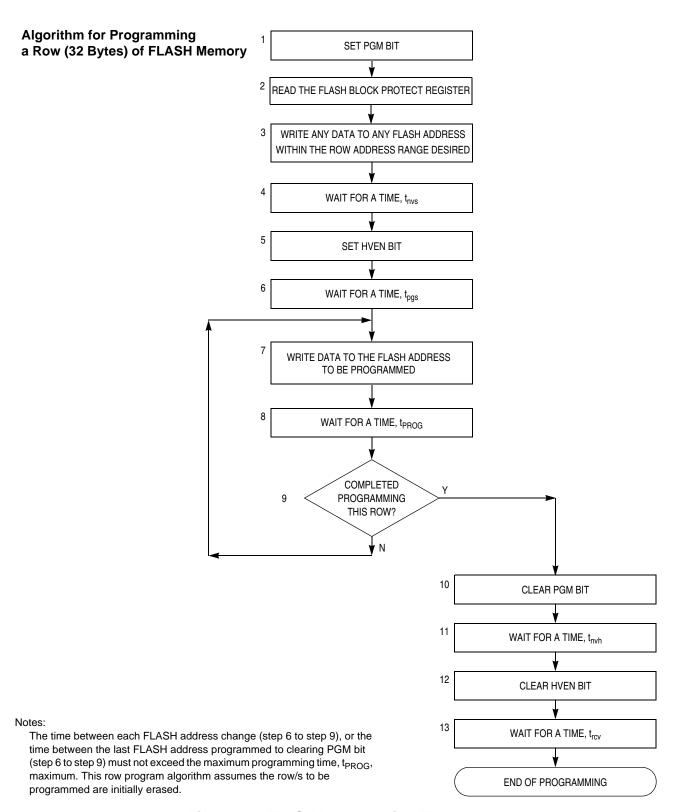

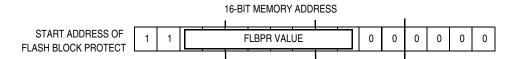

| 2.6<br>2.6.1<br>2.6.2<br>2.6.3<br>2.6.4<br>2.6.5 | FLASH Memory (FLASH)30FLASH Control Register30FLASH Page Erase Operation31FLASH Mass Erase Operation32FLASH Program Operation32FLASH Protection33 |

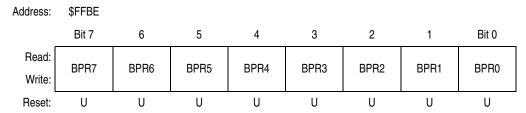

| 2.6.6                                            | FLASH Block Protect Register                                                                                                                      |

| 2.6.7                                            | Wait Mode                                                                                                                                         |

| 2.6.8                                            | Stop Mode                                                                                                                                         |

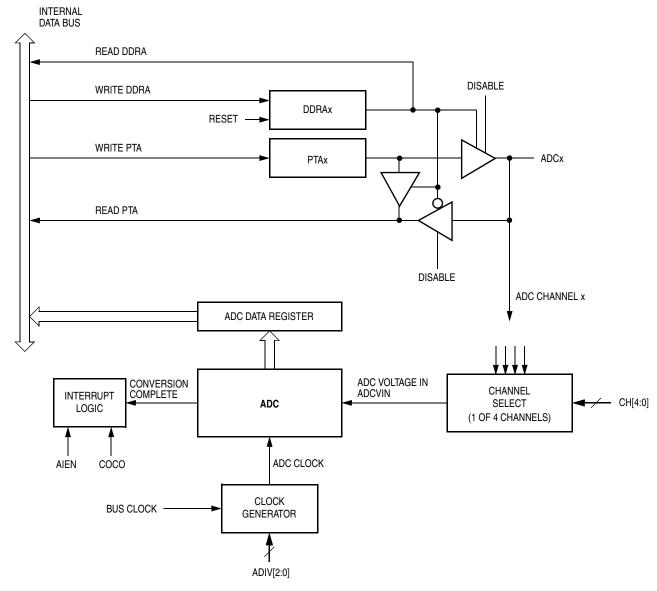

|                                                  | Section 3. Analog-to-Digital Converter (ADC)                                                                                                      |

| 3.1                                              | Introduction                                                                                                                                      |

| 3.2                                              | Features                                                                                                                                          |

| 3.3                                              | Functional Description                                                                                                                            |

| 3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5        | ADC Port I/O Pins. 40 Voltage Conversion 40 Conversion Time. 40 Continuous Conversion 40 Accuracy and Precision 40                                |

| 3.4                                              | Interrupts                                                                                                                                        |

|                                                  |                                                                                                                                                   |

MC68HC908QF4 — Rev. 1.0

Data Sheet

8

# **Table of Contents**

| 3.5<br>3.5.1<br>3.5.2                                                                                   | Wait Mode                                                                                                                                                                                                                                                                                             | . 41                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.6                                                                                                     | •                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                        |

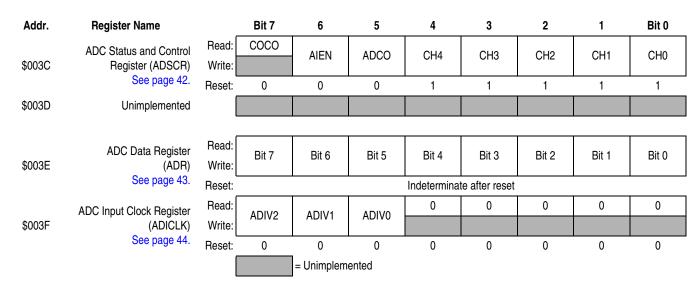

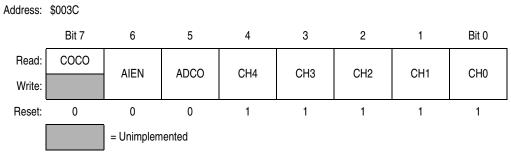

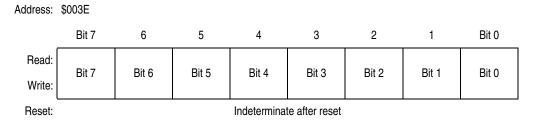

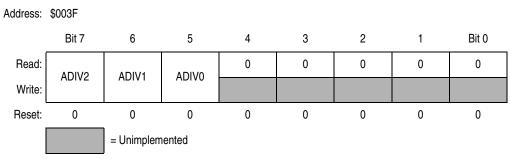

| 3.7<br>3.7.1<br>3.7.2<br>3.7.3                                                                          | ADC Status and Control Register                                                                                                                                                                                                                                                                       | . 42                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                         | Section 4. Auto Wakeup Module (AWU)                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                        |

| 4.1                                                                                                     | Introduction                                                                                                                                                                                                                                                                                          | . 45                                                                                                                                                                                                                                                                                                                                                                   |

| 4.2                                                                                                     | Features                                                                                                                                                                                                                                                                                              | . 45                                                                                                                                                                                                                                                                                                                                                                   |

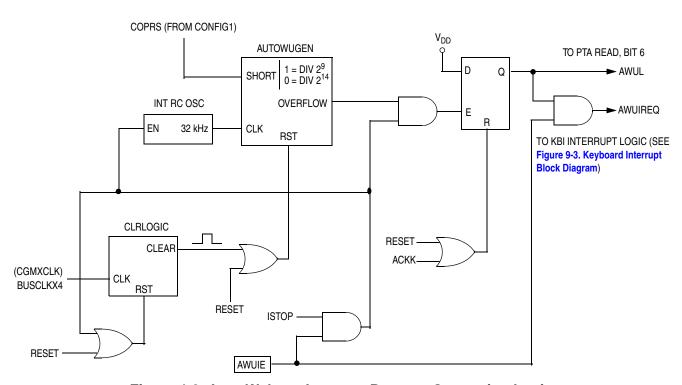

| 4.3                                                                                                     | Functional Description                                                                                                                                                                                                                                                                                | . 46                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4                                                                                                     | Wait Mode                                                                                                                                                                                                                                                                                             | . 47                                                                                                                                                                                                                                                                                                                                                                   |

| 4.5                                                                                                     | Stop Mode                                                                                                                                                                                                                                                                                             | . 47                                                                                                                                                                                                                                                                                                                                                                   |

| 4.6                                                                                                     |                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                        |

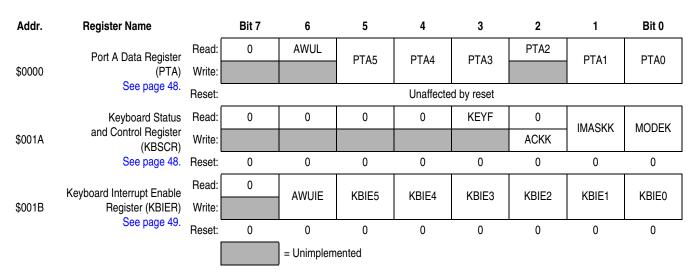

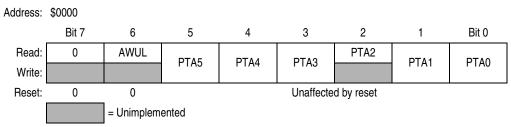

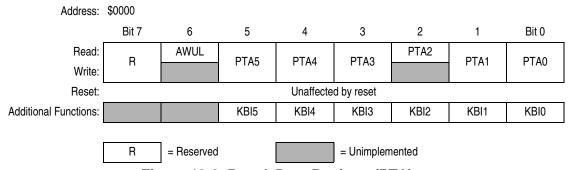

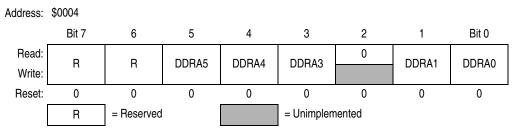

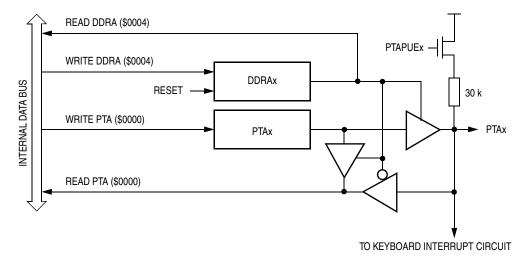

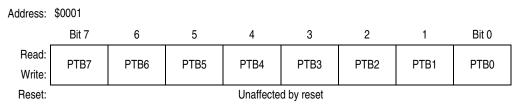

|                                                                                                         | Port A I/O Register                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                         |                                                                                                                                                                                                                                                                                                       | . 40                                                                                                                                                                                                                                                                                                                                                                   |

| 4.6.2<br>4.6.3                                                                                          | Keyboard Interrupt Enable Register                                                                                                                                                                                                                                                                    | . 49                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                         |                                                                                                                                                                                                                                                                                                       | . 49                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                         | Keyboard Interrupt Enable Register                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                        |

| 4.6.3                                                                                                   | Section 5. Configuration Register (CONFIG)                                                                                                                                                                                                                                                            | . 51                                                                                                                                                                                                                                                                                                                                                                   |

| <ul><li>4.6.3</li><li>5.1</li></ul>                                                                     | Section 5. Configuration Register (CONFIG) Introduction.                                                                                                                                                                                                                                              | . 51                                                                                                                                                                                                                                                                                                                                                                   |

| <ul><li>4.6.3</li><li>5.1</li></ul>                                                                     | Section 5. Configuration Register (CONFIG) Introduction Functional Description                                                                                                                                                                                                                        | . 51<br>. 51                                                                                                                                                                                                                                                                                                                                                           |

| <ul><li>4.6.3</li><li>5.1</li><li>5.2</li></ul>                                                         | Section 5. Configuration Register (CONFIG) Introduction. Functional Description Section 6. Computer Operating Properly (COP)                                                                                                                                                                          | . 51<br>. 51                                                                                                                                                                                                                                                                                                                                                           |

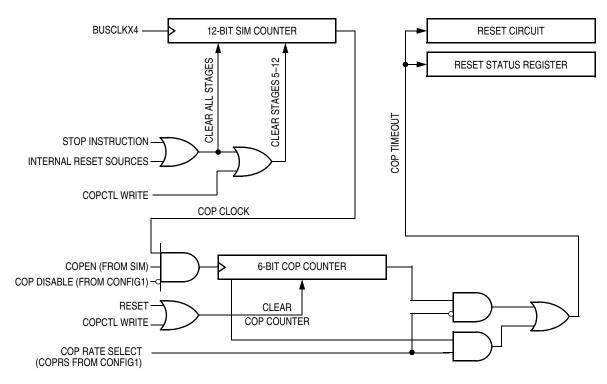

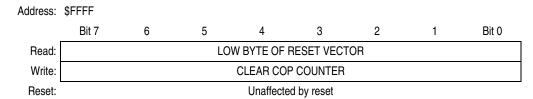

| <ul><li>4.6.3</li><li>5.1</li><li>5.2</li><li>6.1</li></ul>                                             | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals                                                                                                                       | . 51<br>. 51<br>. 55<br>. 55                                                                                                                                                                                                                                                                                                                                           |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1                                                       | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals BUSCLKX4.                                                                                                             | . 51<br>. 51<br>. 55<br>. 55<br>. 56                                                                                                                                                                                                                                                                                                                                   |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2                                              | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals BUSCLKX4 STOP Instruction                                                                                             | . 51<br>. 55<br>. 55<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                                   |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                            | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals BUSCLKX4 STOP Instruction COPCTL Write Power-On Reset                                                                 | . 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                           |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5                   | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals  BUSCLKX4  STOP Instruction  COPCTL Write  Power-On Reset Internal Reset                                              | . 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                   |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                            | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals BUSCLKX4 STOP Instruction COPCTL Write Power-On Reset                                                                 | . 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56                                                                                                                                                                                                                                                                                                                   |

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6          | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals  BUSCLKX4  STOP Instruction  COPCTL Write  Power-On Reset Internal Reset  COPD (COP Disable)                          | . 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 56<br>. 57                                                                                                                                                                                                                                                                                                   |

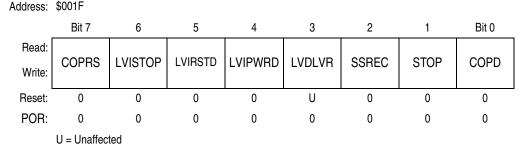

| 4.6.3<br>5.1<br>5.2<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5<br>6.3.6<br>6.3.7 | Section 5. Configuration Register (CONFIG) Introduction. Functional Description  Section 6. Computer Operating Properly (COP) Introduction. Functional Description  I/O Signals  BUSCLKX4  STOP Instruction  COPCTL Write  Power-On Reset Internal Reset  COPD (COP Disable)  COPRS (COP Rate Select) | . 51<br>. 55<br>. 55<br>. 56<br>. 56<br>. 56<br>. 56<br>. 57<br>. 57                                                                                                                                                                                                                                                                                                   |

|                                                                                                         | 3.5.1<br>3.5.2<br>3.6<br>3.7<br>3.7.1<br>3.7.2<br>3.7.3<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.6.1                                                                                                                                                                                            | 3.5.1 Wait Mode. 3.5.2 Stop Mode 3.6 Input/Output Signals. 3.7 Input/Output Registers 3.7.1 ADC Status and Control Register. 3.7.2 ADC Data Register. 3.7.3 ADC Input Clock Register.  Section 4. Auto Wakeup Module (AWU) 4.1 Introduction. 4.2 Features 4.3 Functional Description 4.4 Wait Mode 4.5 Stop Mode 4.6 Input/Output Registers 4.6.1 Port A I/O Register. |

| 6.7<br>6.7.1<br>6.7.2                                                         | Low-Power Modes                                                                                                                                                                                                                                                                                     | . 57                                                                 |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 6.8                                                                           | COP Module During Break Mode                                                                                                                                                                                                                                                                        |                                                                      |

|                                                                               | Section 7. Central Processor Unit (CPU)                                                                                                                                                                                                                                                             |                                                                      |

| 7.1                                                                           | Introduction                                                                                                                                                                                                                                                                                        | . 59                                                                 |

| 7.2                                                                           | Features                                                                                                                                                                                                                                                                                            | . 59                                                                 |

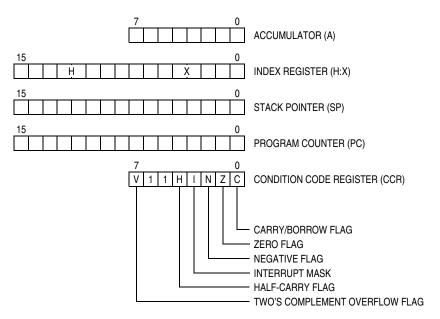

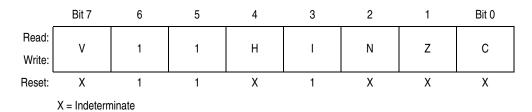

| 7.3<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>7.3.5                              | CPU Registers  Accumulator  Index Register.  Stack Pointer  Program Counter  Condition Code Register.                                                                                                                                                                                               | . 60<br>. 61<br>. 61<br>. 62<br>. 62                                 |

| 7.4                                                                           | Arithmetic/Logic Unit (ALU)                                                                                                                                                                                                                                                                         |                                                                      |

| 7.5<br>7.5.1<br>7.5.2<br>7.6                                                  | Low-Power Modes                                                                                                                                                                                                                                                                                     | . 64<br>. 64                                                         |

| 7.7                                                                           | Instruction Set Summary                                                                                                                                                                                                                                                                             |                                                                      |

| 7.8                                                                           | Opcode Map                                                                                                                                                                                                                                                                                          |                                                                      |

|                                                                               | opoodo map                                                                                                                                                                                                                                                                                          | . , ,                                                                |

|                                                                               | Section 8. External Interrupt (IRQ)                                                                                                                                                                                                                                                                 | . , .                                                                |

| 8.1                                                                           |                                                                                                                                                                                                                                                                                                     |                                                                      |

|                                                                               | Section 8. External Interrupt (IRQ)                                                                                                                                                                                                                                                                 | . 73                                                                 |

| 8.1                                                                           | Section 8. External Interrupt (IRQ) Introduction                                                                                                                                                                                                                                                    | . 73<br>. 73                                                         |

| 8.1<br>8.2                                                                    | Section 8. External Interrupt (IRQ) Introduction Features                                                                                                                                                                                                                                           | . 73<br>. 73<br>. 73                                                 |

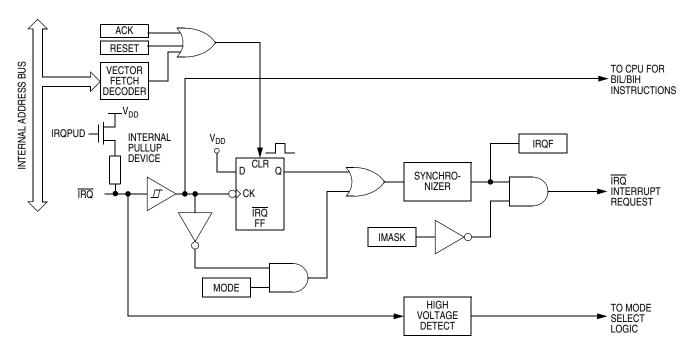

| 8.1<br>8.2<br>8.3                                                             | Section 8. External Interrupt (IRQ) Introduction Features Functional Description                                                                                                                                                                                                                    | . 73<br>. 73<br>. 73<br>. 76                                         |

| 8.1<br>8.2<br>8.3<br>8.4                                                      | Section 8. External Interrupt (IRQ) Introduction. Features Functional Description IRQ Pin.                                                                                                                                                                                                          | . 73<br>. 73<br>. 73<br>. 76                                         |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                               | Section 8. External Interrupt (IRQ) Introduction Features Functional Description IRQ Pin IRQ Module During Break Interrupts                                                                                                                                                                         | . 73<br>. 73<br>. 73<br>. 76                                         |

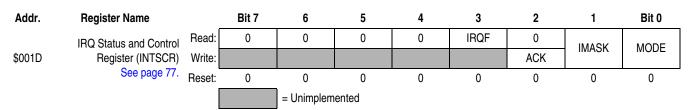

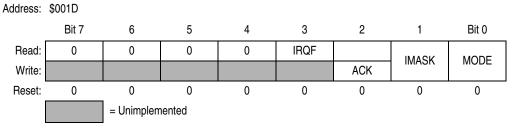

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                               | Section 8. External Interrupt (IRQ) Introduction. Features Functional Description IRQ Pin IRQ Module During Break Interrupts IRQ Status and Control Register                                                                                                                                        | . 73<br>. 73<br>. 73<br>. 76<br>. 76                                 |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                        | Section 8. External Interrupt (IRQ) Introduction Features Functional Description IRQ Pin IRQ Module During Break Interrupts IRQ Status and Control Register Section 9. Keyboard Interrupt Module (KBI)                                                                                              | . 73<br>. 73<br>. 73<br>. 76<br>. 76                                 |

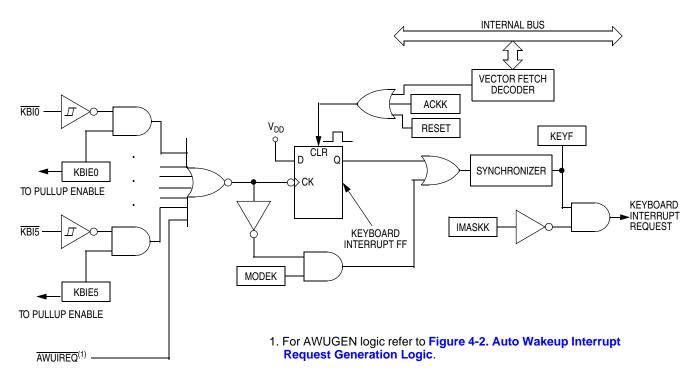

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>9.1<br>9.2<br>9.3<br>9.3.1<br>9.3.2 | Section 8. External Interrupt (IRQ) Introduction. Features Functional Description IRQ Pin. IRQ Module During Break Interrupts IRQ Status and Control Register  Section 9. Keyboard Interrupt Module (KBI) Introduction. Features Functional Description Keyboard Operation Keyboard Initialization. | . 73<br>. 73<br>. 76<br>. 76<br>. 77<br>. 79<br>. 81<br>. 81         |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>9.1<br>9.2<br>9.3<br>9.3.1          | Section 8. External Interrupt (IRQ)  Introduction.  Features.  Functional Description.  IRQ Pin.  IRQ Module During Break Interrupts  IRQ Status and Control Register.  Section 9. Keyboard Interrupt Module (KBI)  Introduction.  Features.  Functional Description  Keyboard Operation            | . 73<br>. 73<br>. 76<br>. 76<br>. 77<br>. 79<br>. 81<br>. 81<br>. 83 |

MC68HC908QF4 — Rev. 1.0

**Data Sheet**

# **Table of Contents**

| 9.6                                                                                                                                  | Keyboard Module During Break Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 9.7                                                                                                                                  | Input/Output Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84                                                                   |

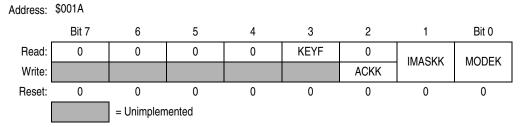

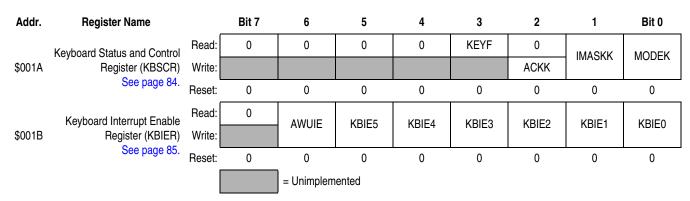

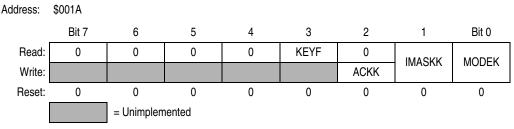

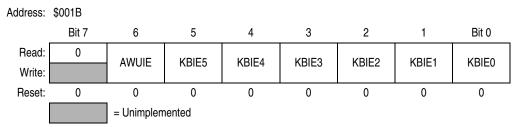

| 9.7.1                                                                                                                                | Keyboard Status and Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 84                                                                   |

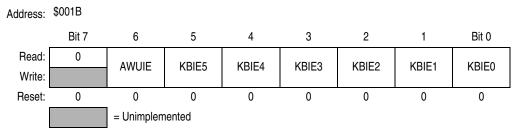

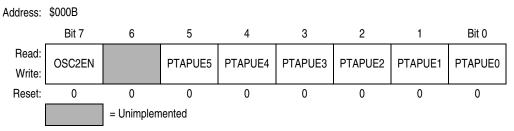

| 9.7.2                                                                                                                                | Keyboard Interrupt Enable Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85                                                                   |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

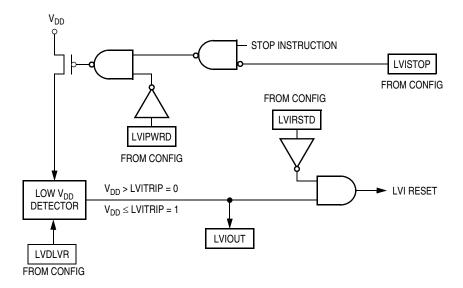

|                                                                                                                                      | Section 10. Low-Voltage Inhibit (LVI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

| 10.1                                                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                                   |

| 10.2                                                                                                                                 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87                                                                   |

| 10.3                                                                                                                                 | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                   |

| 10.3.1                                                                                                                               | Polled LVI Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88                                                                   |

| 10.3.2                                                                                                                               | Forced Reset Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| 10.3.3                                                                                                                               | Voltage Hysteresis Protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| 10.3.4                                                                                                                               | LVI Trip Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

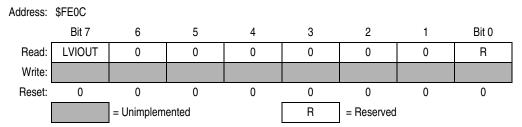

| 10.4                                                                                                                                 | LVI Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 10.5                                                                                                                                 | LVI Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90                                                                   |

| 10.6                                                                                                                                 | Low-Power Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90                                                                   |

| 10.6.1                                                                                                                               | Wait Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 10.6.2                                                                                                                               | Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90                                                                   |

|                                                                                                                                      | Section 11. Oscillator Module (OSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 44.4                                                                                                                                 | ` '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                      |

| 111                                                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 01                                                                   |

| 11.1                                                                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

| 11.2                                                                                                                                 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91                                                                   |

| 11.2<br>11.3                                                                                                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91                                                             |

| 11.2<br>11.3<br>11.3.1                                                                                                               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91<br>91                                                       |

| 11.2<br>11.3<br>11.3.1<br>11.3.1                                                                                                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91<br>91<br>93                                                 |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.1                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91<br>91<br>93<br>93                                           |

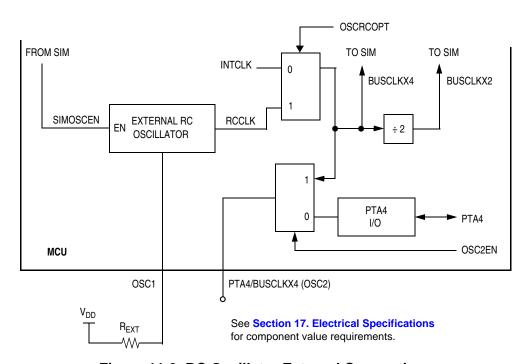

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.1<br>11.3.2                                                                                 | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91<br>93<br>93<br>94                                           |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.1                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91<br>91<br>93<br>93<br>94<br>94                                     |

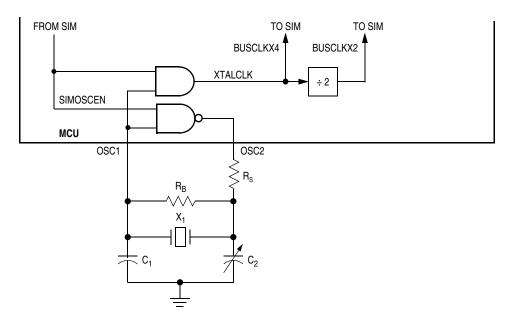

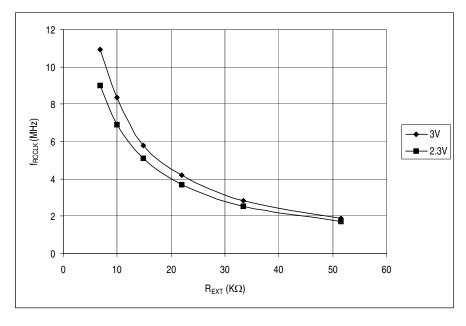

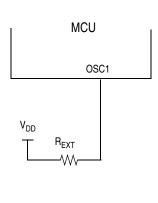

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3                                                                                 | Features  Functional Description  Internal Oscillator  Internal Oscillator Trimming  Internal to External Clock Switching  External Oscillator  XTAL Oscillator  RC Oscillator                                                                                                                                                                                                                                                                                                                                | 91<br>91<br>93<br>93<br>94<br>94                                     |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4                                                                       | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator Oscillator Module Signals                                                                                                                                                                                                                                                                                                           | 91<br>91<br>93<br>93<br>94<br>94<br>95                               |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4                                                               | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming  Internal to External Clock Switching External Oscillator.  XTAL Oscillator.  RC Oscillator.  RC Oscillator.  Oscillator Module Signals  Crystal Amplifier Input Pin (OSC1)  Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)                                                                                                                                                                                             | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>95<br>96                   |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.1<br>11.4.2<br>11.4.3                                 | Features  Functional Description Internal Oscillator  I Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator RC Oscillator Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN)                                                                                                                                                                                            | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>95<br>96                   |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4                       | Features  Functional Description Internal Oscillator  I Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator RC Oscillator Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN) XTAL Oscillator Clock (XTALCLK)                                                                                                                                                            | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>96<br>96<br>96             |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5             | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming Internal to External Clock Switching External Oscillator  XTAL Oscillator  RC Oscillator  Oscillator Module Signals  Crystal Amplifier Input Pin (OSC1)  Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)  Oscillator Enable Signal (SIMOSCEN)  XTAL Oscillator Clock (XTALCLK)  RC Oscillator Clock (RCCLK)                                                                                                              | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>96<br>96<br>96             |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6   | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator RC Oscillator Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN) XTAL Oscillator Clock (XTALCLK) RC Oscillator Clock (RCCLK) Internal Oscillator Clock (INTCLK)                                                                                               | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>96<br>96<br>96<br>97       |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6<br>11.4.7   | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator Oscillator Module Signals Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN) XTAL Oscillator Clock (XTALCLK) RC Oscillator Clock (RCCLK) Internal Oscillator Clock (INTCLK) Oscillator Out 2 (BUSCLKX4)                                                       | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>96<br>96<br>96<br>97<br>97 |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6<br>11.4.7 | Features  Functional Description Internal Oscillator  I Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator RC Oscillator Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN) XTAL Oscillator Clock (XTALCLK) RC Oscillator Clock (RCCLK) Internal Oscillator Clock (INTCLK) Oscillator Out 2 (BUSCLKX4) Oscillator Out (BUSCLKX2)                                       | 91<br>91<br>93<br>93<br>94<br>95<br>95<br>96<br>96<br>96<br>97<br>97 |

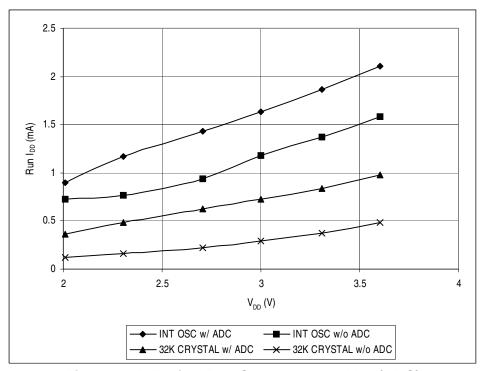

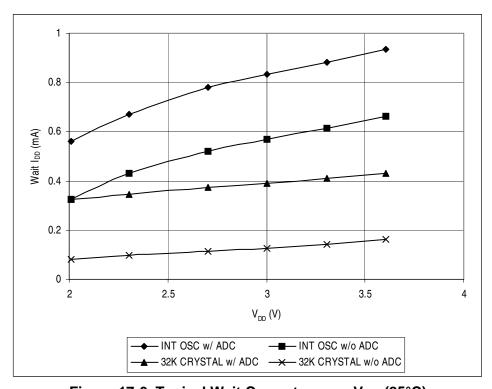

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6<br>11.4.7   | Features  Functional Description Internal Oscillator  Internal Oscillator Trimming  Internal to External Clock Switching External Oscillator  XTAL Oscillator  RC Oscillator  Oscillator Module Signals  Crystal Amplifier Input Pin (OSC1)  Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4)  Oscillator Enable Signal (SIMOSCEN)  XTAL Oscillator Clock (XTALCLK)  RC Oscillator Clock (RCCLK) Internal Oscillator Clock (INTCLK)  Oscillator Out 2 (BUSCLKX4)  Oscillator Out (BUSCLKX2)  Low Power Modes | 91<br>91<br>93<br>94<br>95<br>95<br>96<br>96<br>96<br>97<br>97<br>97 |

| 11.2<br>11.3<br>11.3.1<br>11.3.1<br>11.3.2<br>11.3.3<br>11.3.4<br>11.4.1<br>11.4.2<br>11.4.3<br>11.4.4<br>11.4.5<br>11.4.6<br>11.4.7 | Features  Functional Description Internal Oscillator  I Internal Oscillator Trimming Internal to External Clock Switching External Oscillator XTAL Oscillator RC Oscillator RC Oscillator Crystal Amplifier Input Pin (OSC1) Crystal Amplifier Output Pin (OSC2/PTA4/BUSCLKX4) Oscillator Enable Signal (SIMOSCEN) XTAL Oscillator Clock (XTALCLK) RC Oscillator Clock (RCCLK) Internal Oscillator Clock (INTCLK) Oscillator Out 2 (BUSCLKX4) Oscillator Out (BUSCLKX2)                                       | 91<br>91<br>93<br>94<br>95<br>95<br>96<br>96<br>96<br>97<br>97<br>97 |

|                                                                                      | Oscillator During Break Mode                                                                                                                                                                                                                                                                                                                                                            | 97                                     |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

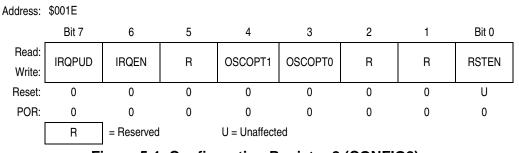

| 11.7                                                                                 | CONFIG2 Options                                                                                                                                                                                                                                                                                                                                                                         | 97                                     |

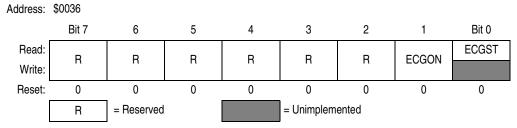

| 11.8                                                                                 | Input/Output (I/O) Registers                                                                                                                                                                                                                                                                                                                                                            | 98                                     |

| 11.8.                                                                                | <b>5</b>                                                                                                                                                                                                                                                                                                                                                                                |                                        |

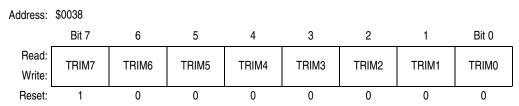

| 11.8.2                                                                               | Oscillator Trim Register (OSCTRIM)                                                                                                                                                                                                                                                                                                                                                      | 99                                     |

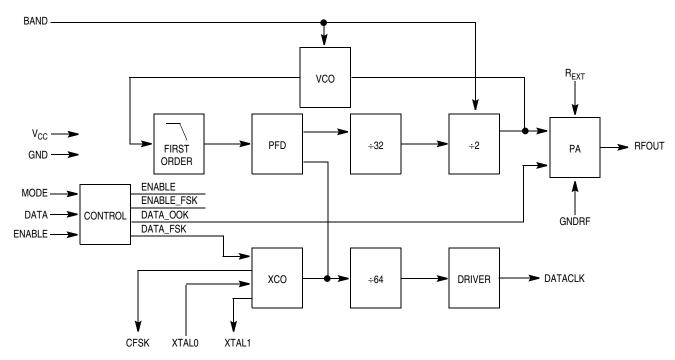

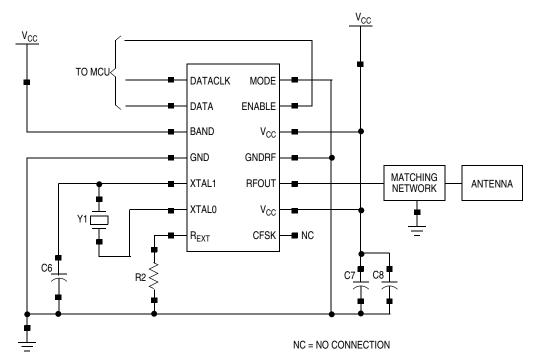

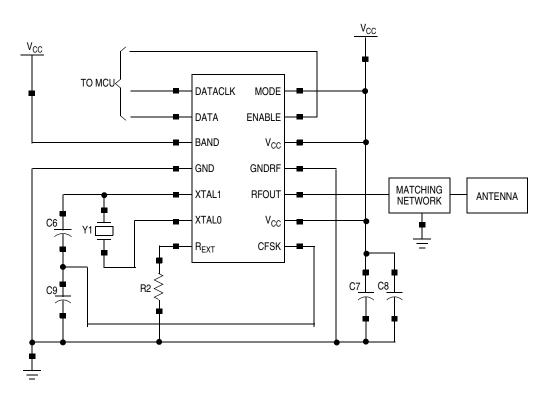

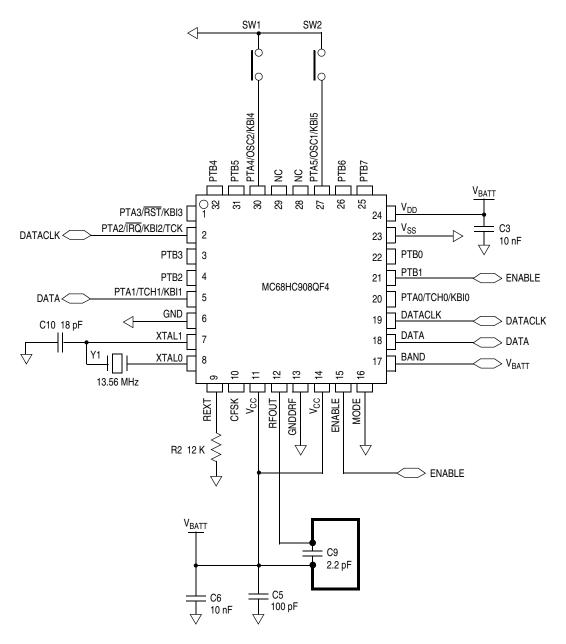

|                                                                                      | Section 12. PLL Tuned UHF Transmitter Module                                                                                                                                                                                                                                                                                                                                            |                                        |

| 12.1                                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                            | 101                                    |

| 12.2                                                                                 | Transmitter Functional Description                                                                                                                                                                                                                                                                                                                                                      | 103                                    |

| 12.3                                                                                 | Phase-Lock Loop (PLL) and Local Oscillator                                                                                                                                                                                                                                                                                                                                              | 103                                    |

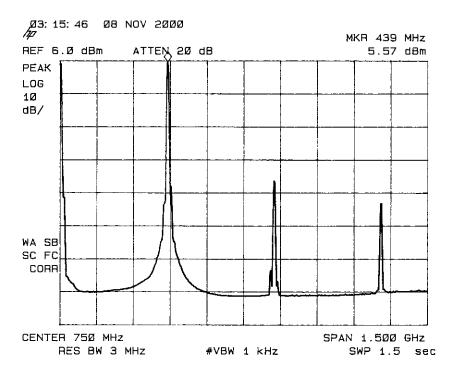

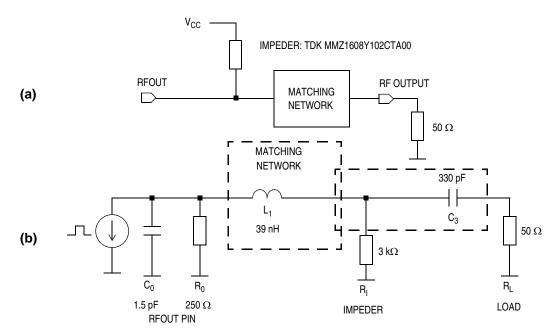

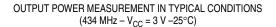

| 12.4                                                                                 | RF Output Stage                                                                                                                                                                                                                                                                                                                                                                         | 103                                    |

| 12.5                                                                                 | Modulation                                                                                                                                                                                                                                                                                                                                                                              | 104                                    |

| 12.6                                                                                 | Microcontroller Interfaces                                                                                                                                                                                                                                                                                                                                                              | 104                                    |

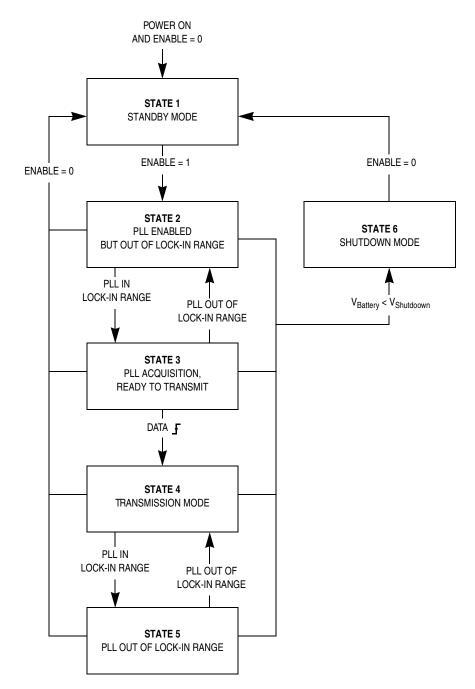

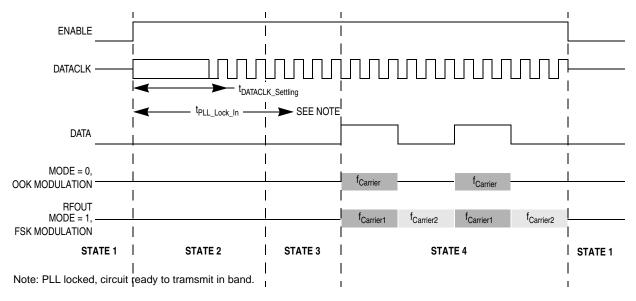

| 12.7                                                                                 | State Machine                                                                                                                                                                                                                                                                                                                                                                           | 105                                    |

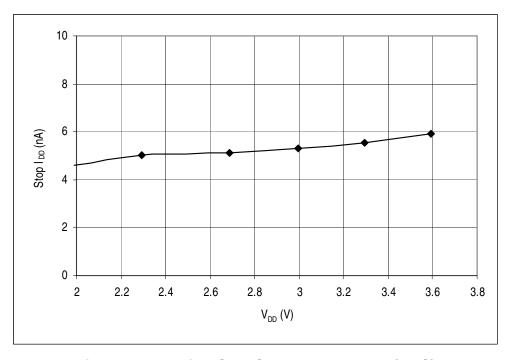

| 12.8                                                                                 | Power Management                                                                                                                                                                                                                                                                                                                                                                        | 107                                    |

| 12.9                                                                                 | Data Clock                                                                                                                                                                                                                                                                                                                                                                              | 107                                    |

| 12.10                                                                                | 1.1                                                                                                                                                                                                                                                                                                                                                                                     |                                        |

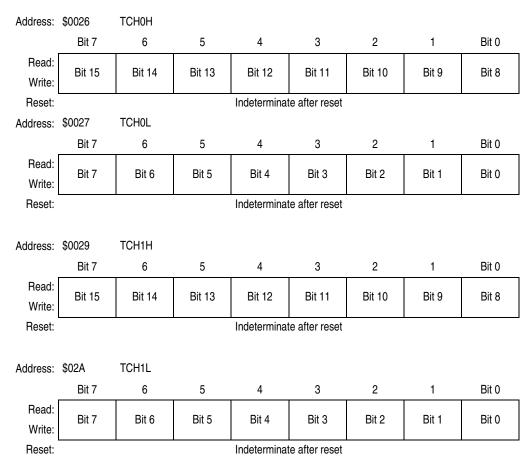

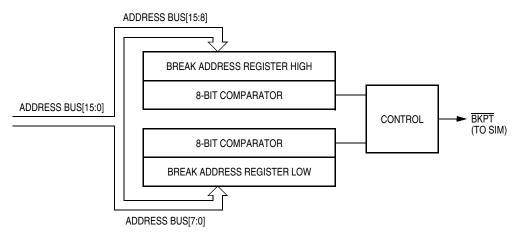

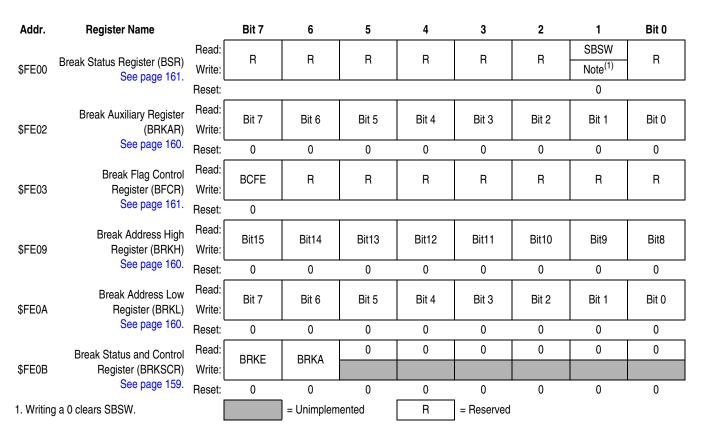

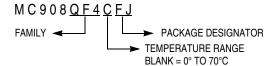

| 12.10<br>12.10                                                                       | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                 |                                        |