## ABOV SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS

# MC71PB204

**USER'S MANUAL (Ver. 1.0)**

## **TABLE OF CONTENTS**

| 1. PRODUCT OVERVIEW                    | 1   |

|----------------------------------------|-----|

| 2. MEMORY ORGANIZATION                 | 12  |

| 3. INTERRUPT                           | 26  |

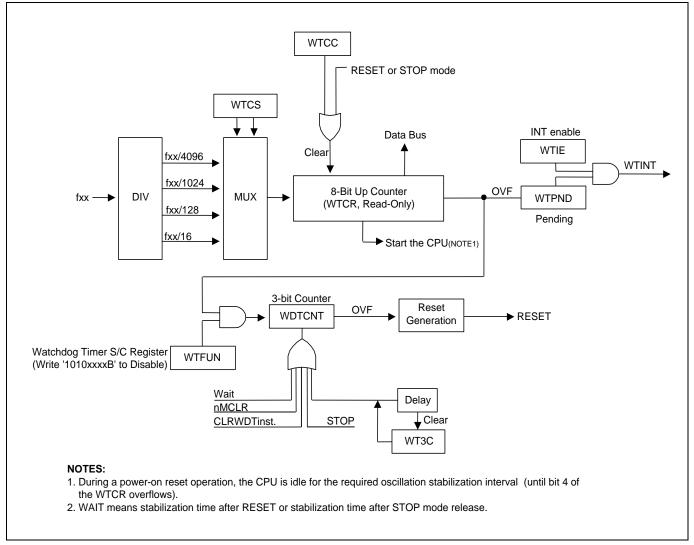

| 4. INSTRUCTION SET                     | 30  |

| 5. CLOCK CIRCUIT                       | 72  |

| 6. RESET AND POWER-DOWN MODE           | 78  |

| 7. I/O PORTS                           | 84  |

| 8. WATCHDOG TIMER                      | 94  |

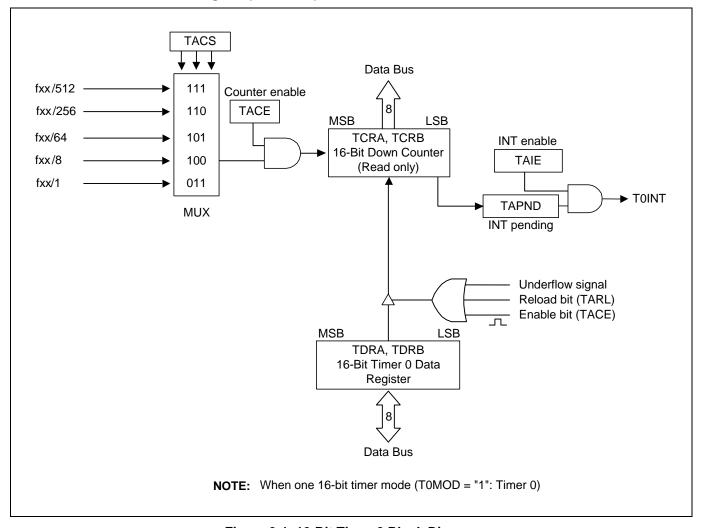

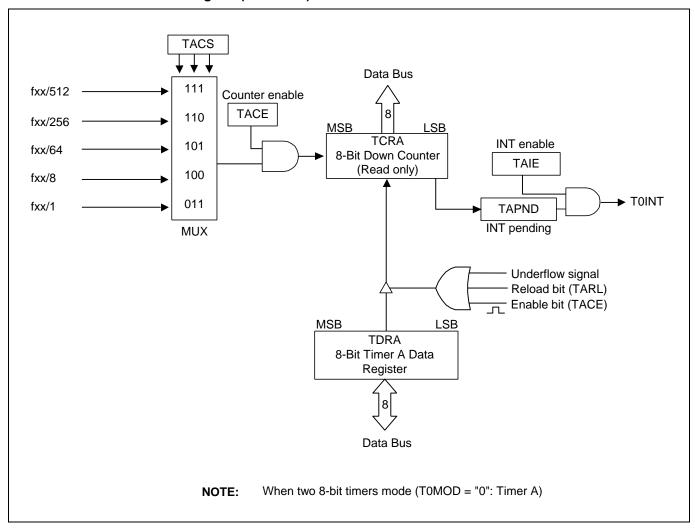

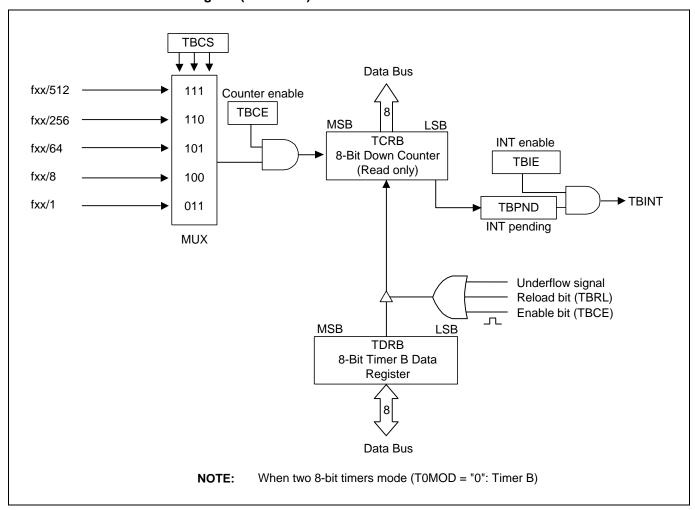

| 9. 16-BIT TIMER 0 (8-BIT TIMER A/B)    |     |

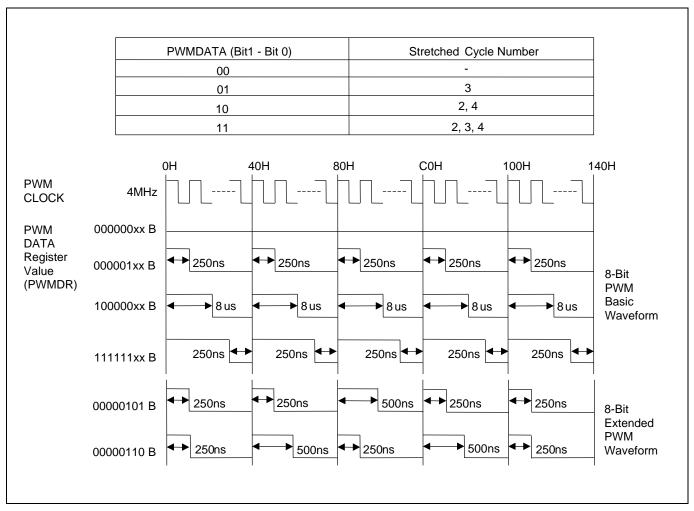

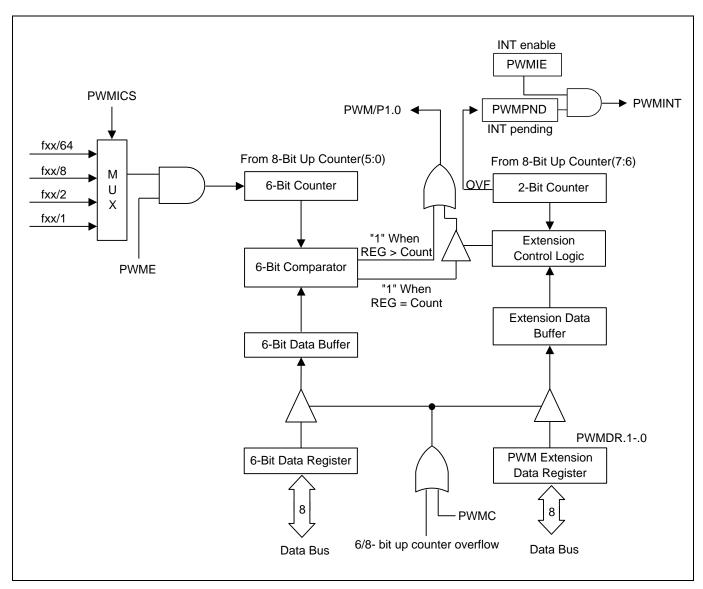

| 10. 6/8-BIT PWM                        | 106 |

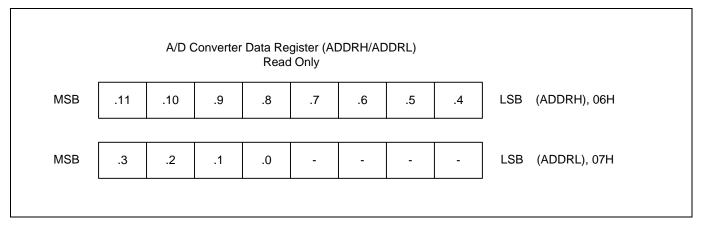

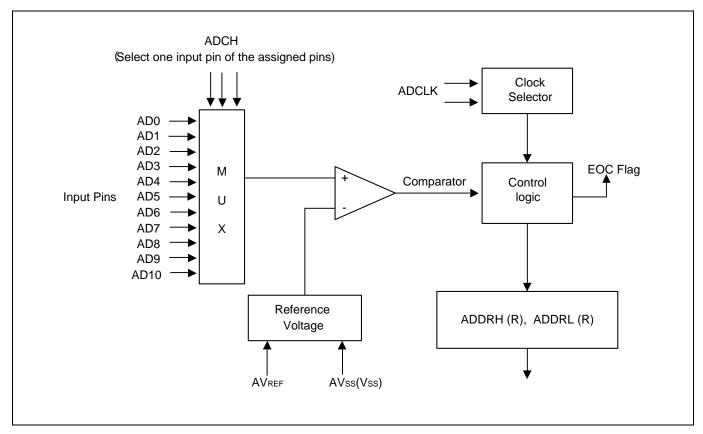

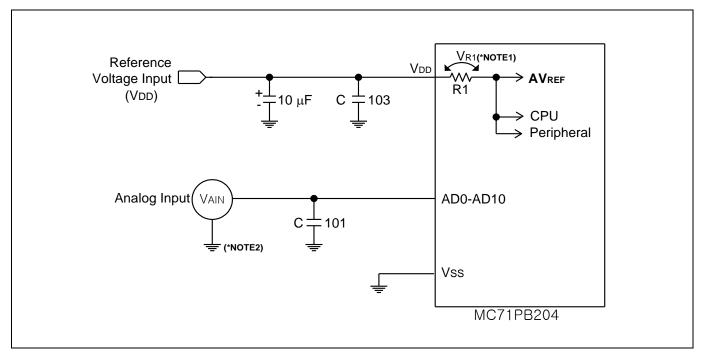

| 11. 12-BIT ANALOG TO DIGITAL CONVERTER | 110 |

| 12. ELECTRICAL DATA                    |     |

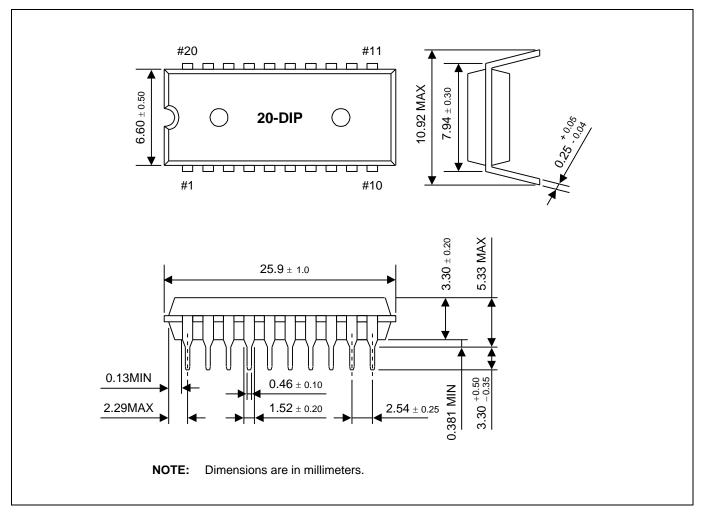

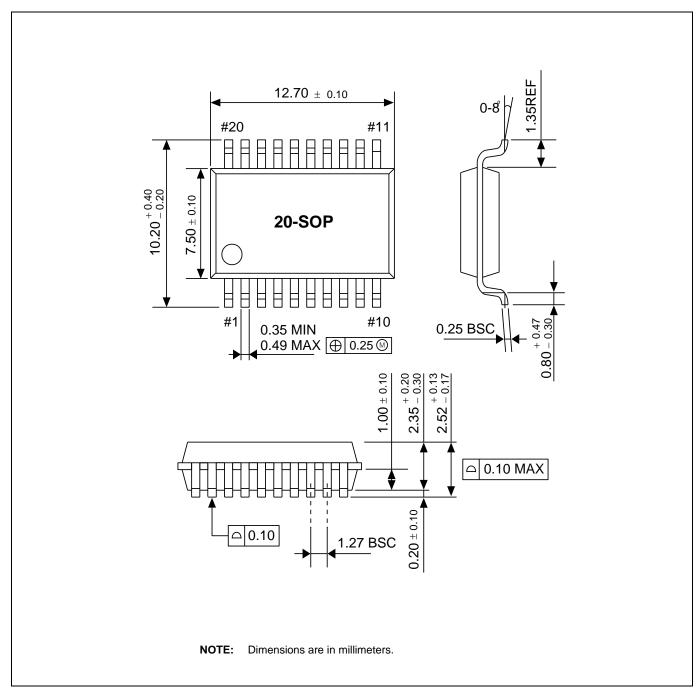

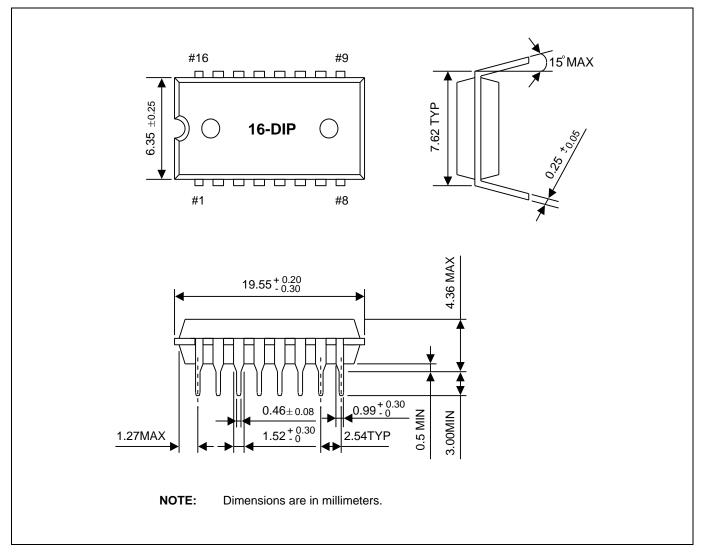

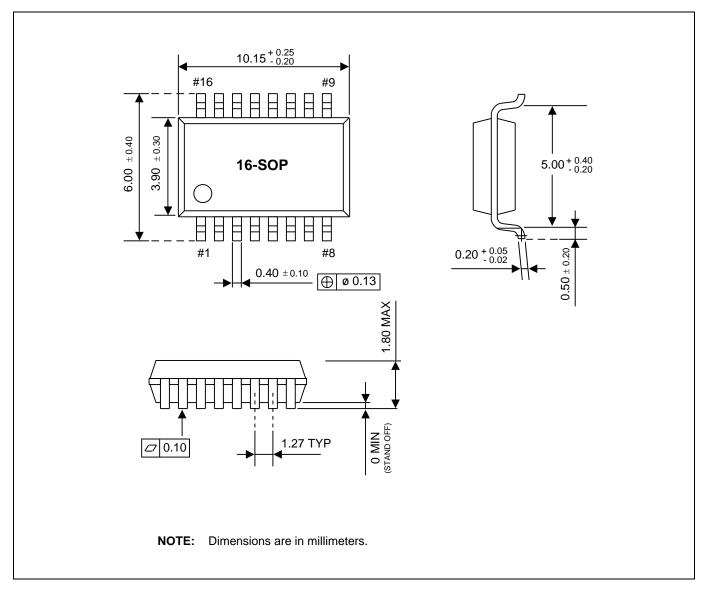

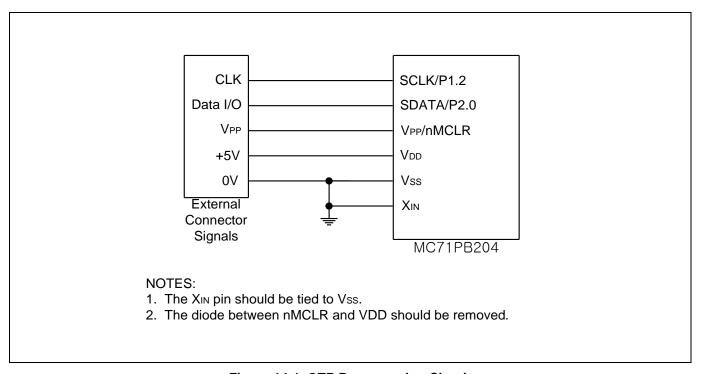

| 13. MECHANICAL DATA                    | 126 |

| 14. MC71PB204 OTP                      | 130 |

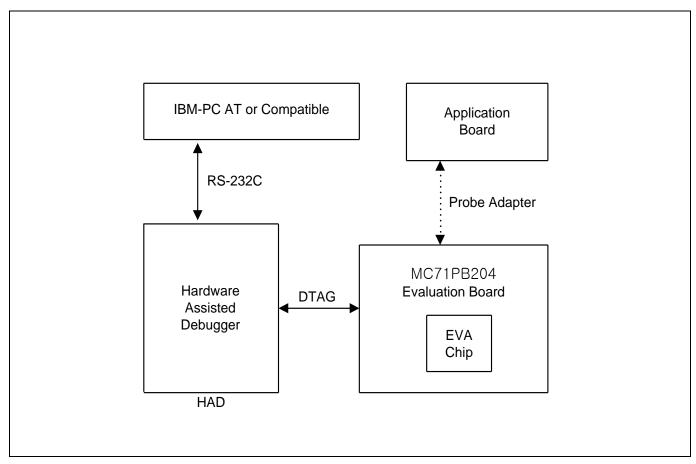

| 15. DEVELOPMENT TOOLS                  | 132 |

## 1. PRODUCT OVERVIEW

## 1.1 KEY FEATURES

| • CPU                         | <br>GMC14 core (8-bit RISC CPU)                                                                                        |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Main Clock                    | <br>Crystal/Ceramic: 0.4MHz – 12MHz<br>Internal RC: 1MHz, 2MHz, 4MHz, 8MHz<br>External RC: 1MHz – 8MHz                 |

| ROM Capacity                  | <br>4,096 x 14-bits (7,168-Byte)                                                                                       |

| RAM Capacity                  | <br>208 x 8-bits                                                                                                       |

| Instruction Set               | <br>35 single word instructions<br>14-bit wide instruction word                                                        |

| • Instruction Execution Times | <br>167nS at 12MHz fx (main)                                                                                           |

| • I/O Port                    | <br>I/O: 17 bits (20-pin package) I/O: 13 bits (16-pin package)                                                        |

| Programmable Timer            | <br>One 16-bit timer/counter (shared with two 8-bit timer/counters)                                                    |

| Watchdog Timer Function       |                                                                                                                        |

| PWM mode                      | <br>6/8-bit selection                                                                                                  |

| A/D Converter                 | <br>12-bit x 11-channel analog input                                                                                   |

| ROM Option                    | <br>LVR (2.6V, 3.0V, 4.0V)<br>Oscillator selectable (Internal or External)                                             |

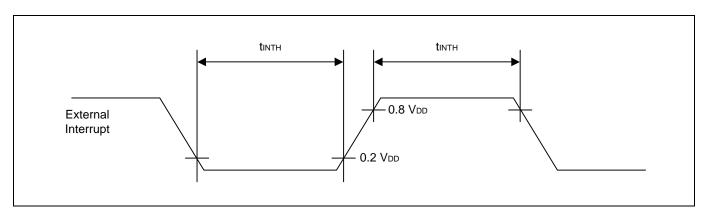

| • Interrupt                   | <br>External : external interrupt x 4 Internal : WDT interrupt, Timer 0/A interrupt, Timer B interrupt, PWM interrupt. |

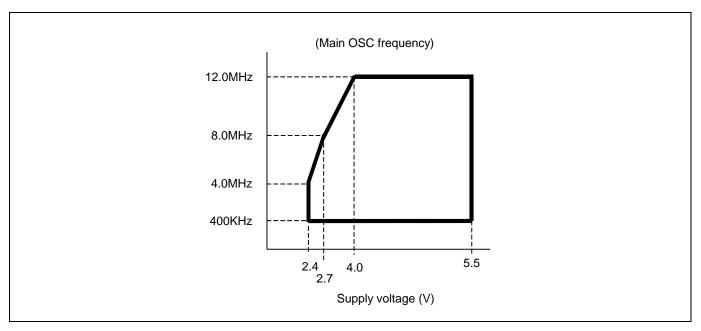

| Power Supply Voltage          | <br>2.4V to 5.5V at 4MHz<br>2.7V to 5.5V at 8MHz<br>4.0V to 5.5V at 12MHz                                              |

| Operating Temperature         | <br>− 20 °C to + 85 °C                                                                                                 |

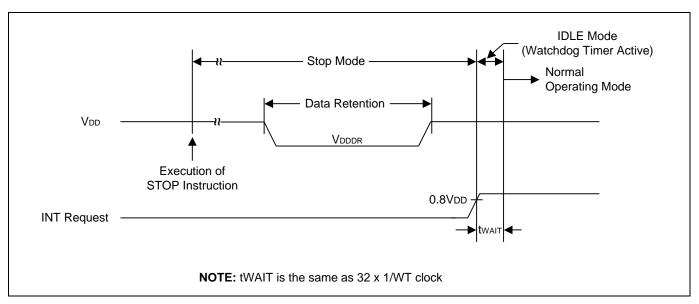

| Power-Saving                  | <br>Idle : only CPU clock stop<br>Stop: System clock and CPU clock stop                                                |

| Package                       | <br>20-pin DIP, 20-pin SOP<br>16-pin DIP, 16-pin SOP                                                                   |

|                               |                                                                                                                        |

## 1.2 Ordering Information

| Device     | ROM Size     | RAM size  | Package |

|------------|--------------|-----------|---------|

| MC71PB204D | 4K words OTP | 208 bytes | 20 SOP  |

| MC71PB204B | 4K words OTP | 208 bytes | 20 DIP  |

| MC71PB204M | 4K words OTP | 208 bytes | 16 SOP  |

| MC71PB204V | 4K words OTP | 208 bytes | 16 DIP  |

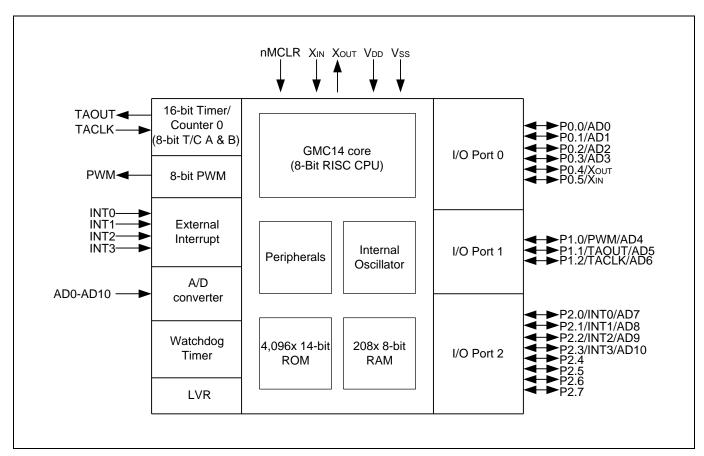

## 1.3 BLOCK DIAGRAM

Figure 1-1. Block Diagram

## 1.4 PIN ASSIGNMENTS

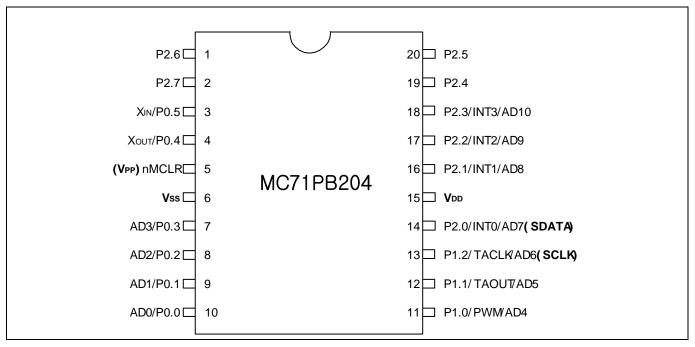

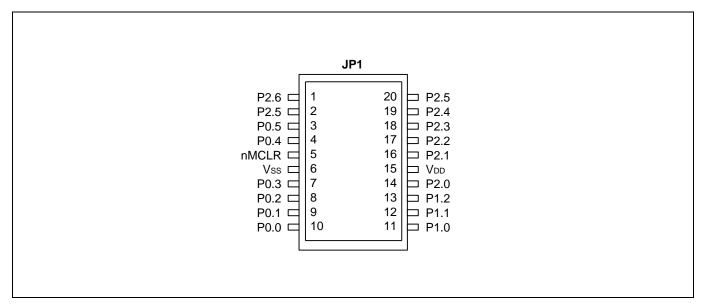

#### **1.4.1 20-PIN PACKAGE**

Figure 1-2. MC71PB204 Pin Assignments (20-Pin)

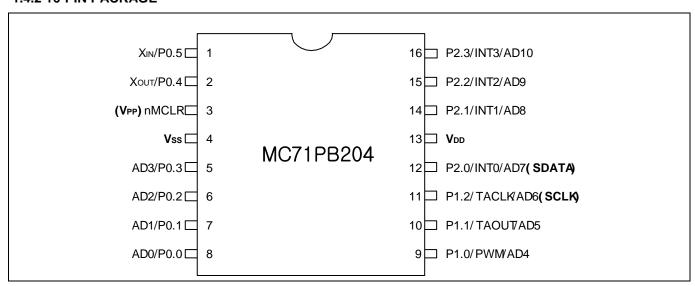

#### **1.4.2 16-PIN PACKAGE**

Figure 1-3. MC71PB204 Pin Assignments (16-Pin)

## 1.5 PIN DESCRIPTIONS

## 1.5.1 20-DIP(SOP) PACKAGE TYPE

| Pin Names   | I/O | Pin Description                                                                                                                                                       | After<br>RESET | Alternative<br>Functions |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|

| P0.0        | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                                                          | Input          | AD0                      |

| P0.1        |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                                                              |                | AD1                      |

| P0.2        |     | ruii-up resistor can be programmed as 1-bit.                                                                                                                          |                | AD2                      |

| P0.3        |     |                                                                                                                                                                       |                | AD3                      |

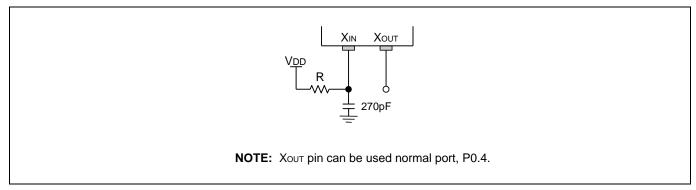

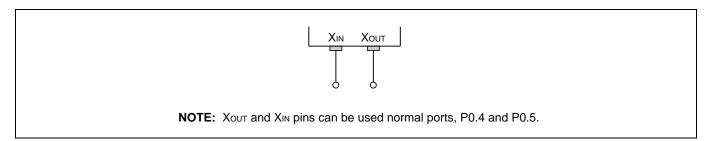

| P0.4        | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                                                          | Input          | X <sub>OUT</sub>         |

| P0.5        |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor or Pull-down resistor can be programmed as 1-bit.                                        |                | X <sub>IN</sub>          |

| P1.0        | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                                                          | Input          | PWM/AD4                  |

| P1.1        |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                                                              |                | TAOUT/AD5                |

| P1.2        |     | Pull-up resistor can be programmed as 1-bit.                                                                                                                          |                | TACLK/AD6                |

| P2.0        | I/O | 1-bit programmable I/O pin. Schmitt trigger Input, Push-pull                                                                                                          | Input          | INT0/AD7                 |

| P2.1        |     | output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                                                                                    |                | INT1/AD8                 |

| P2.2        |     | programmed as 1-bit.                                                                                                                                                  |                | INT2/AD9                 |

| P2.3        |     |                                                                                                                                                                       |                | INT3/AD10                |

| P2.4 - P2.7 | I/O | 1-bit programmable I/O pin. Schmitt trigger Input, Push-pull output, or Open-drain output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit. | Input          | -                        |

| PWM         | I/O | 6/8 bit high speed PWM output                                                                                                                                         | Input          | P1.0                     |

| TACLK       | I/O | Timer 0/A external clock input                                                                                                                                        | Input          | P1.2                     |

| TAOUT       | I/O | Timer 0/A data output                                                                                                                                                 | Input          | P1.1                     |

| INT0        | I/O | External interrupt input pins                                                                                                                                         | Input          | P2.0                     |

| INT1        |     |                                                                                                                                                                       |                | P2.1                     |

| INT2        |     |                                                                                                                                                                       |                | P2.2                     |

| INT3        |     |                                                                                                                                                                       |                | P2.3                     |

| AD0         | I/O | A/D Converter input                                                                                                                                                   | Input          | P0.0                     |

| AD1         |     |                                                                                                                                                                       |                | P0.1                     |

| AD2         |     |                                                                                                                                                                       |                | P0.2                     |

| AD3         |     |                                                                                                                                                                       |                | P0.3                     |

| AD4         |     |                                                                                                                                                                       |                | P1.0                     |

| AD5         |     |                                                                                                                                                                       |                | P1.1                     |

| AD6         |     |                                                                                                                                                                       |                | P1.2                     |

| AD7         |     |                                                                                                                                                                       |                | P2.0                     |

| AD8         |     |                                                                                                                                                                       |                | P2.1                     |

## 1.5.1 20-DIP(SOP) PACKAGE TYPE (CONTINUED)

| Pin Names                          | I/O | Pin Description      | After<br>RESET | Alternative<br>Functions |

|------------------------------------|-----|----------------------|----------------|--------------------------|

| AD9                                | I/O | A/D Converter input  | Input          | P2.2                     |

| AD10                               |     |                      |                | P2.3                     |

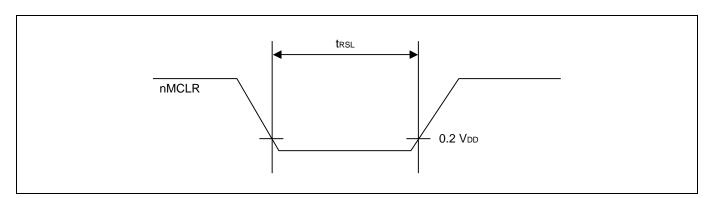

| nMCLR                              | I   | System reset pin     | Input          | -                        |

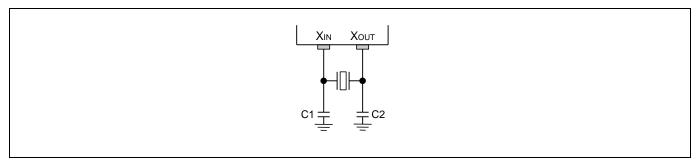

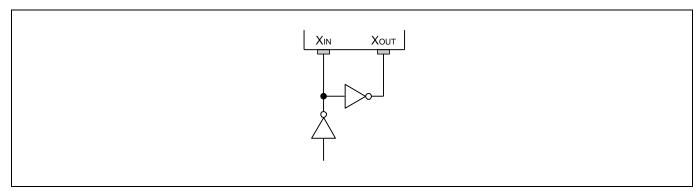

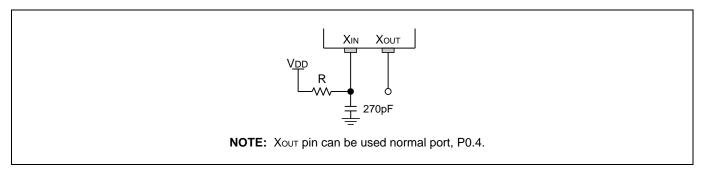

| X <sub>IN</sub> , X <sub>OUT</sub> | -   | Main oscillator pins | Output         | P0.4, P0.5               |

| V <sub>DD</sub> , V <sub>SS</sub>  | -   | Power input pins     | -              | -                        |

## 1.5.2 16-DIP(SOP) PACKAGE TYPE

| Pin Names                          | I/O | Pin Description                                                                                                                | After<br>RESET | Alternative<br>Functions |

|------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|

| P0.0                               | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                   | Input          | AD0                      |

| P0.1                               |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                       |                | AD1                      |

| P0.2                               |     | ruil-up resistor can be programmed as 1-bit.                                                                                   |                | AD2                      |

| P0.3                               |     |                                                                                                                                |                | AD3                      |

| P0.4                               | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                   | Input          | X <sub>OUT</sub>         |

| P0.5                               |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor or Pull-down resistor can be programmed as 1-bit. |                | X <sub>IN</sub>          |

| P1.0                               | I/O | 1-bit programmable I/O pin. Schmitt trigger input, Push-pull                                                                   | Input          | PWM/AD4                  |

| P1.1                               |     | output, or Open-drain output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                       |                | TAOUT/AD5                |

| P1.2                               |     | Pull-up resistor can be programmed as 1-bit.                                                                                   |                | TACLK/AD6                |

| P2.0                               | I/O | 1-bit programmable I/O pin. Schmitt trigger Input, Push-pull                                                                   | Input          | INT0/AD7                 |

| P2.1                               |     | output port. Used as an input port, a Pull-up resistor can be programmed as 1-bit.                                             |                | INT1/AD8                 |

| P2.2                               |     | programmed as 1-bit.                                                                                                           |                | INT2/AD9                 |

| P2.3                               |     |                                                                                                                                |                | INT3/AD10                |

| PWM                                | I/O | 6/8 bit high speed PWM output                                                                                                  | Input          | P1.0                     |

| TACLK                              | I/O | Timer 0/A external clock input                                                                                                 | Input          | P1.2                     |

| TAOUT                              | I/O | Timer 0/A data output                                                                                                          | Input          | P1.1                     |

| INT0                               | I/O | External interrupt input pins                                                                                                  | Input          | P2.0                     |

| INT1                               |     |                                                                                                                                |                | P2.1                     |

| INT2                               |     |                                                                                                                                |                | P2.2                     |

| INT3                               |     |                                                                                                                                |                | P2.3                     |

| AD0                                | I/O | A/D Converter input                                                                                                            | Input          | P0.0                     |

| AD1                                |     |                                                                                                                                |                | P0.1                     |

| AD2                                |     |                                                                                                                                |                | P0.2                     |

| AD3                                |     |                                                                                                                                |                | P0.3                     |

| AD4                                |     |                                                                                                                                |                | P1.0                     |

| AD5                                |     |                                                                                                                                |                | P1.1                     |

| AD6                                |     |                                                                                                                                |                | P1.2                     |

| AD7                                |     |                                                                                                                                |                | P2.0                     |

| AD8                                |     |                                                                                                                                |                | P2.1                     |

| AD9                                |     |                                                                                                                                |                | P2.2                     |

| AD10                               |     |                                                                                                                                |                | P2.3                     |

| nMCLR                              | I   | System reset pin                                                                                                               | Input          | -                        |

| X <sub>IN</sub> , X <sub>OUT</sub> | -   | Main oscillator pins                                                                                                           | Output         | P0.4, P0.5               |

| $V_{DD}, V_{SS}$                   | -   | Power input pins                                                                                                               |                | -                        |

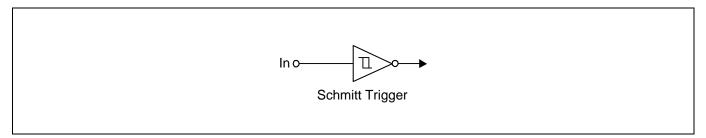

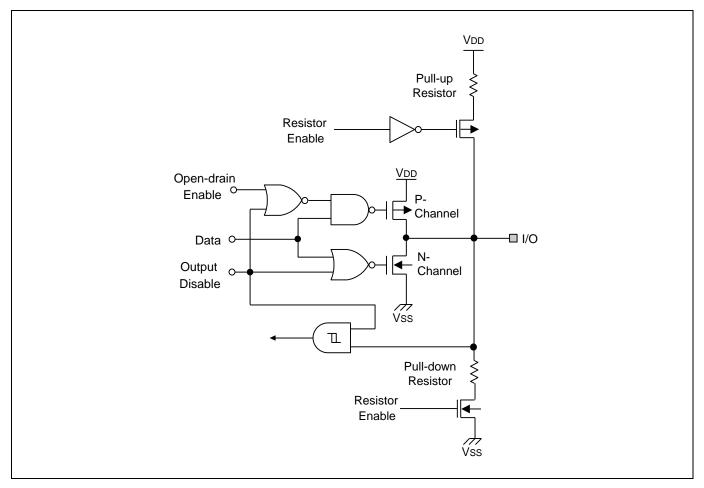

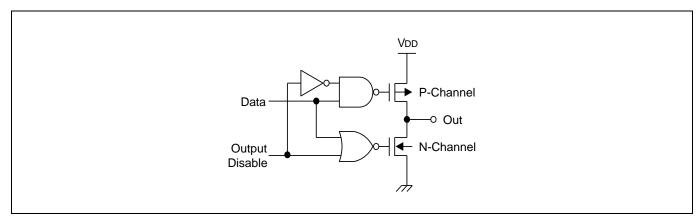

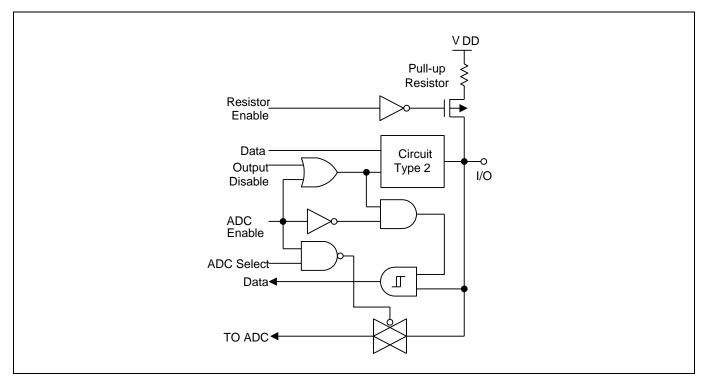

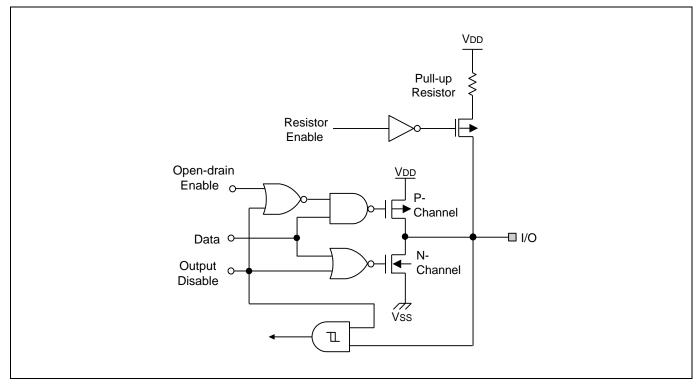

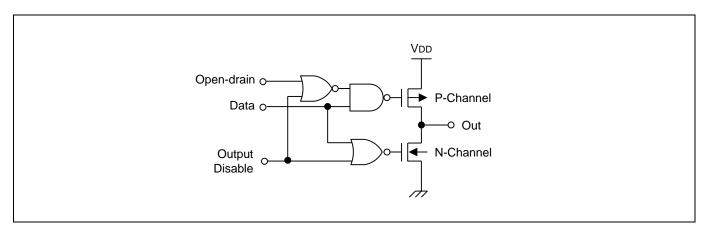

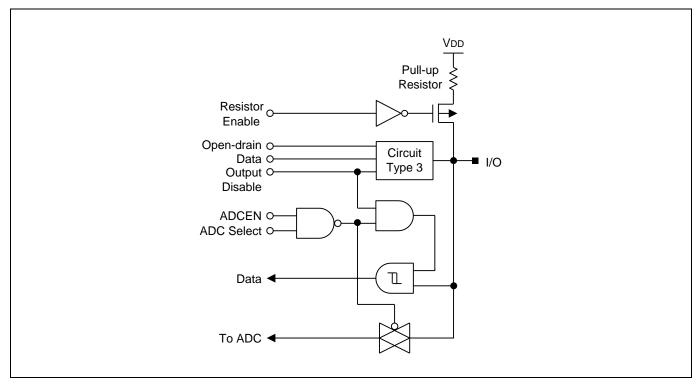

## **1.6 PIN CIRCUITS**

Figure 1-4. Pin Circuit Type 1 (nMCLR)

Figure 1-5. Pin Circuit Type 4-2 (P0.4/X<sub>OUT</sub>, P0.5/X<sub>IN</sub>)

Figure 1-6. Pin Circuit Type 2

Figure 1-7. Pin Circuit Type 6-1 (P2.0-P2.3)

Figure 1-8. Pin Circuit Type 4-1 (P2.4-P2.7)

Figure 1-9. Pin Circuit Type 3

Figure 1-10. Pin Circuit Type 6-3 (P0.0-P0.3, P1.0-P1.2)

## 2. MEMORY ORGANIZATION

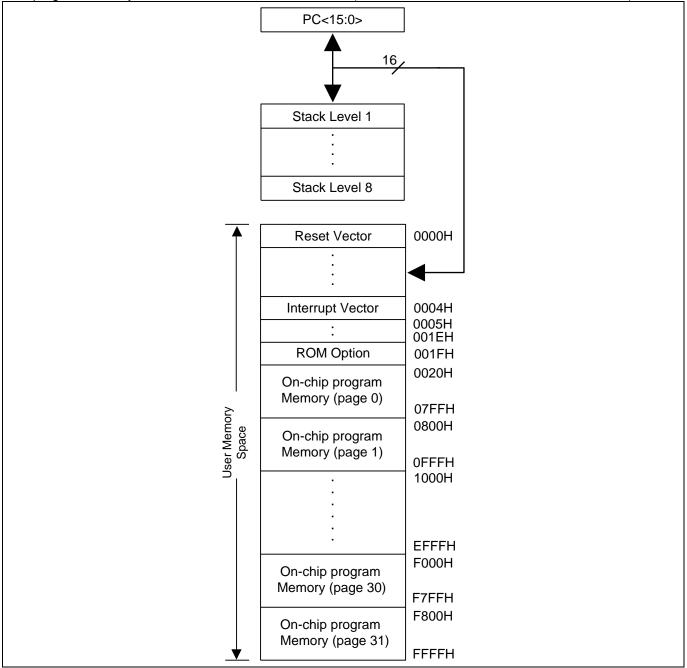

## 2.1 PROGRAM MEMORY ORGANIZATION

The GMC14 series have a 16-bit program counter capable of addressing a 64k x 14-bit program memory space. The reset vector is at 0000H, the interrupt vector at 0004H and the ROM Option at 001FH.

The program memory size of the MC71PB204 is 4k words (4k x 14-bit, from the address 0000H to 0FFFH).

Figure 2-1. Program Memory Map and Stack

#### **2.1.1. ROM OPTION**

The ROM Option is start-condition of the chip. The ROM Option address is 001FH. The default value of the ROM Option is 3FFFH (LVR disable, selected crystal/ceramic oscillator).

For example, if you program as below:

CODE 0x1F ;ROM option area

DW 0x3FBE ;Disable LVR, Select Crystal/Ceramic OSC

ROM OPTION ROM Address: 001FH

|     | .13 | .12 | .11 | .10 | .9 | .8        | .7 | .6 | .5 | .4 | .3 | .2   | .1 | .0 |     |

|-----|-----|-----|-----|-----|----|-----------|----|----|----|----|----|------|----|----|-----|

| MSB | 1   | 1   | 1   | 1   | 1  | LVR<br>EN |    | LV | RS |    |    | oscs |    | 1  | LSB |

## ! To avoid malfunction, You must set undefined bits.

| Bit13-9 | Not available for the MC71PB204   |                                 |  |  |  |  |

|---------|-----------------------------------|---------------------------------|--|--|--|--|

| LVREN   | LVR Enable/Disable Selection Bit  | 0: Enable                       |  |  |  |  |

| LVKEN   | LVK Eliable/Disable Selection bit | 1: Disable                      |  |  |  |  |

|         |                                   | 1100: 2.6 V                     |  |  |  |  |

| LVRS    | LVR Level Selection Bits          | 0111: 3.0 V                     |  |  |  |  |

|         |                                   | 0100: 4.0 V                     |  |  |  |  |

|         |                                   | 000: External RC                |  |  |  |  |

|         |                                   | 001: Internal RC; 4MHz          |  |  |  |  |

| oscs    | Oscillator Selection Bits         | 010: Internal RC; 2MHz          |  |  |  |  |

| 0303    | Oscillator Selection Bits         | 011: Internal RC; 1MHz          |  |  |  |  |

|         |                                   | 100: Internal RC; 8MHz          |  |  |  |  |

|         |                                   | 111: Crystal/Ceramic oscillator |  |  |  |  |

| Bit0    | Not available for the MC71PB204   |                                 |  |  |  |  |

#### NOTES:

- 1. The value of unused bits <0> and <9:13> is don't care.

- 2. When LVR is enabled, LVR level must be set to appropriate value, not default value.

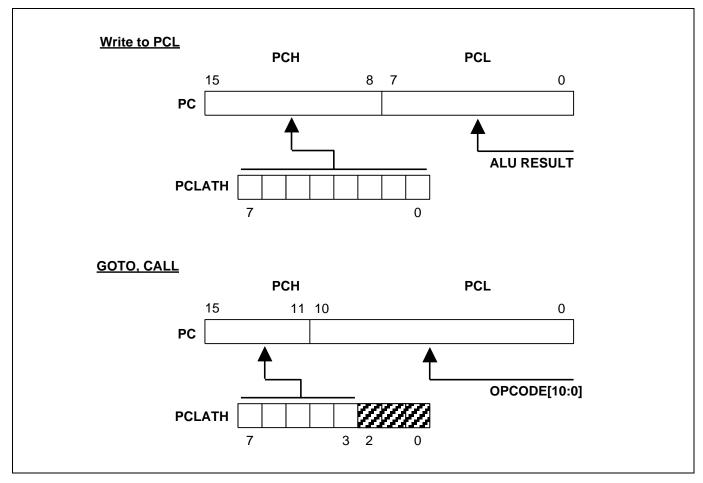

#### 2.1.2 PC AND PCLATH REGISTERS

The Program Counter (PC) is 16-bit wide. The lower bits (PC<7:0>) come from PCL register, which is a readable and writable register. The upper bits (PC<15:8>) are not directly readable (or writable), but are indirectly writable through the PCLATH register. On any reset, (the upper bits of) the PC is (will be) cleared.

Figure 2-2 shows the two situations for PC loading. The upper example in the figure 2-2 shows how the PC is loaded by writing to PCL (PCLATH<7:0>  $\rightarrow$  PCH). The lower example in the figure 2-2 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<7:3>  $\rightarrow$  PCH).

Figure 2-2. Loading of PC in different situations

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When reading a table using a computed GOTO method, pay attention if the table location crosses a PCL memory boundary (each 256 byte block).

#### 2.1.3 PROGRAM MEMORY PAGING

The GMC14 series devices are capable of addressing a continuous 64k words block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2k words program memory page. When doing a CALL or GOTO instruction the upper 5 bits of the address are provided by PCLATH<7:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If RETURN, RETLW, or RETFIE instructions are executed, the entire 16-bit PC is popped from the stack. Therefore, manipulation of the PCLATH<7:3> bits is not required for the return instructions (which pops the address from the stack).

NOTE: Because the MC71PB204 use only PCLATH<3:0> bit, the PCLATH<7:4> bits should be always logic '0000b'.

## 2.2 STACK

The GMC14 series has an 8 level depth x 16-bit width hardware stack. The stack space is neither part of program nor data space and the stack pointer is not readable or writable. The PC is pushed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is popped in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a push or pop operation. The stack operates as a circular buffer. This means that after the stack has been pushed eight times, the ninth push overwrites the value that stored from the first push. The tenth push overwrites the second push (and so on).

#### NOTES:

- 1. There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- 2. There are no instructions/mnemonics called push or pop. These are actions that occur from the execution of the CALL, RETURN, RETLW, and RETFIE instructions, or the vectoring to an interrupt address.

## 2.3 DATA MEMORY

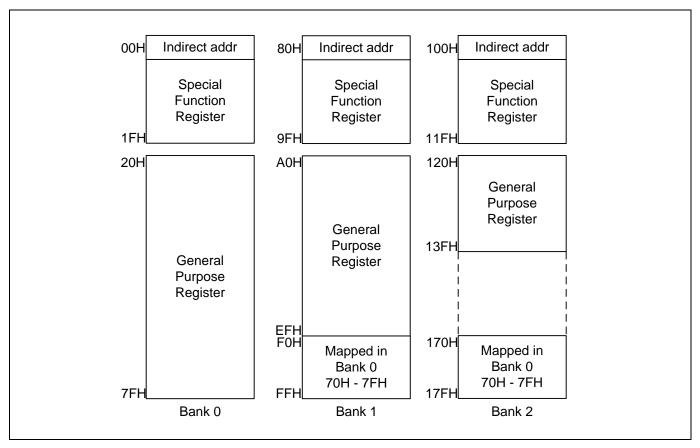

The data memory for the MC71PB204 is partitioned onto three banks which contain the general purpose registers and the special function registers. Bank 0 is selected when the RP1:RP0 bits in status register are 00b, bank 1 when RP1:RP0 are 01b, bank2 when RP1:RP0 are 10b.

Figure 2-3. Register File Organization (MC71PB204)

The lower locations of each bank are reserved for the special function registers. The upper locations of each bank are general purpose registers implemented as static RAM. All three banks contain special function registers. Some of the special function registers are mirrored in other banks for code reduction and quicker access.

The register file can be accessed either directly, or indirectly through the File Select Register (FSR). Refer to 2.3.3 addressing mode.

#### 2.3.1 GENERAL PURPOSE REGISTER

The size of the MC71PB204's general purpose register is 208 bytes (20H~7FH, A0H~EFH and 120H~13FH). The following general purpose registers are not physically implemented:

- 0F0H-0FFH of Bank 1

- 170H-17FH of Bank 2

These locations are used for common access across banks.

#### 2.3.2 SPECIAL FUNCTION REGISTER

There are 33 bytes of special function register. Some of the special function registers are visible on any of three memory banks. As is shown in figure below;

| 00H CONFIC  | CONFIG         | CONFIG     |  |

|-------------|----------------|------------|--|

| 01H CPUCL   |                | -          |  |

| 02H PCL     | PCL            | PCL        |  |

| 03H STATUS  |                | STATUS     |  |

| 04H FSR     | FSR            | FSR        |  |

| 05H ADMR    |                | -          |  |

| 06H ADRRH   |                | _          |  |

| 07H ADRRL   |                | _          |  |

| 08H WTSCF   |                | -          |  |

| 09H WTCR    |                | -          |  |

| 0AH PCLATI  |                | PCLATH     |  |

| 0BH INTCOM  |                | -          |  |

| 0CH IPND    | -              | -          |  |

| 0DH TSCRA   | -              | -          |  |

| 0EH TCRA    | -              | -          |  |

| 0FH TDRA    | -              | -          |  |

| 10H TSCRE   | -              | -          |  |

| 11H TCRB    | -              | -          |  |

| 12H TDRB    | -              | -          |  |

| 13H -       | -              | -          |  |

| 14H         | -              | -          |  |

| 15H DDR0H   |                | -          |  |

| 16H DDR0L   | -              | -          |  |

| 17H PUR0    | -              | -          |  |

| 18H DDR1    | -              | -          |  |

| 19H DDR2F   |                | -          |  |

| 1AH DDR2L   |                | -          |  |

| 1BH EINT2   |                | -          |  |

| 1CH EPND1   |                | -          |  |

| 1DH P0      |                | -          |  |

| 1EH P1      |                | -          |  |

| 1FH P2      |                | -          |  |

| 20H RAM Mem | ory RAM Memory | RAM Memory |  |

| 7FH Space   | Space          | Space      |  |

| Bank 0      | Bank 1         | Bank 2     |  |

Figure 2-4. Data memory map

The special function registers are the registers used by the cpu and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. The special function registers can be classified into two sets (core and peripheral). The special function registers associated with the "core" functions are described below. The rest of special function registers are described in the corresponding peripheral section.

### 2.3.2.1 CONFIG Register

The CONFIG register contains configuration bits, which defines additional the MC71PB204 core features. To change it's contents, the FSR register should be cleared first, and then a particular instruction using indirect addressing mode should be executed.

## **CONFIG REGISTER (CONFIG)**

00H, 80H, 100H

|            | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |                     |

|------------|---|---|---|---|---|---|-----|-----|---------------------|

| CONFIG     | • | - | - | - | - | - | DEC | INC | (Initial value :00) |

| Read/Write | - | - | - | - | - | - | R/W | R/W | <del>-</del>        |

| Bit7-2 | Not available for the MC71PB204    |                                |  |  |  |  |  |  |

|--------|------------------------------------|--------------------------------|--|--|--|--|--|--|

| DEC    | Indirect addressing mode with post | 0: Post FSR decrement disabled |  |  |  |  |  |  |

| DEC    | decrement FSR contents             | 1: Post FSR decrement enabled  |  |  |  |  |  |  |

| INC    | Indirect addressing mode with post | 0: Post FSR increment disabled |  |  |  |  |  |  |

| INC    | increment FSR contents             | 1: Post FSR increment enabled  |  |  |  |  |  |  |

NOTE: Both DEC and INC bits set disable auto increment/decrement function.

### 2.3.2.2 STATUS Register

The STATUS register contains the arithmetic status of the ALU and the bank selection bits for data memory. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then writing to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the nTO and nPD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different from intended.

## **STATUS REGISTER (STATUS)**

03H, 83H, 103H

|            | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | _                |      |   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|------------------|------|---|

| STATUS     | IRP | RP1 | RP0 | nTO | nPD | Z   | DC  | С   | (Initial value : | NOTE | ) |

| Read/Write | R/W | R/W | R/W | R   | R   | R/W | R/W | R/W | _                |      |   |

| IRP        | Register Bank Selection Bit    | 0: Bank 0, 1 (00H – 0FFH)                                                     |  |  |  |  |

|------------|--------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| IKF        | (used for indirect addressing) | 1: Bank 2, 3 (100H – 1FFH)                                                    |  |  |  |  |

|            |                                | 00: Bank 0                                                                    |  |  |  |  |

| RP1        | Register Bank Selection Bits   | 01: Bank 1                                                                    |  |  |  |  |

| RP0        | (used for direct addressing)   | 10: Bank 2                                                                    |  |  |  |  |

|            |                                | 01: Bank 3; (Not used for the MC71PB204)                                      |  |  |  |  |

|            |                                | 0: A WDT time-out occurred                                                    |  |  |  |  |

| nTO        | Time-out Bit                   | After power-up, CLRWDT instruction, or SLEEP instruction.                     |  |  |  |  |

| nPD        | Power-down Bit                 | 0: By execution of the SLEEP instruction                                      |  |  |  |  |

| וורט       | Power-down bit                 | 1: After power-up or by the CLRWDT instruction                                |  |  |  |  |

| 7          | Zero Bit                       | 0: The result of an arithmetic or logic operation is not zero                 |  |  |  |  |

| Z          |                                | 1: The result of an arithmetic or logic operation in zero                     |  |  |  |  |

| <b>D</b> C | Divit Commute Domeste Dit      | 0: No carry-out from the 4 <sup>th</sup> low order bit of the result occurred |  |  |  |  |

| DC         | Digit Carry/nBorrow Bit        | 1: A carry-out from the 4 <sup>th</sup> low order bit of the result occurred  |  |  |  |  |

| С          | Courselo Bourous Bit           | No carry-out from the most significant bit of the result occurred             |  |  |  |  |

| C          | Carry/nBorrow Bit              | 1: A carry-out from the most significant bit of the result occurred           |  |  |  |  |

NOTE: Refer to the Table 6-4 in the Chapter 6. RESET AND POWER DOWN for the initial value of STATUS register.

## 2.3.2.3 Internal Interrupt Control Register (INTCON)

The INTCON register is able to select enable or disable global interrupt, watchdog timer interrupt, PWM interrupt, timer A interrupt, and timer B interrupt.

## INTERNAL INTERRUPT CONTROL REGISTER (INTCON)

0BH

|            | 7   | 6    | 5     | 4    | 3    | 2 | 1 | 0 |                          |

|------------|-----|------|-------|------|------|---|---|---|--------------------------|

| INTCON     | GIE | WTIE | PWMIE | TAIE | TBIE | - | - | - | (Initial value : 0000 0) |

| Read/Write | R/W | R/W  | R/W   | R/W  | R/W  | - | - | - | _                        |

| GIE      | Global Interrupt Enable Bit          | 0: Disable all interrupt           |

|----------|--------------------------------------|------------------------------------|

| GIE      | Global interrupt Enable Bit          | 1: Enable all un-masked interrupts |

| WTIE     | Watchdog Timer Interrupt Enable Bit  | 0: Disable interrupt               |

| VVIIE    | Waterlady Timer Interrupt Enable Bit | 1: Enable interrupt                |

| PWMIE    | PWM Interrupt Enable Bit             | 0: Disable interrupt               |

| PAAIAIIE |                                      | 1: Enable interrupt                |

| TAIE     | Timer 0/A Interrupt Enable Bit       | 0: Disable interrupt               |

| IAIL     |                                      | 1: Enable interrupt                |

| TBIE     | Timor B Interrupt Enable Bit         | 0: Disable interrupt               |

| IDIE     | Timer B Interrupt Enable Bit         | 1: Enable interrupt                |

| Bit2-0   | Not available for the MC71PB204      |                                    |

## 2.3.2.4 Internal Interrupt Pending Register (IPND)

The IPND register is a readable and writable register, which contains various pending bits for internal interrupt.

## **INTERNAL INTERRUPT PENDING REGISTER (IPND)**

0CH

|            | 7 | 6         | 5          | 4         | 3         | 2 | 1 | 0 |                           |

|------------|---|-----------|------------|-----------|-----------|---|---|---|---------------------------|

| IPND       | - | WT<br>PND | PWM<br>PND | TA<br>PND | TB<br>PND |   | - | ı | (Initial value : - 000 0) |

| Read/Write | - | R/W       | R/W        | R/W       | R/W       | - | - | - |                           |

| Bit7          | Not available for the MC71PB204      |                                                                                                                              |  |  |  |  |  |

|---------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|               |                                      | 0: interrupt request is not pending (when read);                                                                             |  |  |  |  |  |

| WTPND         | Watchdog Timer Interrupt Pending Bit | pending bit clear when write 0                                                                                               |  |  |  |  |  |

|               |                                      | 1: interrupt request is pending (when read)  0: interrupt request is not pending (when read); pending bit clear when write 0 |  |  |  |  |  |

|               |                                      | 0: interrupt request is not pending (when read);                                                                             |  |  |  |  |  |

| <b>PWMPND</b> | PWM Interrupt Pending Bit            | pending bit clear when write 0                                                                                               |  |  |  |  |  |

|               |                                      | 1: interrupt request is pending (when read)                                                                                  |  |  |  |  |  |

|               |                                      | 0: interrupt request is not pending (when read);                                                                             |  |  |  |  |  |

| TAPND         | Timer 0/A Interrupt Pending Bit      | pending bit clear when write 0                                                                                               |  |  |  |  |  |

|               |                                      | 1: interrupt request is pending (when read)                                                                                  |  |  |  |  |  |

|               |                                      | 0: interrupt request is not pending (when read);                                                                             |  |  |  |  |  |

| TBPND         | Timer B Interrupt Pending Bit        | pending bit clear when write 0                                                                                               |  |  |  |  |  |

|               |                                      | 1: interrupt request is pending (when read)                                                                                  |  |  |  |  |  |

| Bit2-0        | Not available for the MC71PB204      |                                                                                                                              |  |  |  |  |  |

## 2.3.2.5 Special Function Register's Map

Table 2-1. BANK0 Register's Map

|             | 1       | 1        | 1         | ı           | _          | 1           | 1           | Г          |       |

|-------------|---------|----------|-----------|-------------|------------|-------------|-------------|------------|-------|

| Register    | Address | Bit 7    | Bit 6     | Bit 5       | Bit 4      | Bit 3       | Bit 2       | Bit 1      | Bit 0 |

| Name        | Hex     | <b>2</b> | 2.00      | 2.00        |            | 2           |             |            |       |

| CONFIG      | 00H     | _        | _         | _           | -          | _           | -           | DEC        | INC   |

| CPUCLK      | 01H     | ID       | LE        | _           | -          | _           | -           | CC         | CLK   |

| PCL         | 02H     |          | Р         | rogram co   | unter (PC) | Least Sig   | nificant By | te         |       |

| STATUS      | 03H     | IRP      | RP1       | RP0         | nTO        | nPD         | Z           | DC         | С     |

| FSR         | 04H     |          |           | Indirect of | data mem   | ory addres  | s pointer   |            |       |

| ADMR        | 05H     | SSBIT    | EOC       | ADO         | CLK        |             | AD          | СН         |       |

| ADDRH       | 06H     |          |           | A/D Conv    | erter Data | Register,   | High Byte   |            |       |

| ADDRL       | 07H     |          |           | A/D Conv    | erter Data | Register,   | Low Byte    |            |       |

| WTSCR       | 08H     |          | WT        | FUN         |            | WT3C        | WT          | CS         | WTCC  |

| WTCR        | 09H     |          |           | 8-Bit Wat   | chdog Tim  | er Counte   | r Register  |            |       |

| PCLATH      | 0AH     | _        | _         | _           |            | Write buffe | er upper 5  | bits of PC |       |

| INTCON      | 0BH     | GIE      | WTIE      | PWMIE       | TAIE       | TBIE        | _           | _          | _     |

| IPND        | 0CH     | _        | WT<br>PND | PWM<br>PND  | TA<br>PND  | TB<br>PND   | _           | _          | _     |

| TSCRA       | 0DH     | -        | -         | TARL        | TACE       |             | TACS TOMO   |            |       |

| TCRA        | 0EH     |          | •         | Tim         | er 0/A Co  | unter Regi  | ster        |            |       |

| TDRA        | 0FH     |          |           | Ti          | mer 0/A D  | ata Regist  | er          |            |       |

| TSCRB       | 10H     | -        | _         | TBRL        | TBCE       |             | TBCS        |            | _     |

| TCRB        | 11H     |          |           | Tir         | ner B Cou  | nter Regis  | ter         |            |       |

| TDRB        | 12H     |          |           | Т           | imer B Da  | ata Registe | er          |            |       |

|             |         |          | 13H -     | I4H are no  | t mapped   |             |             |            |       |

| DDR0H       | 15H     | P        | 05        | P05PD       | -          | P           | 04          | P04PD      | _     |

| DDR0L       | 16H     | P        | 03        | P           | )2         | P           | 01          | P          | 00    |

| PUR0        | 17H     | -        | PUR06     | PUR05       | PUR04      | PUR03       | PUR02       | PUR01      | PUR00 |

| DDR1        | 18H     | P        | 12        |             | P11        |             |             | P10        |       |

| DDR2H       | 19H     | P:       | 27        | P2          | 26         | P2          | 25          | P:         | 24    |

| DDR2L       | 1AH     | P:       | 23        | P2          | 22         | P2          | 21          | P:         | 20    |

| EINT2       | 1BH     | IN       | T3        | IN          | T2         | IN          | T1          | IN         | T0    |

| EPND2       | 1CH     | _        | _         | _           | _          | PND3        | PND2        | PND1       | PND0  |

| P0          | 1DH     |          | •         | •           | Port 0 Dat | a Register  |             |            |       |

| P1          | 1EH     |          |           |             | Port 1 Dat | a Register  |             |            |       |

| P2          | 1FH     |          |           |             | Port 2 Dat | a Register  |             |            |       |

| A I I (( 1) |         |          |           |             |            |             |             |            |       |

NOTE: A dash ('-') means that the bit is neither used nor mapped.

Table 2-2. BANK1 Register's Map

| Register | Address | Bit 7 | Bit 6                          | Bit 5      | Bit 4      | Bit 3       | Bit 2       | Bit 1 | Bit 0 |

|----------|---------|-------|--------------------------------|------------|------------|-------------|-------------|-------|-------|

| Name     | Hex     | DIL 1 | DIL 0                          | DIL 3      | DIL 4      | DIL 3       | DIL Z       | DIL I | DIL U |

| CONFIG   | 80H     | _     | _                              | _          | _          | _           | -           | DEC   | INC   |

|          |         |       | 81                             | H is not m | apped      |             |             |       |       |

| PCL      | 82H     |       | Р                              | rogram co  | unter (PC) | Least Sig   | nificant By | te    |       |

| STATUS   | 83H     | IRP   | RP1                            | RP0        | nTO        | nPD         | Z           | DC    | С     |

| FSR      | 84H     |       |                                | Indirect   | data memo  | ory addres  | s pointer   |       |       |

| PWMSCR   | 85H     | PWN   | /IICS                          | -          | -          | PWMD        | PWMC        | PWME  | _     |

| PWMCR    | 86H     |       |                                | Р          | WM Coun    | ter Registe | er          |       |       |

| PWMDR    | 87H     |       |                                |            | PWM Dat    | a Register  |             |       |       |

|          |         |       | 88H - 8                        | 39H are no | ot mapped  |             |             |       |       |

| PCLATH   | 8AH     | _     | With buffer upper 5 bits of PC |            |            |             |             |       |       |

|          |         |       | 8BH –                          | 9FH are n  | ot mapped  |             |             |       |       |

**NOTE:** A dash ('-') means that the bit is neither used nor mapped.

Table 2-3. BANK2 Register's Map

| Register | Address | Bit 7 | Bit 6    | Bit 5      | Bit 4      | Bit 3      | Bit 2       | Bit 1      | Bit 0 |

|----------|---------|-------|----------|------------|------------|------------|-------------|------------|-------|

| Name     | Hex     | DIL 1 | DIL 0    | DIL 3      | DIL 4      | DIL 3      | DIL Z       | DIL I      | DIL U |

| CONFIG   | 100H    | _     | _        | _          | _          | _          | _           | DEC        | INC   |

|          |         |       | 101      | H is not m | napped     |            |             |            |       |

| PCL      | 102H    |       | Р        | rogram co  | unter (PC) | Least Sig  | nificant By | te         |       |

| STATUS   | 103H    | IRP   | RP1      | RP0        | nTO        | nPD        | Z           | DC         | С     |

| FSR      | 104H    |       |          | Indirect   | data memo  | ory addres | s pointer   |            |       |

|          |         |       | 105H - 1 | 109H are r | not mappe  | d          |             |            |       |

| PCLATH   | 10AH    |       | _        | _          |            | With buffe | er upper 5  | bits of PC |       |

|          |         |       | 10BH –   | 11FH are   | not mappe  | ed         | •           |            |       |

NOTE: A dash ('-') means that the bit is neither used nor mapped.

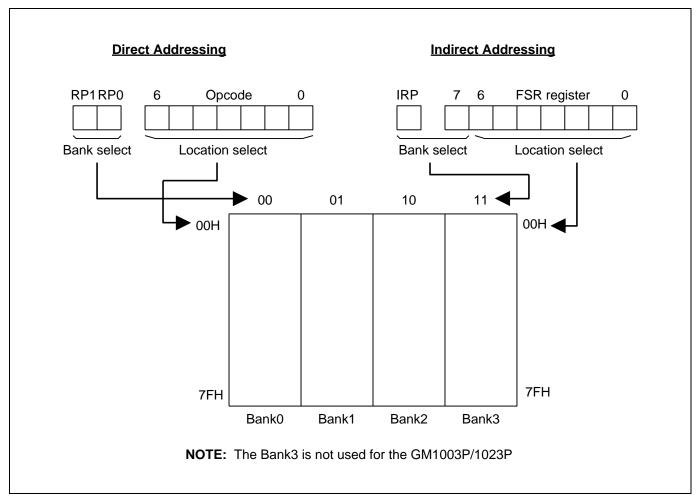

#### 2.3.3 ADDRESSING MODES

The MC71PB204 supports two addressing modes: direct or indirect. In Direct Addressing, the 9-bit direct address is concatenated from RP [1:0] bits of STATUS (03H) register and a 7LSB of instruction word. Indirect addressing is possible by using the CONFIG (00H) register. Any instruction using CONFIG (00H) register actually accesses data pointed by the File Select Register (FSR (04H)). The 9-bit address is concatenated from IRP bit from STATUS (03H) register and 8 bits of FSR (04H) register. Both Direct and indirect addressing modes are shown in figure below.

Figure 2-5. Direct/Indirect addressing

### 2.3.3.1. Indirect Addressing Mode

Indirect addressing mode is applied when the instruction point directly to the CONFIG (00H) register. Any instruction pointing directly the CONFIG (00H) register as a source/destination, actually accesses data pointed by the FSR (file select register, 04H).

In indirect addressing mode, user can select three of supported indirect addressing mode:

- Simple indirect: the indirect address comes from concatenated IRP and FSR.

- Indirect with post increment: the content of FSR register is post incremented, after execution of any instruction using indirect addressing mode.

- Indirect with post decrement: the content of FSR register is post decremented, after execution of any instruction using indirect addressing mode.

A simple program to clear RAM locations 20H-2FH using indirect addressing is shown in Example 2-1.

#### **EXAMPLE 2-1: INDIRECT ADDRESSING**

| NEXT:     | MOVLW<br>MOVWF<br>CLRF<br>INCF<br>BTFSS<br>GOTO | 0x20<br>FSR<br>CONFIG<br>FSR,F<br>FSR,4<br>NEXT | ;initialize pointer<br>;to RAM<br>;clear CONFIG register<br>;inc pointer<br>;all done?<br>;no clear next |

|-----------|-------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| CONTINUE: | GOTO                                            | NEXI                                            | ;no clear next                                                                                           |

|           | :                                               |                                                 | ;yes continue                                                                                            |

## 3. INTERRUPT

## 3.1 INTERRUPT STRUCTURE

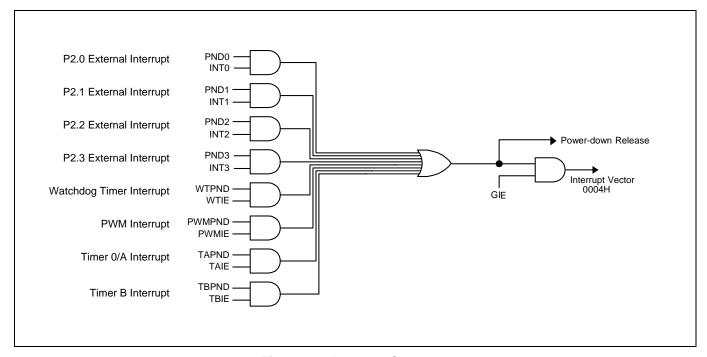

The MC71PB204 has eight interrupt sources:

- Four external interrupts (Port 2.0~Port 2.3)

- Watchdog timer interrupt

- PWM interrupt

- Timer 0/A underflow interrupt

- Timer B underflow interrupt

The interrupt vector address is located at 0004H of ROM address area. Please be careful not to overwrite any of the stored vector addresses.

Figure 3-1. Interrupt Structure

The interrupt control registers, INTCON and EINT2 have enable bit of individual interrupt, and INTCON has global interrupt enable bit. The interrupt pending registers, IPND and EPND2 record individual interrupt requests in corresponding bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When GIE bit is set, and an interrupt's pending bit and interrupt enable bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in the INTCON or EINT2.

The watchdog timer interrupt, PWM interrupt, timer 0/A underflow interrupt, and timer B underflow interrupt control bits are contained in the INTCON register and their corresponding interrupt pending bits are in the IPND register.

Four external interrupts are contained in the EINT2 register and their corresponding interrupt pending bits are in the EPND2 register.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupts, the return address is pushed onto the stack and the PC is loaded with vector address 0004H. At the interrupt service routine, the source(s) of the interrupt can be determined by polling the interrupt pending bits. The interrupt pending bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

## 3.2 SAVING KEY REGISTERS DURING AN INTERRUPT SERVICE

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers like W register or STATUS register during an interrupt. This will have to be implemented in software. Ex 3-1) shows how to store and restore the STATUS, W, and PCLATH registers. The register, W\_TEMP, must be defined in each bank at the same offset from the bank base address.

#### The example:

- 1) Stores the W register.

- 2) Stores the STATUS register in bank 0.

- 3) Stores the PCLATH register.

- 4) Executes the Interrupt Service Routine code.

- 5) Restores the PCLATH register.

- 6) Restores the STATUS and W registers.

#### EX 3-1) SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF       | W_TEMP           | ;Copy W to TEMP register, could be bank one or zero       |

|-------------|------------------|-----------------------------------------------------------|

| SWAPF       | STATUS, W        | ;Swap status to be saved into W                           |

| CLRF        | STATUS           | ;bank 0, regardless of current bank, Clears IRP, RP1, RP0 |

| MOVWF       | STATUS_TEMP      | ;Save status to bank zero STATUS_TEMP register            |

| MOVF        | PCLATH, W        | ;Only required if using pages 1, 2 and/or 3               |

| MOVWF       | PCLATH_TEMP      | ;Save PCLATH into W                                       |

| CLRF        | PCLATH           | ;Page zero, regardless of current page                    |

| :           |                  |                                                           |

| :(Interrupt | Service Routine) |                                                           |

| :           |                  |                                                           |

| MOVF        | PCLATH_TEMP, W   | ;Restore PCLATH                                           |

| MOVWF       | PCLATH           | ;Move W into PCLATH                                       |

| SWAPF       | STATUS_TEMP, W   | ;Swap STATUS_TEMP register into W                         |

|             |                  | ;(sets bank to original state)                            |

| MOVWF       | STATUS           | ;Move W into STATUS register                              |

| SWAPF       | W_TEMP, F        | ;Swap W_TEMP                                              |

| SWAPF       | W_TEMP, W        | ;Swap W_TEMP into W                                       |

## **NOTES**

## 4. INSTRUCTION SET

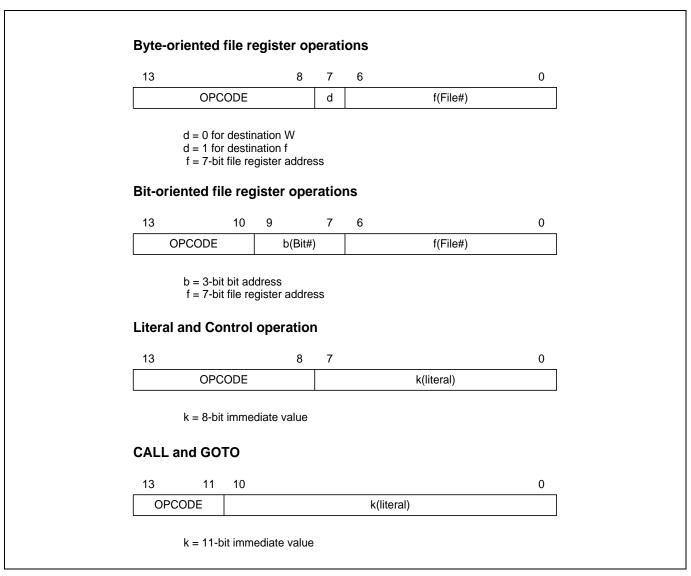

Each MC71PB204 instruction has 14-bit word length divided into an OPCODE, which specifies the instruction type and operands. The instruction set is grouped into the three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Figure below shows three general formats that the instruction can have.

Figure 4-1. General Format of Instructions

All instructions are executed within 2 Clock cycles. Except the instructions using indirect addressing mode which are executed within 4 CLK periods (two instruction cycles).

**Table 4-1. Opcode Filed Descriptions**

| Field       | Description                                                                                                    |

|-------------|----------------------------------------------------------------------------------------------------------------|

| f           | Register file address (0x00 to 0x7F)                                                                           |

| W           | Working register (accumulator)                                                                                 |

| b           | Bit address within an 8-bit file register                                                                      |

| k           | Literal field, constant data or label                                                                          |

| Х           | Don't care location (=0 or 1)                                                                                  |

| d           | Destination selected; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1 |

| label       | Label name                                                                                                     |

| TOS         | Top of Stack                                                                                                   |

| PC          | Program Counter                                                                                                |

| PCLATH      | Program Counter High Latch                                                                                     |

| GIE         | Global Interrupt Enable bit                                                                                    |

| WDTCNT      | Watchdog Timer Counter                                                                                         |

| nTO         | Time-out bit                                                                                                   |

| nPD         | Power-down bit                                                                                                 |

| destination | Destination either the W register or the specified register file location                                      |

## **4.1 INSTRUCTION SET SUMMARY**

## **4.1.1 BYTE-ORIENTED INSTRUCTION**

**Table 4-2. Byte-Oriented Operations**

| Mnemon  | ic.  | Description                      |         | 14-bit | opcode  |      | Status   | Cycles |

|---------|------|----------------------------------|---------|--------|---------|------|----------|--------|

| operand | •    | Description                      | MSB LSB |        |         |      | Status   | Cycles |

| ADDWF   | f, d | Add W and f                      | 0 0     | 0111   | dfff    | ffff | C, DC, Z | 2      |

| ADDWI   | d    | Add W and (FSR)                  | 0 0     | 0111   | d000    | 0000 | C, DC, Z | 4      |

| ANDWF   | f, d | AND W and f                      | 00      | 0101   | dfff    | ffff | Z        | 2      |

| ANDWE   | d    | AND W and (FSR)                  | 00      | 0101   | d000    | 0000 | Z        | 4      |

| CLRF    | f    | Clear f                          | 00      | 0001   | 1fff    | ffff | Z        | 2      |

| CLNI    |      | Clear (FSR)                      | 00      | 0001   | 1000    | 0000 | Z        | 4      |

| CLRW    | f, d | Add W and f                      | 00      | 0001   | 0 x x x | xxxx | Z        | 2      |

| COME    | f, d | Complement f                     | 00      | 1001   | dfff    | ffff | Z        | 2      |

| COMF    | d    | Complement (FSR)                 | 00      | 1001   | d000    | 0000 | Z        | 4      |

| DECF    | f, d | Decrement f                      | 00      | 0011   | dfff    | ffff | Z        | 2      |

| DECF    | d    | Decrement (FSR)                  | 00      | 0011   | d000    | 0000 | Z        | 4      |

| DECFSZ  | f, d | Decrement f, Skip if 0           | 00      | 1011   | dfff    | ffff | -        | 2      |

| DECFSZ  | d    | Decrement (FSR), Skip if 0       | 00      | 1011   | d000    | 0000 | -        | 4      |

| INCF    | f, d | Increment f                      | 00      | 1010   | dfff    | ffff | Z        | 2      |

| INCF    | d    | Increment (FSR)                  | 00      | 1010   | d000    | 0000 | Z        | 4      |

| INCFSZ  | f, d | Increment f, Skip if 0           | 00      | 1111   | dfff    | ffff | -        | 2      |

| INCESZ  | d    | Increment (FSR), Skip if 0       | 00      | 1111   | d000    | 0000 | -        | 4      |

| IORWF   | f, d | Inclusive OR W with f            | 00      | 0100   | dfff    | ffff | Z        | 2      |

| IOKWI   | d    | Inclusive OR W with (FSR)        | 00      | 0100   | d000    | 0000 | Z        | 4      |

| MOVF    | f, d | Move f                           | 00      | 1000   | dfff    | ffff | Z        | 2      |

| IVIOVI  | d    | Move (FSR)                       | 00      | 1000   | d000    | 0000 | Z        | 4      |

| MOVWF   | f, d | Move W to f                      | 00      | 0000   | 1 f f f | ffff | -        | 2      |

| IVIOVVI |      | Move W to (FSR)                  | 00      | 0000   | 1000    | 0000 | -        | 4      |

| NOP     |      | No Operation                     | 00      | 0000   | 0 x x 0 | 0000 | -        | 2      |

| RLF     | f, d | Rotate Left f through Carry      | 00      | 1101   | dfff    | ffff | С        | 2      |

| IXLI    | d    | Rotate Left (FSR) through Carry  | 00      | 1101   | d000    | 0000 | С        | 4      |

| RRF     | f, d | Rotate Right f through Carry     | 00      | 1100   | dfff    | ffff | С        | 2      |

| IXIXI   | d    | Rotate Right (FSR) through Carry | 00      | 1100   | d000    | 0000 | С        | 4      |

| SUBWF   | f, d | Subtract W from f                | 00      | 0010   | dfff    | ffff | C, DC, Z | 2      |

| 30Bvvi  | d    | Subtract W from (FSR)            | 00      | 0010   | d000    | 0000 | C, DC, Z | 2      |

| SWAPF   | f, d | Swap nibbles in f                | 00      | 1110   | dfff    | ffff | -        | 2      |

| JWAFI   | d    | Swap nibbles in (FSR)            | 00      | 1110   | d000    | 0000 | -        | 2      |

| XORWF   | f, d | Exclusive OR W with f            | 00      | 0110   | dfff    | ffff | Z        | 2      |

| AUNVE   | d    | Exclusive OR W with (FSR)        | 00      | 0110   | d000    | 0000 | Z        | 4      |

## **4.1.2 BIT-ORIENTED INSTRUCTION**

**Table 4-3. Bit-Oriented Operations**

| Mnemonic, operands |      | Description                   | 14-bit opcode |      |      |      | Status | Cycles |

|--------------------|------|-------------------------------|---------------|------|------|------|--------|--------|

|                    |      |                               | MSB           |      |      | LSB  | Status | Cycles |

| BCF                | f, b | Bit Clear f                   | 0 1           | 00bb | bfff | ffff | -      | 2      |

|                    | b    | Bit Clear (FSR)               | 0 1           | 00bb | b000 | 0000 | -      | 4      |

| BSF                | f, b | Bit Set f                     | 01            | 01bb | bfff | ffff | -      | 2      |

|                    | b    | Bit Set (FSR)                 | 0 1           | 01bb | b000 | 0000 | -      | 4      |

| BTFSC              | f, b | Bit Test f, Skip if Clear     | 01            | 10bb | bfff | ffff | -      | 2      |

|                    | b    | Bit Test (FSR), Skip if Clear | 0 1           | 10bb | b000 | 0000 | -      | 4      |

| BTFSS              | f, b | Bit Test f, Skip if Set       | 01            | 11bb | bfff | ffff | -      | 2      |

|                    | b    | Bit Test (FSR), Skip if Set   | 01            | 11bb | b000 | 0000 | -      | 2      |

### 4.1.3 LITERAL AND CONTROL OPERATIONS

**Table 4-4. Literal and Control Operations**

| Mnemonic,<br>operands |     | Description                 |     | 14-bi   | Status | Cycles  |          |   |

|-----------------------|-----|-----------------------------|-----|---------|--------|---------|----------|---|

|                       |     |                             | MSB | MSB LSB |        |         |          |   |

| ADDLW                 | imm | Add literal and f           | 1 1 | 111x    | kkkk   | kkkk    | C, DC, Z | 2 |

| ANDLW                 | imm | Add literal and f           | 1 1 | 1001    | kkkk   | kkkk    | Z        | 2 |

| CALL                  | imm | Call subroutine             | 1 0 | 0 k k k | kkkk   | kkkk    | -        | 4 |

| CLRWDT                | -   | Clear Watchdog Timer        | 0 0 | 0000    | 0110   | 0100    | nTO, nPD | 2 |

| GOTO                  | imm | Go to address               | 1 0 | 1 k k k | kkkk   | kkkk    | -        | 4 |

| IORLW                 | imm | Inclusive OR literal with W | 1 1 | 1000    | kkkk   | kkkk    | Z        | 2 |

| MOVLW                 | imm | Move literal to W           | 1 1 | 0 0 x x | kkkk   | kkkk    | -        | 2 |

| RETFIE                | -   | Return from Interrupt       | 0 0 | 0000    | 0000   | 1001    | -        | 4 |

| RETLW                 | imm | Return with literal in W    | 1 1 | 0 1 x x | kkkk   | kkkk    | -        | 4 |

| RETURN                | -   | Return from subroutine      | 0 0 | 0000    | 0000   | 1000    | -        | 4 |

| SLEEP                 | -   | Go into standby mode        | 0 0 | 0000    | 0110   | 0 0 1 1 | nTO, nPD | 2 |

| SUBLW                 | imm | Subtract W from literal     | 1 1 | 1 1 0 x | kkkk   | kkkk    | C, DC, Z | 2 |

| XORLW                 | imm | Exclusive OR literal with W | 1 1 | 1010    | kkkk   | kkkk    | Z        | 2 |

## 4.2 INSTRUCTION DESCRIPTION

## 4.2.1 ADDLW - ADD LITERAL AND W

**Operands:**  $0 \le imm(k) \le 255$

Operation:  $W \leftarrow W + imm(k)$

Status Affected: C, DC, Z

**Description:** The contents of W register are added to the eight bit immediate data 'imm' and the result is placed in the W register.

**Encoding:** 1 1 1 1 1 1 x k k k k k k k k

Cycles: DIR: 2

**Example:** ADDLW 0x15

**Before Instruction**

W = 0x10

**After Instruction**

W = 0x25

#### 4.2.2 ADDWF - ADD W AND F

**Operands:**  $0 \le f \le 127$

$d \in [0, 1]$

**Operation:** destination <= W + f

destination <= W + FSR

Status Affected: C, DC, Z

**Description:** ADDWF instruction add contents of the W register with register specified by 'f' operand. If 'd' is 0 the result is stored in the W register. If 'd' is 1 the result is stored back in register 'f'.

**Encoding:**

| 0 0 | 0 1 1 1 | dfff    | ffff    |

|-----|---------|---------|---------|

| 0 0 | 0 1 1 1 | d 0 0 0 | 0 0 0 0 |

Cycles: DIR: 2

INDIR: 4

**Example:** ADDWF FSR, 0

**Before Instruction**

W = 0x17 FSR = 0xC2

**After Instruction**

W = 0xD9 FSR = 0XC2

## 4.2.3 ANDLW - AND LITERAL WITH W

**Operands:**  $0 \le imm(k) \le 255$

**Operation:**  $W \leftarrow W \text{ and imm } (k)$

Status Affected: Z

**Description:** The contents of W register are AND'ed with the eight bit immediate data 'imm'. The result is

placed in the W

**Encoding:** 1 1 1 0 0 1 k k k k k k k k

Cycles: DIR: 2

**Example:** ANDLW 0x5F

**Before Instruction**

W = 0xA3

**After Instruction**

W = 0x03

#### 4.2.4 ANDWF - AND W WITH F

**Operands:**  $0 \le f \le 127$

$d \in [0, 1]$

**Operation:** destination <= W and f

destination <= W and FSR

Status Affected: Z

**Description:** ANDWF instruction AND the W register with register specified by 'f' operand. The result is stored in W or back in 'f' register respectively to the 'd' value.

**Encoding:**

| 0 0 | 0101 | dfff    | 1 1 1 1 |

|-----|------|---------|---------|

| 0 0 | 0101 | d 0 0 0 | 0 0 0 0 |

Cycles: DIR: 2

INDIR: 4

**Example:** ANDWF FSR, 1

**Before Instruction**

W = 0x17 FSR = 0XC2

**After Instruction**

W = 0X17 FSR = 0x02

# 4.2.5 BCF - BIT CLEAR F

**Operands:**  $0 \le f \le 127$

$0 \le b \le 7$

Operation: f.b  $\leq 0$

FSR.b <= 0

Status Affected: -

**Description:** Bit 'b' in register 'f' is cleared.

01 00bb bfff ffff

Cycles: DIR : 2

INDIR: 4

**Example:** BCF Flag\_Buf, 1

**Before Instruction**

$Flag_Buf = 0x17$

**After Instruction**

$Flag_Buf = 0x16$

# 4.2.6 BSF – BIT SET F

**Operands:**  $0 \le f \le 127$

$0 \le b \le 7$

Operation: f.b <= 1

FSR.b <= 1

Status Affected: -

**Description:** Bit 'b' in register 'f' is cleared.

01 01bb bfff

Encoding:

01 01bb b000 0000

$f\ f\ f\ f$

Cycles: DIR: 2

INDIR: 4

**Example:** BSF Flag\_Buf, 7

**Before Instruction**

$Flag_Buf = 0x17$

**After Instruction**

$Flag_Buf = 0x97$

## 4.2.7 BTFSC - BIT TEST, SKIP IF CLEAR

**Operands:**  $0 \le f \le 127$

$0 \le b \le 7$

**Operation:** skip if, f.b = 0

skip if, FSR.b = 0

Status Affected: -

**Description:** Check the 'b' bit in 'f' register and skip next instruction when 'b' is '0'. If bit 'b' is '0' then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction.

**Encoding:**

| 0 1 | 10bb    | bfff    | ffff    |

|-----|---------|---------|---------|

| 0 1 | 1 0 b b | b 0 0 0 | 0 0 0 0 |

Cycles: DIR: 2

INDIR: 4

**Example:** aaa: BTFSC Flag\_Buf, 1

bbb: GOTO ccc

ddd:

**Before Instruction**

PC = address aaa

**After Instruction**

If  $Flag_Buf < 1 > = 0$ ,

PC = address ddd

If  $Flag_Buf < 1 > = 1$ ,

PC = address bbb

## 4.2.8 BTFSS - BIT TEST, SKIP IF SET

**Operands:**  $0 \le f \le 127$

$0 \le b \le 7$

**Operation:** skip if f.b = 1

skip if FSR.b = 1

Status Affected: -

**Description:** If bit 'b' in register 'f' is '1' then the next instruction is skipped. If bit 'b' is '1' then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction.

**Encoding:**

| 0 1 | 1 1 b b | bfff | ffff |

|-----|---------|------|------|

|     |         |      |      |

01 1166 6000 0000

Cycles: DIR: 2

INDIR: 4

**Example:** aaa: BTFSC Flag\_Buf, 1

bbb: GOTO ccc

ddd:

**Before Instruction**

PC = address aaa

**After Instruction**

If  $Flag_Buf<1>=0$ ,

PC = address bbb

If  $Flag_Buf<1>=1$ ,

PC = address ddd

#### 4.2.9 CALL - CALL SUBROUTINE

**Operands:**  $0 \le imm(k) \le 2047$

Operation: TOS  $\leq$  PC + 1,

$PC[10:0] \le imm(k),$

PC [12:11] <= PCLATH [4:3]

Status Affected: -

**Description:** Call Subroutine. First, return address PC+1 is pushed onto the stack. The eleven bit immediate address is loaded into PC [10:0]. The upper bits of the PC are loaded from PCLATH. CALL is two-cycle instruction.

Encoding: 10 0kkk kkkk kkkk

Cycles: 4

**Example:** aaa: CALL bbb

**Before Instruction**

PC = address aaa

**After Instruction**

PC = address bbb SP = address aaa+1

# 4.2.10 CLRF - CLEAR F

**Operands:**  $0 \le f \le 127$

Operation:  $f \le 0x00$

FSR <= 0x00

Status Affected: Z

**Description:** The contents of register 'f' is cleared and the Z bit in STATUS register is set

Encoding:

00 0001 1000 0000

Cycles: DIR: 2

INDIR: 4

**Example:** CLRF Flag\_Buf

**Before Instruction**

$Flag_Buf = 0xAA$

After Instruction

$Flag_Buf = 0x00$

# 4.2.11 CLRW - CLEAR W

Operands: -

Operation:  $W \le 0x00$

Status Affected: Z

**Description:** The contents of working register W is cleared and the Z bit in STATUS register is set

**Encoding:** 0 0 0 0 0 1 0 x x x x x x x

Cycles: 2

**Example:** CLRW

**Before Instruction**

W = 0xAA

**After Instruction**

W = 0x00

## 4.2.12 CLRWDT - CLEAR WATCHDOG TIMER

Operands: -

Operation: WDTCNT <= Clear

Status Affected: nTO, nPD

**Description:** CLRWDT instruction resets the WDTCNT. Status bits nTO and nPD are set.

**Encoding:** 0 0 0 0 0 0 0 1 1 0 0 1 00

Cycles: 2

**Example:** CLRWDT

**Before Instruction**

WDTCNT = ?

**After Instruction**

WDTCNT = 0x00 nTO = 1 nPD = 1

#### 4.2.13 COMF - COMPLEMENT F

**Operands:**  $0 \le f \le 127$

$d \in [0, 1]$

**Operation:** destination <= f

destination <= FSR

Status Affected: Z

**Description:** The contents of register 'f' is complemented and transferred to the destination W or 'f' depending of the 'd'.

00 1001 dfff ffff

**Encoding:**

00 1001 d000 0000

Cycles: DIR: 2

INDIR: 4

**Example:** COMF REG1, 0

**Before Instruction**

REG1 = 0x13

**After Instruction**

$\begin{array}{ccc} \mathsf{REG1} & = & \mathsf{0x13} \\ \mathsf{W} & = & \mathsf{0xEC} \end{array}$

## 4.2.14 DECF - DECREMENT F

**Operands:**  $0 \le f \le 127$

$d \in [0,\,1]$

**Operation:** destination  $\leq f - 1$

destination <= FSR - 1

Status Affected: Z

**Description:** Decrement register 'f'. The result of operation is stored in the destination W or 'f' depending of the

'd' value.

**Encoding:**

00 0011 dfff ffff

00 0011 d000 0000

Cycles: DIR: 2

INDIR: 4

**Example:** DECF REG1, 1

**Before Instruction**

$\begin{array}{rcl}

\mathsf{REG1} & = & 0\mathsf{x1} \\

\mathsf{Z} & = & 0

\end{array}$

**After Instruction**

$\begin{array}{rcl}

\mathsf{REG1} & = & 0x0 \\

\mathsf{Z} & = & 1

\end{array}$

# 4.2.15 DECFSZ - DECREMENT F, SKIP IF 0

**Operands:**  $0 \le f \le 127$

$d \in [0,\,1]$

**Operation:** destination  $\leftarrow$  f - 1, Skip if result = 0

destination  $\leftarrow$  FSR -1, Skip if result = 0

Status Affected: -

**Description:** The contents of register 'f' are decremented and stored in the destination. If the result of operation is 0, the next instruction, which is already fetched, is discarded and NOP is executed instead making it two-cycle instruction.

00 1011 dfff ffff

Encoding: 0 0 1 0 1 1 d 0 0 0 0 0 0 0

Cycles: DIR: 2

INDIR: 4

**Example:** aaa: DECFSZ REG1, 1

GOTO aaa

bbb:

**Before Instruction**

PC = address aaa

**After Instruction**

REG1 = REG1 -1

If REG1 = 0.

PC = address bbb

If REG1  $\neq$  0,

PC = address aaa + 1

## 4.2.16 GOTO - UNCONDITIONAL BRANCH

**Operands:**  $0 \le imm(k) \le 2047$

**Operation:**  $PC [10:0] \le imm (k)$

PC [12:11] <= PCLATH [4:3]

Status Affected: -

**Description:** *GOTO* is an unconditional branch. The eleven bit immediate value is loaded into PC bits [10:0]. The upper bits of PC are loaded from PCLATH [4:3]. GOTO is a two-cycle instruction

Encoding: 10 1 k k k k k k k k k

Cycles: 4

**Example:** GOTO Loop

**After Instruction**

PC = address Loop

#### 4.2.17 INCF-INCREMENT F

**Operands:**  $0 \le f \le 127$

$d \in [0, 1]$

**Operation:** destination  $\leq f + 1$

destination <= FSR + 1

Status Affected: Z

**Description:** The contents of register 'f' are incremented. The result of operation is stored in the W register or 'f', depending of the 'd' value.

**Encoding:**

00 1010 dfff ffff 00 1010 d000 0000

Cycles: DIR: 2

INDIR: 4

**Example:** INCF REG1, 1

**Before Instruction**

$\begin{array}{ccc} REG1 & = & 0xFF \\ Z & = & 0 \end{array}$

**After Instruction**

$\begin{array}{ccc} REG1 & = & 0x0 \\ Z & = & 1 \end{array}$

## 4.2.18 INCFSZ - INCREMENT F, SKIP IF 0

**Operands:**  $0 \le f \le 127$

$d \in [0,1]$

**Operation:** destination  $\leq$  f + 1, Skip if result = 0

destination <= FSR + 1, Skip if result = 0

Status Affected: -

**Description:** The contents of register 'f' are incremented and stored in the destination. If the result is 0, the next instruction which is already fetched, is discarded, and a NOP is executed instead making it a two-cycle instruction.

**Encoding:**

| 0 0 | 1111 | dfff    | ffff    |

|-----|------|---------|---------|

| 0 0 | 1111 | d 0 0 0 | 0 0 0 0 |

Cycles: DIR: 2

INDIR: 4

**Example:** aaa: INCFSZ REG1, 1

GOTO Loop

bbb:

**Before Instruction**

PC = address aaa

**After Instruction**

REG1 = REG1 + 1

If REG1 = 0,

PC = address bbb

If REG1  $\neq$  0,

PC = address aaa + 1

## 4.2.19 IORLW - INCLUSIVE OR LITERAL WITH W

**Operands:**  $0 \le imm (k) \le 255$

**Operation:**  $W \leftarrow W \cap W \cap W$

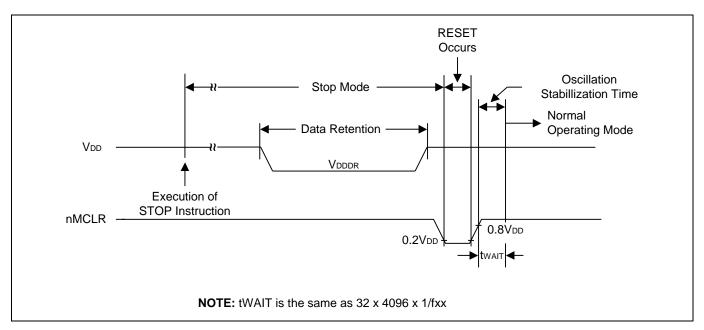

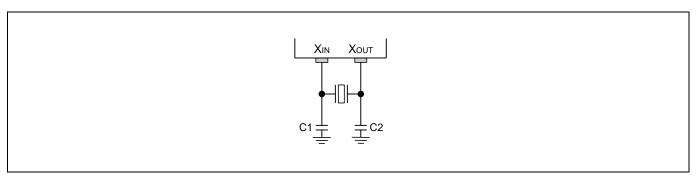

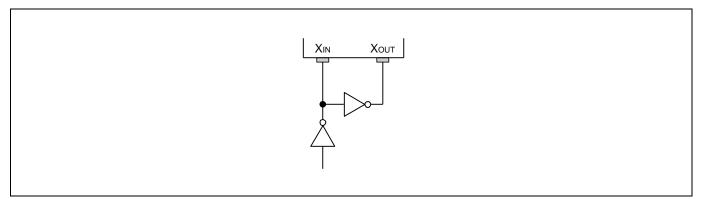

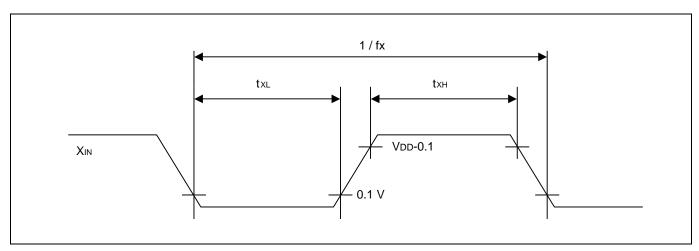

Status Affected: Z