ABOV SEMICONDUCTOR Co., Ltd. LIGHT-TO-DIGITAL CONVERTER

# MC8201

# Data Sheet (REV.1.5)

# **REVISION HISTORY**

#### REVISION 1.0 (October 7, 2011)

- Initial Version

#### REVISION 1.1 (October 11, 2011)

- Modify PS description

#### REVISION 1.2 (November 15, 2011)

- Fix registers description

#### REVISION 1.3 (December 15, 2011)

- Fix ps algorithm description

- Fix ps register description and bit width

- Fix electrical specifications

#### REVISION 1.4 (January 4, 2012)

- Fix DC spec (VIL, VIH)

# **REVISION 1.5 (March 18, 2012)**

- Fix registers description

- Revise PS algorithm (PS resolution is changed to 10/8-bit)

#### REVISION 1.5 Published by Design Team ©2012 ABOV Semiconductor Co., Ltd. All rights reserved.

Additional information of this manual may be served by ABOV Semiconductor offices in Korea or Distributors.

ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

# **Table of Contents**

| 1. | OVERVIEW                                | 6  |

|----|-----------------------------------------|----|

|    | 1.1 DESCRIPTION                         | 6  |

|    | 1.2 FEATURES                            | 6  |

|    | 1.3 ORDERING INFORMATION                | 7  |

|    | 1.4 APPLICATIONS                        | 7  |

|    | 1.5 BLOCK DIAGRAM                       | 7  |

|    | 1.6 PIN CONFIGURATIONS                  | 8  |

|    | 1.7 PKG DIAGRAM                         | 9  |

|    | 1.8 PIN DESCRIPTION                     | 10 |

|    | 1.9 SLAVE ADDRESS                       | 10 |

|    | 1.10 ELELCTRICAL CHARACTERISTICS        | 10 |

|    | 1.10.1 ABSOLUTE MAXIMUM RATINGS         | 10 |

|    | 1.10.2 RECOMMENDED OPERATING CONDITION  | 11 |

|    | 1.10.3 ELECTRICAL SPECIFICATIONS        | 11 |

|    | 1.10.4 I <sup>2</sup> C CHARACTERISTICS | 11 |

|    | 1.10.5 OPTICAL CHARACTERISTICS          | 12 |

| 2. | OPERATION                               | 15 |

|    | 2.1 I <sup>2</sup> C                    | 15 |

|    | 2.1.1 OVERVIEW                          | 15 |

|    | 2.1.2 I <sup>2</sup> C BIT TRANSFER     | 15 |

|    | 2.1.3 START / REPEATED START / STOP     | 15 |

|    | 2.1.4 DATA TRANSFER                     | 16 |

|    | 2.1.5 ACKNOWLEDGE                       | 16 |

|    | 2.1.6 OPERATION                         | 17 |

|    | 2.2 REGISTERS                           | 18 |

|    | 2.2.1 OVERVIEW                          | 18 |

|    | 2.2.2 REGISTER MAP                      | 19 |

|    | 2.2.3 REGISTER DESCRIPTION              | 19 |

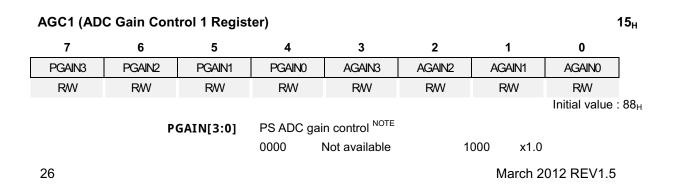

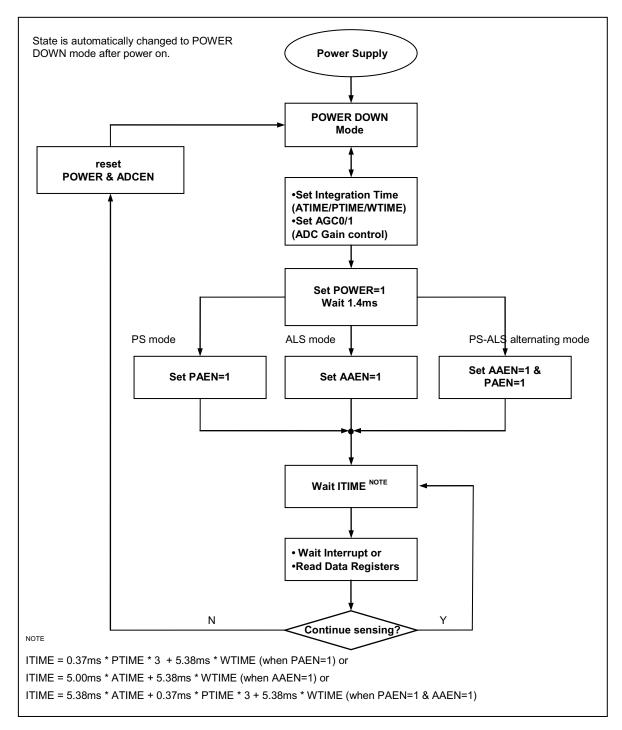

|    | 2.3 PS/ALS OPERATION                    | 28 |

|    | 2.3.1 FSM                               | 28 |

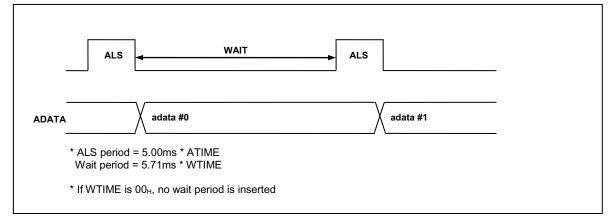

|    | 2.3.2 ALS OPERATION                     | 29 |

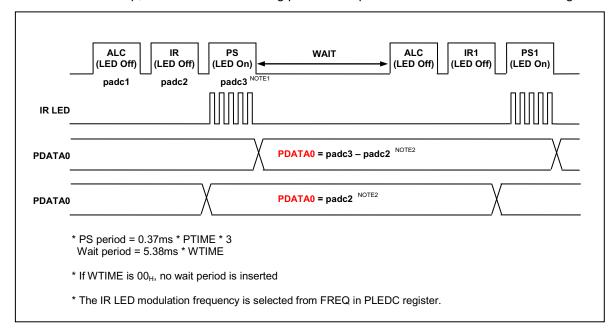

|    | 2.3.3 PS OPERATION                      | 29 |

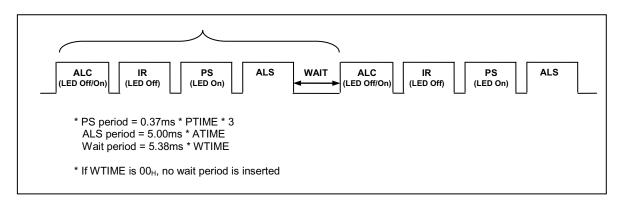

|    | 2.3.4 PS-ALS ALTERNATING OPERATION      | 30 |

|    | 2.3.5 INTERRUPT                         | 30 |

|    | 2.3.6 POWER CONSUMPTION                 | 34 |

|    | 2.4 APPLICATION INFORMATION : SOFTWARE  | 35 |

|    | 2.4.1 OVERVIEW                          | 35 |

| 3. | APPENDIX                                | 36 |

|    |                                         |    |

# **List of Figures**

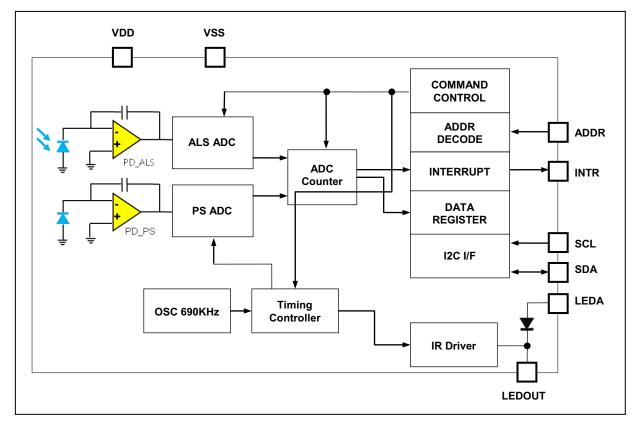

| Figure 1-1 Block Diagram of MC8201                                     |

|------------------------------------------------------------------------|

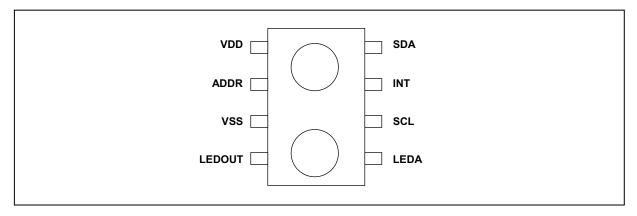

| Figure 1-2 PKG Diagram                                                 |

| Figure 1-3 PKG DIMENSION9                                              |

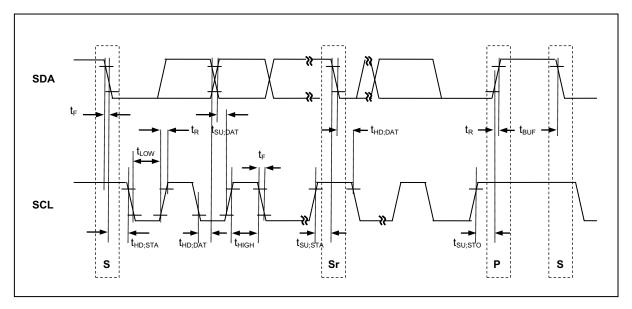

| Figure 1-4 Definition of timing for fast mode devices on the I2C bus12 |

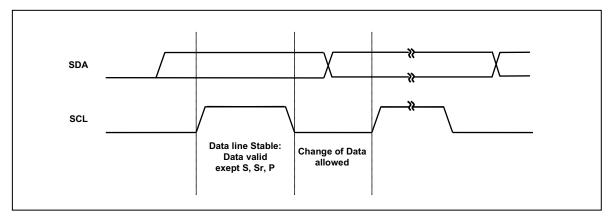

| Figure 2-1 Bit Transfer on the I <sup>2</sup> C-Bus15                  |

| Figure 2-2 START and STOP Condition                                    |

| Figure 2-3 STOP or Repeated START Condition                            |

| Figure 2-4 Acknowledge on the I <sup>2</sup> C-Bus17                   |

| Figure 2-5 I2C Write Protocol                                          |

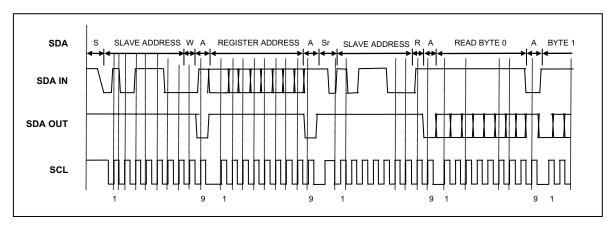

| Figure 2-6 I2C Read Protocol                                           |

| Figure 2-7 PS-ALS Operating State Machine                              |

| Figure 2-8 ALS Operation                                               |

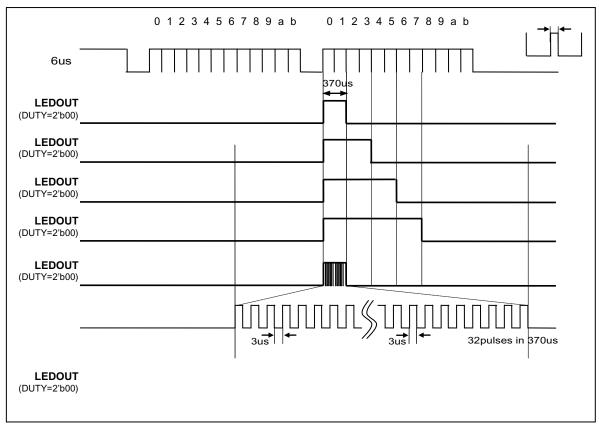

| Figure 2-9 PS Type 0 Operation                                         |

| Figure 2-10 PS Type 1 Operation오류! 책갈피가 정의되어 있지 않습니다.                  |

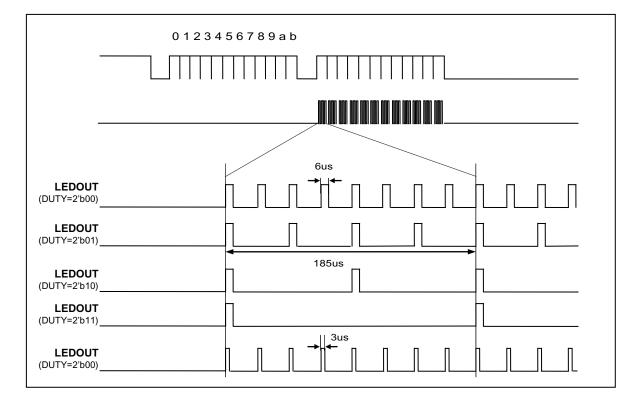

| Figure 2-11 ALS-PS Alternating Operation                               |

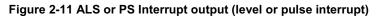

| Figure 2-12 ALS or PS Interrupt output (level or pulse interrupt)      |

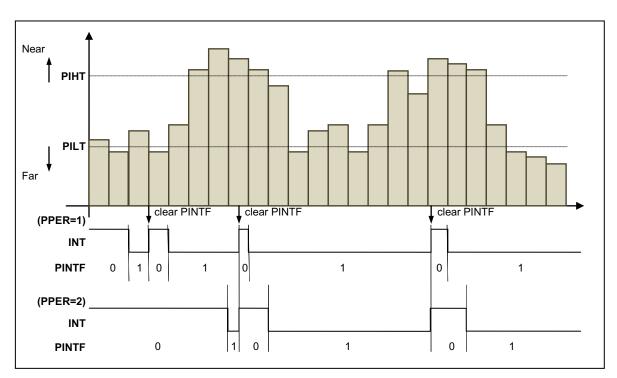

| Figure 2-13 PS Interrupt Output (PPER=1 or 2 & INTEDGE=0)              |

| Figure 2-14 PS Detection (PPER=1 or 2)                                 |

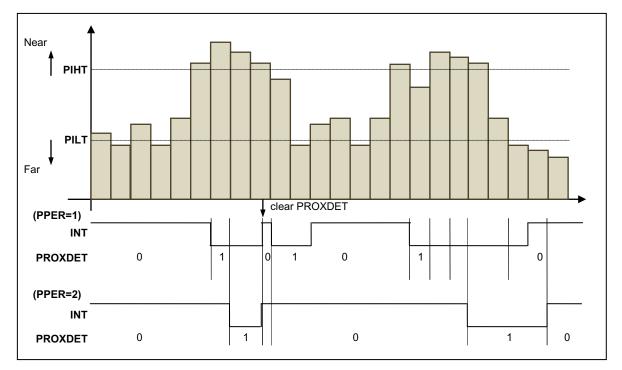

| Figure 2-15 Operating Modes                                            |

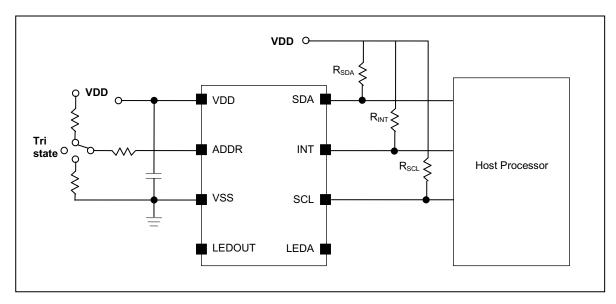

| Figure 3-1 Hardware pin connection diagram                             |

| Figure 3-2 I2C write example                                           |

| Figure 3-3 I2C read example                                            |

# MC8201

# **Digital Proximity and Ambient Light Sensor**

# **1. OVERVIEW**

# **1.1 DESCRIPTION**

The MC8201 integrates ALS(Ambient Light Sensor), PS(Proximity Sensor) and IR LED(Light Emitting Diode) driver in a single die, and merged with IR LED in a extremely small 8 pin package. It is an advanced digital ambient light sensor and proximity sensor, which can transform illuminance (light intensity) to a digital signal output and detect proximity of object.

For ambient light sensing, it combines an opened photodiode and a light shielded photodiode which is used to reduce dark noise. The opened photodiode is capable of providing a photovoltaic response and coated with Infra Red cut off filter on a CMOS integrated circuit. The photovoltaic response is converted into digital counter value by the ALS ADC of 16 bit resolution. It closely approximates the human eye spectral response of visible wavelength.

In addition, the MC8201 has another opened photodiode with IR pass filter in order to detect proximity of an object. When PS is enabled, the IR LED is turned on by the built-in IR LED driver. When the IR from the LED reaches an object and gets reflected back, the opened photodiode for proximity sensing converts the reflected IR light with center frequency of 850nm into current. The amount of current is converted into digital counter value by the PS ADC of 12-bit resolution. The counter value is inversely proportional to the square of the distance between the sensor and the object. The proximity detection feature operates well from bright sunlight to dark rooms. The wide dynamic range also allows for operation in short distance detection behind dark glass such as a cell phone. The operation voltage ranges from 2.4 to 3.6 volt.

The ALS features are ideal for reducing power consumption and adjusting brightness of display equipments like LCD, PDP, LED, virtual keyboard and portable projector, etc. The proximity detection feature is targeted esspecially for cell phones with touch screen. In cell phones, the proximity sensor can detect when a user positions the phone close to their ear and can disable the touch screen to prevent mal-functions due to touch events.

# **1.2 FEATURES**

- CMOS technology

- Independently programmable exposure time for PS and ALS

#### **Ambient Light Sensing**

- Convert incident light intensity to digital data

- 16-bit ALS ADC resolution

- Automatic light flickering cancellation supporting

- Block off IR(Infrared) by IR cut off coating

- Excellent transmittance of glass package

- Spectral response close to human eye

- Linear ALS response for easy design

- Low dark noise

#### **Proximity Detection**

- Integrated IR LED and synchronous LED driver

- Accept only 940nm for precise detection with strong IR background noise cancellation like fluorescent, incandescent light and sunlight

- Excellent ambient light(Background IR noise) cancellation capability

- 10/8-bit PS ADC resolution

#### **Additional Features**

- I<sup>2</sup>C protocol interface

- Low stop current 1uA typical

- Operating rang 2.4 ~ 3.6V

- Small size package (L1.431mm x 1.511mm x H)

- 8-LGA package

# **1.3 ORDERING INFORMATION**

| DEVICE NAME | INTERFACE        | TEMP. RANGE | PACKAGE TYPE | PACKAGE |

|-------------|------------------|-------------|--------------|---------|

| MC8201      | I <sup>2</sup> C | -40 to +85  | LGA          | 8-LGA   |

#### **Table 1-1 Ordering Information**

#### **1.4 APPLICATIONS**

- Cell phone

- Digital TV, Tablet PC, Notebook PC

- Navigation systems

- Display-equipped portable devices,etc..

# 1.5 BLOCK DIAGRAM

Figure 1-1 Block Diagram of MC8201

# **1.6 PIN CONFIGURATIONS**

8 LGA (MC8201)

# 1.7 PKG DIAGRAM

Figure 1-3 PKG DIMENSION

수정!!!

수정!!!

# **1.8 PIN DESCRIPTION**

| PIN Number | PIN Name | Description                                    | I/O           |

|------------|----------|------------------------------------------------|---------------|

| 1          | VDD      | Power supply : 2.4 to 3.6V                     | Power         |

| 2          | ADDR     | Address Select                                 | Input         |

| 3          | VSS      | Ground                                         | Power         |

| 4          | LEDOUT   | LED driver for proximity emitter – up to 180mA | O(Open Drain) |

| 5          | LEDA     | LED Anode, connect to VDD or $V_{BATT}$ on PCB | I             |

| 6          | SCL      | I <sup>2</sup> C Serial Clock Line             | Input         |

| 7          | INT      | ALS, PS Interrupt                              | O(Open Drain) |

| 8          | SDA      | I <sup>2</sup> C Serial Data Line              | O(Open Drain) |

Table 1-2 Pin Description

# **1.9 SLAVE ADDRESS**

| ADDR       | SLAVE ADDRESS |

|------------|---------------|

| LOW / OPEN | 1011_100      |

| HIGH       | 0110_011      |

**Table 1-3 Slave Address Selection**

# **1.10 ELELCTRICAL CHARACTERISTICS**

#### **1.10.1 ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                       | Min. | Max.  | Unit. | Remark |

|--------|---------------------------------|------|-------|-------|--------|

| VDD    | Supply voltage                  | 0    | 4.0   | V     |        |

| Tstg   | Storage temperature range       | -40  | 85    | °C    |        |

| VO     | Digital ouput voltage range     | -0.5 | 4.0   | V     |        |

| Ю      | Digital output current          | -1   | 20    | mA    |        |

| VHBM   | ESD tolerance, Human Body Model |      | 2,000 | V     |        |

#### **Table 1-4 Absolute Maximum Ratings**

<sup>NOTE</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliablility.

#### **1.10.2 RECOMMENDED OPERATING CONDITION**

| Symbol | Parameter                 | Min. | Тур. | Max. | Unit | Remark |

|--------|---------------------------|------|------|------|------|--------|

| VDD    | Supply voltage            | 2.4  | 3.0  | 3.6  | V    |        |

| ТА     | Operating temperature     | -40  |      | 85   | °C   |        |

| VIL    | SCL,SDA input low voltage |      |      | 400  | mV   |        |

| VIH    | SCL,SDA input low voltage | 1.4  |      |      | V    |        |

Table 1-5 Recommended Operating Condition

#### **1.10.3 ELECTRICAL SPECIFICATIONS**

| (VDD =3.0V, VLED=3.0V, VSS =0V, f <sub>SCL</sub> =40 | 00KHz, TA=+25℃±10%) |

|------------------------------------------------------|---------------------|

|------------------------------------------------------|---------------------|

| Symbol            | Parameter                             | Min.  | Тур.  | Max.  | Unit   | Remark                   |

|-------------------|---------------------------------------|-------|-------|-------|--------|--------------------------|

| V <sub>DD</sub>   | Power Supply                          | 2.4   | -     | 3.6   | V      |                          |

| I <sub>STOP</sub> | Power Down Current                    |       |       | 1     | uA     | Power down               |

| IDDALS            | Active Current for ALS                |       |       | 120   | uA     |                          |

| IDDPS             | Active Current for PS                 |       |       | 100   | uA     | Exclude LED driving      |

| λ <sub>P</sub>    | Peak Sensitivity wavelength<br>of ALS |       | 550   |       | nm     |                          |

| $\lambda_{PPS}$   | Peak Sensitivity wavelength<br>of PS  |       | 850   |       | nm     |                          |

| f <sub>OSC</sub>  | Internal Oscillator Frequency         | 552   | 690   | 828   | KHz    |                          |

| t <sub>INT</sub>  | ADC Integration/Conversion<br>Time    |       | 100   | 500   | ms     | 16-bit ADC data          |

| V <sub>OL</sub>   | INT,SDA ouput low voltage             | 0     |       | 0.4   | V      | 8mA sink current         |

| A000L             | ADC Count Value of ALS                | -     | 0     | 4     | counts | @0Lux, white color LED   |

| A <sub>001L</sub> | @ATIME=14 <sub>H</sub> (100ms)        |       | 8     |       | counts | @1Lux, white color LED   |

| A <sub>250L</sub> | AGC1=88 <sub>H</sub>                  | 1600  | 2000  | 2400  | counts | @250Lux, white color LED |

| DF <sub>ALS</sub> | Full Scale ALS ADC Count              |       |       | 65535 | counts |                          |

| DF <sub>PS</sub>  | Full Scale PS ADC Count               |       |       | 1023  | counts |                          |

| f <sub>LED0</sub> |                                       | 138.0 | 172.5 | 207.0 | KHz    | LDCTRL[0]=0 <sub>B</sub> |

| $f_{LED1}$        |                                       | 276.0 | 345.0 | 414.0 | KHz    | LDCTRL[0]=1 <sub>B</sub> |

| I <sub>LED1</sub> | IR LED Modulation<br>Frequency        |       | 60    |       | mA     | TSSEL=01 <sub>B</sub>    |

| I <sub>LED2</sub> |                                       |       | 120   |       | mA     | TSSEL=10 <sub>B</sub>    |

| I <sub>LED3</sub> |                                       |       | 180   |       | mA     | TSSEL=11 <sub>B</sub>    |

|                   |                                       |       |       |       |        |                          |

# **Table 1-6 Electrical Specifications**

# 1.10.4 I<sup>2</sup>C CHARACTERISTICS

The following table and figure show the timing codition of SDA and SCL bus lines for fast mode  $I^2C$  bus devices. <sup>NOTE1</sup>.

March 2012 REV1.5

# (VDD =3.0V, VSS =0V, TA=+25°C±10%)

| Parameter                                                                                         | Symbol <sup>NOTE2</sup> | Min | Max | Unit |

|---------------------------------------------------------------------------------------------------|-------------------------|-----|-----|------|

| SCL clock frequency                                                                               | t <sub>SCL</sub>        | 0   | 400 | KHz  |

| Hold time after (repeated) START condition. After this period, the first clock pulse is generated | t <sub>hd;sta</sub>     | 0.6 | -   | us   |

| LOW period of the SCL clock                                                                       | t <sub>LOW</sub>        | 1.3 | -   | us   |

| HIGH period of the SCL clock                                                                      | t <sub>ніGH</sub>       | 0.6 | -   | us   |

| Setup time for a repeated START condition                                                         | t <sub>SU;STA</sub>     | 0.6 | -   | us   |

| Data hold time                                                                                    | t <sub>hd;dat</sub>     | 0   | 0.9 | us   |

| Data setup time                                                                                   | t <sub>su;dat</sub>     | 100 | -   | ns   |

| Clock/data fall time                                                                              | t⊨                      | 0   | 300 | ns   |

| Clock/data rise time                                                                              | t <sub>R</sub>          | 0   | 300 | ns   |

| Setup time for STOP condition                                                                     | t <sub>su;sto</sub>     | 0.6 | -   | us   |

| Bus free time between a STOP and START condtion                                                   | t <sub>BUF</sub>        | 1.3 | -   | us   |

| Table 1-7 Timing | characteristics of I <sup>2</sup> C |

|------------------|-------------------------------------|

|------------------|-------------------------------------|

$^{\text{NOTE1}}$  All timing is shown with respect to 30% VDD and 70% VDD.

Figure 1-4 Definition of timing for fast mode devices on the I2C bus

#### **1.10.5 OPTICAL CHARACTERISTICS**

#### A. Response linearity by light source

MC8201 has high linearity performance by light illuminace in multi lighting booth system that can emit various lights by controlled its color temperature.

#### A .1. Fluorescent lamp 1

Color temperature (6500K)

Measurement Illuminace : 0~1,855lx

(graph 1. Spectrum of 6500K lamp)

Result under 6500K daylight

#### A .2. Fluorescent lamp 2

Color temperature (4200K) Measurement Illuminace : 0~422lx

Result under 4200K fluorescent lamp

#### A .3. Incandescent lamp

Color temperature (2856K) Illuminace : 0 ~ 1,960lx

(graph 2. Spectrum of 2856K lamp)

#### Result under 2856K fluorescent lamp

#### B. Spectral response

Spectrum of MC8201 is the below curve by using monochrometer and integrated sphere.

NOTE : Optical characteristics/data are included after full evaluation.

# 2. OPERATION

# 2.1 I<sup>2</sup>C

#### 2.1.1 OVERVIEW

The I<sup>2</sup>C is one of industrial standard serial communication protocols, and which uses 2 bus lines Serial Data Line (SDA) and Serial Clock Line (SCL) to exchange data. Because both SDA and SCL lines are open-drain output, each line needs pull-up resistor. The features are as shown below.

- Compatible with I<sup>2</sup>C interface

- Up to 400KHz data transfer speed

- Support two 7-bit slave address

- Slave operation only

#### 2.1.2 I<sup>2</sup>C BIT TRANSFER

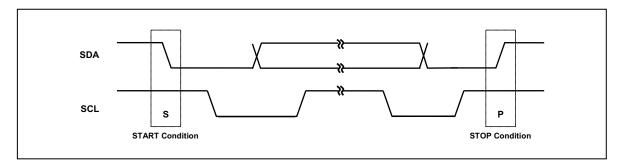

The data on the SDA line must be stable during HIGH period of the clock, SCL. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. The exceptions are START(S), repeated START(Sr) and STOP(P) condition where data line changes when clock line is high.

Figure 2-1 Bit Transfer on the I<sup>2</sup>C-Bus

#### 2.1.3 START / REPEATED START / STOP

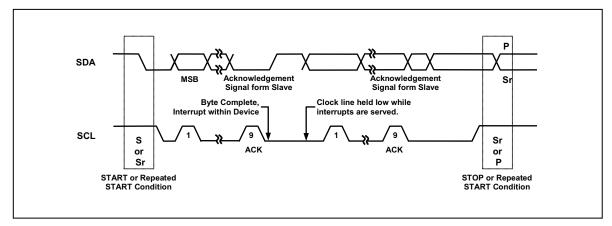

One master can issue a START (S) condition to notice other devices connected to the SCL, SDA lines that it will use the bus. A STOP (P) condition is generated by the master to release the bus lines so that other devices can use it.

A high to low transition on the SDA line while SCL is high defines a START (S) condition.

A low to high transition on the SDA line while SCL is high defines a STOP (P) condition.

START and STOP conditions are always generated by a master. The bus is considered to be busy after START condition. The bus is considered to be free again after STOP condition, ie, the bus is busy between START and STOP condition. If a repeated START condition (Sr) is generated instead of STOP condition, the bus stays busy. So, the START and repeated START conditions are functionally identical.

Figure 2-2 START and STOP Condition

#### 2.1.4 DATA TRANSFER

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unlimited. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first. If a slave can't receive or transmit another complete byte of data until it has performed some other function, it can hold the clock line SCL LOW to force the master into a wait state. Data transfer then continues when the slave is ready for another byte of data and releases clock line SCL.

Figure 2-3 STOP or Repeated START Condition

#### 2.1.5 ACKNOWLEDGE

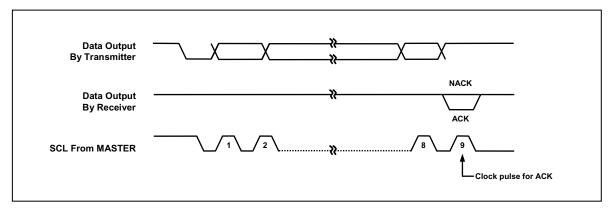

The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse. When a slave is addressed by a master (Address Packet), and if it is unable to receive or transmit because it's performing some real time function, the data line must be left HIGH by the slave. And also, when a slave addressed by a master is unable to receive more data bits, the slave receiver must release the SDA line (Data Packet). The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

If a master receiver is involved in a transfer, it must signal the end of data to the slave transmitter by not generating an acknowledge on the last byte that was clocked out of the slave. The slave transmitter must release the data line to allow the master to generate a STOP or repeated START condition.

Figure 2-4 Acknowledge on the I<sup>2</sup>C-Bus

#### 2.1.6 OPERATION

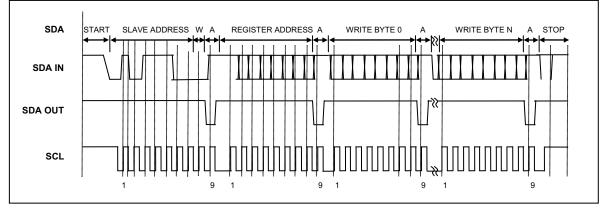

The I<sup>2</sup>C is byte-oriented serial protocol and data transfer between master and this slave device is initiated by a start condition(S) from master. After start condition, the master sends 7-bit slave address and 1-bit read-write control bit. We call these 8-bit data address packet. The next bytes followed by address packet are all data packet unless another start condition is detected before a stop condition.

The 2<sup>nd</sup> byte sent from master after address packet with write direction is interpreted as base register or memory address byte. And this base address is incremented only when master transmits more than 2 bytes after start condition because the 2<sup>nd</sup> byte is register address field.

The MC8201's I<sup>2</sup>C slave address is configured as "1011100<sub>B</sub>" or "0100011<sub>B</sub>" according to the input condition of ADDR pin.

#### 2.1.6.1 WRITE PROTOCOL (MASTER TRANSMITTER)

The master transmits a start condition(S), slave address and Write bit. If the high 7-bits of address packet equal to the device's slave address, the MC8201 acknowledges by pulling down the SDA line at the 9<sup>th</sup> SCL clock period. After address packet and acknowledge bit, the master transmits a data which is used for base address accessing internal memory or register of the device. The master transmits a number of data to be written and the slave always acknowledges for every data received. To finish transfer the master sends a stop condition regardless of the acknowledgement.

The destination address for incoming data byte increments automatically by one data packet. For example, if master transmits 5 data bytes including a base address(=register address in the following figure) byte and the base address is configured as  $00_H$ , the internal address is defined as  $00_H$  for  $1^{st}$  data byte,  $01_H$  for  $2^{nd}$  data byte,  $02_H$  for  $3^{rd}$  data byte and  $03_H$  for  $4^{th}$  data byte. This applies to Read Protocol also.

Figure 2-5 I2C Write Protocol

# 2.1.6.2 READ PROTOCOL (MASTER RECEIVER)

The master transmits a start condition(S), slave address and Write bit. If the high 7-bits of address packet equal to the device's slave address, the MC8201 acknowledges by pulling down the SDA line at the 9th SCL clock period. After address packet and acknowledge bit, the master transmits a data which is used for base address accessing internal memory or register of the device. To initiate read operations, the master sends repeated start condition and slave address with Read bit. After this address packet, the master reads data bytes until it does not acknowledges. Note that to send a stop condition after receiving last data byte, the master must generate a NACK(not acknowledging) on the last data byte received. Like Write Protocol, the read address increases by 1 after every read byte. Note that the transfer direction changes in this protocol.

Figure 2-6 I2C Read Protocol

# **2.2 REGISTERS**

# 2.2.1 OVERVIEW

The MC8201 is controlled and monitored by 23 registers. These registers provide a variety of control functions and can be read to determine results of the ADC conversions.

#### 2.2.2 REGISTER MAP

| Name    | Address         | Dir | Default         | Description                                |

|---------|-----------------|-----|-----------------|--------------------------------------------|

| ADDRSET | -               | W   | -               | Address Set Register                       |

| CONTROL | 00н             | R/W | 00 <sub>H</sub> | Control Register                           |

| INTR    | 01 <sub>н</sub> | R/W | 00н             | Interrupt Control Register                 |

| ATIME   | 02 <sub>H</sub> | R/W | FF <sub>H</sub> | ALS Integration Time Register              |

| PTIME   | 03 <sub>н</sub> | R/W | FF <sub>H</sub> | PS Integration Time Register               |

| WTIME   | 04 <sub>H</sub> | R/W | FF <sub>H</sub> | Wait Time Register                         |

| AILTL   | 05 <sub>н</sub> | R/W | FF <sub>H</sub> | ALS Interrupt Low Threshold Low Register   |

| AILTH   | 06н             | R/W | 03 <sub>Н</sub> | ALS Interrupt Low Threshold High Register  |

| AIHTL   | 07 <sub>Н</sub> | R/W | FF <sub>H</sub> | ALS Interrupt High Threshold Low Register  |

| AIHTH   | 08н             | R/W | BF <sub>H</sub> | ALS Interrupt High Threshold High Register |

| PILTL   | 09 <sub>н</sub> | R/W | FF <sub>H</sub> | PS Interrupt Low Threshold Low Register    |

| PILTH   | 0A <sub>H</sub> | R/W | 03 <sub>Н</sub> | PS Interrupt Low Threshold High Register   |

| PIHTL   | 0B <sub>H</sub> | R/W | FF <sub>H</sub> | PS Interrupt High Threshold Low Register   |

| PIHTH   | 0C <sub>H</sub> | R/W | 03 <sub>H</sub> | PS Interrupt High Threshold High Register  |

| PERSIST | 0D <sub>H</sub> | R/W | 00 <sub>H</sub> | ALS/PS Interrupt Persistence Register      |

| ADATAL  | 0E <sub>H</sub> | R   | FF <sub>H</sub> | ALS ADC Data Low Register                  |

| ADATAH  | 0F <sub>H</sub> | R   | FF <sub>H</sub> | ALS ADC Data High Register                 |

| PDATA0L | 10 <sub>н</sub> | R   | 00н             | PS ADC Data0 Low Register                  |

| PDATA0H | 11 <sub>H</sub> | R   | 00 <sub>H</sub> | PS ADC Data0 High Register                 |

| PDATA1L | 12 <sub>H</sub> | R   | FF <sub>H</sub> | PS ADC Data1 Low Register                  |

| PDATA1H | 13 <sub>н</sub> | R   | 03 <sub>H</sub> | PS ADC Data1 High Register                 |

| AGC0    | 14 <sub>H</sub> | R/W | 00 <sub>H</sub> | ADC Gain control 0 Register                |

| AGC1    | 15 <sub>н</sub> | R/W | 00н             | ADC Gain control 1 Register                |

| PLEDC   | 16 <sub>н</sub> | R/W | 00 <sub>H</sub> | PS LED control Register                    |

#### Table 2-1 Registers of MC8201

**Caution** : Do not access registers addressed between  $17_H$  and  $1F_H$ . Writing to these registers may result in unexpected function.

#### 2.2.3 REGISTER DESCRIPTION

| ADDRSET (Address Set Register) |   |   |       |       |       |       |               |      |  |  |  |

|--------------------------------|---|---|-------|-------|-------|-------|---------------|------|--|--|--|

| 7                              | 6 | 5 | 4     | 3     | 2     | 1     | 0             |      |  |  |  |

| -                              | - | - | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0         |      |  |  |  |

| -                              | - | - | RW    | RW    | RW    | RW    | RW            |      |  |  |  |

|                                |   |   |       |       |       |       | Initial value | . 00 |  |  |  |

Initial value : 00<sub>H</sub>

Base address for subsequent register access. When the I2C master initiates a write protocol with start bit and slave address transfer, the second byte is used to configure register address.

#### **CONTROL (Control Register)**

ADDR[4:0]

**00**<sub>H</sub>

March 2012 REV1.5

| 7       | 6       | 5       | 4                                                   | 3                                     | 2                                | 1                           | 0                                            |  |

|---------|---------|---------|-----------------------------------------------------|---------------------------------------|----------------------------------|-----------------------------|----------------------------------------------|--|

| ONESHOT | SOFTRST | PROXSEL | IRSEL                                               | PSTYPE                                | PAEN                             | AAEN                        | POWER                                        |  |

| RW      | RW      | RW      | RW                                                  | RW                                    | RW                               | RW                          | RW                                           |  |

|         |         |         |                                                     |                                       |                                  |                             | Initial value :                              |  |

|         | 0       | NESHOT  | Stops ADC                                           | integration on                        | completion of                    | one integratio              | on cycle.                                    |  |

|         |         |         | 0 Cc                                                | ntinuous opera                        | ation.                           |                             |                                              |  |

|         |         |         | au<br>reg                                           |                                       | o and also the                   | PAEN/AAEN                   | DC will<br>bits in CONTR<br>n, re-assert PAI |  |

|         | S       | OFTRST  | Soft reset.                                         | This bit is auto-                     | -cleared.                        |                             |                                              |  |

|         |         |         | 0 No                                                | operation                             |                                  |                             |                                              |  |

|         |         |         | 1 Re                                                | eset internal reg                     | gisters                          |                             |                                              |  |

|         | Ρ       | ROXSEL  | The INT pir                                         | n operates as p                       | proximity detection              | tion output m               | ode.                                         |  |

|         |         |         | 0 IN                                                | T pin is used as                      | s PS or ALS in                   | terrupt pin                 |                                              |  |

|         |         |         | 1 INT pin is used as proxmity detection output mode |                                       |                                  |                             |                                              |  |

|         | I       | RSEL    | Selects the                                         | PDATA0H/L re                          | ead data.                        |                             |                                              |  |

|         |         |         | 0 PE<br>AE                                          | OATA0 holds the<br>OC count from F    | e value obtain<br>PS(LED on) Al  | ed by subtrac<br>DC count.  | ting IR(LED off                              |  |

|         |         |         |                                                     | OATA0 holds the<br>OC count. Set th   |                                  | •                           | m IR(LED off)                                |  |

|         | P       | STYPE   | PS mode s                                           | elect                                 |                                  |                             |                                              |  |

|         |         |         | 0 PS                                                | TYPE 0 mode                           | •                                |                             |                                              |  |

|         |         |         | 1 PS                                                | STYPE 1 mode                          | •                                |                             |                                              |  |

|         | P       | AEN     | PS ADC Er<br>integration.                           | nable. This bit e<br>This bit is effe | enables the PS<br>ctive only whe | S ADC channe<br>n POWER bit | el to begin<br>is set to '1'. <sup>NO</sup>  |  |

|         |         |         |                                                     | sable Photo Die                       |                                  |                             |                                              |  |

|         |         |         | 1 En                                                | able Photo Dic                        | de and PS AD                     | )C.                         |                                              |  |

|         | A       | AEN     | ALS ADC E integration.                              | Enable. This bit<br>This bit is effe  | enables the A<br>ctive only whe  | LS ADC char<br>n POWER bit  | nel to begin<br>is set to '1'. <sup>NO</sup> |  |

|         |         |         | 0 Dis                                               | sable Photo Die                       | ode and ALS A                    | DC.                         |                                              |  |

|         |         |         | 1 En                                                | able Photo Dic                        | de and ALS A                     | DC.                         |                                              |  |

|         | P       | OWER    | Power On.                                           | Enables intern                        | al RC oscillato                  | or(Typically 70             | 0KHz)                                        |  |

|         |         |         | 0 Tu                                                | rns off the MC8                       | 3201.                            |                             |                                              |  |

|         |         |         | 1 Tu                                                | rns on the MC8                        | 3201.                            |                             |                                              |  |

|         |         |         |                                                     |                                       |                                  |                             |                                              |  |

<sup>NOTE</sup> The real PAEN and AAEN bits are updated after internal oscillator is enabled. So reading CONTROL register will return "---- --00<sub>B</sub>" when writing '1' to these bits while POWER bit is disabled or enabling PAEN, AAEN and POWER bits simultaneously.

By enabling PAEN or AAEN bits individually, MC8201 operates as PS only mode, ALS only mode or PS-ALS alternating mode.

| INTR (Interrupt Control Register) |        |         |       |       |         |        |               |                   |  |  |  |

|-----------------------------------|--------|---------|-------|-------|---------|--------|---------------|-------------------|--|--|--|

| 7                                 | 6      | 5       | 4     | 3     | 2       | 1      | 0             |                   |  |  |  |

| PSX4EN                            | ALC_IR | PROXDET | PINTF | AINTF | INTEDGE | PINTEN | AINTEN        |                   |  |  |  |

| RW                                | RW     | R       | R     | R     | RW      | RW     | RW            |                   |  |  |  |

|                                   |        |         |       |       |         |        | Initial value | : 40 <sub>H</sub> |  |  |  |

PSX4EN

Enable proximity sensing4 times in row.

|         | 0                                                                                                               | Proximity sensing is performed once in a ps time                                                                                                                                                             |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | 1                                                                                                               | Proximity sensing is performed 4 times in a ps time                                                                                                                                                          |  |  |  |  |

| ALC_IR  | Enable                                                                                                          | ALC function                                                                                                                                                                                                 |  |  |  |  |

|         | 0                                                                                                               | Disable ALC                                                                                                                                                                                                  |  |  |  |  |

|         | 1                                                                                                               | Enable ALC (default)                                                                                                                                                                                         |  |  |  |  |

| PROXDET | PIHT, tł                                                                                                        | ty detection result. When PS ADC counter value is greater than his flag is set. When PS ADC counter value is less than PILT, this cleared. For proper detection result, set PPER greater than $01_{\rm H}$ . |  |  |  |  |

|         | 0                                                                                                               | Non-detect (Object is far)                                                                                                                                                                                   |  |  |  |  |

|         | 1                                                                                                               | Detect (Object is near)                                                                                                                                                                                      |  |  |  |  |

| PINTF   |                                                                                                                 | rrupt Flag. Indicates that the device is asserting an interrupt.<br>0 to this bit clears PINTF.                                                                                                              |  |  |  |  |

|         | 0                                                                                                               | No Interrupt or interrupt cleared.                                                                                                                                                                           |  |  |  |  |

|         | 1                                                                                                               | PS interrupt requested.                                                                                                                                                                                      |  |  |  |  |

| AINTF   | ALS Interrupt Flag. Indicates that the device is asserting an interrupt.<br>Writing 0 to this bit clears AINTF. |                                                                                                                                                                                                              |  |  |  |  |

|         | 0                                                                                                               | No Interrupt or interrupt cleared.                                                                                                                                                                           |  |  |  |  |

|         | 1                                                                                                               | ALS interrupt requested.                                                                                                                                                                                     |  |  |  |  |

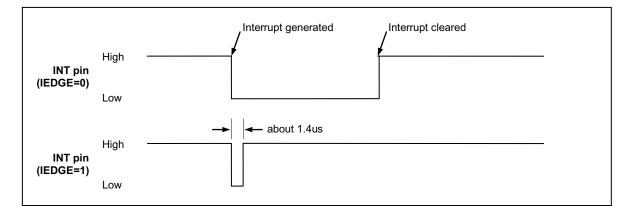

| INTEDGE |                                                                                                                 | ot signal is triggered as pulse type at rising edge of internal pically 1.4us period. The host needs not to clear interrupt.                                                                                 |  |  |  |  |

|         | 0                                                                                                               | Level interrupt                                                                                                                                                                                              |  |  |  |  |

|         | 1                                                                                                               | Edge interrupt                                                                                                                                                                                               |  |  |  |  |

| PINTEN  | Enables                                                                                                         | s PS Interrupt generation.                                                                                                                                                                                   |  |  |  |  |

|         | 0                                                                                                               | PS Interrupt output is disabled.                                                                                                                                                                             |  |  |  |  |

|         | 1                                                                                                               | PS Interrupt occurs on INT pin.                                                                                                                                                                              |  |  |  |  |

| AINTEN  | Enables                                                                                                         | s ALS Interrupt generation.                                                                                                                                                                                  |  |  |  |  |

|         | 0                                                                                                               | ALS Interrupt output is disabled.                                                                                                                                                                            |  |  |  |  |

|         | 1                                                                                                               | ALS Interrupt occurs on INT pin.                                                                                                                                                                             |  |  |  |  |

# ATIME (ALS Integration Time Register)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0               |        |

|--------|--------|--------|--------|--------|--------|--------|-----------------|--------|

| ATIME7 | ATIME6 | ATIME5 | ATIME4 | ATIME3 | ATIME2 | ATIME2 | ATIME1          |        |

| RW              |        |

|        |        |        |        |        |        |        | Initial value : | $FF_H$ |

| ATIME[7:0] | ALS Integration | on Time. Specifies the integration time in 5.0 ms intervals.<br>on time = 5 ms x ATIME[7:0]<br>n ALS integration time is about 1275.0 ms (11111111 <sub>B</sub> ). |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 00000000        | Prohibited. Writing "00 <sub>H</sub> " has no effect.                                                                                                              |

|            | 00000001        | 5.0 ms                                                                                                                                                             |

|            | 00000010        | 10.0 ms                                                                                                                                                            |

|            | 00001010        | 50.0 ms                                                                                                                                                            |

|            | 00010100        | 100.0 ms                                                                                                                                                           |

|            | 00101000        | 200.0 ms                                                                                                                                                           |

|            | 01010000        | 400.0 ms                                                                                                                                                           |

|            | 11111111        | 1275.0 ms                                                                                                                                                          |

# PTIME (PS Integration Time Register)

**02**<sub>H</sub>

| 7      | 6      | 5         | 4              | 3                               | 2                                                            | 1                      | 0                  |

|--------|--------|-----------|----------------|---------------------------------|--------------------------------------------------------------|------------------------|--------------------|

| PTIME7 | PTIME6 | PTIME5    | PTIME4         | PTIME3                          | PTIME2                                                       | PTIME2                 | PTIME1             |

| RW     | RW     | RW        | RW             | RW                              | RW                                                           | RW                     | RW                 |

|        |        |           |                |                                 |                                                              |                        | Initial value : FF |

|        | Ρ.     | FIME[7:0] | PS Integration | on time = 185<br>ım PS integrat | us x PTIME[<br>ion time is abo<br>Writing "00 <sub>H</sub> " | 7:0]<br>out 47.2 ms (1 | ,                  |

#### WTIME (Wait Time Register)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| WTIME7 | WTIME6 | WTIME5 | WTIME4 | WTIME3 | WTIME2 | WTIME2 | WTIME1 |

| RW     |

Initial value : FFH

**04**<sub>H</sub>

| WTIME[7:0] | operations in<br>Wait time = 5 | becifies the wait time between continuous ALS or PS<br>5.38 ms intervals.<br>.38 ms x WTIME[7:0]<br>n wait time is about 1371.9 ms (11111111 <sub>B</sub> ). |

|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 00000000                       | No wait                                                                                                                                                      |

|            | 0000001                        | 5.38 ms                                                                                                                                                      |

|            | 00000010                       | 10.76 ms                                                                                                                                                     |

|            | 00001010                       | 53.8 ms                                                                                                                                                      |

|            | 00010100                       | 107.6 ms                                                                                                                                                     |

|            | 00101000                       | 215.2 ms                                                                                                                                                     |

|            | 01111000                       | 645.6 ms                                                                                                                                                     |

|            | 11111111                       | 1371.9 ms                                                                                                                                                    |

|            |                                |                                                                                                                                                              |

The WTIME is used to reduce average power consumption, because the PS and ALS ADC stop integrating during wait time period.

When PSEN=1 and ALSEN=0, the internal operating state machine repeats PS and WAIT state continuously.

When ALSEN=1 and PSEN=0, the internal operating state machine repeats ALS and WAIT state continuously.

When PSEN=1 and ALSEN=1, the internal operating mode is as follows : PS—ALS—WAIT—PS—ALS—WAIT—PS—ALS—WAIT...

<sup>NOTE</sup> Although setting a larger wait time contributes to reduce average consumption current, it makes update period and response time longer.

#### AILTL (ALS Interrupt Low Threshold Low Register)

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0                 |     |

|--------|--------|--------|--------|--------|--------|--------|-------------------|-----|

| AILTL7 | AILTL6 | AILTL5 | AILTL4 | AILTL3 | AILTL2 | AILTL1 | AILTL0            |     |

| RW                |     |

|        |        |        |        |        |        |        | Initial value : F | ۶FH |

AILTL[7:0] ALS ADC channel interrupt low threshold low register.

| 7                                              | 6                                                                    | 5                                                                          | 4                                                                   | 3                                                                       | 2                                                   | 1                                                  | 0                                                                   |

|------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------|

| AILTH7                                         | AILTH6                                                               | AILTH5                                                                     | AILTH4                                                              | AILTH3                                                                  | AILTH2                                              | AILTH1                                             | AILTH0                                                              |

| RW                                             | RW                                                                   | RW                                                                         | RW                                                                  | RW                                                                      | RW                                                  | RW                                                 | RW                                                                  |

|                                                |                                                                      |                                                                            |                                                                     |                                                                         |                                                     |                                                    | Initial value                                                       |

|                                                | Α                                                                    | ILTH[7:0]                                                                  | ALS ADC c                                                           | hannel interru                                                          | pt low thresho                                      | old high regist                                    | er.                                                                 |

| AHTL (AL                                       | S Interrupt                                                          | High Threst                                                                | nold Low Reg                                                        | gister)                                                                 |                                                     |                                                    |                                                                     |

| 7                                              | 6                                                                    | 5                                                                          | 4                                                                   | 3                                                                       | 2                                                   | 1                                                  | 0                                                                   |

| AIHTTL7                                        | AIHTL6                                                               | AIHTL5                                                                     | AIHTL4                                                              | AIHTL3                                                                  | AIHTL2                                              | AIHTTL1                                            | AIHTL0                                                              |

| RW                                             | RW                                                                   | RW                                                                         | RW                                                                  | RW                                                                      | RW                                                  | RW                                                 | RW                                                                  |

|                                                |                                                                      |                                                                            |                                                                     |                                                                         |                                                     |                                                    | Initial value                                                       |

|                                                | A 1                                                                  | 10117.01                                                                   | ALS ADC c                                                           | hannel interru                                                          | pt high thresh                                      | old low reaist                                     | er.                                                                 |

|                                                |                                                                      | IHTL[7:0]                                                                  |                                                                     |                                                                         |                                                     |                                                    |                                                                     |

| JHTH (AL                                       |                                                                      |                                                                            | nold High Re                                                        |                                                                         |                                                     |                                                    |                                                                     |

| NHTH (AL<br>7                                  |                                                                      |                                                                            |                                                                     |                                                                         | 2                                                   | 1                                                  |                                                                     |

|                                                | S Interrupt                                                          | High Thresl                                                                | nold High Re                                                        | egister)                                                                |                                                     | -                                                  |                                                                     |

| 7                                              | S Interrupt                                                          | High Thresl                                                                | nold High Re                                                        | egister)<br>3                                                           | 2                                                   | 1                                                  | 0                                                                   |

| 7<br>AIHTTH7                                   | S Interrupt<br>6<br>AIHTTH6                                          | High Thres<br>5<br>AHTTH5                                                  | nold High Re<br>4<br>AIHTH4                                         | egister)<br>3<br>AlHTH3                                                 | <b>2</b><br>AIHTH2                                  | 1<br>AHTTH1                                        | 0<br>AIHTHO                                                         |

| 7<br>AIHTTH7                                   | S Interrupt<br>6<br>AIHTH6<br>RW                                     | High Thres<br>5<br>AHTTH5                                                  | nold High Re<br>4<br>AIHTH4<br>RW                                   | e <b>gister)</b><br>3<br>AlHTH3<br>RW                                   | <b>2</b><br>AIHTH2                                  | 1<br>AIHTH1<br>RW                                  | 0<br>AIHTH0<br>RWV<br>Initial value                                 |

| 7<br>AIHTTH7<br>RW                             | S Interrupt<br>6<br>AIHTH6<br>RW<br>A                                | High Thresi<br>5<br>AHTH5<br>RW<br>IHTH[7:0]                               | AIHTTH4<br>AIHTTH4<br>RW<br>ALS ADC c                               | e <b>gister)</b><br>3<br>AIHTH3<br>RW<br>hannel interru                 | <b>2</b><br>AIHTH2<br>RW                            | 1<br>AIHTH1<br>RW                                  | 0<br>AIHTH0<br>RW<br>Initial value<br>ster.                         |

| 7<br>AIHTTH7<br>RW                             | S Interrupt<br>6<br>AIHTH6<br>RW<br>A                                | High Thresi<br>5<br>AHTH5<br>RW<br>IHTH[7:0]                               | nold High Re<br>4<br>AIHTH4<br>RW                                   | e <b>gister)</b><br>3<br>AIHTH3<br>RW<br>hannel interru                 | <b>2</b><br>AIHTH2<br>RW                            | 1<br>AIHTH1<br>RW                                  | 0<br>AIHTH0<br>RWV<br>Initial value                                 |

| 7<br>AIHTTH7<br>RW                             | S Interrupt<br>6<br>AIHTH6<br>RW<br>A                                | High Thresi<br>5<br>AHTH5<br>RW<br>IHTH[7:0]                               | AIHTTH4<br>AIHTTH4<br>RW<br>ALS ADC c                               | e <b>gister)</b><br>3<br>AIHTH3<br>RW<br>hannel interru                 | <b>2</b><br>AIHTH2<br>RW                            | 1<br>AIHTH1<br>RW                                  | 0<br>AIHTH0<br>RW<br>Initial value<br>ster.                         |

| 7<br>AHTH7<br>RW                               | S Interrupt<br>6<br>AIHTH6<br>RW<br>A<br>Interrupt Lo                | High Thres<br>5<br>AIHTH5<br>RW<br>IHTH[7:0]<br>ow Threshol                | AIHTTH4<br>AIHTTH4<br>RW<br>ALS ADC c                               | egister)<br>3<br>AIHTH3<br>RW<br>hannel interru                         | 2<br>AIHTTH2<br>RW<br>apt high thresh               | 1<br>AHTH1<br>RW<br>old high regis                 | 0<br>AIHTHO<br>RW<br>Initial value<br>ster.                         |

| 7<br>AHTTH7<br>RW<br>PILTL (PS<br>7            | S Interrupt<br>6<br>AIHTH6<br>RW<br>A<br>Interrupt Lo<br>6           | High Thres<br>5<br>AIHTH5<br>RW<br>IHTH[7:0]<br>5                          | AIHTH4<br>AIHTH4<br>RW<br>ALS ADC c<br>d Low Regis                  | egister)<br>3<br>AIHTH3<br>RW<br>hannel interru<br>ster)<br>3           | 2<br>AIHTTH2<br>RW<br>upt high thresh               | 1<br>AIHTTH1<br>RW<br>old high regis               | 0<br>AIHTTH0<br>RWV<br>Initial value<br>ster.<br>0<br>PILTL0<br>RWV |

| 7<br>AIHTTH7<br>RW<br>PILTL (PS<br>7<br>PILTL7 | S Interrupt<br>6<br>AIHTH6<br>RW<br>A<br>Interrupt Lo<br>6<br>PILTL6 | High Thres<br>5<br>AIHTH5<br>RW<br>IHTH[7:0]<br>ow Threshol<br>5<br>PILTL5 | AIHTTH4<br>AIHTTH4<br>RW<br>ALS ADC c<br>d Low Regis<br>4<br>PILTL4 | egister)<br>3<br>AIHTH3<br>RW<br>hannel interru<br>ster)<br>3<br>PILTL3 | 2<br>AIHTTH2<br>RW<br>pt high thresh<br>2<br>PILTL2 | 1<br>AHTTH1<br>RW<br>old high regis<br>1<br>PILTL1 | 0<br>AIHTTHO<br>RWV<br>Initial value<br>ster.<br>0                  |

| 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0               |                   |

|---|---|---|---|---|---|--------|-----------------|-------------------|

| - | - | - | - | - | - | PILTH1 | PILTH0          |                   |

| - | - | - | - | - | - | RW     | RW              |                   |

|   |   |   |   |   |   |        | Initial value : | : 03 <sub>H</sub> |

PILTH (PS Interrupt Low Threshold High Register)

**PILTH[1:0]** PS ADC channel interrupt low threshold high register.

**NBOV**

**0A**<sub>H</sub>

23

| PIHTL (PS | Interrupt Hi | gh Thresho  | ld Low Regi | ister)         |                |                 |               | 0 <b>B</b> H |

|-----------|--------------|-------------|-------------|----------------|----------------|-----------------|---------------|--------------|

| 7         | 6            | 5           | 4           | 3              | 2              | 1               | 0             |              |

| PIHTL7    | PIHTL6       | PIHTL5      | PIHTL4      | PIHTL3         | PIHTL2         | PIHTL1          | PIHTL0        |              |

| RW        | RW           | RW          | RW          | RW             | RW             | RW              | RW            |              |

|           |              |             |             |                |                |                 | Initial value | $FF_{H}$     |

|           | P            | [HTL[7:0]   | PS ADC ch   | annel interrup | t high thresho | ld low register |               |              |

| PIHTH (PS | Interrupt H  | igh Thresho | ld High Reg | jister)        |                |                 | (             | 0 <b>С</b> н |

| 7         | 6            | 5           | 4           | 3              | 2              | 1               | 0             | -            |

| - | - | - | - | - | - | PIHTTH1 | PIHTH0          |

|---|---|---|---|---|---|---------|-----------------|

| - | - | - | - | - | - | RW      | RW              |

|   |   |   |   |   |   |         | Initial value : |

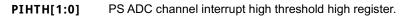

The interrupt threshold registers store the values to be used as the high and low trigger points for the adc data registers. If the value of adc data register crosses below or equal to the low threshold specified, an interrupt can be asserted on the interrupt pin. Likewise, if the result from ADC conversion crosses above the high threshold specified, an interrupt can be asserted on the interrupt pin. Note these high and low threshold registers are 16-bit wide for ambient light sensing, 10/8-bit wide for proximity sensing.

When the device is in ALS mode, the concatenated AILTH and AILTL is used as interrupt low threshold(=AILT) and the concatenated AIHTH and AIHTL is used as interrupt high threshold(=AIHT).

Similarly, when the device is in PS mode, the concatenated PILTH and PILTL is used as interrupt low threshold(=PILT) and the concatenated PIHTH and PIHTL is used as interrupt high threshold(=PIHT). When PROXSEL bit is set, the proximity sensing result is output through the INT pin. The INT pin goes LOW when the PS ADC result is greater than or equal to PIHT and goes HIGH when the PS ADC result is less than PILT. So for proper operation with PROXSEL bit set to 1, the PILT should be non-zero value, otherwise the INT pin will be held LOW unless PINTF is cleared by host command.

Caution : Make sure that the PIHTH register and PILTH register are loaded with "00" when PS resolution is set to 8-bit for proper operation.

| ```   | •     |          | 0 /           |                              |                                  |                 |                 | ••              |

|-------|-------|----------|---------------|------------------------------|----------------------------------|-----------------|-----------------|-----------------|

| 7     | 6     | 5        | 4             | 3                            | 2                                | 1               | 0               |                 |

| PPER3 | PPER2 | PPER1    | PPER0         | APER3                        | APER2                            | APER1           | APER0           |                 |

| RW    | RW    | RW       | RW            | RW                           | RW                               | RW              | RW              |                 |

|       |       |          |               |                              |                                  |                 | Initial value : | 00 <sub>H</sub> |

|       | P     | PER[3:0] | request to he | ost chip.<br>KSEL bit is set | These bit field<br>, PPER should |                 |                 | upt             |

|       |       |          | 0000          | Every PS of                  | cycle generate                   | s an interrupt. |                 |                 |

|       |       |          | 0001          | 1 consecut                   | tive PS ADC va                   | alue out of rar | nge.            |                 |

|       |       |          | 0010          | 2 consecut                   | tive PS ADC va                   | alue out of rar | nge.            |                 |

|       |       |          |               |                              |                                  |                 |                 |                 |

|       |       |          | 1111          | 15 consecu                   | utive PS ADC                     | value out of ra | ange.           |                 |

|       |       |          |               |                              |                                  |                 |                 |                 |

24

**PERSIST (Interrupt Persistence Register)**

0D<sub>H</sub>

0E<sub>н</sub>

| APER[3:0] |      | persistence. These bit field control the rate of ALS est to host chip. |

|-----------|------|------------------------------------------------------------------------|

|           | 0000 | Every ALS cycle generates an interrupt.                                |

|           | 0001 | 1 consecutive ALS ADC value out of range.                              |

|           | 0010 | 2 consecutive ALS ADC value out of range.                              |

|           |      |                                                                        |

|           | 1111 | 15 consecutive ALS ADC value out of range.                             |

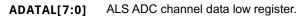

#### ADATAL (ALS ADC Data Low Register)

March 2012 REV1.5

| 7       | 6       | 5       | 4       | 3       | 2       | 1       | 0               |        |

|---------|---------|---------|---------|---------|---------|---------|-----------------|--------|

| ADATAL7 | ADATAL6 | ADATAL5 | ADATAL4 | ADATAL3 | ADATAL2 | ADATAL1 | ADATAL0         |        |

| R       | R       | R       | R       | R       | R       | R       | R               |        |

|         |         |         |         |         |         |         | Initial value : | $FF_H$ |

The ALS ADC included in MC8201 is of 16-bit resolution, and the integrated values appear on two registers ADATAL and ADATAH respectively. All ALS ADC data registers are read-only.

25

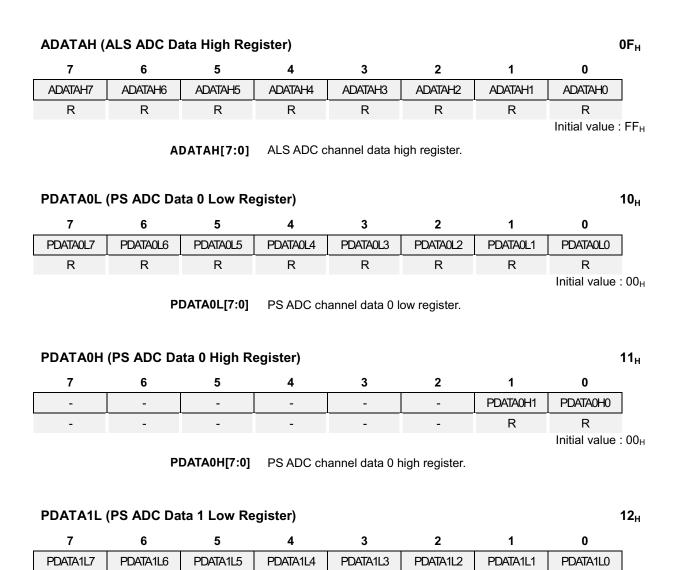

PDATA1L[7:0] PS ADC channel data 1 low register.

| PDATA1H | (PS ADC Da | ata 1 High R | egister) |   |   |          |               | 13 <sub>н</sub>   |

|---------|------------|--------------|----------|---|---|----------|---------------|-------------------|

| 7       | 6          | 5            | 4        | 3 | 2 | 1        | 0             |                   |

| -       | -          | -            | -        | - | - | PDATA1H1 | PDATA1H0      |                   |

| -       | -          | -            | -        | - | - | R        | R             |                   |

|         |            |              |          |   |   |          | Initial value | : 03 <sub>н</sub> |

The PS ADC included in MC8201 is of 10/8-bit resolution, and the integrated values appear on two registers PDATA0(PDATA0H:PDATA0L) and PDATA1(PDATA1H:PDATA1L) respectively. All PS ADC data registers are read-only.

The PDATA0H and PDATA0L registers are updated 1 time during 1 PS cycle and the loading data is selected by IRSEL bit in CONTROL register. If IRSEL bit is '0', the result of subtracting IR(LED off) ADC count from PS(LED on) ADC count is loaded into PDATA0. If IRSEL bit is '1', the IR(LED off) ADC count is directly transferred into PDATA0.

Caution : The PDATA1L/H registers are used for test purpose.

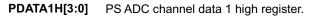

| AGC0 (AD | C Gain Con | trol 0 Regist | ter)                    |                |               |                |               | 14 <sub>н</sub>   |

|----------|------------|---------------|-------------------------|----------------|---------------|----------------|---------------|-------------------|

| 7        | 6          | 5             | 4                       | 3              | 2             | 1              | 0             |                   |

| PS_RES   | -          | -             | -                       | -              | -             | VGAIN1         | VGAIN0        | 7                 |

| RW       | -          | -             | -                       | -              | -             | RW             | RW            |                   |

|          |            |               |                         |                |               |                | Initial value | : 03 <sub>H</sub> |

|          | Р          | S_RES         | Select PS re            | esolution      |               |                |               |                   |

|          |            |               | 0 10-k                  | oit resolution |               |                |               |                   |

|          |            |               | 1 8-bi                  | t resolution   |               |                |               |                   |

|          | V          | GAIN[1:0]     | ADC Voltage operations. | e Gain Contro  | I. This VGAIN | affects on bot | h ALS and P   | S                 |

|          |            |               | 00 x2.                  | 0              |               |                |               |                   |

|          |            |               | 01 x1.4                 | 4              |               |                |               |                   |

|          |            |               | 10 x1.                  | 2              |               |                |               |                   |

|          |            |               | 11 x1.                  | 0              |               |                |               |                   |

Caution : Do not alter AGC0[7:2]. Writing non-zero value to these bits may result in mal-function.

|            | 0001                                 |                                                |                     | x0.89                            |

|------------|--------------------------------------|------------------------------------------------|---------------------|----------------------------------|

|            |                                      |                                                |                     |                                  |

|            |                                      |                                                |                     |                                  |