## **USB 1.1 to IrDA Controller**

### Features

- USB Specification 1.1 Compliant.

- Supports all USB Standard Commands.

- Full Compliance to IrDA 1.4

- WHQL Certified

- Low-Power CMOS Design

- Powered from USB port

- Single 12 MHz Crystal

- IrDA Data Rates from 2.4 Kbps to 115.2 Kbps in SIR mode

- Supports MIR (Medium IR) at 1.152 Mbps

- Supports FIR (Fast IR) mode with Data Rate of 4 Mbps

- Uses Standard IrDA Transceivers

- LED Driver capable of 650 mA @ 5V, 25% Duty Cycle

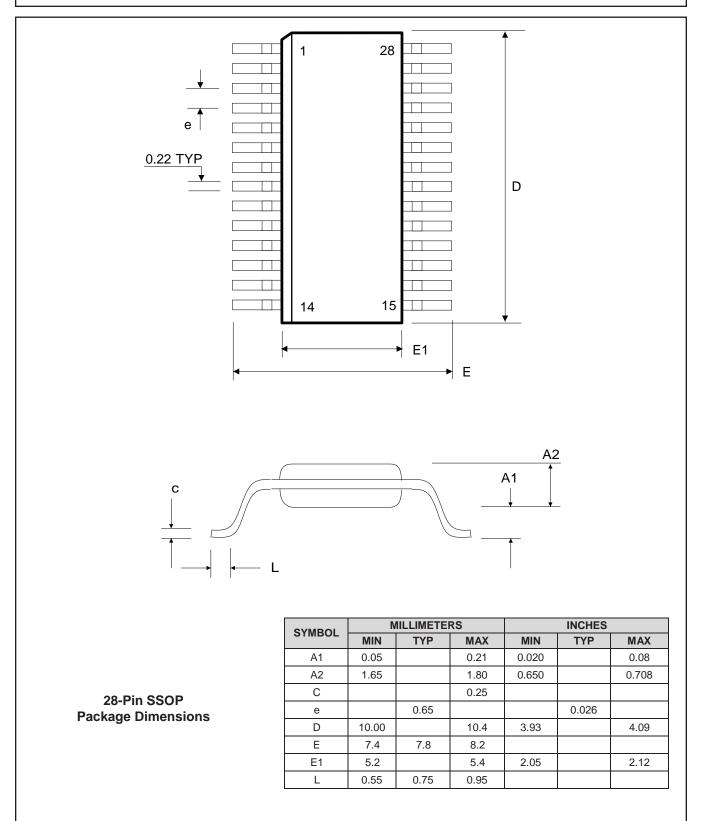

- Low-Profile 28-Pin SSOP Package

### Applications

- High-Speed IrDA Communications

- Cell Phone Interface Cable

### **Application Note**

• AN-7780

### **Evaluation Board**

MCS7780-EVB

"IrReady Qualified" in Demo Adapters Customer boards require IrDA qualification

RoHS

### **General Description**

The MCS7780 controller provides bridging between the Universal Serial Bus (USB) input and an IrDA wireless data communication port. This device contains all the necessary logic to communicate with the host computer via the USB Bus.

The MCS7780 operates in Bus-Powered mode, and uses a reduced frequency (12MHz) crystal oscillator. This combination of features allows significant cost savings in system design along with straight forward implementation of IrDA port functionality into PC peripherals using the host's USB port.

| Ordering Information              |  |  |  |  |  |  |

|-----------------------------------|--|--|--|--|--|--|

| Commercial Grade (0° C to +70° C) |  |  |  |  |  |  |

MCS7780CS-GR 2

80CS-GR 28-SSOP

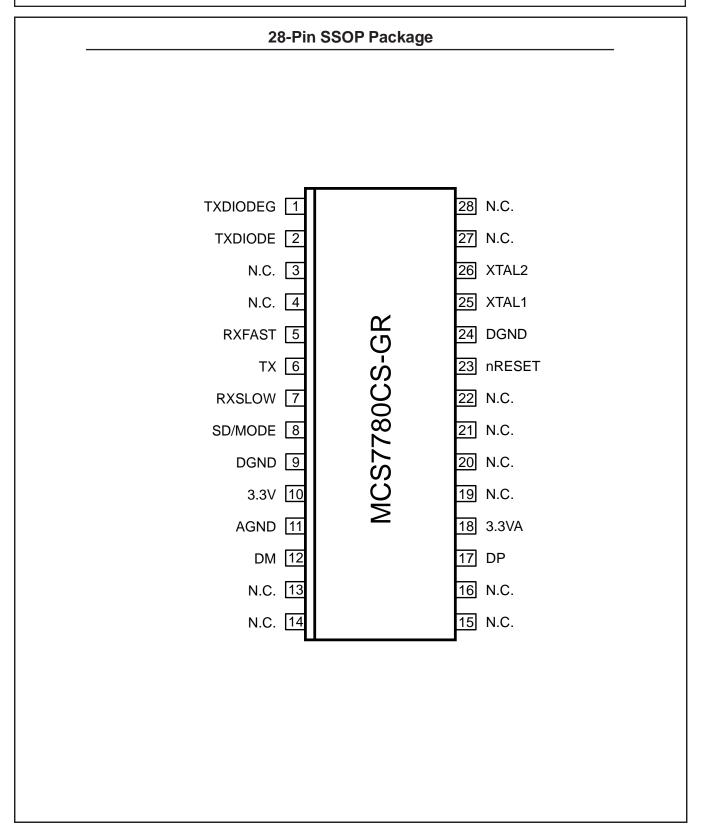

#### **Pin Descriptions** Description **Pin Name** Pin Туре **TXDIODEG** 1 PWR Optional LED Driver Output GND TXDIODE 2 0 **Optional Transmit LED Driver Output** RXFAST 5 I Receive Data from IR module (Fast) ТΧ 6 0 Transmit Data output to IR module **RXSLOW** 7 L Receive Data from IR module (Slow) SD/MODE 0 8 Mode Control to IR module DM 12 I/O USB Interface differential Data Negative DP 17 I/O USB Interface differential Data Positive nRESET 23 I Master Reset, (active low) XTAL1 25 L 12 MHz Crystal/Clock Input XTAL2 26 0 12 MHz Crystal/Clock Output 3.3VA PWR 18 **USB** Transceiver Power Supply 3.3V PWR 10 **Digital Power Supply** AGND 11 PWR USB Transceiver Power Supply Ground DGND 9,24 PWR **Digital Power Supply Ground**

## **Functional Description**

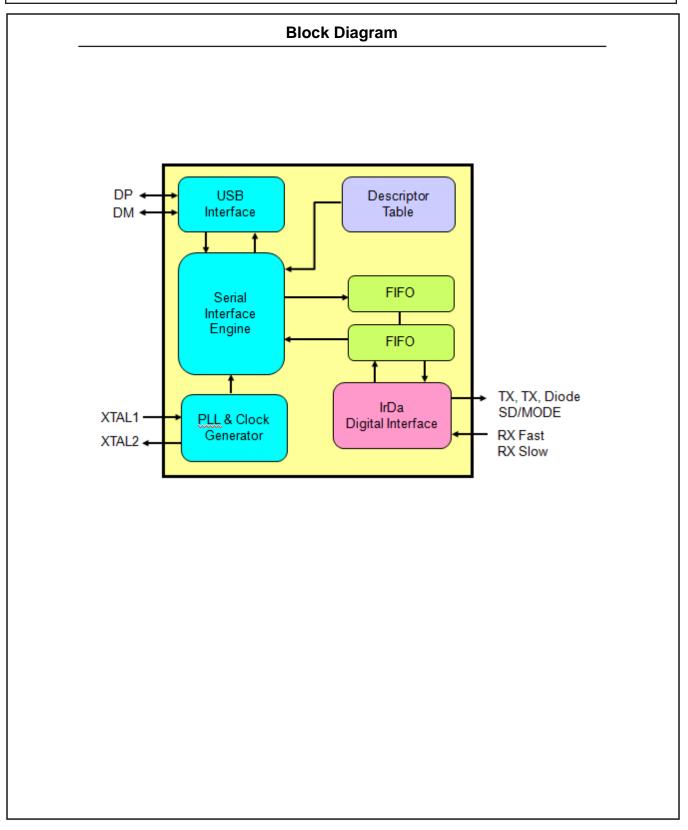

The MCS7780 consists of two major functional blocks, the USB controller, and the digital IR transceiver. The USB controller provides Control, Bulk-In, and Bulk-Out endpoints to the USB host. The digital IR transceiver consists of transmit and receive interfaces that connect to an analog IR front end.

This USB/IrDA Bridge Controller has full interface capability to connect between a USB Bus, and an IrDA compatible infrared transceiver device.

## **USB** Interface

The USB Device Controller implements a USB protocol engine. It has one configuration with a single interface. Two Bulk endpoints with maximum packet size of 64 Bytes are used for data transfers. The MCS7780 uses Vendor Specific commands for IR configuration and control. Two vendor specific requests ("Write Word" & "Read Word") are defined for this purpose. The vendor specific requests are piped through the Control endpoint.

"Write Word" is a 2 phase transaction which can be used to write a single 16-bit register. The setup phase of this command supplies both the index and data value to be written into the register. There is no data phase in this transfer.

The "Read Word" request is used to read the register contents of the MCS7780. It allows reading one 16bit register at a time. The setup phase specifies the register address to be read and the data is returned in the data phase.

## **Digital IR Transceiver**

The Digital IR Transceiver is responsible for driving the transmit diode and receiving the digital input from an analog IR front end. The primary components are the transmit modulator, the receive demodulator, the FIFO, the analog transmit section, and the register array.

By programming the registers in the register array, the device's operation is determined. Various registers are used to specify operations such as the modulation scheme, the Baud rate, the current frame size in the FIFO, the RX input selection, etc.

In steady state transmit operation, the USB controller is filling the FIFO with data while the Digital IR Transceiver is emptying it via the transmit modulator. In steady state receive operation, the USB controller is emptying the FIFO while the RX demodulator is filling the FIFO.

## **IR FRAMING**

Framing involves adding wrappers around the payload received from NDIS to make a valid IR frame. MCS7780 uses a custom framing style to achieve low gate count. The hardware and software together play a role in making of SIR, MIR, and FIR frames.

## Mode Register: offset 0x00

| Name    | Bit     | Access   | Default | Description                                                                                                                                                                                                              |  |

|---------|---------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FIR     | 0 *     | R/W      | 0       | <ul><li>1 = Puts the device in Fast Infrared mode (4MHz).</li><li>0 = Device uses SIR/MIR mode based on Baud Rate register.</li></ul>                                                                                    |  |

| SIR     | 1 *     | R/W      | 0       | 1 = The SIR pulse width of 1.6 uS is used.<br>0 = The SIR pulse used is 3/16th of bit time.                                                                                                                              |  |

| BBTG    | 2       | R/W      | 1       | 1 = Enables back to back transmission with no inter packet gap.<br>Invalid in SIR mode.                                                                                                                                  |  |

| ASK     | 3 *     | Reserved |         | Reserved                                                                                                                                                                                                                 |  |

| PARITY  | 4 *     | R/W      | 0       | 1 = Odd parity to be used by ASK.<br>0 = Even parity is used                                                                                                                                                             |  |

| RATE    | [7:5] * | R/W      | 1       | Baud Rate selector. (See Table Below)                                                                                                                                                                                    |  |

| PLLPWD  | 8       | R/W      | 1       | 1 = Enable power down feature of the PLL<br>0 = power down feature of the PLL disabled.                                                                                                                                  |  |

| DRIVER  | 9       | R/W      | 0       | <ul> <li>1 = Upon initialization.</li> <li>0 = Upon reset.</li> <li>The Device Driver sets this bit as the first step of initialization to<br/>enable further access to the register set.</li> </ul>                     |  |

| DTD     | 10      | R/W      | 1       | <ul> <li>1 = Device determines the transfer direction automatically.</li> <li>0 = The direction is controlled by software by writing a 1 (TX) or 0 (RX) in DIR bit of this register</li> </ul>                           |  |

| DIR     | 11      | R/W      | 0       | 1 = Transmit<br>0 = Receive<br>This bit is valid only when DTD = 0.<br>Software should check the CHGDIR bit before writing to this bit.                                                                                  |  |

| SIPEN   | 12      | R/W      | 1       | <ul> <li>1 = Enables automatic hardware generation of SIP pulse.</li> <li>0 = Disables the auto SIP generation.</li> <li>Software must generate it through Vendor Specific commands.</li> </ul>                          |  |

| SENDSIP | 13      | R/W      | 0       | On detecting a transition from low to high on this bit,<br>the device generates a SIP.                                                                                                                                   |  |

| CHGDIR  | 14      | R        | 1       | <ul> <li>1 = Software is allowed to change the transfer direction by writing to DIR bit.</li> <li>0 = Direction change is not allowed.<br/>Software polls until this bit goes high before changing direction.</li> </ul> |  |

| RESET   | 15      | R/W      | 1       | 0 = Resets the bridge and IR TOP modules.<br>This bit is self clearing.                                                                                                                                                  |  |

\* IR needs to be reset when this bit is changed.

| Baud Rate | Frequency Selected |  |  |  |

|-----------|--------------------|--|--|--|

| 0         | 2.4 Kbps           |  |  |  |

| 1         | 9.6 Kbps           |  |  |  |

| 2         | 19.2 Kbps          |  |  |  |

| 3         | 38.4 Kbps          |  |  |  |

| 4         | 57.6 Kbps          |  |  |  |

| 5         | 115.2 Kbps         |  |  |  |

| 6         | 0.576 Mbps         |  |  |  |

| 7         | 1.152 Mbps         |  |  |  |

**USB 1.1 to IrDA Controller**

### Framing Register: offset 0x01

| Name | Bit    | Access | Default | Description                                                                                                                                         |

|------|--------|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|      |        |        |         | The number of STAs to be used                                                                                                                       |

| STAL | [7:0]  | R/W    | 0x00    | <ul> <li>* Bit-7 = 1, The 6 LSBs indicate the number of STAs to be used.</li> <li>* Bit-7 = 0, Uses the values hard coded in the design.</li> </ul> |

| IPG  | [15:8] | R/W    | 0x00    | Inter-packet gap<br>Specified in terms of number of bit times (MIR) or chip time (FIR).                                                             |

|      | [10.0] |        | 0.00    | * Bit-15 = 1, The 6 LSBs indicate the inter-packet gap to be used.<br>* Bit-15 = 0, Uses the values hard coded in the design.                       |

\* IR needs to be reset when this bit is changed.

#### XCVR Register: offset 0x02 Name Bit Access Default Description Used to configure the transceiver. 0 R/W The usage varies with the transceiver make and is reflected in MODE0 0 the transceiver truth table. Used to configure the transceiver. 1 The usage varies with the transceiver make and is reflected in STFIR R/W 0 the transceiver truth table. 1 = Puts the transceiver in Configuration Mode. 2 R/W 0 XCVR 0 = Puts the transceiver in Data Transfer Mode. 1 = Causes the device to use RXFAST as the input pin for R/W RXFAST 3 0 receive from transceiver. 0 = Causes the device to use RXSLOW as the receive signal. Sets the current control bits of the pad that drives TX-LED. TXCUR R/W 0 [6:4] This controls the current supplied to TX-LED. Used to configure the transceiver. MODE1 R/W The usage varies with the transceiver make and is reflected in 7 0 the transceiver truth table. Value of MODE0 to be configured to put it into shut down. SMODE0 8 R/W 1 Varies with transceiver make. Value of MODE1 to be configured to put it in shut down. SMODE1 9 R/W 0 Varies with transceiver make. 1 = inverts the data bits being fed into transceiver for transmit. INVTX 10 R/W 0 0 = the transmit line works as active high signal. 1 = RXD line from transceiver is treated as an active low signal INVRX 11 R/W 0 = RXD line from transceiver is treated as an active high signal. EEDATA [15:12] R 0 Loaded from the EEPROM.

The table below shows the usage of XCVR Register for various Transceivers.

| Vendor               | Code | Dynamic Configuration                                          |       |         |              |  |  |  |

|----------------------|------|----------------------------------------------------------------|-------|---------|--------------|--|--|--|

| Vendor               | Code | MODE0                                                          | MODE1 | STC_FIR | Latched From |  |  |  |

| Vishay<br>TDFU6614   | 0    | 1->0                                                           | 0     | 0       | TXD          |  |  |  |

| Vishay<br>TDFU6102   | 0    | 1->0                                                           | 0     | 0       | TXD          |  |  |  |

| SHARP<br>GP2W100YP   | 1    | 1->0                                                           | 0     | 1       | TXD          |  |  |  |

| Agilent<br>3602/3600 | 2    | Can switch pins dynamically.<br>There is no latching mechanism |       |         |              |  |  |  |

## SIP Resister: offset 0x03

| Name   | Bit    | Access | Default | Description                                                           |

|--------|--------|--------|---------|-----------------------------------------------------------------------|

| SIPON  | [6:0]  | R/W    | 0x4C    | Specifies pulse width of the SIP in terms of number of 48 MHz clocks. |

| SIPOFF | [15:7] | R/W    | 0x154   | The SIP low time.<br>Specified as of number of 48 MHz clocks.         |

## MINRXPW Register: offset 0x04

| Name  | Bit    | Access | Default | Description                                                                                                                                                        |

|-------|--------|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNRXW | [15:0] | R/W    | 0x00    | Minimum pulse width of the signal to be received.<br>0 = Device uses the hard coded values.<br>X = non zero<br>Device uses the value specified from this register. |

### TXPW Register: offset 0x05

| Name | Bit    | Access | Default | Description                                                                                                                                                   |

|------|--------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXPW | [15:0] | R/W    | 0x00    | Pulse width of the signal transmitted.<br>0 = device uses the hard coded values<br>X = non zero value,<br>device uses the value specified from this register. |

## RFIFO2 Register: offset 0x06

| Name   | Bit    | Access | Default | Description                                                                                                                                                    |

|--------|--------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMEOT | [7:0]  | R/W    | 0x0A    | Timeout specified in intervals of 50mS.<br>Used in SIR mode to abort a receive if idle for long<br>period specified by this register.<br>N => N*50 mS timeout. |

| TRSHD  | [14:8] | R/W    | 0x40    | FIFO Threshold                                                                                                                                                 |

| CLRFF  | 15     | R/W    | 0       | 1 = Clear FIFO pointers<br>0 = FIFO pointers not cleared<br><i>This bit is self clearing</i>                                                                   |

## RESV Register: offset 0x07

| Name   | Bit    | Access | Default | Description                                                                                                           |

|--------|--------|--------|---------|-----------------------------------------------------------------------------------------------------------------------|

| IRINTX | 0      | R      | 0       | <ul><li>1 = Indicates that transmit is in progress</li><li>0 = Indicates that transmit is not in progress</li></ul>   |

| IRINRX | 1      | R      | 0       | <ul><li>1 = Indicates that the receive is in progress</li><li>0 = Indicates that receive is not in progress</li></ul> |

| RESV   | [15:2] | R/W    | 0x0A    | Reserved                                                                                                              |

## Absolute Maximum Ratings

| Supply Voltage        | 3.8 Volts              |

|-----------------------|------------------------|

| Voltage at any pin    | GND - 0.3 to Vcc + 0.3 |

| Operating Temperature | -45° C to +90° C       |

| Storage Temperature   | -65° C to +150° C      |

| Package Dissipation   | 500 mW                 |

| ESD                   | ±2000 Volts            |

| Latch up              | 220 mA                 |

## **DC Electrical Specifications**

Temp =  $0^{\circ}$  C to +70° C, Vcc = 3.3V ± 10% unless otherwise specified.

| Symbol            | Parameter              | Min  | Max  | Unit | Condition               |

|-------------------|------------------------|------|------|------|-------------------------|

| Vcc               | Supply Voltage         | 3.0  | 3.6  | V    |                         |

| Vclk              | Clock input low level  | -0.5 | 0.6  | V    | External                |

| Vclk <sub>H</sub> | Clock input high level | 2.4  | Vcc  | V    | External                |

| Vi                | Input low level        |      | 1.08 | V    | CMOS                    |

| Vi <sub>H</sub>   | Input high level       | 2.1  |      | V    | CMOS                    |

| VoL               | Output low level       |      | 0.4  | V    | $Io_{L} = 4 \text{ mA}$ |

| Vo <sub>H</sub>   | Output high level      | 1.85 |      | V    | Io <sub>H</sub> = 4 mA  |

| li                | Input leakage current  | -10  | +10  | μA   |                         |

| lcc               | Operating current      | 12   | 19   | mA   |                         |

| Ср                | Input pin Capacitance  |      | 5    | pF   |                         |

## **AC Electrical Specifications**

Temp =  $0^{\circ}$  C to +70° C, Vcc = 3.3V ± 10% unless otherwise specified.

| Symbol | Parameter           | Min | Мах | Unit | Condition |

|--------|---------------------|-----|-----|------|-----------|

| CLKA   | USB clock frequency | 12  | 12  | MHz  | ±50PPM    |

**USB 1.1 to IrDA Controller**

## IMPORTANT NOTICE

Copyright © 2004-2011 ASIX Electronics Corporation. All rights reserved.

## DISCLAIMER

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of ASIX. ASIX may make changes to the product specifications and descriptions in this document at any time, without notice.

ASIX provides this document "as is" without warranty of any kind, either expressed or implied, including without limitation warranties of merchantability, fitness for a particular purpose, and non-infringement.

Designers must not rely on the absence or characteristics of any features or registers marked "reserved", "undefined" or "NC". ASIX reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. Always contact ASIX to get the latest document before starting a design of ASIX products.

## TRADEMARKS

ASIX, the ASIX logo are registered trademarks of ASIX Electronics Corporation. All other trademarks are the property of their respective owners.

## **USB 1.1 to IrDA Controller**

| <b>Revision History</b> |            |                                                                                                                                                                                                                                                   |  |  |

|-------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Revision                | Date       | Comment                                                                                                                                                                                                                                           |  |  |

| 1.0                     | Feb-2004   | Corrections                                                                                                                                                                                                                                       |  |  |

| 1.1                     | 9-Dec-2005 | Corrected Package Dimensions                                                                                                                                                                                                                      |  |  |

| 1.2                     | 3-Jan-2006 | Corrected Internal Register Details                                                                                                                                                                                                               |  |  |

| 2.00                    | 2011/08/05 | <ol> <li>Changed to ASIX Electronics Corp. logo, strings and contact<br/>information.</li> <li>Added ASIX copyright legal header information.</li> <li>Modified the Revision History table format.</li> <li>Updated the block diagram.</li> </ol> |  |  |

| 2.01                    | 2011/11/01 | 1. Updated the ordering information.                                                                                                                                                                                                              |  |  |