# MCTG35P60F1

PART WITHDRAWN

PROCESS OBSOLETE - NO NEW DESIGNS

S \ 35A, 600V P-Type MOS Controlled Thyristor (MCT)

April 1999

#### Features

- 35A, -600V

- V<sub>TM</sub> = -1.3V(Maximum) at I = 35A and +150°C

- 800A Surge Current Capability

- 800A/us di/dt Capability

- MOS Insulated Gate Control

- 50A Gate Turn-Off Capability at +150°C

## Description

The MCT is an MOS Controlled Thyristor designed for switching currents on and off by negative and positive pulsed control of an insulated MOS gate. It is designed for use in motor controls, inverters, line switches and other power switching applications.

The MCT is especially suited for resonant (zero voltage or zero current switching) applications. The SCR like forward drop greatly reduces conduction power loss.

MCTs allow the control of high power circuits with very small amounts of input energy. They feature the high peak current capability common to SCR type thyristors, and operate at junction temperatures up to +150°C with active switching.

#### PART NUMBER INFORMATION

| PART NUMBER | PACKAGE | BRAND    |

|-------------|---------|----------|

| MCTG35P60F1 | TO-247  | M35P60F1 |

NOTE: When ordering, use the entire part number.

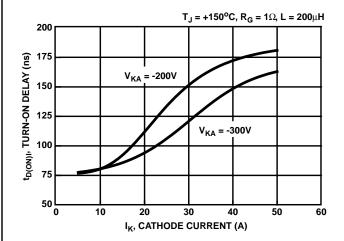

### Package

**JEDEC STYLE TO-247**

## Symbol

MCTG35D60E1

#### **Absolute Maximum Ratings** $T_C = +25^{\circ}C$ , Unless Otherwise Specified

|                                                              | MIC 1 G35P60F1 | UNITS |

|--------------------------------------------------------------|----------------|-------|

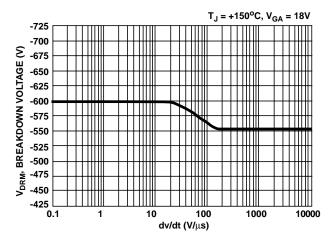

| Peak Off-State Voltage (See Figure 11)V <sub>DRM</sub>       | -600           | V     |

| Peak Reverse Voltage                                         | +5             | V     |

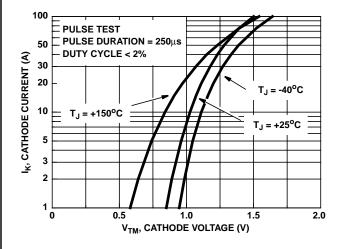

| Continuous Cathode Current (See Figure 2)                    |                |       |

| T <sub>C</sub> = +25°C (Package Limited)                     | 60             | Α     |

| $T_{C} = +115^{\circ}C$                                      | 35             | Α     |

| Non-Repetitive Peak Cathode Current (Note 1)I <sub>KSM</sub> | 800            | Α     |

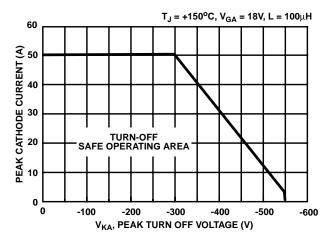

| Peak Controllable Current (See Figure 10)                    | 50             | Α     |

| Gate-Anode Voltage (Continuous)                              | ±20            | V     |

| Gate-Anode Voltage (Peak)                                    | ±25            | V     |

| Rate of Change of Voltage                                    | See Figure 11  |       |

| Rate of Change of Current                                    | 800            | A/μs  |

| Maximum Power Dissipation                                    | 178            | W     |

| Linear Derating Factor                                       | 1.43           | W/°C  |

| Operating and Storage Temperature                            | -55 to +150    | °C    |

| Maximum Lead Temperature for Soldering                       | 260            | °C    |

NOTE:

1. Maximum Pulse Width of 250 $\mu$ s (Half Sine) Assume T $_J$  (Initial) = +90°C and T $_J$  (Final) = T $_J$  (Max) = +150°C

LIMITO

# Specifications MCTG35P60F1

**Electrical Specifications**  $T_C = +25^{\circ}C$ , Unless Otherwise Specified

| PARAMETER                          | SYMBOL                | TEST CONDIT                                                                                                                                         | MIN                               | TYP | MAX | UNITS |      |

|------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|-----|-------|------|

| Peak Off-State Blocking<br>Current | I <sub>DRM</sub>      | V <sub>KA</sub> = -600V,<br>V <sub>GA</sub> = +18V                                                                                                  | $T_{\rm C} = +150^{\rm o}{\rm C}$ | -   | -   | 1.5   | mA   |

|                                    |                       |                                                                                                                                                     | T <sub>C</sub> = +25°C            | -   | -   | 50    | μΑ   |

| Peak Reverse Blocking<br>Current   | I <sub>RRM</sub>      | V <sub>KA</sub> = +5V<br>V <sub>GA</sub> = +18V                                                                                                     | $T_C = +150^{\circ}C$             | -   | -   | 2     | mA   |

|                                    |                       |                                                                                                                                                     | $T_{\rm C} = +25^{\rm o}{\rm C}$  | -   | -   | 50    | μΑ   |

| On-State Voltage                   | V <sub>TM</sub>       | I <sub>K</sub> = I <sub>K115</sub> ,<br>V <sub>GA</sub> = -10V                                                                                      | $T_C = +150^{\circ}C$             | -   | -   | 1.35  | V    |

|                                    |                       |                                                                                                                                                     | $T_{\rm C} = +25^{\rm o}{\rm C}$  | -   | -   | 1.4   | V    |

| Gate-Anode Leakage Current         | I <sub>GAS</sub>      | V <sub>GA</sub> = ±20V                                                                                                                              |                                   | -   | -   | 100   | nA   |

| Input Capacitance                  | C <sub>ISS</sub>      | V <sub>KA</sub> = -20V, T <sub>J</sub> = +25°C<br>V <sub>GA</sub> = +18V                                                                            |                                   | -   | 5   | -     | nF   |

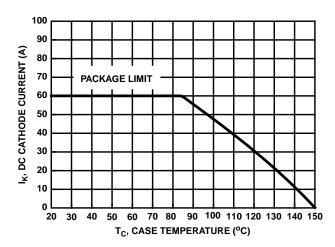

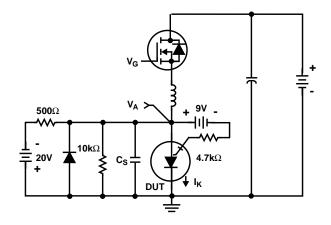

| Current Turn-On Delay Time         | t <sub>D(ON)I</sub>   | $\begin{split} L &= 200 \mu H, \ I_K = I_{K115} \\ R_G &= 1 \Omega, \ V_{GA} = +18 V, \ -7 V \\ T_J &= +125 ^{o} C \\ V_{KA} &= -300 V \end{split}$ |                                   | -   | 140 | -     | ns   |

| Current Rise Time                  | t <sub>RI</sub>       |                                                                                                                                                     |                                   | -   | 180 | -     | ns   |

| Current Turn-Off Delay Time        | t <sub>D(OFF)</sub> I |                                                                                                                                                     |                                   | -   | 640 | -     | ns   |

| Current Fall Time                  | t <sub>FI</sub>       |                                                                                                                                                     |                                   | -   | 1.1 | 1.4   | μs   |

| Turn-Off Energy                    | E <sub>OFF</sub>      |                                                                                                                                                     | -                                 | 5.6 | -   | mJ    |      |

| Thermal Resistance                 | $R_{	heta JC}$        |                                                                                                                                                     |                                   | -   | 0.6 | 0.7   | °C/W |

# **Typical Performance Curves**

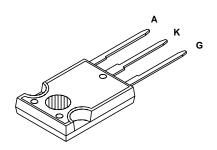

FIGURE 1. CATHODE CURRENT vs SATURATION VOLTAGE (TYPICAL)

FIGURE 2. MAXIMUM CONTINUOUS CATHODE CURRENT

## Typical Performance Curves (Continued)

FIGURE 3. TURN-ON DELAY VS CATHODE CURRENT (TYPICAL)

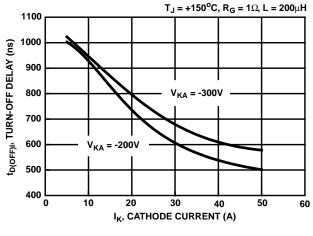

FIGURE 4. TURN-OFF DELAY vs CATHODE CURRENT (TYPICAL)

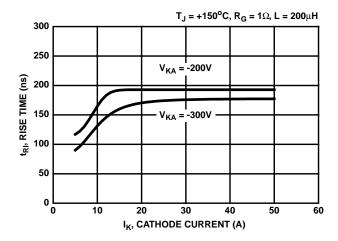

FIGURE 5. TURN-ON RISE TIME vs CATHODE CURRENT (TYPICAL)

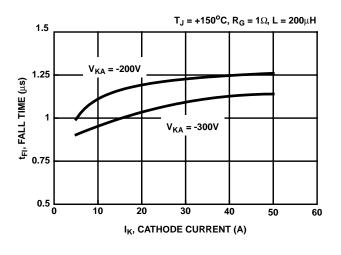

FIGURE 6. TURN-OFF FALL TIME vs CATHODE CURRENT (TYPICAL)

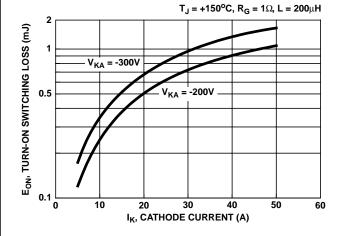

FIGURE 7. TURN-ON ENERGY LOSS vs CATHODE CURRENT (TYPICAL)

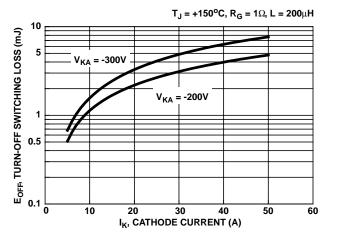

FIGURE 8. TURN-OFF ENERGY LOSS vs CATHODE CURRENT (TYPICAL)

## Typical Performance Curves (Continued)

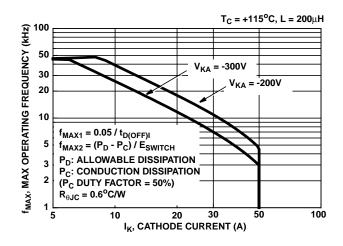

FIGURE 9. OPERATING FREQUENCY VS CATHODE CURRENT (TYPICAL)

FIGURE 10. TURN-OFF CAPABILITY vs ANODE-CATHODE VOLTAGE

FIGURE 11. BLOCKING VOLTAGE vs dv/dt

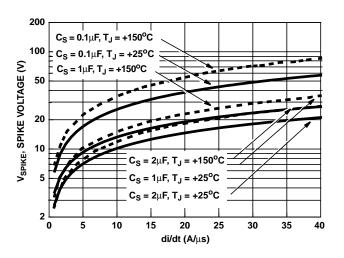

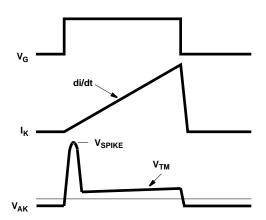

FIGURE 12. SPIKE VOLTAGE vs di/dt (TYPICAL)

## Operating Frequency Information

Operating frequency information for a typical device (Figure 9) is presented as a guide for estimating device performance for a specific application. Other typical frequency vs cathode current ( $I_{AK}$ ) plots are possible using the information shown for a typical unit in Figure 3 to Figure 8. The operating frequency plot (Figure 9) of a typical device shows  $f_{MAX1}$  or  $f_{MAX2}$  whichever is lower at each point. The information is based on measurements of a typical device and is bounded by the maximum rated junction temperature.

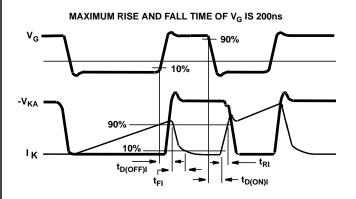

$f_{MAX1}$  is defined by  $f_{MAX1}=0.05\ /\ (t_{D(ON)I}+t_{D(OFF)I}).\ t_{D(ON)I}+t_{D(OFF)I}$  deadtime (the denominator) has been arbitrarily held to 10% of the on-state time for a 50% duty factor. Other definitions are possible.  $t_{D(ON)I}$  is defined as the 10% point of the leading edge of the input pulse and the point where the cathode current rises to 10% of its maximum value.  $t_{D(OFF)I}$  is defined as the 90% point of the trailing edge of the input pulse and the point where the cathode current falls to 90% of

its maximum value. Device delay can establish an additional frequency limiting condition for an application other than  $T_{\text{JMAX}}.\ t_{\text{D(OFF)I}}$  is important when controlling output ripple under a lightly loaded condition.

$f_{MAX2}$  is defined by  $f_{MAX2}=(P_D-P_C)$  /  $(E_{ON}+E_{OFF}).$  The allowable dissipation  $(P_D)$  is defined by  $P_D=(T_{JMAX}-T_C)$  /  $R_{\theta JC}.$  The sum of device switching and conduction losses must not exceed  $P_D.$  A 50% duty factor was used (Figure 10) and the conduction losses  $(P_C)$  are approximated by  $PC=(V_{AK}\bullet I_{AK})$  / (duty factor/100).  $E_{ON}$  is defined as the sum of the instantaneous power loss starting at the leading edge of the input pulse and ending at the point where the anodecathode voltage equals saturation voltage  $(V_{AK}=V_{TM}).$   $E_{OFF}$  is defined as the sum of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the cathode current equals zero  $(I_K=0).$

## **Test Circuits**

FIGURE 13. SWITCHING TEST CIRCUIT

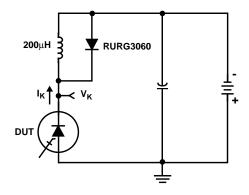

FIGURE 14. V<sub>SPIKE</sub> TEST CIRCUIT

FIGURE 15. SWITCHING TEST WAVEFORMS

FIGURE 16. V<sub>SPIKE</sub> TEST WAVEFORMS

## Handling Precautions for MCTs

MOS Controlled Thyristors are susceptible to gate-insulation damage by the electrostatic discharge of energy through the devices. When handling these devices, care should be exercised to assure that the static charge built in the handler's body capacitance is not discharged through the device. MCT's can be handled safely if the following basic precautions are taken:

- Prior to assembly into a circuit, all leads should be kept shorted together either by the use of metal shorting springs or by the insertion into conductive material such as "ECCOSORB LD26" or equivalent.

- When devices are removed by hand from their carriers, the hand being used should be grounded by any suitable means - for example, with a metallic wristband.

- 3. Tips of soldering irons should be grounded.

- Devices should never be inserted into or removed from circuits with power on.

- 5. Gate Voltage Rating Never exceed the gate-voltage rating of  $V_{\text{GA}}$ . Exceeding the rated  $V_{\text{GA}}$  can result in permanent damage to the oxide layer in the gate region.

- 6. Gate Termination The gates of these devices are essentially capacitors. Circuits that leave the gate open-circuited or floating should be avoided. These conditions can result in turn-on of the device due to voltage buildup on the input capacitor due to leakage currents or pickup.

- 7. Gate Protection These devices do not have an internal monolithic zener diode from gate to emitter. If gate protection is required an external zener is recommended.

- † Trademark Emerson and Cumming, Inc.