## Freescale Semiconductor Technical Data

## System Basis Chip with Low Speed Fault Tolerant CAN Interface

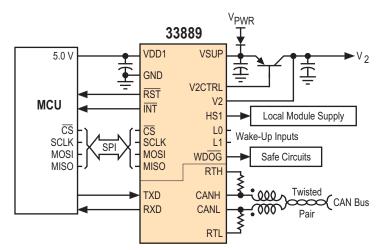

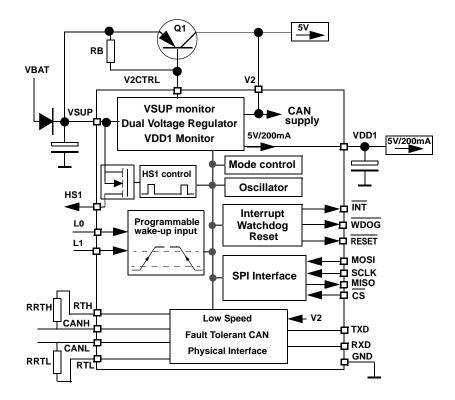

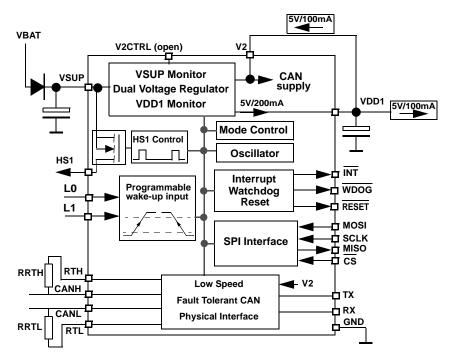

An SBC device is a monolithic I<sup>C</sup> combining many functions repeatedly found in standard microcontroller-based systems, e.g., protection, diagnostics, communication, power, etc. The 33889 is an SBC having fully protected, fixed 5.0 V low drop-out regulator, with current limit, over-temperature pre-warning and reset.

An output drive with sense input is also provided to implement a second 5.0 V regulator using an external PNP. The 33889 has Normal, Standby, Stop and Sleep modes; an internally switched high-side power supply output with two wake-up inputs; programmable timeout or window watchdog, Interrupt, Reset, SPI input control, and a low-speed fault tolerant CAN transceiver, compatible with CAN 2.0 A and B protocols for module-to-module communications. The combination is an economical solution for power management, high-speed communication, and control in MCU-based systems.

#### Features

- VDD1: 5.0 V low drop voltage regulator, current limitation, overtemperature detection, monitoring and reset function with total current capability 200 mA

- V<sub>2</sub>: tracking function of VDD1 regulator; control circuitry for external bipolar ballast transistor for high flexibility in choice of peripheral voltage and current supply

- · Four operational modes

- Low standby current consumption in Stop and Sleep modes

- Built-in low speed 125 kbps fault tolerant CAN physical interface.

- External high voltage wake-up input, associated with HS1 VBAT switch

- 150 mA output current capability for HS1 VBAT switch allowing drive of external switches pull-up resistors or relays

- Pb-Free Packaging Designated by Suffix Code EG

Figure 1. 33889 Simplified Application Diagram

Freescale Semiconductor, Inc. reserves the right to change the detail specifications, as may be required, to permit improvements in the design of its products. © Freescale Semiconductor, Inc., 2006. All rights reserved.

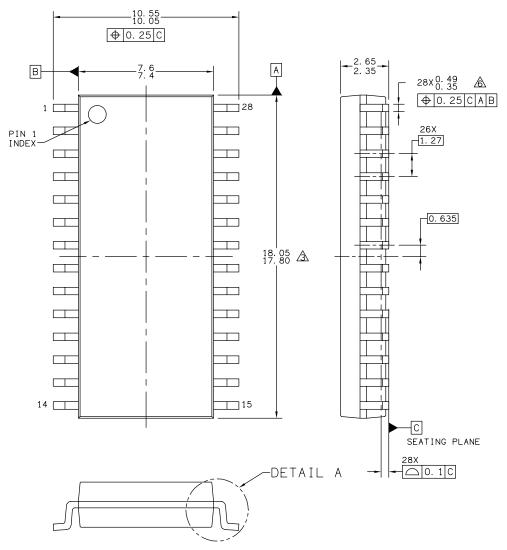

## 33889

#### SYSTEM BASIS CHIP

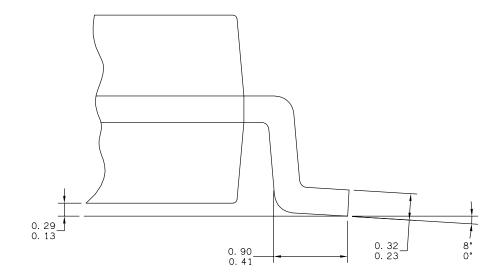

DW SUFFIX EG SUFFIX (PB-FREE) PLASTIC PACKAGE 98ASB42345B 28-PIN SOICW

## ORDERING INFORMATION

| Device          | Temperature<br>Range (T <sub>A</sub> ) | Package    |

|-----------------|----------------------------------------|------------|

| MC33889BDW/R2   |                                        |            |

| MCZ33889BEG/R2  | -40°C to 125°C                         | 28 SOICW   |

| MC33889DDW/R2   | -40 C to 125 C                         | 28 3010 10 |

| *MCZ33889DEG/R2 |                                        |            |

\*Recommended for new designs

Document Number: MC33889 Rev. 11.0, 12/2006

## **DEVICE VARIATIONS**

## Table 1. Device Variations Between the 33889D and 33889B Versions <sup>(1)</sup>

| Proventions                                                                                     | 0 miliot           | Tasir | Device Pa                        | rt Number               |

|-------------------------------------------------------------------------------------------------|--------------------|-------|----------------------------------|-------------------------|

| Parameters                                                                                      | Symbol             | Trait | MC33889B <sup>(2)</sup>          | MC33889D <sup>(2)</sup> |

| Differential Receiver, Recessive To Dominant Threshold                                          |                    | Min   | 3.2 V                            | 3.5 V                   |

| (By Definition, $V_{DIFF} = V_{CANH} - V_{CANL}$ )                                              | V <sub>DIFF1</sub> | Тур   | 2.6 V                            | 3.0 V                   |

|                                                                                                 |                    | Max   | 2.1 V                            | 2.5 V                   |

| Differential Receiver, Dominant To Recessive Threshold                                          |                    | Min   | 3.2 V                            | 3.5 V                   |

| (Bus Failures 1, 2, 5)                                                                          | V <sub>DIFF2</sub> | Тур   | 2.6 V                            | 3.0 V                   |

|                                                                                                 |                    | Max   | 2.1 V                            | 2.5 V                   |

| CANH Output Current ( $V_{CANH} = 0$ ; TX = 0.0)                                                |                    | Min   | 50 mA                            | 50 mA                   |

|                                                                                                 | I <sub>CANH</sub>  | Тур   | 75 mA                            | 100 mA                  |

|                                                                                                 |                    | Max   | 110 mA                           | 130 mA                  |

| CANL Output Current (V <sub>CANL</sub> = 14 V; TX = 0.0)                                        | ICANL              | Min   | 50 mA                            | 50 mA                   |

|                                                                                                 |                    | Тур   | 90 mA                            | 140 mA                  |

|                                                                                                 |                    | Max   | 135 mA                           | 170 mA                  |

| Detection threshold for Short circuit to Battery voltage                                        | Vcanh              | max   | Vsup/2 + 5V                      | Vsup/2 + 4.55\          |

| loop time Tx to Rx, no bus failure, ISO configuration                                           | tLOOPRD            | max   | N/A                              | 1.5us                   |

| loop time Tx to Rx, with bus failure, ISO configuration                                         | tLOOPRD-F          | max   | N/A                              | 1.9us                   |

| loop time Tx to Rx, with bus failure and +-1.5V gnd shift,<br>5 node network, ISO configuration | tLOOPRD/DR-F+GS    |       | N/A                              | 3.6us                   |

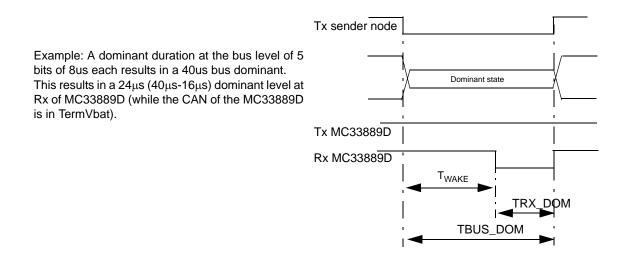

| Minimum Dominant time for Wake up on CANL or CANH                                               | tWAKE              | min   | N/A                              | 8                       |

| (Tem Vbat mode)                                                                                 |                    | typ   | 30                               | 16                      |

|                                                                                                 |                    | max   | N/A                              | 30                      |

| T2SPI timing                                                                                    | T2spi              | min   | not specified, 25us spec applied | 25us                    |

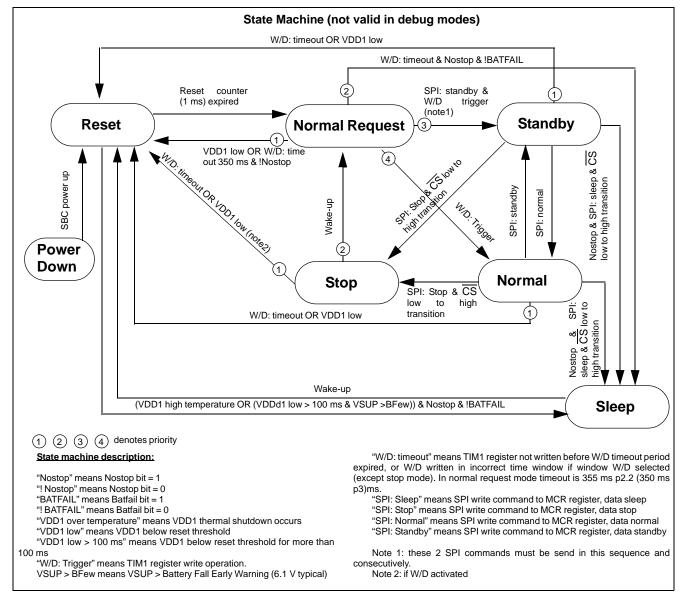

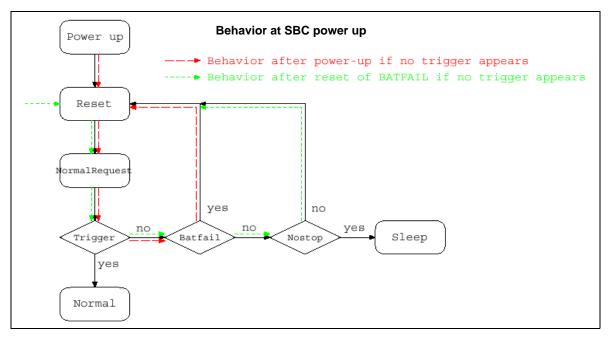

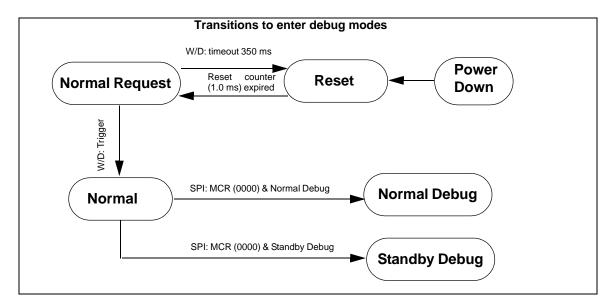

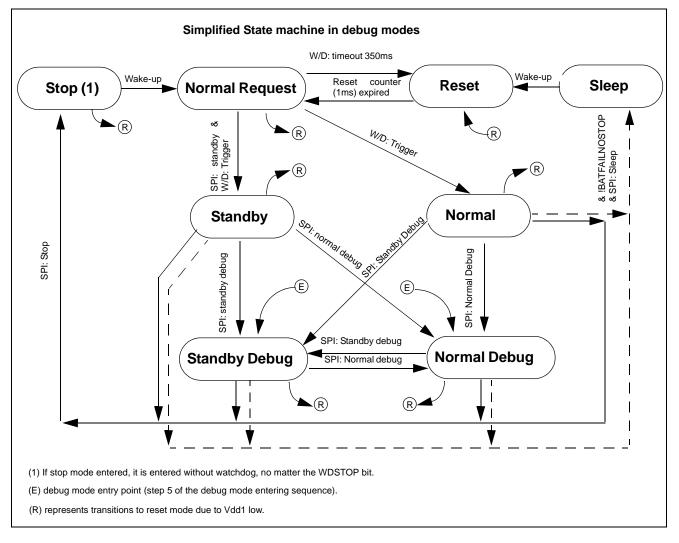

#### DEVICE BEHAVIOR

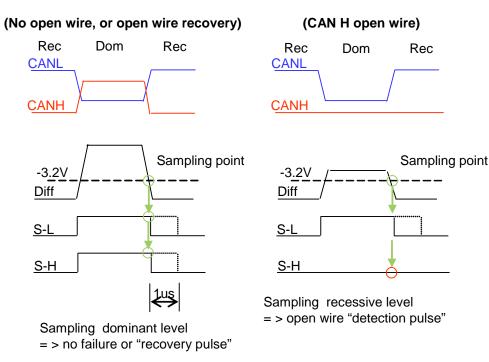

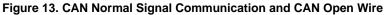

| CANH or CANL open wire recovery principle | Reference MC33889B: on page 33 | after 4 non<br>consecutive pulses | after 4 consecutive pulses                               |

|-------------------------------------------|--------------------------------|-----------------------------------|----------------------------------------------------------|

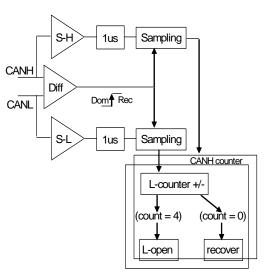

| Rx behavior in TermVbat mode              | Reference MC33889D: on page 34 | Rx recessive, no pulse            | Rx recessive, dominant<br>pulse to signal bus<br>traffic |

Notes

1. This datasheet uses the term 33889 in the inclusive sense, referring to both the D version (33889D) and the B version (33689B).

2. The 33889D and 33889B versions are nearly identical. However, where variations in characteristic occur, these items will be separated onto individual lines.

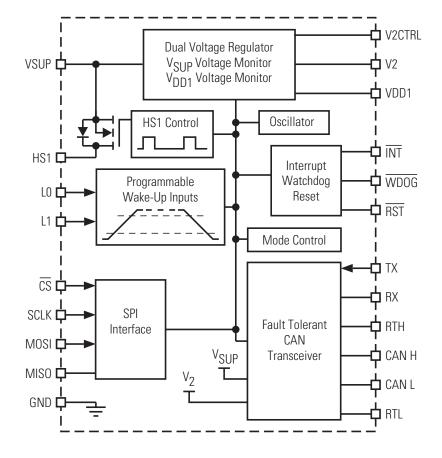

## INTERNAL BLOCK DIAGRAM

## 33889 Internal Block Diagram

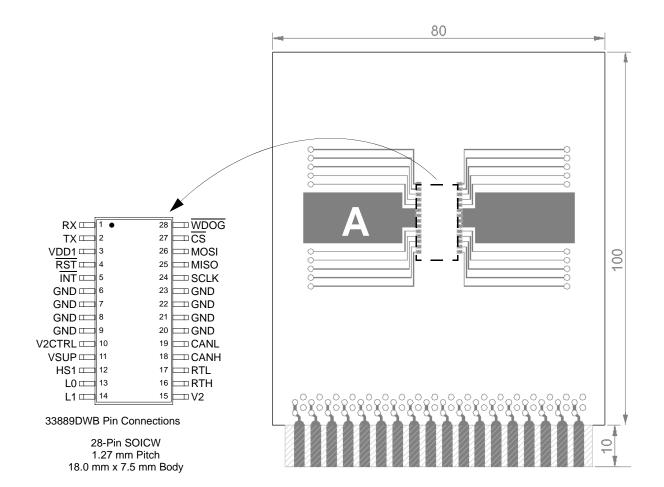

## **PIN CONNECTIONS**

| 1 • | 28                                                           |                                                                                                                                                                                                                                                                               |

|-----|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | 27                                                           | □ CS                                                                                                                                                                                                                                                                          |

| 3   | 26                                                           | 💷 MOSI                                                                                                                                                                                                                                                                        |

| 4   | 25                                                           | □ – I MISO                                                                                                                                                                                                                                                                    |

| 5   | 24                                                           | - SCLK                                                                                                                                                                                                                                                                        |

| 6   | 23                                                           | 💷 GND                                                                                                                                                                                                                                                                         |

| 7   | 22                                                           | 💷 GND                                                                                                                                                                                                                                                                         |

| 8   | 21                                                           | 💷 GND                                                                                                                                                                                                                                                                         |

| 9   | 20                                                           | 💷 GND                                                                                                                                                                                                                                                                         |

| 10  | 19                                                           | 💷 CANL                                                                                                                                                                                                                                                                        |

| 11  | 18                                                           | 📼 CANH                                                                                                                                                                                                                                                                        |

| 12  | 17                                                           | 💷 RTL                                                                                                                                                                                                                                                                         |

| 13  | 16                                                           | 📼 RTH                                                                                                                                                                                                                                                                         |

| 14  | 15                                                           | 🖵 V2                                                                                                                                                                                                                                                                          |

|     | 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13 | 2         27           3         26           4         25           5         24           6         23           7         22           8         21           9         20           10         19           11         18           12         17           13         16 |

#### Figure 2. 33889 Pin Connections

## Table 2. Pin Definitions

A functional description of each pin can be found in the Functional pin description section page 24.

| Pin              | Pin Name | Pin<br>Function | Formal Name              | Definition                                                                                                          |

|------------------|----------|-----------------|--------------------------|---------------------------------------------------------------------------------------------------------------------|

| 1                | RX       | Output          | Receiver Data            | CAN bus receive data output pin                                                                                     |

| 2                | ТХ       | Input           | Transmitter Data         | CAN bus receive data input pin                                                                                      |

| 3                | VDD1     | Power<br>Output | Voltage Regulator One    | 5.0 V pin is a 2% low drop voltage regulator for to the microcontroller supply.                                     |

| 4                | RST      | Output          | Reset                    | This is the device reset output pin whose main function is to reset the MCU.                                        |

| 5                | INT      | Output          | Interrupt                | This output is asserted LOW when an enabled interrupt condition occurs.                                             |

| 6 -9,<br>20 - 23 | GND      | Ground          | Ground                   | These device ground pins are internally connected to the package lead frame to provide a 33889-to-PCB thermal path. |

| 10               | V2CTRL   | Output          | Voltage Source 2 Control | Output drive source for the V2 regulator connected to the external series pass transistor.                          |

| 11               | VSUP     | Power<br>Input  | Voltage Supply           | Supply input pin.                                                                                                   |

| 12               | HS1      | Output          | High-Side Output         | Output of the internal high-side switch.                                                                            |

| 13 - 14          | L0, L1   | Input           | Level 0 - 1 Inputs       | Inputs from external switches or from logic circuitry.                                                              |

| 15               | V2       | Input           | Voltage Regulator Two    | 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.                                      |

| 16               | RTH      | Output          | RTH                      | Pin for connection of the bus termination resistor to CANH.                                                         |

| 17               | RTL      | Output          | RTL                      | Pin for connection of the bus termination resistor to CANL.                                                         |

| 18               | CANH     | Output          | CAN High                 | CAN high output pin.                                                                                                |

| 19               | CANL     | Output          | CAN Low                  | CAN low output pin.                                                                                                 |

| 24               | SCLK     | Input           | System Clock             | Clock input pin for the Serial Peripheral Interface (SPI).                                                          |

## Table 2. Pin Definitions (continued)

A functional description of each pin can be found in the Functional pin description section page 24.

| Pin | Pin Name | Pin<br>Function | Formal Name         | Definition                                                                                                                                                                   |

|-----|----------|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25  | MISO     | Output          | Master In/Slave Out | SPI data sent to the MCU by the 33889. When $\rm CS_{\rm LOW}$ is HIGH, the pin is in the high impedance state.                                                              |

| 26  | MOSI     | Input           | Master Out/Slave In | SPI data received by the 33889.                                                                                                                                              |

| 27  | CS       | Input           | Chip Select         | The $\rm CS_{\rm LOW}$ input pin is used with the SPI bus to select the 33889. When the $\rm CS_{\rm LOW}$ is asserted LOW, the 33889 is the selected device of the SPI bus. |

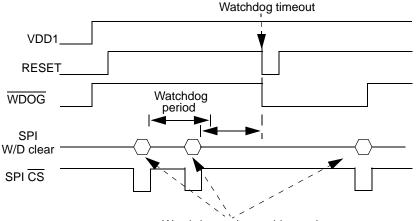

| 28  | WDOG     | Output          | Watchdog            | The WDOG output pin is asserted LOW if the software watchdog is not correctly triggered.                                                                                     |

ELECTRICAL CHARACTERISTICS MAXIMUM RATINGS

## **ELECTRICAL CHARACTERISTICS**

#### **MAXIMUM RATINGS**

#### Table 3. Maximum Ratings

Transient Voltage On Pins CANH, CANL

DC Voltage On Pins RTH, RTL

Transient Voltage At Pins RTH, RTL

(Coupled Through 1.0 nF Capacitor)

0.0 < V2-INT < 5.5 V; VSUP = 0.0; T < 500 ms

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                      | Symbol                               | Max                           | Unit |

|----------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------|------|

| ELECTRICAL RATINGS                                                                           |                                      |                               |      |

| Supply Voltage at VSUP                                                                       |                                      |                               | V    |

| Continuous voltage                                                                           | V <sub>SUP</sub>                     | -0.3 to 27                    |      |

| Transient voltage (Load dump)                                                                |                                      | 40                            |      |

| Logic Signals                                                                                | V <sub>LOG</sub>                     | -0.3 to V <sub>DD1</sub> +0.3 | V    |

| $(RX, TX, MOSI, MISO, \overline{CS}, SCLK, \overline{RST}, \overline{WDOG}, \overline{INT})$ | 200                                  | 551                           |      |

| Output current VDD1                                                                          | I                                    | Internally Limited            | mA   |

| HS1                                                                                          |                                      |                               |      |

| Voltage                                                                                      | V                                    | -0.2 to V <sub>SUP</sub> +0.3 | V    |

| Output Current                                                                               | I                                    | Internally Limited            | А    |

| L0, L1                                                                                       |                                      |                               |      |

| DC Input voltage                                                                             | V <sub>WU</sub>                      | -0.3 to 40                    | V    |

| DC Input current                                                                             | I <sub>WU</sub>                      | -2.0 to 2.0                   | mA   |

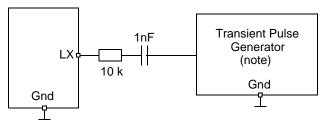

| Transient input voltage (according to ISO7637 specification) and with                        | V <sub>TRWU</sub>                    | +-100                         | V    |

| external component per Figure 3.                                                             |                                      |                               |      |

| DC voltage at V2 (V2INT)                                                                     | V <sub>2INT</sub>                    | 0 to 5.25                     | V    |

| DC Voltage On Pins CANH, CANL                                                                | V <sub>BUS</sub>                     | -20 to +27                    | V    |

| Fransient Voltage At Pins CANH, CANL                                                         | V <sub>CANH</sub> /V <sub>CANL</sub> | -40 to +40                    | V    |

| 0.0 < V2-INT < 5.5 V; VSUP = 0.0; T < 500 ms                                                 | ' CAINE' ' CAINL                     |                               | •    |

-150 to +100

-0.3 to +27V

-0.3 to +40

$V_{\mathsf{TR}}$

$V_{RTL}, V_{RTH}$

V<sub>RTH</sub>/V<sub>RTL</sub>

V

V

V

#### Table 3. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                                                 | Symbol               | Мах                  | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| ESD voltage (HBM 100 pF, 1.5 k) <sup>(3)</sup><br>CANL, CANH, HS1, L0, L1<br>RTH, RTL<br>All other pins | V <sub>ESDH</sub>    | ±4.0<br>±3.0<br>±2.0 | kV   |

| ESD voltage (Machine Model) All pins, MC33889B <sup>(3) (4)</sup>                                       | V <sub>ESD-MM</sub>  | ±200                 | V    |

| ESD voltage (CDM) All pins, MC33889D <sup>(4)</sup><br>Pins 1,14,15, & 28<br>All other pins             | V <sub>ESD-CDM</sub> | 750<br>500           | V    |

| RTH, RTL Termination Resistance                                                                         | R <sub>T</sub>       | 500 to 16000         | ohms |

#### THERMAL RATINGS

| Junction Temperature                                  | TJ                 | -40 to 150 | °C   |

|-------------------------------------------------------|--------------------|------------|------|

| Storage Temperature                                   | Τ <sub>S</sub>     | -55 to 165 | °C   |

| Ambient Temperature (for info only)                   | T <sub>A</sub>     | -40 to 125 | °C   |

| Thermal resistance junction to gnd pin <sup>(5)</sup> | R <sub>THJ/P</sub> | 20         | °C/W |

Notes:

- 3. Testing done in accordance with the Human Body Model (CzAP=100 pF, RzAP=1500 ), Machine Model (CzAP=200 pF, RzAP=0 ).

- 4. ESD machine model (MM) is for MC33889B only. MM is now replaced by CDM (Charged Discharged model).

- 5. Gnd pins 6,7,8,9,20, 21, 22, 23.

Note: Waveform in accordance to ISO7637 part1, test pulses 1, 2, 3a and 3b.

#### Figure 3. Transient test pulse for L0 and L1 inputs

## STATIC ELECTRICAL CHARACTERISTICS

#### Table 4. Static Electrical Characteristics .

Characteristics noted under conditions - VSUP From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Description                                                                                                                                                          | Symbol                                | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|------|-----|------|

| INPUT PIN (VSUP)                                                                                                                                                     |                                       |     |      |     |      |

| Nominal DC Voltage range                                                                                                                                             | V <sub>SUP</sub>                      | 5.5 | -    | 18  | V    |

| Extended DC Voltage range 1<br>Reduced functionality <sup>(6)</sup>                                                                                                  | V <sub>SUP-EX1</sub>                  | 4.5 | -    | 5.5 | V    |

| Extended DC Voltage range 2 <sup>(8)</sup>                                                                                                                           | V <sub>SUP-EX2</sub>                  | 18  | -    | 27  | V    |

| Input Voltage during Load Dump<br>Load dump situation                                                                                                                | V <sub>SUPLD</sub>                    | -   | -    | 40  | V    |

| Input Voltage during jump start<br>Jump start situation                                                                                                              | V <sub>SUPJS</sub>                    | -   | -    | 27  | V    |

| Supply Current in Sleep Mode $^{(7)}$ $V_{DD1} \mbox{ & V2 off, } V_{SUP} \leq 12 \mbox{ V, oscillator running }^{(10)}$                                             | I <sub>SUP</sub><br>(SLEEP1)          | -   | 95   | 130 | μA   |

| Supply Current in Sleep Mode $^{(7)}$ $V_{DD1}$ & V2 off, $V_{SUP} \leq$ 12 V, oscillator not running                                                                | I <sub>SUP</sub><br>(SLEEP2)          | -   | 55   | 90  | μΑ   |

| Supply current in sleep mode $^{(7)}$<br>V <sub>DD1</sub> & V2 off, V <sub>SUP</sub> = 18 V, oscillator running $^{(10)}$                                            | I <sub>SUP</sub><br>(SLEEP3)          | -   | 170  | 270 | μΑ   |

| Supply Current in Stand-by Mode $^{(7),(9)}$<br>lout at V <sub>DD1</sub> = 40 mA, CAN recessive state or disabled                                                    | I <sub>SUP</sub> ( <sub>STDBY</sub> ) | -   | 42   | 45  | mA   |

| Supply Current in Normal Mode $^{(7)}$<br>lout at V <sub>DD1</sub> = 40 mA, CAN recessive state or disabled                                                          | I <sub>SUP(NORM)</sub>                | -   | 42.5 | 45  | mA   |

| Supply Current in Stop mode $^{(7),(9)}$ I out V <sub>DD1</sub> < 2.0 mA, V <sub>DD1</sub> on $^{(11)}$ , V <sub>SUP</sub> $\leq$ 12 V, oscillator running $^{(10)}$ | I <sub>SUP</sub><br>(STOP1)           | -   | 120  | 150 | μΑ   |

| Supply Current in Stop mode $^{(7),(9)}$ lout V <sub>DD1</sub> < 2.0 mA, V <sub>DD1</sub> on $^{(11)}$ V <sub>SUP</sub> $\leq$ 12V, oscillator not running $^{(10)}$ | I <sub>SUP</sub><br>(STOP2)           | -   | 80   | 110 | μΑ   |

| Supply Current in Stop mode $^{(7),(9)}$<br>lout V <sub>DD1</sub> < 2.0 mA, V <sub>DD1</sub> on $^{(11)}$ , V <sub>SUP</sub> = 18 V, oscillator<br>running $^{(10)}$ | I <sub>SUP</sub><br>(STOP3)           | -   | 200  | 285 | μΑ   |

Notes

6.  $V_{DD1} > 4.0 V$ , reset high, if  $R_{STTH-2}$  selected and  $I_{OUT} V_{DD1}$  reduced, logic pin high level reduced, device is functional.

7. Current measured at V<sub>SUP</sub> pin.

8. Device is fully functional. All modes available and operating, Watchdog, HS1 turn ON turn OFF, CAN cell operating, L0 and L1 inputs operating, SPI read write operation. Over temperature may occur.

9. Measured in worst case condition with 5.0 V at V2 pin (V2 pin tied to VDD1).

10. Oscillator running means "Forced Wake-Up" or "Cyclic Sense" or "Software Watchdog" timer activated. Software Watchdog is available in stop mode only.

11.  $V_{DD1}$  is ON with 2.0 mA typical output current capability.

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                                                                  | Symbol                           | Min        | Тур      | Max      | Unit |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------|----------|----------|------|

| Supply Fail Flag internal threshold                                                                                          | V <sub>THRESH</sub>              | 1.5        | 3.0      | 4.0      | V    |

| Supply Fail Flag hysteresis <sup>(12)</sup>                                                                                  | V <sub>DETHYST</sub>             | -          | 1.0      | -        | V    |

| Battery fall early warning threshold<br>In normal & standby mode                                                             | BF <sub>EW</sub>                 | 5.8        | 6.1      | 6.4      | V    |

| Battery fall early warning hysteresis<br>In normal & standby mode <sup>(12)</sup>                                            | BF <sub>EWH</sub>                | 0.1        | 0.2      | 0.3      | V    |

| OUTPUT PIN (VDD1) <sup>(13)</sup>                                                                                            |                                  |            |          |          |      |

| VDD1 Output Voltage<br>I <sub>DD1</sub> from 2.0 to 200mA                                                                    | V <sub>DD1OUT</sub>              |            |          |          | V    |

| 5.5 V < V <sub>SUP</sub> < 27 V<br>4.5 V < V <sub>SUP</sub> < 5.5 V                                                          |                                  | 4.9<br>4.0 | 5.0<br>- | 5.1<br>- |      |

| Drop Voltage V <sub>SUP</sub> > V <sub>DDOUT</sub><br>I <sub>DD1</sub> = 200 mA                                              | V <sub>DD1DROP</sub>             | -          | 0.2      | 0.5      | V    |

| Drop Voltage $V_{SUP} > V_{DDOUT}$ , limited output current<br>$I_{DD1} = 50 \text{ mA}$<br>4.5 V < $V_{SUP} < 27 \text{ V}$ | V <sub>DD1DP2</sub>              | -          | 0.1      | 0.25     | V    |

| I <sub>DD1</sub> Output Current<br>Internally limited                                                                        | I <sub>DD1</sub>                 | 200        | 270      | 350      | mA   |

| VDD1 Output Voltage in stop mode<br>lout < 2.0 mA                                                                            | V <sub>DDSTOP</sub>              | 4.75       | 5.00     | 5.25     | V    |

| I <sub>DD1</sub> stop output current to wake-up SBC<br>Default value after reset. <sup>(14)</sup>                            | I <sub>DD1S-WU1</sub>            | 2.0        | 3.5      | 6.0      | mA   |

| I <sub>DD1</sub> stop output current to wake-up SBC <sup>(14)</sup>                                                          | I <sub>DD1S-WU2</sub>            | 10         | 14       | 18       | mA   |

| I <sub>DD1</sub> over current wake deglitcher<br>(with I <sub>DD1S-WU1</sub> selected) <sup>(12)</sup>                       | I <sub>DD1-DGIT11</sub>          | 40         | 55       | 75       | μS   |

| I <sub>DD1</sub> over current wake deglitcher<br>(with I <sub>DD1S-WU2</sub> selected) <sup>(12)</sup>                       | I <sub>DD1-DGIT2</sub>           | -          | 150      | -        | μs   |

| Thermal Shutdown<br>Normal or standby mode                                                                                   | T <sub>SD</sub>                  | 160        | -        | 190      | °C   |

| Over temperature pre warning<br>VDDTEMP bit set                                                                              | T <sub>PW</sub>                  | 130        | -        | 160      | °C   |

| Temperature Threshold difference                                                                                             | T <sub>SD</sub> -T <sub>PW</sub> | 20         | -        | 40       | °C   |

Notes

12. Guaranteed by design

13.  $I_{DD1}$  is the total regulator output current. VDD specification with external capacitor  $C \ge 22\mu F$  and ESR < 10 ohm.

14. Selectable by SPI

Characteristics noted under conditions - VSUP From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                 | Symbol               | Min  | Тур | Мах | Unit |

|-----------------------------------------------------------------------------|----------------------|------|-----|-----|------|

| Reset threshold 1<br>Default value after reset. <sup>(15)</sup>             | V <sub>RST-TH1</sub> | 4.5  | 4.6 | 4.7 | V    |

| Reset threshold 2 <sup>(15)</sup>                                           | V <sub>RST-TH2</sub> | 4.1  | 4.2 | 4.3 | V    |

| Reset duration                                                              | RESET-DUR            | 0.85 | 1.0 | 2.0 | ms   |

| VDD1 range for Reset Active                                                 | V <sub>DD</sub>      | 1.0  | -   | -   | V    |

| Reset Delay Time<br>Measured at 50% of reset signal. <sup>(16)</sup>        | t <sub>D</sub>       | 5.0  | -   | 20  | μS   |

| Line Regulation<br>9.0 V < V <sub>SUP</sub> < 18, I <sub>DD</sub> = 10 mA   | LR1                  | -    | 5.0 | 25  | mV   |

| Line Regulation<br>5.5 V < V <sub>SUP</sub> < 27 V, I <sub>DD</sub> = 10 mA | LR2                  | -    | 10  | 25  | mV   |

| Load Regulation<br>1 mA < I <sub>IDD</sub> < 200 mA                         | LD                   | -    | 25  | 75  | mV   |

| Thermal stability<br>V <sub>SUP</sub> = 13.5 V, I = 100 mA                  | THERMS               | -    | 5.0 | -   | mV   |

| V2 Output Voltage<br>I2 from 2.0 to 200 mA<br>5.5 V < V <sub>SUP</sub> < 27 V                                  | V2                 | 0.99 | 1.0 | 1.01 | V <sub>DD1</sub> |

|----------------------------------------------------------------------------------------------------------------|--------------------|------|-----|------|------------------|

| I2 output current (for information only)<br>Depending on the external ballast transistor                       | 12                 | 200  | -   | -    | mA               |

| V2 CTRL sink current capability                                                                                | 12 <sub>CTRL</sub> | 10   | -   | -    | mA               |

| V2LOW flag threshold                                                                                           | V2L <sub>TH</sub>  | 3.75 | 4.0 | 4.25 | V                |

| Internal V2 Supply Current (CAN and SBC in Normal Mode). TX = $5.0 \text{ V}$ , CAN in Recessive State         | I <sub>V2RS</sub>  | 3.8  | 5.6 | 6.8  | mA               |

| Internal V2 Supply Current (CAN and SBC in Normal Mode). TX = $0.0 \text{ V}$ , No Load, CAN in Dominant State | I <sub>V2DS</sub>  | 4.0  | 5.8 | 7.0  | mA               |

| Internal V2 Supply Current (CAN in Receive Only Mode, SBC in Normal mode). $V_{SUP}$ = 12 V                    | I <sub>V2R</sub>   |      | 80  | 120  | μΑ               |

| Internal V2 Supply Current (CAN in Bus TermVbat mode, SBC in normal mode), $V_{SUP}$ = 12 V                    | I <sub>V2BT</sub>  |      | 35  | 60   | μΑ               |

Notes

15. Selectable by SPI

16. Guaranteed by design

17. V2 TRACKING VOLTAGE REGULATOR - V2 specification with external capacitor

- option 1: C  $\ge$  22  $\mu$ F and ESR < 10 ohm. Using a resistor of 2 kohm or less between the base and emitter of the external PNP is recommended.

- option2: 1.0  $\mu$ F < C < 22  $\mu$ F and ESR < 10 ohm. In this case depending on the ballast transistor gain an additional resistor and capacitor network between emitter and base of PNP ballast transistor might be required. Refer to Freescale application information or contact your local technical support.

- option 3: 10uF < C < 22uF ESR > 0.2 ohms: a resistor of 2 kohm or less is required between the base and emitter of the external PNP.

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                                                        | Symbol                             | Min                   | Тур  | Max                    | Unit     |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|------|------------------------|----------|

| LOGIC OUTPUT PINS (MISO)                                                                                           |                                    | 1 1                   |      |                        | I        |

| Low Level Output Voltage<br>I <sub>OUT</sub> = 1.5 mA                                                              | V <sub>OL</sub>                    | -                     | -    | 1.0                    | V        |

| High Level Output Voltage<br>I <sub>OUT</sub> = -250 μA                                                            | V <sub>OH</sub>                    | V <sub>DD1-0.9</sub>  | -    | -                      | V        |

| Tri-state MISO Leakage Current<br>0.0 V < V <sub>miso</sub> < V <sub>DD</sub>                                      | I <sub>HZ</sub>                    | -2.0                  | -    | +2.0                   | μΑ       |

| LOGIC INPUT PINS (MOSI, SCLK, CS)                                                                                  |                                    | 1 1                   |      |                        | I        |

| High Level Input Voltage                                                                                           | V <sub>IH</sub>                    | 0.7V <sub>DD1</sub>   | -    | V <sub>DD1</sub> +0.3V |          |

| Low Level Input Voltage                                                                                            | VIL                                | -0.3                  | -    | 0.3 V <sub>DD1</sub>   | V        |

| Input Current on $\overline{CS}$<br>V <sub>I</sub> = 4.0 V<br>V <sub>I</sub> = 1.0 V                               | l <sub>iH</sub><br>l <sub>iL</sub> | -100                  | -    | -20                    | μΑ       |

| Low Level Input Current $\overline{CS}$<br>V <sub>I</sub> = 1.0 V                                                  | I <sub>IL</sub>                    | -100                  | -    | -20                    | μΑ       |

| MOSI, SCLK Input Current<br>0.0 < V <sub>IN</sub> < V <sub>DD</sub>                                                | IIN                                | -10                   | -    | 10                     | μΑ       |

| RESET PIN (RST)                                                                                                    |                                    | • •                   |      | 4                      | <u> </u> |

| High Level Output current<br>0.0 < V <sub>out</sub> < 0.7 V <sub>DD</sub>                                          | I <sub>ОН</sub>                    | -350                  | -250 | -150                   | μΑ       |

| Low Level Output Voltage ( $I_0 = 1.5 \text{ mA}$ )<br>5.5 v < V <sub>SUP</sub> < 27 V<br>1.0 V < V <sub>DD1</sub> | V <sub>OL</sub>                    | 0.0<br>0.0            | -    | 0.9<br>0.9             | V        |

| Reset pull down current                                                                                            | I <sub>PDW</sub>                   | 2.3                   | -    | 5.0                    | mA       |

| WATCHDOG PIN (WDOG)                                                                                                |                                    | 1 1                   |      |                        | I        |

| Low Level Output Voltage (I $_0$ = 1.5 mA)<br>5.5 V < V <sub>SUP</sub> < 27 V                                      | V <sub>OL</sub>                    | 0.0                   | -    | 0.9                    | V        |

| High Level Output Voltage (I <sub>0</sub> = -250 $\mu$ A)                                                          | V <sub>OH</sub>                    | V <sub>DD1</sub> -0.9 | -    | V <sub>DD1</sub>       | V        |

| INTERRUPT PIN (INT)                                                                                                | •                                  | . 1                   |      |                        |          |

| Low Level Output Voltage ( $I_0 = 1.5 \text{ mA}$ )                                                                | V <sub>OL</sub>                    | 0.0                   | -    | 0.9                    | V        |

| High Level Output Voltage ( $I_0 = -250 \ \mu A$ )                                                                 | V <sub>OH</sub>                    | V <sub>DD1</sub> -0.9 | -    | V <sub>DD1</sub>       | V        |

| HIGH-SIDE OUTPUT PIN (HS1)                                                                                         |                                    | · ·                   |      |                        | •        |

| R <sub>DSON</sub> at Tj = 25°C, and I <sub>OUT</sub> -150 mA<br>V <sub>SUP</sub> >9V                               | R <sub>DSON25</sub>                | -                     | -    | 2.5                    | Ohms     |

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                                                         | Symbol                | Min               | Тур                | Мах               | Unit |

|---------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|--------------------|-------------------|------|

| $R_{DSON}$ at Tj = 125°C, and $I_{OUT}$ -150 mA $V_{SUP}$ > 9.0 V                                                   | R <sub>DSON125</sub>  | -                 | -                  | 5.0               | Ohms |

| R <sub>DSON</sub> at Tj = 125°C, and I <sub>OUT</sub> -120 mA<br>5.5 V < V <sub>SUP</sub> < 9.0 V                   | R <sub>DON125-2</sub> | -                 | 4.0                | 5.5               | Ohms |

| Output current limitation                                                                                           | I <sub>LIM</sub>      | 160               | -                  | 500               | mA   |

| Over temperature Shutdown                                                                                           | O <sub>VT</sub>       | 155               | -                  | 190               | °C   |

| Leakage current                                                                                                     | I <sub>LEAK</sub>     | -                 | -                  | 10                | μA   |

| Output Clamp Voltage at I <sub>OUT</sub> = -1.0 mA <sup>(18)</sup><br>no inductive load drive capability            | V <sub>CL</sub>       | -1.5              | -                  | -0.3              | V    |

| INPUT PINS (L0 AND L1)                                                                                              |                       |                   |                    | I                 | 1    |

| L0 Negative Switching Threshold<br>$5.5 V < V_{SUP} < 6.0 V$<br>$6.0 V < V_{SUP} < 18 V$<br>$18 V < V_{SUP} < 27 V$ | V <sub>THON</sub>     | 1.7<br>2.0<br>2.0 | 2.0<br>2.4<br>2.5  | 3.0<br>3.0<br>3.1 | V    |

| L0 Positive Switching Threshold<br>$5.5 V < V_{SUP} < 6.0 V$<br>$6.0 V < V_{SUP} < 18 V$<br>$18 V < V_{SUP} < 27 V$ | V <sub>THOP</sub>     | 2.2<br>2.5<br>2.5 | 2.75<br>3.4<br>3.5 | 4.0<br>4.0<br>4.1 | V    |

| L1 Negative Switching Threshold<br>$5.5 V < V_{SUP} < 6.0 V$<br>$6.0 V < V_{SUP} < 18 V$<br>$18 V < V_{SUP} < 27 V$ | V <sub>TH1N</sub>     | 2.0<br>2.5<br>2.7 | 2.5<br>3.0<br>3.2  | 3.0<br>3.7<br>3.8 | V    |

| L1 Positive Switching Threshold<br>$5.5 V < V_{SUP} < 6.0 V$<br>$6.0 V < V_{SUP} < 18V$<br>$18 V < V_{SUP} < 27 V$  | V <sub>TH1P</sub>     | 2.7<br>3.0<br>3.5 | 3.3<br>4.0<br>4.2  | 3.8<br>4.7<br>4.8 | V    |

| Hysteresis<br>5.5 V < V <sub>SUP</sub> < 27 V                                                                       | V <sub>HYST</sub>     | 0.6               | 1.0                | 1.3               | V    |

| Input current                                                                                                       | I <sub>IN</sub>       | -10               | -                  | 10                | μΑ   |

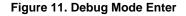

#### CAN MODULE SPECIFICATION (TX, RX, CANH, CANL, RTH, AND RTL)

| DC Voltage On Pins TX, RX     | V <sub>LOGIC</sub> | -0.3 | V <sub>DD1</sub> | + 0.3 | V |

|-------------------------------|--------------------|------|------------------|-------|---|

| DC voltage at V2 (V2INT)      | V2 <sub>INT</sub>  | 0.0  | 5.2              | 25    | V |

| DC Voltage On Pins CANH, CANL | V <sub>BUS</sub>   | -20  | +2               | 7     | V |

Notes

-0.2 V <  $V_{IN}$  < 40 V

18. Refer to HS1 negative maximum rating voltage limitation of -0.2V.

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                                                    | Symbol                               | Min                      | Тур          | Мах                          | Unit |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------|--------------|------------------------------|------|

| Transient Voltage At Pins CANH, CANL 0.0 < V <sub>2-INT</sub> < 5.5 V; V <sub>SUP</sub> $\geq$ 0.0; T < 500 ms | V <sub>CANH</sub> /V <sub>CANL</sub> | -40                      |              | 40                           | V    |

| Transient Voltage On Pins CANH, CANL (Coupled Through 1.0 nF Capacitor)                                        | V <sub>TR</sub>                      | -150                     |              | 100                          | V    |

| Detection Threshold For Short-circuit To Battery Voltage<br>(Term VBAT Mode) MC33889B                          | V <sub>CANH</sub>                    | V <sub>SUP</sub> /2+3    |              | V <sub>SUP</sub> /2+5        | V    |

| Detection Threshold For Short-circuit To Battery Voltage<br>(Term VBAT Mode) MC33889D                          | V <sub>CANH</sub>                    | V <sub>SUP</sub> /2+3    |              | V <sub>SUP</sub> /<br>2+4.55 | V    |

| DC Voltage On Pins RTH, RTL                                                                                    | V <sub>RTL</sub> , V <sub>RTH</sub>  | -0.3                     |              | +27                          | V    |

| Transient Voltage At Pins RTH, RTL 0.0 < V <sub>2-INT</sub> < 5.5 V; V <sub>SUP</sub> $\ge$ 0.0; T < 500 ms    | V <sub>RTH</sub> /V <sub>RTL</sub>   | -0.3                     |              | 40                           | V    |

| RANSMITTER DATA PIN (TX)                                                                                       |                                      | · · · · ·                |              |                              |      |

| High Level Input Voltage                                                                                       | V <sub>IH</sub>                      | 0.7*V <sub>2</sub>       |              | V <sub>2</sub> +0.3V         | V    |

| Low Level Input Voltage                                                                                        | V <sub>IL</sub>                      | -0.3                     |              | 0.3 * V <sub>2</sub>         | V    |

| TX High Level Input Current ( $V_1 = 4.0 V$ )                                                                  | I <sub>TXH</sub>                     | -100                     | -50          | -25                          | μA   |

| TX Low Level Input Current (V <sub>I</sub> = 1.0 V)                                                            | I <sub>TXL</sub>                     | -100                     | -50          | -25                          | μA   |

| RECEIVE DATA PIN (RX)                                                                                          |                                      |                          |              |                              |      |

| High Level Output Voltage RX ( $I_0 = -250 \mu A$ )                                                            | V <sub>OH</sub>                      | V <sub>2-INT</sub> - 0.9 |              | V <sub>2-INT</sub>           | V    |

| Low Level Output Voltage (I <sub>0</sub> = 1.5 mA)                                                             | V <sub>OL</sub>                      | 0.0                      |              | 0.9                          | V    |

| CAN HIGH AND CAN LOW PINS (CANH, CANL)                                                                         |                                      |                          |              | •                            |      |

| Differential Receiver, Recessive To Dominant Threshold (By Definition, $V_{DIFF} = V_{CANH} - V_{CANL}$ )      | V <sub>DIFF1</sub>                   |                          |              |                              | V    |

| For 33889D<br>For 33889B                                                                                       |                                      | -3.5<br>-3.2             | -3.0<br>-2.6 | -2.5<br>-2.1                 |      |

| Differential Receiver, Dominant To Recessive Threshold (Bus Failures 1, 2, 5)                                  | V <sub>DIFF2</sub>                   |                          |              |                              | V    |

| For 33889D<br>For 33889B                                                                                       |                                      | -3.5<br>-3.2             | -3.0<br>-2.6 | -2.5<br>-2.1                 |      |

| CANH Recessive Output Voltage<br>TX = 5.0 V; R <sub>(RTH)</sub> < 4.0 k                                        | V <sub>CANH</sub>                    |                          |              | 0.2                          | V    |

| CANL Recessive Output Voltage<br>TX = 5.0 V; $R_{(RTL)} < 4.0 $ k                                              | V <sub>CANL</sub>                    | V <sub>2-INT</sub> - 0.2 |              |                              | V    |

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                                                   | Symbol                                     | Min                  | Тур       | Мах             | Unit |

|---------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|-----------|-----------------|------|

| CANH Output Voltage, Dominant<br>TX = 0.0 V; $I_{CANH}$ = -40 mA; Normal Operating Mode <sup>(19)</sup>       | V <sub>CANH</sub>                          | V <sub>2</sub> - 1.4 |           |                 | V    |

| CANL Output Voltage, Dominant<br>TX = 0.0 V; I <sub>CANL</sub> = 40 mA; Normal Operating Mode <sup>(19)</sup> | V <sub>CANL</sub>                          |                      |           | 1.4             | V    |

| CANH Output Current ( $V_{CANH} = 0$ ; TX = 0.0)<br>For 33889D<br>For 33889B                                  | ICANH                                      | 50<br>50             | 100<br>75 | 130<br>110      | mA   |

| CANL Output Current ( $V_{CANL} = 14 V$ ; TX = 0.0)<br>For 33889D<br>For 33889B                               | ICANL                                      | 50<br>50             | 140<br>90 | 170<br>135      | mA   |

| Detection Threshold For Short-circuit To Battery Voltage (Normal Mode)                                        | V <sub>CANH</sub> , V <sub>CANL</sub>      | 7.3                  | 7.9       | 8.9             | V    |

| Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode), MC33889B                           | VcanH                                      | Vsup/2+3             |           | Vsup/2+5        | V    |

| Detection Threshold For Short-circuit To Battery Voltage (Term VBAT Mode), MC33889D                           | VcanH                                      | Vsup/2+3             |           | Vsup/<br>2+4.55 | V    |

| CANH Output Current (Term $V_{BAT}$ Mode; $V_{CANH}$ = 12 V, Failure3)                                        | I <sub>CANH</sub>                          |                      | 5.0       | 10              | μΑ   |

| CANL Output Current (Term $V_{BAT}$ Mode; $V_{CANL} = 0.0$ V; $V_{BAT} = 12$ V, Failure 4)                    | I <sub>CANL</sub>                          |                      | 0.0       | 2.0             | μA   |

| CANL Wake-Up Voltage Threshold                                                                                | V <sub>WAKE,L</sub>                        | 2.5                  | 3.0       | 3.9             | V    |

| CANH Wake-Up Voltage Threshold                                                                                | V <sub>WAKE,H</sub>                        | 1.2                  | 2.0       | 2.7             | V    |

| Wake-Up Threshold Difference (Hysteresis)                                                                     | V <sub>WAKEL</sub> -<br>V <sub>WAKEH</sub> | 0.2                  |           |                 | V    |

| CANH Single Ended Receiver Threshold (Failures 4, 6, 7)                                                       | V <sub>SE, CANH</sub>                      | 1.5                  | 1.85      | 2.15            | V    |

| CANL Single Ended Receiver Threshold (Failures 3, 8)                                                          | V <sub>SE, CANL</sub>                      | 2.8                  | 3.05      | 3.4             | V    |

| CANL Pull Up Current (Normal Mode)                                                                            | I <sub>CANL,PU</sub>                       | 45                   | 75        | 90              | μA   |

| CANH Pull Down Current (Normal Mode)                                                                          | I <sub>CANH,PD</sub>                       | 45                   | 75        | 90              | μΑ   |

| Receiver Differential Input Impedance CANH / CANL                                                             | R <sub>DIFF</sub>                          | 100                  |           | 300             | kohm |

| Differential Receiver Common Mode Voltage Range <sup>(20)</sup>                                               | V <sub>COM</sub>                           | -10                  |           | 10              | V    |

| CANH To Ground Capacitance                                                                                    | C <sub>CANH</sub>                          |                      |           | 50              | pF   |

| CANL To Ground Capacitance                                                                                    | C <sub>CANL</sub>                          |                      |           | 50              | pF   |

| C <sub>CANL</sub> to C <sub>CANH</sub> Capacitor Difference                                                   | DC <sub>CAN</sub>                          |                      |           | 10              | pF   |

| CAN Driver Thermal Shutdown                                                                                   | t <sub>CSD</sub>                           | 150                  | 160       |                 | °C   |

Notes

19. For MC33889B, after 128 pulses on TX and no bus failure.

20. Guaranteed by design

Characteristics noted under conditions - Vsup From 5.5 V to 18 V and TJ from -40°C to 125°C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Description                                                                             | Symbol           | Min | Тур  | Мах | Unit |

|-----------------------------------------------------------------------------------------|------------------|-----|------|-----|------|

| BUS TERMINATION PINS (RTH, RTL)                                                         |                  |     |      |     |      |

| RTL to V2 Switch On Resistance<br>(I <sub>OUT</sub> < -10 mA; Normal Operating Mode)    | R <sub>RTL</sub> | 10  | 30   | 90  | ohms |

| RTL to BAT Switch Series Resistance (term $V_{BAT}$ Mode)                               | R <sub>RTL</sub> | 8.0 | 12.5 | 20  | kohm |

| RTH To Ground Switch On Resistance (I <sub>OUT</sub> < 10 mA;<br>Normal Operating Mode) | R <sub>RTH</sub> | 10  | 30   | 90  | ohm  |

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### Table 5. Dynamic Electrical Characteristics

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40°C to 150°C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Conditions | Symbol | Min | Тур | Max | Unit |

|------------|--------|-----|-----|-----|------|

|------------|--------|-----|-----|-----|------|

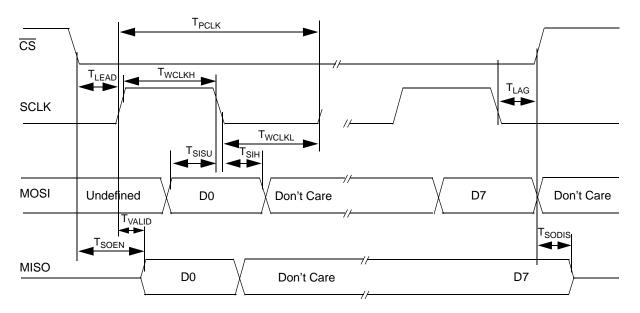

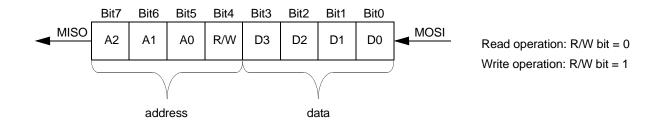

### DIGITAL INTERFACE TIMING (SCLK, CS, MOSI, MISO)

| SPI operation frequency                                                                                                                         | FREQ                                    | -   | -   | 4.0      | MHz |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----|----------|-----|

| SCLK Clock Period                                                                                                                               | t <sub>PCLK</sub>                       | 250 | -   | -        | ns  |

| SCLK Clock High Time                                                                                                                            | t <sub>WSCLKH</sub>                     | 125 | -   | -        | ns  |

| SCLK Clock Low Time                                                                                                                             | t <sub>WSCLKL</sub>                     | 125 | -   | -        | ns  |

| Falling Edge of $\overline{\text{CS}}$ to Rising<br>Edge of SCLK                                                                                | t <sub>ILEAD</sub>                      | 100 | 50  | -        | ns  |

| Falling Edge of SCLK to Rising Edge of $\overline{\text{CS}}$                                                                                   | t <sub>LAG</sub>                        | 100 | 50  | -        | ns  |

| MOSI to Falling Edge of SCLK                                                                                                                    | tsisu                                   | 40  | 25  | -        | ns  |

| Falling Edge of SCLK to MOSI                                                                                                                    | t <sub>SIH</sub>                        | 40  | 25  | -        | ns  |

| MISO Rise Time (CL = 220 pF)                                                                                                                    | t <sub>RSO</sub>                        | -   | 25  | 50       | ns  |

| MISO Fall Time (CL = 220 pF)                                                                                                                    | t <sub>fSO</sub>                        | -   | 25  | 50       | ns  |

| Time from Falling or Rising Edges of CS to:<br>- MISO Low Impedance<br>- MISO High Impedance                                                    | <sup>t</sup> soen<br><sup>t</sup> sodis | -   | -   | 50<br>50 | ns  |

| Time from Rising Edge of SCLK to MISO Data Valid 0.2 V1 $\leq$ SO $\geq$ 0.8 V1, $C_L$ = 200 pF                                                 | <sup>t</sup> valid                      | -   | -   | 50       | ns  |

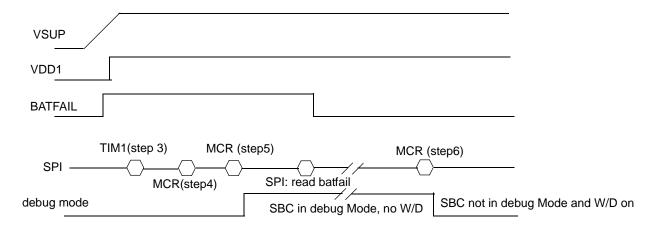

| Delay between CS low to high transition (at end of SPI stop<br>command) and Stop or sleep mode activation <sup>(21)</sup><br>detected by V2 off | T <sub>CS-STOP</sub>                    | 18  | -   | 34       | μs  |

| Interrupt low level duration<br>SBC in stop mode                                                                                                | T <sub>INT</sub>                        | 7.0 | 10  | 13       | μs  |

| Internal oscillator frequency<br>All modes except Sleep and Stop <sup>(21)</sup>                                                                | O <sub>SC-F1</sub>                      | -   | 100 | -        | kHz |

Notes

21. Guaranteed by design

| Conditions                                                                     | Symbol              | Min  | Тур  | Мах   | Unit |

|--------------------------------------------------------------------------------|---------------------|------|------|-------|------|

| nternal low power oscillator frequency<br>Sleep and Stop modes <sup>(22)</sup> | O <sub>SC-F2</sub>  | -    | 100  | -     | kHz  |

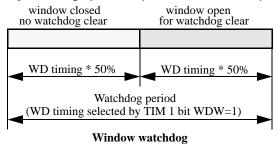

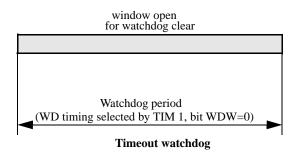

| Watchdog period 1<br>Normal and standby modes                                  | W <sub>D1</sub>     | 8.58 | 9.75 | 10.92 | ms   |

| Watchdog period 2<br>Normal and standby modes                                  | W <sub>D2</sub>     | 39.6 | 45   | 50.4  | ms   |

| Watchdog period 3<br>Normal and standby modes                                  | W <sub>D3</sub>     | 88   | 100  | 112   | ms   |

| Watchdog period 4<br>Normal and standby modes                                  | W <sub>D4</sub>     | 308  | 350  | 392   | ms   |

| Watchdog period accuracy<br>Normal and standby modes                           | F1 <sub>ACC</sub>   | -12  | -    | 12    | %    |

| Normal request mode timeout<br>Normal request mode                             | NR <sub>TOUT</sub>  | 308  | 350  | 392   | ms   |

| Watchdog period 1 - stop<br>Stop mode                                          | WD1 <sub>STOP</sub> | 6.82 | 9.75 | 12.7  | ms   |

| Watchdog period 2- stop<br>Stop mode                                           | WD2 <sub>STOP</sub> | 31.5 | 45   | 58.5  | ms   |

| Watchdog period 3 - stop<br>Stop mode                                          | WD3 <sub>STOP</sub> | 70   | 100  | 130   | ms   |

| Watchdog period 4 - stop<br>Stop mode                                          | WD4 <sub>STOP</sub> | 245  | 350  | 455   | ms   |

| Stop mode watchdog period accuracy<br>Stop mode                                | F2 <sub>ACC</sub>   | -30  | -    | 30    | %    |

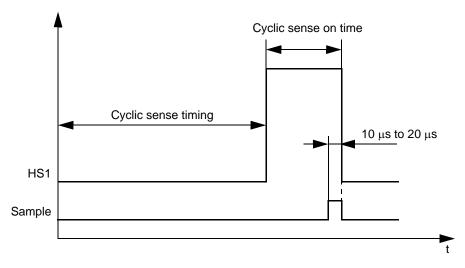

| Cyclic sense/FWU timing 1<br>Sleep and stop modes                              | CSFWU1              | 3.22 | 4.6  | 5.98  | ms   |

| Cyclic sense/FWU timing 2<br>Sleep and stop modes                              | CSFWU2              | 6.47 | 9.25 | 12    | ms   |

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40°C to 150°C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

Notes

22. Guaranteed by design

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40°C to 150°C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Conditions                                                                                               | Symbol               | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Cyclic sense/FWU timing 3<br>Sleep and stop modes                                                        | CSFWU3               | 12.9 | 18.5 | 24   | ms   |

| Cyclic sense/FWU timing 4<br>Sleep and stop modes                                                        | CSFWU4               | 25.9 | 37   | 48.1 | ms   |

| Cyclic sense/FWU timing 5<br>Sleep and stop modes                                                        | CSFWU5               | 51.8 | 74   | 96.2 | ms   |

| Cyclic sense/FWU timing 6<br>Sleep and stop modes                                                        | CSFWU6               | 66.8 | 95.5 | 124  | ms   |

| Cyclic sense/FWU timing 7<br>Sleep and stop modes                                                        | CSFWU7               | 134  | 191  | 248  | ms   |

| Cyclic sense/FWU timing 8<br>Sleep and stop modes                                                        | CSFWU8               | 271  | 388  | 504  | ms   |

| Cyclic sense On time<br>in sleep and stop modes                                                          | t <sub>ON</sub>      | 200  | 300  | 400  | μS   |

| Cyclic sense/FWU timing accuracy<br>in sleep and stop mode                                               | t <sub>ACC</sub>     | -30  | -    | +30  | %    |

| Delay between SPI command and HS1 turn on $^{(23)}$<br>Normal or standby mode, V <sub>SUP</sub> > 9.0 V  | t <sub>S-HSON</sub>  | -    | -    | 22   | μS   |

| Delay between SPI command and HS1 turn off $^{(23)}$<br>Normal or standby mode, V <sub>SUP</sub> > 9.0 V | ts-hsoff             | -    | -    | 22   | μs   |

| Delay between SPI and V2 turn on <sup>(23)</sup><br>Standby mode                                         | t <sub>S-V2ON</sub>  | 9.0  | -    | 25   | μS   |

| Delay between SPI and V2 turn off <sup>(23)</sup><br>Normal modes                                        | t <sub>S-V2OFF</sub> | 9.0  | -    | 25   | μS   |

| Delay between Normal Request and Normal mode, after<br>W/D trigger command<br>Normal request mode        | t <sub>S-NR2N</sub>  | 15   | 35   | 70   | μS   |

Notes

23. State Machine Timing - Delay starts at rising edge of CS (end of SPI command) and start of Turn on or Turn off of HS1 or V2.

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40°C to 150°C unless otherwise noted. Typical values<br/>noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.ConditionsSymbolMinTypMaxUnit

| Conditions                                                                                                                      | Symbol                | Min | Тур | Мах | Unit |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| Delay between SPI and "CAN normal mode"<br>SBC Normal mode <sup>(24)</sup>                                                      | <sup>t</sup> s-cann   | -   | -   | 10  | μs   |

| Delay between SPI and "CAN sleep mode"<br>SBC Normal mode <sup>(24)</sup>                                                       | ts-cans               | -   | -   | 10  | μS   |

| Delay between CS wake-up (CS low to high) and SBC<br>normal request mode (V <sub>DD1</sub> on & reset high)<br>SBC in stop mode | t <sub>W-CS</sub>     | 15  | 40  | 90  | μs   |

| Delay between CS wake-up (CS low to high) and first<br>accepted SPI command<br>SBC in stop mode                                 | <sup>t</sup> w-spi    | 90  | -   | -   | μs   |

| Delay between INT pulse and 1st SPI command accepted<br>In stop mode after wake-up                                              | t <sub>S-1STSPI</sub> | 20  | -   | -   | μs   |

| Delay between two SPI messages addressing the same<br>register<br>For 33889D only                                               | t2 <sub>SPI</sub>     | 25  | _   | _   | μS   |

|                                                                                                                                 |                       | 25  | -   | -   |      |

#### INPUT PINS (L0 AND L1)

Γ

| Wake-up Filter Time (enable/disable option on L0 input) | t <sub>WUF</sub> | 8.0 | 20 | 38 | μS | Ì |

|---------------------------------------------------------|------------------|-----|----|----|----|---|

| (If filter enabled)                                     |                  |     |    |    |    |   |

#### PIN AC CHARACTERISTICS (CANH, CANL, RX, TX)

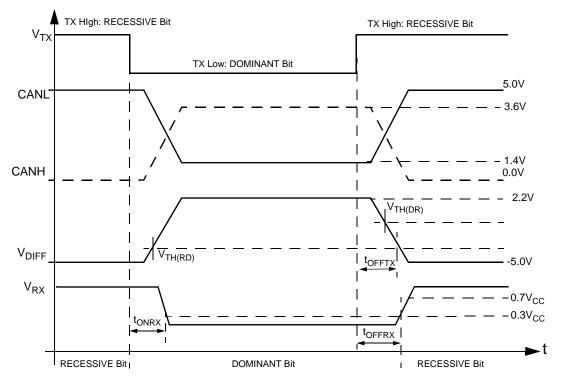

| CANL and CANH Slew Rates (25% to 75% CAN signal). <sup>(25)</sup><br>Recessive to Dominant state<br>Dominant to Recessive state | <sup>t</sup> SLDR  | 2.0<br>2.0 |            | 8.0<br>9.0 | V/µs |

|---------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|------------|------------|------|

| Propagation Delay TX to RX Low40°C < T $\leq$ 25°C. <sup>(26)</sup> TX to RX Low. 25°C < T < 125°C. <sup>(26)</sup>             | tonrx              |            | 1.2<br>1.1 | 1.6<br>1.8 | μS   |

| Propagation Delay TX to RX High. (26)                                                                                           | <sup>t</sup> OFFRX |            | 1.8        | 2.2        | μs   |

Notes

24. Guaranteed by design

25. Dominant to recessive slew rate is dependant upon the bus load characteristics.

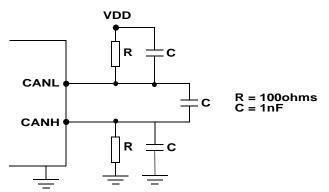

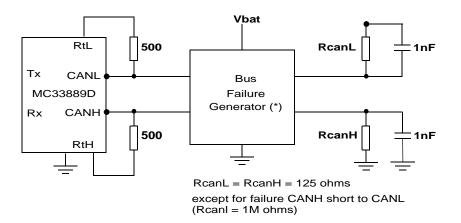

26. AC Characteristics measured according to schematic Figure 4

$V_{SUP}$  From 5.5 V to 18 V, V2INT from 4.75 to 5.25 V and  $T_J$  from -40°C to 150°C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Conditions                                                                                                                           | Symbol                      | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|------|------|------|

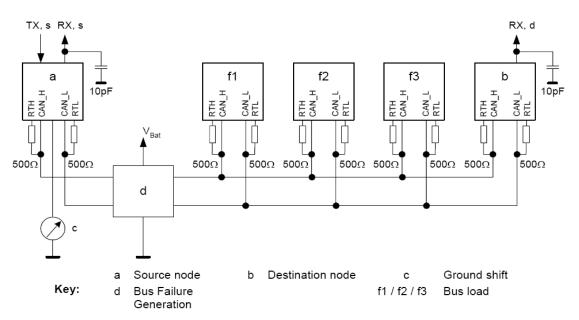

| Loop time Tx to Rx, no bus failure, MC33889D only ((27),<br>Figure 5) (ISO ICT test series 10)                                       | t <sub>looprd</sub>         |      |      |      | μs   |

| Tx high to low transition (dominant edge)                                                                                            |                             |      | 1.15 | 1.5  |      |

| Tx low to high transition (recessive edge)                                                                                           |                             |      | 1.45 | 1.5  |      |

| Loop time Tx to Rx, with bus failure, MC33889D only ((27),<br>Figure 6) (ISO ICT test series 10)                                     | t <sub>LOOPRD-F</sub>       |      |      |      | μS   |

| Tx high to low transition (dominant edge)                                                                                            |                             |      | -    | 1.9  |      |

| Tx low to high transition (recessive edge)                                                                                           |                             |      | -    | 1.9  |      |

| Loop time Tx to Rx, with bus failure and +-1.5V gnd shift, 5<br>nodes network, MC33889D,((28), Figure 7, ISO ICT tests<br>series 11) | <sup>t</sup> looprd/dr-f+gs |      |      | 3.6  | μS   |

| Min. Dominant Time For Wake-up On CANL or CANH<br>(Term Vbat; V <sub>SUP</sub> = 12V) Guaranteed by design.                          | t <sub>WAKE</sub>           |      |      |      | μS   |

| MC33889B                                                                                                                             |                             |      | 30   |      |      |

| MC33889D                                                                                                                             |                             | 8.0  | 16   | 30   |      |

| Failure 3 Detection Time (Normal Mode)                                                                                               | t <sub>DF3</sub>            | 10   | 30   | 80   | μS   |

| Failure 3 Recovery Time (Normal Mode)                                                                                                | t <sub>DR3</sub>            |      | 160  |      | μS   |

| Failure 6 Detection Time (Normal Mode)                                                                                               | t <sub>DF6</sub>            | 50   | 200  | 500  | μS   |

| Failure 6 Recovery Time (Normal Mode)                                                                                                | t <sub>DR6</sub>            | 150  | 200  | 1000 | μS   |

| Failure 4, 7 Detection Time (Normal Mode)                                                                                            | t <sub>DF47</sub>           | 0.75 | 1.5  | 4.0  | ms   |

| Failure 4, 7 Recovery Time (Normal Mode)                                                                                             | t <sub>DR47</sub>           | 10   | 30   | 60   | μS   |

| Failure 3a, 8 Detection Time (Normal Mode)                                                                                           | t <sub>DF8</sub>            | 0.75 | 1.7  | 4.0  | ms   |

| Failure 3a, 8 Recovery Time (Normal Mode)                                                                                            | tT <sub>DR8</sub>           | 0.75 | 1.5  | 4.0  | ms   |

| Failure 4, 7 Detection Time, (Term $V_{BAT}$ ; $V_{SUP}$ = 12 V)                                                                     | t <sub>DR47</sub>           | 0.8  | 1.2  | 8.0  | ms   |