# Memory/Clock Drivers

## MH0013/MH0013C two phase MOS clock driver

### general description

The MH0013/MH0013C is a general purpose clock driver that is designed to be driven by DTL or TTL line drivers or buffers with high output current capability. It will provide fixed width clock pulses for both high threshold and low threshold MOS devices. Two external input coupling capacitors set the pulse width maximum, below which the output pulse width will closely follow the input pulse width or logic control of output pulse width may be obtained by using larger value input capacitors and no input resistors.

### features

- High Output Voltage Swings-up to 30V

- High Output Current Drive Capability-up to 500 mA

- High Repetition Rate-up to 5.0 MHz

- Pin Compatible with the MH0009/MH0009C

- "Zero" Quiescent Power

#### Order Number MH0013G or MH0013CG See Package 6

### typical applications

### absolute maximum ratings

| (V <sup>+</sup> – V <sup>-</sup> ) Voltage Differential | 30V             |

|---------------------------------------------------------|-----------------|

| Input Current (Pin 2, 4, 6 or 8)                        | ±75 mA          |

| Peak Output Current                                     | ±600 mA         |

| Power Dissipation (Figure 7)                            | 1.5W            |

| Storage Temperature                                     | -65°C to +150°C |

| Operating Temperature MH0013                            | –55°C to +125°C |

| MH0013C                                                 | 0°C to +85°C    |

| Lead Temperature (Soldering, 10 sec 1/16" from Case     | e) 300°C        |

### electrical characteristics (Note 1 and Figure 8)

| PARAMETER                         | CONDITIONS                                                                                             | MIN      | ТҮР                                        | MAX                  | UNITS  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|----------|--------------------------------------------|----------------------|--------|

| Logical "0" Output Voltage        | I <sub>OUT</sub> = -50 mA I <sub>IN</sub> = 10 mA<br>I <sub>OUT</sub> = -10 mA I <sub>IN</sub> = 10 mA | V* - 3 0 | V <sup>+</sup> - 10<br>V <sup>+</sup> - 07 | V* - 0 5             | v<br>v |

| Logical "1" Output Voltage        | I <sub>OUT</sub> = 50 mA I <sub>IN</sub> = 10 mA                                                       |          | V <sup></sup> + 1 5                        | V <sup>-</sup> + 2 0 | v<br>v |

| Power Supply Leakage Current      | (V <sup>+</sup> - V <sup>-</sup> ) = 30V<br>I <sub>OUT</sub> = I <sub>IN</sub> = 0 mA                  |          | 10                                         | 100                  | μΑ     |

| Negative Input Voltage Clamp      | I <sub>IN</sub> = - 10 mA                                                                              | V" - 12  | V <sup>-</sup> - 0 8                       | L.                   | v      |

| <sup>t</sup> d ON                 |                                                                                                        |          | 20                                         | 35                   | ns     |

| t <sub>rise</sub>                 | C <sub>IN</sub> = 0 0022 μF                                                                            |          | 35                                         | 50                   | ns     |

| tdOFF (Note 2)                    | $R_{IN} = 0.0022 \mu^{\mu}$                                                                            |          | 30                                         | 60                   | ns     |

| t <sub>fall</sub> (Note 2)        | $C_{L} = 0.001 \mu\text{F}$                                                                            | 40       | 50                                         | 80 .                 | ns     |

| t <sub>fall</sub> (Note 3)        |                                                                                                        | 40       | 70                                         | 120                  | ns     |

| Pulse Width (50% to 50%) (Note 3) |                                                                                                        | 340      | 420                                        | 490                  | ns     |

| t <sub>rise</sub>                 | C <sub>IN</sub> = 500 pF                                                                               |          | 15                                         |                      | ns     |

| t <sub>fall</sub>                 | $R_{IN} = 0\Omega$                                                                                     | ,        | 20                                         |                      | ns     |

| Pulse Width (50% to 50%) (Note 3) | C <sub>L</sub> = 200 pF                                                                                |          | 110                                        |                      | ns     |

| Positive Output Voltage Swing     |                                                                                                        |          | V <sup>+</sup> - 0 7V                      |                      | v      |

| Negative Output Voltage Swing     |                                                                                                        |          | V <sup>-</sup> + 0 7V                      |                      | v      |

Note 1: Min/Max limits apply over guaranteed operating temperature range of -55°C to +125°C for MH0013 and 0°C to +85°C for MH0013C, with  $V^{-} = -20V$  and  $V^{+} = 0V$  unless otherwise specified. Typical values are for 25°C

Note 2: Parameter values apply for clock pulse width determined by input pulse width.

Note 3: Parameter values apply for input pulse width greater than output clock pulse width

#### TABLE I. Typical Drive Capability of One Half MH0013 at 70°C Ambient

| (V <sub>3</sub> - V <sub>2</sub> )<br>VOLTS | FREQUENCY<br>MHz | PULSE WIDTH | TYPICAL R <sub>IN</sub><br>Ω | TYPICAL C <sub>IN</sub><br>pF | OUTPUT DRIVE<br>CAPABILITY IN pF | RISE TIME<br>LIMIT ns <sup>2</sup> |

|---------------------------------------------|------------------|-------------|------------------------------|-------------------------------|----------------------------------|------------------------------------|

| 28                                          |                  |             |                              |                               | 50                               | -                                  |

| 20                                          | 40               | 100         | , 0                          | 750                           | 200                              | 7                                  |

| 16                                          |                  |             |                              |                               | 350                              | 10                                 |

| 28                                          |                  |             |                              |                               | 100                              | 5                                  |

| 20                                          | 20               | 200         | 10                           | 1600                          | 400                              | 14                                 |

| 16                                          |                  |             |                              |                               | 700                              | 19                                 |

| 28                                          | 1                |             |                              |                               | 400                              | 19                                 |

| 20                                          | 10               | 200         | 0                            | 2300                          | 1000                             | 34                                 |

| 16                                          | }                | ]           |                              |                               | 1700                             | 45                                 |

| 28                                          |                  |             |                              |                               | 2800                             | 130                                |

| 20                                          | 05               | 500         | 10                           | 4000                          | 5500                             | - 183                              |

| 16                                          | 1                | 1           | 1                            |                               | 9300                             | 248                                |

Note 1: Output load is the maximum load that can be driven at 70°C without exceeding the package rating under the given conditions.

Note 2: The rise time given is the minimum that can be used without exceeding the peak transient output current for the full rated output load.

### circuit operation

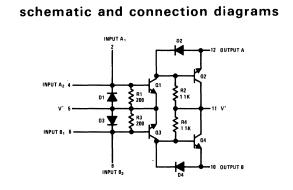

Input current forced into the base of Q1 through the coupling capacitor  $C_{1N}$  causes Q1 to be driven into saturation, swinging the output to  $V^{-} + V_{CE}$  (SAT) +  $V_{DIODE}$ .

When the input current has decayed, or has been switched, such that Q1 turns off, Q2 receives base

drive through R2, turning Q2 on. This supplies current to the load and the output swings positive to  $V^+ - V_{BE}$ .

It may "be noted that Q1 always switches off before Q2 begins to supply current; hence, high internal transient currents from V<sup>+</sup> to V<sup>-</sup> cannot occur.

MH0013/MH0013C

### pulse width

Maximum output pulse width is a function of the input driver characteristics and the coupling capacitance and resistance. After being turned on, the input current must fall from its initial value IIN peak to below the input threshold current  $I_{1\,N}\mbox{ min }\simeq V_{B\,E}/R\,l$  for the clock driver to turn off. For example, referring to the test circuit of Figure 8, the output pulse width, 50% to 50%, is given by

$$\begin{split} pw_{O\,U\,T} &\cong \frac{1}{2} \left( t_{r\,ise} + t_{fall} \right) \\ &+ R_O C_{I\,N} \, \ln \frac{I_{I\,N} \, peak}{I_{I\,N} \, min} \cong 400 \; ns. \end{split}$$

For operation with the input pulse shorter than the above maximum pulse width, the output pulse width will be directly determined by the input pulse width.

$pw_{OUT} = pw_{IN} + t_{dOFF} + t_{dON} + \frac{1}{2} (t_{fall} + t_{rise})$

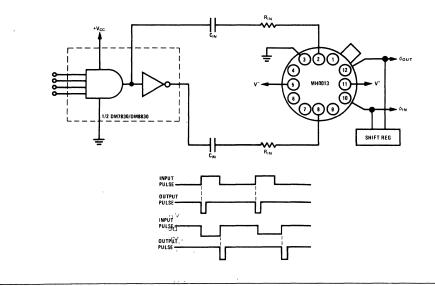

Typical maximum pulse width for various CIN and R<sub>IN</sub> values are given in Figure 6.

### fan-out calculation

The drive capability of the MH0013 is a function of system requirements, i.e., speed, ambient temperature, voltage swing, drive circuitry, and stray wiring capacity.

The following equations cover the necessary calculations to enable the fan-out to be calculated for any system condition. Some typical fan-outs for conditions are given in Table 1.

#### **Transient Current**

The maximum peak output current of the MH0013 is given as 600 mA. Average transient current required from the driver can be calculated from.

$$I = \frac{C_{L} (V^{+} - V^{-})}{T_{R}}$$

(1)

This can give a maximum limit to the load.

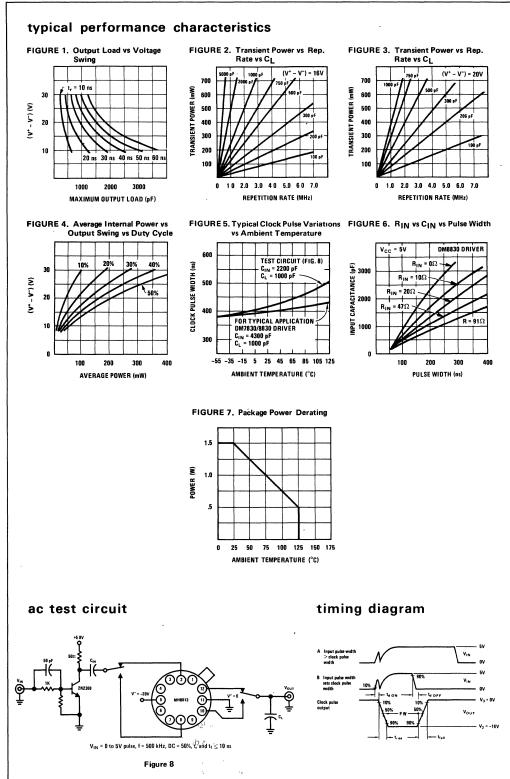

Figure 1 shows maximum voltage swing and capacitive load for various rise times

### 1. Transient Output Power

The average transient power (PAC) dissipated is equal to the energy needed to charge and discharge the output capacitive load (CL) multiplied by the frequency of operation (F)

$$P_{AC} = C_{L} \times (V^{+} - V^{-})^{2} \times F$$

(2)

Figures 2 and 3 show transient power for two different values of  $(V^+ - V^-)$  versus output load and frequency.

2. Internal Power

"O" State

Negligible (<3 mW)

"1" State

$$P_{INT} = \frac{(V^+ - V^-)^2}{R_2} \times Duty Cycle.$$

(3)

Figure 4 gives various values of internal power versus ouptut voltage and duty cycle.

#### 3 Input Power

The average input power is a function of the input current and duty cycle. Due to input voltage clamping, this power contribution is small and can therefore be neglected. At maximum duty cycle of 50%, at 25°C, the average input power is less than 10 mW per phase for  $R_{1\,N}\,C_{1\,N}$  controlled pulse widths For pulse widths much shorter than  $R_{1\,N}\,C_{1\,N}\,,$  and maximum duty cycle of 50%, input power could be as high as 30 mW, since I<sub>IN</sub> peak is maintained for the full duration of the pulse width

#### 4 Package Power Dissipation

Total Average Power = Transient Output Power + Internal Power + Input Power

#### Typical Example Calculation for One Half MH0013C

How many MM506 shift registers can be driven by an MH0013C driver at 1 MHz using a clock pulse width of 400 ns, rise time 30-50 ns and 16 volts amplitude over the temperature range 0-70°C?

### **Power Dissipation**

From the graph of power dissipation versus temperature, Figure 7, it can be seen that an MH0013C at 70°C can dissipate 1W without a heat sink, therefore, each half can dissipate 500 mW.

### **Transient Peak Current Limitation**

From Figure 1 (equation 1), it can be seen that at 16V and 30 ns, the maximum load that can be driven is limited to 1140 pF.

#### Average Internal Power

Figure 4 (equation 3) gives an average power of 102 mW at 16V 40% duty cycle. Input power will be a maximum of 8 mW

#### Transient Output Power

For one half of the MH0013C 500 mW = 102 mW + 8 mW

+ transient output power 390 mW = transient output power

Using Figure 2 (equation 2) at 16V, 1 MHz and 390 mW, each half of the MH0013C can drive a 1520 pF load. This is, however, in excess of the load derived from the transient current limitation (Figure 1, equation 1), and so a maximum load of 1140 pF would prevail.

From the data sheet for the MM506, the average clock pulse load is 80 pF. Therefore the number of devices, driven is  $\frac{1140}{80}$  or 14 registers.

For nonsymmetrical clock widths, drive capability is improved.