# **Memory/Clock Drivers**

### MH8808 dual high speed MOS clock driver

#### general description

The MH8808 is a high speed dual MOS clock driver intended to drive the two phases of a memory array of 500 pF per phase at rates up to 4 MHz. The design includes output current limiting for controlled rise and fall times, and thermal shutdown which protects the chip against excessive power dissipation or accidental output shorts. Two DTL/TTL compatible status outputs monitor clock outputs and provide a corresponding TTL logic level for status indication. Both direct and internally damped outputs are available for each phase to suit the particular application. It is ideally suited for driving MM5262 2k RAMs.

#### features

- High Speed: 18 ns typ delay and 20 ns typ rise and fall times with 500 pF load

- Current limited outputs ±450 mA typ

- Direct and damped outputs available

- Thermal shutdown protection

- TTL compatible status outputs

- 1W dissipation capability at 25°C T<sub>A</sub>

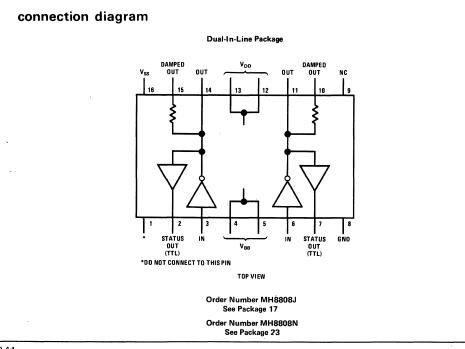

- 16 pin cavity dual-in-line package

- Output high level clamped to +5V

# absolute maximum ratings

| V <sub>SS</sub>                   | +7V          |

|-----------------------------------|--------------|

| V <sub>BB</sub> - V <sub>DD</sub> | 26V          |

| Total Power Dissipation (Note 1)  | 1W           |

| Operating Temperature Range       | 0°C to +70°C |

## electrical characteristics

The following apply for V<sub>BB</sub> = +7V, V<sub>SS</sub> = +5V, V<sub>DD</sub> = -15V, T<sub>A</sub> =  $25^{\circ}$ C unless otherwise stated

| PARAMETER                                  | CONDITIONS                                                                                                                    | MIN | MAX | UNITS   |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|

| Input Current                              | V <sub>IN</sub> = -9V (Note 2)                                                                                                |     | 10  | mA      |

| Output Low Voltage                         | I <sub>OUT</sub> = +1 mA, V <sub>IN</sub> = -10V<br>(Note 2)                                                                  | -14 |     | V       |

| Output High Voltage                        | I <sub>OUT</sub> = -1 mA, V <sub>IN</sub> = -14V                                                                              | 4 5 | 53  | v       |

| Status ''1'' Voltage                       | $I_{OUT} = -250 \mu A,  V_{IN} = -14 V$                                                                                       | 3   |     | v       |

| Status ''0'' Voltage                       | I <sub>OUT</sub> = 20 mA, V <sub>IN</sub> = -10V<br>(Note 2)                                                                  |     | 05  | v       |

| Output Leakage Current<br>Damping Resistor | V <sub>BB</sub> = +8 5V, V <sub>SS</sub> = 5V<br>V <sub>DD</sub> = -17 5V, V <sub>OUT</sub> = +8 5V<br>V <sub>IN</sub> = open | 4   | 100 | μA<br>Ω |

| I <sub>BB</sub>                            | V <sub>IN</sub> = -11 5V<br>V <sub>SS</sub> = +6 5V, V <sub>DD</sub> = -17 5V<br>V <sub>BB</sub> = +8 5V (Note 2)             |     | 32  | mA      |

| I <sub>SS</sub>                            | V <sub>IN</sub> = -11 5V<br>V <sub>SS</sub> = +6 5V, V <sub>DD</sub> = -17 5V<br>V <sub>BB</sub> = +8 5V (Note 2)             |     | 23  | mA      |

| I <sub>DD</sub>                            | V <sub>IN</sub> = -11 5V<br>V <sub>SS</sub> = +6 5V, V <sub>DD</sub> = -17 5V<br>V <sub>BB</sub> = +8 5V (Note 2)             |     | -55 | mA      |

| Output Rise Time                           | C <sub>L</sub> = 500 pF                                                                                                       |     | 26  | ns      |

| Output Fall Time                           | C <sub>L</sub> = 500 pF                                                                                                       |     | 26  | ns      |

| Delay to Negative-Going Output             | C <sub>L</sub> = 500 pF                                                                                                       | 7   | 22  | ns      |

| Delay to Positive-Going Output             | $C_{1} = 500  \text{pF}$                                                                                                      | 10  | 25  | ns      |

Note 1: Maximum junction temperature is +125°C. For operation above +25°C derate at +80°C/W  $\theta_{JA}$  for still air. Note 2: Test only one input high (more positive) at a time.

3