# MULTI-INNO TECHNOLOGY CO., LTD.

# **LCD MODULE SPECIFICATION**

Model: MI9664FK

| Revision      |  |

|---------------|--|

| Engineering   |  |

| Date          |  |

| Our Reference |  |

### DOCUMENT REVISION HISTORY

|                              |      | 1 0 1 1 1   |               |               |

|------------------------------|------|-------------|---------------|---------------|

| REVISION                     | DATE | DESCRIPTION | CHANGED<br>BY | CHECKED<br>BY |

| DOCUMENT REVISION FROM TO  A |      | DESCRIPTION |               |               |

|                              |      |             |               |               |

## **CONTENTS**

|     |                                          | <u>Page No</u> |

|-----|------------------------------------------|----------------|

| 1.  | GENERAL DESCRIPTION                      | 4              |

| 2.  | MECHANICAL SPECIFICATIONS                | 4              |

| 3.  | INTERFACE SIGNALS                        | 7              |

| 4.  | ABSOLUTE MAXIMUM RATINGS                 | 8              |

| 4.1 | ELECTRICAL MAXIMUM RATINGS – FOR IC ONLY | 8              |

| 4.2 | ENVIRONMENTAL CONDITION                  | 8              |

| 5.  | ELECTRICAL SPECIFICATIONS                | 9              |

| 5.1 | TYPICAL ELECTRICAL CHARACTERISTICS       | 9              |

| 5.2 | TIMING SPECIFICATIONS                    | 10             |

| 5.3 | POWER-UP/DOWN SEQUENCE                   | 14             |

| 6.  | ELECTRICAL & OPTICAL CHARACTERISTICS     | 15             |

| 7.  | CSTN PANEL INSPECTION SPECIFICATION      | 15             |

| 8.  | REMARK                                   | 17             |

### Preliminary Specification of LCD Module Type Model No.: MI9664FK

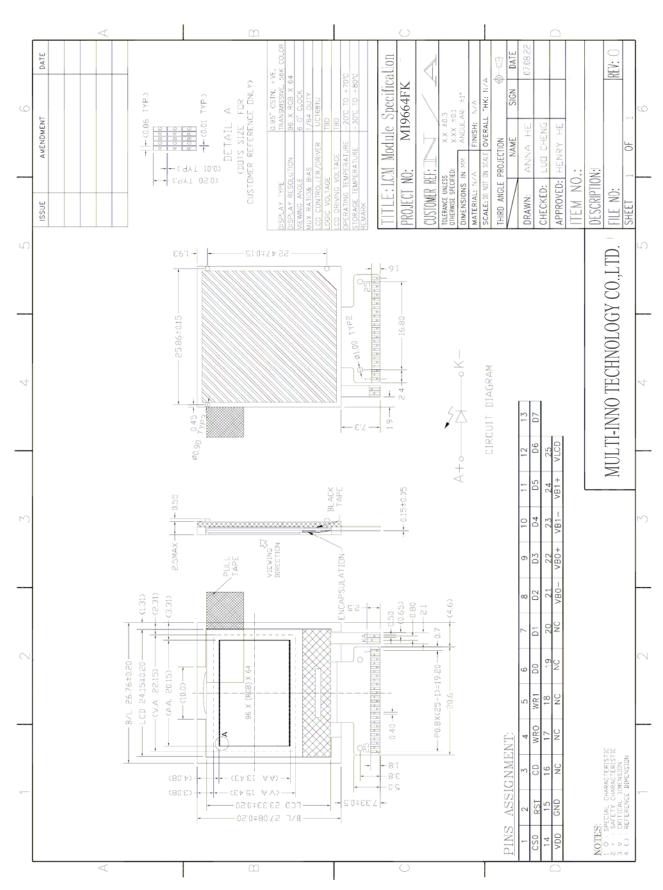

### 1. General Description

- 0.95", 96 x RGB x 64 dots 56K CSTN Negative transmissive dot matrix LCD module.

- Viewing angle: 6 o'clock.

- Driving scheme: 1/64 duty, 1/9 bias.

- Driving IC: 'ULTRACHIP' UC1681SGBB (COG) LCD controller / driver or equivalent.

- Data interface: 8080 system, 8-bit parallel bus.

- Logic voltage: 2.8V.

- Analog voltage: 2.8V.

- White LED backlight.

- Low power.

- FPC connection.

- "RoHS" compliance.

#### 2. Mechanical Specifications

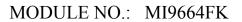

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

Table 1

| Parameter          |                     | Specifications                                                            | Unit |

|--------------------|---------------------|---------------------------------------------------------------------------|------|

| Outline dimensions |                     | 26.76(W) x 27.08(H) x 3.05(D)<br>(Exclude FPC and terminals of backlight) | mm   |

|                    | Viewing area        | 22.15(W) x 15.43(H)                                                       | mm   |

|                    | Active area         | 20.15(W) x 13.43(H)                                                       | mm   |

| CSTN               | Display format      | 96 x RGB x 64                                                             | dots |

| 96xRGBx64          | Color configuration | R.G.B. stripe                                                             | -    |

| 90xKGDx04          | Dot size            | 0.20 (RGB)(W) x 0.20 (H)                                                  | mm   |

|                    | Dot spacing         | 0.01 (W) x 0.01 (H)                                                       | mm   |

|                    | Dot pitch           | $0.21(RGB)(W) \times 0.21(H)$                                             | mm   |

| Weight             |                     | TBD                                                                       | gram |

Figure 1: Module Specification

Figure 2: Block Diagram

### 3. Interface signals

Table 2

| Pin No.   | Symbol       |             | Description                                                            |                  |                  |                 |                 |

|-----------|--------------|-------------|------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|

| 1         | CS0          | Chip Sele   | ct. Chip is sel                                                        | ected when C     | S0 = "L".        |                 |                 |

|           | CSU          | When the    | chip is not se                                                         | lected, D[7:0]   | will be high     | impedance.      |                 |

| 2         | RST          | When RS     | T= "L", all co                                                         | ontrol registers | s are re-initial | ized by their c | lefault states. |

|           |              |             | ntrol data or I                                                        | 1 -              |                  | 1               |                 |

| 3         | CD           |             |                                                                        |                  |                  | SS when not u   | sed.            |

|           |              |             | trol data "H'                                                          |                  |                  |                 |                 |

| 4         | WR0          |             | controls the re                                                        |                  |                  |                 |                 |

| _         | HID 4        |             |                                                                        |                  | [1:0] depends    | on whether the  | ne interface    |

| 5         | WR1          |             | mode or 8080                                                           |                  |                  | . 1             | A- NCC          |

|           |              |             |                                                                        |                  |                  | ed, connect th  |                 |

| 6         | D0           |             | onal bus for b<br>[0] to SCK, I                                        |                  | paramet nost     | interfaces. In  | seriai modes,   |

|           | D.1          | T COMMECT L |                                                                        |                  | 514.64           |                 |                 |

| 7         | D1           |             | BM=1x                                                                  | BM=0x            | BM=01            | BM=00           |                 |

| 8         | D2           |             | (Parallel)                                                             | (Parallel)       | (S9)             | (S8/S8uc)       |                 |

|           |              | D0          | D0                                                                     | D0/D4            | SCK              | SCK             |                 |

| 9         | D3           | D1          | D1                                                                     | D1/D5            | _                | _               |                 |

|           |              | D2          | D2                                                                     | D2/D6            | _                | _               |                 |

| 10        | D4           | D3          | D3                                                                     | D3/D7            | SDA              | SDA             |                 |

| 11        | D5           | D4          | D4                                                                     | _                | _                | _               |                 |

| 11        | <u>D3</u>    | D5          | D5                                                                     | _                | _                | _               |                 |

| 12        | D6           | D6          | D6                                                                     | _                | 0                | S8/S8uc         |                 |

|           |              | D7          | D7                                                                     | 0                | 1                | 1               |                 |

| 13        | D7           | Connect 1   | inused pins to                                                         | VDD or VSS       |                  |                 |                 |

| 14        | VDD          | Power sup   | -                                                                      |                  |                  |                 |                 |

| 15        | GND          | Ground ((   |                                                                        |                  |                  |                 |                 |

| 16~20     | NC           | No conne    | ,                                                                      |                  |                  |                 |                 |

| 21        | VB0-         | LCD Bias    | S Voltages.                                                            |                  |                  |                 |                 |

| <u>~1</u> | <b>√</b> D∪- | These are   | the voltage so                                                         |                  |                  |                 |                 |

| 22        | VB-+         |             | -                                                                      |                  | ly. Connect c    | apacitors of C  | BX value        |

| 2.2       | * T T 1      |             | VBX+ and VB                                                            |                  |                  |                 |                 |

| 23        | VB1-         |             |                                                                        | •                |                  | riving strength |                 |

| 24        | VB1+         |             | electrodes and impacts the image of the LCD module. Minimize the trace |                  |                  |                 |                 |

|           |              |             | esistance is critical in achieving high quality image.                 |                  |                  |                 |                 |

| 25        | VLCD         |             | er supply.                                                             |                  |                  |                 |                 |

| -         | A            |             | LED backligh                                                           |                  |                  |                 |                 |

| -         | K            | Cathode of  | of LED backli                                                          | gnt.             |                  |                 |                 |

### **Absolute Maximum Ratings**

#### 4.1 **Electrical Maximum Ratings – for IC Only**

Table 3

| Parameter           | Symbol   | Min. | Max.    | Unit |

|---------------------|----------|------|---------|------|

| Supply Voltage (1)  | VDD,VDD2 | -0.3 | +4.0    | V    |

| Supply Voltage (2)  | VDD2-VDD | -    | +1.6    | V    |

| LCD driving voltage | VLCD     | -0.3 | +11.8   | V    |

| Input voltage range | Vin      | -0.4 | VDD+0.5 | V    |

#### Note:

The module may be destroyed if they are used beyond the absolute maximum ratings.

All voltage values are referenced to VSS= 0V.

#### 4.2 **Environmental Condition**

Table 4

| Item                                                                 | Operating temperature (Topr)                         |                                                                                        | Storage<br>temperature<br>(Tstg)<br>(note 1) |       | Remark       |

|----------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------|-------|--------------|

|                                                                      | Min.                                                 | Max.                                                                                   | Min.                                         | Max.  |              |

| Ambient temperature (Ta)                                             | -20°C                                                | +70°C                                                                                  | -30°C                                        | +80°C | Dry          |

| Humidity (note 1)                                                    | < 50% RH fo                                          | 90% max. RH for Ta ≤ 40°C<br>< 50% RH for 40°C < Ta ≤ Maximum<br>operating temperature |                                              |       |              |

| Vibration (IEC 68-2-6) cells must be mounted on a suitable connector | Amplitude: (                                         | Frequency: 10 ~ 55 Hz  Amplitude: 0.75 mm  Duration: 20 cycles in each direction.      |                                              |       |              |

| Shock (IEC 68-2-27)<br>Half-sine pulse shape                         | Pulse duration Peak accelerate Number of significant | ation: 981 n<br>hocks: 3 sho                                                           | •                                            | ually | 3 directions |

Note 1: Product cannot sustain at extreme storage conditions for long time.

### **5.** Electrical Specifications

### **5.1** Typical Electrical Characteristics

At Ta = 25 °C, VDD = 2.8V, GND=0V.

Table 5

| Parameter                  | Symbol   | Conditions        | Min.   | Typ. | Max.   | Unit              |

|----------------------------|----------|-------------------|--------|------|--------|-------------------|

| Supply voltage (logic)     | VDD      |                   | 2.4    | 2.8  | 3.3    | V                 |

| Supply voltage (LCD)       | VLCD     | Ta=-20°C,         | -      | TBD  | -      | V                 |

| (Build-in)                 |          | Character mode,   |        |      |        |                   |

|                            |          | VDD=2.8V, Note 1. |        |      |        |                   |

|                            |          | Ta=+25°C,         | -      | TBD  | -      | V                 |

|                            |          | VDD=2.8V, Note 1. |        |      |        |                   |

|                            |          | Ta=+70°C,         | -      | TBD  | -      | V                 |

|                            |          | Character mode,   |        |      |        |                   |

|                            |          | VDD=2.8V, Note 1. |        |      |        |                   |

| Low level input voltage    | $V_{IL}$ |                   | VSS    |      | 0.2VDD | V                 |

| High level input voltage   | $V_{IH}$ |                   | 0.8VDD |      | VDD    | V                 |

| Supply Current             | IDD      | All mode,         | -      | TBD  | -      | mA                |

| Supply Current             |          | VDD=2.8V          |        |      |        |                   |

| Supply voltage of white    | VLED     | Forward current   | 3.0    | 3.2  | 3.4    | v                 |

| LED backlight              |          | =15mA             | 3.0    | 3.2  | 5.4    | V                 |

| Luminance of backlight     |          | Number of LED     | 2500   |      |        | cd/m <sup>2</sup> |

| (on the backlight surface) |          | dies=1            | 2300   | -    | _      | Cu/III            |

Note (1): There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

### **5.2** Timing Specifications

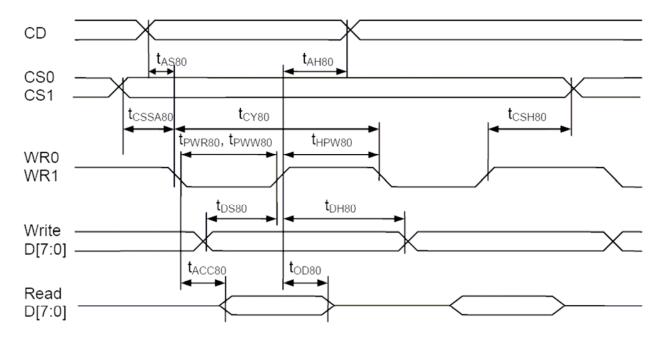

### **5.2.1** Parallel Bus Timing Characteristics (for 8080 MCU)

At Ta =-20 °C To +70 °C, VDD= 2.8V, GND=0V.

Table 6

| Symbol                             | Signal   | Description                             | Condition              | Min.    | Max. | Units |

|------------------------------------|----------|-----------------------------------------|------------------------|---------|------|-------|

| t <sub>AS80</sub><br><b>t</b> AH80 | CD       | Address setup time<br>Address hold time |                        | 0<br>15 | -    | nS    |

| t <sub>CY80</sub>                  |          | System cycle time                       |                        |         | -    | nS    |

|                                    |          | 8 bits bus (read)                       |                        | 140     |      |       |

|                                    |          | (write)                                 |                        | 80      |      |       |

|                                    |          | 4 bits bus (read)                       |                        | 140     |      |       |

|                                    |          | (write)                                 |                        | 80      |      |       |

| t <sub>PWR80</sub>                 | WR1      | Pulse width 8 bits (read)               |                        | 70      | -    | nS    |

|                                    |          | 4 bits                                  |                        | 70      |      |       |

| t <sub>PWW80</sub>                 | WR0      | Pulse width 8 bits (write)              |                        | 40      | -    | nS    |

|                                    |          | 4 bits                                  |                        | 40      |      |       |

| t <sub>HPW80</sub>                 | WR0, WR1 | High pulse width                        |                        |         | -    | nS    |

|                                    |          | 8 bits bus (read)                       |                        | 70      |      |       |

|                                    |          | (write)                                 |                        | 40      |      |       |

|                                    |          | 4 bits bus (read)                       |                        | 70      |      |       |

|                                    |          | (write)                                 |                        | 40      |      |       |

| t <sub>DS80</sub>                  | D0~D7    | Data setup time                         |                        | 30      | -    | nS    |

| t <sub>DH80</sub>                  |          | Data hold time                          |                        | 15      |      |       |

| t <sub>ACC80</sub>                 |          | Read access time                        | C <sub>L</sub> = 100pF | _       | 50   | nS    |

| t <sub>OD80</sub>                  |          | Output disable time                     |                        | 25      | 50   |       |

| tcssa80                            | CS1/CS0  | Chip select setup time                  |                        | 5       |      | nS    |

| t <sub>CSH80</sub>                 |          |                                         |                        | 5       |      |       |

Figure 3: Parallel Bus Timing Characteristics (for 8080 MCU)

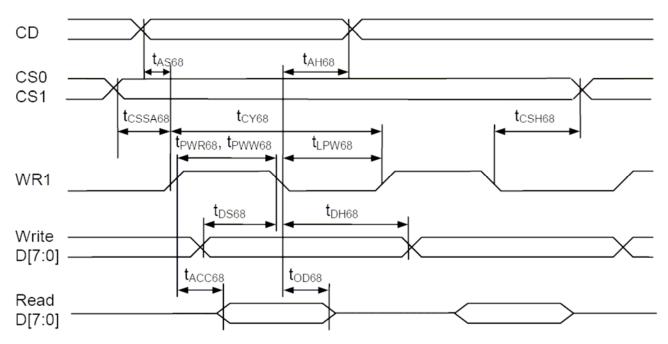

### **5.2.2** Parallel Bus Timing Characteristics (for 6800 MCU)

At Ta =-20 °C To +70 °C, VDD= 2.8V, GND=0V.

Table 7

| Symbol                                 | Signal  | Description                             | Condition              | Min.    | Max. | Units |

|----------------------------------------|---------|-----------------------------------------|------------------------|---------|------|-------|

| t <sub>AS68</sub><br>t <sub>AH68</sub> | CD      | Address setup time<br>Address hold time |                        | 0<br>20 | -    | nS    |

| t <sub>CY68</sub>                      |         | System cycle time                       |                        |         | -    | nS    |

|                                        |         | 8 bits bus (read)                       |                        | 140     |      |       |

|                                        |         | (write)                                 |                        | 80      |      |       |

|                                        |         | 4 bits bus (read)                       |                        | 140     |      |       |

|                                        |         | (write)                                 |                        | 80      |      |       |

| t <sub>PWR68</sub>                     | WR1     | Pulse width 8 bits (read)               |                        | 70      | _    | nS    |

|                                        |         | 4 bits                                  |                        | 70      |      |       |

| t <sub>PWW68</sub>                     |         | Pulse width 8 bits (write)              |                        | 40      | _    | nS    |

|                                        |         | 4 bits                                  |                        | 40      |      |       |

| t <sub>LPW68</sub>                     |         | Low pulse width                         |                        |         | _    | nS    |

|                                        |         | 8 bits bus (read)                       |                        | 70      |      |       |

|                                        |         | (write)                                 |                        | 40      |      |       |

|                                        |         | 4 bits bus (read)                       |                        | 70      |      |       |

|                                        |         | (write)                                 |                        | 40      |      |       |

| t <sub>DS68</sub>                      | D0~D7   | Data setup time                         |                        | 30      | _    | nS    |

| t <sub>DH68</sub>                      |         | Data hold time                          |                        | 15      |      |       |

| t <sub>ACC68</sub>                     |         | Read access time                        | C <sub>L</sub> = 100pF |         | 50   | nS    |

| t <sub>OD68</sub>                      |         | Output disable time                     |                        | 25      | 50   |       |

| tcssA68                                | CS1/CS0 | Chip select setup time                  |                        | 5       |      | nS    |

| t <sub>CSH68</sub>                     |         |                                         |                        | 5       |      |       |

Figure 4: Parallel Bus Timing Characteristics (for 6800 MCU)

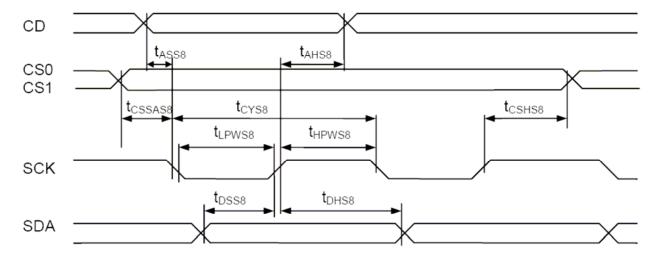

### **5.2.3** Serial Bus Timing Characteristics (for S8)

At Ta =-20 °C To +70 °C, VDD= 2.8V, GND=0V.

Table 8

| Symbol                                 | Signal  | Description                       | Condition | Min.     | Max. | Units |

|----------------------------------------|---------|-----------------------------------|-----------|----------|------|-------|

| t <sub>ASS8</sub>                      | CD      | Address setup time                |           | 0        | _    | nS    |

| t <sub>AHS8</sub>                      | CD      | Address hold time                 |           | 15       | -    | nS    |

| t <sub>CYS8</sub>                      |         | System cycle time                 |           | 80       | ı    | nS    |

| t <sub>LPWS8</sub>                     | SCK     | Low pulse width                   |           | 35       | -    | nS    |

| t <sub>HPWS8</sub>                     |         | High pulse width                  |           | 35       | -    | nS    |

| t <sub>DSS8</sub><br>t <sub>DHS8</sub> | SDA     | Data setup time<br>Data hold time |           | 30<br>20 | ı    | nS    |

| tcssas8<br>t <sub>cshs8</sub>          | CS1/CS0 | Chip select setup time            |           | 5 5      |      | nS    |

Figure 5: Serial Bus Timing Characteristics (for S8)

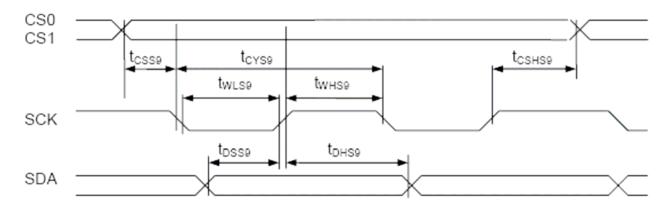

### **5.2.4** Serial Bus Timing Characteristics (for S9)

At Ta =-20 °C To +70 °C, VDD= 2.8V, GND=0V.

Table 9

| Symbol                        | Signal  | Description                       | Condition | Min.     | Max. | Units |

|-------------------------------|---------|-----------------------------------|-----------|----------|------|-------|

| tcyse                         |         | System cycle time                 |           | 80       | -    | nS    |

| t <sub>LPWS9</sub>            | SCK     | Low pulse width                   |           | 35       | _    | nS    |

| t <sub>HPWS9</sub>            |         | High pulse width                  |           | 35       | _    | nS    |

| tosse<br>t <sub>ohse</sub>    | SDA     | Data setup time<br>Data hold time |           | 30<br>20 | ı    | nS    |

| tcssase<br>t <sub>cshse</sub> | CS1/CS0 | Chip select setup time            |           | 5<br>5   |      | nS    |

Figure 6: Serial Bus Timing Characteristics (for S9)

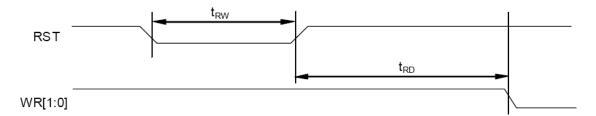

### 5.2.5 Reset Input Timing

At Ta =-20 °C To +70 °C, VDD=2.8V, GND=0V.

Table 10

| Symbol          | Signal  | Description             | Condition | Min. | Max. | Units |

|-----------------|---------|-------------------------|-----------|------|------|-------|

| t <sub>RW</sub> | RST     | Reset low pulse width   |           | 3    | _    | μS    |

| t <sub>RD</sub> | RST, WR | Reset to WR pulse delay |           | 10   |      | mS    |

Figure 7: Reset Input Timing

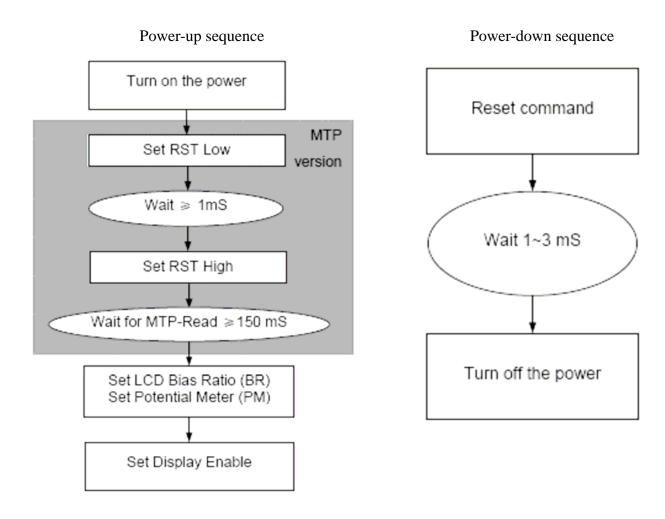

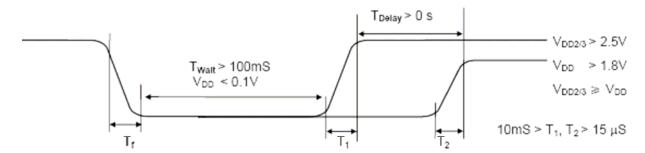

### 5.3 Power-up/down sequence

Delay allowance and Power Off-On Sequence

# 6. Electrical & Optical Characteristics (TBD)

### 7. CSTN Panel Inspection Specifications

|                                                                                                                                        | TER POLEO GIR                                                                                                                                                                                                        |                                                                                                                                                   |                                                                           | 可接受                                                                                    |                  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|--|

| 壞品名稱                                                                                                                                   | 圖例說明                                                                                                                                                                                                                 | 分类<br>Category(Unit: mm)                                                                                                                          |                                                                           | Acceptable count<br>可视区 非可视区                                                           |                  |  |

| Failure mode                                                                                                                           | Illustration                                                                                                                                                                                                         |                                                                                                                                                   |                                                                           | Viewing area                                                                           | non-Viewing area |  |

| 黑點<br>Black spot<br>白點<br>White spot                                                                                                   | <b>♦ ♦</b> Width                                                                                                                                                                                                     | A                                                                                                                                                 | Φ≦0.10                                                                    | 不计<br>Not count                                                                        | non viewing area |  |

|                                                                                                                                        | Length Φ= (Length+width)/2                                                                                                                                                                                           | В                                                                                                                                                 | 0. 10<Φ ≤ 0. 15                                                           | 2,两点间距离不<br>小于 5mm<br>The gap between<br>the two spots<br>should be 5 mm<br>and above. | 不计<br>Not count  |  |

|                                                                                                                                        | (====g                                                                                                                                                                                                               | С                                                                                                                                                 | 0. 15<Φ ≤ 0. 20                                                           | 1                                                                                      |                  |  |

|                                                                                                                                        |                                                                                                                                                                                                                      | D                                                                                                                                                 | 0. 20<Φ                                                                   | 0                                                                                      |                  |  |

| 亮點(因為濾光<br>片損壞造成的<br>紅點,綠點,藍<br>點等)<br>Bright spot<br>(Red spot,<br>green spot and<br>blue spot caused<br>by damaged<br>colour filter) |                                                                                                                                                                                                                      | A                                                                                                                                                 | 缺陷面積小於或等<br>於一個單基色面積<br>Area≦1<br>sub-pixel                               | 1                                                                                      | N/A              |  |

| 黑线<br>Black line                                                                                                                       | → W                                                                                                                                                                                                                  | A                                                                                                                                                 | W≦0.03                                                                    | 不计<br>Not count                                                                        | 不计<br>Not count  |  |

| 白线<br>White line                                                                                                                       |                                                                                                                                                                                                                      | В                                                                                                                                                 | 0. 03<₩≤0. 05, L≤<br>3. 0                                                 | 2                                                                                      |                  |  |

| winte fine                                                                                                                             | L L                                                                                                                                                                                                                  | С                                                                                                                                                 | O. 05 <w< td=""><td>按黑白点判定<br/>Judged by spot<br/>spec</td><td></td></w<> | 按黑白点判定<br>Judged by spot<br>spec                                                       |                  |  |

| 以下为外观标准(                                                                                                                               | Below are cosmetic inspection s                                                                                                                                                                                      | specifications                                                                                                                                    | s)                                                                        |                                                                                        |                  |  |

| 玻璃毛刺<br>Excess glass                                                                                                                   | b≤1.0 且不影响外形尺寸及装配(注意COG 工序对b的要求,不同尺寸LCD 的 b 都不同) b≤1.0, this defect shall not affect the outline dimension or assembly process.(Remarks: For COG process, the defect size is decided by the dimension of LCD panel.) |                                                                                                                                                   |                                                                           |                                                                                        |                  |  |

|                                                                                                                                        |                                                                                                                                                                                                                      | 不影响外形尺寸及装配.<br>This defect shall not affect the outline dimension or assembly process.                                                            |                                                                           |                                                                                        |                  |  |

| 进胶尺寸<br>The depth of UV<br>glue entered in<br>LCD cell                                                                                 | D1                                                                                                                                                                                                                   | 進膠深度大於等於 0.2mm 且不可進入視域范圍,膠水凸出玻璃邊高度小于等于 0.8mm,长度=(注入口宽度)+(2~6 mm)a. D1≥0.2, not enter into viewing area b. D2≤0.8, c. W=End mouth width + (2~6 mm) |                                                                           |                                                                                        |                  |  |

|                                          | ①台阶破损(LCD ledge damage)                                                                                  | 分类 Category                                                               |                                                                                                                   |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

|                                          |                                                                                                          | A                                                                         | 非电极区,台阶破损不得影响装配及外形尺寸<br>The defect shall not affect the outline dimension or<br>assembly process at non ITO zone. |  |

| 玻璃缺陷划伤、缺损 Glass defect (scratch, damage) |                                                                                                          | В                                                                         | 电极区的破损, b 不得超过邦定电极长度(该长度应不小于 1. 2mm)的 1/4, a、c 方向不限制 b≤1/4w, a & c not count (at ITO zone)                        |  |

|                                          |                                                                                                          | С                                                                         | 台阶两侧的缺损不得损伤对位标识或走线<br>Alignment mark on LCD ledge shall not be damaged.                                           |  |

|                                          | ②非封接面破损 (Outside of perimeter damage) 边框架(Perimeter) 边框架(Inside of perimeter) 边框外沿(outside of perimeter) | b 方向破损不得到达边框内沿b can't reach inside of perimeter.                          |                                                                                                                   |  |

|                                          | ③ 封接面破损 (Joint glass damage) 边框架(Perimeter)  边框内沿(Inside of perimeter) 边框外沿(Outside of perimeter)        | b 方向破损不得到达边框外沿或走线 b can't reach outside of perimeter or ITO layout.       |                                                                                                                   |  |

|                                          | ④角上破损                                                                                                    | A                                                                         | a ≦ t, b ≦ 3.0, c ≦ 3.0                                                                                           |  |

|                                          | (Corner damage)                                                                                          | B. 玻璃破损不允许损伤电极图形和/或对位标识 Alignment mark on LCD ledge shall not be damaged. |                                                                                                                   |  |

|                                          |                                                                                                          |                                                                           | ;表示单片玻璃厚度:单位:mm                                                                                                   |  |

| Remark: a stands t                       | for thickness of damage, b for w                                                                         | idth, c for lengtl                                                        | n and t for glass thickness. (Unit: mm)                                                                           |  |

#### Remark

#### HANDLING LCD AND LCD MODULES

#### 1. Liquid Crystal Display (LCD)

LCD is made up of glass, organic sealant, organic fluid and polymer based polarizers. The following precautions should be taken when handling:

- Keep the temperature within range for use and storage. Excessive temperature and humidity could cause polarization degredation, polarizer peel-off or bubble generation. When storage for a long period over 40° C is required, the relative humidity should be kept below 60%.

- Do not contact the exposed polarizers with anything harder than an HB pencil lead. To clean dust off the display surface, wipe gently with cotton, chamois or other soft material soaked in petroleum benzin. Never

- Varitronix does not responsible for any polarizer (3) defect after the protective film has been removed from the display Wipe off saliva or water drops immediately. Contact

- with water over a long period of time may cause polarizer deformation or color fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes.

- PETROLEUM BENZIN is recommended to remove adhesives used to attach front/rear polarizers and reflectors, while chemicals like acetone, toluene, ethanol and isopropyl alcohol will cause damage to the polarizer. Avoid oil and fats. Avoid lacquer and epoxies which might contain solvents and hardeners to cause electrode errosion. Some solvents will also soften the epoxy covering the DIL pins and thereby weakening the adhesion of the epoxy on glass. This will cause the exposed electrodes to erode electrochemically when operating in high humidity and condensing environment.

- and condensing environment.

Glass can be easily chipped or cracked from rough

handling, especially at corners and edges.

Do not drive LCD with DC voltage.

- When soldering DIL pins, avoid excessive heat and keep soldering temperature between 260°C to 300°C for no more than 5 seconds. Never use wave or reflow soldering.

#### 2. Liquid Crystal Display Modules (MDL)

#### 2.1 Mechanical Considerations

MDL's are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted. (1) Do not tamper in any way with the tabs on the metal

- (2)

- Do not modify the PCB by drilling extra holes, changing its outline, moving its components or modifying its pattern.

- Do not touch the elastomer connector (conductive rubber), especially when inserting an EL panel.

When mounting a MDL make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any the elements.

- Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels.

- the first area on the specification. The stiffener and component area on FPC/FFC/COF must not be bent. during or after assembly (Note: for those models with

- FPC/FFC/COF+stiffener). Sharp bending should be avoided on FPC to prevent track cracking.

#### 2.2 Static Electricity

MDL contains CMOS LSI's and the same precaution for such devices should apply, namely:

- The operator should be grounded whenever he comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any

- part of the human body.

The modules should be kept in antistatic bags or other containers resistant to static for storage.

- Only properly grounded soldering irons should be (3)

- used.

If an electric screwdriver is used it should be well grounded and shielded from commutator sparks.

- The normal static prevention measures should be observed for work clothes and working benches; for

- the latter conductive (rubber) mat is recommended. Since dry air is inducive to statics, a relative humidity of 50 60% is recommended.

#### 2.3 Soldering

- Solder only to the I/O terminals.

- Use only soldering irons with proper grounding and

- no leakage. Soldering temperature is  $280^{\circ}\text{C} \pm 10^{\circ}\text{C}$

- Soldering time: 3 to 4 seconds.

Use eutectic solder with resin flux fill.

If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed afterwards.

- Use proper de-soldering methods (e.g. suction type desoldering irons) to remove lead wires from the I/O terminals when necessary. Do not repeat the soldering/ desoldering process more than three times as the pads and plated through holes may be damaged.

Identification labels will be stuck on the module without

obstructing the viewing area of display.

#### 3. Operation

- The viewing angle can be adjusted by varying the LCD driving voltage Vo.

Driving voltage should be kept within specified range

- excess voltage shortens display life. Response time increases wit temperature. with

- Display may turn black or dark Blue at temperature above its operational range; this is however not destructive and the display will return to normal once the temperature falls back to range.

- Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear "fractured". They will recover once the display is turned off.

Condensation at terminals will cause malfunction and possible electrochemical reaction. Relative humidity

- of the environment should therefore be kept below

- Display performance may vary out of viewing area If there is any special requirement on performance out of viewing area, please consult Varitronix.

#### 4. Storage and Reliability

- LCD's should be kept in sealed polyethylene bag: while MDL's should use antistatic ones. If properly sealed, there is no need for desiccant.

- Store in dark places and do not expose to sunlight o fluorescent light. Keep the temperature between 0°C and 35°C and the relative humidity low. Please consult MULTI-INNO for other storage

- requirements Water cor Water condensation will affect reliability performance of the display and is not allowed.

- Semi-conductor device on the display is sensitive to light and should be protected properly.

- (5) Power up/down sequence.

- a) Power Up: in general, LCD supply voltage, Vo must be supplied after logic voltage, VDD becomes steady. Please refer to related IC data sheet for details.

- Power Down: in general, LCD supply voltage, Vo must be removed before logic voltage, VDD turns off. Please refer to related IC data sheet for details.

#### 5. Safety

If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all times.

#### LIMITED WARRANTY

MULTI-INNO LCDs and modules are not consumer products, but may be incorporated by MULTI-INNO 's customers into consumer products or components thereof. MULTI-INNO does not warrant that its LCDs and components are fit for any such particular purpose.

The liability of MULTI-INNO is limited to repair or replacement on the terms set forth below. MULTI-INNO will not be responsible for any subsequent or consequential events or injury or damage to any personnel or user including third party personnel and/or user.

Unless otherwise agreed in writing between MULTI-INNO and the customer, MULTI-INNO will only replace or repair any of its LCD which is found defective electrically or visually when inspected in

accordance with MULTI-INNO LCD Acceptance Standards (copies available on request), for a period of one year from the date of shipment. Confirmation of such date shall be based on freight

- No warranty can be granted if any of the precautions stated in HANDLING LCD and LCD Modules above have been disregarded Broken glass, scratches on polarizers, mechanical damages as well as defects that are caused by accelerated environmental tests are excluded from warranty.

In returning the LCD and Modules, they must be properly packaged and there should be detailed description of the failures or defects.

#### IMPORTANT NOTICE

The information presented in this document has been carefully checked and is believed to be accurate, however, no responsibility is assumed for inaccuracies. MULTI-INNO reserves the right to make changes to any specifications without further notice for performance, reliability, production technique and other considerations, MULTI-INNO does not assume any liability arising out of the application or use of products herein. Please see Limited Warranty in the previous section.