# 2 MBIT PCM SIGNALLING CIRCUIT MJ 1444

# PCM SYNCHRONISING WORD GENERATOR

The 2.048 Mbit PCM signalling circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048 Mbit 30 channel PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in N-channel metal gate MOS and operate from a single 5 volt supply. Relevant inputs and outputs are TTL compatible.

The MJ1444 generates the synchronising word in accordance with CCITT recommendations G732. The MJ1445 has been designed to detect this synchronising word when received at the remote end of the transmission system.

The synchronising word is injected onto the PCM data highway during time slot 0 in alternate frames. The spare time slot 0 data bits, bit 1 in every frame and bits 3 to 8 inclusive in alternate frames (i.e. those not containing the synchronising word) are available as parallel inputs and are output onto the PCM data highway.

The data output of the MJ1444 is 'open collector' and can be wire-OR'd directly onto the highway.

The device also provides a time slot 0 channel pulse 'TS0', time slot 0 non-sync. frame 'TS0 SF', and time slot 16 'TS16' outputs.

# **FEATURES**

- 5V±5% Supply—20mA Typical

- Fully Conforms to CCITT Recommendation G732

- Outputs Directly Onto PCM Data Highway

- Provides Both Time Slot 0 and Time Slot 16 Channel Pulses

- All Inputs and Outputs are TTL Compatible

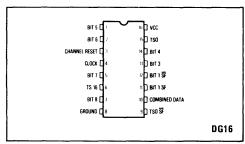

Fig.1 Pin connections

# **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

# **Electrical Ratings**

+Vcc 7V

Inputs Vcc + 0.5V Gnd - 0.3V

Outputs Vcc, Gnd -0.3V

# **Thermal Ratings**

Max Junction Temperature 175°C

Thermal Resistance: Chip to Case

35°C/Watt

120°C/Watt

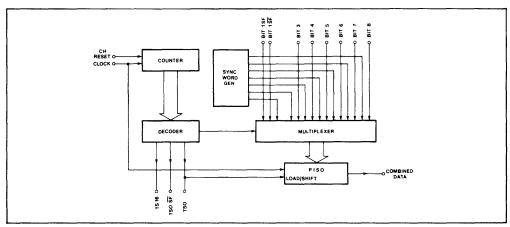

Fig.2 MJ1444 block diagram

# MJ1444

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Supply voltage,  $V_{CC}=5V\pm0.25V$  Ambient operating temperature – 10°C to +70°C

# Static Characteristics

| Characteristic                                       | Symbol          | Pins                                    | Value |      |                 | Units | Conditions                                         |  |

|------------------------------------------------------|-----------------|-----------------------------------------|-------|------|-----------------|-------|----------------------------------------------------|--|

|                                                      |                 |                                         | Min.  | Тур. | Max.            | Units | Conditions                                         |  |

| Low level input voltage                              | V <sub>IL</sub> | 1, 2, 3, 4, 5,<br>7, 11, 12, 13,<br>14. | -0.3  |      | 0.8             | ٧     |                                                    |  |

| Low level input current } High level input current } | 1 <sub>IN</sub> | 11                                      |       | 1    | 50              | μА    |                                                    |  |

| High level input voltage                             | V <sub>IH</sub> | 11                                      | 2.4   |      | V <sub>cc</sub> |       |                                                    |  |

| Low level output voltage                             | V <sub>OL</sub> | 6, 9, 15<br>10                          |       |      | 0.5<br>0.7      | V     | l <sub>sink</sub> = 2mA<br>l <sub>sink</sub> = 5mA |  |

| High level output voltage                            | V <sub>OH</sub> | 6, 9, 15                                | 2.8   |      |                 | v     | I <sub>source</sub> = 200 μA                       |  |

| High level output leakage current                    | I <sub>OH</sub> | 10                                      |       |      | 20              | μΑ    | V <sub>OUT</sub> = V <sub>CC</sub>                 |  |

| Supply current                                       | Icc             | İ                                       |       | 20   | 40              | mA    | $V_{CC} = 5.25V$                                   |  |

# **Dynamic Characteristics**

| Characteristic                                                           | S                | Value     |  |      | Units | Conditions                    |  |  |

|--------------------------------------------------------------------------|------------------|-----------|--|------|-------|-------------------------------|--|--|

| Characteristic                                                           | Symbol           | Min. Typ. |  | Max. | Units | Conditions                    |  |  |

| Max clock frequency                                                      | F <sub>max</sub> | 3         |  |      | MHz   |                               |  |  |

| Propagation delay, clock to TS0, TS0 SF, TS16 and combined data outputs. | t <sub>P</sub>   | 80        |  | 200  | ns    | See Figs.5 and 6              |  |  |

| Set up time channel reset to clock                                       | T <sub>S1</sub>  | 100       |  | 450  | ns    | f <sub>cfock</sub> = 2.048 MH |  |  |

| Hold time of channel reset input                                         | t <sub>H1</sub>  | 20        |  | 400  | ns    | ł                             |  |  |

| Set up time of bit 1 (SF) to datum B                                     | t <sub>S2</sub>  | 100       |  | 1    | ns    |                               |  |  |

| Hold time of bit 1 (SF) wrt datum B                                      | t <sub>H2</sub>  | 300       |  | 1    | ns    | 1                             |  |  |

| Set up time of bit 1 ( $\overline{SF}$ ) and data bits 3 — 8 to datum B  | t <sub>S2</sub>  | 100       |  |      | ns    |                               |  |  |

| Hold time of bit 1 ( $\overline{SF}$ ) and data bits 3 — 8 wrt datum B   | t <sub>H2</sub>  | 300       |  | Ì    | ns    |                               |  |  |

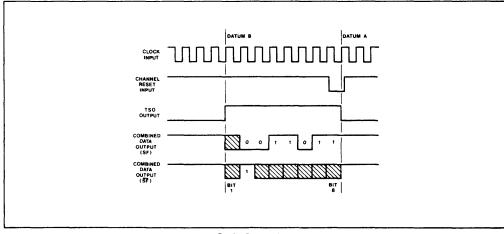

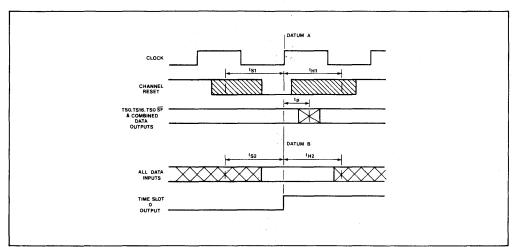

Fig.3 Data timing

# **FUNCTIONAL DESCRIPTION**

# Functions Listed by pin number

# 1, 2, 5, 7, 13, 14. Bits 3 to 8

Parallel data on these inputs is asynchronously loaded into bits 3 to 8 of the PISO shift register for transmission during Time slot 0 of non-sync. frames.

### 3. Channel Reset

A low going pulse at this input synchronises the MJ1444 with the other devices at the transmit end of the PCM link. It may be applied as a start pulse or repeated at the same instant in successive frames.

# 4. Clock

System clock input (2.048MHz for a 2 Mbit PCM system).

This output provides a positive pulse equivalent to 8 clock periods during time slot 16 of every 30 + 2 channel PCM frame.

### 8. GND

Zero volts.

# 9. TS0 SF

This output provides a positive pulse equivalent to 8 clock periods during time slot 0 of non-sync. frames.

10. Combined data

This 'open collector' output injects the contents of the PISO shift register onto the PCM data highway during time slot 0 in successive frames. The contents of the PISO shift register are defined as follows:

|                 | Bit 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|-----------------|-------|---|---|---|---|---|---|---|

| Sync. Frame     | Х     | 0 | 0 | 1 | 1 | 0 | 1 | 1 |

| Non-sync. frame | X     | 1 | X | X | X | X | Х | Х |

X-indicates that these bits may be set according to the parallel data inputs.

#### 11. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of sync. frames.

# 12. Bit 1 SF

Data on this input is asynchronously loaded into bit 1 of the PISO shift register for transmission during time slot 0 of non-sync, frames.

#### 15. TS0

This output provides a positive pulse equivalent to 8 clock period during time slot 0 of every 30 channel PCM

16.  $V_{CC}$ Positive supply,  $5V \pm 5\%$ .

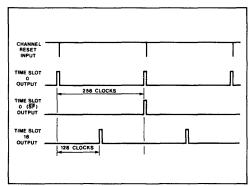

Fig.4 Sync. timing

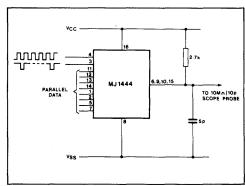

Fig.5 Test conditions (all outputs)

Fig.6 Timing definitions