# MJ1473

# PCM TRANSMITTER CIRCUIT

The MJ1400 Series of circuits have been specifically designed for use in 30 channel PCM systems.

The MJ1473 is designed to simplify the transmit section of a 30 channel, 2 MBit PCM link by converting NRZ PCM data to either AMI or HDB3 format after inserting a synchronising word in channel 0 (conforming to CCITT recommendations G.703 and G.732).

The data is output in pseudo-ternary form to facilitate driving the line interface via a transformer and AMI or HDB3 code may be remotely selected using bits 2 and 3 in channel 0 of the incoming data stream.

#### FEATURES

- 5V 30mA Power Requirements

- 0-70°C Operation

- Complies with Relevant CCITT Recommendations

- Control Signals Compatible with MJ1472,4

- NRZ, AMI or HDB3-Transmission Format

- Transmission Format Controlled Locally or Remotely Via TSO Data

- Fabricated in NMOS Technology

- Inputs and Outputs TTL Compatible

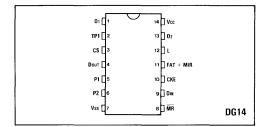

Fig.1 Pin connections - top view

| Bit                                            | 1 | 2 | 3   | 4 | 5 | 6 | 7 | 8 |

|------------------------------------------------|---|---|-----|---|---|---|---|---|

| Channel 0<br>TS0.TA                            | х | 0 | 0   | 1 | 1 | 0 | 1 | 1 |

| Channel 0<br>TS0.TB                            | х | 1 | ATL | х | х | х | х | х |

| <b>—</b> • • • • • • • • • • • • • • • • • • • |   |   |     |   |   |   |   |   |

Table 1

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage on any pin with respect to Vss : 7V Storage temperature : -55° C to +155° C

## MJ1473

### **ELECTRICAL CHARACTERISTICS**

#### Test conditions (unless otherwise stated):

Supply voltage 5V  $\pm$  0.25V Ambient operating temperature 0°C to  $\,$  +70°C Package thermal resistance 95°C/watt

#### DC CHARACTERISTICS

| Characteristic            | Cumhal | In mute (euterute | Value          |    |       | Units | Test conditions  |  |

|---------------------------|--------|-------------------|----------------|----|-------|-------|------------------|--|

| Characteristic            | Symbol | Inputs/outputs    | Min. Typ. Max. |    | Units |       |                  |  |

| High-level input voltage  | ViH    | All inputs        | 2.0            |    |       | v     |                  |  |

| Low-level input voltage   | VIL    | All inputs        |                |    | 0.8   | v     |                  |  |

| High-level output voltage | Vон    | Outputs L & DOUT  | 2.7            |    |       | l v   | -60µA            |  |

| Low-level output voltage  | Vol    | Outputs L & DOUT  |                |    | 0.5   | l v   | 0.8mA            |  |

| High-level input current  | Ьн     | All inputs        |                |    | 50    | μΑ    | VIN = 5.25V 25°C |  |

| High-level output current | Іон1   | Outputs L & DOUT  | 60             |    |       | μA    | Vон = 2.7V       |  |

| High-level output current | Іон2   | Outputs O1 & O2   | 2              |    |       | mA    | Vон = 2.8V       |  |

| Low-level output current  | loL    | Outputs L & DOUT  | 0.8            |    |       | mA    | Vон = 0.5V       |  |

| Input capacitance         | CIN1   | All inputs except |                |    | 10    | pF    | 1MHz 100mV       |  |

|                           |        | CKE               |                |    |       |       |                  |  |

|                           | CIN2   | Input CKE         |                |    | 20    | pF    |                  |  |

| Supply current            | Icc    |                   |                | 30 | 45    | mA    | Vcc = 5.25V      |  |

#### AC CHARACTERISTICS

| Characteristic                                                    | Symbol           | Value |           |     | Units | Conditions                                                                                                                              |  |

|-------------------------------------------------------------------|------------------|-------|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| Characteristic                                                    | Symbol           | Min.  | Typ. Max. |     | Units | Conditions                                                                                                                              |  |

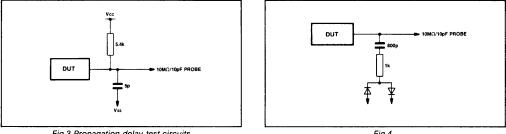

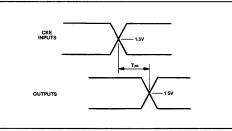

| O1 & O2                                                           | tpd1             |       |           | 100 | ns    | Fig. 4 for loading; measure<br>from CKE leading edge. See<br>Fig. 5 for definition: total<br>delay in tet + 4 CKE periods.              |  |

| L Propagation delays                                              | t <sub>pd2</sub> |       |           | 200 | ns    | Fig. 3 for loading; measure<br>from CKE trailing edge. See<br>Fig. 5 for definition.                                                    |  |

| Dout                                                              | tpd3             |       |           | 180 | ns    | Fig. 3 for loading; measure<br>from CKE leading edge. See<br>Fig. 5 for definition: total<br>delay is t <sub>pd3</sub> + 8 CKE periods. |  |

| Rise and fall times of O1 & O2                                    | trtf             |       |           | 20  | ns    | Fig. 4 for loading. Measured between 0.5V and 2.4V points.                                                                              |  |

| Required delay from D <sub>IN</sub> P1.P2<br>transition to CKE TE | tı               | 50    |           | 430 | ns    |                                                                                                                                         |  |

| Required delay from FAT + MIR<br>transition to CKE LE             | t2               | 50    |           | 430 | ns    |                                                                                                                                         |  |

| Required delay from CS transition to CKE TE                       | ta               | 50    |           | 430 | ns    |                                                                                                                                         |  |

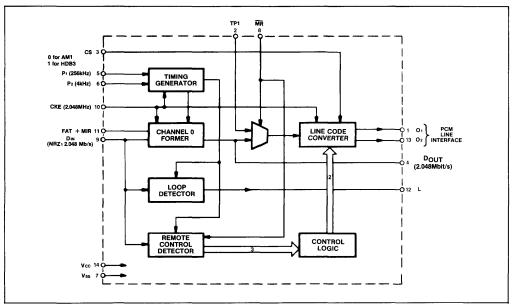

#### **CIRCUIT DESCRIPTION**

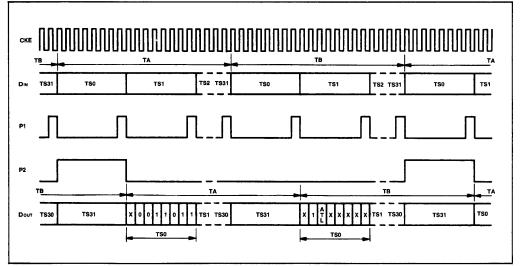

The MJ1473 generates exchange timing by a synchronous 9-bit counter driven by exchange clock CKE and preset by P1,P2. The exchange clock also clocks data, Distribution the channel 0 former and to Dour via an eight bit shift register. In the channel 0 former, data bits of channel 0 are modified as shown in Table 1.

An X in Table 1 indicates transparency through the circuit, bits 2 and 3 of the shift register are concerned with the loop command circuitry. When '01' is detected an internal latch is set and the loop condition on output L is registered.

Dout may also be routed through the HDB3/AMI Encoder. The CS control is logic '0' for AMI and logic '1' for HDB3. Encoded data is then output to 0<sub>1</sub> and 0<sub>2</sub> in a form suitable for driving the PCM interface.

The line code converter can also be controlled by the

remote control commands present on bits 2 and 3 of the shift register. These commands are as follows:

- The presence of '00' in the first frame yields AMI transmission except channel 0 and 1, which are transmitted in a code determined by CS.

The presence of '00' in each consecutive frame yields unipolar transmission except in channel 0 and 1 as above.

The polarity of unipolar transmission is constant for any number of consecutive '00' frames but will alternate with respect to the previous unipolar transmission provided there has been an intermediate frame where '00' was not detected.

- The presence of '11' in any frame yields AMI transmission except for channel 0 and 1 which are transmitted in a code determined by CS.

ATL is forced to a '1' by the presence of the external signal FAT + MIR, or by the presence of one of the two remote control commands or by the loop comand.

An 'all ones' condition on the encoded data outputs (O1 O2) is forced in the presence of a '1' in position 4 of channel 0, when the loop condition is met.

For normal operation  $\overline{MR} = TP1 = 1$ . The test point TP1 is provided as an input independent of the line code converter. In order to enable this input when  $\overline{MR} = 0$ .

All inputs and outputs are compatible with LSTTL.

Fig.3 Propagation delay test circuits

Fig.6 Timing diagram