Issue Date: Apr, 10, 2015

# MK71050-03

Bluetooth ® Low Energy wireless module

## ■ Overview

MK71050-03 is a Bluetooth® Low Energy (here in after LE) wireless module which is integrating ML7105C-001 Bluetooth LE SoC, E2PROM, 26MHz crystal oscillator, 2.4GHz PCB pattern antenna and passive components. It has Bluetooth® LE compliant 2.4GHz band radio communication capability.

MK71050-03 is suitable for applications such as Healthcare device, Remote Controller or PC peripherals.

## ■ Features

• Bluetooth® SIG Core Spec v4.0 compliant

• Radio certification

MIC JAPAN(certification no:006-000238)

FCC (FCC ID:2ACIJ71050-3)

CE(R&TTE)

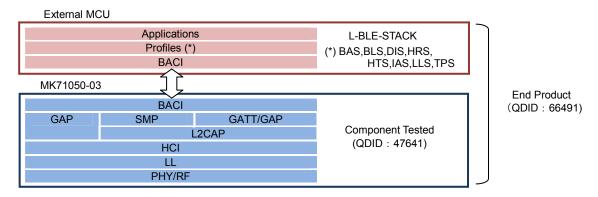

• Bluetooth® Qualification (End Product, QDID:66491)

Integrating ML7105C-001 Bluetooth<sup>®</sup> LE single mode LSI

• Integrating 26MHz xtal oscillator

• Integrating 128kbit EEPROM

• Single power supply 1.8V to 3.6V

Operating Temperature -20 deg.C to 70 deg.C

• Current Consumptions

Deep Sleep Mode 0.8uA(Typ.) (with external Low Power Clock)

Idle Mode 3mA (Typ.)

TX mode 9mA (Typ.)

RX mode 9mA (Typ.)

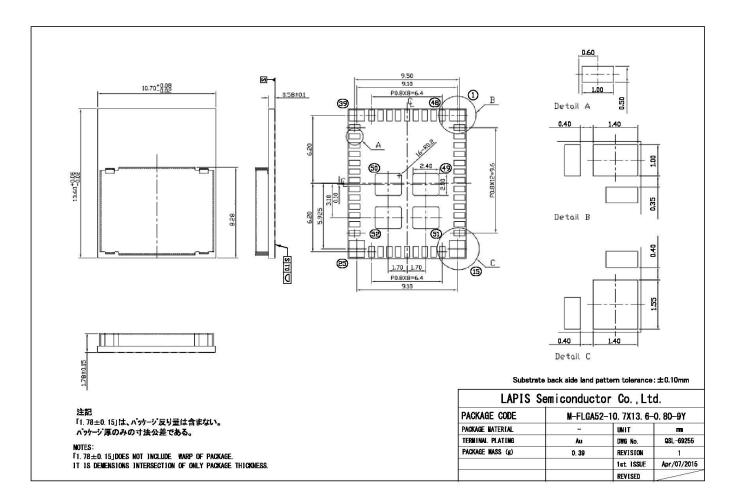

• Dimension 10.7mm(W) x 13.6mm (L) x 1.78mm (H)

• Pb Free, RoHS compliant

• Product Name MK71050-03

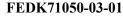

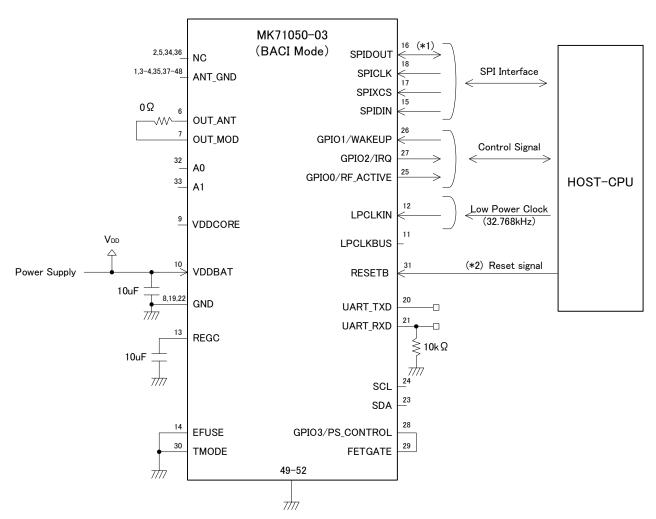

## **■**Schematics

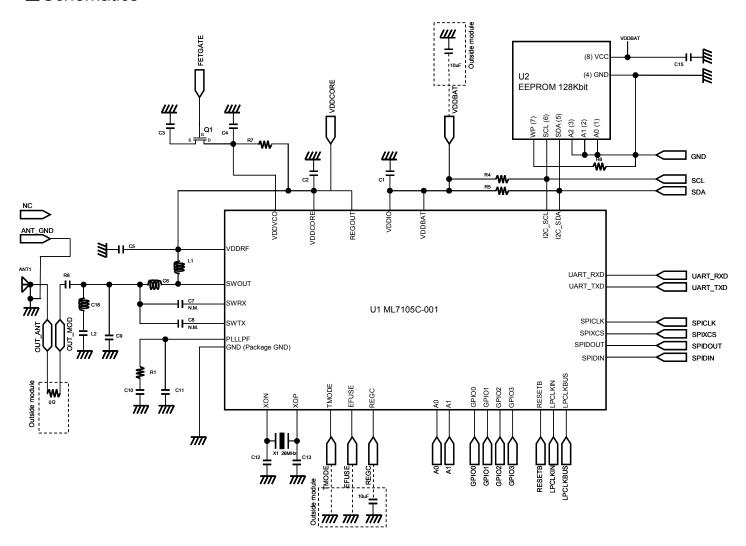

## ■Pin assignment

TOP VIEW

# ■Pin definitions

| No  | Pin Name          | I/O      | Ana/Dig | I/O type       | Function                                          |

|-----|-------------------|----------|---------|----------------|---------------------------------------------------|

| 1   | ANT_GND           |          |         |                | Antenna GND(※Refer to PIN descriptions.)          |

| 2   | NC                |          |         |                | No connection (**Refer to PIN descriptions.)      |

| 3-4 | ANT_GND           |          |         |                | Antenna GND(※Refer to PIN descriptions.)          |

| 5   | NC                |          |         |                | No connection (※Refer to PIN descriptions.)       |

| 6   | OUT_ANT           | INOUT    | ANA     |                | Output from Antenna                               |

|     |                   |          |         |                | (to be connected to OUT_MOD by user's PCB)        |

| 7   | OUT_MOD           | INOUT    | ANA     |                | Output from Module                                |

|     |                   |          |         |                | (to be connected to OUT_ANT by user's PCB)        |

| 8   | GND               |          | GND     | GND            | GND                                               |

| 9   | VDDCORE           |          | PWR     | VCC            | Internally generated power supply,                |

| 10  | VDDBAT            |          | PWR     | VCC            | Power supply 1.8 to 3.6V,                         |

|     |                   |          |         |                | require 10uF capacitor.                           |

| 11  | LPCLKBUS          | INOUT    | ANA     | DIRIO          | Please use this pin open.                         |

| 12  | LPCLKIN           | INOUT    | ANA     | DIRIO          | Low Power clock input                             |

| 13  | REGC              | OUT      | ANA     | DIRIO          | REGOUT, require 10uF capacitor.                   |

| 14  | EFUSE             |          | DIG     | DIRIO          | Control signal for EFUSE programming,             |

| 45  | ODIDIN            | 15.1     | DIO     | 01400          | fix to GND for normal usage                       |

| 15  | SPIDIN            | IN       | DIG     | CMOS,          | Data input for SPI slave                          |

| 16  | SPIDOUT           | INOUT    | DIG     | IN<br>CMOS,    | Data output for SPI slave                         |

| 10  | SFIDOUT           | INOUT    | DIG     | BiDIR          | Data output for SFT slave                         |

| 17  | SPIXCS            | IN       | DIG     | CMOS,          | Chip select for SPI slave                         |

| ''  | 01 17.00          | 111      | Dio     | IN             | Only select for or I slave                        |

| 18  | SPICLK            | IN       | DIG     | CMOS,          | Clock input for SPI slave                         |

|     | 01.1021           |          | 5.0     | IN             | Stock input for or relate                         |

| 19  | GND               |          | GND     | GND            | GND                                               |

| 20  | UART_TXD          | OUT      | DIG     | CMOS,          | Data TX port for UART                             |

|     | _                 |          |         | OUT            |                                                   |

| 21  | UART_RXD          | IN       | DIG     | CMOS,          | Data RX port for UART                             |

|     |                   |          |         | IN             |                                                   |

| 22  | GND               |          | GND     | GND            | GND                                               |

| 23  | SDA               | INOUT    | DIG     | CMOS,          | SDA data port for I2C                             |

|     |                   |          |         | BiDIR          |                                                   |

| 24  | SCL               | INOUT    | DIG     | CMOS,          | SCL clock port for I2C                            |

|     | ODIO0/DE 4.0TI)/E | IN IOLIT | DIO.    | BiDIR          | ODIO: UDE A II                                    |

| 25  | GPIO0/RF_ACTIVE   | INOUT    | DIG     | CMOS,          | GPIO inout/RF_Active                              |

| 26  | CDIO1ANAKEUD      | INOUT    | DIC     | BiDIR          | CDIO inquit/M/AKELID                              |

| 26  | GPIO1/WAKEUP      | INOUT    | DIG     | CMOS,<br>BiDIR | GPIO inout/WAKEUP                                 |

| 27  | GPIO2/IRQ         | INOUT    | DIG     | CMOS,          | GPIO inout/IRQ                                    |

| "   | Si iOZ/ii\Q       | 111001   | 210     | BiDIR          |                                                   |

| 28  | GPIO3/PS_CONTR    | INOUT    | DIG     | CMOS,          | GPIO inout/external switch control (Q1)           |

|     | OL                |          | 2.3     | BiDIR          | (To be connected to FETGATE by user's PCB.)       |

| 29  | FETGATE           | IN       | DIG     |                | Gate control Pin of internal FET (To be connected |

|     |                   |          |         |                | to PS_CONTROL by user's PCB.)                     |

| 30  | TMODE             | IN       | DIG     | CMOS,          | Test mode control, fix to GND for normal usage    |

|     |                   |          |         | IN             |                                                   |

| 31  | RESETB            | IN       | DIG     | CMOS,          | Reset, low active                                 |

|     |                   |          |         | IN             |                                                   |

| 32  | A0                | IN       | ANA     | DIRIO          | Analog Test Pin0                                  |

| 33  | A1                | IN       | ANA     | DIRIO          | Analog Test Pin1                                  |

| 34  | NC                |          |         |                | No connection (※Refer to PIN descriptions.)       |

| 35  | ANT_GND           |          |         |                | Antenna GND(※Refer to PIN descriptions.)          |

| 36    | NC      | <br>    |     | No connection (※Refer to PIN descriptions.) |

|-------|---------|---------|-----|---------------------------------------------|

| 37-48 | ANT_GND | <br>    |     | Antenna GND(**Refer to PIN descriptions.)   |

| 49-52 | GND     | <br>GND | GND | GND                                         |

# ■PIN descriptions

$\label{eq:lossymbol} \text{I/O symbol} \quad \text{I}_{\text{RF}} \qquad : \quad \text{RF input output pin}$

I : Digital input pin

$\begin{array}{lll} I_{pd} & : & \text{Digital input with pull-down resistor} \\ I_{AH} & : & \text{Analog High voltage input pin} \\ I_{SH} & : & \text{Low power clock input pin} \\ X_{SH} & : & \text{Low power clock oscillator pin} \end{array}$

$\begin{array}{lll} O_2 & : & \text{Digital output pin with 2mA load capability} \\ B_2 & : & \text{Digital bidirectional pin with 2mA load capability} \end{array}$

B<sub>2</sub>P<sub>U</sub> : Digital bidirectional pin with 2mA load capability and pull-up resistor

## ●RF, Analog signals

| #  | Pin Name | Status/Value at reset | I/O              | Active<br>Level | Function                                                       |

|----|----------|-----------------------|------------------|-----------------|----------------------------------------------------------------|

| 6  | OUT_ANT  |                       | $I_{RF}$         |                 | Output from Antenna (to be connected to OUT_MOD by user's PCB) |

| 7  | OUT_MOD  |                       | I <sub>RF</sub>  |                 | Output from Module (to be connected to OUT_ANT by user's PCB)  |

| 32 | A0       | Hi-Z                  | $I_{AH}$         |                 | Analog test pin0                                               |

| 33 | A1       | Hi-Z                  | I <sub>AH,</sub> |                 | Analog test pin1                                               |

## ●XO、LPXO signals

| #  | Pin Name | Status/Value at reset | I/O                               | Active<br>Level | Function                  |

|----|----------|-----------------------|-----------------------------------|-----------------|---------------------------|

| 11 | LPCLKBUS | 0V                    | X <sub>SH</sub>                   |                 | Please use this pin open. |

| 12 | LPCLKIN  | I <sub>SH</sub>       | $X_{\text{SH}}$ , $I_{\text{SH}}$ |                 | Low power clock input     |

### ●SPI signals

| #  | Pin Name | Status/Value at reset | I/O | Active<br>Level | Function              |

|----|----------|-----------------------|-----|-----------------|-----------------------|

| 15 | SPIDIN   | Input                 | I   |                 | SPI SLAVE Data input  |

| 16 | SPIDOUT  | Input                 | B2  |                 | SPI SLAVE Data output |

| 17 | SPIXCS   | Input                 | - 1 | Low             | SPI SLAVE Chip Select |

| 18 | SPICLK   | Input                 | I   |                 | SPI SLAVE Clock       |

## UART signals

| #  | Pin Name | Status/Value at reset | I/O            | Active<br>Level | Function        |

|----|----------|-----------------------|----------------|-----------------|-----------------|

| 20 | UART_TXD | Output High           | O <sub>2</sub> |                 | UART TXD output |

| 21 | UART_RXD | Input                 | lpd            |                 | UART RXD input  |

●I2C signals

| #  | Pin Name | Status/Value at reset | I/O               | Active<br>Level | Function                                       |

|----|----------|-----------------------|-------------------|-----------------|------------------------------------------------|

| 24 | SCL      | Input                 | B <sub>2</sub> PU |                 | I2C_SCL monitor pin.Please use this pin open.  |

| 23 | SDA      | Input                 | B <sub>2</sub> PU |                 | I2C_SDA monitor pin. Please use this pin open. |

GPIO signals

| #  | Pin Name             | Status/Value at reset | I/O | Active<br>Level | Function                                                                                                        |

|----|----------------------|-----------------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------|

| 25 | GPIO0<br>/RF_ACTIVE  | Output Low            | B2  |                 | GPIO inout/RF_ACTIVE output (default: RF_ACTIVE)                                                                |

| 26 | GPIO1<br>/WAKEUP     | Input                 | B2  |                 | GPIO inout/WAKEUP input (default: WAKEUP)                                                                       |

| 27 | GPIO2<br>/IRQ        | Output High           | B2  |                 | GPIO inout/IRQ output (default: IRQ)                                                                            |

| 28 | GPIO3<br>/PS_CONTROL | Output Low            | B2  |                 | GPIO inout/Control signal for external Switch (default: PS_CONTROL) (To be connected to FETGATE by user's PCB.) |

Miscellaneous signals

|    | arreede eignale |                       |     |                 |                                                                       |

|----|-----------------|-----------------------|-----|-----------------|-----------------------------------------------------------------------|

| #  | Pin Name        | Status/Value at reset | I/O | Active<br>Level | Function                                                              |

| 31 | RESETB          | Input                 | I   | Low             | Reset input (Low = Reset)                                             |

| 14 | EFUSE           |                       |     |                 | E-Fuse writing voltage supply(Fixed to Low)                           |

| 30 | TMODE           | Input                 | I   |                 | TESTMODE input (Fixed to Low)                                         |

| 29 | FETGATE         | Input                 | ı   |                 | FET gate control input (To be connected to PS_CONTROL by user's PCB.) |

● Regulator signal

| #  | Pin Name | Status/Value at reset | I/O | Active<br>Level | Function                                                       |

|----|----------|-----------------------|-----|-----------------|----------------------------------------------------------------|

| 9  | VDDCORE  |                       |     |                 | Internally generated power supply. (Note)Don't short this pin. |

| 13 | REGC     | 1.2V 出力               |     |                 | Pin for de-coupling capacitor, require 10uF capacitor.         |

Power supply and Ground

| #     | Pin Name | Status/Value at reset | I/O | Active<br>Level | Function                                         |

|-------|----------|-----------------------|-----|-----------------|--------------------------------------------------|

| 10    | VDDBAT   |                       |     |                 | Power supply 1.8 to 3.6V,require 10uF capacitor. |

| 8     | GND      |                       |     |                 | GND                                              |

| 19    | GND      |                       |     |                 | GND                                              |

| 22    | GND      |                       |     |                 | GND                                              |

| 49-52 | GND      |                       |     |                 | GND                                              |

●ANT\_GND signals

| #                    | Pin Name | Status/Value at reset | I/O | Active<br>Level | Function                                                                                                                                                                                           |

|----------------------|----------|-----------------------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,3-4<br>35<br>37-48 | ANT_GND  |                       |     |                 | Antenna GND pins.  ANT_GND pins has to be connected to board, but not to be connected any components on board.  (Note) The pins are connected to GND in the module, but please use this pins open. |

NC signals

| #            | Pin Name | Status/Value at reset | I/O | Active<br>Level | Function                                                                                                          |

|--------------|----------|-----------------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------|

| 2,5<br>34,36 | NC       |                       |     |                 | NC pins has to be connected to board, but not to be connected any components on board. Please use this pins open. |

## Unused pins

Followings are recommendation for unused pins.

| #                 | Pin Name         | Recommendation                                                                                    |

|-------------------|------------------|---------------------------------------------------------------------------------------------------|

| 2,5,34,36         | NC               | OPEN(NC pins has to be connected to board, but not to be connected any components on board.)      |

| 1,3-4,35<br>37-48 | ANT_GND          | Open(ANT_GND pins has to be connected to board, but not to be connected any components on board.) |

| 11                | LPCLKBUS         | Open                                                                                              |

| 14                | EFUSE            | Fix to 0V                                                                                         |

| 15                | SPIDIN           | Fix to High                                                                                       |

| 16                | SPIDOUT          | Fix to High                                                                                       |

| 17                | SPIXCS           | Fix to High                                                                                       |

| 18                | SPICLK           | Fix to High                                                                                       |

| 20                | UART_TXD         | Open                                                                                              |

| 21                | UART_RXD         | Fix to Low (See section for operating mode)                                                       |

| 23                | SDA              | Open (Pull-up resistor in the module)                                                             |

| 24                | SCL              | Open (Pull-up resistor in the module)                                                             |

| 25                | GPIO0/RF_ACTIVE  | Open                                                                                              |

| 26                | GPIO1/WAKEUP     | Fix to High or Low<br>See section for operating mode                                              |

| 27                | GPIO2/IRQ        | Open                                                                                              |

| 28                | GPIO3/PS_CONTROL | To be connected to FETGATE by user's PCB.                                                         |

| 29                | FETGATE          | To be connected to PS_CONTROL by user's PCB.                                                      |

| 32                | A0               | Open                                                                                              |

| 33                | A1               | Open                                                                                              |

## Remarks

If input pins are left open with High Impedance status, significant current consumption might be observed. All input pins have to be fixed high or low level to avoid such current consumption.

## **■**Electrical Characteristics

## Absolute Maximum Rating

| Item                             | Symbol | Condition             | Rating          | Unit  |

|----------------------------------|--------|-----------------------|-----------------|-------|

| Power supply (*1)                | VDDBAT |                       | -0.3 to +4.6    | V     |

| Digital input voltage (*2)       | Vdin   |                       | -0.3 to VDD+0.3 | V     |

| Digital output voltage (*3)      | VDO    | Ta = -20 to +70 deg.C | -0.3 to VDD+0.3 | V     |

| Analog HV IO voltage (*4)        | Vah    | GND=0V                | -0.3 to VDD+0.3 | V     |

| Digital IO load current (*2)(*3) | IDO    |                       | –10 to +10      | mA    |

| Analog IO current (*4)           | lA     |                       | −2 to +2        | mA    |

| Power Dissipation                | Pp     |                       | T.B.D.          | W     |

| Storage temperature              | Tstg   | -                     | -40 to +85      | deg.C |

(\*1) VDDBATpin

(\*2) IO pins with I, IPD, B2 symbol in pin definition (\*3) IO pins with O<sub>2</sub>,B<sub>2</sub> symbol in pin definition (\*4) IO pins with IAH, I<sub>SH</sub>, X<sub>SH</sub>, symbol in pin definition

Recommended Operating Conditions

| Item                                | Symbol           | Condition                                              | Min         | Тур    | Max         | Unit |

|-------------------------------------|------------------|--------------------------------------------------------|-------------|--------|-------------|------|

| Power Supply                        | VDD              | VDDBAT pin                                             | 1.8         | 3.3    | 3.6         | ٧    |

| Ambient Temperature                 | Ta               | -                                                      | -20         | +25    | +70         | °C   |

| Rising time digital input pins      | t <sub>IR1</sub> | Digital input/inout pins                               | _           | _      | 20          | Ns   |

| Falling time digital input pins     | t <sub>IF1</sub> | Digital input/inout pins                               | _           | _      | 20          | Ns   |

| Load capacitance digital            | CDL              | Digital output/inout pins                              | _           | _      | 20          | pF   |

| Low Power Clock<br>(32.768 kHz)     | FLPCK1           | LPCLKIN pin                                            | –250<br>ppm | 32.768 | +250<br>ppm | kHz  |

| Low Power Clock<br>Input Duty Ratio | DLPCK1           | External input from LPCLKIN,<br>LPCLKBUS pin left OPEN | 30          | 50     | 70          | %    |

| RF Channel frequency (*1)           | FRF              | OUT_MOD pin                                            | 2402        | _      | 2480        | MHz  |

| RF input level                      | Prfin            | _                                                      | -70         | _      | -10         | dBm  |

(\*1) Frequency range F = 2402 + 2 x k [MHz]here k=0, 1,2,...,39.

## Current consumption

(Ta = 25 deg.C)

| Item                | Symbol | Condition                                   | Min | Тур  | Max | Unit |

|---------------------|--------|---------------------------------------------|-----|------|-----|------|

|                     | IDD1   | Deep Sleep state (External Low Power Clock) | -   | 0.8  | ı   | uA   |

|                     | IDD2   | Idle state                                  | -   | 3    | -   | mA   |

| Current Consumption | IDD3   | RF RX state                                 | -   | 9    | ı   | mA   |

| ·                   | lpp4   | RF TX state (-6dBm)                         | -   | 9    | -   | mA   |

|                     | IDD4   | RF TX state (0dBm)                          | -   | 10.9 | ı   | mA   |

(note) Condition:Ta=25dec.C, VDDBAT=3.3V

## DC characteristics

(Ta = -20 to +70 deg.C)

| Item                                 | Symbol | Condition                  | Min                    | Тур | Max                    | Unit |

|--------------------------------------|--------|----------------------------|------------------------|-----|------------------------|------|

| H level Voltage Input                | VIH1   | (*1) (*2) (*5)             | VDD<br>X0.7            | -   | VDD                    | V    |

| L level Voltage input                | VIL1   | (*1) (*2) (*5)             | 0                      | -   | VDD<br>X0.3            | V    |

| LPCLKIN pin<br>H level Voltage Input | VIH2   | (*3)                       | 1                      | -   | VDD                    | V    |

| LPCLKIN pin L level Voltage input    | VIL2   | (*3)                       | 0                      | -   | 0.3                    | V    |

| H level Voltage Output               | Vон    | Iон = -2mA (*4) (*5)       | V <sub>DD</sub> × 0.75 | -   | VDD                    | V    |

| L level Voltage Output               | Vol    | IoL = 2mA (*4) (*5)        | 0                      | _   | V <sub>DD</sub> × 0.25 | V    |

| Input pin capacitance                | CIN    | F=1MHz (*1) (*2) (*4) (*5) | _                      | 8   | _                      | pF   |

<sup>(\*1)</sup> IO pins with I symbol in pin definition

(\*2) IO pins with IPD symbol in pin definition

(\*3) IO pins with ISH symbol in pin definition

(\*4) IO pins with O2 symbol in pin definition

(\*5) IO pins with B2 symbol in pin definition

### RF Characteristics

(Ta = -20 to +70 deg.C)

|                                |                      |                                 |      |      | (1a 20 | to 170 acg.c |

|--------------------------------|----------------------|---------------------------------|------|------|--------|--------------|

| Item                           | Symbol               | Condition                       | Min  | Тур  | Max    | Unit         |

| TX                             |                      |                                 |      |      |        |              |

| Maxium TX power                | P <sub>OUT</sub>     | 0dBm setting                    | -    | 0    | _      | dBm          |

| Centre Frequency tolerance     | F <sub>CERR</sub>    | Master Clock tolerance < 40 ppm | -40  | _    | 40     | ppm          |

| Modulation data rate           | D <sub>RATE</sub>    | _                               | -    | 1    | _      | Mbps         |

| Modulation index               | F <sub>IDX</sub>     | _                               | 0.45 | 0.50 | 0.55   | _            |

| Bandwidth-bit rate products BT | ВТ                   | GFSK                            | _    | 0.5  | _      | _            |

| RX                             |                      |                                 |      |      |        |              |

| Receiver Sensitivity           | P <sub>SENS</sub>    | PER =30.8% (*1)                 | _    | -85  | -70    | dBm          |

| Maximum input level(*2)        | P <sub>RXMAX</sub>   | PER=30.8% (*1)                  | -    | -    | -10    | dBm          |

|                                | P <sub>RSSIMAX</sub> | Upper                           | -50  | -    | -      | dBm          |

| RSSI detection range           | P <sub>RSSIMIN</sub> | Lower                           | _    | _    | -80    | dBm          |

(\*1) PER=30.8% is corresponding to BER=0.1%

(\*2) Condition: Ta =  $25^{\circ}$ C \ VDDHV = 3.3V

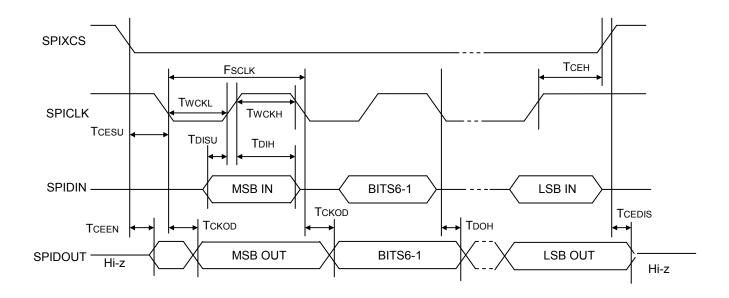

### ●SPI interface

$(Ta = -20 \sim +70 ^{\circ}C)$

| Item                             | Symbol | Condition                   | Min     | Тур    | Max | Unit |

|----------------------------------|--------|-----------------------------|---------|--------|-----|------|

| SPICLK Clock Frequency           | Fsclk  |                             | 16.384  | 32.768 | 500 | kHz  |

| SPIXCS input setup time          | Tcesu  |                             | 1/Fsclk | -      | -   | ms   |

| SPIXCS input hold time           | Тсен   |                             | 1/Fsclk | -      | -   | ms   |

| SPICLK high pluse width          | Twckh  |                             | 250     | _      | _   | ns   |

| SPICLK low pluse width           | Twckl  |                             | 250     | _      | _   | ns   |

| SPIDIN input setup time          | Toisu  | Load capacitance<br>CL=20pF | 5       | -      | -   | ns   |

| SPIDIN input hold time           | TDIH   | OL-20pi                     | 250     | -      | -   | ns   |

| SPICLK output delay time         | Тскор  |                             | -       | -      | 250 | ns   |

| SPIDOUT output hold time         | Трон   |                             | 5       | -      | -   | ns   |

| SPIXCS output enable delay time  | TCEEN  |                             | 0       | _      | 300 | ns   |

| SPIXCS output disable delay time | TCEDIS |                             | 150     | _      |     | ns   |

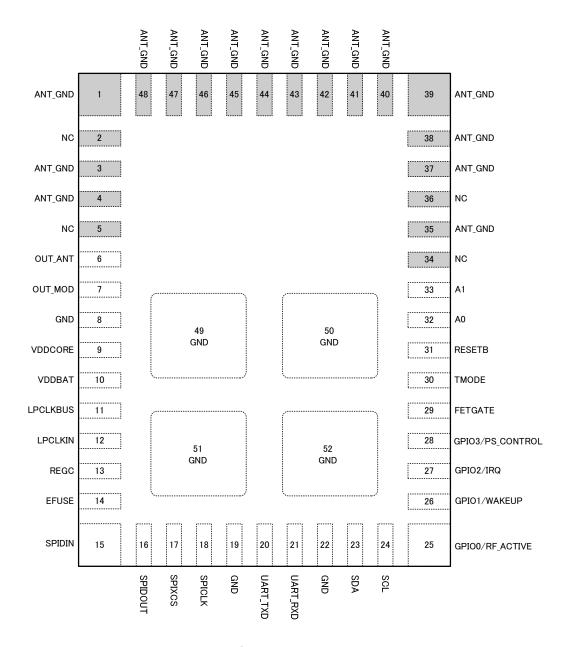

Remarks: All timing specification is defined at VDDIO x 20% and VDDIO x 80% SPIXCS input setup/hold time have to be at least 1cycle of SPICLK clock frequency

### Measurement point

(\*) SPIDOUT becomes Hi-Z input when SPIXCS is High.So please insert the pull-up or pull-down resister .

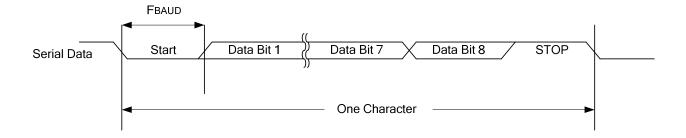

### ■UART interface

(Ta = -20 to +70 deg.C)

| Item      | Symbol | Condition                   | Min | Тур   | Max | Unit    |

|-----------|--------|-----------------------------|-----|-------|-----|---------|

| Baud Rate | FBAUD  | Load capacitance<br>CL=20pF | -   | 57600 | -   | bps(Hz) |

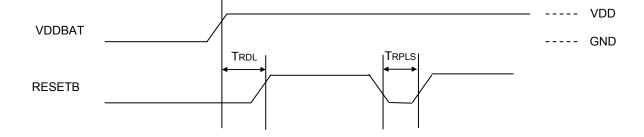

### Reset operation

(Ta = -20 to +70 deg.C)

| Item                                     | Symbol | Condition                      | Min | Тур | Max | Unit |

|------------------------------------------|--------|--------------------------------|-----|-----|-----|------|

| RESETB propagation delay time (Power on) | TRDL   | Start supplying power (VDDBAT) | 20  | ı   | -   | ms   |

| Reset pulse width                        | TRPLS  | RESETB pin                     | 1   | -   | -   | us   |

### Power on reset function

### Reset function from RESETB pin

It is possible to reset internal circuit by asserting RESETB after power supply is on.

It is possible to reset internal circuit by same way even if it is not power sequence. Internal circuit will move to normal state after oscillation circuit become stable by clock stabilizing circuit after reset function.

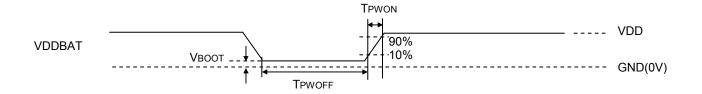

### Power on

(Ta = -20 to +70 deg.C)

| Item                | Symbol | Condition                        | Min | Тур | Max | Unit |

|---------------------|--------|----------------------------------|-----|-----|-----|------|

| VDD pin rising time | Tpwon  | While power on VDD pins (VDDBAT) | 0.2 | 1   | 5   | ms   |

| Power off Time      | Tpwoff | VDD pins(VDDBAT)                 | 10  | -   | -   | ms   |

| Initial power level | Vвоот  | VDD pins(VDDBAT)                 | -   | -   | 0.3 | V    |

## ■Operating mode

Following 3 operating modes are available to use

BACI Mode: Application mode using SPI-SLAVE interface

HCI Mode: HCI mode (Bluetooth LE standard compliant) using UART interface.

RAM Mode: Function extention mode downloading user program to internal memory

## ■Operating mode configuration

Configuration of operating mode will be done by pin status shown in table below. The symbol "X" is don't care, it has to be used as normal function. When configure operating mode, reset has to be issued.

RAM mode and Debug mode is distinguished by configuration parameter.

| Operating mode | Pin confitions |

|----------------|----------------|

| Operating mode | UART_RXD       |

| BLI Mode       | Low            |

| HCI Mode(*1)   | High           |

| RAM Mode       | Х              |

<sup>(\*1)</sup>Please fix wakeup pin to low level when using in HCl mode.

Please refer to ML7105C-001 data sheet and associtated documentation for more detail.

## ■ Module dimension

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact a ROHM sales office for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

## ■Application example

- (\*1) SPIDOUT becomes Hi-Z input when SPIXCS is High.So please insert the pull-up or pull-down resister .

- (\*2) Please be careful to satisfy the RESETB propagation delay time( $T_{RDL}$ ). And if the state of reset signal is undefined after power on reset of HOST-CPU, please insert the pull-up or pull-down resistor.

# ■Appendix

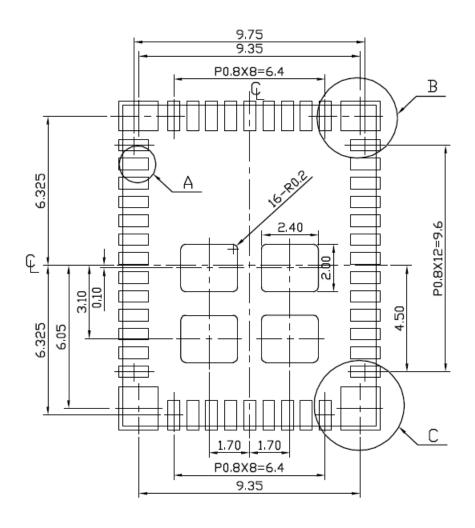

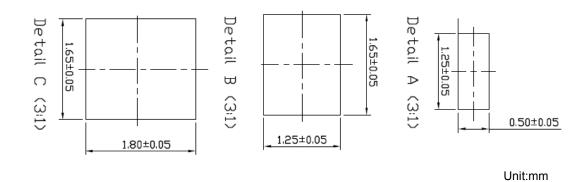

## ●PCB Land Pattern

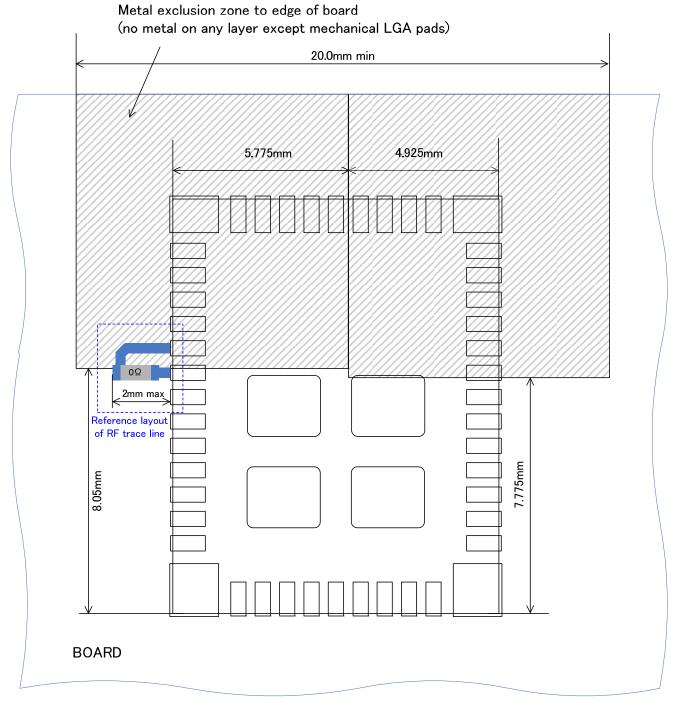

## ● Metal Keep-Out Area / Reference layout of RF trace line

TOP VIEW

#### Radio certitication

#### MIC JAPAN(certification no:006-000238)

MK71050-03 complies with MIC JAPAN radio certification.(certification no:006-000238)

#### FCC (FCC ID: 2ACIJ71050-3)

This device complies with Part 15 of the FCC Rules.

Operation is subject to the following two conditions:

(1)this device may not cause harmful interference, and (2)this device must accept any interference received, including interference that may cause undesired operation.

The regulatory label on the final system must include the statement: "Contains FCC ID: 2ACIJ71050-3" or using electronic labeling method as documented in KDB 784748.

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment.

The antenna used for this transmitter must not be collocated or operating in conjunction with any other antenna or transmitter within a host device, except in accordance with FCC multi-transmitter product procedures.

The final system integrator must ensure there is no instruction provided in the user manual or customer documentation indicating how to install or remove the transmitter module except such device has implemented two-ways authentication between module and the host system.

### OEM Responsibilities to comply with FCC Regulations

This module has been certified for integration into products only by OEM integrators under the following condition:

- The transmitter module must not be colocated or operating in conjunction with any other antenna or transmitter.

As long as the conditions above are met, further transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

### IMPORTANT NOTE:

In the event that any of these conditions can not be met (for example the reference trace specified in this manual, or use of a different antenna), then the FCC authorization is no longer considered valid and the FCC ID can not be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC authorization.

### CE(R&TTE)

MK71050-03 complies with the radio test requirements (EN 300 328 V1.8.1) ,which is based on the R&TTE Directive (1999/5/EC).

EMC and Safety test that is required for the CE marking should be done in the final end-product.

#### Bluetooth SIG Qualification(End Product)

MK71050-03 is listed on the Bluetooth SIG website as qualified End Products. (QDID:66491)

## ■ Caution

When implementing this product to double-sided printed board, please do not implement this product for the first time reflow side.( Opposite side reflow is prohibited due to module weight.)

•Shield case may be discolored ,but there is no influence to the product performance and quality.

# ■ Revision History

| Document<br>No. | Date        | Page                |                    |                 |

|-----------------|-------------|---------------------|--------------------|-----------------|

|                 |             | Previous<br>Edition | Current<br>Edition | Description     |

| FEDK71050-03-01 | Apr,10,2015 | _                   | _                  | Final edition 1 |

## Precautions for the Specification

- 1) Contents of the Specification are the information at the time of their issuance. The information contained herein is subject to change without notice.

- 2) LAPIS Semiconductor has used reasonable care in preparing the information included in the Specification, but LAPIS Semiconductor does not warrant that such information is error free. LAPIS Semiconductor assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 4) The Specification contains information related to the LAPIS Semiconductor's copyright and technical know-how. Any use of them other than pertaining to the usage of appropriate products is not permitted. Further, the Specification, in part or in whole, may not be reprinted or reproduced and disclosed to third parties without prior consent of LAPIS Semiconductor.

### Precautions for the Products

### Precautions for Safety

- 1) The Products are designed and produced for application in ordinary electronic equipment (AV equipment, OA equipment, telecommunication equipment, home appliances, amusement equipment, etc.).

- 2) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 3) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 4) The Products are designed for use in a standard environment and not in any special environments. Application of the Products in a special environment can deteriorate product performance. Accordingly, verification and confirmation of product performance, prior to use, is recommended if used under the following conditions:

- [a] Use in various types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use outdoors where the Products are exposed to direct sunlight, or in dusty places

- [c] Use in places where the Products are exposed to sea winds or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use in places where the rPoducts are exposed to static electricity or electromagnetic waves

- [e] Use in environment subject to strong vibration and impact.

- [f] Use in proximity to heat-producing components, plastic cords, or other flammable items

- [g] Use involving sealing or coating the Products with resin or other coating materials

- [h] Use of the Products in places subject to dew condensation

- 5) The Products might receive the radio wave interference from electronic devices such as Wireless LAN devices, Bluetooth devices, digital cordless telephone, microwave oven and so on that radiate electromagnetic wave.

- 6) The Products are not radiation resistant.

- 7) Verification and confirmation of performance characteristics of Products, after on-board mounting, is advised.

- 8) Confirm that operation temperature is within the specified range described in the Specification.

- 9) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, if product malfunctions may result in serious damage, including that to human life, sufficient fail-safe measures must be taken, including the following:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits in the case of single-circuit failure

- 10) Failure induced under deviant condition from what defined in the Specification can not be guaranteed.

- 11) This product is a specification to radiate the radio wave. It is necessary to acquire the attestation of decided Radio Law of each region used to use the equipment that radiates the radio wave.

Please inquire about the attestation of Radio Law that this product acquires.

- 12) When product safety related problems arises, please immediately inform to LAPIS Semiconductor, and consider technical counter measure.

### Precautions for Reference Circuits

- 1) If change is made to the constant of an external circuit, allow a sufficient margin due to variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- 2) The reference circuit examples, their constants, and other types of information contained herein are applicable only when the Products are used in accordance with standard methods. Therefore, if mass production is intended, sufficient consideration to external conditions must be made.

### • Precaution for Electrostatic

This product is Electrostatic sensitive product, which may be damaged due to Electrostatic discharge. Please take proper caution during manufacturing and storing so that voltage exceeding Product maximum rating won't be applied to the Products. Please take special care under dry condition (Grounding of human body / equipment / solder iron, isolation from charged objects, setting of Ionizer, friction prevention and temperature / humidity control etc.)

### • Precautions for Storage / Transportation

- 1) Product performance and connector mating may deteriorate if the Products are stored in the following places:

- [a] Where the Products are exposed to sea winds or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub> and NO<sub>2</sub>

- [b] Where the temperature or humidity exceeds those recommended by LAPIS Semiconductor Temperature: 5°C to 40°C, Humidity 40% to 60%

- [c] Storage in direct sunshine or condensation.

- [d] Storage in high Electrostatic.

- 2) Even under LAPIS Semiconductor recommended storage condition, connector mating, mountability, and heat resistance of products over 1 year old may be degraded.

- 3) Store / transport cartons in the correct direction, which is indicated on a carton as a symbol, otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

### • Precaution for Product Label

QR code printed on LAPIS Semiconductor product label is only for internal use, and please do not use at customer site. It might contain internal products information that is inconsistent with product information.

#### • Precaution for Disposition

When disposing Products, please dispose them properly with a industry waste company.

#### • Prohibition Regarding Intellectual Property

LAPIS Semiconductor prohibits the purchaser of the Products to exercise or use the intellectual property rights, industrial property rights, or any other rights that either belong to or are controlled by LAPIS Semiconductor, other than the right to use,

sell, or dispose of the Products.

### • The other precautions

- Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS

Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor

shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 2) When providing our Products and technologies contained in the Specification to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

Copyright 2015 LAPIS Semiconductor Co., Ltd.

## LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/