# MK eMMC Specification eMMC5.10

AMC: Confilder

www.mkfounder.com

# **Product List**

MKEMF032GZ1E-C 32GB eMMC

# **Revision History**

| Version                             | Date               | Description                                      |            |

|-------------------------------------|--------------------|--------------------------------------------------|------------|

| Rev 1.0                             | 2021/02/01         | Released                                         |            |

|                                     |                    |                                                  | <i>b</i> . |

|                                     |                    |                                                  | *9,        |

|                                     |                    |                                                  | iletan     |

|                                     |                    |                                                  |            |

|                                     |                    |                                                  | 2          |

|                                     | nder               | roved by MK Founder semiconductor co., LTD.      |            |

| <i>Notice :</i> The datasheet is pr | epared and appr    | roved by MK Founder semiconductor co., LTD.      |            |

| MK Founder reserv                   | es the right to cl | nange products or specifications without notice. |            |

#### Notice:

MK Founder reserves the right to change products or specifications without notice. ©2021 MK Founder semiconductor co., LTD. All rights reserved.

| Table of Contents                 |      |

|-----------------------------------|------|

| 1. Description                    | 5-   |

| 2. Product List                   | 5 -  |

| 3. Features                       | 5 -  |

| 4. Functional Block Diagram       | 6 -  |

| 5. e-MMC Device and System        | 7-   |

| 5.1 e-MMC System Overview         | 7 -  |

| 5.2 e-MMC Device Overview         | 8-   |

| 6. e·MMC 5.1 Feature Overview     | 9-   |

| 6.1 Boot                          | 9-   |

| 6.2 Sleep (CMD5)                  | 9-   |

| 6.3 Bus Modes                     | 10 - |

| 6.4 Reliable Write                | 11 - |

| 6.5 Secure Erase                  | 11 - |

| 6.6 Secure Trim                   | 12 - |

| 6.7 Trim                          | 12 - |

| 6.8 Partition Management          | 12 - |

| 6.9 High priority integrupt (HPI) | 13 - |

| 6.10 Background Operations        | 13 - |

| 6. 11 H/W Reset                   | 13 - |

| 6.12 Packed Commands              | 13 - |

| 6.13 Cache                        |      |

| 6-14 Discard                      | 14 - |

| 6-15 Sanitize                     |      |

| 6-16 Dynamic Capacity Management  |      |

| 7. Product Specifications         |      |

|                                   |      |

| 7-1 Power Consumption              | 15 -         |

|------------------------------------|--------------|

| 7-2 Performance                    | 15 -         |

| 7-3 Operating Conditions           | 15 -         |

| 7-4 Physical Specification         | 15 -         |

| 8. Interface Description           | 18-          |

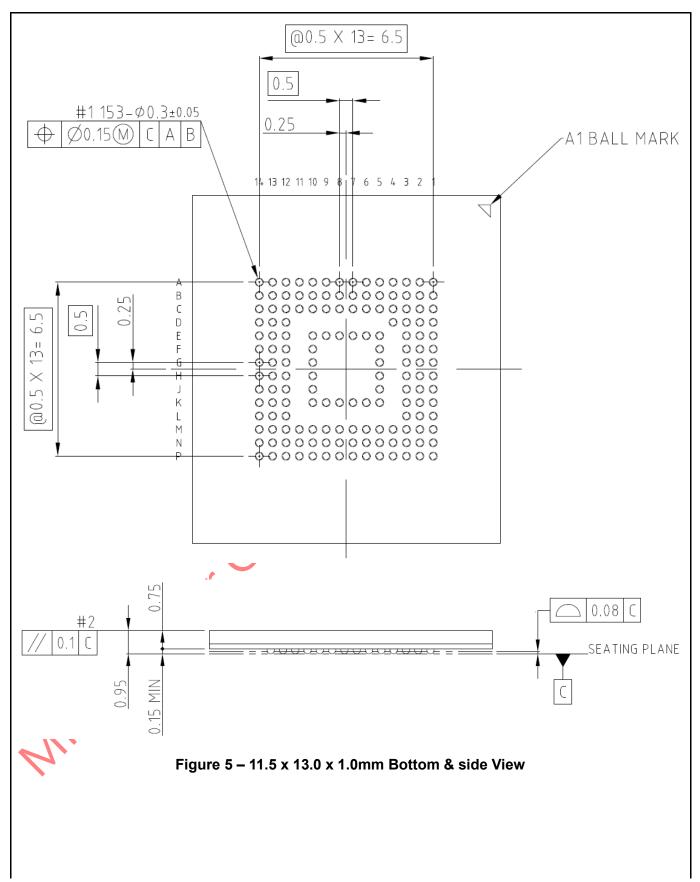

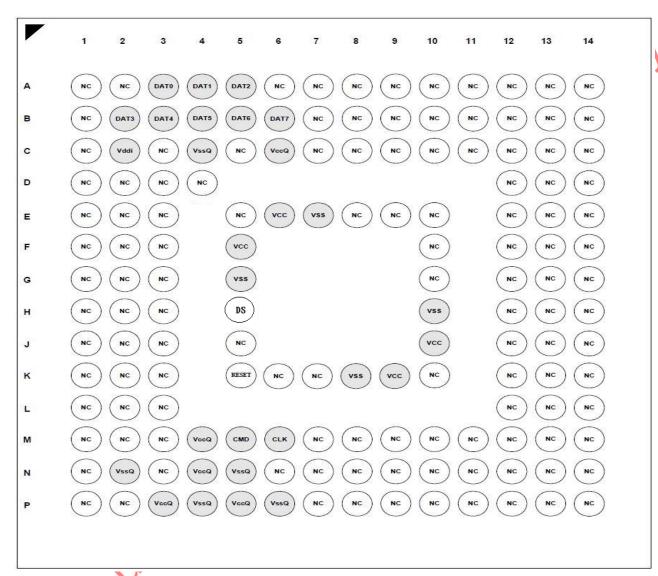

| 8-1 e·MMC Interface ball array     | 18 -         |

| 8-2 Pins and Signal Description.   | 18 -         |

| 9. Device Resisters                | 20 -         |

| 9.1 Operating Condition Resister   | r (OCR) 20 - |

| 9.2 Card Identification Resister ( | CID)         |

| 9-3 Card Specific Data Resister    | (CSD)        |

| 9-4 Extended CSD Resister          | 22 -         |

| MK Founder Cons                    |              |

# 1. Description

MK Founder e·MMC is an embedded flash memory storage solution.

MK Founder e·MMC is a hybrid device combining an embedded flash controller include LDPC based ECC and flash memory, with JEDEC Standard e·MMC 5.1 interface.

The e·MMC controller include LDPC based ECC directs the Flash management, including ECC, wear-leveling, IOPS optimization and read sensing, significantly reducing the storage management burden of the host CPU.

e·MMC is an ideal storage solution for many electronics devices. e·MMC designed to cover a wide area of application such as smart phones, Tablet PCs, Mobile phones, PDAs, Handheld electronics, Digital video cameras, Multimedia equipment, etc. Not only used in consumer products, e·MMC is being adopted rapidly in embedded applications, such as many Computer on Module designs, because of its compact size, low power consumption and many enhanced feature.

The technology specifications of e·MMC are managed by JEDEC, the global leader in developing open standards for the microelectronics industry.

## 2. Product List

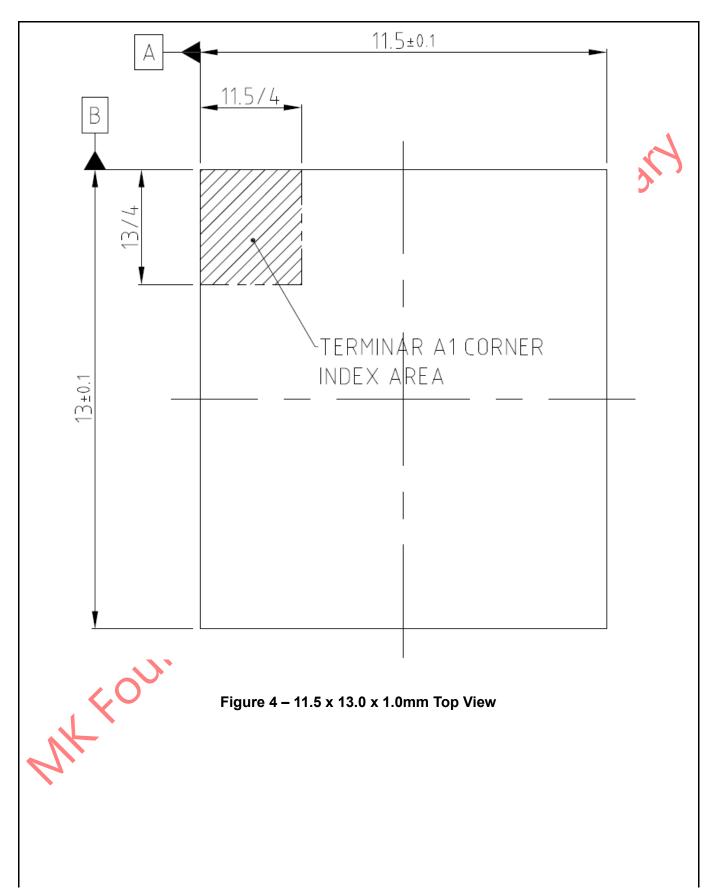

| Density | Part Number    | Package | PKG size (mm)     | Remark  |

|---------|----------------|---------|-------------------|---------|

| 32GB    | MKEMF032GZ1E-C | FBGA153 | 11.5 x 13.0 x 1.0 | 1 stack |

|         |                |         |                   |         |

|         | ounder         |         |                   |         |

## <u>3. Features</u>

- Support JEDEC/ e•MMC 5.1 Compliant

- Support 3.3V/1.8V power supply

- Support 12 wire bus (CLK, CMD, Data Strobe, DAT[7:0] and hardware reset (RST n))

- Up to 400MHz clock speed

- Support Single Data Rate(SDR) and Dual Data Rate(DDR)

- Support different Bus width: 1bit, 4bit, 8bit

- Support Original Boot and Alternative Boot modes

- Support Data Removal (Erase, Trim and Sanitize)

- Support Replay Protected Memory Block(RPMB)

- Support Multiple Partitions with enhanced attribute

- Support Lock/Unlock and Write Protection

- Support Data Protection for Power Failure

- Support Power Saving Sleep Mode

- Support High Priority Interrupt(HPI)

- Support Background Operation

- Support Packed Commands

- Support Sampling Tuning Sequence

- Support Dynamic Power Manager : standby and sleep modes

- Support Command Queuing

- Support Secure Write Protection

- Package size

- 11.5mm x 13.0mm x 1.0mm

- Operating Voltage range

- $V_{CC} = 2.7V \sim 3.6V$  (typical 3.3V)

- $V_{CCQ} = 1.7V \sim 1.95V(typical 1.8V), 2.7V \sim 3.6V (typical 3.3V)$

- Temperature

- Operating: 25°C ~ 85°C

- Storage : -40° ~ 85° €

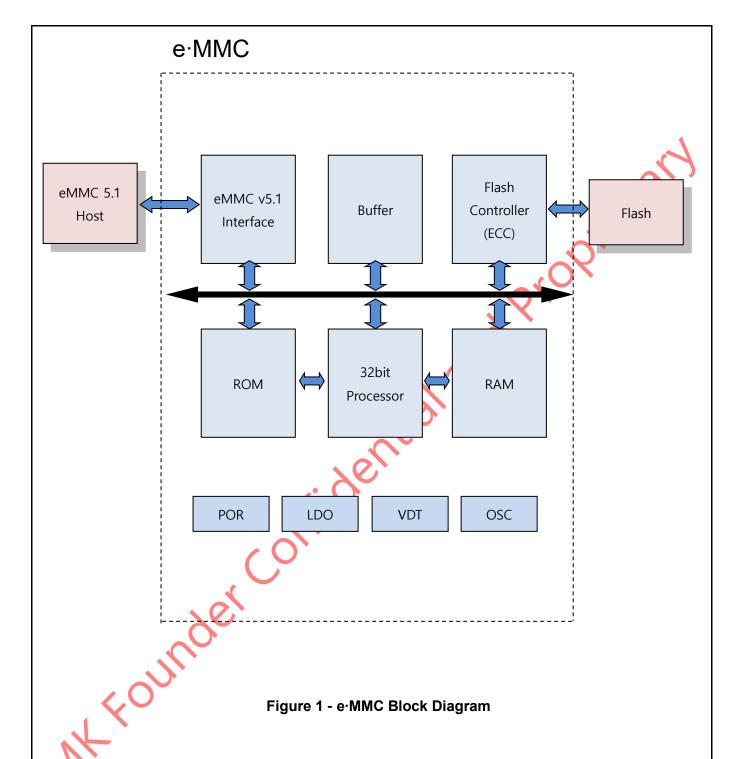

## 4. Functional Block Diagram

# 5. e-MMC Device and System

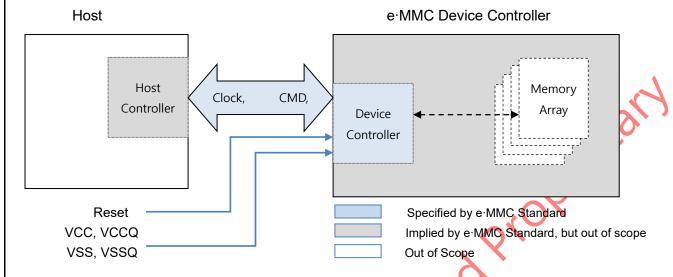

# 5.1 e-MMC System Overview

The e·MMC specification covers the behavior of the interface and the device controller include LDPC based ECC. AS part of this specification the existence of a host controller include LDPC based

ECC and a memory storage array are implied but the operation of these pieces is not fully specified

Figure 2 - e-MMC System Overview

#### 5.2 e-MMC Device Overview

The e-MMC bus has the following communication and power lines

- CLK : Clock Input

- DS : Data strobe used for output in HS400 mode.

- CMD : Command is a bidirectional signal. The host and e·MMC operate in two modes, open drain and push-pull

- DAT0~DAT7 : Data lines are bidirectional signal. Host and e·MMC operate in push-pull mode.

- RST n : Hardware Reset Input

- VCC: VCC is the power supply for core and flash IO.

- VCCQ : VCCQ is the power supply line for host interface

- VSS, VSSQ : Ground lines.

| Name | Туре   | Description |

|------|--------|-------------|

| CLK  | I      | Clock       |

| DS   | O/PP   | Data Strobe |

| DAT0 | I/O/PP | Data        |

| DAT1 | I/O/PP | Data        |

| DAT2 | I/O/PP | Data        |

| DAT3                    | I/O/PP                  | Data                                      |

|-------------------------|-------------------------|-------------------------------------------|

| DAT4                    | I/O/PP                  | Data                                      |

| DAT5                    | I/O/PP                  | Data                                      |

| DAT6                    | I/O/PP                  | Data                                      |

| DAT7                    | I/O/PP                  | Data                                      |

| CMD                     | I/O/PP/OD               | Command/Response                          |

| RST_n                   | 1                       | Hardware reset                            |

| VCC                     | S                       | Supply voltage for Core                   |

| VCCQ                    | S                       | Supply voltage for I/O                    |

| VSS                     | S                       | Supply voltage ground for Core            |

| VSSQ                    | S                       | Supply voltage ground for I/O             |

| I: input, O: output, PF | : push-pull, OD: open-o | drain, NC: Not connected, S: power supply |

Table 1 - e·MMC Interface

| Name    | Width (bytes) | Description                                                                                                                       | Implementation |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------|

| CID     | 16            | Device Identification number, an individual number for Identification.                                                            | Mandatory      |

| RCA     | 2             | Relative Device Address, is the device system address, Dynamically assigned by the host during initialization.                    | Mandatory      |

| DSR     | 2             | Driver stage Resister, to configure the Device's output drivers .                                                                 | Optional       |

| CSD     | 16            | Device Specific Data, information about the Device operation Conditions.                                                          | Mandatory      |

| OCR     | 4             | Operation Conditions Resister. Used by a special broadcast command to identify the voltage type of the Device.                    | Mandatory      |

| EXT_CSD | 512           | Extended Device Specific Data. Contains information about the Device capabilities and selected modes. Introduced in standard v4.0 | Mandatory      |

Table 2 - e-MMC registers

# 6. e-MMC 5.1 Feature Overview

## 6.1 Boot

e-MMC supports JESD84-B51A boot operation mode, both mandatory as well as alternate mode are supported.

## 6.2 Sleep (CMD5)

A Device may be switched between a Sleep state and a Standby state by SLEEP/AWAK(CMD5). In

the Sleep State the power consumption of the memory device is minimized. In this state the memory device reacts only to the commands RESET(CMD0 with argument of either 0x00000000 or 0XF0F0F0F000 or H/W reset) and SLEEP/AWAKE(CMD5). All the other commands are ignored by the memory device.

The Vcc power supply may be switched off in Sleep state is to enable even further system power consumption saving.

For additional information please refer JESD84-B51A.

#### 6.3 Bus Modes

#### Boot mode

The device will be in boot mode after power cycle, reception of CMD0 with argument of 0xF0F0F0F0 or the assertion of hardware reset signal.

#### Device identification mode

The device will be in device identification mode after boot operation mode is finished or if host and/or device does not support boot operation mode. The device will be in this mode, until the SET\_RCA command (CMD3) is received.

#### Interrupt mode

Host and device enter and exit interrupt mode simultaneously. In interrupt mode there is no data transfer. The only message allowed is an interrupt service request from the device or the host.

#### Data transfer mode

The device will enter data transfer mode once an RCA is assigned to it. The host will enter data transfer mode after identifying the device on the bus

#### Inactive mode

The device will enter inactive mode if either the device operating voltage range or access mode is not valid. The device can also enter inactive mode with GO\_INACTIVE\_STATE command(CMD15). The device will reset to Pre-idle state with power cycle.

| Device State         | Operation mode             | Bus mode   |

|----------------------|----------------------------|------------|

| Inactive State       | Inactive mode              |            |

| Pre-Idle State       | Boot mode                  |            |

| Pre-Boot State       | Boot mode                  | Open-drain |

| Idle State           | Device identification mode |            |

| Identification State | Device identification mode |            |

| Stand-by State     |                    |            |

|--------------------|--------------------|------------|

| Sleep State        |                    | Push-pull  |

| Transfer State     |                    |            |

| Bus-Test State     |                    | (C)        |

| Sending-data State | Data transfer mode | XO         |

| Receive-data State |                    | die        |

| Programming State  |                    | 308        |

| Disconnect State   |                    | (8)        |

| Boot State         | Boot mode          | O          |

| Wait-IRQ State     | Interrupt mode     | Open-drain |

Table 3 - Bus mode's overview

#### 6.4 Reliable Write

e·MMC supports 512B reliable write as defined in e·MMC 5.1 spec.

Reliable write is a special write mode in which the old data pointed to by a logical address must remain unchanged until the new data written to same logical address has been successfully programmed. This is to ensure that the target address updated by the reliable write transaction never contains undefined data. When writing reliable write, data will remain valid even if a sudden power loss occurs during programming.

#### 6.5 Secure Erase

In addition to the standard Erase command the e·MMC support the optional Secure erase command. The Secure Erase command differs from the basic Erase command in that it requires the device and host to wait until the operation is complete before moving to the next device operation.

For additional information please refer JESD84-B51A.

The secure erase command requires device to perform a secure purge operation on the erase groups, and copy items identified for erase, in those erase groups.

A purge operation is defined as overwriting addressable location with a single character and the

performing an erase.

This new command meets high security application requirements that once data has been erased, it can no longer be retrieved from device.

#### 6.6 Secure Trim

The Secure Trim command is very similar to the Secure Erase command. The Secure Trim command performs a secure purge operation on write blocks instead of erase groups. To minimize the impact on the device's performance and reliability the Secure Trim operation is completed by executing two distinct steps.

For additional information please refer JESD84-B51A.

#### 6.7 Trim

The Trim function is similar to the Erase command but applies the erase operation to write blocks instead of erase groups.

For additional information please refer JESD84-B51A.

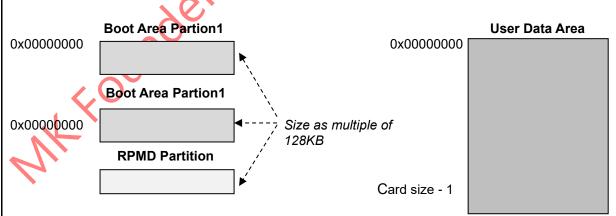

## 6.8 Partition Management

The default area of the memory device consists of a User Data Area to store data, two possible boot area partitions for booting and the Replay Protected Memory Block Area Partition to manage data in an authenticated and replay protected manner. The memory configuration initially consists(before any partitioning operation) of the User Data Area and RPMB Area Partitions and Boot Area Partitions.

Figure 3 - e-MMC memory organization at time zero

For additional information please refer JESD84-B51A.

## 6.9 High priority interrupt (HPI)

Many operating systems use demand-paging to launch a process requested by the user. If the host needs to fetch pages while in a middle of a wire operation, the request will be delayed until the completion of the write command which, in the worst case scenario, can take up to 350ms.

The high priority interrupt (HPI) as defined in JESD84-B51A enables low read latency operation by suspending a lower priority operation before it is actually completed. This mechanism can reduce read latency, in typical condition, to 5msec

For additional information please refer JESD84-B51A.

## 6.10 Background Operations

Devices have various maintenance operations that they need to perform internally, such as garbage collection, erase and compaction. In order to reduce latencies during time critical operations, it is better to execute maintenance operations when the device is not serving the host.

Operations are then separated into two types: foreground operations – such as read or write command, and background operations- operations that the device can execute when the host is not being served.

For additional information please refer JESD84-B51A.

#### 6.11 H/W Reset

Hardware reset may be used by host to reset the device, moving the card to a Pre-Idle state and disabling the power-on period write protect on blocks that was set as power-on write protect before the reset was asserted.

For additional information please refer JESD84-B51A.

## 6.12 Packed Commands

Read and write commands can be packed in groups of commands (either all read or all write) that transfer the data for all commands in the group in one transfer on the bus to reduce overheads.

For additional information please refer JESD84-B51A.

#### 6.13 Cache

Cache is temporary storage space in an e-MMC device. The cache should in typical case reduce the access time (compared to an access to the main non-voltage) for both write and read. The cache is not directly accessible by the host. This temporary storage space may be utilized also for some implementation specific operations like as an execution memory for the memory controller include LDPC based ECC and/or as storage for an address mapping table etc but which definition is out of

scope of this specification.

For additional information please refer JESD84-B51A.

#### 6-14 Discard

The Discard is similar operation to TRIM. The Discard function allows the host to identify data that is no longer required so that the device can erase the data if necessary during background erase events. The contents of a write block where the discard function has been applied shall be 'don't care'. After discard operation, the original data may be remained partially or fully accessible to the host dependent on device. The portions of data that are no longer accessible by the host may be removed or unmapped just as in the case of TRIM. The device will decide the contents of discarded write block.

For additional information please refer JESD84-B51A.

#### 6-15 Sanitize

The sanitize operation is a feature, in addition to TRIM and Erase that is used to remove data from the device. The use of the Sanitize operation requires the device to physically remove data from the unmapped user address space. A Sanitize operation is initiated by writing a value to the extended CSD[165] SANITIZE START.

For additional information please refer JESD84-B51A.

## 6-16 Dynamic Capacity Management

Extensive memory usage and aging of Flash could result in bad block.

Dynamic Capacity Management provides a mechanism for the memory device to reduce its reported capacity and extend the device life time.

The mechanism to manipulate dynamic capacity is based on: memory array partitioning and the granularity of WP groups. Reducing the capacity is done by releasing of WP-groups anywhere within the address space of the user area. A released WP-Group will behave as a permanently write protected group and it shall not be read from: Writing to an address within a released WP-Group returns a WP error; Reading form an address tithing a released WP-Group is forbidden and may return an error; Checking write protection (using CMD30) and write protect type (using CMD31) shall report protected groups and permanent write protection accordingly.

For additional information please refer JESD84-B51A.

# 7. Product Specifications

# 7-1 Power Consumption

| Power Consumption        | 32GB | Units |

|--------------------------|------|-------|

| Standby(VCCQ & VCC on)   | 85   | uA    |

| Sleep (VCCQ on, VCC off) | 75   | uA    |

| HS400 Read VCC           | 60   | mA    |

| HS400 Read VCCQ          | 120  | mA    |

| HS400 Write VCC          | 45   | mA    |

| HS400 Write VCCQ         | 65   | mA    |

Table 4 - Power Consumption (Ta=25℃@VCC=3.3V & VCCQ=1.8V)

## 7-2 Performance

| HS400 Performance | 32GB | Units |

|-------------------|------|-------|

| Sequential Read   | 280  | MB/s  |

| Sequential Write  | 140  | MB/s  |

| Random Read       | 4900 | IOPS  |

| Random Write      | 4800 | IOPS  |

Table 5 - Performance

# 7-3 Operating Conditions

|               | Temperature  | Remark |

|---------------|--------------|--------|

| Operating     | -25°C ~85°C  |        |

| Non-Operating | -40°C ~ 85°C |        |

Table 6 - Operating and Storage Temperature

# 7-4 Physical Specification

e·MMC is a 153pin, thin fine-pitched ball grid array.(BGA)

# 8. Interface Description

## 8-1 e-MMC Interface ball array

Figure 6 - FBGA153 Package Connection (top view through package)

## 8-2 Pins and Signal Description

| 153-Ball Device    | Symbol | Туре   | Ball Function                                                                                                                                                                                    |

|--------------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| М6                 | CLK    | Input  | Clock: Each cycle directs a 1-bit transfer on the command and DAT lines.                                                                                                                         |

| M5                 | CMD    | Input  | Command: A bidirectional channel used for device initialization and command transfer. Command has two operating mode:  1) Open-drain for initialization. 2) Push-pull for fast command transfer. |

| А3                 | DAT0   | I/O    | Data I/O0:<br>Bidirectional channel used for data transfer.                                                                                                                                      |

| A4                 | DAT1   | I/O    | Data I/O1:<br>Bidirectional channel used for data transfer.                                                                                                                                      |

| A5                 | DAT2   | I/O    | Data I/O2:<br>Bidirectional channel used for data transfer.                                                                                                                                      |

| B2                 | DAT3   | I/O    | Data I/O3: Bidirectional channel used for data transfer.                                                                                                                                         |

| В3                 | DAT4   | I/O    | Data I/O4: Bidirectional channel used for data transfer.                                                                                                                                         |

| B4                 | DAT5   | I/O    | Data I/O5:<br>Bidirectional channel used for data transfer.                                                                                                                                      |

| B5                 | DAT6   | I/O    | Data I/O6:<br>Bidirectional channel used for data transfer.                                                                                                                                      |

| В6                 | DAT7   | I/O    | Data I/O7: Bidirectional channel used for data transfer.                                                                                                                                         |

| K5                 | RST_n  | Input  | Reset signal pin                                                                                                                                                                                 |

| E6, F5, J10, K9    | vcc C  | Supply | VCC:<br>Flash memory I/F and Flash memory power<br>supply.                                                                                                                                       |

| C6, M4, N4, P3, P5 | VccQ   | Supply | VccQ: Memory controller core and MMC interface I/O power supply.                                                                                                                                 |

| E7, G5, H10, K8    | VSS    | Supply | Vss:<br>Flash memory I/F and Flash memory ground<br>connection.                                                                                                                                  |

| C4, N2, N5, P4, P6 | VssQ   | Supply | VssQ                                                                                                                                                                                             |

| C2                 | VDDi   |        | VDDi :<br>Connect 1uF capacitor from VDDi to ground.                                                                                                                                             |

| H5                 | DS     |        | Data Strobe :<br>Return clock signal used in HS400 mode                                                                                                                                          |

| •                  |        |        | ·                                                                                                                                                                                                |

Table 7 – Pin and signal Description

## 9. Device Resisters

### 9.1 Operating Condition Resister (OCR)

The 32-bit operation condition register(OCR) store the Vdd voltage profile of the e·MMC and the access mode indication. In addition, this register includes a status information bit. This status bit is set if the e·MMC power up procedure has been finished. The OCR register shall be implemented by e·MMC.

| OCR bit | Description                      | Value        | Remark    |

|---------|----------------------------------|--------------|-----------|

| [6:0]   | Reserved                         | 000 0000b    |           |

| [7]     | 1.70 ~ 1.95V                     | 1b           | $\sim$ 0. |

| [14:8]  | 2.0 ~ 2.6V                       | 000 0000b    | 0,        |

| [23:15] | 2.7 ~ 3.6V                       | 1 1111 1111b |           |

| [28:24] | Reserved                         | 0 0000b      |           |

| [30:29] | Access mode                      | 10b          |           |

| [31]    | card power up status bit (busy)1 |              |           |

<sup>1)</sup> This bit is set to LOW if the Device has not finished the power up routine.

Table 8 - OCR register definition

# 9.2 Card Identification Resister (CID)

The Card Identification(CID) register is 128 bits wide. In contains the Device identification information used during the Device identification phase e-MMC protocol). Every individual flash or I/O Device shall have an unique identification number. Table 21 lists these identifiers.

The structure of the CID register is defined in the following section.

| Name                  | Field | Width | CID-Slice | CID Value                | Remark    |

|-----------------------|-------|-------|-----------|--------------------------|-----------|

| Manufacture ID        | MID   | 8     | [127:120] | 16h                      |           |

| Reserved              |       | 6     | [119:114] |                          |           |

| Card / BGA            | CBX   | 2     | [113:112] | 01h                      | BGA       |

| OEM/Application ID    | OID   | 8     | [111:104] | 00h                      | Not fixed |

| Product name          | PNM   | 48    | [103:56]  | 32G BEC032<br>64G BEC064 | Not fixed |

| Product revision      | PRV   | 8     | [55:48]   | 3A                       | Not fixed |

| Product serial number | PSN   | 32    | [47:16]   | Random by<br>Production  | Not fixed |

| Manufacturing date    | MDT   | 8     | [15:8]    | month , year             | Not fixed |

| CRC7 checksum         | CRC   | 7     | [7:1]     | 0h                       | Not fixed |

| Not used, always '1'  | -     | 1     | [0:0]     | 0h                       |           |

Table 9 - Card Identification register definition

## 9-3 Card Specific Data Resister (CSD)

The Device-specific Data (CSD) register provides information on how to access the Device contents.

The CSD defines the data format, error correction type, maximum data access time, data transfer speed, whether the DSR register can be used etc. The programmable part of the register(entries marked by W or E, see below) can be changed by CMD27. The type of the CSD Registry entries below is coded as follows:

- R : Read only

- W : One time programmable and not readable.

- R/W : One time programmable and readable

- W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and not readable.

- R/W/E: Multiple writable with value kept after power failure, H/W reset assertion and any CMD0 reset and not readable.

- R/W/C\_P: Writeable after value cleared by power failure and H/W reset assertion (the value not cleared by CMD0 reset) and readable.

- R/W/E\_P: Multiple writable with value reset after power failure, H/W reset assertion and any CMD0 reset and readable.

- W/E\_P : Multiple writable with value reset power failure, H/W reset assertion and any CMD0 reset and not readable.

| Name                                           | Field              | Width | Cell<br>type | CSD<br>Slice | CSD<br>Value | Remark                        |

|------------------------------------------------|--------------------|-------|--------------|--------------|--------------|-------------------------------|

| CSD structure                                  | CSD_STRUCTURE      | 2     | R            | [127:126]    | 3h           |                               |

| System Specification version                   | SPEC_VERS          | 4     | R            | [125:122]    | 4h           |                               |

| Reserved                                       | -                  | 2     | R            | [121:120]    |              |                               |

| Data read access-time 1                        | TAAC               | 8     | R            | [119:112]    | 2Fh          | 20ms                          |

| Data read access-time 2in CLK cycle (NSAC*100) | NSAC               | 8     | R            | [111:104]    | 1h           |                               |

| Max. bus clock frequency                       | TRAN_SPEED         | 8     | R            | [103:96]     | 2Ah          | 20MHz                         |

| Device command classes                         | ccc                | 12    | R            | [95:84]      | 5F5h         | Class<br>0,2,4,5,6,<br>7,8,10 |

| Max. read data block length                    | READ_BL_LEN        | 4     | R            | [83:80]      | 9h           | 512B                          |

| Partial blocks for read allowed                | READ_BL_PARTIAL    | 1     | R            | [79:79]      | 0h           | Not support                   |

| Write block misalignment                       | WIRTE_BLK_MISALIGN | 1     | R            | [78:78]      | 0h           | Not support                   |

| Name                                           | Field              | Width | Cell<br>type | CSD<br>Slice | CSD<br>Value | Remark                        |

| Read block misalignment                        | READ_BLK_MISALIGN  | 1     | R            | [77:77]      | 0h           | Not support                   |

| DSR implemented                                | DSR_IMP            | 1     | R            | [76:76]      | 0h           | Not support                   |

| Reserved                         |                    | 2  | R     | [75:74] |      |             |

|----------------------------------|--------------------|----|-------|---------|------|-------------|

| Device size                      | C_SIZE             | 12 | R     | [73:62] | FFFh |             |

| Max read current @VDD min        | VDD_R_CURR_MIN     | 3  | R     | [61:59] | 6h   |             |

| Max read current @VDD max        | VDD_R_CURR_MAX     | 3  | R     | [58:56] | 6h   |             |

| Max write current @VDD min       | VDD_W_CURR_MIN     | 3  | R     | [53:53] | 6h   |             |

| Max write current @VDD max       | VDD_W_CURR_MAX     | 3  | R     | [52:50] | 6h   | 0/1         |

| Device size multiplier           | C_SIZE_MULT        | 3  | R     | [49:47] | 7h   | Co          |

| Erase group size                 | ERASE_GRP_SIZE     | 5  | R     | [46:42] | 1Fh  | /           |

| Erase group size multiplier      | ERASE_GRP_MULT     | 5  | R     | [41:37] | 1Fh  |             |

| Write protect group size         | WP_GRP_SIZE        | 5  | R     | [36:32] | 1h   |             |

| Write protect group enable       | WP_GRP_ENABLE      | 1  | R     | [31:31] | 1h   |             |

| Manufacturer default ECC         | DEFAULT_ECC        | 2  | R     | [30:29] | 0h   |             |

| Write speed factor               | R2W_FACTOR         | 3  | R     | [28:26] | 1h   |             |

| Max. write data block length     | WRITE_BL_LEN       | 47 | R     | [25:22] | 9h   | 512B        |

| Partial blocks for write allowed | WRITE_BL_PARTIAL   | 1  | R     | [21:21] | 0h   | Not support |

| Reserved                         |                    | 4  | R     | [20:17] |      |             |

| Content protection application   | CONTENT_PROT_APP   | 1  | R     | [16:16] | 0h   | Not support |

| File format group                | FILE_FORMAT_GRP    | 1  | R/W   | [15:15] | 0h   |             |

| Copy flag (OTP)                  | COPY               | 1  | R/W   | [14:14] | 0h   |             |

| Permanent write protection       | PERM_WRITE_PROTECT | 1  | R/W   | [13:13] | 0h   |             |

| Temporary write protection       | TMP_WRITE_PROTECT  | 1  | R/W/E | [12:12] | 0h   |             |

| File format                      | FILE_FORMAT        | 2  | R/W   | [11:10] | 0h   |             |

| ECC code                         | ECC                | 2  | R/W/E | [9:8]   | 0h   | None        |

| CRC                              | CRC                | 7  | R/W/E | [7:1]   | Dh   |             |

| Not used, always'1'              |                    | 1  | -     | [0:0]   | 1h   |             |

The following sections describe the CSD fields and the relevant data types. If not explicitly defined otherwise, all bit strings are interpreted as binary coded numbers starting with the left bit first.

#### Table 10 - CSD Field

#### 9-4 Extended CSD Resister

The Extended CSD register defines the Device properties and selected modes. It is 512bytes long. The most significant 320bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host means of the SWITCH command.

For details, refer to section 7.4 of the JEDEC Standard Specification No. JESD84-B51A.

| Name                                    | Field                      | Cell<br>type | CSD<br>Slice | EXT_<br>CSD<br>Value | Remark                                                                                                                                                                                      |

|-----------------------------------------|----------------------------|--------------|--------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Properties Segment                      |                            |              |              |                      |                                                                                                                                                                                             |

| Reserved <sub>1</sub>                   | RESERVED                   | TBD          | [511:506]    |                      |                                                                                                                                                                                             |

| Extended Security<br>Command Error      | EXT_SECURITY_ER R          | R            | [505]        | 0h                   | Only for eMMC4.5 by JESD84-B51A                                                                                                                                                             |

| Supported Command<br>Sets               | S_CMD_SET                  | R            | [504]        | 1h                   | Allocated by MMCA                                                                                                                                                                           |

| HPI features                            | HPI_FEATURES               | R            | [503]        | 3h                   | Bit[1]=1: HPI mechanism implementation base on CMD12  Bit[1]=0: HPI mechanism implementation base on CMD13  Bit[0]=1: HPI mechanism support  Bit[0]=0: HPI mechanism not support (default ) |

| Background operations support           | BKOPS_SUPPORT              | R            | [502]        | 1h                   | Background operation are supported                                                                                                                                                          |

| Max packed read commands                | MAX_PACKED_REA<br>DS       | R            | [501]        | 5h                   |                                                                                                                                                                                             |

| Max packed write commands               | MAX_PACKED_WRI             | R            | [500]        | 3h                   |                                                                                                                                                                                             |

| Data Tag Support                        | DATA_TAG_SUPPORT           | R            | [499]        | 1h                   | System data tag supported                                                                                                                                                                   |

| Tag Unit Size                           | TAG_UNIT_SIZE              | R            | [498]        | 1h                   | 1024Bytes                                                                                                                                                                                   |

| Tag Resources Size                      | TAG_RES_SIZE               | R            | [497]        | 0h                   |                                                                                                                                                                                             |

| Context Management Capabilities         | CONTEXT_CAPABIL ITIES      | R            | [496]        | 5h                   |                                                                                                                                                                                             |

| Large Unit Size                         | LARGE_UNIT_SIZE<br>_M1     | R            | [495]        | 0h                   |                                                                                                                                                                                             |

| Extended partition<br>Attribute Support | EXT_SUPPORT                | R            | [494]        | 3h                   |                                                                                                                                                                                             |

| Supported modes                         | SUPPORTED_MOD<br>ES        | R            | [493]        | 1h                   |                                                                                                                                                                                             |

| FFU features                            | FFU_FEATURES               | R            | [492]        | 1h                   |                                                                                                                                                                                             |

| Operation codes timeout                 | OPERATION_CODE<br>_TIMEOUT | R            | [491]        | 17h                  |                                                                                                                                                                                             |

| FFU Argument                            | FFU_ARG                    | R            | [490:487]    | 0h                   |                                                                                                                                                                                             |

| Barrier support                             | BARRIER_SUPPOR<br>T                                   | R            | [486]        | 0h                   |                                     |

|---------------------------------------------|-------------------------------------------------------|--------------|--------------|----------------------|-------------------------------------|

| Reserved1                                   |                                                       | TBD          | [485:309]    |                      |                                     |

| CMD Queuing Support                         | CMDQ_SUPPORT                                          | R            | [308]        | 0h                   |                                     |

| CMD Queuing Depth                           | CMDQ_DEPTH                                            | R            | [307]        | 0h                   | 7                                   |

| Reserved1                                   |                                                       | TBD          | [306]        |                      |                                     |

| Number of FW sectors correctly programmed   | NUMBER_OF_FW_<br>SECTORS_CORRE<br>CTLY_PROGRAMM<br>ED | R            | [305:302]    | 0h                   | Pile                                |

| Vendor proprietary health report            | VENDOR_PROPRIE<br>TARY_HEALTH_RE<br>PORT              | R            | [301:270]    | 0h                   | XP10                                |

| Device life time estimation type B          | DEVICE_LIFE_TIME<br>_EST_TYP_B                        | R            | [269]        | 1h                   |                                     |

| Device life time estimation type A          | DEVICE_LIFE_TIME<br>_EST_TYP_A                        | R            | [268]        | 1h                   | 0                                   |

| Pre EOL information                         | PRE_EOL_INFO                                          | R            | [267]        | 1h                   |                                     |

| Optimal read size                           | OPTIMAL_READ_SI<br>ZE                                 | R            | [266]        | 8h                   |                                     |

| Optimal write size                          | OPTIMAL_WRITE_S                                       | R            | [265]        | 8h                   |                                     |

| Optimal trim unit size                      | OPTIMAL_TRIM_UNIT_SIZE                                | R            | [264]        | 8h                   |                                     |

| Device version                              | DEVICE_VERSION                                        | R            | [263:262]    | 0h                   |                                     |

| Firmware version                            | FIRMWARE_VERSI                                        | R            | [261:254]    |                      |                                     |

| Power class for 200MHz,<br>DDR at VCC= 3.6V | PWR_CL_DDR_200<br>_360                                | R            | [253]        | 0h                   |                                     |

| Cache size                                  | CACHE_SIZE                                            | R            | [252:249]    | 100h                 |                                     |

| Generic CMD6 timeout                        | GENERIC_CMD5_TI<br>ME                                 | R            | [248]        | 32h                  | Not defined                         |

| Name                                        | Field                                                 | Cell<br>type | CSD<br>Slice | EXT_<br>CSD<br>Value | Remark                              |

| Power off notification (long)timeout        | POWER_OFF_LON<br>G_TIME                               | R            | [247]        | 3Ch                  | Not defined                         |

| Background operations status                | BKOPS_STATUS                                          | R            | [246]        | 0h                   | Outstanding : No operation required |

| Number of correctly programmed sectors      | CORRECTLY_PRG_<br>SECTORS_NUM                         | R            | [245:242]    | 0h                   |                                     |

| 1st initialization time after partitioning              | INI_TIMEOUT_AP          | R            | [241]        | 1Eh                  | Initial time out 3s                                                                                                                                                                                                   |

|---------------------------------------------------------|-------------------------|--------------|--------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Flushing Policy                                   | CACHE_FLUSH_PO<br>LICY  | R            | [240]        | 0h                   |                                                                                                                                                                                                                       |

| Power class for 52MHz,<br>DDR at VCC = 3.6V             | PWR_CL_DDR_52_<br>360   | R            | [239]        | 0h                   |                                                                                                                                                                                                                       |

| Power class for 52MHz,<br>DDR at VCC = 1.95V            | PWR_CL_DDR_52_<br>195   | R            | [238]        | 0h                   |                                                                                                                                                                                                                       |

| Power class for 200MHz at VCCQ = 1.95V, VCC = 3.6V      | PWR_CL_200_195          | R            | [237]        | 0h                   |                                                                                                                                                                                                                       |

| Power class for 200MHz<br>at VCCQ = 1.3V, VCC<br>= 3.6V | PWR_CL_200_130          | R            | [236]        | 0h                   |                                                                                                                                                                                                                       |

| Minimum Write Performance for 8bit At 52MHz in DDR mode | MIN_PERF_DDR_W<br>_8_52 | R            | [235]        | 0h                   |                                                                                                                                                                                                                       |

| Minimum Read Performance for 8bit At 52MHz in DDR mode  | MIN_PERF_DDR_R<br>_8_52 | R            | [234]        | 0h                   |                                                                                                                                                                                                                       |

| Reserved <sub>1</sub>                                   | RESERVED                | TBD          | [233]        |                      |                                                                                                                                                                                                                       |

| TRIM Multiplier                                         | TRIM_MULT               | R            | [232]        | 2h                   | TRIM Timeout =300ms*2=600ms                                                                                                                                                                                           |

| Secure Feature support                                  | SEC_FEATURE_SU<br>PPORT | R            | [231]        | 55h                  | Support the sanitize operation     Support the secure and insecure trim operation     Support the auto erase on retired defective portion of array     Secure purge operations are supported                          |

| Secure Erase Multiplier                                 | SEC_ERASE_MULT          | R            | [230]        | 1Bh                  | Secure Erase Timeout=<br>5.1 sec                                                                                                                                                                                      |

| Secure TRIM Multiplier                                  | SEC_TRIM_MULT           | R            | [229]        | 11h                  | Secure trim Timeout=<br>8.1 sec                                                                                                                                                                                       |

| Boot information                                        | BOOT_INFO               | R            | [228]        | 7h                   | Bit[2]=1: Device supports high speed timing during boot Bit[1]=1: Device supports dual data rate during boot Bit[0]=1: Device supports alternate boot method Bit[0,1,2]=0: Not supports each feature Bit[7:3=Reserved |

| Name                                                    | Field                   | Cell<br>type | CSD<br>Slice | EXT_<br>CSD<br>Value | Remark                                                                                                                                                                                                                |

| Reserved <sub>1</sub>                                   | RESERVED                | TBD          | [227]        |                      |                                                                                                                                                                                                                       |

| Boot partition size                                     | BOOT_SIZE_MULT          | R            | [226]        | 20h                  |                                                                                                                                                                                                                       |

| Access size                                             | ACC_SIZE                | R            | [225]        | 6h                   |                                                                                                                                                                                                                       |

| High-capacity erase unit size                           | HC_ERASE_GRP_S<br>IZE   | R            | [224]        | 1h                   |                                                                                                                                                                                                                       |

|                                                         |                         |              |              |                      |                                                                                                                                                                                                                       |

| High-capacity erase timeout                                          | ERASE_TIMEOUT_<br>MULT                     | R            | [223]        | 1h                   | High Capacity erase timeout : 300ms                  |

|----------------------------------------------------------------------|--------------------------------------------|--------------|--------------|----------------------|------------------------------------------------------|

| Reliable write sector count                                          | REL_WR_SEC_C                               | R            | [222]        | 1h                   | 1sector                                              |

| High-capacity write protect group size                               | HC_WP_GRP_SIZE                             | R            | [221]        | 20h                  |                                                      |

| Sleep current (VCC)                                                  | s_c_vcc                                    | R            | [220]        | 7h                   | Sleep Current :128uA                                 |

| Sleep current(VCCQ)                                                  | s_c_vccq                                   | R            | [219]        | 7h                   | Sleep Current :128uA                                 |

| Production state awarene ss timeout                                  | PRODUCTION_STA<br>TE_AWARENESS_T<br>IMEOUT | R            | [218]        | 17h                  |                                                      |

| Sleep/awake timeout                                                  | S_A_TIMEOUT                                | R            | [217]        | 17h                  | Sleep/Awake Timeout : 85ms                           |

| Sleep Notification Timeout                                           | SLEEP_NOTIFICATI<br>ON_TIME                | R            | [216]        | 11h                  |                                                      |

| Sector Count                                                         | SEC_COUNT                                  | R            | [215:212]    |                      | 32GB: 3A3E000h<br>64GB: 747C000h                     |

| Secure Write Protect<br>Information                                  | SECURE_WP_INFO                             | TBD          | [211]        | 0h                   |                                                      |

| Minimum Write Performance for 8bit At 52MHz                          | MIN_PERF_W_8_52                            | R            | [210]        | 0h                   |                                                      |

| Minimum Read<br>Performance for 8bit<br>At 52MHz                     | MIN_PERF_R_8_52                            | R            | [209]        | 0h                   |                                                      |

| Minimum Write<br>Performance for 8bit at<br>26MHz, for 4bit at 52MHz | MIN_PERF_W_8_26<br>_4_52                   | R            | [208]        | 0h                   |                                                      |

| Minimum Write<br>Performance for 8bit at<br>26MHz, for 4bit at 52MHz | MIN_PERF_R_8_26<br>_4_52                   | R            | [207]        | 0h                   |                                                      |

| Minimum Write Performance for 4bit at 26MHz                          | MIN_PERF_W_4_26                            | R            | [206]        | 0h                   |                                                      |

| Minimum Write<br>Performance for 4bit at<br>26MHz                    | MIN_PERF_R_26                              | R            | [205]        | 0h                   |                                                      |

| Reserved <sub>1</sub>                                                | RESERVED                                   | R            | [204]        |                      |                                                      |

| Power class for 26MHz at 3.6V 1R                                     | PWR_CL_26_360                              | R            | [203]        | 0h                   | MAX RMS Current = 100mA,<br>MAX Peak Current = 200mA |

| Power class for 52MHz at 3.6V 1R                                     | PWR_CL_52_360                              | R            | [202]        | 0h                   | MAX RMS Current = 100mA,<br>MAX Peak Current = 200mA |

| Name                                                                 | Field                                      | Cell<br>type | CSD<br>Slice | EXT_<br>CSD<br>Value | Remark                                               |

| Power class for 26MHz at 1.95V 1R                                    | PWR_CL_26_195                              | R            | [201]        | 0h                   | MAX RMS Current = 65mA,<br>MAX Peak Current = 130mA  |

| Power class for 52MHz at 1.95V 1R                                    | PWR_CL_52_195                              | R            | [200]        | 0h                   | MAX RMS Current = 65mA,<br>MAX Peak Current = 130mA  |

| Partition switching timing                                           | PARTITION_SWITC<br>H TIME                  | R            | [199]        | 5h                   | Partition switch time : 10ms                         |

| Out-of-interrupt busy timing                                         | OUT_OF_INTERRU<br>PT_TIME                  | R            | [198]        | 19h                  | HPI time out : 20ms                                  |

| I/O Driver Strength         | DRIVER_STRENGT<br>H  | R                      | [197]        | Fh                   | Support driver strength : Type0,1,2,3                                  |

|-----------------------------|----------------------|------------------------|--------------|----------------------|------------------------------------------------------------------------|

|                             |                      |                        |              |                      | 1. HS400 @1.8V                                                         |

|                             |                      |                        |              |                      | 2. High-speed Data Rate 52@1.8V/3.3V                                   |

| Device type                 | DEVICE_TYPE          | R                      | [196]        | 57h                  | High-speed Data Rate 52@rated device voltage(s)                        |

|                             |                      |                        |              |                      | High-speed Data Rate 26@rated device voltage(s)                        |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [195]        |                      |                                                                        |

| CSD structure               | CSD_STRUCTURE        | R                      | [194]        | 2h                   | CSD version No.1.2                                                     |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [193]        |                      |                                                                        |

| Extend CSD revision         | EXT_CSD_REV          | R                      | [192]        | 8h                   | Revision 1.8(for MMC v5.1)                                             |

| Modes Segment               |                      |                        |              |                      |                                                                        |

| Command set                 | CMD_SET              | R/W/<br>E_P            | [191]        | 0h                   |                                                                        |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [190]        |                      |                                                                        |

| Command set revision        | CMD_SET_REV          | R                      | [189]        | 0h                   | V4.0                                                                   |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [188]        |                      |                                                                        |

| Power class                 | POWER_CLASS          | R/W/<br>E_P            | [187]        | 0h                   | See EXT_CSD in spec.                                                   |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [186]        |                      |                                                                        |

| High-speed interface timing | HS_TIMING            | R/W/<br>E_P            | [185]        | 0h                   | It depends on Host I/F speed. Default is 0,<br>But it can be 1 by host |

| Strobe Support              | STROBE_SUPPORT       | R                      | [184]        | 1h                   |                                                                        |

| Bus width mode              | BUS_WIDTH            | W/E<br>_P              | [183]        | 0h                   |                                                                        |

| Reserved <sub>1</sub>       | RESERVED             |                        | [182]        |                      |                                                                        |

| Erase memory content        | ERASED_MEM_CO        | R                      | [181]        | 0h                   | 0 after erase                                                          |

| Name                        | Field                | Cell<br>type           | CSD<br>Slice | EXT_<br>CSD<br>Value | Remark                                                                 |

| Reserved <sub>1</sub>       | RESERVED             | TBD                    | [180]        |                      |                                                                        |

| Partition configuration     | PARTITION_CONFI<br>G | R/W/E<br>& R/W<br>/E_P | [179]        | 0h                   |                                                                        |

| Boot config protection      | BOOT_CONFIG_PR<br>OT | R/W/E<br>& R/W<br>/C_P | [178]        | 0h                   |                                                                        |

| Reserved:  RESERVED TBD [176]  High-density erase group definition Boot write protection status registers  Boot area write protection register  BOOT_WP  RAWIE & RW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Boot bus Conditions        | BOOT_BUS_CONDI | R/W                   | [177] | 0h  |                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------|-----------------------|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-density erase group definition  Boot write protection status registers  TBD [174] 0h  Bit[6]=0: Master is permitted to set B_PWR_WP_EN (bit0)  Bit[4]=0: Master is permitted to set B_PRM_WP_EN (bit2)  Bit[2]=0: Boot Region is not perman write protected  Bit[0]=0: Master is permitted to set B_PRM_WP_EN (bit0)  Bit[4]=0: Master is permitted to set MB_PRM_WP_EN (bit0)  Bit[4]=0: Master is permitted to | Reserved <sub>1</sub>      |                |                       |       |     |                                                                                                                                                                                  |

| Boot write protection status registers    TBD   [174]   Oh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-density erase group   | ERASE_GROUP_D  |                       |       | 0h  |                                                                                                                                                                                  |

| Boot area write protection register  BOOT_WP  BOOT WOOT WOOT WOOT WOOT WOOT WOOT WOOT                                                                                                                                                                                                                                                                                                                                                                                                                              | Boot write protection      | EF             | TBD                   | [174] | 0h  |                                                                                                                                                                                  |

| User area write protection register  USER_WP  Reserved  RESERVED  TBD  [170]  FW configuration  FW_CONFIG  RPMB Size  RPMB_SIZE_MULT  R  [168]  Write reliability setting register  WR_REL_SET  WR_REL_PARAM  R  [166]  RPMB  1. Enhanced definition of reliable write register  WR_REL_PARAM  R  [166]  14h  2. All the WR_DATA_REL_parameter register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Boot area write protection |                | & R/W                 | [173] | Oh  | B_PWR_WP_EN (bit0)  Bit[4]=0 : Master is permitted to set B_PERM_WP_EN (bit2)  Bit[2]=0 : Boot Region is not permanently write protected  Bit[0]=0 : Boot Region is not power-on |