FEDL228XX-07

Issue Date: Feb. 9, 2024

# ML2282X-XXX/ML2286X-XXX

Speech Synthesis LSI with Built-in P2ROM Including 2-Channel Mixing Function

#### **GENERAL DESCRIPTION**

ML2282X(ML22825/ML22824/ML22823-XXX) and ML2286X (ML22865/ML22864/ML22863-XXX) are voice synthesis LSIs with built-in P2ROM that stores speech data.

These LSIs include edit ROM, ADPCM2 decoder, 16-bit DA converter, low pass filter and monaural speaker amplifier. Also, ML2282X supports the synchronous serial interface and ML22865/ML22864/ML22863 supports the I2C interface.

By integrating all the functions required for voice output into a single chip, these LSIs can be more easily incorporated in compact portable devices.

• Built-in memory capacity and maximum vocal reproduction time:

(at the case of 4-bit ADPCM2 algorithm)

| Product name        | DOM consoity | Maximum vocal reproduction time (sec) |                         |                         |  |  |

|---------------------|--------------|---------------------------------------|-------------------------|-------------------------|--|--|

| Product name        | ROM capacity | $F_S = 4.0 \text{ kHz}$               | $F_S = 8.0 \text{ kHz}$ | F <sub>S</sub> = 16 kHz |  |  |

| ML22825-XXX/ML22865 | 16 Mbits     | 1,044                                 | 522                     | 261                     |  |  |

| ML22824-XXX/ML22864 | 8 Mbits      | 520                                   | 260                     | 130                     |  |  |

| ML22823-XXX/ML22863 | 4 Mbits      | 258                                   | 129                     | 64                      |  |  |

• Voice synthesis method: 4-bit ADPCM2

8-bit Nonlinear PCM 8-bit PCM, 16-bit PCM

Can be specified for each phrase.

• Sampling frequency(Fs): 4.0 / 5.3 / 6.4 / 8.0 / 10.6 / 12.0 / 12.8 / 16.0 / 21.3 / 24.0 / 25.6 / 32.0 /

48.0 kHz

f<sub>s</sub> can be specified for each phrase.

• Built-in low-pass filter and 16-bit DA converter

• Speaker driving amplifier:  $0.7 \text{ W} \text{ (when } 8\Omega \text{ , } DV_{DD}=5 \text{ V}, \text{ Ta}=25^{\circ}\text{C})$

2ch analog input (internal: 1ch; external: 1ch)

• CPU command interface: 3-wired serial clock-synchronized (ML2282X)

I2C interface (ML2286X)

• Maximum number of phrases: 4,096 phrases from 000h to 3FFh (1024 phrases/bank)

• Memory bank switching: Enabled between bank 1 and bank 4 using the SEL0 and SEL1 pins

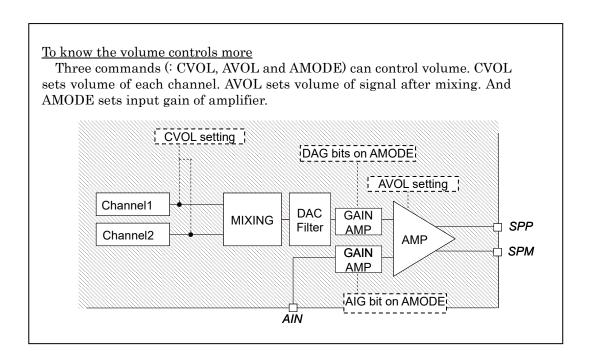

• Volume control: 32 levels (OFF is included) can be set by CVOL command.

50 levels (OFF is included) can be set by AVOL command

• Repeat function: LOOP commands

• 2-channel mixing function: Available except case using 32kHz as sampling frequencys

• Source oscillation frequency: 4.096 MHz

• Power supply voltage: 2.7 to 3.6 V / 4.5 to 5.5 V

• Operating temperature range: -40 to +85°C

## **APPLICATIONS**

• Consumer and Industrial equipment (e.g., Household appliances, Housing equipment, Office equipment, Measurement instrumentation, etc.).

## [NOTE]

This product cannot be applicable for automotive use, automatic train control systems, and railway safety systems. Please contact ROHM sales office in advance if contemplating the integration of this product into applications that requires high reliability, such as transportation equipment for ships and railways, communication equipment for trunk lines, traffic signal equip.

## **TABLE FORMAT**

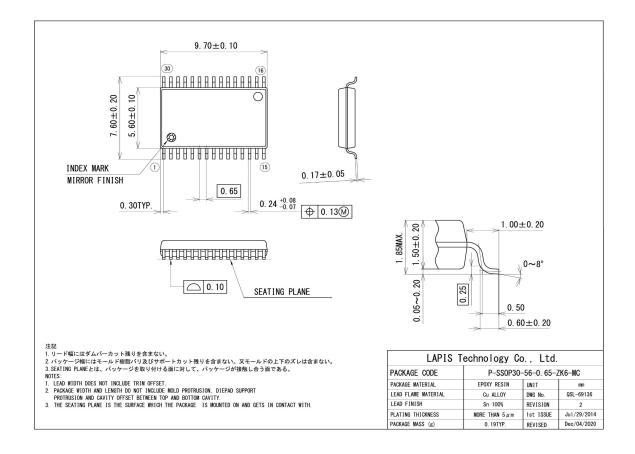

| Daakana             | Body size                     | Pin pitch | Packing form and Product name <sup>*1</sup>                                                                                |                                                                                                                            |  |

|---------------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Package             | (including lead)<br>[mm × mm] | [mm]      | Tray                                                                                                                       | Tape & Reel                                                                                                                |  |

| 30 pin plastic SSOP | 9.7 × 5.6<br>(9.7 × 7.6)      | 0.65      | ML22825-xxxMBZ0MX<br>ML22824-xxxMBZ0MX<br>ML22823-xxxMBZ0MX<br>ML22865-xxxMBZ0MX<br>ML22864-xxxMBZ0MX<br>ML22863-xxxMBZ0MX | ML22825-xxxMBZ0NX<br>ML22824-xxxMBZ0NX<br>ML22823-xxxMBZ0NX<br>ML22865-xxxMBZ0NX<br>ML22864-xxxMBZ0NX<br>ML22863-xxxMBZ0NX |  |

<sup>\*1 &</sup>quot;xxx" denotes ROM code number.

The following table shows the differences among the other speech synthesis LSIs.

| Parameter                                                            | ML2216                                                                           | ML22800 series        | ML22825/ML22824/<br>ML22823-XXX                                          | ML22865/ML22864/<br>ML22863-XXX |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------|---------------------------------|

| CPU interface                                                        | Serial                                                                           | <b>←</b>              | <b>←</b>                                                                 | I2C                             |

| Playback method                                                      | 4-bit ADPCM2<br>8-bit nonlinear PCM<br>8-bit straight PCM<br>16-bit straight PCM | ←                     | <b>←</b>                                                                 | <b>←</b>                        |

| Maximum number of phrases                                            | 256                                                                              | 1,024 (256/bank)      | 4,096 (1,024/bank)                                                       | <b>←</b>                        |

| Sampling<br>frequency (kHz)                                          | 4.0/5.3/6.4/<br>8.0/10.6/12.8<br>16.0                                            | <b>←</b>              | 4.0/5.3/6.4/8.0/<br>10.6/12.0/12.8/<br>16.0/21.3/24.0/<br>25.6/32.0/48.0 | <b>←</b>                        |

| Clock frequency                                                      | 4.096MHz<br>(with a built-in crystal<br>oscillator circuit)                      | <b>←</b>              | <b>←</b>                                                                 | <b>←</b>                        |

| DA converter                                                         | 12 bits                                                                          | 12 bits               | 16 bits                                                                  | ←                               |

| Low-pass filter                                                      | 3rd order comb filter                                                            | 3rd order comb filter | FIR interpolation filter                                                 | ←                               |

| Speaker driving amplifier                                            | Built-in 0.3W $(8\Omega, DV_{DD} = 5 V)$                                         | No                    | Built-in 0.7W $(8\Omega, DV_{DD} = 5 V)$                                 | <b>←</b>                        |

| Edit ROM function                                                    | Yes                                                                              | <b>←</b>              | ←                                                                        | ←                               |

| Simultaneous<br>sound production<br>function (mixing<br>function)    | No                                                                               | ←                     | 2-channel                                                                | <b>←</b>                        |

| Volume control                                                       | 16 levels                                                                        | <b>←</b>              | 32 levels                                                                | <b>←</b>                        |

| Silence insertion                                                    | Yes<br>20 ms to 1024 ms<br>(4 ms/step)                                           | <b>←</b>              | <b>←</b>                                                                 | <b>←</b>                        |

| Repeat function                                                      | Yes                                                                              | ←                     | ←                                                                        | ←                               |

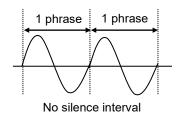

| Interval at which a seam is silent during continuous playback (Note) | No                                                                               | <b>~</b>              | <b>←</b>                                                                 | <b>←</b>                        |

| Memory bank switching                                                | No                                                                               | Yes                   | <b>←</b>                                                                 | <b>←</b>                        |

| Power supply voltage                                                 | 2.7 V to 5.5 V                                                                   | 2.7 V to 3.6 V        | 2.7 to 3.6V<br>4.5 to 5.5 V                                              | 2.7 to 3.6V<br>4.5 to 5.5 V     |

| Package                                                              | 44-pin QFP                                                                       | 30-pin SSOP           | ←                                                                        | <b>←</b>                        |

<sup>\*1:</sup> Continuous playback as shown below is possible.

(Playback method: 8-bit straight PCM, 8-bit non-linear PCM, 16-bit straight PCM)

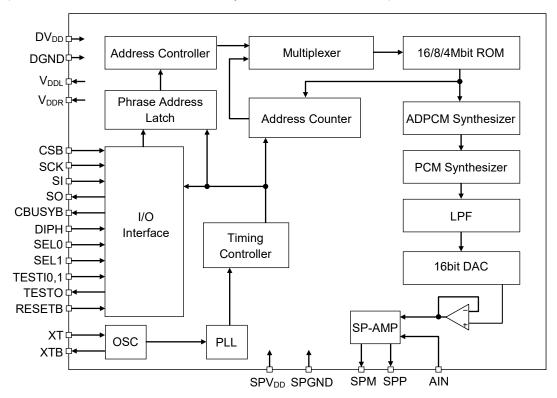

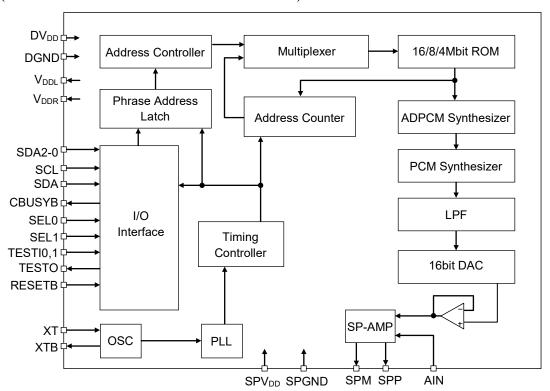

#### **BLOCK DIAGRAMS**

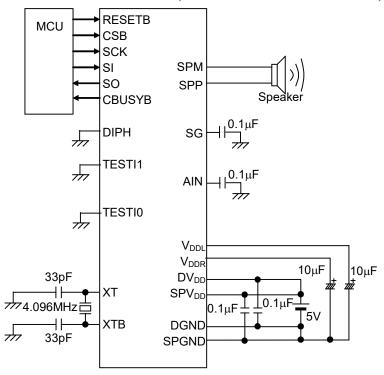

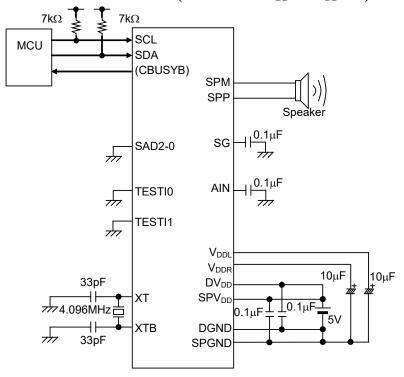

(ML22825/ML22824/ML22823-XXX : Synchronous serial interface)

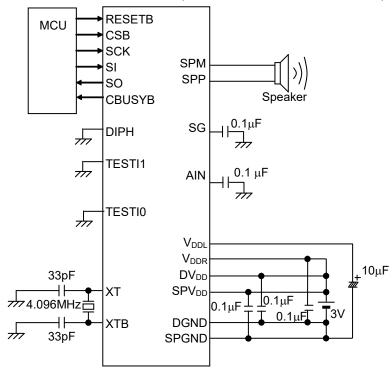

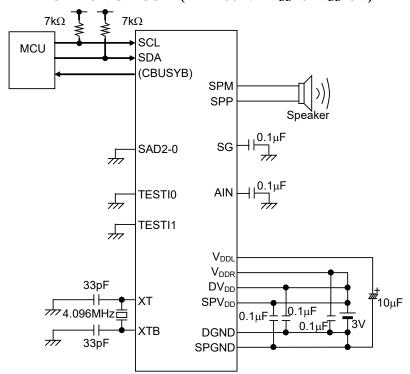

## (ML22865/ML22864/ML22863-XXX : I2C interface)

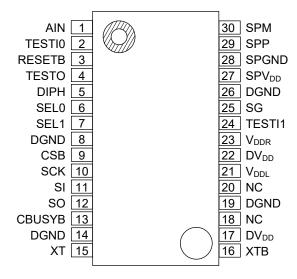

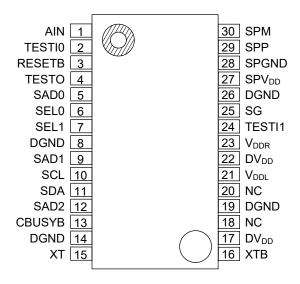

## PIN CONFIGURATIONS (TOP VIEW)

(ML22825/ML22824/ML22823-XXXMB : Synchronous serial interface)

NC: No Connection

30-Pin Plastic SSOP

## (ML22865/ML22864/ML22863-XXXMB : I2C interface)

NC: No Connection

30-Pin Plastic SSOP

# PIN DESCRIPTION (COMMON TO ALL PRODUCTS)

| Pin              | Symbol            | I/O | Initial value<br>(*1) | Description                                                                                                                                                                                                                                                                                                                                        |

|------------------|-------------------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | AIN               | ı   | 0                     | Input pin for speaker amplifier.                                                                                                                                                                                                                                                                                                                   |

| 2                | TESTI0            | I   | 0                     | Input pin for testing.  Fix this pin to "L" level (DGND level). This pin has a pull-down resistor built in.                                                                                                                                                                                                                                        |

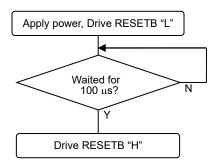

| 3                | RESETB            | -   | 0<br>(*2)             | Input pin for reset.  At the "L" level, the LSI enters initial state. During reset, the entire circuitry stops and enters power down state. Input "L" level when power is supplied. After the power supply voltage is stable, drive this pin to "H" level. Then the entire circuitry can be powered up.  This pin has a pull-up resistor built in. |

| 4                | TESTO             | 0   | Hi-Z                  | Output pins for testing.<br>Leave these pins open.                                                                                                                                                                                                                                                                                                 |

| 6, 7             | SEL0<br>SEL1      | I   | 0                     | Memory bank switching pins. Fix these pins to "L" level when the memory bank function is not used.                                                                                                                                                                                                                                                 |

| 8, 14,<br>19, 26 | DGND              | I   | _                     | Digital ground pin. Also serves as a ground pin for the internal memory.                                                                                                                                                                                                                                                                           |

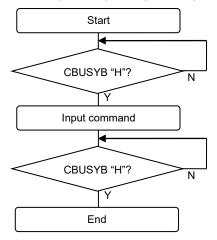

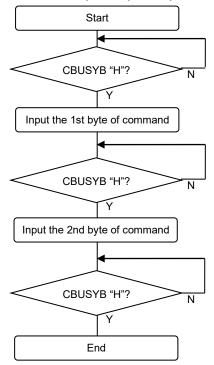

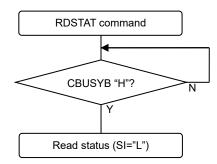

| 13               | CBUSYB            | 0   | 1                     | Output pin for command processing status.  This pin outputs "L" level during command processing. Any command should be entered when this pin is "H" level.                                                                                                                                                                                         |

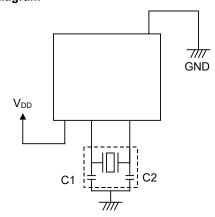

| 15               | XT                | I   | 0                     | Connect to the crystal or ceramic resonator. A feedback resistor around 1 $M\Omega$ is built in between this pin and the XTB pin. Use this pin if need to use an external clock. If the resonator is used, connect it as close to this pin as possible.                                                                                            |

| 16               | ХТВ               | 0   | 1                     | Connect to the crystal or ceramic resonator.  When to use an external clock, leave this pin open.  If the resonator is used, connect it as close to this pin as possible.                                                                                                                                                                          |

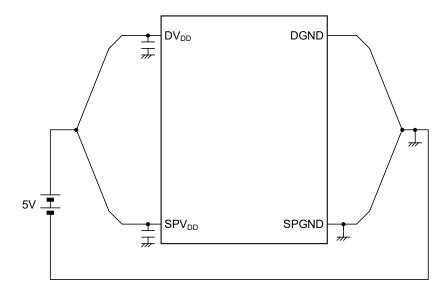

| 17, 22           | DV <sub>DD</sub>  |     | _                     | Power supply pins for logic circuitry. Connect a capacitor of $0.1\mu F$ or more between these pins and DGND pins.                                                                                                                                                                                                                                 |

| 18, 20           | N.C               | _   | _                     | Non connected pins. Leave these pins open.                                                                                                                                                                                                                                                                                                         |

| 21               | $V_{DDL}$         | _   | 0                     | Regulator output pin for internal logic circuitry. Connect a capacitor recommended between this pin and DGND pin.                                                                                                                                                                                                                                  |

| 23               | $V_{\text{DDR}}$  | -   | 0                     | Regulator output pin for Built-in ROM.  Connect a capacitor recommended between this pin and DGND pin.                                                                                                                                                                                                                                             |

| 24               | TESTI1            | _   | 0                     | Test pin. Fix this pin to a DGND level.                                                                                                                                                                                                                                                                                                            |

| 25               | SG                | _   | 0                     | Reference voltage output pin for the speaker amplifier built-in.  Connect a capacitor recommended between this pin and DGND pin.                                                                                                                                                                                                                   |

| 27               | SPV <sub>DD</sub> | _   | _                     | Power supply pin for the speaker amplifier. Connect a bypass capacitor of 0.1μF or more between this pin and SPGND pin.                                                                                                                                                                                                                            |

| 28               | SPGND             |     | _                     | Ground pin for the speaker amplifier.                                                                                                                                                                                                                                                                                                              |

| 29               | SPP               | 0   | 0                     | Positive(+) output pin of the speaker amplifier built-in. Serves as the LINE output (*3), if built-in speaker amplifier is not used.                                                                                                                                                                                                               |

| 30               | SPM               | 0   | Hi-Z                  | Negative(-) output pin of the speaker amplifier built-in.                                                                                                                                                                                                                                                                                          |

<sup>\*1:</sup> Indicates the initial value during reset input or power down.

<sup>\*2: &</sup>quot;H" during power down.

<sup>\*3:</sup> Outputs a voice signal before amplified by the speaker amplifier built-in.

# PIN DESCRIPTION (FOR ML2282X SYNCHRONOUS SERIAL INTERFACE)

| Pin | Symbol | I/O | Initial value<br>(*1) | Description                                                                                                                                                                                                                                                                            |

|-----|--------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | DIPH   | I   | 0                     | Set pin of the SCK clock edge. When this pin is "L" level, rising edge is available for input(SI) and falling edge is available for output(SO). When this pin is "H" level, falling edge is available for input(SI) and rising edge is available for output(SO).                       |

| 9   | CSB    | I   | 1                     | Chip select pin. At the "L" level, data input/output is available.                                                                                                                                                                                                                     |

| 10  | SCK    | I   | 0                     | Synchronous clock input pin for serial interface.                                                                                                                                                                                                                                      |

| 11  | SI     | ı   | 0                     | Input pin of synchronous serial data.  When the DIPH pin is "L" level, data is shifted in at the rising edges of the SCK clock pulses.  When the DIPH pin is "H" level, data is shifted in at the falling edges of the SCK clock pulses.                                               |

| 12  | so     | 0   | Hi-Z                  | Output pin of synchronous serial data. When the DIPH pin is "L" level, data is output at the falling edges of the SCK clock pulses. When the DIPH pin is "H" level, data is output at the rising edges of the SCK clock pulses. When the CSB pin is "H" level, this pin is Hi-Z state. |

<sup>\*1:</sup> Indicate the initial value during reset or power down.

# PIN DESCRIPTION (FOR ML2286X I2C INTERFACE)

| Pin      | Symbol               | I/O | Initial value<br>(*1) | Description                                                                                                                                                                                                                                                       |

|----------|----------------------|-----|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5, 9, 12 | SAD0<br>SAD1<br>SAD2 | I   | 0                     | Set pin of the slave address.                                                                                                                                                                                                                                     |

| 10       | SCL                  | I   | 1                     | Clock input pin for I2C serial interface. This pin should be connected to pull-up resistor.                                                                                                                                                                       |

| 11       | SDA                  | Ю   | 1                     | Input/output pin for I2C serial data. Use for setting the mode of write/read and writing address, writing data or reading data. This pin should be connected to pull-up resistor. (N-ch MOS) open drain, when output mode. High impedance(Hi-Z), when input mode. |

<sup>\*1:</sup> Indicate the initial value during reset or power down.

## **ABSOLUTE MAXIMUM RATINGS**

(DGND = SPGND = 0 V, Ta = 25°C)

|                              |                                         |                                                                  | (50.15 0.015                  | 0 t, ia 20 0) |

|------------------------------|-----------------------------------------|------------------------------------------------------------------|-------------------------------|---------------|

| Parameter                    | Symbol                                  | Condition                                                        | Rating                        | Unit          |

| Power supply voltage         | DV <sub>DD</sub> ,<br>SPV <sub>DD</sub> | _                                                                | -0.3 to +7.0                  | V             |

| Input voltage                | V <sub>IN</sub>                         |                                                                  | -0.3 to DV <sub>DD</sub> +0.3 | V             |

| Power dissipation            | P <sub>D</sub>                          | _                                                                | 938                           | mW            |

| ·                            |                                         | Applies to all pins except SPM, SPP, $V_{DDL}$ , and $V_{DDR}$ . | 10                            | mA            |

| Output short-circuit current | los                                     | Applies to SPM and SPP pins.                                     | 300                           | mA            |

|                              |                                         | Applies to V <sub>DDL</sub> and V <sub>DDR</sub> pins.           | 50                            | mA            |

| Storage temperature          | T <sub>STG</sub>                        | _                                                                | −55 to +150                   | °C            |

## RECOMMENDED OPERATING CONDITIONS

(DGND = SPGND = 0 V)

| Parameter                                  | Symbol                                  | Condition | Range                    |               |             | Unit |

|--------------------------------------------|-----------------------------------------|-----------|--------------------------|---------------|-------------|------|

| Power supply voltage                       | DV <sub>DD</sub> ,<br>SPV <sub>DD</sub> | _         | 2.7 to 3.6<br>4.5 to 5.5 |               |             | ٧    |

| Operating temperature                      | T <sub>OP</sub>                         | _         | -40 to +85               |               |             | °C   |

| Master clock frequency                     | f <sub>osc</sub>                        | _         | Min.<br>3.5              | Typ.<br>4.096 | Max.<br>4.5 | MHz  |

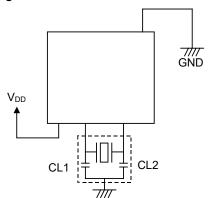

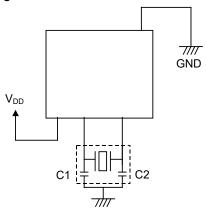

| External capacitors for crystal oscillator | Cd, Cg                                  | _         | 15                       | 30            | 45          | pF   |

## **ELECTRICAL CHARACTERISTICS**

## DC Characteristics (for the 3V applications)

$DV_{DD}$  =  $SPV_{DD}$  = 2.7 to 3.6 V, DGND = AGND = 0 V, Ta = -40 to +85°C

|                                | 1                 | D V DD                             | 3 0.0 V, BOILE        | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | v, ia io i            | 000  |

|--------------------------------|-------------------|------------------------------------|-----------------------|-----------------------------------------|-----------------------|------|

| Parameter                      | Symbol            | Condition                          | Min.                  | Тур.                                    | Max.                  | Unit |

| _"H" input voltage             | VIH               | _                                  | $0.86 \times DV_{DD}$ |                                         | $DV_DD$               | V    |

| "L" input voltage              | VIL               | _                                  | 0                     |                                         | $0.14 \times DV_{DD}$ | V    |

| "H" output voltage 1           | V <sub>OH1</sub>  | $I_{OH} = -1 \text{ mA}$           | DV <sub>DD</sub> -0.4 |                                         | _                     | V    |

| "H" output voltage 2 (*1)      | $V_{OH2}$         | I <sub>OH</sub> = -50 μA           | DV <sub>DD</sub> -0.4 | _                                       | _                     | V    |

| "L" output voltage 1           | V <sub>OL1</sub>  | $I_{OL} = 2 \text{ mA}$            |                       |                                         | 0.4                   | V    |

| "L" output voltage 2 (*1)      | V <sub>OL2</sub>  | I <sub>OL</sub> = 50 μA            | _                     |                                         | 0.4                   | V    |

| "L" output voltage 3 (*2)      | $V_{OL3}$         | $I_{OL} = 3 \text{ mA}$            | _                     |                                         | 0.4                   | V    |

| "H" input current 1            | I <sub>IH1</sub>  | $V_{IH} = DV_{DD}$                 | _                     |                                         | 10                    | μΑ   |

| "H" input current 2 (*3)       | I <sub>IH2</sub>  | $V_{IH} = DV_{DD}$                 | 0.3                   | 2.0                                     | 15                    | μA   |

| "H" input current 3 (*4)       | I <sub>IH3</sub>  | $V_{IH} = DV_{DD}$                 | 2                     | 30                                      | 200                   | μA   |

| "L" input current 1            | I <sub>IL1</sub>  | V <sub>IL</sub> = GND              | -10                   |                                         | _                     | μA   |

| "L" input current 2 (*3)       | I <sub>IL2</sub>  | V <sub>IL</sub> = GND              | -15                   | -2.0                                    | -0.3                  | μA   |

| "L" input current 3 (*5)       | I <sub>IL3</sub>  | V <sub>IL</sub> = GND              | -200                  | -30                                     | -2                    | μΑ   |

| "H" output leak current 3 (*6) | Іігон             | V <sub>OH</sub> = DV <sub>DD</sub> | _                     |                                         | 10                    | μΑ   |

| "L" output leak current 3 (*6) | I <sub>ILOL</sub> | V <sub>OL</sub> = GND              | -10                   |                                         | _                     | μΑ   |

| Supply current during playback | I <sub>DD</sub>   | fosc = 4.096 MHz<br>No output load | _                     | _                                       | 20                    | mA   |

| Power-down supply              | 1                 | Ta = -40 to +40°C                  |                       | 1                                       | 10                    | μΑ   |

| current                        | I <sub>DDS</sub>  | Ta = -40 to +85°C                  | _                     | 1                                       | 20                    | μA   |

<sup>\*1:</sup> Applies to the XTB pin.

<sup>\*2:</sup> Applies to the SCL, SDA pin.

<sup>\*3:</sup> Applies to the XT pin.

<sup>\*4:</sup> Applies to the TESTI0 pin.

<sup>\*5:</sup> Applies to the RESETB pin.

<sup>\*6:</sup> Applies to the TESTO pin.

## DC Characteristics (for the 5V applications)

$DV_{DD} = SPV_{DD} = 4.5 \text{ to } 5.5 \text{ V}, DGND = SPGND = 0 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C}$

|                                    |                   | $DV_{DD} = SPV_{DD} = 4.5 \text{ to}$          | 3.3 V, DGND           | - 3FGND - U | v, ra – <del>-4</del> 0 i | .0 +65 C |

|------------------------------------|-------------------|------------------------------------------------|-----------------------|-------------|---------------------------|----------|

| Parameter                          | Symbol            | Condition                                      | Min.                  | Тур.        | Max.                      | Unit     |

| _"H" input voltage                 | VIH               | _                                              | $0.8 \times DV_{DD}$  | _           | DV <sub>DD</sub>          | V        |

| "L" input voltage                  | $V_{IL}$          | _                                              | 0                     | _           | $0.2 \times DV_{DD}$      | V        |

| "H" output voltage 1               | V <sub>OH1</sub>  | $I_{OH} = -1 \text{ mA}$                       | DV <sub>DD</sub> -0.4 |             |                           | V        |

| "H" output voltage 2 (*1)          | $V_{\text{OH2}}$  | I <sub>OH</sub> = −50µА                        | DV <sub>DD</sub> -0.4 |             | _                         | V        |

| "L" output voltage 1               | $V_{OL1}$         | $I_{OL} = 2 \text{ mA}$                        | _                     |             | 0.4                       | V        |

| "L" output voltage 2 (*1)          | $V_{OL2}$         | I <sub>OL</sub> = 50 μA                        |                       |             | 0.4                       | V        |

| "L" output voltage 3 (*2)          | V <sub>OL3</sub>  | $I_{OL} = 3 \text{ mA}$                        | _                     |             | 0.4                       | V        |

| "H" input current 1                | I <sub>IH1</sub>  | $V_{IH} = DV_{DD}$                             | _                     |             | 10                        | μA       |

| "H" input current 2 (*3)           | I <sub>IH2</sub>  | $V_{IH} = DV_{DD}$                             | 0.8                   | 5.0         | 20                        | μA       |

| "H" input current 3 (*4)           | I <sub>IH3</sub>  | $V_{IH} = DV_{DD}$                             | 20                    | 100         | 400                       | μA       |

| "L" input current 1                | I <sub>IL1</sub>  | V <sub>IL</sub> = GND                          | -10                   |             | _                         | μA       |

| "L" input current 2 (*3)           | I <sub>IL2</sub>  | V <sub>IL</sub> = GND                          | -20                   | -5.0        | -0.8                      | μA       |

| "L" input current 3 (*5)           | I <sub>IL3</sub>  | VIL = GND                                      | -400                  | -100        | -20                       | μA       |

| "L" output leak current 2 (*6)     | I <sub>ILOH</sub> | V <sub>OH</sub> = DV <sub>DD</sub>             |                       |             | 10                        | μΑ       |

| "L" output leak current 3<br>_(*6) | lilol             | V <sub>OL</sub> = GND                          | -10                   |             | _                         | μA       |

| Supply current during playback     | I <sub>DD</sub>   | f <sub>OSC</sub> = 4.096 MHz<br>No output load | _                     |             | 25                        | mA       |

| Power-down supply                  | lone              | Ta = -20 to +40°C                              |                       | 1           | 15                        | μA       |

| current                            | I <sub>DDS</sub>  | Ta = -20 to +85°C                              | _                     | 1           | 30                        | μA       |

<sup>\*1:</sup> Applies to the XTB pin.

<sup>\*2:</sup> Applies to the SCL and SDA pins.

<sup>\*3:</sup> Applies to the XT pin.

<sup>\*4:</sup> Applies to the TESTI0 pin.

<sup>\*5:</sup> Applies to the RESETB pin.

<sup>\*6:</sup> Applies to the TESTO pin.

## **Characteristics of Analog Circuitry (for the 3V applications)**

$DV_{DD}$  =  $SPV_{DD}$  = 2.7 to 3.6 V, DGND = SPGND = 0 V, Ta = -40 to +85°C

|                                                                        |                  | עט יסו דעט – טויי דעט – טויי דעט – טויי דעט – טויי דעט א                            | 0.0 V, DOIND             | 01 0110             | v, ia io to              | .00 0 |

|------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------|-------|

| Parameter                                                              | Symbol           | Condition                                                                           | Min.                     | Тур.                | Max.                     | Unit  |

| AIN input resistance                                                   | RAIN             | _                                                                                   | 15                       | 20                  | 25                       | kΩ    |

| AIN input voltage range                                                | V <sub>AIN</sub> |                                                                                     |                          |                     | DV <sub>DD</sub> ×2/3    | Vp-p  |

| LINE output load resistance                                            | RLA              | During 1/2 DV <sub>DD</sub> output                                                  | 10                       |                     |                          | kΩ    |

| LINE output voltage range                                              | V <sub>AO</sub>  | No output load                                                                      | DV <sub>DD</sub> /6      |                     | DV <sub>DD</sub> ×5/6    | V     |

| SG output voltage                                                      | $V_{SG}$         | _                                                                                   | 0.95×V <sub>DDL</sub> /2 | V <sub>DDL</sub> /2 | 1.05×V <sub>DDL</sub> /2 | V     |

| SG output resistance                                                   | Rsg              | During power down                                                                   | 57                       | 96                  | 135                      | kΩ    |

| SPM, SPP output load resistance                                        | RLSP             | _                                                                                   | 8                        |                     |                          | Ω     |

| Speaker amplifier output power                                         | P <sub>SPO</sub> | SPV <sub>DD</sub> = 3.3V, f = 1kHz<br>R <sub>SPO</sub> = $8\Omega$ , THD $\geq$ 10% | 100                      | 300                 |                          | mW    |

| Output offset voltage<br>between SPM and SPP<br>with no signal present | Vof              | SPIN–SPM gain = 0dB With a load of $8\Omega$                                        | <del>-5</del> 0          | _                   | +50                      | mV    |

## **Characteristics of Analog Circuitry (for the 5V applications)**

$DV_{DD}$  =  $SPV_{DD}$  = 4.5 to 5.5 V, DGND = SPGND = 0 V, Ta = -20 to +85°C

|                                                                        |                  |                                                                                 | ,                        |                     | ,                        |      |

|------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|--------------------------|---------------------|--------------------------|------|

| Parameter                                                              | Symbol           | Condition                                                                       | Min.                     | Тур.                | Max.                     | Unit |

| AIN input resistance                                                   | RAIN             | _                                                                               | 15                       | 20                  | 25                       | kΩ   |

| AIN input voltage range                                                | V <sub>AIN</sub> |                                                                                 | _                        |                     | DV <sub>DD</sub> ×2/3    | Vp-p |

| LINE output load resistance                                            | R <sub>LA</sub>  | During 1/2 DV <sub>DD</sub> output                                              | 10                       |                     |                          | kΩ   |

| LINE output voltage range                                              | V <sub>AO</sub>  | No output load                                                                  | DV <sub>DD</sub> /6      |                     | DV <sub>DD</sub> ×5/6    | V    |

| SG output voltage                                                      | Vsg              | _                                                                               | 0.95×V <sub>DDL</sub> /2 | V <sub>DDL</sub> /2 | 1.05×V <sub>DDL</sub> /2 | V    |

| SG output resistance                                                   | R <sub>SG</sub>  | During power down                                                               | 57                       | 96                  | 135                      | kΩ   |

| SPM, SPP output load resistance                                        | R <sub>LSP</sub> | _                                                                               | 8                        |                     |                          | Ω    |

| Speaker amplifier output power                                         | Pspo             | SPV <sub>DD</sub> = 5.0V, f = 1kHz<br>R <sub>SPO</sub> = 8Ω, THD≥10%<br>Ta=25°C | 500                      | 700                 | _                        | mW   |

| Output offset voltage<br>between SPM and SPP<br>with no signal present | V <sub>OF</sub>  | SPIN–SPM gain = 0dB With a load of $8\Omega$                                    | -50                      |                     | +50                      | mV   |

## **AC Characteristics (Common to All Products)**

|                                 | DV <sub>DD</sub> = SPV <sub>D</sub>                                 | $_{DD}$ = 2.7 to 5.5 V, DGND = SPGND = 0 V, Ta = -40 to +8 |                                    |                  |                   |      |      |

|---------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|------------------------------------|------------------|-------------------|------|------|

| Parameter                       | Applicable command                                                  | Symbol                                                     | /mbol Condition                    |                  | Тур.              | Max. | Unit |

| Master clock duty cycle         |                                                                     | f <sub>duty</sub>                                          | _                                  | 40               | 50                | 60   | %    |

| RESETB input pulse width        |                                                                     | t <sub>RST</sub>                                           | _                                  | 100              | _                 |      | μS   |

| Reset noise rejection pulse wid | dth                                                                 | t <sub>NRST</sub>                                          | _                                  | _                | _                 | 0.1  | μS   |

|                                 | STOP, SLOOP,<br>CLOOP, CVOL,<br>AVOL                                | t <sub>INT</sub>                                           |                                    | 2                | _                 | _    | ms   |

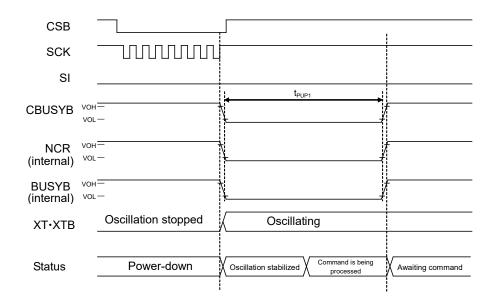

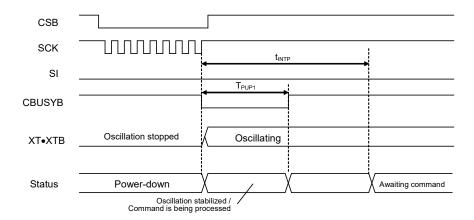

| Command input interval time     | PUP                                                                 | t <sub>INTP</sub>                                          | f <sub>OSC</sub> = 4.096 MHz       | 10               | _                 | _    | ms   |

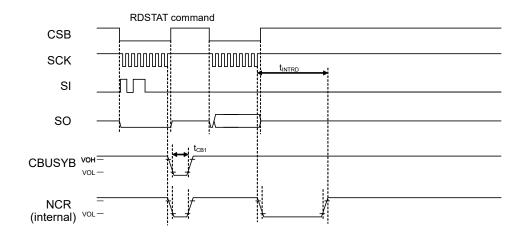

|                                 | RDSTAT (After status read)                                          | t <sub>INTRD</sub>                                         |                                    | 500              | _                 | _    | μS   |

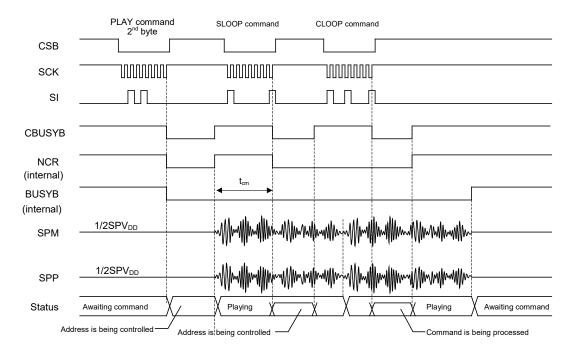

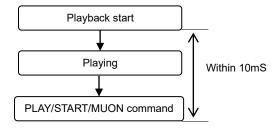

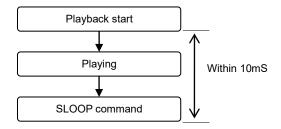

| Command input enable time       | SLOOP<br>Continuous play<br>by PLAY/MUON                            | t <sub>cm</sub>                                            | fosc = 4.096 MHz                   | _                | _                 | 10   | ms   |

|                                 | PUP                                                                 | t <sub>PUP1</sub>                                          | f <sub>OSC</sub> = 4.096 MHz       | 2.0              | 2.5               | 3.0  | ms   |

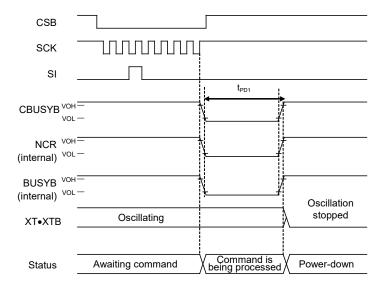

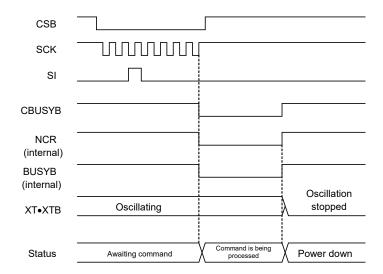

|                                 | PDWN                                                                | t <sub>PD1</sub>                                           | f <sub>OSC</sub> = 4.096 MHz       | _                | _                 | 20   | μS   |

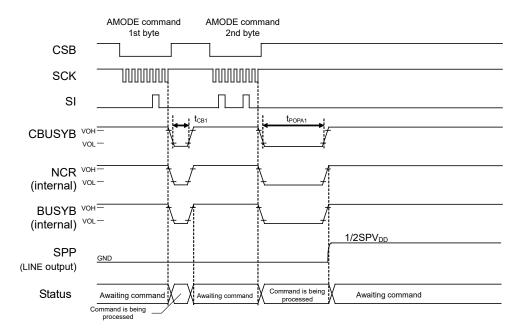

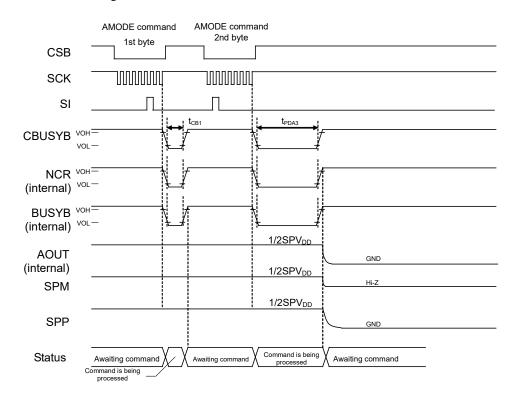

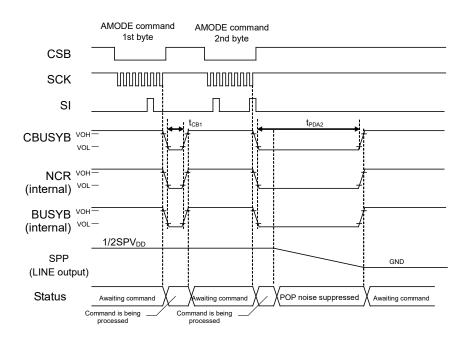

|                                 | 2nd byte of AMODE<br>(POP = "0"<br>SPEN = "0",<br>DAEN = "0" → "1") | t <sub>POPA1</sub>                                         | f <sub>OSC</sub> = 4.096 MHz       | 58               | 60                | 62   | ms   |

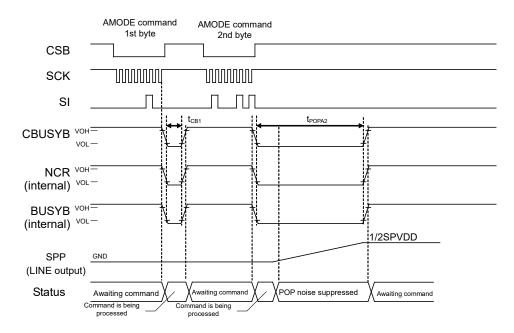

|                                 | 2nd byte of AMODE<br>(POP = "1"<br>SPEN = "0",<br>DAEN = "0" →"1")  | tpopa2                                                     | fosc = 4.096 MHz                   | 90               | 93                | 95   | ms   |

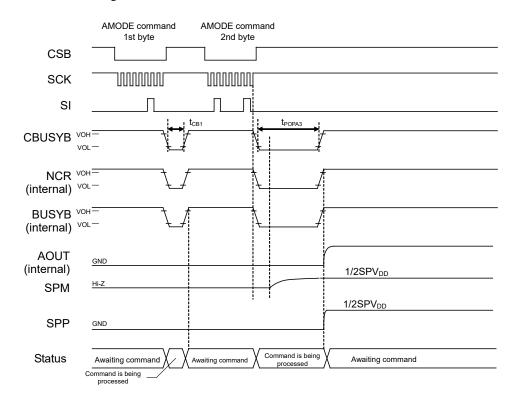

| CBUSYB "L" level output time    | 2nd byte of AMODE (SPEN = "0" →"1")                                 | t <sub>РОРАЗ</sub>                                         | fosc = 4.096 MHz<br>AVOL="0Eh~3Fh" | 46* <sup>2</sup> | 60*3              | 70*4 | ms   |

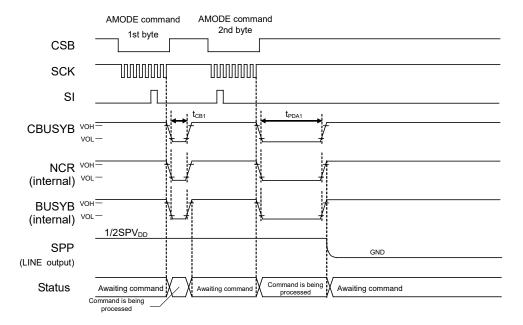

|                                 | 2nd byte of AMODE<br>(POP = "0"<br>SPEN = "0",<br>DAEN = "1" →"0")  | t <sub>PDA1</sub>                                          | f <sub>OSC</sub> = 4.096 MHz       | 108              | 110               | 112  | ms   |

|                                 | 2nd byte of AMODE<br>(POP = "1"<br>SPEN = "0",<br>DAEN = "1" →"0")  | tPDA2                                                      | fosc = 4.096 MHz                   | 140              | 142               | 144  | ms   |

|                                 | 2nd byte of AMODE (SPEN = "1" →"0")                                 | t <sub>PDA3</sub>                                          | fosc = 4.096 MHz<br>AVOL="0Eh~3Fh" | 0.2*2            | 6.5 <sup>*3</sup> | 17*4 | ms   |

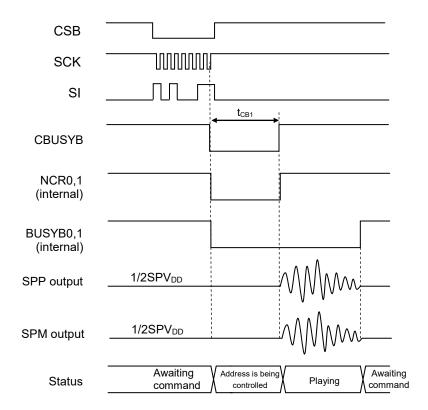

|                                 | (*1)                                                                | t <sub>CB1</sub>                                           | f <sub>OSC</sub> = 4.096 MHz       | _                | _                 | 2    | ms   |

Note: Output pin load capacitance = 45 pF

<sup>\*1:</sup> Applies to cases where a command is input except after a PUP, PDWN, or 2nd byte of AMODE command input.

<sup>\*2:</sup> The value when AVOL="0Eh" is set.

<sup>\*3:</sup> The value when AVOL="23h" is set.

<sup>\*4:</sup> The value when AVOL="3Fh" is set.

## AC Characteristics of Synchronous Serial Command Interface (Applied to ML2282X)

$DV_{DD} = SPV_{DD} = 2.7 \text{ to } 5.5 \text{ V}, DGND = SPGND = 0 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C}$

|                                 | D 4 UU - OI        | V DD - Z.1 to             | 3.5 V, DGIND - 31 C       | ט – טווכ | v, ra - | - <del>- 1</del> 0 10 | 100 0 |

|---------------------------------|--------------------|---------------------------|---------------------------|----------|---------|-----------------------|-------|

| Parameter                       | Applicable command | Symbol                    | Condition                 | Min.     | Тур.    | Max.                  | Unit  |

| SCK input enable time from CS   | SB fall edge       | tesck                     | _                         | 100      |         | _                     | ns    |

| SCK hold time from CSB rise e   | edge               | tсsн                      | _                         | 100      |         | _                     | ns    |

| Data floating time from CSB ris | se edge            | t <sub>DOZ</sub>          | $R_L = 3 \text{ k}\Omega$ | _        |         | 100                   | ns    |

| Data setup time from SCK rise   | edge               | t <sub>DIS1</sub>         | DIPH = "0"                | 50       | _       | _                     | ns    |

| Data hold time from SCK rise e  | t <sub>DIH1</sub>  | DIPH = "0"                | 50                        |          | _       | ns                    |       |

| Data output delay time from SO  | t <sub>DOD1</sub>  | $R_L = 3 \text{ k}\Omega$ | _                         | _        | 80      | ns                    |       |

| Data setup time from SCK fall   | t <sub>DIS2</sub>  | DIPH = "1"                | 50                        |          | _       | ns                    |       |

| Data hold time from SCK fall e  | t <sub>DIH2</sub>  | DIPH = "1"                | 50                        |          | _       | ns                    |       |

| Data output delay time from SO  | t <sub>DOD2</sub>  | $R_L = 3 \text{ k}\Omega$ | _                         | _        | 80      | ns                    |       |

| SCK "H" level pulse width       | tsckh              | _                         | 100                       |          | _       | ns                    |       |

| SCK "L" level pulse width       | t <sub>SCKL</sub>  | _                         | 100                       |          | _       | ns                    |       |

| CBUSYB output delay time from   | t <sub>DBSY1</sub> | DIPH = "0"                | _                         | _        | 150     | ns                    |       |

| CBUSYB output delay time from   | t <sub>DBSY2</sub> | DIPH = "1"                | _                         | _        | 150     | ns                    |       |

Note: Output pin load capacitance = 45 pF

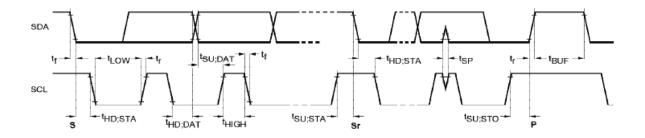

## AC Characteristics of I2C Command Interface (Applied to ML2286X)

$DV_{DD} = SPV_{DD} = 2.7 \text{ to } 5.5 \text{ V}, DGND = SPGND = 0 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C}$

| December:                                                       |                     | (High-spe        | 1.1  |      |

|-----------------------------------------------------------------|---------------------|------------------|------|------|

| Parameter                                                       | Symbol              | Min.             | Max. | Unit |

| SCL clock frequence                                             | tscl                | 0                | 400  | kHz  |

| Hold time (repeated) START condition                            | t <sub>HD:STA</sub> | 0.6              |      | 6    |

| After this period, the first clock pulse is generated.          | thD;STA             | 0.0              | _    | μS   |

| SCL "L" level pulse width                                       | t <sub>LOW</sub>    | 1.3              | —    | μS   |

| SCL "H" level pulse width                                       | t <sub>HIGH</sub>   | 0.6              | _    | μS   |

| Setup time for repeated START condition                         | tsu;sta             | 0.6              | _    | μS   |

| Data hold time: For I2C bus devices                             | thd;dat             | 0                | 0.9  | μS   |

| Data setup time                                                 | t <sub>SU;DAT</sub> | 100              | _    | ns   |

| SDA and SCL signal rise time                                    | tr                  | 20               | 300  | ns   |

| SDA and SCL signal fall time                                    | <b>t</b> f          | 20               | 300  | ns   |

| STOP condition setup time                                       | t <sub>SU;STO</sub> | 0.6              | _    | μS   |

| Bus free time between STOP condition and START condition        | t <sub>BUF</sub>    | 1.3              | _    | μS   |

| Capacitive load for each bus line                               | Cb                  |                  | 400  | PF   |

| Noise margin at a "L" level in each device connected (including | \/                  | 0.1×             |      | V    |

| hysteresis)                                                     | $V_{nL}$            | $DV_DD$          | _    | V    |

| Noise margin at a "H" level in each device connected (including | V <sub>nH</sub>     | 0.1×             |      | V    |

| hysteresis)                                                     | VnH                 | DV <sub>DD</sub> | _    | V    |

| Pulse width of spikes which must be suppressed by the input     | t <sub>sp</sub>     | 0                | 50   | ns   |

| filter                                                          | ısp                 | J                | 30   | 113  |

Note: Output pin load capacitance = 45 pF

## TIMING DIAGRAMS (3-WIRED SERIAL CLOCK-SYNCHRONIZED (ML2282X))

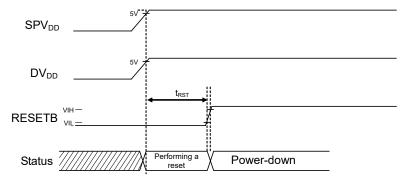

## **Power-On Timing**

Oscillation is stopped after power-on.

#### **Power-Up Timing**

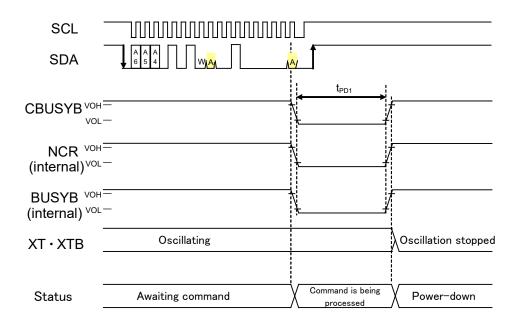

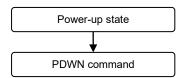

## Power-Down Timing (At the PDWN command Input)

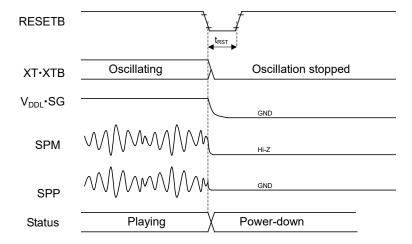

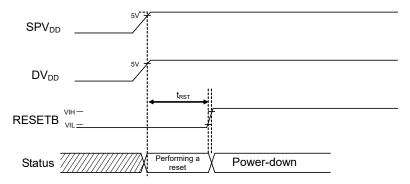

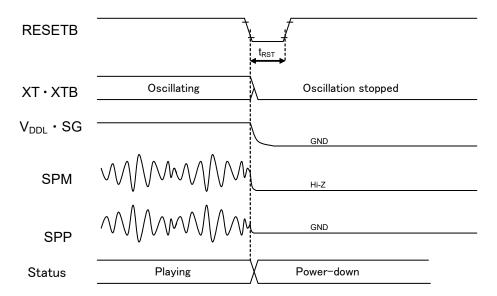

## **Power-Down Timing (At the RESETB Input)**

Note: The same timing is applied in the case that the RESETB signal is input during command waiting.

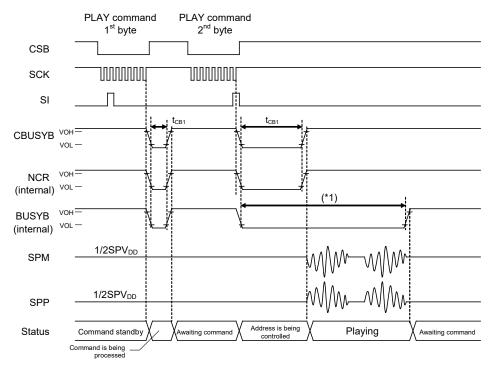

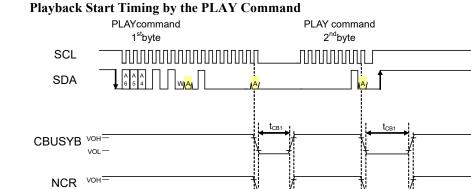

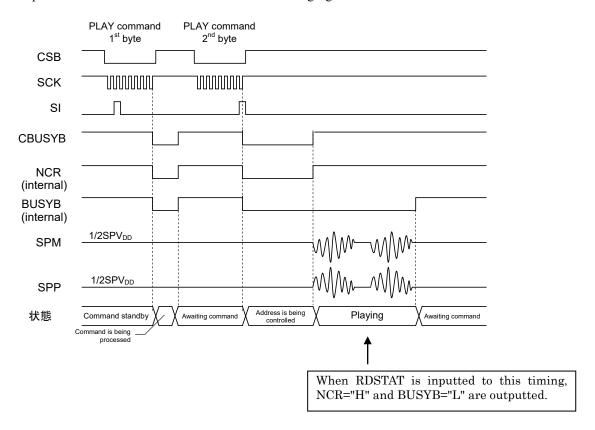

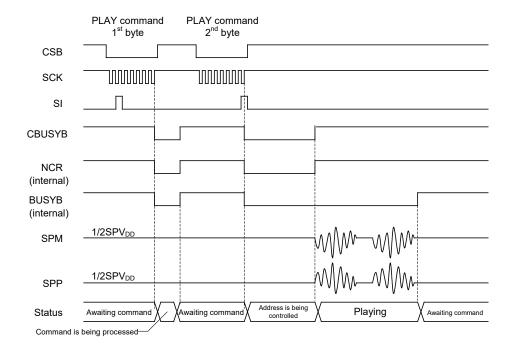

## Playback Start Timing by the PLAY Command

Note: The length of the "L" interval of BUSYB is  $t_{\text{CB1}}$  + voice reproduction time.

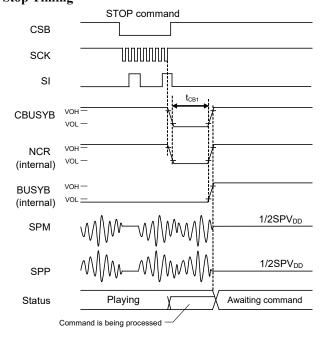

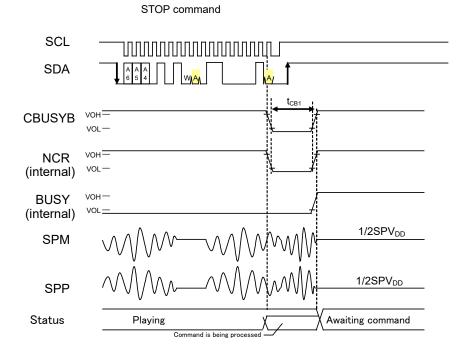

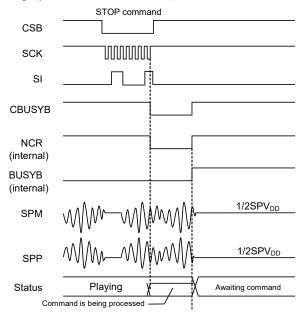

## **Playback Stop Timing**

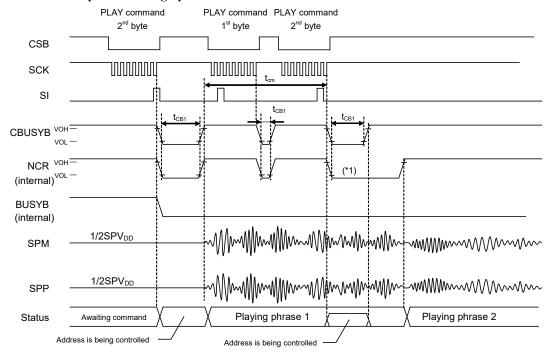

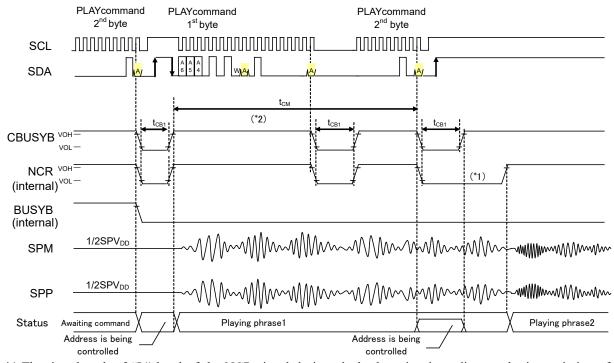

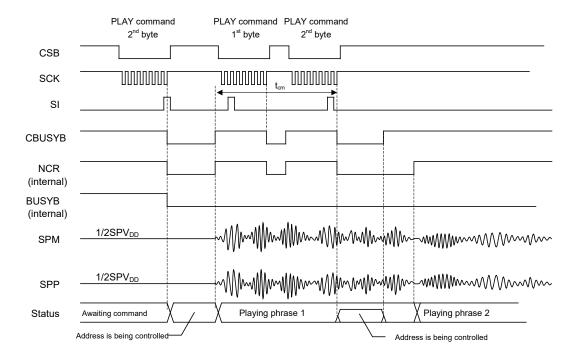

#### Continuous Playback Timing by the PLAY Command

- \*1: The time length of "L" level of the NCR signal during playback varies depending on the input timing of command.

- \*2: The following PLAY command must be inputted within t<sub>cm</sub>. When it cannot, please input the phrase 2 PLAY command after checking that BUSYB became "H"(phrase 1 playback has been finished).

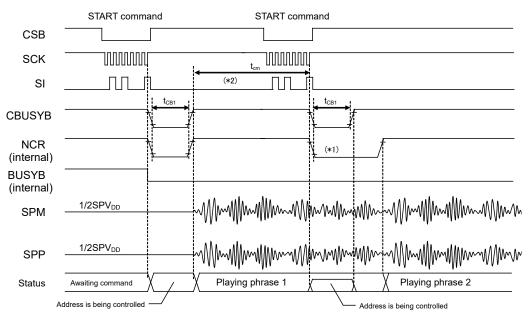

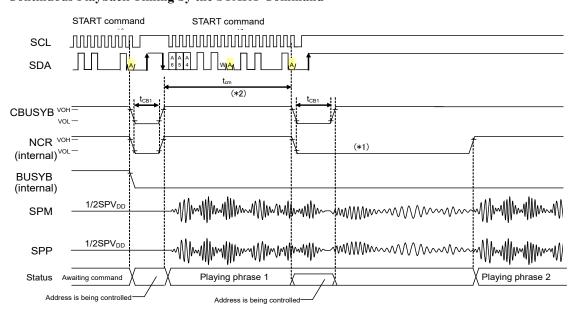

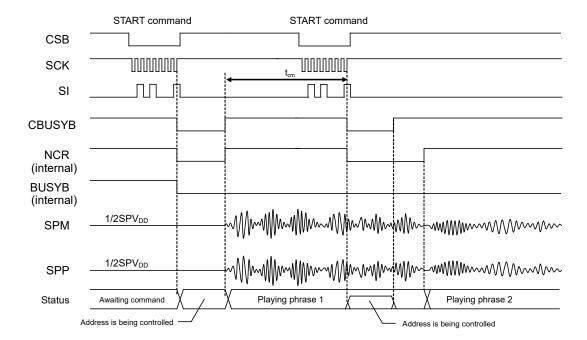

#### Continuous Playback Timing by the START Command

- \*1: The time length of "L" level of the NCR signal during playback varies depending on the input timing of

- \*2: The following START command must be inputted within t<sub>cm</sub>. When it cannot, please input the phrase 2 START command after checking that BUSYB became "H"(phrase 1 playback has been finished).

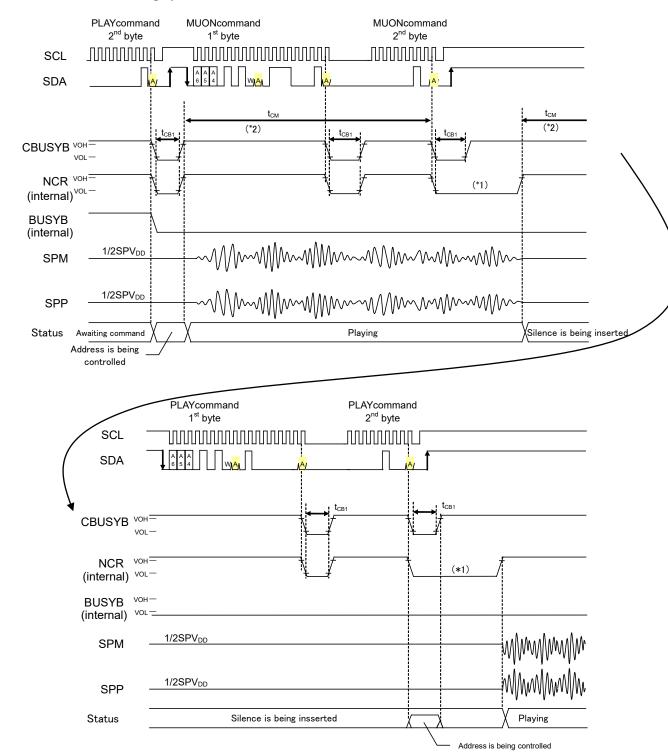

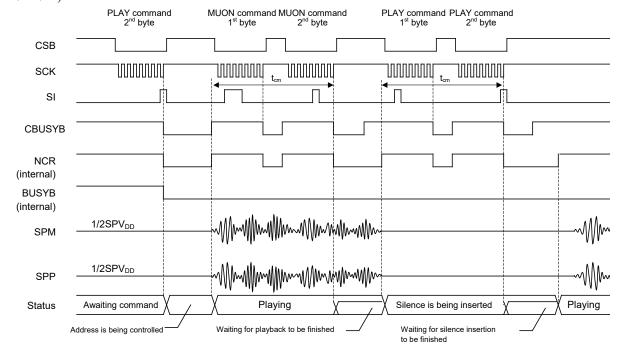

- \*1: The time length of "L" level of the NCR signal during playback or silence insertion varies depending on the input timing of command.

- \*2: The following MUON commnad or PLAY command must be inputted within t<sub>cm</sub>. When it cannot, please input the MUON commnad or PLAY command after checking that BUSYB became "H"(playback has been finished).

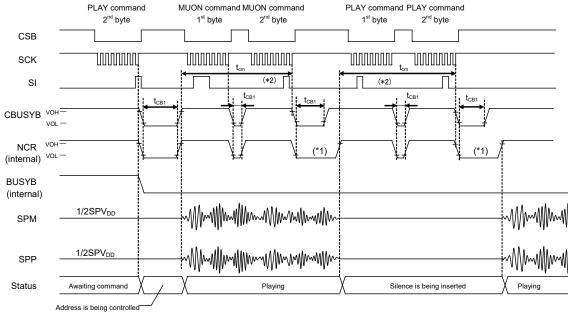

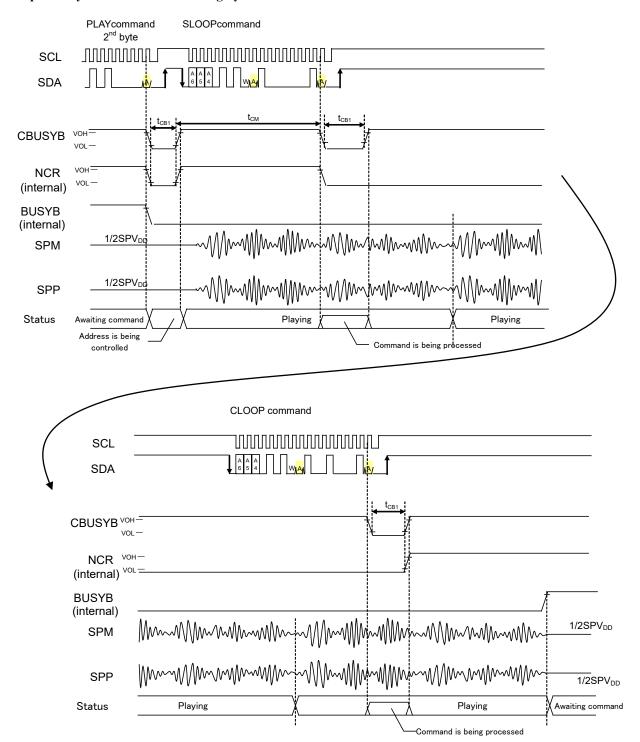

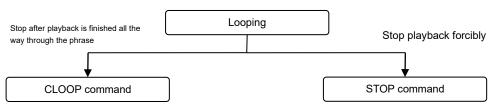

#### Repeat Playback Set/Release Timing by the SLOOP and CLOOP Commands

\*1: The SLOOP commnad must be inputted within t<sub>cm</sub>.

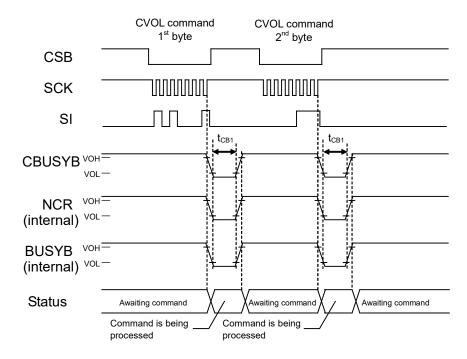

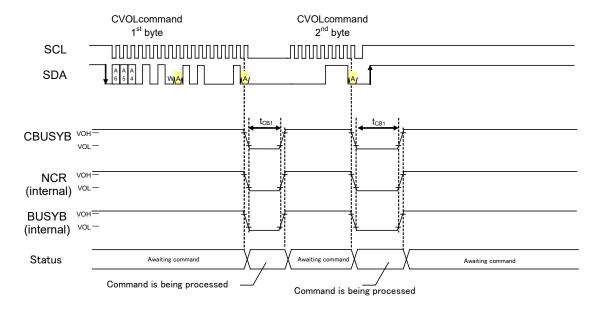

## Timing of Volume Change by the CVOL Command

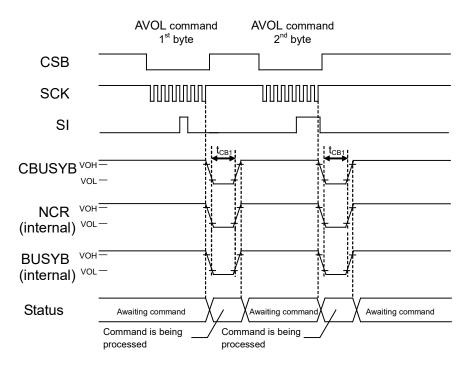

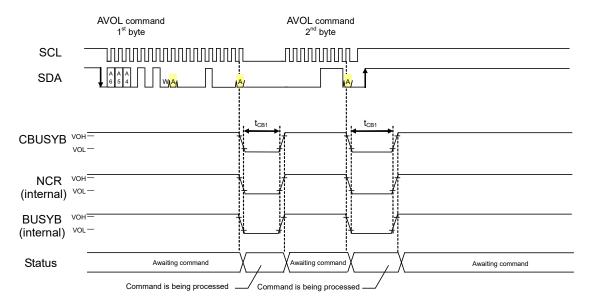

## Timing of Volume Change by the AVOL Command

## TIMING DIAGRAMS ( I2C INTERFACE (ML2286X) )

## **Power-On Timing**

Oscillation is stopped after power-on.

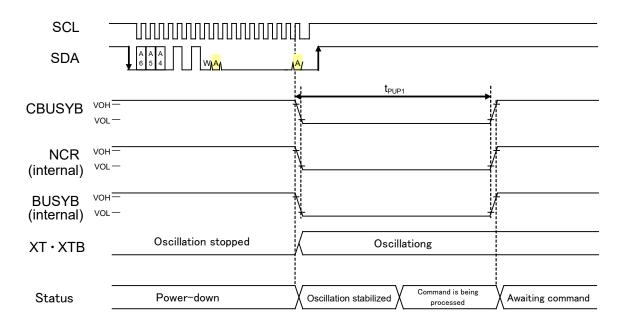

## **Power-Up Timing**

#### Power-Down Timing (At the PDWN command Input)

## **Power-Down Timing (At the RESETB Input)**

Note: The same timing is applied in the case that the RESETB signal is input during command waiting.

Address is being

contorolled

Note: The length of the "L" interval of BUSYB is t<sub>CB1</sub> + voice reproduction time.

Command is being processed-

## **Playback Stop Timing**

#### Continuous Playback Timing by the PLAY Command

<sup>\*1:</sup>The time length of "L" level of the NCR signal during playback varies depending on the input timing of command.

#### Continuous Playback Timing by the START Command

<sup>\*1:</sup> The time length of "L" level of the NCR signal during playback varies depending on the input timing of command.

<sup>\*2:</sup> The following PLAY command must be inputted within t<sub>cm</sub>. When it cannot, please input the phrase 2 PLAY command after checking that BUSYB became "H"(phrase 1 playback has been finished).

<sup>\*2:</sup> Please input the following START command within tcm. When it cannot, please input the phrase 2 START command after checking that BUSYB became "H"(phrase 1 playback has been finished).

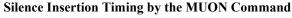

#### Silence Insertion Timing by the MUON Command

- \*1: The time length of "L" level of the NCR signal during playback or silence insertion varies depending on the input timing of command.

- \*2: Please input the following MUON command or PLAY command within tcm. When it cannot, please input the MUON command or PLAY command after checking that BUSYB became "H"(playback has been finished).

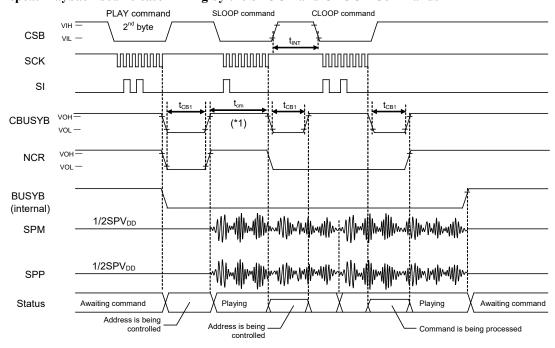

#### Repeat Playback Set/Release Timing by the SLOOP and CLOOP Commands

<sup>\*1:</sup> The SLOOP commnad must be inputted within  $t_{\text{cm}}$ .

## Timing of Volume Change by the CVOL Command

## Timing of Volume Change by the AVOL Command

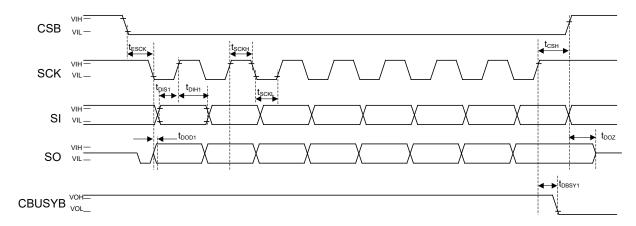

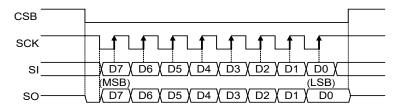

## Serial Command Interface Timing (Applied to ML2282X)

when DIPH pin is "L" level (Rise edge for input, fall edge for output)

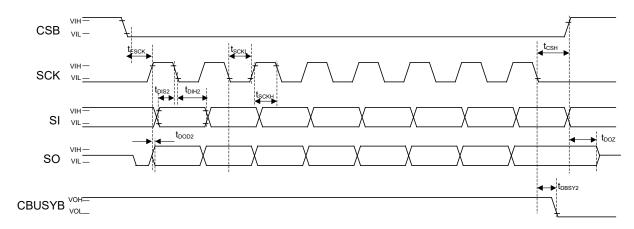

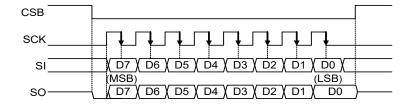

## **Serial Command Interface Timing (Applied to ML2282X)**

when DIPH pin is "H" level (Fall edge for input, rise edge for output)

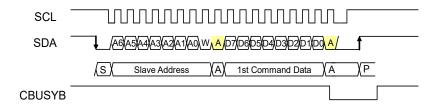

#### I2C Command Interface Timing (Applied to ML2286X)

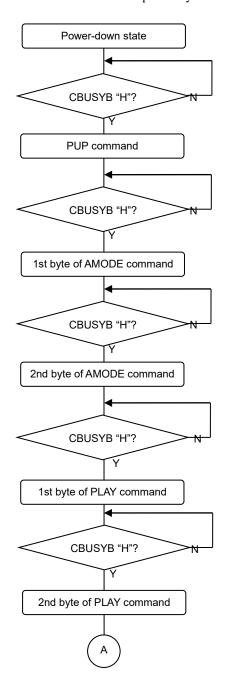

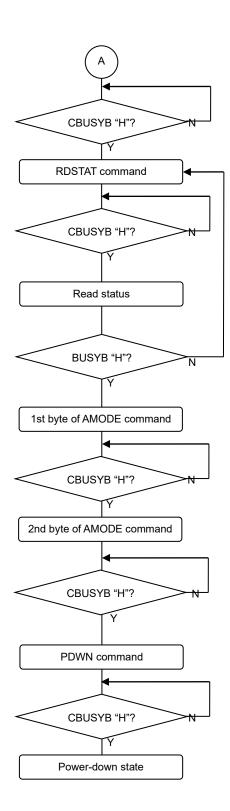

#### **FUNCTIONAL DESCRIPTION**

#### **Synchronous Serial Command Interface**

The CSB, SCK, SI, and SO pins are used to input the command data or to read the status. Driving the CSB pin to "L" level enables the serial CPU interface.

After the CSB pin is driven to "L" level, the command data are input through the SI pin from the MSB synchronized with the SCK clock. The command data shifts in through the SI pin at the rising or falling edge of the SCK clock pulse. Then, a command is executed at the rising or falling edge of the eighth pulse of the SCK clock.

As for status reading, status is output from the SO pin, synchronized with the SCK clock after the CSB pin is driven to "L" level.

The SCK clock edge is specified by the input level of the DIPH pin.

- When the DIPH pin is "L" level, rising edge is available for input from SI pin and falling edge is available for output from SO pin.

- When the DIPH pin is "H" level, falling edge is available for input from SI pin and rising edge is available for output from SO pin.

It is possible to input command data, even if the CSB pin is fixed by "L" level. However, if unexpected pulses caused by noise are induced through the SCK pin, SCK clock pulses are incorrectly counted, causing a failure in normal recognition of command. Then it is recommended that the CSB pin is "L" level only for command input.

The count of the SCK clock pulse is initialized when the CSB pin goes to "H" level.

#### Command Data Input or Status Read Timing

• When DIPH pin is "L" level

• When DIPH pin is "H" level

The following table shows the contents of each data output at a status read.

|     | Output status signal            |

|-----|---------------------------------|

| MSB | _                               |

| 7SB | _                               |

| 6SB | Channel 2 BUSYB output (BUSYB1) |

| 5SB | Channel 1 BUSYB output (BUSYB0) |

| 4SB | _                               |

| 3SB | _                               |

| 2SB | Channel 2 NCR output (NCR1)     |

| LSB | Channel 1 NCR output (NCR0)     |

The BUSYB output is "L" level when a command is being processed or the playback of a particular channel is going on. In other states, the BUSYB output is "H" level. The NCR output is "L" level when a command is being processed or particular channel is in standby for playback. In other states, the NCR output is "H" level.

#### **I2C Command Interface (Applies to ML2286X)**

The I2C Interface built-in is an serial interface (: slave side) that is compliant with I2C bus specification. It supports Fast mode and enables data transmission/reception at 400 kbps. The SCL and SDA pins are used to input the command data or to read the status. Pins (:SAD0, 1 and 2) are used to set the slave address. Pull-up resister should be connected to SCL pin and SDA pin.

For the master on the I2C bus to communicate with this device (: slave), input the slave address with the first seven bits after setting the start condition. The upper three bits of the slave address can be set using the SAD0 to 2 pins. The eighth bit of slave address is used to set the direction (: write or read) of communication. If the eighth bit is "0" level, it is write mode from master to slave. And, if the eighth bit is "1" level, it is read mode from master.

The communication is made in the unit of byte. And acknowledge is needed for each byte.

The protocol of I2C communication is shown below.

Command flow at data write( 1byte command )

START condition

Slave address +W (0)

Write address (ex. 1st byte of a command)

STOP condition

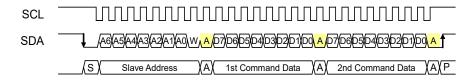

• Data write timing( 1byte command )

- Command flow at data write( 2byte command )

START condition

Slave address +W (0)

Write address (ex. 1st byte of a command)

Write data (ex. 2nd byte of a command)

STOP condition

- Data write timing(2byte command)

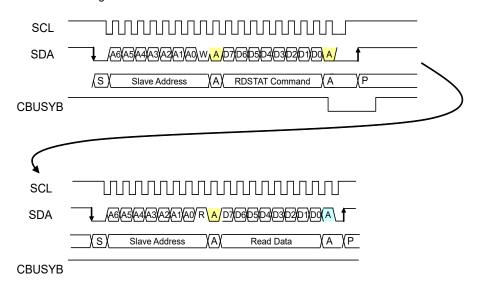

#### Command flow at data read

Start condition Slave address +W(0) Write address (RDSTAT command) STOP condition

Start condition Slave address +R(1) Read data (ex. Status read) STOP condition

#### • Data read timing

Setting of the slave address using the SAD0 to 2 pins

| SAD2 | SAD1 | SAD0 | Lower 4 bits |

|------|------|------|--------------|

| 0    | 0    | 0    | 0101         |

| 0    | 0    | 1    | 0101         |

| 0    | 1    | 0    | 0101         |

| 0    | 1    | 1    | 0101         |

| 1    | 0    | 0    | 0101         |

| 1    | 0    | 1    | 0101         |

| 1    | 1    | 0    | 0101         |

| 1    | 1    | 1    | 0101         |

The following table shows the contents of each data output at a status read. Status is updated by the RDSTAT command; therefore, be sure to input the RDSTAT command in order to read status.

|     | Output status signal            |

|-----|---------------------------------|

| MSB |                                 |

| 7SB |                                 |

| 6SB | Channel 2 BUSYB output (BUSYB1) |

| 5SB | Channel 1 BUSYB output (BUSYB0) |

| 4SB |                                 |

| 3SB |                                 |

| 2SB | Channel 2 NCR output (NCR1)     |

| LSB | Channel 1 NCR output (NCR0)     |

The BUSYB signal is "L" level when either a command is being processed or the playback of a particular channel is going on. In other states, the BUSYB signal is "H" level.

The NCR signal is "L" level when either a command is being processed or a particular channel is in standby for playback. In other states, the NCR signal is "H" level.

## **Command List**

Each command is configured by the unit of byte (8-bit). The following commands, AMODE, AVOL FADR, PLAY, MUON, and CVOL, use two bytes.

| Command | D7      | D6   | D5   | D4   | D3   | D2   | D1                             | D0  | Description                                                                                                                                                                                                                  |

|---------|---------|------|------|------|------|------|--------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command | וט      | _ D0 | D0   | DŦ   |      | DZ   | Di                             | DO  | Power-up command.                                                                                                                                                                                                            |

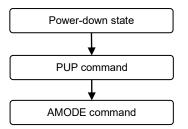

| PUP     | 0       | 0    | 0    | 0    | 0    | 0    | S1                             | S0  | Shifts from the power down state to the command waiting state. Also, sets the number of memory banks.                                                                                                                        |

| PDWN    | 0       | 0    | 1    | 0    | 0    | 0    | 0                              | 0   | Power-down command. Shifts form the command waiting state to the power down state.                                                                                                                                           |

| RDSTAT  | 1       | 0    | 1    | 1    | 0    | 0    | 0                              | 0   | Status read command. Reads the command status on each channel.                                                                                                                                                               |

| 444005  | 0       | 0    | 0    | 0    | 0    | 1    | 0                              | 0   | Control command of analog circuitry.                                                                                                                                                                                         |

| AMODE   | FAD     | DAG1 | DAG0 | AIG1 | AIG0 | DAEN | SPEN                           | POP | Setoperation of power-up/dpwn and input/output.                                                                                                                                                                              |

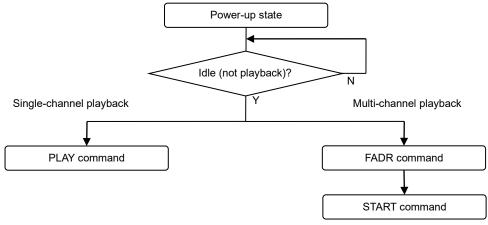

| PLAY    | 0       | 1    | 0    | 0    | F9   | F8   | 0                              | СН  | Playback start command. Use the data of the 2nd byte to                                                                                                                                                                      |

|         | F7      | F6   | F5   | F4   | F3   | F2   | F1                             | F0  | specify a phrase number. Can be specified for each channel.                                                                                                                                                                  |

| STOP    | 0       | 1    | 1    | 0    | 0    | 0    | CH1                            | CH0 | Playback stop command. Can be set for each channel.                                                                                                                                                                          |

|         | 0       | 0    | 1    | 1    | F9   | F8   | 0                              | СН  | Set command of playback phrase.                                                                                                                                                                                              |

| FADR    | F7      | F6   | F5   | F4   | F3   | F2   | F1                             | F0  | Can be set for each channel. Use START command to start.                                                                                                                                                                     |

| START   | 0       | 1    | 0    | 1    | 0    | 0    | CH1                            | СНО | Playback start command without phrase spec. Use FADR command to set phrase.Can start playback on multiple channels simultaneously.  After played back by PLAY command, the same phrase can be played back with this command. |

| MUON    | 0       | 1    | 1    | 1    | 0    | 0    | CH1                            | CH0 | Silence insertion command. Set the silent time length for each                                                                                                                                                               |

| MOON    | M7      | M6   | M5   | M4   | МЗ   | M2   | M1                             | M0  | channel using M7 to M0 bits in the 2nd byte.                                                                                                                                                                                 |

| SLOOP   | 1       | 0    | 0    | 0    | 0    | 0    | CH1                            | CH0 | Set command of repeat playback. Setting is enabled during playback. Can be specified for each channel.                                                                                                                       |

| CLOOP   | 1       | 0    | 0    | 1    | 0    | 0    | CH1                            | CH0 | Stop command of repeat playback. Can be specified for each channel. Also, repeat playback is released by STOP command automatically.                                                                                         |

| CVOL    | 1       | 0    | 1    | 0    | 0    | 0    | CH1                            | CH0 | Volume control command. Set volume for each channel using                                                                                                                                                                    |

| CVOL    | 0       | 0    | 0    | CV4  | CV3  | CV2  | CV1                            | CV0 | CV4 to CV0 bits in the 2nd byte.                                                                                                                                                                                             |

| A) (O)  | 0 0 0 0 | 0    | 1    | 0    | 0    | 0    | Analog volume control command. |     |                                                                                                                                                                                                                              |

| AVOL    | 0       | 0    | AV5  | AV4  | AV3  | AV2  | AV1                            | AV0 | Set volume after channel mixing using AV5 to AV0 bits.                                                                                                                                                                       |

## **Voice Synthesis Algorithm**

Four types of voice synthesis algorithm are supported. They are 4-bit ADPCM2, 8-bit non-linear PCM, 8-bit straight PCM and 16-bit straight PCM. Select the best one according to the characteristics of playback voice.

The following table shows key features of each algorithm.

| Voice synthesis algorithm | Applied waveform                                               | Feature                                                                                                             |

|---------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| 4-bit ADPCM2              | Normal voice waveform                                          | Up version of LAPIS Semiconductor's specific voice synthesis algorithm (: 4-bit ADPCM).  Voice quality is improved. |

| 8-bit Nonlinear PCM       | Waveform including high frequency signals (sound effect, etc.) | Algorithm, which plays back mid-range of waveform as 10-bit equivalent voice quality.                               |

| 8-bit straight PCM        |                                                                | Normal 8-bit PCM algorithm                                                                                          |

| 16-bit straight PCM       | (Sound effect, etc.)                                           | Normal 16-bit PCM algorithm                                                                                         |

#### **Memory Allocation and Creating Voice Data**

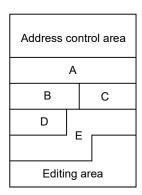

The ROM is partitioned into four data areas: voice (i.e., phrase) control area, test area, voice area, and edit ROM area.

The voice control area manages the voice data in the ROM. It contains data for controlling the start/stop addresses of voice data for 1,024 phrases, use/non-use of the edit ROM function and so on.

The test area contains data for testing.

The voice area contains actual waveform data.

The edit ROM area contains data for effective use of voice data. For the details, refer to the section of "Edit ROM Function."

The edit ROM area is not available if the edit ROM is not used.

The ROM data is created using a dedicated tool.

#### Configuration of ROM data

| 0x00000       | Voice control area<br>(Fixed 64 Kbits)               |

|---------------|------------------------------------------------------|

| 0x01FFF       | , , , , , , , , , , , , , , , , , , ,                |

| 0x02000       | Test area                                            |

| 0x0205F       | 1001 4104                                            |

| 0x02060       | Voice area                                           |

| max: 0x1FFFFF |                                                      |

| max: 0x1FFFFF | Edit ROM area<br>Depends on creation<br>of ROM data. |

#### **Playback Time and Memory Capacity**

The playback time depends on the memory capacity, sampling frequency, and playback method.

The equation to know the playback time is shown below. But this is not applied if the edit ROM function is used.

Playback time [sec] =

$$\frac{1.024 \times (Memory capacity - 64.75 \text{ [Kbits]})}{Sampling frequency \text{ [kHz]} \times Bit \text{ length}}$$

(Bit length is 4 at the 4-bit ADPCM2 and 8/16 at the PCM.)

Example) In the case that the sampling frequency is 16 kHz, algorithm is 4-bit ADPCM2 and ROM capacity is 16 Mbits, the playback time is approx. 261 seconds, as shown below.

Playback time =

$$\frac{1.024 \times (16834 - 64.75) \text{ [Kbits]}}{16 \text{ [kHz]} \times 4 \text{ [bits]}} \cong 261 \text{ [sec]}$$

#### **Edit ROM Function**

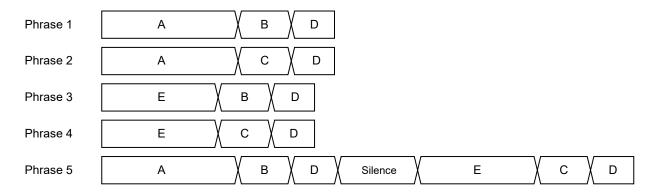

The edit ROM function makes it possible to play back multiple phrases in succession. The following functions are set using the edit ROM function:

• Continuous playback: There is no limit to set the number of times of continuous playback. It

depends on the memory capacity only.

• Silence insertion function: 20ms to 1,024 ms (4ms/step)

It is possible to use voice ROM effectively to use the edit ROM function. Below is an example of the ROM structure, case of using the edit ROM function.

Example 1) Phrases using the Edit ROM Function

Example 2) Structure of the ROM that contents of Example 1 are stored

#### **Mixing Function**

It is possible to perform mixing of two channels simultaneously. And also, it is possible to specify PLAY, STOP, and CVOL commands for each channel respectively. The mixing function is available if the sampling frequency  $(F_S)$  is 32 kHz or less.

#### - Precautions for Waveform Clamp

Adjust the volume of each channel using the CVOL command, if the waveform clamp is increased by channel mixing.

#### **Memory Bank Switching Function**

The memory bank switching function enables the built-in ROM area that is divivided into up to four banks to be used. When four banks are used, the maximum number of phrases per bank is 1,024 so that up to 4096 phrases can be played back.

Using this function, multiple ROM codes can be grouped into one code.

The settings of SEL1 pin and SEL0 pin determines which memory bank is used. To playback phrases, the number of memory banks must be specified in PUP.

When using a memory bank switching function, data must be divided and saved in the specified areas at ROM data creation.

- When the number of memory banks is 1

| SEL1 | SEL0 | ML22825<br>ML22865 | ML22824<br>ML22864 | ML22823<br>ML22863 |  |

|------|------|--------------------|--------------------|--------------------|--|

| 0    | 0    | 00000h – 1FFFFFh   | 00000h – FFFFFh    | 00000h -7FFFFh     |  |

- When the number of memory banks is 2

| SEL1 | SEL0 | ML22825<br>ML22865 | ML22824<br>ML22864 | ML22823<br>ML22863 |  |  |

|------|------|--------------------|--------------------|--------------------|--|--|

| 0    | 0    | 00000h – FFFFFh    | 00000h – 7FFFFh    | 00000h – 3FFFFh    |  |  |

| 0    | 1    | 100000h – 1FFFFFh  | 80000h – FFFFFh    | 40000h – 7FFFFh    |  |  |

- When the number of memory banks is 4

|      | ······································ |                    |                    |                    |  |  |  |  |

|------|----------------------------------------|--------------------|--------------------|--------------------|--|--|--|--|

| SEL1 | SEL0                                   | ML22825<br>ML22865 | ML22824<br>ML22864 | ML22823<br>ML22863 |  |  |  |  |

| 0    | 0                                      | 00000h – 7FFFFh    | 00000h – 3FFFFh    | 00000h – 1FFFFh    |  |  |  |  |

| 0    | 1                                      | 80000h – FFFFFh    | 40000h – 7FFFFh    | 20000h – 3FFFFh    |  |  |  |  |

| 1    | 0                                      | 100000h – 17FFFFh  | 80000h – BFFFFh    | 40000h – 5FFFFh    |  |  |  |  |

| 1    | 1                                      | 180000h – 1FFFFFh  | C0000h – FFFFFh    | 60000h – 7FFFFh    |  |  |  |  |

The memory (16 Mbits) in the ML22825 is divided as shown below.

| 0-7FFFFh       | Bank 1<br>Capacity: 16 Mbits<br>Max. Phrase count: 1024 | Bank 1<br>Capacity: 8 Mbits<br>Max. Phrase count: 1024 | Bank 1<br>Capacity: 4 Mbits<br>Max. Phrase count: 1024 |