January 9, 2024

# **ML5236**

Analog Front-End IC for 14-Serial-Cell Lithium-Ion Rechargeable Battery Protection

#### ■ General Description

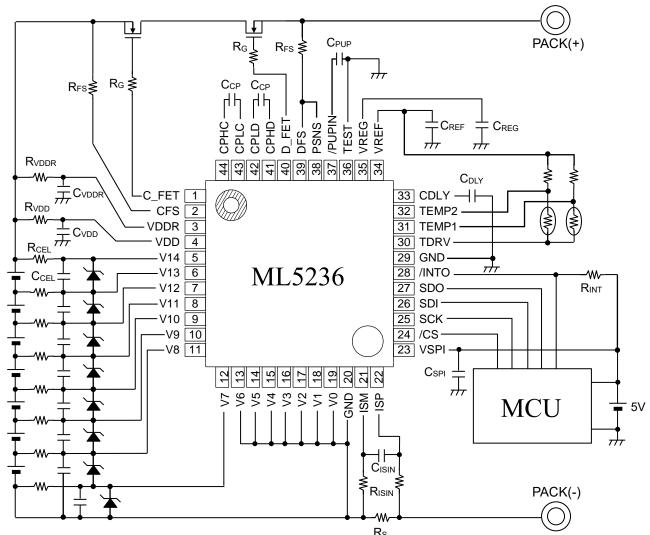

The ML5236 is an analog front-end IC intended for 14-cell Li-ion rechargeable battery protection systems. With integrated individual cell voltage monitor and charge/discharge current monitor functions, it protects cell overvoltage, cell undervoltage, and pack over-current working with an external microcontroller (MCU). Also, it is equipped with the short-circuit protection function, which autonomously turns off the external charge/discharge Nch-FETs on the high-side power rail without the external MCU.

#### Features

5- to 14-cell high-precision cell voltage measurement function Built-in 12-bit successive approximation type ADC Cell voltage measurement precision: ±10mV (typ) at cell voltage 4V

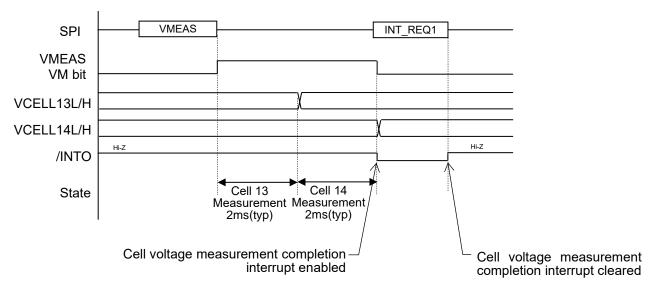

Cell voltage measurement time: 2ms per cell (typ)

• Charge/discharge current measurement function

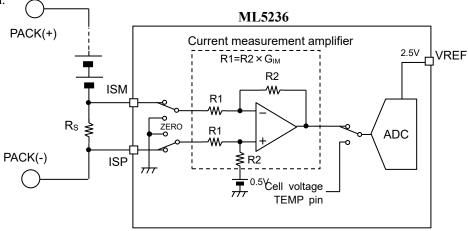

The potential differential between the ISP and ISM pins amplified by 12- or 60-fold, then digitized with the 12-bit ADC.

(A single ADC module is shared in cell voltage measurement and pack current measurement.)

• Short-circuit protection function

Variable detection threshold between ISP and ISM pins: 50mV/100mV/150mV/200mV (typ) Detection delay time adjustable using an external capacitor

- Built-in cell balancing switch on each cell: Switch ON resistance  $6\Omega$  (typ)

- External charge/discharge FET control: Built-in gate driver for highside Nch-FET

- Temperature sensor measurement function: Two thermistor inputs

- Overvoltage protection function: Overvoltage protection tripped by comparing each A/D converted cell voltage value with the detection threshold defined in the control register

- MCU interface: SPI serial interface (mode 0)

Dedicated power supply pin VSPI allows 5V interface

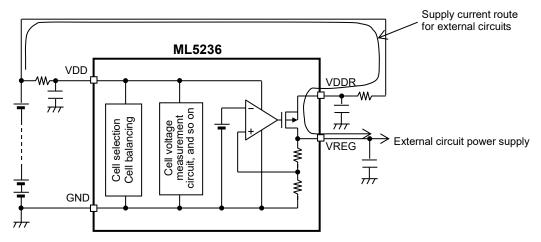

• Built-in 3.3V regulator for an external MCU: 10mA (max) output current Current boost circuitry configurable with an external Pch-FET

• Low current consumption

$\begin{array}{ll} \mbox{Normal operation} & : 330 \mu \mbox{A(typ)}, 700 \mu \mbox{A (max)} \\ \mbox{Power-save} & : 120 \mu \mbox{A(typ)}, 200 \mu \mbox{A (max)} \\ \mbox{Power-down} & : 0.1 \mu \mbox{A(typ)}, 1 \mu \mbox{A(max)} \end{array}$

Power supply voltage : +8V to +64V

Operating temperature range : -40°C to +85°C

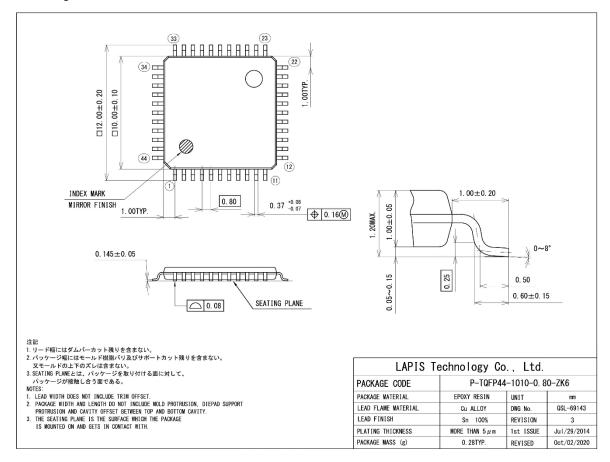

Package : 44-Pin TQFP

#### Application

- Power tools and Garden tools

- •E-Bike and Electric assisted bicycle

- •Uninterruptible Power Supplies (UPS)

- Energy Storage Systems (ESS)

#### Part number

ML5236TB

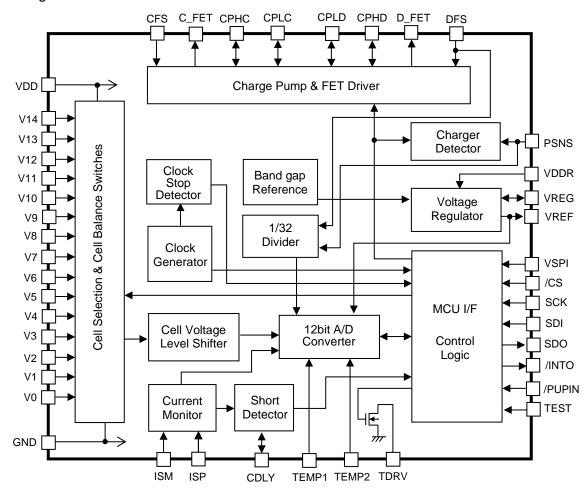

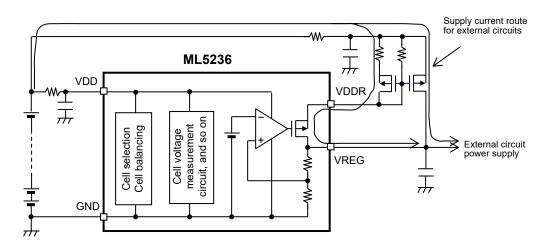

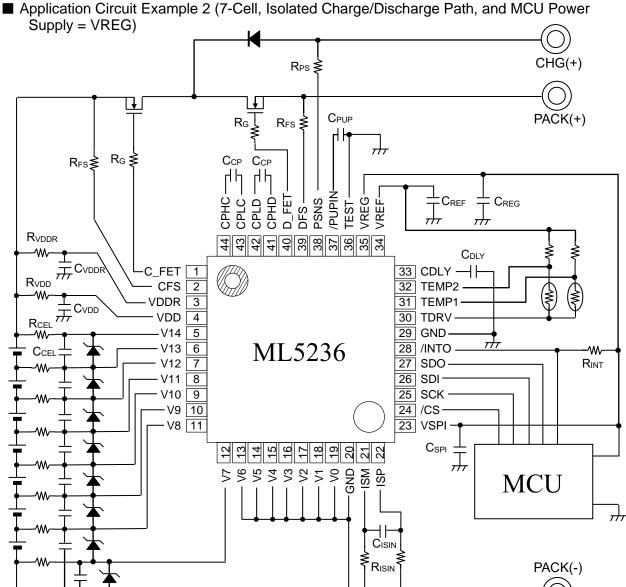

### ■ Block Diagram

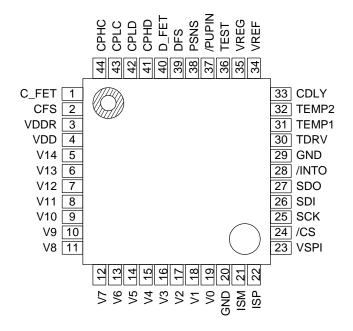

## ■ Pin Configuration (Top View)

# LAPIS Technology Co.,Ltd.

| ■ Pin Desc | cription | •   |                                                                                                                                                                                    |

|------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.    | Pin name | I/O | Description                                                                                                                                                                        |

| 1          | C_FET    | 0   | Charge FET gate drive. Connected to the gate pin of the external Nch-FET. In the ON state, the CFS level +12V (typ) is asserted, while the CFS level is asserted in the OFF state. |

| 2          | CFS      | ı   | Reference voltage input for the C_FET drive charge pump. Connected to the source pin of the charge FET.                                                                            |

| 3          | VDDR     | _   | Power supply for the internal regulator. Configure an external CR noise filter circuit.                                                                                            |

| 4          | VDD      | _   | Power supply.  Configure an external CR noise filter circuit.                                                                                                                      |

| 5          | V14      | I   | Cell 14 positive input.                                                                                                                                                            |

| 6          | V13      | I   | Cell 14 negative input and Cell 13 positive input.                                                                                                                                 |

| 7          | V12      | I   | Cell 13 negative input and Cell 12 positive input.                                                                                                                                 |

| 8          | V11      | I   | Cell 12 negative input and Cell 11 positive input.                                                                                                                                 |

| 9          | V10      | I   | Cell 11 negative input and Cell 10 positive input.                                                                                                                                 |

| 10         | V9       | I   | Cell 10 negative input and Cell 9 positive input.                                                                                                                                  |

| 11         | V8       | I   | Cell 9 negative input and Cell 8 positive input. For the 5-cell applications, connected to GND.                                                                                    |

| 12         | V7       | ı   | Cell 8 negative input and Cell 7 positive input. For the 5- to 6-cell application, connected to GND.                                                                               |

| 13         | V6       | I   | Cell 7 negative input and Cell 6 positive input.  For the 5- to 7-cell applications, connected to GND.                                                                             |

| 14         | V5       | I   | Cell 6 negative input and Cell 5 positive input. For the 5- to 8-cell applications, connected to GND.                                                                              |

| 15         | V4       | I   | Cell 5 negative input and Cell 4 positive input. For the 5- to 9-cell applications, connected to GND.                                                                              |

| 16         | V3       | I   | Cell 4 negative input and Cell 3 positive input.  For the 5- to 10-cell applications, connected to GND.                                                                            |

| 17         | V2       | I   | Cell 3 negative input and Cell 2 positive input.  For the 5- to 11-cell applications, connected to GND.                                                                            |

| 18         | V1       | I   | Cell 2 negative input and Cell 1 positive input.  For the 5- to 12-cell applications, connected to GND.                                                                            |

| 19         | V0       | I   | Cell 1 negative input.  For the 5- to 13-cell applications, connected to GND.                                                                                                      |

| 20         | GND      | _   | Ground pin.                                                                                                                                                                        |

| 21         | ISM      | I   | Current sense negative input. Connected to the negative terminal of the most negative battery cell.                                                                                |

| 22         | ISP      | I   | Current sense positive input. The ISP pin level should be higher than the ISM pin level in discharge state.                                                                        |

| 23         | VSPI     | _   | Serial MCU interface power supply. Tied to the external MCU power supply.                                                                                                          |

| 24         | /CS      | ı   | Serial MCU interface chip select input. Serial MCU interface is enabled with L-level input.                                                                                        |

# LAPIS Technology Co.,Ltd.

| Pin No. | Pin name | I/O | Description                                                                                                                                                                                       |

|---------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | SCK      | 1   | Serial MCU interface clock input. SDI input is captured at the rising edge of the SCK clock, while SDO output should be read at the falling edge of the SCK.                                      |

| 26      | SDI      | I   | Serial MCU interface data input.                                                                                                                                                                  |

| 27      | SDO      | 0   | Serial MCU interface data output. If /CS input is "H" level, SDO is fixed to Hi-Z state.                                                                                                          |

| 28      | /INTO    | 0   | Interrupt signal output to an external MCU, NMOS open drain. Should be pulled up externally so that "L" level is asserted when an interrupt occurs.                                               |

| 29      | GND      | _   | Ground.                                                                                                                                                                                           |

| 30      | TDRV     | 0   | Ground for thermistors. 0V is asserted during temperature measurement, or fixed to the Hi-Z state otherwise.                                                                                      |

| 31      | TEMP1    | ı   | Thermistor inputs. Connected to TDRV through an NTC thermistor, and                                                                                                                               |

| 32      | TEMP2    | I   | also pulled up to VREF via a resistor.                                                                                                                                                            |

| 33      | CDLY     | Ю   | Short circuit detection delay time configuration pin. Connected to GND through a capacitor.                                                                                                       |

| 34      | VREF     | 0   | 2.5V reference level output for the internal ADC. Connected to GND through a $4.7\mu F$ capacitor.                                                                                                |

| 35      | VREG     | 0   | Built-in 3.3V regulator output. Connected to GND through a 4.7μF capacitor. Can power the external MCU.                                                                                           |

| 36      | TEST     | I   | Device test enable input. Should be fixed to GND.                                                                                                                                                 |

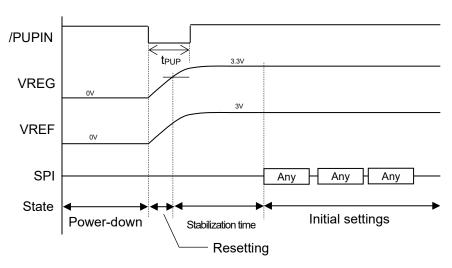

| 37      | /PUPIN   | I   | Power-up trigger input. The device wakes up with the "L" level input. Internally pulled up to VDD through a $1M\Omega$ resistor.                                                                  |

| 38      | PSNS     | ı   | Charger presence detection input at power-down. The device is powered-up when the PSNS level becomes 1/2VDD or higher during power-down. The ADC can measure 1/32-fold voltage of the PSNS level. |

| 39      | DFS      | I   | Reference voltage input for the D_FET drive charge pump. Connected to the source pin of the discharge FET. The ADC can measure 1/32-fold voltage of the DFS level.                                |

| 40      | D_FET    | 0   | Discharge FET gate drive. Connected to the gate pin of the external Nch-FET. In the ON state, the DFS level +12V (typ) is asserted, while the DFS level is asserted in the OFF state.             |

| 41      | CPHD     | 0   | Charge pump capacitor input for D_FET drive. Connect a capacitor with                                                                                                                             |

| 42      | CPLD     | 0   | approximately twice the gate capacitance of the discharge FET between the CPHD and CPLD pins.                                                                                                     |

| 43      | CPLC     | 0   | Charge pump capacitor input for C_FET drive. Connect a capacitor with                                                                                                                             |

| 44      | CPHC     | 0   | approximately twice the gate capacitance of the charge FET between the CPHC and CPLC pins.                                                                                                        |

## ■ Absolute Maximum Ratings

| GND=0V.  | Ta-25°C |

|----------|---------|

| いいコンニいひこ | 14=70 ( |

| Parameter                    | Symbol            | Condition                                                                     | Rating                         | Unit |

|------------------------------|-------------------|-------------------------------------------------------------------------------|--------------------------------|------|

| Power supply voltage         | $V_{DD}$          | Applied to VDD and VDDR pins                                                  | -0.3 to +86.5                  | V    |

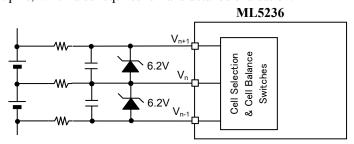

|                              | V <sub>IN1</sub>  | Applied to V14 to V0 pins Voltage difference between Vn+1 and Vn pins (note)  | -0.3 to +6.5                   | V    |

|                              | V <sub>IN2</sub>  | Applied to CFS, DFS, and PSNS pins                                            | -0.3 to +86.5                  | V    |

| Input voltage                | V <sub>IN3</sub>  | Applied to /PUPIN pin                                                         | -0.3 to V <sub>DD</sub> +0.3   | V    |

|                              | V <sub>IN4</sub>  | Applied to TEMP1, TEMP2, ISM, and ISP pins                                    | -0.3 to V <sub>REG</sub> +0.3  | V    |

|                              | V <sub>IN5</sub>  | Applied to /CS, SCK, and SDI pins                                             | -0.3 to V <sub>SPI</sub> +0.3  | V    |

|                              | V <sub>OUT1</sub> | Applied to D_FET pin VDFS=DFS pin voltage                                     | V <sub>DFS</sub> -0.3 to +86.5 | V    |

| Output voltage               | V <sub>OUT2</sub> | Applied to C_FET pin VcFs=CFS pin voltage                                     | V <sub>CFS</sub> -0.3 to +86.5 | V    |

|                              | V <sub>ОUТ3</sub> | Applied to /INTO ,TDRV and CDLY pins                                          | -0.3 to +6.5                   | V    |

|                              | V <sub>OUT4</sub> | Applied to SDO pin                                                            | -0.3 to V <sub>SPI</sub> +0.3  | V    |

| Short circuit output current | los               | VDD=50V, Applied to VREG, VREF, SDO, /INTO, TDRV, CDLY, C_FET, and D_FET pins | 20                             | mA   |

| Cell balancing current       | Ісв               | Per cell balancing switch                                                     | 100                            | mA   |

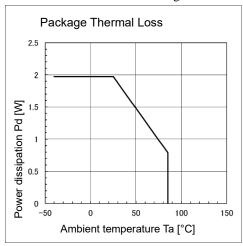

| Power dissipation            | PD                | Ta=25°C                                                                       | 1.9                            | W    |

| Junction temperature         | Tj <sub>MAX</sub> | _                                                                             | 125                            | °C   |

| Package thermal resistance   | θја               | JEDEC double-side board mounted                                               | 50.7                           | °C/W |

| Storage temperature          | T <sub>STG</sub>  | _                                                                             | -55 to +150                    | °C   |

Note: When connecting and disconnecting battery cells, voltage exceeding the absolute maximum rating may be applied between the adjacent Vn+1 and Vn inputs, resulting in permanent damage on the LSI. Make a full and detailed evaluation before usage.

Package thermal loss tolerance decreases with increased ambient temperature Ta as in the left diagram. Make sure that the thermal loss tolerance is not exceeded especially when the output current on the VREG pin is high.

## ■ Recommended Operating Conditions

(GND= 0 V)

|                       |                  |                              | ( )        | JIND UV |

|-----------------------|------------------|------------------------------|------------|---------|

| Parameter             | Symbol           | Condition                    | Range      | Unit    |

| Power supply voltage  | $V_{DD}$         | Applied to VDD and VDDR pins | 8 to 64    | V       |

|                       | V <sub>SPI</sub> | Applied to VSPI pin          | 2.7 to 5.5 | V       |

| Operating temperature | Та               | No VREG output load          | -40 to +85 | °C      |

## ■ Electrical Characteristics

## DC Characteristics

|                                                           | o 64V, V <sub>SPI</sub> | = 2.7  to  5.5V,  GND  = 0                                                                                          |                       |                    |                     |      |

|-----------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|---------------------|------|

| Parameter                                                 | Symbol                  | Condition                                                                                                           | Min.                  | Тур.               | Max.                | Unit |

| Digital "H" input voltage (*1)                            | ViH                     | _                                                                                                                   | 0.8×Vspi              | _                  | V <sub>SPI</sub>    | V    |

| Digital "L" input voltage (*1)                            | VIL                     | _                                                                                                                   | 0                     | _                  | 0.2×Vspi            | V    |

| /PUPIN pin "H" input voltage                              | VIHP                    | _                                                                                                                   | 0.8×V <sub>DD</sub>   | _                  | $V_{DD}$            | V    |

| /PUPIN pin "L" input voltage                              | V <sub>ILP</sub>        | _                                                                                                                   | 0                     | _                  | 0.2×V <sub>DD</sub> | V    |

| Digital "H" input<br>current (*1)                         | Іін                     | VIH = VSPI                                                                                                          | _                     |                    | 2                   | μΑ   |

| Digital "L" input<br>current (*1)                         | Iı∟                     | V <sub>IL</sub> = GND                                                                                               | -2                    | _                  | _                   | μΑ   |

| /PUPIN pin "H" input current                              | Іінр                    | V <sub>IH</sub> = V <sub>DD</sub>                                                                                   | _                     | _                  | 2                   | μΑ   |

| /PUPIN pin "L" input current                              | I <sub>ILP</sub>        | V <sub>DD</sub> =64V, V <sub>IL</sub> = GND                                                                         | -128                  | -64                | -32                 | μΑ   |

| Digital "H" output voltage (*2)                           | Vон                     | Іон=-100μΑ                                                                                                          | V <sub>SPI</sub> -0.2 | _                  | Vspi                | V    |

| Digital "L" output<br>voltage (*3)                        | Vol                     | I <sub>OL</sub> =1mA                                                                                                | 0                     | _                  | 0.2                 | V    |

| Digital output leakage current (*3)                       | I <sub>OLK</sub>        | V <sub>OH</sub> = V <sub>SPI</sub><br>V <sub>OL</sub> =0V                                                           | -2                    | _                  | 2                   | μΑ   |

| Cell voltage monitor pin Input current (*4)               | I <sub>INVC</sub>       | Cell voltage being<br>measured                                                                                      | -5                    | _                  | 15                  | μΑ   |

| Cell voltage monitor<br>pin Input leakage<br>current (*4) | lilvc                   | Cell voltage not being measured                                                                                     | -5                    | _                  | 5                   | μΑ   |

| FET "H" output<br>voltage (*5)                            | Vohf                    | I <sub>OH</sub> =-1µA<br>V <sub>DD</sub> =V <sub>S</sub> =18V to 64V<br>V <sub>S</sub> : CFS and DFS pin<br>voltage | Vs+8                  | V <sub>S</sub> +12 | Vs+16               | V    |

| FET "L" output<br>voltage (*5)                            | Volf                    | $I_{OL} = 1\mu A$ $V_{DD} = V_{S} = 18V$ to 64V $V_{S}$ : CFS and DFS pin voltage                                   | Vs                    | _                  | Vs+0.3              | V    |

| VPFC output voltage                                       | $V_{REG1}$              | V <sub>DD</sub> =10V to 64V<br>Output load current <<br>10mA                                                        | 3.0                   | 3.3                | 3.6                 | V    |

| VREG output voltage                                       | V <sub>REG2</sub>       | V <sub>DD</sub> =8V to 10V<br>Output load current <<br>5mA                                                          | 3.0                   | 3.3                | 3.6                 | V    |

| \/PEE output voltage                                      | $V_{REF1}$              | Ta=0 to 60°C<br>Output load current <<br>1mA                                                                        | 2.48                  | 2.50               | 2.54                | V    |

| VREF output voltage                                       | V <sub>REF2</sub>       | Ta=-40 to 85°C<br>Output load current <<br>1mA                                                                      | 2.45                  | 2.50               | 2.55                | V    |

| Cell balancing switch ON resistance                       | R <sub>BL</sub>         | Internal balancing FET  V <sub>DS</sub> =0.6V,  V <sub>DD</sub> =18V to 64V                                         | 3                     | 6                  | 30                  | Ω    |

<sup>(\*1)</sup> Applied to /CS, SCK, and SDI pins. (\*2) Applied to SDO pin. (\*3) Applied to SDO, /INTO, and TDRV pins. (\*4) Applied to V14 to V0 pins. (\*5) Applied to C\_FET and D\_FET pins.

# **Supply Current Characteristics**

consumption

| $V_{DD} = 8 \text{ to } 64V, V_{SPI}$ | = 2.7  to 5.      | 5V, $GND = 0V$ , $Ia = -40$ | 1 to +85°C, | no vkeg a | na vket o | utput load |

|---------------------------------------|-------------------|-----------------------------|-------------|-----------|-----------|------------|

| Parameter                             | Symbol            | Condition                   | Min.        | Тур.      | Max.      | Unit       |

| Cell voltage                          |                   |                             |             |           |           |            |

| measurement state                     | $I_{DD1}$         | No output load              | _           | 330       | 700       | μΑ         |

| current consumption                   |                   |                             |             |           |           |            |

| Power-save state                      | I <sub>DD2</sub>  | No output load              |             | 120       | 200       | μA         |

| current consumption                   | 1002              | 140 output load             |             | 120       | 200       | μΛ         |

| Power-down state                      | lana              | No output load              |             | 0.1       | 1.0       | μA         |

| current consumption                   | I <sub>DDS</sub>  | เพื่อ อินเคนเ เอลน          |             | 0.1       | 1.0       | μΑ         |

| VSPI pin                              |                   | No output load              |             |           |           |            |

| static current                        | I <sub>VSPI</sub> | Without SPI                 | _           | _         | 10        | μA         |

(Note) The above current consumption values are defined by the total current on the VDD and VDDR pins.

communication

## Cell Voltage Measurement Characteristics

| $V_{DD}$ = 8 to 64V, $V_{SPI}$ = 2.7 to 5.5V, GND = 0V, Ta = -40 to +85°C, no VREG output load |                   |                                                   |      |           |      |      |

|------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------|------|-----------|------|------|

| Parameter                                                                                      | Symbol            | Condition                                         | Min. | Тур.      | Max. | Unit |

| Cell voltage measurement range                                                                 | $V_{\text{VMR}}$  | (*1)                                              | 0.1  | -         | 4.5  | V    |

|                                                                                                | V <sub>ER1T</sub> | Cell voltage = 3.8 to<br>4.3V<br>Ta = 25°C        | -15  | l         | 15   | mV   |

| Cell voltage                                                                                   | V <sub>ER2T</sub> | When cell voltage = 1V<br>Ta = 25°C               | -50  |           | 50   | mV   |

| measurement error<br>(*2)                                                                      | $V_{\text{ER1}}$  | Cell voltage = 3.8 to<br>4.3V<br>Ta = 0°C to 60°C | -20  | I         | 20   | mV   |

|                                                                                                | V <sub>ER2</sub>  | When cell voltage = 1V<br>Ta = 0°C to 60°C        | -70  |           | 70   | mV   |

| Cell voltage measurement step                                                                  | V <sub>LSB</sub>  | _                                                 |      | 5000/4095 | _    | mV   |

| Cell voltage                                                                                   | tscan             | 14-cell scan                                      | 22   | 28        | 36   | ms   |

| measurement time                                                                               | tsel              | Individual cell select                            | 1.6  | 2         | 2.6  | ms   |

- (\*1) The power supply voltage VDD should be greater than 8V.

- (\*2) The measurement error within 1.0-to-3.8V cell voltage range is obtained by linear extrapolation.

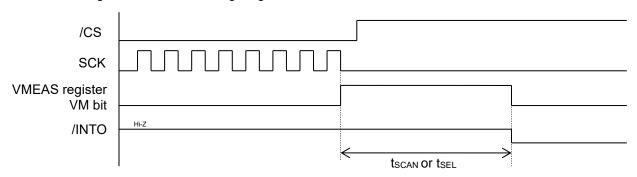

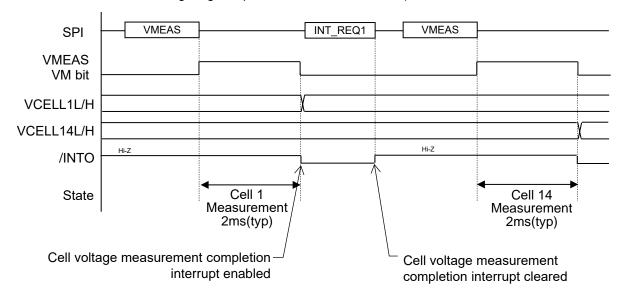

#### Cell voltage measurement timing diagram

#### Current Measurement Characteristics

$V_{DD}$  = 8 to 64V,  $V_{SPI}$  = 2.7 to 5.5V, GND = 0V, Ta = -40 to +85°C, shunt resistor=1m $\Omega$ , no VREG output load

| Parameter                                 | Symbol            | Condition                              | Min. | Tup    | Max.    | Unit     |

|-------------------------------------------|-------------------|----------------------------------------|------|--------|---------|----------|

|                                           | Symbol            |                                        |      | Тур.   |         |          |

| Current measurement                       | I <sub>MR1</sub>  | GIM bit = "0"                          | -150 | _      | 30      | A        |

| range                                     | I <sub>MR2</sub>  | GIM bit = "1"                          | -25  | _      | 5       | Α        |

|                                           | 0                 | GIM bit = "0"                          | 44.4 | 40     | 40.0    | <b>-</b> |

| Current measurement                       | G <sub>IM0</sub>  | Ta = 0°C to 60°C                       | 11.4 | 12     | 12.6    | Factor   |

| amplifier gain (*1)                       | G <sub>IМ1</sub>  | GIM bit = "1"                          | 57   | 60     | 63      | Factor   |

|                                           | GIM1              | Ta = 0°C to 60°C                       | 37   | 00     | 03      | Factor   |

| Current messurement                       | 1/                | GIM bit = "0"                          | 2B84 | 2222   | 2 N E 1 | Hex      |

| Current measurement  A/D conversion value | $V_{ZIM1}$        | Ta = 0°C to 60°C                       | 2D04 | 3333   | 3AE1    | нех      |

| at zero current                           | 1/                | GIM bit = "1"                          | 2055 | 3333   | 3D70    | Hex      |

| at zero current                           | $V_{ZIM2}$        | Ta = 0°C to 60°C                       | 28F5 |        |         |          |

|                                           | I <sub>ER1</sub>  | GIM bit = "0"                          | -2.5 |        | 2.5     | А        |

|                                           |                   | Ta = 0°C to $60$ °C                    |      | _      |         |          |

| Current measurement                       |                   | -50A measurement                       |      |        |         |          |

| error (*2)                                |                   | GIM bit = "1"                          |      |        |         |          |

|                                           | $I_{ER2}$         | Ta = 0°C to 60°C                       | -0.5 |        | 0.5     | Α        |

|                                           |                   | -10A measurement                       |      |        |         |          |

| Current measurement                       | I <sub>LSB1</sub> | GIM bit = "0"                          | _    | 3.1790 | _       | mA       |

| step                                      | I <sub>LSB2</sub> | GIM bit = "1"                          | _    | 0.6358 | _       | mA       |

| Current measurement                       |                   | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |      |        |         |          |

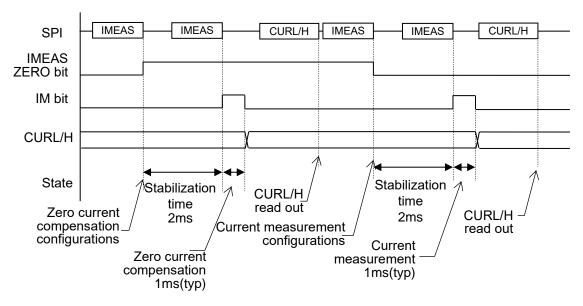

| setup                                     | tsтв              | When changing GIM                      |      | _      | 2       | ms       |

| stabilization time                        |                   | and ZERO bits                          |      |        |         |          |

| Current measurement                       | 4                 |                                        | 0.0  | 4.0    | 4.0     |          |

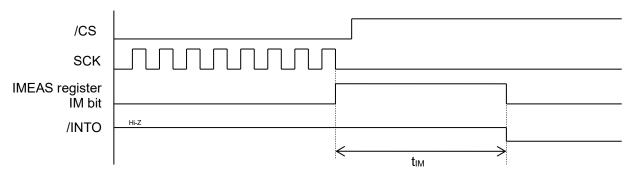

| time (*3)                                 | tıм               | _                                      | 0.8  | 1.0    | 1.3     | ms       |

- (\*1) The both ends of the shunt resistor should be tied to the ISP and ISM pins via a  $1k\Omega$  resistor respectively .

- (\*2) Assuming a  $1m\Omega$  shunt resistor without resistance error, the A/D conversion value at zero current flow is compensated. The given values include errors in the amplification gain factor of 12- or 60-fold. (\*3) Stabilization time for current measurement amplifier gain switching is not included.

#### Current measurement timing diagram

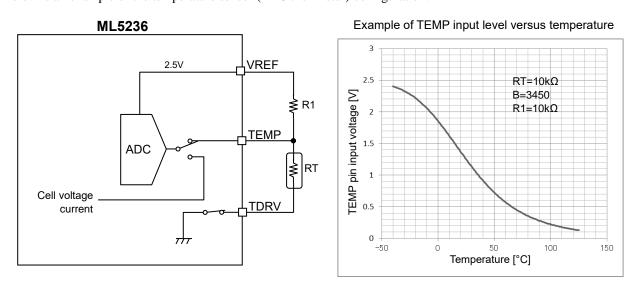

# Temperature Sensor Measurement Characteristics Vop. = 8 to 64V, Vop. = 2.7 to 5.5V, GND = 0

| $V_{DD} = 8$ to 64V, $V_{SPI} = 2.7$ to 5.5V, GND = 0V, Ia = -40 to +85°C, no VREG output load. |                  |                                         |      |           |      |      |

|-------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------|-----------|------|------|

| Parameter                                                                                       | Symbol           | Condition                               | Min. | Тур.      | Max. | Unit |

| TEMP1 and TEMP2 pins input current                                                              | Ітемр            | V <sub>IN</sub> =0V to V <sub>REG</sub> | -2   | _         | 2    | μΑ   |

| TEMP1 and TEMP2 pins input voltage measurement error                                            | V <sub>TER</sub> | TEMP input = 0.3 to 2.3V                | -25  | _         | 25   | mV   |

| Temperature sensor measurement step                                                             | $V_{TLSB}$       | _                                       | _    | 2500/4095 | _    | mV   |

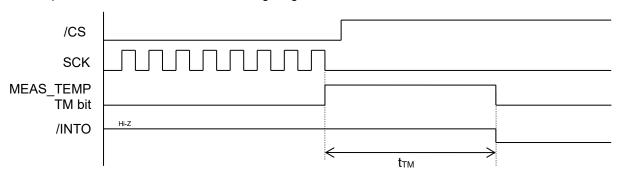

| Temperature sensor                                                                              | tтемр            | _                                       | 0.8  | 1.0       | 1.3  | ms   |

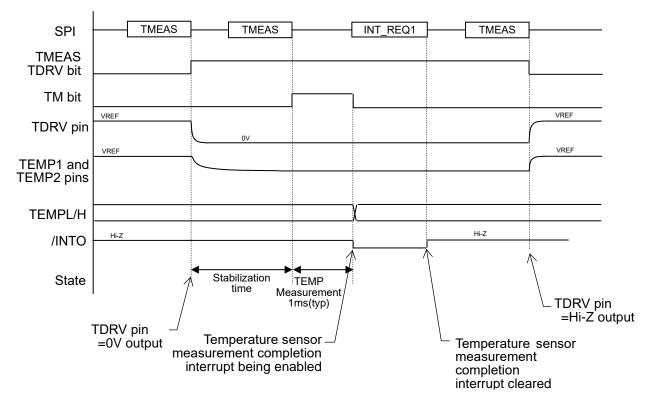

## Temperature sensor measurement timing diagram

# • Short circuit Detection and VREG Threshold Characteristics

| $V_{DD}$ = 8 to 64V, $V_{SPI}$ = 2.7 to 5.5V, GND = 0V, Ta = -40 to +85°C, no VREG output load |                   |                                        |      |      |      |      |

|------------------------------------------------------------------------------------------------|-------------------|----------------------------------------|------|------|------|------|

| Parameter                                                                                      | Symbol            | Condition                              | Min. | Тур. | Max. | Unit |

|                                                                                                | V <sub>S0T</sub>  | SC1 and SC0 bits =<br>(0,0) Ta = 25°C  | 30   | 50   | 70   | mV   |

|                                                                                                | Vs1T              | SC1 and SC0 bits = (0,1), Ta = 25°C    | 75   | 100  | 125  | mV   |

|                                                                                                | V <sub>S2T</sub>  | SC1 and SC0 bits =<br>(1,0), Ta = 25°C | 120  | 150  | 180  | mV   |

| Short circuit detection                                                                        | V <sub>S3T</sub>  | SC1 and SC0 bits =<br>(1,1), Ta = 25°C | 160  | 200  | 240  | mV   |

| threshold                                                                                      | Vso               | SC1 and SC0 bits = (0,0)               | 25   | 50   | 75   | mV   |

|                                                                                                | V <sub>S1</sub>   | SC1 and SC0 bits = (0,1)               | 65   | 100  | 135  | mV   |

|                                                                                                | V <sub>S2</sub>   | SC1 and SC0 bits = (1,0)               | 110  | 150  | 190  | mV   |

|                                                                                                | V <sub>S3</sub>   | SC1 and SC0 bits = (1,1)               | 140  | 200  | 260  | mV   |

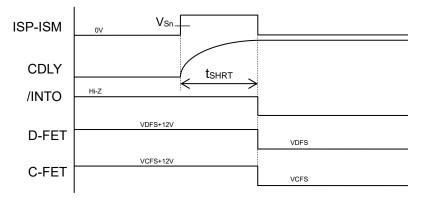

| Short circuit detection delay time                                                             | t <sub>SHRT</sub> | C <sub>DLY</sub> =1nF                  | 50   | 100  | 180  | μs   |

| VREG drop threshold                                                                            | $V_{RD}$          | _                                      | 2.3  | 2.45 | 2.6  | V    |

| VREG recovery threshold                                                                        | $V_{RR}$          | _                                      | 2.5  | 2.75 | 2.9  | V    |

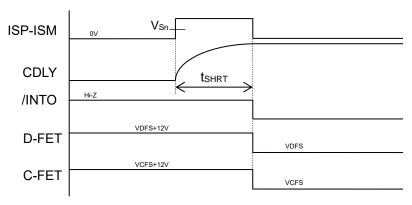

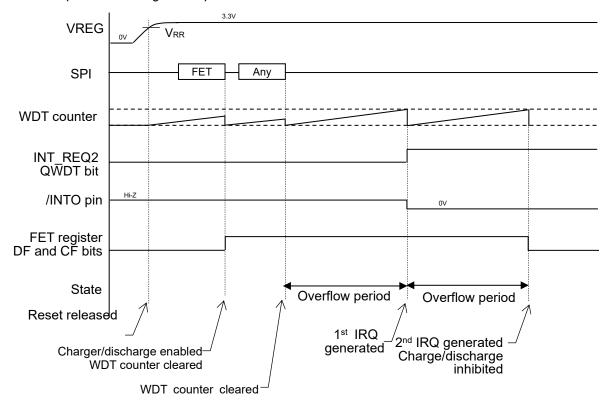

Short current detection timing diagram

## PSNS-and-DFS-Pins Voltage Measurement and Charger Detection Threshold Characteristics

$V_{DD} = 8$  to 64V,  $V_{SPI} = 2.7$  to 5.5V, GND = 0V, Ta = -40 to +85°C, no VREG output load Parameter Condition Min. Symbol Тур. Max Unit PSNS and DFS pins -5 5 ٧ input voltage VERS Input voltage = 64V measurement error PSNS and DFS pins input voltage 19.536  $V_{\text{SLSB}}$  $\mathsf{mV}$ measurement step PSNS and DFS pins input voltage 1.6 2.0 2.6 ms tsm measurement time Charger detection When powered-up from V  $V_{PC}$  $V_{DD}X0.2$  $V_{DD}X0.5$  $V_{DD}X0.8$ the power down state PSNS pin threshold PSNS pull-down PSNS pin voltage is not  $R_{\text{PD}}$ 200 500 1000 ΚΩ resistance being measured DFS pin voltage is not DFS pull-up resistor 0.5 2 4  $\mathsf{M}\Omega$  $R_{\text{PU}}$ being measured Pull-down resistance during voltage Pull-down/pull-up 8 20 50  $M\Omega$  $R_{\text{DM}}$ measurement on resistor released PSNS and DFS pins Pull-down resistor PSNS input leakage released PSNS pin 2 ILPS -2 μΑ current voltage is not being measured Pull-up resistor DFS input leakage released D-FET turned -2 2 μΑ  $I_{LFS}$ current OFF DFS pin voltage is not being measured

## AC Characteristics

V<sub>DD</sub> = 8 to 64V, V<sub>SPI</sub> = 2.7 to 5.5V, GND = 0V, Ta = -40 to +85°C, no VREG output load

Symbol Condition Min. Typ. Max. Unit

| Parameter                 | Symbol           | Condition | Min. | Тур. | Max. | Unit |

|---------------------------|------------------|-----------|------|------|------|------|

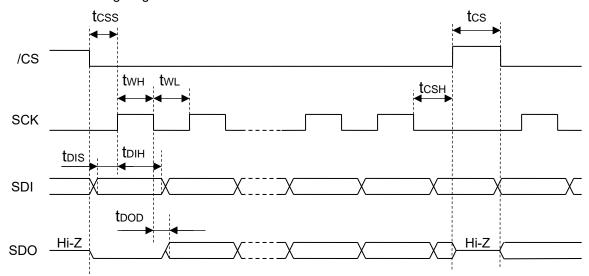

| /CS-SCK setup time        | tcss             | _         | 100  | _    | _    | ns   |

| SCK-/CS hold time         | tсsн             | _         | 100  | _    | _    | ns   |

| SCK "H" pulse width       | t <sub>WH</sub>  | _         | 500  | _    | _    | ns   |

| SCK "L" pulse width       | twL              | _         | 500  | _    | _    | ns   |

| SCK-SDI setup time        | t <sub>DIS</sub> | _         | 50   | _    | _    | ns   |

| SCK-SDI hold time         | t <sub>DIH</sub> | _         | 50   | _    | _    | ns   |

| SCK-SDO output delay time | t <sub>DOD</sub> | _         | _    | _    | 400  | ns   |

| /CS "H" pulse width       | tcs              | _         | 500  | _    | _    | ns   |

| /PUPIN "L" pulse<br>width | t <sub>PUP</sub> | _         | 1    | _    |      | ms   |

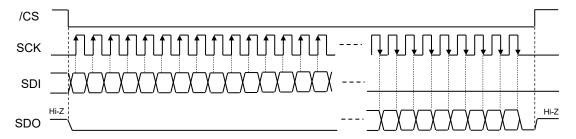

## Serial interface timing diagram

#### ■ Functional Description

#### MCU Interface

The ML5236 is equipped with the SPI interface.

The SPI interface is enabled by asserting the /CS pin to the "L" level. It takes in the MSB-first input data on the SDI pin synchronous to the rising edges of SCK clock. Output- data is supplied on the SDO pin in the MSB-first order synchronous to the falling edges of SCK clock. The SPI interface is disabled with the "H" level input on the /CS pin and returns to the initial state. The /CS pin should be fixed to the "H" level every time after one data write/read operation is completed.

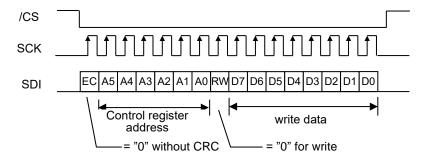

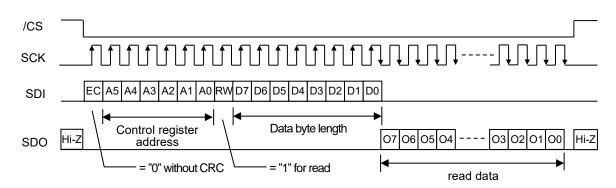

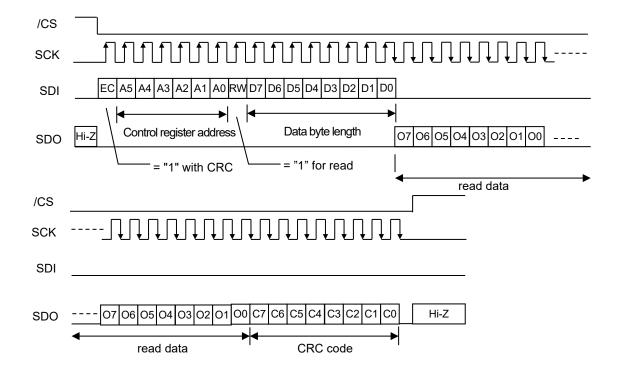

Configurations and controls can be done by reading/writing corresponding addresses in the control register. Write data is one-byte length, while read data length is specified in read commands. Set the RW bit to "0" for data write and "1" for data read. Also, set the EC bit to "1" if the CRC code for detecting a communication error is required, or to "0" otherwise.

When using by applying an external voltage to the VSPI pin, set the /CS pin level at power down to "H" level.

#### 1. Data Write Communication Format without CRC

#### 2. Data Read Communication Format without CRC

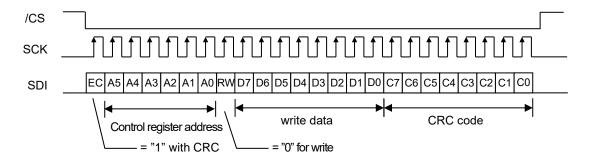

#### 3. Data Write Communication Format with CRC

If the EC bit is enabled, 1-byte CRC (Cyclic Redundancy Code) is generated according to an  $X^8+X^2+X+1$  equation, and added at the end of each communication data. Set the /CS pin to the "H" level to initialize CRC computation to the default FF [h].

Data write is performed on the specified control register only if the result from CRC computation matches the received CRC. Otherwise, data write is not performed. When a CRC error is detected, the CRC error flag is set, allowing the interrupt signal to the external MCU to be asserted on the /INTO pin. For details, refer to the INT EN and INT REQ registers description.

#### 4. Data Read Communication Format with CRC

The CRC computation is also performed for each transmitted/received data during data read operation and the result is appended at the end of the read data. The external MCU can detect any communication errors by comparing the CRC computation result and the received CRC. The CRC code is not included in the data byte length.

# Control Register

The control register map is shown below.

| Address    | Pogister name                           | R/W  | Default | Docarintion                                           |

|------------|-----------------------------------------|------|---------|-------------------------------------------------------|

| 00H        | Register name<br>NOOP                   | R/W  | 00H     | Description User register                             |

| 00H<br>01H | INT EN1                                 | R/W  | 00H     | Interrupt enable 1                                    |

| 02H        | INT EN2                                 | R/W  | 00H     | Interrupt enable 1                                    |

| 03H        | INT REQ1                                | R/W  | 00H     | Interrupt request 1                                   |

| 04H        | INT REQ2                                | R/W  | 00H     | Interrupt request 2                                   |

| 05H        | VMEAS                                   | R/W  | 00H     | Cell voltage measurement control                      |

| 06H        | IMEAS                                   | R/W  | 00H     | Current measurement control                           |

| 07H        | TMEAS                                   | R/W  | 00H     | Temperature measurement control                       |

| 08H        | SMEAS                                   | R/W  | 00H     | PSNS/DFS pin voltage measurement control              |

| 09H        | FET                                     | R/W  | 00H     | FET control                                           |

| 0AH        | CBALL                                   | R/W  | 00H     | Cell balancing control (lower 8 cells)                |

| 0BH        | CBALH                                   | R/W  | 00H     | Cell balancing control (higher 8 cells)               |

| 0CH        | POWER                                   | R/W  | 00H     | Power-save/power-down control                         |

| 0DH        | STATUS                                  | R    | 00H     | Status register                                       |

|            |                                         |      |         | Short circuit detection threshold/watchdog            |

| 0EH        | SCWDT                                   | R/W  | 00H     | timer                                                 |

|            |                                         |      |         | control                                               |

| 0FH        | SETOV                                   | R/W  | 00H     | Overvoltage alarm control                             |

| 10H        | OVDETL                                  | R/W  | FFH     | Overvoltage threshold                                 |

|            | 0.021.1                                 | 1011 |         | (low-order 8 bits)                                    |

| 11H        | OVDETH                                  | R/W  | 0FH     | Overvoltage threshold                                 |

|            |                                         | ,    |         | (high-order 4 bits)                                   |

| 12H        | VCELL1L                                 | R    | 00H     | Cell 1 voltage measurement result                     |

|            |                                         |      |         | (low-order 8 bits)                                    |

| 13H        | VCELL1H                                 | R    | 00H     | Cell 1 voltage measurement result                     |

|            |                                         |      |         | (high-order 4 bits) Cell 2 voltage measurement result |

| 14H        | VCELL2L                                 | R    | 00H     | (low-order 8 bits)                                    |

|            |                                         | _    |         | Cell 2 voltage measurement result                     |

| 15H        | VCELL2H                                 | R    | 00H     | (high-order 4 bits)                                   |

| 4011       | \/OFI   0                               | _    | 0011    | Cell 3 voltage measurement result                     |

| 16H        | VCELL3L                                 | R    | 00H     | (low-order 8 bits)                                    |

| 17H        | VCELL3H                                 | R    | 00H     | Cell 3 voltage measurement result                     |

| 1711       | VCELLSH                                 | K    | ООП     | (high-order 4 bits)                                   |

| 18H        | VCELL4L                                 | R    | 00H     | Cell 4 voltage measurement result                     |

| 1011       | VOLLE-L                                 | 11   | 0011    | (low-order 8 bits)                                    |

| 19H        | VCELL4H                                 | R    | 00H     | Cell 4 voltage measurement result                     |

| 1011       | , , , , , , , , , , , , , , , , , , , , | - '` | 30.1    | (high-order 4 bits)                                   |

| 1AH        | VCELL5L                                 | R    | 00H     | Cell 5 voltage measurement result                     |

|            |                                         | -    |         | (low-order 8 bits)                                    |

| 1BH        | VCELL5H                                 | R    | 00H     | Cell 5 voltage measurement result                     |

|            |                                         |      |         | (high-order 4 bits)                                   |

| 1CH        | VCELL6L                                 | R    | 00H     | Cell 6 voltage measurement result (low-order 8 bits)  |

|            |                                         |      |         | Cell 6 voltage measurement result                     |

| 1DH        | VCELL6H                                 | R    | 00H     | (high-order 4 bits)                                   |

|            |                                         |      |         | Cell 7 voltage measurement result                     |

| 1EH        | VCELL7L                                 | R    | 00H     | (low-order 8 bits)                                    |

|            |                                         | _    |         | Cell 7 voltage measurement result                     |

| 1FH        | VCELL7H                                 | R    | 00H     | (high-order 4 bits)                                   |

| 0011       | \/OF!   0!                              | _    | 0011    | Cell 8 voltage measurement result                     |

| 20H        | VCELL8L                                 | R    | 00H     | (low-order 8 bits)                                    |

| 21⊔        | VCELL OLL                               | R    | ᄱᄱ      | Cell 8 voltage measurement result                     |

| 21H        | VCELL8H                                 | ιτ   | 00H     | (high-order 4 bits)                                   |

| Address | Register name | R/W | Default | Description                                              |

|---------|---------------|-----|---------|----------------------------------------------------------|

| 22H     | VCELL9L       | R   | 00H     | Cell 9 voltage measurement result (low-order 8 bits)     |

| 23H     | VCELL9H       | R   | 00H     | Cell 9 voltage measurement result (high-order 4 bits)    |

| 24H     | VCELL10L      | R   | 00H     | Cell 10 voltage measurement result (low-order 8 bits)    |

| 25H     | VCELL10H      | R   | 00H     | Cell 10 voltage measurement result (high-order 4 bits)   |

| 26H     | VCELL11L      | R   | 00H     | Cell 11 voltage measurement result (low-order 8 bits)    |

| 27H     | VCELL11H      | R   | 00H     | Cell 11 voltage measurement result (high-order 4 bits)   |

| 28H     | VCELL12L      | R   | 00H     | Cell 12 voltage measurement result (low-order 8 bits)    |

| 29H     | VCELL12H      | R   | 00H     | Cell 12 voltage measurement result (high-order 4 bits)   |

| 2AH     | VCELL13L      | R   | 00H     | Cell 13 voltage measurement result (low-order 8 bits)    |

| 2BH     | VCELL13H      | R   | 00H     | Cell 13 voltage measurement result (high-order 4 bits)   |

| 2CH     | VCELL14L      | R   | 00H     | Cell 14 voltage measurement result (low-order 8 bits)    |

| 2DH     | VCELL14H      | R   | 00H     | Cell 14 voltage measurement result (high-order 4 bits)   |

| 2EH     | CURL          | R   | 00H     | Current measurement result (low-order 8 bits)            |

| 2FH     | CURH          | R   | 00H     | Current measurement result (high-order 8 bits)           |

| 30H     | TEMP1L        | R   | 00H     | Temperature 1 measurement result (low-<br>order 8 bits)  |

| 31H     | TEMP1H        | R   | 00H     | Temperature 1 measurement result (high-<br>order 4 bits) |

| 32H     | TEMP2L        | R   | 00H     | Temperature 2 measurement result (low-<br>order 8 bits)  |

| 33H     | TEMP2H        | R   | 00H     | Temperature 2 measurement result (high-<br>order 4 bits) |

| 34H     | SNSL          | R   | 00H     | PSNS/DFS measurement result (low-order 8 bits)           |

| 35H     | SNSH          | R   | 00H     | PSNS/DFS measurement result (high-order 4 bits)          |

## 1. NOOP Register (Adrs = 00H)

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit name | NO7 | NO6 | NO5 | NO4 | NO3 | NO2 | NO1 | NO0 |

| R/W      | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Default  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

No function is assigned to the NOOP register. Read/write access to this register does not change the LSI status. The written data can be read as it is.

#### 2. INT\_EN1 Register (Adrs = 01H)

|          | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|----------|---|---|---|---|-----|-----|-----|-----|

| Bit name |   |   |   |   | ESM | ETM | EIM | EVM |

| R/W      | R | R | R | R | R/W | R/W | R/W | R/W |

| Default  | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |

The INT\_EN1 register enables or disables the interrupt signal output on the /INTO pin.

The EVM bit enables or disables the interrupt signal output at the completion of cell voltage measurement.

| EVM | Cell voltage measurement complete interrupt |

|-----|---------------------------------------------|

| 0   | Disabled (default)                          |

| 1   | Enabled                                     |

The EIM bit enables or disables the interrupt signal output at the completion of current measurement.

| EIM | Current measurement complete interrupt |

|-----|----------------------------------------|

| 0   | Disabled (default)                     |

| 1   | Enabled                                |

The ETM bit enables or disables the interrupt signal output at the completion of temperature sensor measurement.

| ETM | Temperature sensor measurement complete interrupt |

|-----|---------------------------------------------------|

| 0   | Disabled (default)                                |

| 1   | Enabled                                           |

The ESM bit enables or disables the interrupt signal output at the completion of PSNS/DFS pin voltage measurement.

| ESM | PSNS/DFS pin voltage measurement complete interrupt |

|-----|-----------------------------------------------------|

| 0   | Disabled (default)                                  |

| 1   | Enabled                                             |

## 3. INT\_EN2 Register (Adrs = 02H)

|          | 7 | 6 | 5 | 4    | 3     | 2    | 1   | 0   |

|----------|---|---|---|------|-------|------|-----|-----|

| Bit name | _ | _ | _ | EWDT | ECKSP | ECRC | ESC | EOV |

| R/W      | R | R | R | R/W  | R/W   | R/W  | R/W | R/W |

| Default  | 0 | 0 | 0 | 0    | 0     | 0    | 0   | 0   |

The INT\_EN2 register enables or disables the interrupt signal output on the /INTO pin.

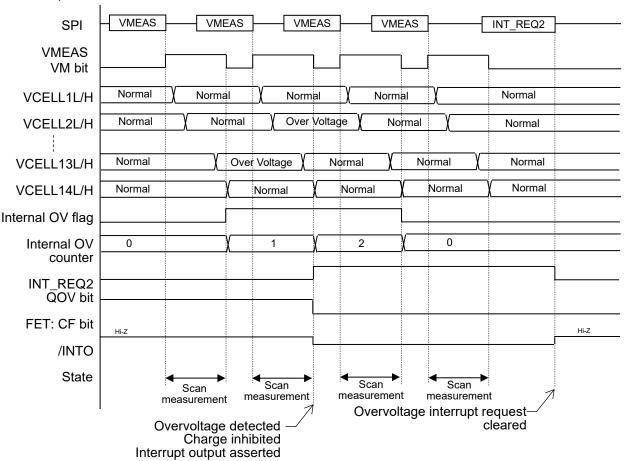

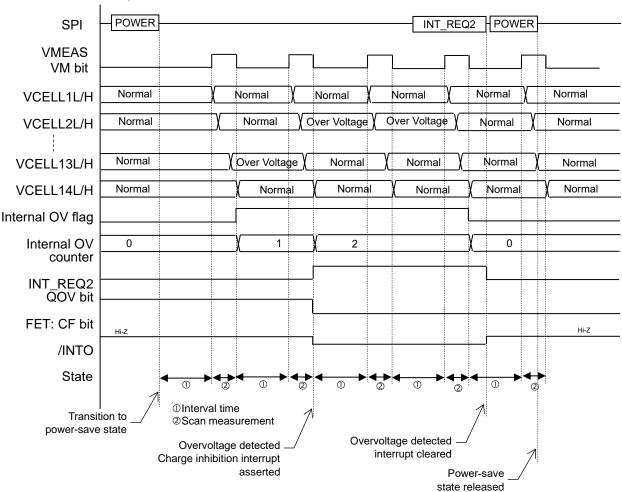

The EOV bit enables or disables the interrupt signal output at overvoltage detection.

| EOV | Overvoltage detection interrupt |

|-----|---------------------------------|

| 0   | Disabled (default)              |

| 1   | Enabled                         |

The ESC bit enables or disables the interrupt signal output at short circuit detection.

| ESC | Short circuit detection interrupt |

|-----|-----------------------------------|

| 0   | Disabled (default)                |

| 1   | Enabled                           |

The ECRC bit enables or disables the interrupt signal output at CRC error detection.

| ECRC | CRC error interrupt |

|------|---------------------|

| 0    | Disabled (default)  |

| 1    | Enabled             |

The ECKSP bit enables or disables the interrupt signal output when the internal clock is halted.

| ECKSP | Internal clock halt interrupt |

|-------|-------------------------------|

| 0     | Disabled (default)            |

| 1     | Enabled                       |

The EWDT bit enables or disables the interrupt signal output when a watchdog timer overflow occurs.

| EWDT | WDT overflow interrupt |

|------|------------------------|

| 0    | Disabled (default)     |

| 1    | Enabled                |

## 4. INT\_REQ1 Register (Adrs = 03H)

|          | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|----------|---|---|---|---|-----|-----|-----|-----|

| Bit name | _ | _ | _ |   | QSM | QTM | QIM | QVM |

| R/W      | R | R | R | R | R/W | R/W | R/W | R/W |

| Default  | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   |

The INT\_REQ1 register contains interrupt request flags. Each request flag is set to "1" when the corresponding interrupt request is generated, regardless of the INT\_EN1 register configuration. Only if the generated interrupt is enabled by the INT\_EN1 register, the "L" level is asserted on the /INTO pin. An interrupt request flag can be cleared by writing data "0" to the corresponding data bit. Since writing data "1" is ignored, if you want to clear one specific interrupt request flag, fill in data "1" to the other bits. When all the enabled interrupt request flags are cleared, the /INTO pin is set to the "Hi-Z" level.

The QVM bit indicates the interrupt request generated on completion of cell voltage measurement.

| QVM | Cell voltage measurement complete interrupt request |

|-----|-----------------------------------------------------|

| 0   | No interrupt request (default)                      |

| 1   | An interrupt request is generated                   |

The QIM bit indicates the interrupt request generated on completion of current measurement.

|  | QIM | Current measurement complete interrupt |

|--|-----|----------------------------------------|

|  |     | request                                |

|  | 0   | No interrupt request (default)         |

|  | 1   | An interrupt request is generated      |

The QTM bit indicates the interrupt request generated on completion of temperature measurement.

| QTM | Temperature measurement complete interrupt request |

|-----|----------------------------------------------------|

| 0   | No interrupt request (default)                     |

| 1   | An interrupt request is generated                  |

The QSM bit indicates the interrupt request generated on completion of PSNS/DFS pin voltage measurement.

| QSM | PSNS/DFS pin voltage measurement  |

|-----|-----------------------------------|

|     | complete interrupt request        |

| 0   | No interrupt request (default)    |

| 1   | An interrupt request is generated |

#### 5. INT\_REQ2 Register (Adrs = 04H)

|          | 7 | 6 | 5 | 4    | 3     | 2    | 1   | 0   |

|----------|---|---|---|------|-------|------|-----|-----|

| Bit name | _ | _ | _ | QWDT | QCKSP | QCRC | QSC | QOV |

| R/W      | R | R | R | R/W  | R/W   | R/W  | R/W | R/W |

| Default  | 0 | 0 | 0 | 0    | 0     | 0    | 0   | 0   |

The INT\_REQ2 register contains interrupt request flags. Each request flag is set to "1" when the corresponding interrupt request is generated, regardless of the INT\_EN2 register configuration. Only if the generated interrupt is enabled by the INT\_EN2 register, the "L" level is asserted on the /INTO pin. An interrupt request flag can be cleared by writing data "0" to the corresponding data bit. Since writing data "1" is ignored,if you want to clear one specific interrupt request flag, fill in data "1" to the other bits. When all enabled interrupt request flags are cleared, the /INTO pin is set to the "Hi-Z" level.

The QOV bit indicates the interrupt request generated at overvoltage detection.

| QOV | Overvoltage detection interrupt request |

|-----|-----------------------------------------|

| 0   | No interrupt request (default)          |

| 1   | An interrupt request is generated       |

The QSC bit indicates the interrupt request generated at short circuit detection.

| QSC | Short circuit detection interrupt request |

|-----|-------------------------------------------|

| 0   | No interrupt request (default)            |

| 1   | An interrupt request is generated         |

The QCRC bit indicates the interrupt request generated at CRC error detection.

| QCRC | CRC error interrupt request       |

|------|-----------------------------------|

| 0    | No interrupt request (default)    |

| 1    | An interrupt request is generated |

The QCKSP bit indicates the interrupt request generated when the internal clock stop is halted.

|       | 1 1 6                                 |

|-------|---------------------------------------|

| QCKSP | Internal clock halt interrupt request |

| 0     | No interrupt request (default)        |

| 1     | An interrupt request is generated     |

The QWDT bit indicates the interrupt request generated when a watchdog timer overflow occurs.

| QWDT | WDT overflow interrupt request    |

|------|-----------------------------------|

| 0    | No interrupt request (default)    |

| 1    | An interrupt request is generated |

## 6. VMEAS Register (Adrs = 05H)

|          | 7   | 6 | 5 | 4    | 3   | 2   | 1   | 0   |

|----------|-----|---|---|------|-----|-----|-----|-----|

| Bit name | VM  | _ | _ | SCAN | VC3 | VC2 | VC1 | VC0 |

| R/W      | R/W | R | R | R/W  | R/W | R/W | R/W | R/W |

| Default  | 0   | 0 | 0 | 0    | 0   | 0   | 0   | 0   |

The VMEAS register configures the cell voltage measurement conditions.

Configure the SCAN bit and the V0 to V3 bits to select the measurement mode and the battery cell(s) to measure.

| e    |     |     |     |     |                            |

|------|-----|-----|-----|-----|----------------------------|

| SCAN | VC3 | VC2 | VC1 | VC0 | Cell voltage measurement   |

| 0    | 0   | 0   | 0   | 0   | Cell 1 selected            |

| 0    | 0   | 0   | 0   | 1   | Cell 2 selected            |

| 0    | 0   | 0   | 1   | 0   | Cell 3 selected            |

| 0    | 0   | 0   | 1   | 1   | Cell 4 selected            |

| 0    | 0   | 1   | 0   | 0   | Cell 5 selected            |

| 0    | 0   | 1   | 0   | 1   | Cell 6 selected            |

| 0    | 0   | 1   | 1   | 0   | Cell 7 selected            |

| 0    | 0   | 1   | 1   | 1   | Cell 8 selected            |

| 0    | 1   | 0   | 0   | 0   | Cell 9 selected            |

| 0    | 1   | 0   | 0   | 1   | Cell 10 selected           |

| 0    | 1   | 0   | 1   | 0   | Cell 11 selected           |

| 0    | 1   | 0   | 1   | 1   | Cell 12 selected           |

| 0    | 1   | 1   | 0   | 0   | Cell 13 selected           |

| 0    | 1   | 1   | 0   | 1   |                            |

| 0    | 1   | 1   | 1   | 0   | Cell 14 selected           |

| 0    | 1   | 1   | 1   | 1   | Cell 14 Selected           |

| 1    | 0   | 0   | 0   | 0   |                            |

| 1    | 0   | 0   | 0   | 1   | Cell 13 to cell 14 scanned |

| 1    | 0   | 0   | 1   | 0   | Cell 12 to cell 14 scanned |

| 1    | 0   | 0   | 1   | 1   | Cell 11 to cell 14 scanned |

| 1    | 0   | 1   | 0   | 0   | Cell 10 to cell 14 scanned |

| 1    | 0   | 1   | 0   | 1   | Cell 9 to cell 14 scanned  |

| 1    | 0   | 1   | 1   | 0   | Cell 8 to cell 14 scanned  |

| 1    | 0   | 1   | 1   | 1   | Cell 7 to cell 14 scanned  |

| 1    | 1   | 0   | 0   | 0   | Cell 6 to cell 14 scanned  |

| 1    | 1   | 0   | 0   | 1   | Cell 5 to cell 14 scanned  |

| 1    | 1   | 0   | 1   | 0   | Cell 4 to cell 14 scanned  |

| 1    | 1   | 0   | 1   | 1   | Cell 3 to cell 14 scanned  |

| 1    | 1   | 1   | 0   | 0   | Cell 2 to cell 14 scanned  |

| 1    | 1   | 1   | 0   | 1   |                            |

| 1    | 1   | 1   | 1   | 0   | Cell 1 to cell 14 scanned  |

| 1    | 1   | 1   | 1   | 1   |                            |

The VM bit starts or stops cell voltage measurement operation and indicates the cell voltage measurement status at the same time. The cell voltage measurement results are stored in the VCELLnL and VCELLnH registers (12H to 2DH).

|    | Write          | Read |                             |  |

|----|----------------|------|-----------------------------|--|

| VM | Cell voltage   | VM   | Cell voltage                |  |

|    | measurement    |      | measurement                 |  |

| 0  | Stop (default) | 0    | Completed/stopped (default) |  |

| 1  | Start          | 1    | Being measured              |  |

If the value "0" is written to the VM bit in the middle of cell voltage measurement, the on-going measurement is completed before measurement is stopped. The VM bit value continues to be "1" until the end of measurement, and it is reset to "0" when the measurement stops.

Any changes to the SCAN and VC3 to VC0 bits are ignored during measurement (while the VM bit is "1").

Also, writing the value "1" to the VM bit during current measurement, temperature measurement, or PSNS/DFS pin voltage measurement is ignored.

## 7. IMEAS Register (Adrs = 06H)

|          | 7   | 6 | 5 | 4    | 3 | 2           | 1    | 0   |

|----------|-----|---|---|------|---|-------------|------|-----|

| Bit name | IM  |   | _ | ENIM | _ | <del></del> | ZERO | GIM |

| R/W      | R/W | R | R | R/W  | R | R           | R/W  | R/W |

| Default  | 0   | 0 | 0 | 0    | 0 | 0           | 0    | 0   |

The IMEAS register controls current measurement and its conditions.

The GIM bit selects the voltage gain of the current measurement amplifier.

| GIM | Voltage gain G <sub>™</sub> |

|-----|-----------------------------|

| 0   | 12 times (default)          |

| 1   | 60 times                    |

The ZERO bit executes zero current compensation of the current measurement amplifier. Because the compensated values may differ for different voltage gains of the current measurement amplifier or different temperatures, periodic compensations are suggested for each voltage gain.

| ZERO | ISP input ISM input |                 | State                             |

|------|---------------------|-----------------|-----------------------------------|

| 0    | Pin input level     | Pin input level | Current measurement enabled       |

| 1    | GND level           | GND level       | Zero current compensation enabled |

The ENIM bit runs and stops the current measurement amplifier.

| ENIM | Current measurement amplifier |

|------|-------------------------------|

| 0    | Stop (default)                |

| 1    | Run                           |

If the value "1" is written to the IM bit, current measurement is repeated for 16 times. For zero current compensation, if the value "1" is written to both the ZERO bit and IM bit, zero current compensation is repeated for 16 times. When the ENIM bit is "0", writing "1" to the IM bit does not execute current measurement or compensation.

Current measurement status can be obtained by reading the IM bit.

The 16-times repeated measurement results are summed up and stored as a 16-bit data to the CURL and CURH registers (2EH to 2FH).

|    | Write                        |    | Read                |

|----|------------------------------|----|---------------------|

| IM | Current measurement          | IM | Current measurement |

| 0  | Not being measured (default) | 0  | Completed (default) |

| 1  | Start                        | 1  | Being measured      |

After the current measurement is started, writing "0" to the IM bit does not stop the current measurement in progress. Also, writing "1" to the IM bit during cell voltage measurement, temperature measurement, or PSNS/DFS pin voltage measurement is ignored.

#### 8. TMEAS Register (Adrs = 07H)

|          | 7   | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|----------|-----|---|---|---|---|---|------|------|

| Bit name | TM  | _ |   |   | _ | _ | TSEL | TDRV |

| R/W      | R/W | R | R | R | R | R | R/W  | R/W  |

| Default  | 0   | 0 | 0 | 0 | 0 | 0 | 0    | 0    |

The TMEAS register controls temperature measurement and its conditions. The input voltage on the TEMP1 and TEMP2 pins can be measured.

The TDRV bit specifies the TDRV pin output status.

The temperature measurement should be performed after the input voltages on the TEMP1 and TEMP2 pins are stabilized.

| TDRV | TDRV pin status |

|------|-----------------|

| 0    | Hi-Z (default)  |

| 1    | 0V              |

The TSEL bit selects the input pin to be measured.

| TSEL | TEMP pin to be measured |

|------|-------------------------|

| 0    | TEMP1 pin (default)     |

| 1    | TEMP2 pin               |

Writing "0" to the TM bit executes temperature measurement. The temperature measurement result is stored in the TEMPnL and TEMPnH registers (30H to 33H).

|    | Write                        | Read |                      |  |  |

|----|------------------------------|------|----------------------|--|--|

| TM | TEMP pin measurement         | TM   | TEMP pin measurement |  |  |

| 0  | Not being measured (default) | 0    | Completed (default)  |  |  |

| 1  | Start                        | 1    | Being measured       |  |  |

After temperature measurement is started, writing "0" to the TM bit does not stop the temperature measurement in progress. Also, writing "1" the TM bit during cell voltage measurement, current measurement, or PSNS/DFS pin voltage measurement is ignored.

#### 9. SMEAS Register (Adrs = 08H)

|          | 7   | 6 | 5 | 4    | 3 | 2    | 1   | 0   |

|----------|-----|---|---|------|---|------|-----|-----|

| Bit name | SM  |   |   | ENSM |   | SSEL | PU  | PD  |

| R/W      | R/W | R | R | R/W  | R | R/W  | R/W | R/W |

| Default  | 0   | 0 | 0 | 0    | 0 | 0    | 0   | 0   |

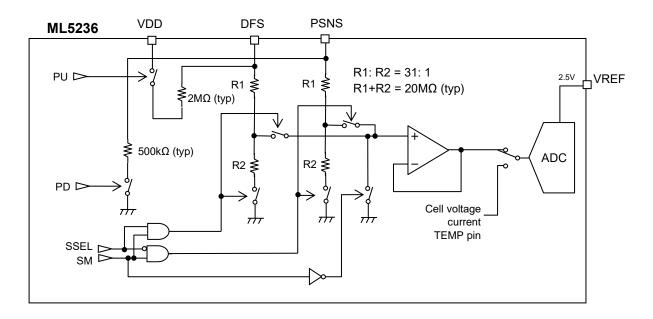

The SMEAS register controls voltage measurement on the PSNS and DFS pins, configures the pull-down resistor on the PSNS pin and the pull-up resistor on the DFS pin. The 1/32-fold voltage of the input levels on the PSNS and DFS pins can be measured.

The PD bit specifies the connection of a pull-down resistor on the PSNS pin.

| ٠. | specifies the c | connection of a pair down resistor on the 1 St 18 pm: |  |  |  |  |  |  |

|----|-----------------|-------------------------------------------------------|--|--|--|--|--|--|

|    | PD              | PD PSNS pin status                                    |  |  |  |  |  |  |

|    | 0               | Pull-down resistor not connected (default)            |  |  |  |  |  |  |

|    | 1               | 500kΩ pull-down resistor connected                    |  |  |  |  |  |  |

The PU bit specifies the connection of a pull-up resistor on the DFS pin.

| PU | DFS pin status                           |

|----|------------------------------------------|

| 0  | Pull-up resistor not connected (default) |

| 1  | 2MΩ pull-up resistor connected           |

The SSEL bit selects the input pin to be measured.

| SSEL | Pin to be measured |

|------|--------------------|

| 0    | PSNS pin (default) |

| 1    | DFS pin            |

The ENSM bit runs and stops the PSNS/DFS pin voltage measurement circuit.

| ENSM | Measurement circuit |

|------|---------------------|

| 0    | Stop (default)      |

| 1    | Run                 |

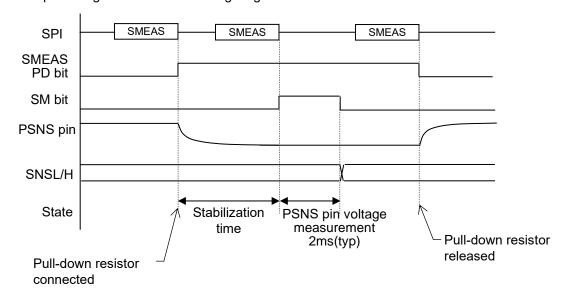

Writing "1" to the SM bit executes voltage measurement on the PSNS or DFS pin. The measurement result is stored in the SNSL and SNSH registers (34H to 35H). When the ENSM bit is set to "0", writing "1" to the SM bit does not execute measurement.

|    | Write                        |    | Read                    |

|----|------------------------------|----|-------------------------|

| SM | Pin voltage measurement      | SM | Pin voltage measurement |

| 0  | Not being measured (default) | 0  | Completed (default)     |

| 1  | Start                        | 1  | Being measured          |

After voltage measurement is started, writing "0" to the SM bit does not stop the measurement in progress. Also, writing "1" to the SM bit during cell voltage measurement, current measurement, or temperature measurement is ignored.

#### 10. FET Register (Adrs = 09H)

|          | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0   |

|----------|---|---|---|---|---|---|-----|-----|

| Bit name | _ | _ | _ | _ | _ | _ | CF  | DF  |

| R/W      | R | R | R | R | R | R | R/W | R/W |

| Default  | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0   |

The FET register turns on or turns off the C-FET and D-FET pins, and the C-/D-FET output status can be obtained by reading it.

The DF bit specifies the D-FET pin output status. When short circuit is detected, the DF bit is automatically reset to "0". Note that it is not automatically set to "1" even after the short circuit detection state is restored to the normal state. It is required to turn on the DF pin using the external MCU.

| DF | Discharge-FET status | D-FET pin output level         |

|----|----------------------|--------------------------------|

| 0  | OFF (default)        | DFS pin level V <sub>DFS</sub> |

| 1  | ON                   | V <sub>DFS</sub> +12V(typ)     |

The CF bit specifies the C-FET pin output status. When short circuit is detected, the CF bit is automatically reset to "0". Note that it is not automatically set to "1" even after the short circuit detection state is restored to the normal state. It is required to turn on the CF pin using the external MCU.

| CF | Charge–FET status | C_FET pin output level         |

|----|-------------------|--------------------------------|

| 0  | OFF (default)     | CFS pin level V <sub>CFS</sub> |

| 1  | ON                | V <sub>CFS</sub> +12V(typ)     |

## 11. CBALL Register (Adrs = 0AH)

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|

| Bit name | SW8 | SW7 | SW6 | SW5 | SW4 | SW3 | SW2 | SW1 |

| R/W      | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Default  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

The CBALL register turns ON or turns OFF the cell balancing switches for the lower 8 cells.

Use the SW8 to SW1 bits to control the respective cells.

| Use the | Use the SW8 to SW1 bits to control the respective cells. |     |     |     |     |     |     |                                    |  |  |  |

|---------|----------------------------------------------------------|-----|-----|-----|-----|-----|-----|------------------------------------|--|--|--|

| SW8     | SW7                                                      | SW6 | SW5 | SW4 | SW3 | SW2 | SW1 | Switch ON/OFF                      |  |  |  |

| 0       | 0                                                        | 0   | 0   | 0   | 0   | 0   | 0   | Lower 8 cells turned OFF (default) |  |  |  |

| 0       | 0                                                        | 0   | 0   | 0   | 0   | 0   | 1   | V1-to-V0 switch turned ON          |  |  |  |

| 0       | 0                                                        | 0   | 0   | 0   | 0   | 1   | 0   | V2-to-V1 switch turned ON          |  |  |  |

| 0       | 0                                                        | 0   | 0   | 0   | 1   | 0   | 0   | V3-to-V2 switch turned ON          |  |  |  |

| 0       | 0                                                        | 0   | 0   | 1   | 0   | 0   | 0   | V4-to-V3 switch turned ON          |  |  |  |

| 0       | 0                                                        | 0   | 1   | 0   | 0   | 0   | 0   | V5-to-V4 switch turned ON          |  |  |  |

| 0       | 0                                                        | 1   | 0   | 0   | 0   | 0   | 0   | V6-to-V5 switch turned ON          |  |  |  |

| 0       | 1                                                        | 0   | 0   | 0   | 0   | 0   | 0   | V7-to-V6 switch turned ON          |  |  |  |

| 1       | 0                                                        | 0   | 0   | 0   | 0   | 0   | 0   | V8-to-V7 switch turned ON          |  |  |  |

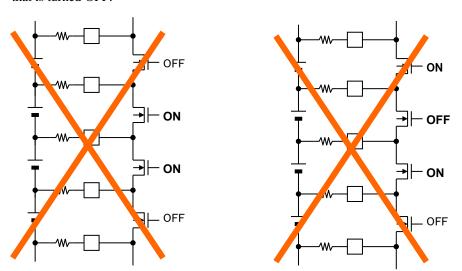

Multiple switches can be turned ON simultaneously, but the following configurations are inhibited, because they may damage the built-in cell balancing switches.

- (1) Do not turn on adjacent cell balancing switches.

- (2) Do not turn on cell balancing switches simultaneously on both sides of a cell balancing switch that is turned OFF.

The cell balancing current and the ON-resistance of cell balancing switch generate heat. Configure the number of turned-on switches and the turned-on duration so that the total power loss in the cell balancing switches does not exceed the power dissipation limit.

#### 12. CBALH Register (Adrs = 0BH)

|          | 7 | 6 | 5    | 4    | 3    | 2    | 1    | 0   |

|----------|---|---|------|------|------|------|------|-----|

| Bit name | _ | _ | SW14 | SW13 | SW12 | SW11 | SW10 | SW9 |

| R/W      | R | R | R/W  | R/W  | R/W  | R/W  | R/W  | R/W |

| Default  | 0 | 0 | 0    | 0    | 0    | 0    | 0    | 0   |

The CBALH register turns ON or turns OFF the cell balancing switches for the higher 6 cells. Use the SW14 to SW9 bits to control the respective cells.

| Ose the SW 14 to SW 9 bits to control the respective cens. |      |      |      |      |     |                                     |  |  |

|------------------------------------------------------------|------|------|------|------|-----|-------------------------------------|--|--|

| SW14                                                       | SW13 | SW12 | SW11 | SW10 | SW9 | Switch ON/OFF                       |  |  |

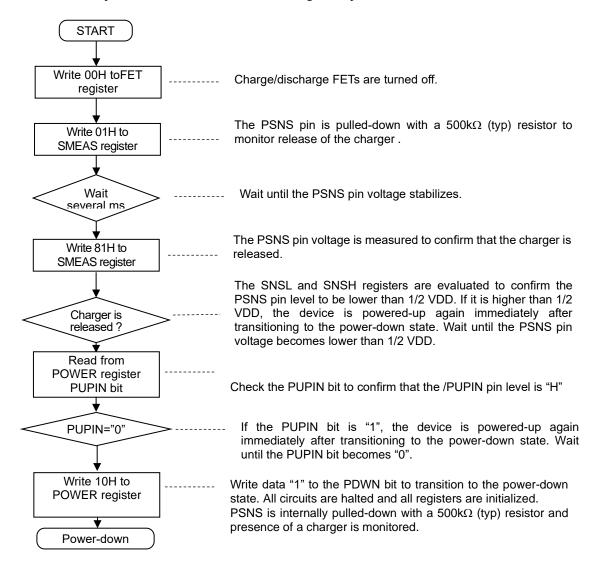

| 0                                                          | 0    | 0    | 0    | 0    | 0   | Higher 6 cells turned OFF (default) |  |  |