8-bit Microcontroller with a Built-in LCD driver

#### **GENERAL DESCRIPTION**

This LSI is a high-performance 8-bit CMOS microcontroller into which peripheral circuits, such as synchronous serial port, UART, RC oscillation type A/D converter, and LCD driver, are incorporated around LAPIS Semiconductor-original 8-bit CPU nX-U8/100. ML610Q461 /ML610Q462/ML610Q463 operates in both high/low-speed mode and power-saving mode, it is most suitable for battery operated products.

### FEATURES

- CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction system: 16-bit instructions

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- On-Chip debug function

- Minimum instruction execution time 30.5 µs (@32.768 kHz system clock) 2µs (@500kHz system clock) 0.5µs(@2MHz system clock)

- Internal memory

- Internal 16KByte Flash ROM (8K×16 bits) (including unusable 1K Byte TEST area)

- Internal 1KByte Data RAM (1024×8 bits)

- Interrupt controller

- 1 non-maskable interrupt sources

- Internal source: 1 (Watch dog timer)

- 17 maskable interrupt sources

Internal sources: 12 (SSIO0, Timer0, Timer1, Timer2, Timer3, UART0, RC-A/D converter, PWM0, TBC128Hz, TBC32Hz, TBC16Hz, TBC2Hz)

External sources: 5 (P00, P01, P02, P03, P04)

- Time base counter

- Low-speed time base counter ×1 channel

Frequency compensation (Compensation range: Approx. –488ppm to +488ppm. Compensation accuracy: Approx. 0.48ppm)

- High-speed time base counter ×1 channel

- Watchdog timer

- Non-maskable interrupt and reset

- Free running

- Overflow period: 4 types selectable (125ms, 500ms, 2s, and 8s)

#### ML610Q461/ML610Q462/ML610Q463

#### • Timers

- 8 bits × 4 channels (Timer0-3: 16-bit x 2 configuration available by using Timer0-1 or Timer2-3)

- Clock frequency measurement mode (in one channel of 16-bit configuration using Timer2-3)

- Capture

- Time base capture  $\times$  2 channels (4096 Hz to 32 Hz)

- PWM

- Resolution 16 bits  $\times$  1 channel

#### • Synchronous serial port

- Master/slave selectable × 1 channel

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- UART

- Half-Duplex Communication

- TXD/RXD × 1 channel

- Bit length, parity/no parity, odd parity/even parity, 1 stop bit/2 stop bits

- Positive logic/negative logic selectable

- Built-in baud rate generator

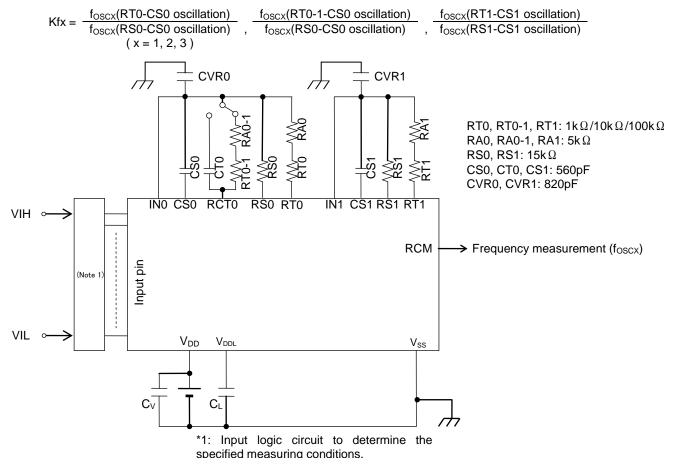

- RC oscillation type A/D converter

- 16-bit counter

- Time division  $\times$  2 channels

- General-purpose ports

- Input-only port × 5 channels (including secondary functions)

- Output-only port

- ML610Q461 : 10 channels (including secondary functions)

- ML610Q462 : 6 channels (including secondary functions)

- ML610Q463 : 2 channels (including secondary functions)

- Input/output port × 14 channels (including secondary functions)

- LCD driver

- The number of segments

- ML610Q461 : 64 dots max. (16seg×4com)

- ML610Q462 : 80 dots max. (20seg×4com)

- ML610Q463 : 96 dots max. (24seg×4com)

- 1/1 to 1/4 duty

- -1/2, 1/3 bias (built-in bias generation circuit)

- Frame frequency selecable: approx. 64Hz, 73Hz, 85Hz, and 102Hz

- Bias voltage multiplying clock selectable (8 types)

- LCD drive stop mode, LCD display mode, all LCDs on mode, and all LCDs off mode selectable

- Reset

- Reset through the RESET\_N pin

- Power-on reset generation when powered on

- Reset when oscillation stop of the low-speed clock is detected

- Reset by the watchdog timer (WDT) overflow

- Clock

- Low-speed clock: Crystal oscillation (32.768 kHz)

- (This LSI can not guarantee the operation withoug low-speed crystal oscillation clock)

- High-speed clock: Built-in RC oscillation (500 kHz, 2MHz)

#### • Power management

- HALT mode: Instruction execution by CPU is suspended (peripheral circuits are in operating states).

- STOP mode: Stop of low-speed oscillation and high-speed oscillation (Operations of CPU and peripheral circuits are stopped.)

- High-speed Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, 1/8 of the oscillation clock)

- Block Control Function: Resets and completely turns circuits of unused peripherals off.

- Guaranteed operating range

- Operating temperature: -20°C to +70°C

- Operating voltage:  $V_{DD} = 1.25V$  to 3.6V

#### • Product name — Supported Function

The line-up of the ML610Q461 ,the ML610Q462 and the ML610Q463 are below.

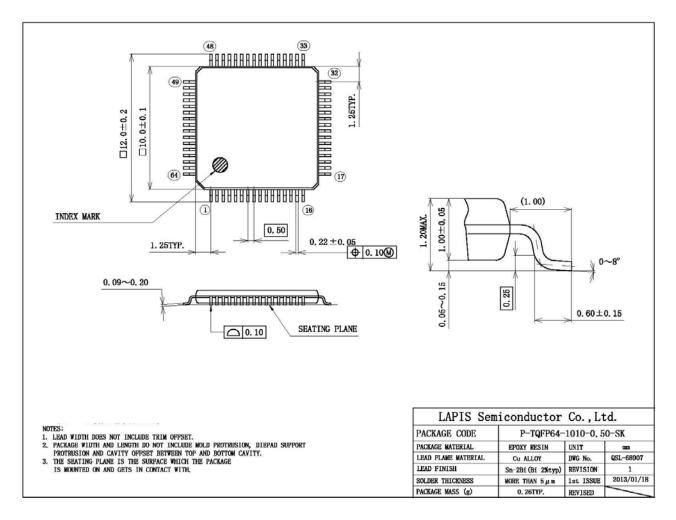

| - 64-Pin plastic<br>TQFP - | ROM type  | Operating<br>temperature | Product availability |  |

|----------------------------|-----------|--------------------------|----------------------|--|

| ML610Q461-xxxTB            | Flash ROM | -20°C to +70°C           | Yes                  |  |

| ML610Q462-xxxTB            | Flash ROM | -20°C to +70°C           | Yes                  |  |

| ML610Q463-xxxTB            | Flash ROM | -20°C to +70°C           | Yes                  |  |

xxx:ROM code number (xxx of the blank product is NNN) Q:Flash ROM version TB:TQFP

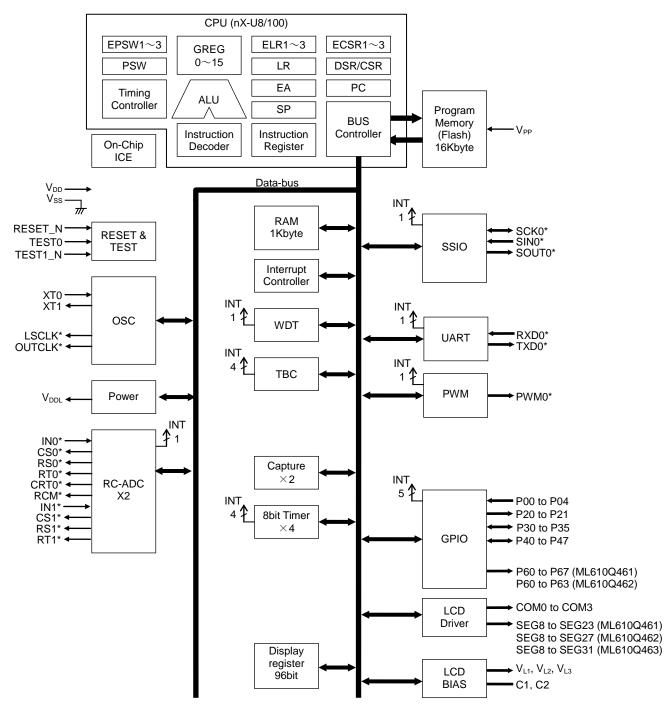

#### **BLOCK DIAGRAM**

#### Block Diagram of ML610Q461/ML610Q462/ML610Q463

Figure 1 show the block diagram of the ML610Q461/ML610Q462/ML610Q463.

"\*" indicates the secondary or tertiary function of each port.

Figure 1 ML610Q461/ML610Q462/ML610Q463 Block Diagram

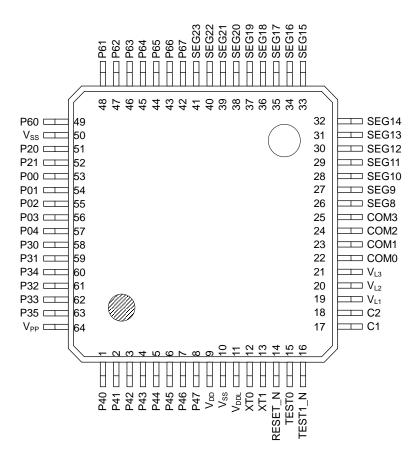

#### PIN CONFIGURATION

#### ML610Q461 TQFP64 Pin Layout

Note: The assignment of the P30 to P35 are not in order.

#### Figure 2 ML610Q461 TQFP64 Pin Configuration

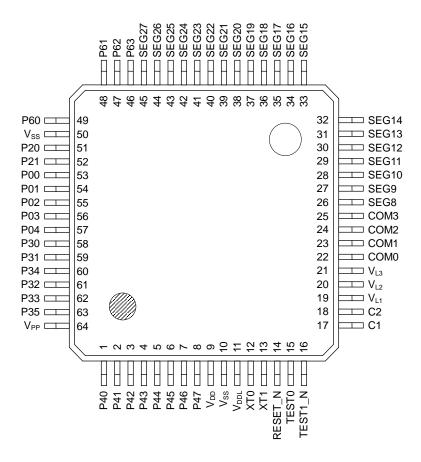

#### ML610Q462 TQFP64 Pin Layout

Note: The assignment of the P30 to P35 are not in order.

#### Figure 3 ML610Q462 TQFP64 Pin Configuration

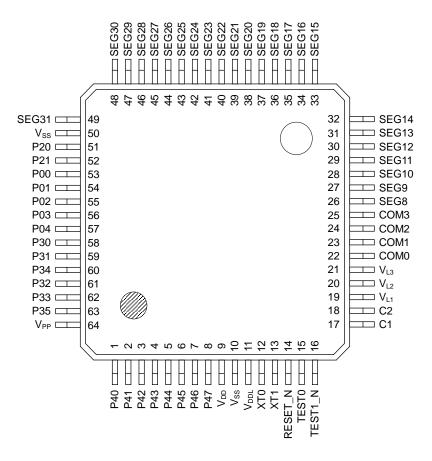

#### ML610Q463 TQFP64 Pin Layout

Note: The assignment of the P30 to P35 are not in order.

#### Figure 4 ML610Q463 TQFP64 Pin Configuration

#### FEDL610Q461-03

### ML610Q461/ML610Q462/ML610Q463

# PIN LIST

|            |                      | F   | Primary function                                                                                               | S                      | econdarv fu | Inctio | n or Tertiary function                                      |

|------------|----------------------|-----|----------------------------------------------------------------------------------------------------------------|------------------------|-------------|--------|-------------------------------------------------------------|

| PIN<br>No. | Pin name             | I/O | Function                                                                                                       | Secondary<br>/Tertiary | Pin name    | I/O    | Function                                                    |

| 10<br>50   | Vss                  | —   | Negative power supply pin                                                                                      | _                      |             |        | —                                                           |

| 9          | V <sub>DD</sub>      |     | Positive power supply pin                                                                                      |                        |             |        |                                                             |

| 11         | V <sub>DDL</sub>     |     | Power supply pin for internal logic<br>(internally generated)                                                  |                        |             |        | —                                                           |

| 64         | V <sub>PP</sub>      | —   | Power supply pin for Flash ROM                                                                                 |                        |             | —      |                                                             |

| 19         | V <sub>L1</sub>      |     | Power supply pin for LCD bias (internally generated or connected to positive power supply pin) <sup>(*1)</sup> | _                      | _           |        | _                                                           |

| 20         | V <sub>L2</sub>      | —   | Power supply pin for LCD bias (internally generated or connected to positive power supply pin) <sup>(*1)</sup> | _                      | _           |        | _                                                           |

| 21         | V <sub>L3</sub>      | —   | Power supply pin for LCD bias (internally generated)                                                           | _                      | _           | _      | —                                                           |

| 17         | C1                   | —   | Capacitor connection pin for LCD bias generation                                                               |                        |             | —      | _                                                           |

| 18         | C2                   | —   | Capacitor connection pin for LCD bias generation                                                               | _                      | _           | —      | —                                                           |

| 15         | TEST0                | I/O | Test pin                                                                                                       | —                      | —           |        | —                                                           |

| 16         | TEST1_N              | I   | Test pin                                                                                                       |                        |             | _      |                                                             |

| 14         | RESET_N              | Ι   | Reset input pin                                                                                                |                        |             |        |                                                             |

| 12         | XT0                  | 1   | Low-speed clock oscillation pin                                                                                |                        |             |        |                                                             |

| 13         | XT1                  | 0   | Low-speed clock oscillation pin                                                                                | _                      | _           |        |                                                             |

| 53         | P00/EXI0/<br>CAP0    | I   | Input port,<br>External interrupt,<br>Capture 0 input                                                          |                        | _           |        | —                                                           |

| 54         | P01/EXI1/<br>CAP1    | I   | Input port,<br>External interrupt,<br>Capture 1 input                                                          | _                      | _           | _      | _                                                           |

| 55         | P02/EXI2/<br>RXD0    | I   | Input port,<br>External interrupt,<br>UART0 received data                                                      |                        |             |        | —                                                           |

| 56         | P03/EXI3             | Ι   | Input port,<br>External interrupt                                                                              |                        |             |        | _                                                           |

| 57         | P04/EXI4/<br>T02P0CK | I   | Input port,<br>Timer 0/Timer 2/PWM0 external<br>clock input<br>External interrupt                              |                        |             |        | —                                                           |

| 51         | P20/LED0             | 0   | Output port                                                                                                    | Secondary              | LSCLK       | 0      | Low-speed clock output                                      |

| 52         | P21/LED1             | 0   | Output port                                                                                                    | Secondary              | OUTCLK      | 0      | High-speed clock output                                     |

| 58         | P30                  | I/O | Input/output port                                                                                              | Secondary              | IN0         | Ι      | RC type ADC0 oscillation input<br>pin                       |

| 59         | P31                  | I/O | Input/output port                                                                                              | Secondary              | CS0         | 0      | RC type ADC0 reference<br>capacitor connection pin          |

| 60         | P34                  | I/O | Input/output port                                                                                              | Secondary              | RCT0        | 0      | RC type ADC0<br>resistor/capacitor sensor<br>connection pin |

| 61         | P32                  | I/O | Input/output port                                                                                              | Secondary              | RS0         | 0      | RC type ADC0 reference<br>resistor connection pin           |

| 62         | P33                  | I/O | Input/output port                                                                                              | Secondary              | RT0         | 0      | RC type ADC0 measurement resistor sensor connection pin     |

| 63         | P35                  | I/O | Input/output port                                                                                              | Secondary              | RCM         | 0      | RC type ADC oscillation monitor                             |

| PIN | Primary function |     |                                                      | Secondary function or Tertiary function |          |     |                                                         |

|-----|------------------|-----|------------------------------------------------------|-----------------------------------------|----------|-----|---------------------------------------------------------|

| No. | Pin name         | I/O | Function                                             | Secondary<br>/Tertiary                  | Pin name | I/O | Function                                                |

| 1   | P40              | I/O | Input/output port                                    | Secondary                               | —        |     |                                                         |

| 1   | F40              | 1/0 |                                                      | Tertiary                                | SIN0     | Ι   | SSIO0 data input                                        |

|     |                  |     |                                                      | Secondary                               | —        |     | —                                                       |

| 2   | P41              | I/O | Input/output port                                    | Tertiary                                | SCK0     | I/O | SSIO0 synchronous clock<br>input/output                 |

| 3   | P42              | I/O | Innut/outnut nort                                    | Secondary                               | RXD0     |     | UART data input                                         |

| 3   | P42              | 1/0 | Input/output port                                    | Tertiary                                | SOUT0    | 0   | SSIO0 data output                                       |

| 4   | P43              | I/O | Input/output port                                    | Secondary                               | TXD0     | 0   | UART data output                                        |

| 4   | F43              | Ņ   |                                                      | Tertiary                                | PWM0     | 0   | PWM0 output                                             |

| 5   | P44/<br>T02P0CK  | I/O | Input/output port,<br>Timer 0/Timer 2/PWM0 external  | Secondary                               | IN1      | Ι   | RC type ADC1 oscillation input<br>pin                   |

|     | TUZFUCK          |     | clock input                                          | Tertiary                                | SIN0     | —   | SSIO0 data input                                        |

| 6   | P45/T13CK        | I/O | Input/output port,<br>Timer 1/Timer 3 external clock | Secondary                               | CS1      | 0   | RC type ADC1 reference<br>capacitor connection pin      |

| 0   | 140/11001        | 10  | input                                                | Tertiary                                | SCK0     | I/O | SSIO0 synchronous clock<br>input/output                 |

| 7   | P46              | I/O | Input/output port                                    | Secondary                               | RS1      | 0   | RC type ADC1 reference<br>resistor connection pin       |

|     |                  |     |                                                      | Tertiary                                | SOUT0    | 0   | SSIO0 data output                                       |

| 8   | P47              | I/O | Input/output port                                    | Secondary                               | RT1      | 0   | RC type ADC1 measurement resistor sensor connection pin |

### ML610Q461/ML610Q462/ML610Q463

| PIN |                            | Pr  | imary function  | Se                     | condary fu  | Inctior | n or Tertiary function |

|-----|----------------------------|-----|-----------------|------------------------|-------------|---------|------------------------|

| No. | Pin name                   | I/O | Function        | Secondary/<br>Tertiary | Pin<br>name | I/O     | Function               |

| 22  | COM0                       | 0   | LCD common pin  | —                      | _           |         |                        |

| 23  | COM1                       | 0   | LCD common pin  | _                      | _           |         |                        |

| 24  | COM2                       | 0   | LCD common pin  | —                      | _           | _       |                        |

| 25  | COM3                       | 0   | LCD common pin  | —                      | _           |         |                        |

| 26  | SEG8                       | 0   | LCD segment pin | _                      | _           | _       |                        |

| 27  | SEG9                       | 0   | LCD segment pin | —                      | _           |         | —                      |

| 28  | SEG10                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 29  | SEG11                      | 0   | LCD segment pin | —                      | _           |         | —                      |

| 30  | SEG12                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 31  | SEG13                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 32  | SEG14                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 33  | SEG15                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 34  | SEG16                      | 0   | LCD segment pin | _                      | _           | _       |                        |

| 35  | SEG17                      | 0   | LCD segment pin | —                      |             | —       |                        |

| 36  | SEG18                      | 0   | LCD segment pin | _                      | _           | _       |                        |

| 37  | SEG19                      | 0   | LCD segment pin | —                      |             | _       |                        |

| 38  | SEG20                      | 0   | LCD segment pin | —                      | _           | —       |                        |

| 39  | SEG21                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 40  | SEG22                      | 0   | LCD segment pin | _                      | _           | _       |                        |

| 41  | SEG23                      | 0   | LCD segment pin | —                      | _           |         |                        |

| 42  | P67 <sup>(*2)</sup>        | 0   | Output port     | _                      | _           | _       |                        |

| 42  | SEG24 <sup>(*3) (*4)</sup> | 0   | LCD segment pin | _                      | _           | _       |                        |

| 40  | P66 <sup>(*2)</sup>        | 0   | Output port     | _                      | _           | —       | _                      |

| 43  | SEG25 <sup>(*3) (*4)</sup> | 0   | LCD segment pin | _                      | _           | —       | _                      |

| 44  | P65 <sup>(*2)</sup>        | 0   | Output port     | —                      |             | _       |                        |

| 44  | SEG26 <sup>(*3) (*4)</sup> | 0   | LCD segment pin | _                      | _           | _       |                        |

| 45  | P64 <sup>(*2)</sup>        | 0   | Output port     | —                      | _           | —       |                        |

| 45  | SEG27 <sup>(*3) (*4)</sup> | 0   | LCD segment pin | —                      | _           | —       |                        |

| 46  | P63 <sup>(*2)</sup> (*3)   | 0   | Output port     | _                      |             |         |                        |

| 40  | SEG28 <sup>(*4)</sup>      | 0   | LCD segment pin | _                      | _           | —       | _                      |

| 47  | P62 <sup>(*2)</sup> (*3)   | 0   | Output port     | —                      | _           | —       | —                      |

| 47  | SEG29 <sup>(*4)</sup>      | 0   | LCD segment pin | —                      | _           | —       | _                      |

| 40  | P61 <sup>(*2)</sup> (*3)   | 0   | Output port     | _                      |             | —       |                        |

| 48  | SEG30 <sup>(*4)</sup>      | 0   | LCD segment pin |                        | _           | _       | _                      |

| 40  | P60 <sup>(*2)</sup> (*3)   | 0   | Output port     |                        |             | —       | _                      |

| 49  | SEG31 <sup>(*4)</sup>      | 0   | LCD segment pin |                        | _           | —       |                        |

<sup>(\*1)</sup> Internally generated, or connect to either positive power supply pin (V<sub>DD</sub>) or power supply pin for internal logic (V<sub>DDL</sub>). For details, see "Chapter 20 LCD Drivers. In the user's manual"

<sup>(\*2)</sup> For ML610Q461. <sup>(\*3)</sup> For ML610Q462. <sup>(\*4)</sup> For ML610Q463.

# ML610Q461/ML610Q462/ML610Q463

# PIN DESCRIPTION

| Pin name      | I/O    | Description                                                                                                                                                                                                                                              | Primary/<br>Secondary/<br>Tertiary | Logic    |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|

| System        |        |                                                                                                                                                                                                                                                          |                                    |          |

| RESET_N       | I      | Reset input pin. When this pin is set to a "L" level, system reset mode is set<br>and the internal section is initialized. When this pin is set to a "H" level<br>subsequently, program execution starts. A pull-up resistor is internally<br>connected. | _                                  | Negative |

| XT0           | I      | Crystal connection pin for low-speed clock.                                                                                                                                                                                                              |                                    | —        |

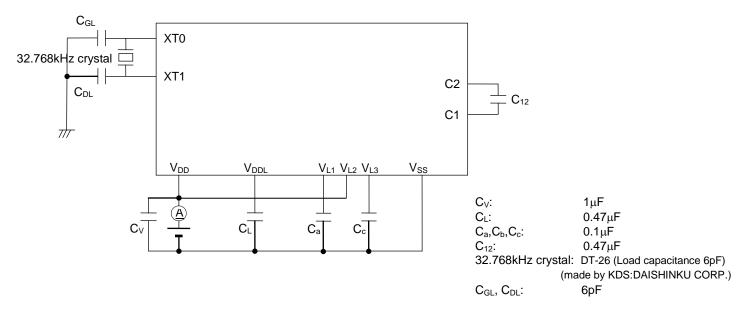

| XT1           | 0      | A 32.768 kHz crystal oscillator (see measuring circuit 1) is connected to this pin. Capacitors CDL and CGL are connected across this pin and $V_{SS}$ .                                                                                                  | —                                  | —        |

| LSCLK         | 0      | Low-speed clock output pin. This pin is used as the secondary function of the P20 pin.                                                                                                                                                                   | Secondary                          | _        |

| OUTCLK        | 0      | High-speed clock output pin. This pin is used as the secondary function of the P21 pin.                                                                                                                                                                  | Secondary                          | —        |

| General-purpo | ose in | put port                                                                                                                                                                                                                                                 |                                    |          |

| P00-P04       | I      | General-purpose input port.<br>Since these pins have secondary functions, the pins cannot be used as a<br>port when the secondary functions are used.                                                                                                    | Primary                            | Positive |

| General-purpo | ose ou | utput port                                                                                                                                                                                                                                               |                                    |          |

| P20-P21       | 0      | General-purpose output port.<br>Since these pins have secondary functions, the pins cannot be used as a<br>port when the secondary functions are used.                                                                                                   | Primary                            | Positive |

| General-purpo | ose in | put/output port                                                                                                                                                                                                                                          |                                    |          |

| P30-P35       | I/O    | General-purpose input/output port.<br>Since these pins have secondary functions, the pins cannot be used as a<br>port when the secondary functions are used.                                                                                             | Primary                            | Positive |

| P40-P47       | I/O    | General-purpose input/output port.<br>Since these pins have secondary functions, the pins cannot be used as a<br>port when the secondary functions are used.                                                                                             | Primary                            | Positive |

| P60-P63       | 0      | General-purpose output port.<br>Incorporated only into ML610Q461/ML610Q462, and not into ML610Q463.                                                                                                                                                      | Primary                            | Positive |

| P64-P67       | 0      | General-purpose output port.<br>Incorporated only into ML610Q461, and not into ML610Q462/ ML610Q463.                                                                                                                                                     | Primary                            | Positive |

### ML610Q461/ML610Q462/ML610Q463

| Pin name       | I/O                                                                                         | Description                                                                                                                                                                              | Primary/<br>Secondary/<br>Tertiary | Logic                 |

|----------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|

| UART           |                                                                                             |                                                                                                                                                                                          |                                    |                       |

| TXD0           | 0                                                                                           | UART data output pin. This pin is used as the secondary function of the P43 pin.                                                                                                         | Secondary                          | Positive              |

| RXD0           | I                                                                                           | UART data input pin. This pin is used as the secondary function of the P42 or the primary function of the P02 pin.                                                                       | Primary/<br>Secondary              | Positive              |

| Synchronous    | serial                                                                                      | (SSIO)                                                                                                                                                                                   |                                    |                       |

| SCK0           | I/O                                                                                         | Synchronous serial clock input/output pin. This pin is used as the tertiary function of the P41 or P45 pin.                                                                              | Tertiary                           | —                     |

| SIN0           | Ι                                                                                           | Synchronous serial data input pin. This pin is used as the tertiary function of the P40 or P44pin.                                                                                       | Tertiary                           | Positive              |

| SOUT0          | 0                                                                                           | Synchronous serial data output pin. This pin is used as the tertiary function of the P42 or P46 pin.                                                                                     | Tertiary                           | Positive              |

| PWM            |                                                                                             |                                                                                                                                                                                          |                                    |                       |

| PWM0           | 0                                                                                           | PWM0 output pin. This pin is used as the tertiary function of the P43 or P34 pin.                                                                                                        | Tertiary                           | Positive              |

| External inter | rrupt                                                                                       |                                                                                                                                                                                          |                                    |                       |

| EXI0-4         | I                                                                                           | External maskable interrupt input pins. Interrupt enable and edge selection can be performed for each bit by software. These pins are used as the primary functions of the P00-P04 pins. | Primary                            | Positive/<br>negative |

| Capture        |                                                                                             |                                                                                                                                                                                          |                                    |                       |

| CAP0           | Ι                                                                                           | Capture trigger input pins. The value of the time base counter is captured in the register synchronously with the interrupt edge selected by software.                                   | Primary                            | Positive/<br>negative |

| CAP1           | CAP1   These pins are used as the primary functions of the P00 pin(CAP0) and P01 pin(CAP1). |                                                                                                                                                                                          | Primary                            | Positive/<br>negative |

| LED drive      |                                                                                             |                                                                                                                                                                                          |                                    |                       |

| LED0-1         | 0                                                                                           | Nch open drain output pins to drive LED.                                                                                                                                                 | Primary                            | Positive/<br>negative |

# ML610Q461/ML610Q462/ML610Q463

|                  |        |                                                                                                                                                          | Primary/     |       |

|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|

| Pin name         | I/O    | Description                                                                                                                                              | Secondary/   | Logic |

|                  | ., C   |                                                                                                                                                          | Tertiary     | _09.0 |

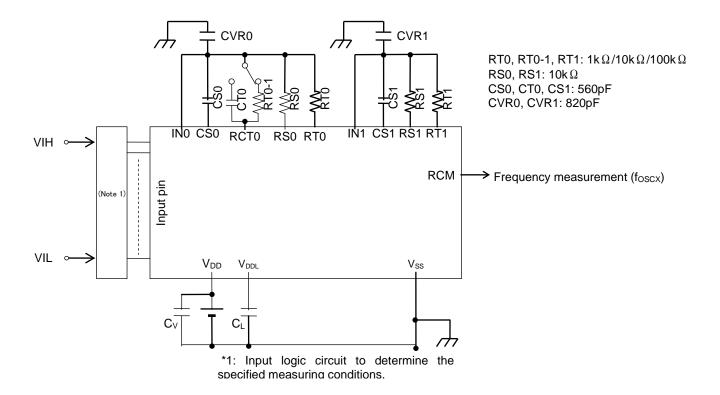

| RC oscillation   | n type | A/D converter                                                                                                                                            |              |       |

| INO              | I      | Channel 0 oscillation input pin. This pin is used as the secondary function of the P30 pin.                                                              | Secondary    |       |

| CS0              | 0      | Channel 0 reference capacitor connection pin. This pin is used as the secondary function of the P31 pin.                                                 | Secondary    |       |

| RCT0             | 0      | Resistor/capacitor sensor connection pin of Channel 0 for measurement.<br>This pin is used as the secondary function of the P33 pin.                     | Secondary    |       |

| RS0              | 0      | This pin is used as the secondary function of the P32 pin which is the reference resistor connection pin of Channel 0.                                   | Secondary    |       |

| RT0              | 0      | Resistor sensor connection pin of Channel 0 for measurement. This pin is used as the secondary function of the P34 pin.                                  | Secondary    | _     |

| RCM              | 0      | RC oscillation monitor pin. This pin is used as the secondary function of the P35 pin.                                                                   | Secondary    | _     |

| IN1              | Ι      | Oscillation input pin of Channel 1. This pin is used as the secondary function of the P44 pin.                                                           | Secondary    | _     |

| CS1              | 0      | Reference capacitor connection pin of Channel 1. This pin is used as the secondary function of the P45 pin.                                              | Secondary    | _     |

| RS1              | 0      | Reference resistor connection pin of Channel 1. This pin is used as the secondary function of the P46 pin.                                               | Secondary    | _     |

| RT1              | 0      | Resistor sensor connection pin for measurement of Channel 1. This pin is used as the secondary function of the P47 pin.                                  | Secondary    | —     |

| LCD drive sig    | inal   |                                                                                                                                                          |              |       |

| COM0-3           | 0      | Common output pins.                                                                                                                                      | —            | _     |

| SEG8-23          | 0      | Segment output pins.                                                                                                                                     | —            | _     |

| SEG24-27         | 0      | Segment output pins. Incorporated into ML610Q462/ML610Q463, not into ML610Q461.                                                                          |              | _     |

| SEG28-31         | 0      | Segment output pins. Incorporated into ML610Q463, not into ML610Q461/ML610Q462.                                                                          | —            | —     |

| LCD driver po    | ower s | upply                                                                                                                                                    |              |       |

| V <sub>L1</sub>  | —      | Power supply pins for LCD bias (internally generated or positive power supply                                                                            | —            | _     |

| V <sub>L2</sub>  | —      | pin connected ). Depending on LCD Bias setting and $V_{\text{DD}}$ voltage level, $V_{\text{DD}}$                                                        |              | —     |

| V <sub>L3</sub>  | —      | or $V_{\text{DDL}}$ or capacitor is connected. For details of the connection method, see user's manual.                                                  | —            |       |

| C1               | —      | Power supply pins for LCD bias (internally generated). Capacitors C12 is                                                                                 |              | —     |

| C2               |        | connected between C1 and C2.                                                                                                                             | —            | —     |

| For testing      | 1      |                                                                                                                                                          | · · · ·      |       |

| TEST0            | I/O    | Input/output pin for testing. A pull-down resistor is internally connected.                                                                              |              | —     |

| TEST1_N          | I      | Input pin for testing. A pull-up resistor is internally connected.                                                                                       | —            | _     |

| Power supply     | '      |                                                                                                                                                          | ,          т |       |

| Vss              | —      | Negative power supply pin.                                                                                                                               | -            | —     |

| V <sub>DD</sub>  | -      | Positive power supply pin for I/O, internal regulator, battery low detector, and power-on reset.                                                         | —            |       |

| V <sub>DDL</sub> | -      | Positive power supply pin (internally generated) for internal logic. Capacitor CL (see measuring circuit 1) is connected between this pin and $V_{SS}$ . | —            | _     |

| V <sub>PP</sub>  |        | Power supply pin for programming Flash ROM. A pull-down resistor is internally connected.                                                                | —            | —     |

### TERMINATION OF UNUSED PINS

Table 2 shows methods of terminating the unused pins.

| Pin                                                 | Recommended pin termination        |

|-----------------------------------------------------|------------------------------------|

| V <sub>PP</sub>                                     | Open                               |

| V <sub>L1</sub> , V <sub>L2</sub> , V <sub>L3</sub> | Open                               |

| C1, C2                                              | Open                               |

| RESET_N                                             | Open                               |

| TEST0                                               | Open                               |

| TEST1_N                                             | Open                               |

| P00 to P04                                          | V <sub>DD</sub> or V <sub>SS</sub> |

| P20 to P21                                          | Open                               |

| P30 to P35                                          | Open                               |

| P40 to P47                                          | Open                               |

| P60 to P67                                          | Open                               |

| COM0 to 3                                           | Open                               |

| SEG8 to 31                                          | Open                               |

### Table 2 Termination of Unused Pins

Note:

It is recommended to set the unused input ports and input/output ports to the inputs with pull-down resistors/pull-up resistors or the output mode since the supply current may become excessively large if the pins are left open in the high impedance input setting.

#### FEDL610Q461-03

# LAPIS Semiconductor Co., Ltd.

#### ML610Q461/ML610Q462/ML610Q463

### ELECTRICAL CHARACTERISTICS

### ABSOLUTE MAXIMUM RATINGS

|                        |                   |                    |                              | $(V_{SS} = 0)$ |

|------------------------|-------------------|--------------------|------------------------------|----------------|

| Parameter              | Symbol            | Condition          | Rating                       | Unit           |

| Power supply voltage 1 | V <sub>DD</sub>   | Ta = 25°C          | -0.3 to +4.6                 | V              |

| Power supply voltage 2 | V <sub>PP</sub>   | Ta = 25°C          | -0.3 to +9.5                 | V              |

| Power supply voltage 3 | V <sub>DDL</sub>  | Ta = 25°C          | -0.3 to +3.6                 | V              |

| Power supply voltage 4 | V <sub>L1</sub>   | Ta = 25°C          | -0.3 to +2.0                 | V              |

| Power supply voltage 5 | V <sub>L2</sub>   | Ta = 25°C          | -0.3 to +4.0                 | V              |

| Power supply voltage 6 | V <sub>L3</sub>   | Ta = 25°C          | -0.3 to +6.0                 | V              |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C          | –0.3 to V <sub>DD</sub> +0.3 | V              |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C          | –0.3 to V <sub>DD</sub> +0.3 | V              |

| Output current 1       | I <sub>OUT1</sub> | Port3–6, Ta = 25°C | -12 to +11                   | mA             |

| Output current 2       | I <sub>OUT2</sub> | Port2, Ta = 25°C   | -12 to +20                   | mA             |

| Power dissipation      | PD                | Ta = 25°C          | 0.9                          | W              |

| Storage temperature    | T <sub>STG</sub>  |                    | -55 to +150                  | °C             |

### **RECOMMENDED OPERATING CONDITIONS**

|                                                          |                      |                                   |             | $(V_{SS} = 0V)$ |

|----------------------------------------------------------|----------------------|-----------------------------------|-------------|-----------------|

| Parameter                                                | Symbol               | Condition                         | Range       | Unit            |

| Operating temperature                                    | T <sub>OP</sub>      |                                   | -20 to +70  | °C              |

|                                                          |                      | $f_{OP} = 30k \text{ to } 625kHz$ | 1.25 to 3.6 | Ň               |

| Operating voltage                                        | V <sub>DD</sub>      | $f_{OP}$ = 30k to 2.5MHz          | 1.8 to 3.6  | V               |

|                                                          | £                    | V <sub>DD</sub> = 1.25 to 3.6V    | 30k to 625k | Hz              |

| Operating frequency (CPU)                                | f <sub>OP</sub>      | V <sub>DD</sub> = 1.8 to 3.6V     | 30k to 2.5M | HZ              |

| Capacitor externally connected to $V_{\text{DDL}}$ pin   | CL                   | _                                 | 0.47±30%    | μF              |

| Capacitors externally connected to $V_{L1, 2, 3}$ pins   | С <sub>а, b, c</sub> | —                                 | 0.1±30%     | μF              |

| Capacitors externally connected<br>across C1 and C2 pins | C <sub>12</sub>      | _                                 | 0.47±30%    | μF              |

### CLOCK GENERATION CIRCUIT OPERATING CONDITIONS

|                                                                                       |                                  |                                                  |      |         |       | (100 01)   |

|---------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------|------|---------|-------|------------|

| Parameter                                                                             | Cumhal                           |                                                  |      |         | 11-14 |            |

| Parameter                                                                             | Symbol                           | Condition                                        | Min. | Тур.    | Max.  | Unit       |

| Low-speed crystal oscillation<br>frequency                                            | f <sub>XTL</sub>                 | _                                                | —    | 32.768k | _     | Hz         |

| Recommended equivalent series<br>resistance value of low-speed<br>crystal oscillation | R∟                               |                                                  |      |         | 40k   | Ω          |

| Low-speed crystal oscillation                                                         | C /C                             | C <sub>L</sub> =6pF of<br>crystal<br>oscillation |      | 12      |       | <b>р</b> Г |

| external capacitor                                                                    | C <sub>DL</sub> /C <sub>GL</sub> | C <sub>L</sub> =9pF of<br>crystal<br>oscillation |      | 18      |       | pF         |

$(V_{SS} = 0V)$

#### FEDL610Q461-03

#### ML610Q461/ML610Q462/ML610Q463

### **OPERATING CONDITIONS OF FLASH ROM**

|                       |                  |                              |             | (V <sub>SS</sub> = 0√ |

|-----------------------|------------------|------------------------------|-------------|-----------------------|

| Parameter             | Symbol           | Condition                    | Range       | Unit                  |

| Operating temperature | T <sub>OP</sub>  | At write/erase               | 0 to +40    | °C                    |

| · ·                   | V <sub>DD</sub>  | At write/erase <sup>*1</sup> | 2.75 to 3.6 |                       |

| Operating voltage     | V <sub>DDL</sub> | At write/erase <sup>*1</sup> | 2.5 to 2.75 | V                     |

|                       | V <sub>PP</sub>  | At write/erase <sup>*1</sup> | 7.7 to 8.3  |                       |

| erase/program cycles  | C <sub>EP</sub>  |                              | 80          | cycles                |

| Data retention        | Y <sub>DR</sub>  |                              | 10          | years                 |

<sup>1</sup>: Those voltages must be supplied to V<sub>DDL</sub> pin and V<sub>PP</sub> pin when programming and eraseing Flash ROM. V<sub>PP</sub> pin has an internal pulldown resister.

#### **DC CHARACTERISTICS (1/5)**

$(V_{DD} = 1.25 \text{ to } 3.6 \text{V}, V_{SS} = 0 \text{V}, \text{Ta} = -20 \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise specified})$

| Doromotor                                               | Symbol            | Condition Rating Min. Typ. |           | Rating       |           | Unit         | Measuring |         |

|---------------------------------------------------------|-------------------|----------------------------|-----------|--------------|-----------|--------------|-----------|---------|

| Parameter                                               | Symbol            |                            |           | Min.         | Typ. Max. |              | Unit      | circuit |

|                                                         |                   | V <sub>DD</sub> = 1.25     | Ta = 25°C | Typ.<br>–10% | 500       | Тур.<br>+10% | kU-       |         |

| 500kHz/2MHz RC oscillation                              | £                 | to 3.6V                    | *3        | Тур.<br>–25% | 500       | Тур.<br>+25% | kHz       |         |

| frequency                                               | f <sub>RC</sub>   | V <sub>DD</sub> = 1.80     | Ta = 25°C | Тур.<br>–10% | 2.0       | Тур.<br>+10% |           | MHz     |

|                                                         |                   | to 3.6V                    | *3        | Тур.<br>–25% | 2.0       | Тур.<br>+25% |           |         |

| Low-speed crystal oscillation start time* <sup>2</sup>  | T <sub>XTL</sub>  |                            |           |              | 0.6       | 2            | S         | 1       |

| 500kHz/2MHz RC oscillation<br>start time                | T <sub>RC</sub>   | _                          |           |              |           | 0.3          | μS        |         |

| Low-speed oscillation stop<br>detect time <sup>*1</sup> | T <sub>STOP</sub> |                            | _         |              | 16.4      | 41           | ms        |         |

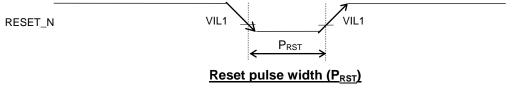

| Reset pulse width                                       | P <sub>RST</sub>  |                            | —         | 200          |           |              |           |         |

| Reset noise elimination<br>pulse width                  | P <sub>NRST</sub> |                            | _         |              |           | 0.3          | μS        |         |

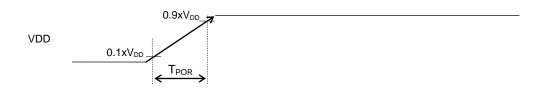

| Power-on reset activation<br>power rise time            | T <sub>POR</sub>  |                            | _         |              | _         | 10           | ms        |         |

\*<sup>1</sup>: When low-speed crystal oscillation stops for a duration more than the low-speed oscillation stop detect time, the system is reset to shift to system reset mode.

\*<sup>2</sup>: Use 32.768KHz Crystal resonator DT-26 (Load capacitance 6pF) (made by KDS:DAISHINKU CORP.) is used  $(C_{GL}=C_{DL}=12pF).$

$*^3$ : Recommended operating temperature (Ta = -20 to +70°C) [Reset pulse width]

[Power-on reset activation power rise time]

#### Power-on reset activation power rise time (T<sub>POR</sub>)

FEDL610Q461-03

#### ML610Q461/ML610Q462/ML610Q463

## **DC CHARACTERISTICS (2/5)**

|                                                       |                         | $(V_{DD} = 1.25 \text{ to } 3.6 \text{V}, \text{V}_{SS})$ | = 0V, Ta | = -20 to · | +70°C, ur | nless othe | rwise specified) |

|-------------------------------------------------------|-------------------------|-----------------------------------------------------------|----------|------------|-----------|------------|------------------|

| Deremeter                                             | Symbol                  | Condition                                                 |          | Rating     |           | Unit       | Measuring        |

| Parameter S                                           | Symbol                  | Condition                                                 | Min.     | Тур.       | Max.      | Unit       | circuit          |

|                                                       | V                       | $f_{OP} = 30k \text{ to } 625kHz$                         | 1.1      | 1.2        | 1.3       |            |                  |

| V <sub>DDL</sub> voltage                              | V <sub>DDL</sub>        | $f_{OP}$ = 30k to 2.5MHz                                  | 1.35     | 1.5        | 1.65      |            |                  |

| V <sub>DDL</sub> temperature deviation * <sup>1</sup> | $\Delta V_{\text{DDL}}$ | $V_{DD} = 3.0V$                                           | _        | -1         |           | mV/°C      | 1                |

| V <sub>DDL</sub> voltage<br>dependency * <sup>1</sup> | $\Delta V_{DDL}$        |                                                           |          | 5          | 20        | mV/V       |                  |

\*<sup>1</sup>:V<sub>DDL</sub> can not exceed V<sub>DD</sub> level. The maximum V<sub>DDL</sub> becomes V<sub>DD</sub> level when the V<sub>DDL</sub> calculated by the temperature deviation and voltage dependency is going to exceed the V<sub>DD</sub> level.

#### ML610Q461/ML610Q462/ML610Q463

#### **DC CHARACTERISTICS (3/5)**

|                   |                       |                                                                                                     |                                                                    | (V <sub>DD</sub> = | = 3.0V, V | $V_{\rm SS} = 0V$ | , Ta = −2 | 0 to +70°C) |   |

|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------|-----------|-------------------|-----------|-------------|---|

| Parameter         | Sumbol                | Condition                                                                                           |                                                                    |                    | Rating    |                   |           | Measuring   |   |

| Parameter         | Symbol                | Condition                                                                                           | Condition                                                          |                    | Тур.      | Max.              | Unit      | circuit     |   |

| Supply current 1  | IDD1                  | CPU: In STOP state.<br>Low-speed/high-speed                                                         | Ta= 25°C                                                           | _                  | 0.4       | 0.8               | μA        |             |   |

|                   |                       | RC500kHz/2MHz oscillation: stopped.                                                                 | *5                                                                 | _                  |           | 8                 | μ         |             |   |

| Supply current 2  | IDD2                  | CPU: In HALT state (LTBC and WDT are Operating). <sup>*3*4</sup><br>High-speed 500kHz/2MHz          | Ta= 25°C                                                           | _                  | 0.9       | 1.8               | μA        |             |   |

|                   |                       | oscillation: Stopped.<br>LCD and BIAS circuits: Operating. * <sup>6</sup>                           | *5                                                                 |                    |           | 9                 | μ         |             |   |

| Currate surrout 2 |                       |                                                                                                     | CPU: In 32.768kHz operating<br>state.* <sup>1</sup> * <sup>3</sup> | Ta= 25°C           | _         | 5                 | 8         | •           | 1 |

| Supply current 3  | IDD3                  | High-speed 500kHz/2MHz<br>oscillation: Stopped.<br>LCD and BIAS circuits: Operating. * <sup>2</sup> | *2                                                                 |                    |           | 15                | μA        |             |   |

| Supply current    | IDD4-1                | CPU: In RC 500kHz operating state.                                                                  | Ta= 25°C                                                           |                    | 70        | 100               | •         |             |   |

| 4-1               | IDD4-1                | LCD and BIAS circuits: Operating. * <sup>2</sup>                                                    | *5                                                                 |                    |           | 120               | μA        |             |   |

| Supply current    | Supply current IDD4-2 | CPU: In RC 2MHz operating state.                                                                    | Ta= 25°C                                                           | _                  | 280       | 350               | μA        |             |   |

| 4-2 IDD4          |                       | LCD and BIAS circuits: Operating. * <sup>2</sup>                                                    |                                                                    |                    |           | 400               | h         |             |   |

\*<sup>1</sup>: When the CPU operating rate is 100% (No HALT state).

\*<sup>2</sup>: All SEGs: off waveform, No LCD panel load, 1/3 bias, 1/3 duty, Frame frequency: Approx. 64 Hz, Bias voltage multiplying clock: 1/128 LSCLK (256Hz) \*<sup>3</sup> : Use 32.768KHz Crystal resonator DT-26 (Load capacitance 6pF) (made by KDS:DAISHINKU CORP.) is used (C<sub>GL</sub>=C<sub>DL</sub>=6pF)

\*<sup>4</sup> : Significant bits of BLKCON0~BLKCON4 registers except DLCD bit on BLKCON4 are all "1". \*<sup>5</sup> : Recommended operating temperature (Ta = -20 to  $+70^{\circ}$ C)

\*6: LCD Stop mode, 1/3 bias, Bias voltage multiplying clock: 1/128 LSCLK (256Hz)

#### FEDL610Q461-03

#### ML610Q461/ML610Q462/ML610Q463

### DC CHARACTERISTICS (4/5)

| Parameter                                                           | Symbol | ymbol Condition                                                                      |                                  | Rating | 1                       | Unit | Measuring |  |

|---------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------|----------------------------------|--------|-------------------------|------|-----------|--|

| randineter                                                          | Symbol | Condition                                                                            | Min.                             | Тур.   | Max.                    | Unit | circuit   |  |

| Output voltage 1<br>(P20–P21 Nch                                    | VOH1   | IOH1 = $-0.5$ mA, V <sub>DD</sub> = 1.8 to 3.6V                                      | V <sub>DD</sub><br>-0.5          |        |                         |      |           |  |

| open drain mode<br>is Not selected)                                 | VOITI  | IOH1 = -0.03mA, $V_{DD}$ = 1.25 to 3.6V $V_{DD}$ -0.3                                |                                  |        |                         |      |           |  |

| (P30–P35)<br>(P40–P47)                                              |        | IOL1 = +0.5mA, V <sub>DD</sub> = 1.8 to 3.6V                                         |                                  |        | 0.5                     |      |           |  |

| (P60–P67)                                                           | VOL1   | $IOL1 = +0.1 mA$ , $V_{DD} = 1.25 to 3.6 V$                                          |                                  |        | 0.3                     |      |           |  |

| Output voltage 2<br>(P20–P21 Nch<br>open drain mode is<br>selected) | VOL2   | IOL2 = +5mA, V <sub>DD</sub> = 1.8 to 3.6V                                           |                                  |        | 0.5                     |      |           |  |

| -                                                                   | VOH3   | IOH4 = -0.05mA, VL1=1.2V                                                             | V <sub>L3</sub><br>-0.2          |        |                         | V    | 2         |  |

| Output voltage 3                                                    | VOML3  | IOMH4 = +0.05mA, VL1=1.2V                                                            |                                  |        | V <sub>L2</sub><br>+0.2 |      |           |  |

| (COM0 to 3)<br>(SEG8 to 23) <sup>*1</sup>                           | VOML3S | IOM4S = -0.05mA, VL1=1.2V                                                            | V <sub>L2</sub><br>-0.2          |        |                         |      |           |  |

| (SEG8 to 27) <sup>*2</sup><br>(SEG8 to 31) <sup>*3</sup>            | VOLM3  | IOML4 = +0.05mA, VL1=1.2V                                                            |                                  |        | V <sub>L1</sub><br>+0.2 |      |           |  |

|                                                                     | VOLM3S | IOML4S = -0.05mA, VL1=1.2V                                                           | V <sub>L1</sub><br>-0.2          |        | —                       |      |           |  |

|                                                                     | VOL3   | IOL4 = +0.05mA, VL1=1.2V                                                             |                                  |        | 0.2                     |      |           |  |

| Output leakage<br>(P20–P21)<br>(P30–P35)                            | IOOH   | VOH = $V_{DD}$ (in high-impedance state)                                             |                                  |        | 1                       | μA   | 3         |  |

| (P40–P47)<br>(P60–P67)                                              | IOOL   | VOL = $V_{SS}$ (in high-impedance state)                                             | (in high-impedance state) -1 — — |        |                         |      |           |  |

| Input current 1                                                     | IIH1   | VIH1 = V <sub>DD</sub>                                                               | 0                                |        | 1                       |      |           |  |

| (RESET_N)<br>(TEST1_N)                                              | IIL1   | VIL1 = V <sub>SS</sub>                                                               | -600                             | -300   | -2                      |      |           |  |

| Input current 2                                                     | IIH2   | VIH1 = V <sub>DD</sub>                                                               | 2                                | 300    | 600                     |      |           |  |

| (TEST0)                                                             | IIL2   | VIL1 = V <sub>ss</sub>                                                               | -1                               |        |                         |      |           |  |

|                                                                     |        | $VIH3 = V_{DD}$ , $V_{DD} = 1.8$ to 3.6V<br>(when pulled-down)                       | 2                                | 30     | 200                     |      |           |  |

| Input current 3                                                     | IIH3   | VIH3 = V <sub>DD</sub> ,V <sub>DD</sub> = 1.25 to 3.6V<br>(when pulled-down)         |                                  |        |                         | μΑ   | 4         |  |

| (P00-P04)<br>(P30-P35)                                              |        | $UIL3 = V_{SS}, V_{DD} = 1.8 \text{ to } 3.6V$ (when pulled-up) -200 -30 -30 -30 -30 |                                  | -30    | -2                      |      |           |  |

| (P40-P47)                                                           | IIL3   |                                                                                      |                                  | -0.01  |                         |      |           |  |

|                                                                     | IIH3Z  | VIH3 = $V_{DD}$ (in high-impedance state)                                            |                                  |        | 1                       |      |           |  |

| -                                                                   | IIL3Z  | VIL3 = $V_{SS}$ (in high-impedance state)                                            | -1                               |        |                         |      |           |  |

\*1: Characteristics for ML610Q461.

\*2: Characteristics for ML610Q462.

\*3: Characteristics for ML610Q463.

#### FEDL610Q461-03

### ML610Q461/ML610Q462/ML610Q463

# DC CHARACTERISTICS (5/5)

|                                                                 |              | $(V_{DD} = 1.25 \text{ to } 3.6 \text{V}, \text{V}_{SS})$ | = 0V, Ta                | = -20 to | +70°C, u                | nless oth | erwise specified) |  |

|-----------------------------------------------------------------|--------------|-----------------------------------------------------------|-------------------------|----------|-------------------------|-----------|-------------------|--|

| Devenueter                                                      | Ci uma la al | Condition                                                 |                         | Rating   | 1                       | l lait    | Measuring         |  |

| Parameter                                                       | Symbol       | Condition                                                 | Min.                    | Тур.     | Max.                    | Unit      | circuit           |  |

| Input voltage 1<br>(RESET_N)<br>(TEST0,<br>TEST1_N)             | VIH1         | _                                                         | 0.7<br>×V <sub>DD</sub> |          | V <sub>DD</sub>         |           | _                 |  |

| (P00–P04)<br>(P30–P35)                                          | VIL1         | V <sub>DD</sub> = 1.8 to 3.6V                             | 0 —                     |          | 0.3<br>×V <sub>DD</sub> | V         | 5                 |  |

| (P40–P47)                                                       | VILI         | $V_{DD} = 1.25$ to 3.6V                                   | 0                       | —        | 0.2<br>×V <sub>DD</sub> |           |                   |  |

| Input pin<br>capacitance<br>(P00–P04)<br>(P30–P35)<br>(P40–P47) | CIN          | f = 10kHz<br>$V_{rms} = 50mV$<br>$Ta = 25^{\circ}C$       |                         |          | 5                       | pF        |                   |  |

#### FEDL610Q461-03

# LAPIS Semiconductor Co., Ltd.

#### ML610Q461/ML610Q462/ML610Q463

## **MEASURING CIRCUITS**

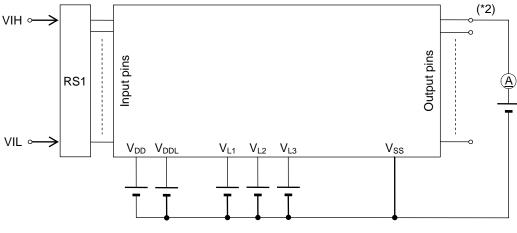

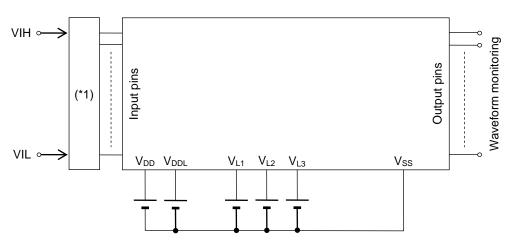

### **MEASURING CIRCUIT 1**

**MEASURING CIRCUIT 2**

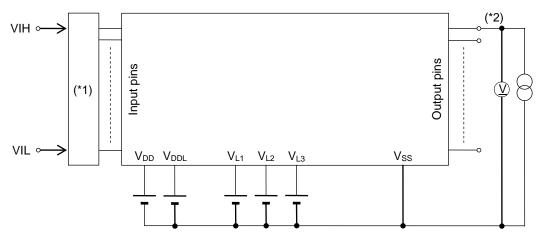

(\*1) Input logic circuit to determine the specified measuring conditions.(\*2) Measured at the specified output pins.

#### ML610Q461/ML610Q462/ML610Q463

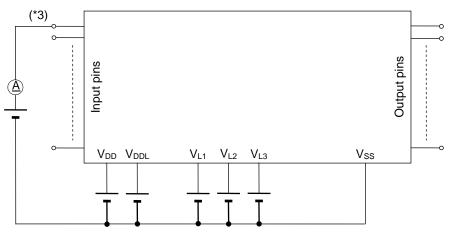

### **MEASURING CIRCUIT 3**

\*1: Input logic circuit to determine the specified measuring conditions.\*2: Measured at the specified output pins.

### **MEASURING CIRCUIT 4**

\*3: Measured at the specified output pins.

### **MEASURING CIRCUIT 5**

\*1: Input logic circuit to determine the specified measuring conditions.

#### -

FEDL610Q461-03

#### ML610Q461/ML610Q462/ML610Q463

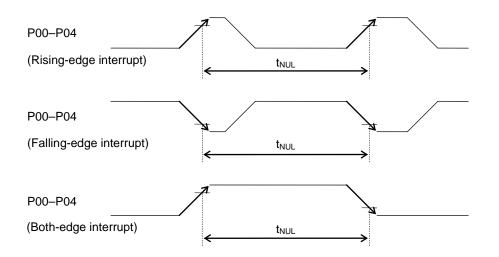

### AC CHARACTERISTICS (External Interrupt)

|                                   | (V <sub>D</sub>  | <sub>D</sub> = 1.25 to 3.6V, V <sub>SS</sub> = 0V, Ta = –20 to +               | -70°C, ur | nless oth | erwise sp | ecified) |

|-----------------------------------|------------------|--------------------------------------------------------------------------------|-----------|-----------|-----------|----------|

| Deremeter                         | Symbol Condition |                                                                                |           | Rating    |           | Linit    |

| Parameter                         |                  |                                                                                | Min.      | Тур.      | Max.      | Unit     |

| External interrupt disable period | T <sub>NUL</sub> | Interrupt: Enabled (MIE = 1),<br>CPU: NOP operation<br>System clock: 32.768kHz | 76.8      |           | 106.8     | μs       |

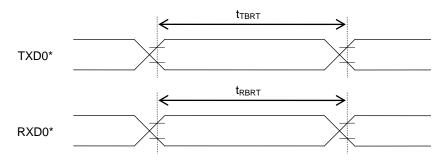

### **AC CHARACTERISTICS (Serial Port)**

|                    | (V <sub>D</sub>   | $_{\rm D}$ = 1.25 to 3.6V, V <sub>SS</sub> = 0V, Ta | = -20 to +7              | 0°C, unless       | otherwise sp             | pecified) |  |

|--------------------|-------------------|-----------------------------------------------------|--------------------------|-------------------|--------------------------|-----------|--|

| Deveryeter         | Currente e l      | Condition                                           |                          |                   | 1.1                      |           |  |

| Parameter          | Symbol            | Condition                                           | Min.                     | Тур.              | Max.                     | Unit      |  |

| Transmit baud rate | t <sub>TBRT</sub> |                                                     |                          | BRT* <sup>1</sup> |                          | s         |  |

| Receive baud rate  | t <sub>RBRT</sub> |                                                     | BRT* <sup>1</sup><br>–3% | BRT* <sup>1</sup> | BRT* <sup>1</sup><br>+3% | S         |  |

\*1: Baud rate period (including the error of the clock frequency selected) set with the serial port baud rate register (SIOBRTL,H) and the serial port mode register 0 (SIOMOD0).

\*: Indicates the secondary function of the port.

FEDL610Q461-03

#### ML610Q461/ML610Q462/ML610Q463

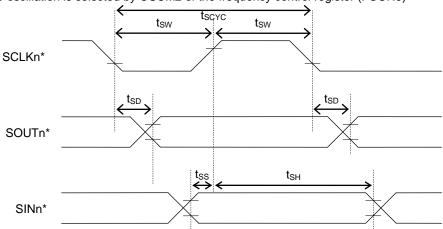

#### AC CHARACTERISTICS (Synchronous Serial Port)

$(V_{DD} = 1.25 \text{ to } 3.6\text{V}, V_{SS} = 0\text{V}, \text{Ta} = -20 \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise specified})$

| Deremeter                              | Cumbel.         | under a Constituer                                                                                   |                             | Rating                      |                             |      |  |

|----------------------------------------|-----------------|------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|------|--|

| Parameter                              | Symbol          | Condition                                                                                            | Min.                        | Тур.                        | Max.                        | Unit |  |

| SCLKn input cycle                      |                 | When RC oscillation is 500kHz $*^2$ (V <sub>DD</sub> = 1.25 to 3.6V)                                 | 10                          |                             |                             |      |  |

| (slave mode)                           | tscyc           | When RC oscillation is 2MHz $*^3$ (V <sub>DD</sub> = 1.8 to 3.6V)                                    | 2                           |                             |                             | μS   |  |

| SCLKn output cycle<br>(master mode)    | tscyc           |                                                                                                      | _                           | SCLKn*1                     |                             | S    |  |

| SCLKn input pulse width                |                 | When RC oscillation is 500kHz $*^2$ (V <sub>DD</sub> = 1.25 to 3.6V)                                 | 4                           |                             |                             |      |  |

| (slave mode)                           | t <sub>SW</sub> | When RC oscillation is 2MHz $*^3$ (V <sub>DD</sub> = 1.8 to 3.6V)                                    | 04                          |                             |                             | μS   |  |

| SCLKn output pulse width (master mode) | t <sub>SW</sub> |                                                                                                      | SCLKn* <sup>1</sup><br>×0.4 | SCLKn* <sup>1</sup><br>×0.5 | SCLKn* <sup>1</sup><br>×0.6 | s    |  |

| SOUTn output delay time                |                 | When RC oscillation is 500kHz<br>* <sup>2</sup> (V <sub>DD</sub> = 1.25 to 3.6V)<br>output load 10pF |                             | _                           | 500                         |      |  |

| (slave mode)                           | t <sub>SD</sub> | When RC oscillation is 2MHz<br>* <sup>3</sup> ( $V_{DD}$ = 1.8 to 3.6V)<br>output load 10pF          |                             |                             | 240                         | ns   |  |

| SOUTn output delay time                |                 | When RC oscillation is 500kHz<br>* <sup>2</sup> (V <sub>DD</sub> = 1.25 to 3.6V)<br>output load 10pF |                             |                             | 500                         |      |  |

| (master mode)                          | t <sub>SD</sub> | When RC oscillation is 2MHz<br>* <sup>3</sup> ( $V_{DD}$ = 1.8 to 3.6V)<br>output load 10pF          |                             |                             | 240                         | ns   |  |

| SINn input setup time<br>(slave mode)  | t <sub>ss</sub> |                                                                                                      | 80                          |                             |                             | ns   |  |

| SINn input setup time                  |                 | When RC oscillation is 500kHz $*^2$ (V <sub>DD</sub> = 1.25 to 3.6V)                                 | 500                         |                             |                             |      |  |