# ML7396A/B/E

### Sub GHz band short range wireless transceiver IC

### ■Overview

The ML7396 family (ML7396A (915MHz band), ML7396B (920MHz band), and ML7396E (868MHz band)) are ICs for transmitting/receiving data which integrate the RF, IF, MODEM and HOST interface sections into one chip for the specified low power radio communication. The ML7396 family is used for FCC PART15, ARIB STD-108(specified low-power radio station, 920MHz-band telemeter, telecontrol and data transmission radio equipment), ETSI EN 300 220 compliant radio station, and uses a packet transmission function of IEEE802.15.4d and IEEE802.15.4g.

### ■Features

- Compliant to ARIB STD T-108 (ML7396B)

- Compliant to FCC Part15 (ML7396A)

- Compliant to ETSI EN 300-220 (ML7396E)

- High resolution modulation by using fractional-N PLL direct modulation.

- Modulation: GFSK / GMSK, FSK / MSK

(MSK is FSK transmission of modulation index: m=0.5)

- Data rates: 10 / 20 / 40 / 50 / 100 / 150 / 200 kbps and 400 kbps (option)

- Data coding: NRZ and Manchester codes

- Programable channel filter suited to data rates

- Programmable frequency deviation function

- TX and RX data inverse function

- 36MHz oscillator circuit

- TCXO direct inputs available

- Oscillator capacitance fine tuning function

- Frequency fine tuning function (using fractional-N PLL)

- Synchronous serial peripheral interface (SPI)

- On chip TX PA (20mW/10mW/1mW selectable)

- External TX PA control function

- RSSI indicator and threshold judgement function

- AFC function

- Antenna diversity function

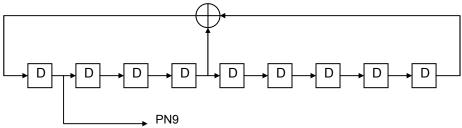

- Test pattern generator (PN9, CW, 01 pattern, all"1", all"0")

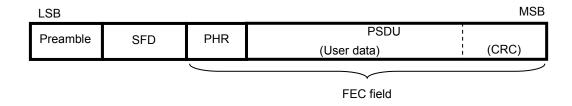

- FEC function

- CRC32 (Note: This function is not compliant to IEEE802.15.4g.)

- IEEE802.15.4d/g support

- o Two 256-byte FIFOs (TX/RX common use)

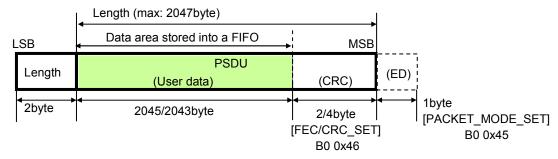

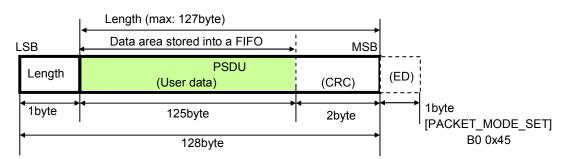

- o Max packet length 2047 byte (IEEE802.15.4g mode)

- o RX Preamble pattern detection function (Programmable between 1 to 15 byte)

- o Programmable TX preamble length (Max 255 byte)

- o SFD generation and detection function (Max 4 byte)

- o Programmable CRC function (CRC32, CRC16-IBM, CRC16, CRC8 or no-CRC)

- Whitening function

- Address filtering function

- o Automatic Acknowledge (Ack TX or RX) function

- o FEC function (IEEE802.15.4g mode)

- Note; Interleaving mode is not compliant to IEEE802.15.4g.

ML7396A/B/E

• Supply voltage: 1.8 to 3.6V (TX power 1mW mode)

2.3 to 3.6V (TX power 10mW mode)

2.6 to 3.6V (TX power 20mW mode)

• Operating temperature: -40 to +85 °C

• Current consumption (920MHz)

Sleep mode 0.6 µA (Typ.) (registor value retention)

Idle mode

1.4mA (Typ.)

TX

20mW

32 mA (Typ.)

10mW

24 mA (Typ.)

1mW

13 mA (Typ.)

RX 15 mA (Typ.) (@100kbps)

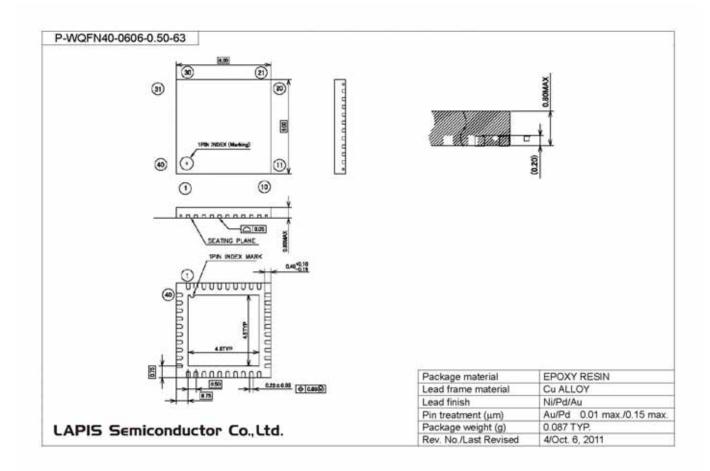

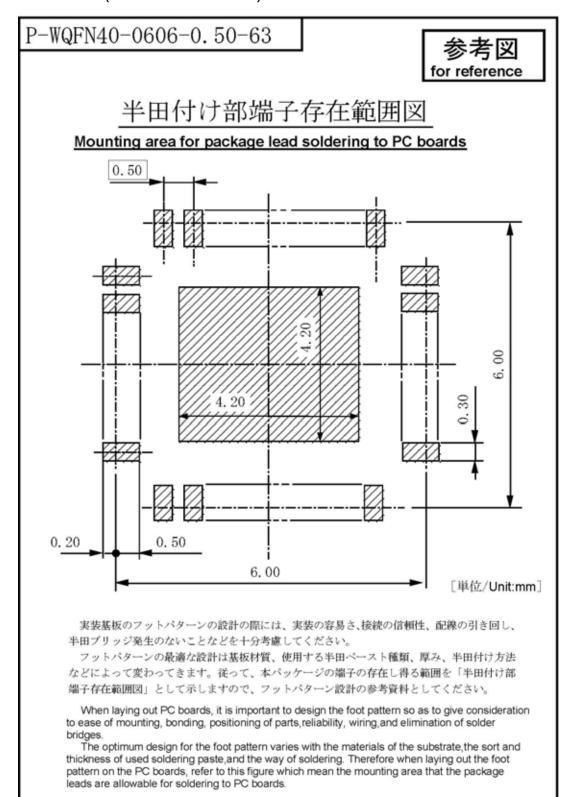

• Package

40 pin WQFN P-WQFN40-0606-0.50

Pb free, RoHS compliant

# ■Description Convention

1) Numbers description

'0xnn' indicates hexa decimal. '0bnn' indicates binary.

Example: 0x11 = 17(decimal), 0b11 = 3(decimal)

2) Registers description

[<register name>: B<Bank No> <register address>] register

Example: [CLK\_SET:B0 0x02] register

Register name: CLK\_SET

Bank No: 0

Register address: 0x02

3) Bir name description

<br/><br/>

<br/>

<

Example: RATE[2:0] ([DATA SET:B0 0x47(2-0)])

Bit name: RATE[2:0] Register name: DATA SET

Bank No: 0

Register address: 0x47 Bit location: bit2 to bit0

4) In this document

"TX" stands for transmittion.

"RX" stands for reception.

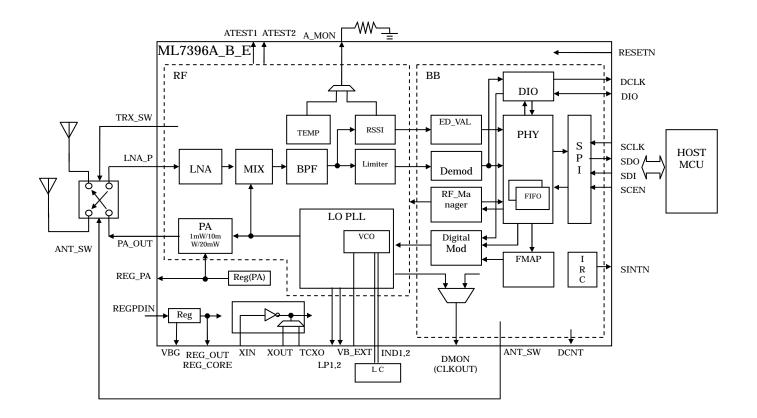

# ■Block Diagram

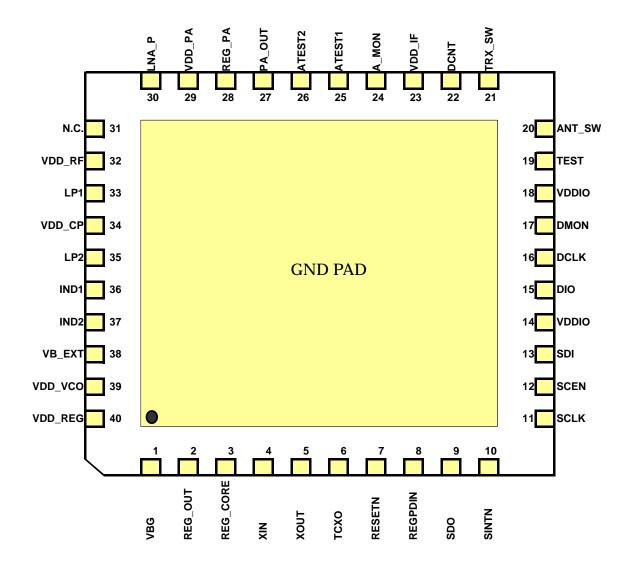

# ■PIN Configuration

# 40 Pin WQFN

NOTE) GND pad in the middle of the IC is reverse side (name: GND PAD)

# **■PIN Definitions**

# Symbols

$\begin{array}{lll} I_{RF} & : RF \ input \\ O_{RF} & : RF \ output \\ I_{A} & : Analog \ input \\ I_{OS} & : Oscillator \ input \\ O_{OS} & : Oscillator \ output \\ I & : Digital \ input \\ O & : Digital \ output \\ I/O & : Digital \ inout \\ \end{array}$

Is : Schmitt Trigger input

# •RF and Analog pins

| Pin<br>No | Pin name | Reset<br>state | I/O      | Active<br>Level | Detail function                                            |

|-----------|----------|----------------|----------|-----------------|------------------------------------------------------------|

| 30        | LNA_P    | I              | $I_{RF}$ | -               | RF antenna input                                           |

| 27        | PA_OUT   | О              | $O_{RF}$ | -               | RF antenna output                                          |

| 36        | IND1     | -              | -        | -               | Pin for VCO inductor                                       |

| 37        | IND2     | -              | -        | -               | Pin for VCO inductor                                       |

| 33        | LP1      | -              | -        | -               | Pin for PLL loop filter                                    |

| 38        | VB_EXT   | -              | -        | -               | Pin for smoothing capacitor for internal bias              |

| 25        | ATEST1   | Hi-Z           | $O_{RF}$ | -               | Test pin for analog circuit. *Left open when in normal use |

| 26        | ATEST2   | Hi-Z           | $O_{RF}$ | -               | Test pin for analog circuit. *Left open when in normal use |

| 24        | A_MON    | Hi-Z           | $O_{RF}$ | -               | Analog monitor pin (*1)                                    |

# [Description]

<sup>\*1</sup> Analog monitor signal can be configured by [RSSI/TEMP\_OUT:B1 0x03] register, no signal assigned as default condition.

# PIN DEFINITION(continued)

# •SPI interface pins

| Pin<br>No | Pin name | Reset<br>state | I/O | Active<br>Level | Detail function                               |

|-----------|----------|----------------|-----|-----------------|-----------------------------------------------|

| 9         | SDO      | O/L            | О   | H or L          | SPI data output                               |

| 13        | SDI      | I              | Is  | H or L          | SPI data input                                |

| 11        | SCLK     | I              | Is  | P or N          | SPI clock input                               |

| 12        | SCEN     | I              | Is  | L               | SPI chip enable L: enable H: disable          |

| 10        | SINTN    | О/Н            | О   | L               | SPI interrupt output L: interrupt occurs H: - |

# •DIO interface pins

| Pin No | Pin name | Reset state | I/O | Active<br>Level | Detail function       |

|--------|----------|-------------|-----|-----------------|-----------------------|

| 15     | DIO      | O/L         | I/O | H or L          | DIO data input/output |

| 16     | DCLK     | O/L         | О   | P or N          | DIO clock output      |

# •Regulator pins

| Pin<br>No | Pin name | Reset<br>state | I/O | Active<br>Level | Detail function                                                                         |

|-----------|----------|----------------|-----|-----------------|-----------------------------------------------------------------------------------------|

| 2         | REG_OUT  | -              | -   | -               | Regulator output (typ.1.5V) (Cap 10uF) Note: This pin will output 0V in the sleep state |

| 3         | REG_CORE | -              | -   | -               | Monitor pin for power supply to digital core(typ.1.5V) (Cap 10uF)                       |

| 1         | VBG      | -              | -   | -               | Pin for decoupling capacitor pin (Cap 0.1uF)                                            |

| 8         | REGPDIN  | I              | I   | Н               | Power down pin for regulator * Fix to "L" for normal use                                |

| 28        | REG_PA   | -              | -   | -               | Regulator output for PA block Note: This pin will output 0V in the sleep state          |

### PIN DEFINITION(continued)

### Miscellaneous pins

| Pin<br>No | Pin name | Reset<br>state | I/O   | Active<br>Level | Detail function                                                                                                                 |

|-----------|----------|----------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| 7         | RESETN   | I              | Is    | L               | Hardware reset L: Hardware reset enable H: normal operation                                                                     |

| 4         | XIN      | I              | Ios   | P or N          | 36MHz crystal pin1 *Fixed to GND in case of using external clock                                                                |

| 5         | XOUT     | О              | Oos   | P or N          | 36MHzcristal pin2 *Fixed to GND in case of using external clock                                                                 |

| 6         | TCXO     | I              | $I_A$ | -               | External clock (TCXO) input pin.  *Fixed to GND in case of using crystal oscillator                                             |

| 20        | ANT_SW   | O/L            | О     | H or L or<br>OD | Diversity control signal                                                                                                        |

| 21        | TRX_SW   | O/L            | О     | H or L or<br>OD | TX-RX switch signal                                                                                                             |

| 19        | TEST     | I              | I     | Н               | Test mode input Fixed to "L" for normal use                                                                                     |

| 17        | DMON*1   | О              | О     | Н               | Digital monitor pin Primary function: Clock output (6MHz) Secondary function: PLL_LD output Third function: FIFO trigger output |

| 22        | DCNT     | O/L            | 0     | H or L or<br>OD | External TX PA control signal                                                                                                   |

| 31,35     | N.C.     | -              | -     | -               | Non connection                                                                                                                  |

### [Description]

### Configuration of DMON output

| <b>Function Name</b> | Configuration register name | Address | Bit position (bit symbol) |  |  |  |  |

|----------------------|-----------------------------|---------|---------------------------|--|--|--|--|

| CLK output           | CLK_SET                     | B0 0x02 | bit4 (CLKOUT_EN)          |  |  |  |  |

| PLL_LD output        | PLL_MON/DIO_SEL             | B0 0x69 | bit4 (PLL_LD)             |  |  |  |  |

| FIFO trigger output  | CRC_AREA/FIFO_TRG           | B0 0x77 | bit0 (FIFO_TRG_EN)        |  |  |  |  |

<sup>\*1</sup> Function of DMON pin can be selected by following condition. Clock output as a default.

If clock output is not used, please select another function. Please refer to each register description for more details.

Primary function will have higher priority when multiple function are configured simultaneously.

### Power supply pins

| Pin<br>No | Pin name | Reset<br>state | I/O | Active<br>Level | Detail function                                                                  |

|-----------|----------|----------------|-----|-----------------|----------------------------------------------------------------------------------|

| 14,18     | VDDIO    | -/-            | PWR | -               | Power supply for digital IOs<br>(Input voltage: 1.8V to 3.3V)                    |

| 40        | VDD_REG  | -/-            | PWR | -               | Power supply for regulator input (Input voltage: 1.8V to 3.3V)                   |

| 29        | VDD_PA   | -/-            | PWR | -               | Power supply for PA block<br>(Input voltage: 1.8V to.3.3V, depending on TX mode) |

| 32        | VDD_RF   | -/-            | PWR | -               | Power supply for RF blocks (REG_OUT is connected, typ.1.5V)                      |

| 23        | VDD_IF   | -/-            | PWR | -               | Power supply for IF block (REG_OUT is connected, typ.1.5V)                       |

| 34        | VDD_CP   | -/-            | PWR | -               | Power supply for charge pump (REG_OUT is connected, typ.1.5V)                    |

| 39        | VDD_VCO  | -/-            | PWR | -               | Power supply for VCO (REG_OUT is connected, typ.1.5V)                            |

| EL        | -        | -/-            | GND | -               | GND PAD                                                                          |

# Unused pins

Unused pins treatments are as follows:

| Pin Name | Pin number | Recommended treatment                   |

|----------|------------|-----------------------------------------|

| XIN      | 4          | Fixed to GND (When TCXO is used)        |

| XOUT     | 5          | Fixed to GND (When TCXO is used)        |

| TCXO     | 6          | Fixed to GND (When crystal OSC is used) |

| ATEST1   | 25         | Left OPEN                               |

| ATEST2   | 26         | Left OPEN                               |

| A_MON    | 24         | Left OPEN                               |

| ANT_SW   | 20         | Left OPEN                               |

| DMON     | 17         | Left OPEN *1                            |

| DCNT     | 22         | Left OPEN                               |

<sup>\*1</sup> If not using DMON, it is necessary to stop clock out (default output on DMON) by CLKOUT\_EN ([CLK\_SET:B0 0x02(4)]). Left open with enableing clock out causes the performance down on RX sensitivity.

Note: If input pins are high-impedence state and leave open, excess current could be drawn. Care must be taken that unused input pins and unused I/O pins should not be left open.

# **■**Electrical Characteristics

# • Absolute maximum ratings

| Item                        | Symbol              | Condition       | Rating                         | Unit |

|-----------------------------|---------------------|-----------------|--------------------------------|------|

| Power Supply (I/O) (*1)     | $V_{\mathrm{DDIO}}$ |                 | -0.3 to +4.6                   | V    |

| Power Supply (RF) (*2)      | $V_{ m DDRF}$       |                 | -0.3 to +2.0                   | V    |

| Digital Input Voltage       | $V_{\mathrm{DIN}}$  |                 | -0.3 to V <sub>DDIO</sub> +0.3 | V    |

| RF Input Voltage            | V <sub>RFIN</sub>   |                 | -1.0 to +2.0                   | V    |

| Analog Input Voltage        | V <sub>AIN</sub>    |                 | -0.3 to V <sub>DDIO</sub> +0.3 | V    |

| Analog Input Voltage2 (*3)  | V <sub>AIN2</sub>   |                 | -0.3 to V <sub>DDRF</sub> +0.3 | V    |

| TCXO Input Voltage          | VTCXO               |                 | -0.3 to +1.75                  | V    |

| Digital Output Voltage      | $V_{DO}$            | Ta=-40 to 85 °C | -0.3 to V <sub>DDIO</sub> +0.3 | V    |

| RF Output Voltage           | $V_{RFO}$           | GND=0V          | -0.3 to V <sub>DDRF</sub> +1.9 | V    |

| Analog Output Voltage       | $V_{AO}$            |                 | -0.3 to V <sub>DDIO</sub> +0.3 | V    |

| Analog Output Voltage2 (*4) | $V_{AO2}$           |                 | -0.3 to V <sub>DDRF</sub> +0.3 | V    |

| Digital Input Current       | $I_{DI}$            |                 | -10 to +10                     | mA   |

| RF Input Current            | $I_{RF}$            |                 | -2 to +2                       | mA   |

| Analog Input Current        | $I_{AI}$            |                 | -2 to +2                       | mA   |

| Analog Input Current2 (*3)  | $I_{AI2}$           |                 | -2 to +2                       | mA   |

| TCXO Input Current          | ITCXO               |                 | -2 to +2                       | mA   |

| Digital Output Current      | $I_{DO}$            |                 | -8 to +8                       | mA   |

| RF Output Current           | $I_{RFO}$           |                 | -2 to +60                      | mA   |

| Analog Output Current       | $I_{AO}$            |                 | -2 to +2                       | mA   |

| Analog Output Current2 (*4) | I <sub>AO2</sub>    |                 | -2 to +2                       | mA   |

| Power Dissipation           | $P_d$               | Ta=+25 °C       | 300                            | mW   |

| Storage Temperature         | $T_{stg}$           | -               | -55 to +150                    | °C   |

<sup>\*1</sup> VDD\_IO, VDD\_REG, VDD\_PA pins \*2 VDD\_RF, VDD\_IF, VDD\_VCO, VDD\_CP pins \*3 XIN, TCXO pins

<sup>\*4</sup> XOUT pin

# • Recommended operating conditions

| Item                                | Symbol              | Conditions                                    | Min            | Тур | Max            | Unit |

|-------------------------------------|---------------------|-----------------------------------------------|----------------|-----|----------------|------|

| Power Supply (I/O)                  | $V_{\mathrm{DDIO}}$ | VDD_IO, VDD_REG pins                          | 1.8            | 3.3 | 3.6            | V    |

|                                     |                     | VDD_PA pin<br>TX power 1mW mode               | 1.8            | 3.3 | 3.6            | V    |

| Power Supply (PA)                   | $V_{ m DDPA}$       | VDD_PA pin<br>TX power 10mW mode              | 2.3            | 3.3 | 3.6            | V    |

|                                     |                     | VDD_PA pin<br>TX power 20mW mode              | 2.6            | 3.3 | 3.6            | V    |

| Power Supply (RF) (*2)              | $ m V_{DDRF}$       | VDD_RF,<br>VDD_IF,<br>VDD_VCO,<br>VDD_CP pins | 1.4            | 1.5 | 1.6            | V    |

| Operating Temperature               | T <sub>a</sub>      | -                                             | -40            | +25 | +85            | °C   |

| Digital Input Rising Time           | $T_{IR}$            | Digital input pins (*1)                       | -              | 1   | 20             | ns   |

| Digital Input Falling Time          | $T_{\mathrm{IF}}$   | Digital Input pins (*1)                       | -              | -   | 20             | ns   |

| Digital Output Loads                | $C_{DL}$            | All Digital Output pins                       | -              | 1   | 20             | pF   |

| Master Clock1 Accuracy<br>(Crystal) | F <sub>MCK1</sub>   | XIN, XOUT pins                                | -20ppm<br>(*3) | 36  | +20ppm<br>(*3) | MHz  |

| Master Clock2 Accuracy (TCXO)       | F <sub>MCK2</sub>   | TCXO pin                                      | -20ppm<br>(*3) | 36  | +20ppm<br>(*3) | MHz  |

| TCXO Input Voltage                  | $V_{TCXO}$          | DC cut                                        | 0.8            | -   | 1.5            | Vpp  |

| SPI clock frequency                 | $F_{SCLK}$          | SCLK pin                                      | 0.032          | 2   | 16             | MHz  |

| SPI clock duty ratio                | $D_{SCLK}$          | SCLK pin                                      | 45             | 50  | 55             | %    |

| RF channel frequency                | $F_{RF}$            | LNA_P,PA_OUT pins                             | 863            | -   | 960            | MHz  |

<sup>\*1</sup> Those pins with symbol I, Is at pin definition section

#### [Note]

Electrical characteristics are in the above recommended operating conditions without special instruction.

<sup>\*2</sup> Use REG\_OUT output of this LSI.

<sup>\*3</sup> It's max.+10ppm and min.-10ppm at 10kbps setting.

### Power consumption

| Item                   | Symbol | Conditions                                 | Min | Typ (*2) | Max     | Unit |

|------------------------|--------|--------------------------------------------|-----|----------|---------|------|

| Power Consumption (*1) | IDD1   | Sleep state<br>(Retaining register values) | -   | 0.6      | 3.0(*3) | μΑ   |

|                        | IDD2   | Idle state                                 | -   | 1.4      | 3.0     | mA   |

|                        | IDD3   | RF RX state (*4)                           | -   | 15.0     | 20.0    | mA   |

|                        | IDD4   | RF TX state (1mW) (*4)                     | -   | 13.0     | 20.0    | mA   |

|                        | IDD5   | RF TX state (10mW) (*4)                    | -   | 24.0     | 35.0    | mA   |

|                        | IDD6   | RF TX state (20mW) (*4)                    | -   | 32.0     | 43.0    | mA   |

- \*1 Power consumption is sum of current consumption of all power supply pins

- \*2 "Typ" value is centre value under condition of VDDIO=3.3V, 25 °C.

- \*3 This "Max" value is under condition of 25 °C. Other "Max" values are defind under recommended operating coditions.

- \*4 Current consumption when the data rate is 100kbps and the RF frequency is 920MHz.

<sup>\*</sup> Following "Typ" value is not guaranteed value studied variation of IC but typical centre value.

# •DC characteristics

| Item                                                                                                                                                              | Symbol   | Conditions                         | Min                         | Typ (*2) | Max                                                                                                                                                                                                              | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------|-----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Walter Land High                                                                                                                                                  | VIH1     | Digital input/inout pins           | V <sub>DDIO</sub><br>* 0.75 | -        | $V_{\mathrm{DDIO}}$                                                                                                                                                                                              | V    |

| Voltage Input High                                                                                                                                                | VIH2     | XIN pin                            | V <sub>DDRF</sub><br>*0.9   | -        | $V_{ m DDRF}$                                                                                                                                                                                                    | V    |

| Voltage Input Low                                                                                                                                                 | VIL1     | Digital input/inout pins           | 0                           | -        | V <sub>DDIO</sub><br>*0.18                                                                                                                                                                                       | V    |

| Voltage input Low                                                                                                                                                 | VIL2     | XIN pin                            | 0                           | -        | $V_{ m DDIO}$ $V_{ m DDRF}$ $V_{ m DDIO}$                                                                                                                                                                        | V    |

| Schmitt trigger<br>Threshold High level                                                                                                                           | VT+      | RESETN pin<br>SDI, SCLK, SCEN pins | -                           | 1.2      | V <sub>DDIO</sub><br>*0.75                                                                                                                                                                                       | V    |

| Schmitt Trigger<br>Threshold Low level                                                                                                                            | VT-      | ESETN pin<br>SDI, SCLK, SCEN pins  | V <sub>DDIO</sub><br>*0.18  | 0.8      | -                                                                                                                                                                                                                | V    |

|                                                                                                                                                                   | IIH1     | Digital input/inout pins           | -1                          | -        | 1                                                                                                                                                                                                                | μΑ   |

| Input Leakage Current                                                                                                                                             | IIH2     | XIN pin                            | -0.3                        | -        | 0.3                                                                                                                                                                                                              | μА   |

|                                                                                                                                                                   | IIL1     | Digital input/inout pins           | -1                          | -        | 1                                                                                                                                                                                                                | μА   |

|                                                                                                                                                                   | IIL2     | XIN pin                            | -0.3                        | -        | V <sub>DDRF</sub> V <sub>DDIO</sub> *0.18 V <sub>DDRF</sub> *0.1 V <sub>DDRF</sub> *0.1 V <sub>DDIO</sub> *0.75  -  1                                                                                            | μΑ   |

| Tri-state Output Leakage                                                                                                                                          | IOZH1    | Digital inout pins                 | -1                          | -        | 1                                                                                                                                                                                                                | μА   |

| Current                                                                                                                                                           | IOZL1    | Digital inout pins                 | -1                          | -        | 1                                                                                                                                                                                                                | μΑ   |

| Voltage Output Level H                                                                                                                                            | VOH      | IOH=-4mA /-2mA (*1)                | V <sub>DDIO</sub><br>*0.8   | -        | $V_{\mathrm{DDIO}}$                                                                                                                                                                                              | V    |

| Voltage Output Level L                                                                                                                                            | VOL      | IOL=4mA /2mA (*1)                  | 0                           | -        | 0.3                                                                                                                                                                                                              | V    |

| Regulator output                                                                                                                                                  | REG_CORE | Sleep state                        | 0.95                        | 1.3      | 1.65                                                                                                                                                                                                             | V    |

| Voltage                                                                                                                                                           | (*2)     | Other states                       | 1.40                        | 1.5      | - V <sub>DDRF</sub> - V <sub>DDIO</sub> *0.18 - V <sub>DDIO</sub> *0.18 - V <sub>DDRF</sub> *0.1 1.2 V <sub>DDIO</sub> *0.75 0.8 - 1 - 0.3 - 1 - 0.3 - 1 - V <sub>DDIO</sub> - 0.3 1.3 1.65 1.5 1.60 6 - 9 - 9 9 | V    |

|                                                                                                                                                                   | CIN      | Input pins                         | -                           | 6        | -                                                                                                                                                                                                                | pF   |

| Threshold High level Schmitt Trigger Threshold Low level  Input Leakage Current  Tri-state Output Leakage Current  Voltage Output Level H  Voltage Output Level L | COUT     | Output pins                        | -                           | 9        | -                                                                                                                                                                                                                | pF   |

|                                                                                                                                                                   | CRFIO    | RF inout pins                      | -                           | 9        | -                                                                                                                                                                                                                | pF   |

|                                                                                                                                                                   | CAI      | Analog input pins                  | -                           | 9        | -                                                                                                                                                                                                                | pF   |

<sup>\*1</sup> DMON pin is IOH=-2mA/2mA

<sup>\*2</sup> REG\_CORE pin and REG\_OUT pin. REG\_OUT pin becomes 0V when in sleep state.

ML7396A/B/E

### •RF characteristics

Data Rate : 10kbps/ 20kbps/ 40kbps/ 50kbps/100kbps/ 150kbps/200kbps/ 400kbps

Modulation scheme : GFSK

Channel spacing : 200kHz/400kHz/600kHz

Frequency : Support 750MHz to 1GHz by changing L/C components between IND1 and IND2 pins

Others Definition point is a antenna connector in the reference circuit.

RF characteristics out of below table include 400kbps (option) are available as reference data

separately.

### [TX]

| Item                                | Condition                                                                                                                                                                                                                                   | Min | Тур | Max     | Unit  |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| TX Power                            | 20mW (13dBm) mode                                                                                                                                                                                                                           | 9   | 13  | 15      | dBm   |

| 1X Tower                            | 10mW (10dBm) mode                                                                                                                                                                                                                           | 6   | 10  | 12      | dBm   |

|                                     | 1mW (0dBm) mode                                                                                                                                                                                                                             | -4  | 0   | 2       | dBm   |

| Frequency deviation setting         |                                                                                                                                                                                                                                             | -   | -   | 2,250   | kHz   |

| range [Fdev] (*1)                   | 1) (1)                                                                                                                                                                                                                                      |     |     |         |       |

| 920MHz band (920.5MHz to 928        |                                                                                                                                                                                                                                             |     |     | 200 #   | 1 7 7 |

| Occupied bandwidth                  | n : number of channel                                                                                                                                                                                                                       | -   | -   | 200 * n | kHz   |

| Power at channel edge               | 20mW mode (920.5MHz to 922.3MHz)                                                                                                                                                                                                            | -   | -   | -7      | dBm   |

|                                     | 10mW mode                                                                                                                                                                                                                                   | -   | -   | -10     | dBm   |

|                                     | 1mW mode                                                                                                                                                                                                                                    | -   | -   | -20     | dBm   |

| Adjacent Channel Power              | 20mW mode ±1ch, bandwidth 200kHz)                                                                                                                                                                                                           | -   | -33 | -15     | dBm   |

| ragacent channel I ower             | 10mW mode +/-1ch bandwidth: 200kHz                                                                                                                                                                                                          | -   | -39 | -18     | dBm   |

|                                     | 1mW mode +/-1ch bandwidth: 200kHz                                                                                                                                                                                                           | -   | -47 | -26     | dBm   |

| Spurious emission level             | 710MHz or lower, 100kHz band                                                                                                                                                                                                                | -   | -65 | -36     | dBm   |

| (20mW mode)                         | Higher than 710MHz to 900MHz, 1MHz band                                                                                                                                                                                                     | -   | -70 | -55     | dBm   |

|                                     | Higher than 900MHz to 915MHz, 100kHz band                                                                                                                                                                                                   | -   | -72 | -55     | dBm   |

|                                     | Higher than 915MHz to 930MHz, 100kHz band (Excluding within 200 + 100*n kHz above and below the channel frequency, however, within 100 + 100*n kHz above and below for 920.5MHz to 922.3MHz. n is the number of concurrently used channels) | -   | -51 | -36     | dBm   |

|                                     | Higher than 930MHz to 1000MHz, 100kHz band                                                                                                                                                                                                  | -   | -70 | -55     | dBm   |

|                                     | Higher than 1000MHz to 1215MHz, 1MHz band                                                                                                                                                                                                   | -   | -75 | -45     | dBm   |

|                                     | Higher than 1215MHz, 1MHz band (2nd harmonics or higher)                                                                                                                                                                                    | -   | -40 | -30     | dBm   |

| 915MHz band (902MHz to 928M         | Hz)                                                                                                                                                                                                                                         |     |     |         |       |

| 6dB bandwidth                       | Frequency deviation=171kHz                                                                                                                                                                                                                  | 500 | -   | -       | kHz   |

| Power spectrum density              | 20mW mode, frequency deviation = 171kHz,<br>3kHz band                                                                                                                                                                                       | -   | -   | 8       | dBm   |

| Spurious emission level             | 900MHz or lower                                                                                                                                                                                                                             | -   | -65 | -56     | dBm   |

| (20mW mode)                         | Higher than 960MHz (2nd harmonics or higher)                                                                                                                                                                                                | -   | -50 | -41     | dBm   |

| 868MHz band (863MHz to 870M         |                                                                                                                                                                                                                                             |     |     | 1 **    | 42    |

| Spurious emission level (10mW mode) | Higher than 1000MHz (2nd harmonics or higher)                                                                                                                                                                                               | -   | -35 | -30     | dBm   |

<sup>\*1</sup> While the setting range is described as above, the possible maximum value depends on the RF channel frequency to be used. RF channel frequency ± frequency deviation should not include a multiple of 36MHz (864MHz, 900MHz, 936MHz, and so on).

Example) For 902MHz, 2,000kHz is a possible maximum frequency deviation value.

<sup>\*2 863.5</sup>MHz to 866.2MHz cannot be used. For details, refer section "Programing Channel Frequency."

# [RX]

| Item                                      | Condition                                     | Min | Тур   | Max  | Unit |

|-------------------------------------------|-----------------------------------------------|-----|-------|------|------|

| 920MHz band (920.5MHz to 928              | 3.1MHz)                                       |     |       |      |      |

| Minimum DV amaiticity                     | 50kbps mode (*1)                              | -   | -108  | -102 | dBm  |

| Minimum RX sensitivity<br>BER<0.1%        | 100kbps mode (*1)                             | -   | -106  | -100 | dBm  |

| BEK~0.176                                 | 200kbps mode (*1)                             | -   | -102  | -97  | dBm  |

| Maximum input level                       | 50kbps mode/100kbps mode/200kbps mode         | 0   | -     | -    | dBm  |

|                                           | 50kbps mode                                   | 20  | 35    | -    | dB   |

| Adjacent channel selectivity              | 100kbps mode                                  | 20  | 35    | -    | dB   |

|                                           | 200kbps mode                                  | 20  | 35    | -    | dB   |

|                                           | 50kbps mode                                   | 30  | 45    | -    | dB   |

| Alternate channel selectivity             | 100kbps mode                                  | 30  | 45    | -    | dB   |

|                                           | 200kbps mode                                  | 30  | 45    | -    | dB   |

| Minimum energy detection level [ED value] |                                               | -   | -     | -100 | dBm  |

| Energy detection range                    | Dynamic range                                 | 60  | 70    | -    | dB   |

| Energy detection accuracy                 |                                               | -6  | -     | +6   | dB   |

| Spurious emission level                   | 710MHz or lower, 100kHz band                  | -   | <-93  | -54  | dBm  |

| ARIB T108 measurement                     | Higher than 710MHz to 900MHz, 1MHz band       | -   | <-83  | -55  | dBm  |

| condition                                 | Higher than 900MHz to 915MHz, 100kHz band     | -   | <-93  | -55  | dBm  |

| 915.9MHz~916.9MHz                         | Higher than 915MHz to 930MHz, 100kHz band     | -   | -63   | -54  | dBm  |

| 920.5MHz~929.7MHz                         | Higher than 930MHz to 1000MHz, 100kHz band    | -   | <-93  | -55  | dBm  |

|                                           | Higher than 1000MHz                           | -   | -57   | -47  | dBm  |

| 915MHz band (902MHz to 928M               |                                               |     |       |      |      |

|                                           | 100kbps mode (modulation index = 1) (*1)      | -   | -106  | -99  | dBm  |

|                                           | 150kbps mode (modulation index = $0.5$ ) (*1) | -   | -102  | -96  | dBm  |

| Minimum receiver sensitivity              | 200kbps mode (modulation index = 1) (*1)      | -   | -102  | -96  | dBm  |

| BER<0.1%                                  | 100kbps mode (frequency shift: 171kHz)        | -   | -100  | -87  | dBm  |

|                                           | 150kbps mode (frequency shift: 171kHz)        | -   | -97.5 | -84  | dBm  |

|                                           | 200kbps mode (frequency shift: 171kHz)        | -   | -96.5 | -83  | dBm  |

| 868MHz band (863MHz to 870M               | MHz) (*2)                                     |     |       |      |      |

| Minimum receiver sensitivity              | 50kbps mode (*1)                              | -   | -108  | -102 | dBm  |

| BER<0.1%                                  | 100kbps mode (*1)                             | -   | -106  | -100 | dBm  |

| DEK~0.170                                 | 200kbps mode (*1)                             | -   | -102  | -97  | dBm  |

| Collateral emission level                 | 1000MHz or lower (local frequency)            | -   | -63   | -57  | dBm  |

| Conateral enhission level                 | Higher than 1000MHz                           | -   | -57   | -47  | dBm  |

<sup>\*1</sup> When NBO\_SEL([DATA\_SET:B0 0x47(7)])=0b0.

\*2 863.5MHz to 866.2MHz cannot be used. For details, refer section "Programing Channel Frequency."

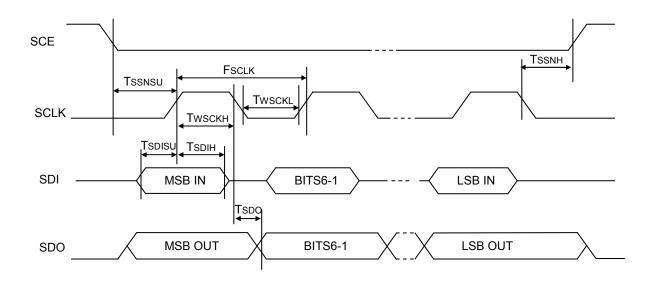

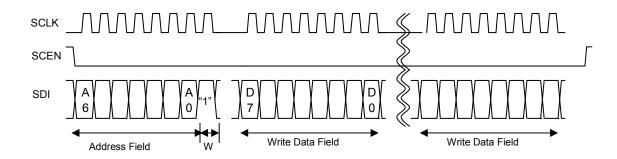

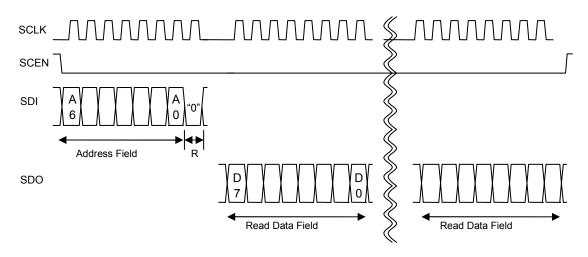

# •SPI interface characteristics

| Item                  | Symbol | Condition                   | Min   | Тур | Max | Unit |

|-----------------------|--------|-----------------------------|-------|-----|-----|------|

| SCLK clock frequency  | FSCLK  |                             | 0.032 | 2   | 16  | MHz  |

| SCEN input setup time | TSSNSU |                             | 30    | -   | -   | ns   |

| SCEN input hold time  | TSSNH  |                             | 30    | -   | -   | ns   |

| SCLK high pulse width | TWSCKH | T 1 '                       | 28    | -   | -   | ns   |

| SCLK low pulse width  | TWSCKL | Load capacitance<br>CL=20pF | 28    | -   | -   | ns   |

| SDI input setup time  | Tsdisu | СЕ 20р1                     | 5     | -   | -   | ns   |

| SDI input hold time   | Tsdih  |                             | 15    | -   | -   | ns   |

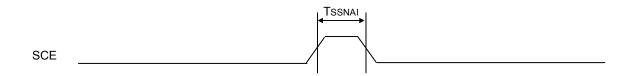

| SCEN negate interval  | TSSNAI |                             | 60    | -   | -   | ns   |

| SDO output delay time | Tsdo   |                             | -     | -   | 22  | ns   |

### [Note]

All timing parameter is defined at voltage level of  $V_{DDIO}$  \* 20% and  $V_{DDIO}$  \* 80%.

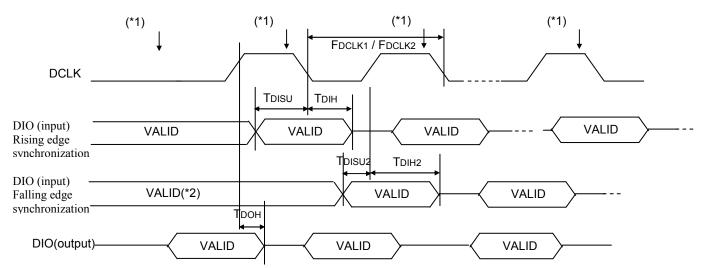

### •DIO interface characteristics

| Item                                                       | Symbol             | Condition                   | Min            | Тур              | Max    | Unit |

|------------------------------------------------------------|--------------------|-----------------------------|----------------|------------------|--------|------|

| DIO input setup time<br>(Rising edge synchronization)      | Tdisu              |                             | 1              | -                | -      | μs   |

| DIO input setup time<br>(Falling edge synchronization)     | TDISU2             |                             | 0              | -                | -      | μs   |

| DIO input hold time<br>(Rising edge synchronization)       | Тын                |                             | 0              | -                | -      | ns   |

| DIO input hold time (*3)<br>(Falling edge synchronization) | Тын2               |                             | 10<br>5<br>2.5 | -                | -      | μs   |

| DIO Output hold time                                       | $T_{DOH}$          | Load capacitance<br>CL=20pF | 20             | -                | -      | ns   |

| DCLK frequency (*1) (*3) (TX)                              | F <sub>DCLK1</sub> |                             | -20ppm         | 50<br>100<br>200 | +20ppm | kHz  |

| DCLK frequency (*2) (*3) (RX)                              | F <sub>DCLK2</sub> |                             | -4%            | 50<br>100<br>200 | +4%    | kHz  |

| DCLK output duty ratio (TX)                                | $D_{DCLK}$         |                             | -              | 50               | -      | %    |

| DCLK output duty ratio (RX)                                | $D_{DCLK}$         |                             | 40             | -                | 60     | %    |

- \*1 DCLK clock frequency in TX mode will be varied depending on the variance of master clock frequency.

- \*2 DCLK clock frequency in RX mode will be varied by reproduced clock and its jitter.

- \*3 These characteristics are depend on the setting to the RATE [2:0] ([DATA\_SET:B0 0x47(2-0)]. (upper: 50kbps, mid: 100kbps, lower: 200kbps)

#### [Note]

All timing parameter is defined at voltage level of  $V_{DDIO}$  \* 20% and  $V_{DDIO}$  \* 80%

- (\*1) Timing when ML7396 takes the DIO input.

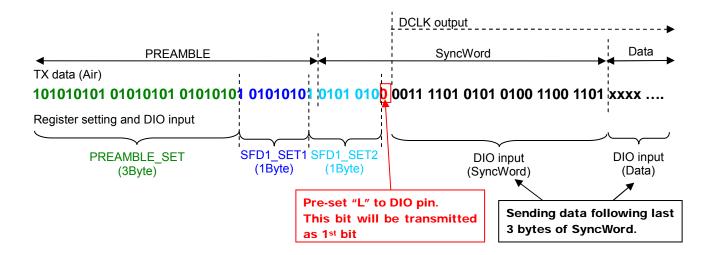

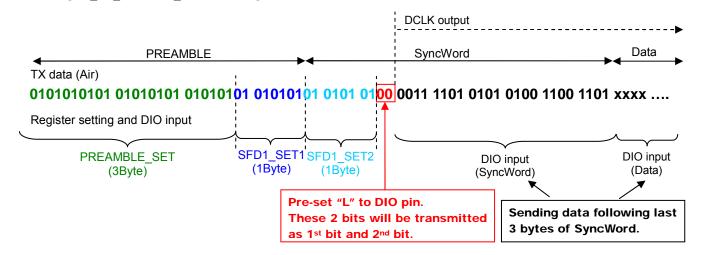

- (\*2) For the falling edge synchronization, the first two bits of DIO input have the same data, refer section "TX mode (with DIO mode)"

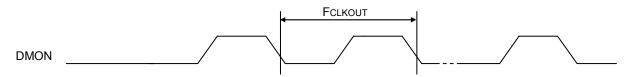

# •Clock output characteristics

Clock output can be controled by [CLK\_SET:B0 0x02] register (Initial value:enable), Clock output from DMON pin.

| Item                    | Symbol              | Co                             | ndition          | Min    | Тур | Max | Unit |

|-------------------------|---------------------|--------------------------------|------------------|--------|-----|-----|------|

| Clock output frequency  | F <sub>CLKOUT</sub> |                                | -                | 0.0088 | 6   | 36  | MHz  |

| Clock output duty ratio | D                   | Load<br>capacitance<br>CL=20pF | 12MHz            | 30     | -   | 70  | %    |

| (*1)                    | $D_{CLKOUT}$        | CL 20p1                        | Other than above | 48     | 50  | 52  | %    |

\*1 Duty ratio will be H:L = 1:2 when output frequency is 12MHz.. Refer [CLK\_OUT: B0 0x03] register ().

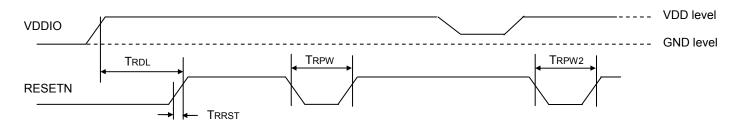

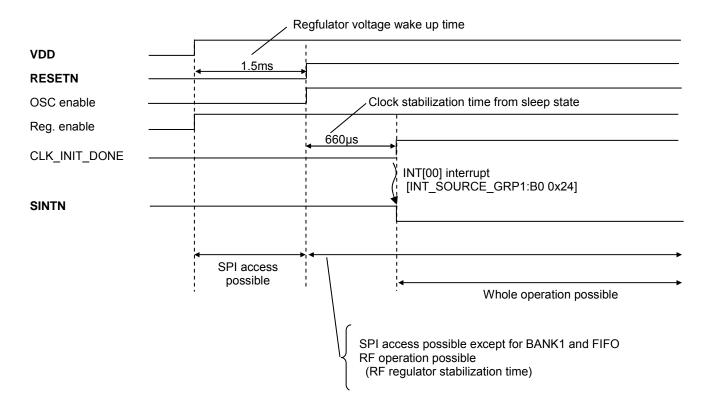

### Reset

| Item                                                        | Symbol    | Condition                              | Min | Тур | Max | Unit |

|-------------------------------------------------------------|-----------|----------------------------------------|-----|-----|-----|------|

| RESETN delay time (Power on)                                | $T_{RDL}$ | All power supply pins (After power on) | 1.5 | ı   | ı   | ms   |

| RESETN pulse period<br>(When starting from VDDIO=0V)        | $T_{RPW}$ |                                        | 200 | -   | -   | ns   |

| RESETN pulse period 2 (*1)<br>(When starting from VDDIO≠0V) | Trpw2     | VDD>1.8V                               | 1.5 | -   | -   | ms   |

| RESETN rising period                                        | Trrst     |                                        | -   | -   | 1   | ms   |

(\*1) When starting from VDDIO \( \neq .0 \text{V}, \) input a pulse to the RESETN signal after VDDIO exceeds 1.8 \( \text{V}. \)

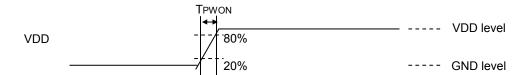

# •Power on sequence

| Item          | Symbol     | Condition                                 | Min | Тур | Max | Unit |

|---------------|------------|-------------------------------------------|-----|-----|-----|------|

| Power on time | $T_{PWON}$ | Power on state<br>(All power supply pins) | -   | -   | 5   | ms   |

# ■Registers

### •Register map

It is consist of 3bank, BANK0, BANK1, BANK2. Each BANK has address space of 0x00 to 0x7F, 128 byte in total. The space shown as gray highlighted part is not implemented in LSI or reserved bits. TX/RX FIFO is implemented in PHY block, those register except for FIFO is implemented in SPI block. The address not exist in the memory map is not accessible. Also, the address is not accessible during the VCO calibration.

In each BANK, there are some registers that can not be access unless give access allowance by TST\_ACEN ([BANK\_SEL: B0/B1/B2 0x00(7)] =0b1. Such registers are marked with "#" in the following list. The TST\_ACEN enable setting is required in the initial setting or test mode setting, but it is recommended to set disable when in normal operation to avoid miss-setting.

For registers whose setting value is specified by the "ML7396Family\_InitialRegisterSetting" file, please set the value shown in the file.

| : Implemented as functionable register |

|----------------------------------------|

| : Implemented as reserved bits         |

# BANK0

|              | Symbol            |   |   |   | R | it |   |   |   |                                                                                        |

|--------------|-------------------|---|---|---|---|----|---|---|---|----------------------------------------------------------------------------------------|

| Address      | (# test register) | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 | Description                                                                            |

| 0x00         | BANK SEL          |   |   |   |   |    |   |   |   | Register access bank selection                                                         |

| 0x01         | RST SET           |   |   |   |   |    |   |   |   | Software reset setting                                                                 |

| 0x02         | CLK SET           |   |   |   |   |    |   |   |   | Clock configuration                                                                    |

| 0x03         | CLKOUT            |   |   |   |   |    |   |   |   | CLKOUT frequency setting                                                               |

| 0x04         | RATE SET1         |   |   |   |   |    |   |   |   | Data rate conversion setting 1                                                         |

| 0x05         | RATE SET2         |   |   |   |   |    |   |   |   | Data rate conversion setting 2                                                         |

| 0x06-0x07    | Reserved          |   |   |   |   |    |   |   |   | Reserved                                                                               |

| 0x08         | #ADC CLK SET      |   |   |   |   |    |   |   |   | RSSI ADC clock frequency setting                                                       |

| 0x09-0x0a    | Reserved          |   |   |   |   |    |   |   |   | Reserved                                                                               |

| 0x0b         | #OSC ADJ          |   |   |   |   |    |   |   |   | Load capacitor adjustment for oscillation circuit                                      |

| 0x0c         | #RF TEST MODE     |   |   |   |   |    |   |   |   | TX test pattern setting                                                                |

| 0x0d-0x0e    | Reserved          |   |   |   |   |    |   |   |   | Reserved                                                                               |

| 0x0f         | # PHY STATE       |   |   |   |   |    |   |   |   | PHY status indication                                                                  |

| 0x10         | #FIFO BANK        |   |   |   |   |    |   |   |   | FIFO bank indication                                                                   |

| 0x11         | #PLL LOCK DETECT  |   |   |   |   |    |   |   |   | PLL lock detection configuration                                                       |

| 0x11         | CCA IGNORE LEVEL  |   |   |   |   |    |   |   |   | ED threshold level setting for excluding CCA judgement                                 |

| 0x12<br>0x13 | CCA_IGNORE_LEVEL  |   |   |   |   |    |   |   |   | CCA threshold level setting for excluding CCA judgement                                |

|              | _                 |   |   |   |   |    |   |   |   | Timing setting for forced termincation of CCA operation                                |

| 0x14         | CCA_ABORT         |   |   |   |   |    |   |   |   |                                                                                        |

| 0x15         | CCA_CNTRL         |   |   |   |   |    |   |   |   | CCA control setting and result indication                                              |

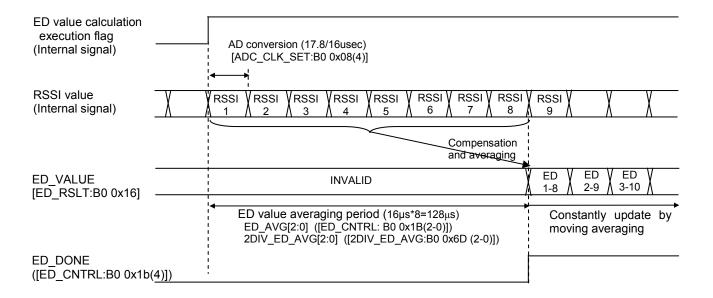

| 0x16         | ED_RSLT           |   |   |   |   |    |   |   |   | ED (Energy Detection) value indication                                                 |

| 0x17         | IDLE_WAIT_L       |   |   |   |   |    |   |   |   | IDLE detection period setting during CCA (low 8bits)                                   |

| 0x18         | IDLE_WAIT_H       |   |   |   |   |    |   |   |   | IDLE detection period setting during CCA (high 2bits)                                  |

| 0x19         | CCA_PROG_L        |   |   |   |   |    |   |   |   | IDLE judgement elapsed time indication during CCA (low byte)                           |

| 0x1a         | CCA_PROG_H        |   |   |   |   |    |   |   |   | IDLE judgement elapsed time indication during CCA (high 2bits)                         |

| 0x1b         | ED_CNTRL          |   |   |   |   |    |   |   |   | ED detection control setting                                                           |

| 0x1c         | GAIN_MtoL         |   |   |   |   |    |   |   |   | Threshold level setting for switching middle gain to low gain                          |

| 0x1d         | GAIN_LtoM         |   |   |   |   |    |   |   |   | Threshold level setting for switching low gain to middle gain                          |

| 0x1e         | GAIN_HtoM         |   |   |   |   |    |   |   |   | Gain update setting and threshold level setting for switching high gain to middle gain |

| 0x1f         | GAIN_MtoH         |   |   |   |   |    |   |   |   | Threshold level setting for switching middle gain to high gain                         |

| 0x20         | RSSI_ADJ_M        |   |   |   |   |    |   |   |   | RSSI offset value setting during middle gain operation                                 |

| 0x21         | RSSI_ADJ_L        |   |   |   |   |    |   |   |   | RSSI offset value setting during low gain operation                                    |

| 0x22         | RSSI_STABLE_TIME  |   |   |   |   |    |   |   |   | Time parameter for RSSI value become stable after gain switch                          |

| 0x23         | RSSI_VAL_ADJ      |   |   |   |   |    |   |   |   | RSSI scale factor setting for ED value conversion.                                     |

| 0x24         | INT_SOURCE_GRP1   |   |   |   |   |    |   |   |   | FIFO clear setting and interrupt status for INT00 to INT05                             |

| 0x25         | INT_SOURCE_GRP2   |   |   |   |   |    |   |   |   | Interrupt status for INT08 to INT15                                                    |

| 0x26         | INT_SOURCE_GRP3   |   |   |   |   |    |   |   |   | Interrupt status for INT16 to INT23                                                    |

| 0x27         | INT_SOURCE_GRP4   |   |   |   |   |    |   |   |   | Interrupt status for INT24 and INT25                                                   |

| 0x28         | PD_DATA_REQ       |   |   |   |   |    |   |   |   | Data transmission request status indication                                            |

| 0x29         | PD_DATA_IND       |   |   |   |   |    |   |   |   | Data reception status indication                                                       |

| 0x2a         | INT_EN_GRP1       |   |   |   |   |    |   |   |   | Interrupt mask for INT00 to INT05                                                      |

| 0x2b         | INT EN GRP2       |   |   |   |   |    |   |   |   | Interrupt mask for INT08 to INT15                                                      |

| 0x2c         | INT EN GRP3       |   |   |   |   |    |   |   |   | Interrupt mask for INT16 to INT23                                                      |

| 0x2d         | INT EN GRP4       |   |   |   |   |    |   |   |   | Interrupt mask for INT24 and INT25                                                     |

| 0x2e         | CH EN L           |   |   |   |   |    |   |   |   | RF channel enable setting for low 8ch                                                  |

| 0x2f         | CH EN H           |   |   |   |   |    |   |   |   | RF channel enable setting for high 8ch                                                 |

| 0x30         | IF FREQ AFC H     |   |   |   |   |    |   |   |   | IF frequency setting during AFC operation (high byte)                                  |

| 0x31         | IF FREQ AFC L     |   |   |   |   |    |   |   |   | IF frequency setting during AFC operation (low byte)                                   |

| 0x32         | BPF AFC ADJ H     |   |   |   |   |    |   |   |   | Bandpass filter capacitance adjustment during AFC operation (high 2bits)               |

| 0x33         | BPF_AFC_ADJ_L     |   |   |   |   |    |   |   |   | Bandpass filter capacitance adjustment during AFC operation (low byte)                 |

| 0x34         | AFC CNTRL         |   |   |   |   |    |   |   |   | AFC control setting                                                                    |

| 0x35         | TX ALARM LH       |   |   |   |   |    |   |   |   | TX FIFO full level setting                                                             |

| 0x36         | TX_ALARM_HL       |   |   |   |   |    |   |   |   | TX FIFO empty level setting                                                            |

| 0x37         | RX ALARM LH       |   |   |   |   |    |   |   | - | RX FIFO full level setting                                                             |

| 0.7.7        | ICA_ADAKWI_LH     |   |   |   |   |    |   |   | l | 1011 II O Iun Iovoi sounig                                                             |

# ML7396A/B/E

# BANK0 (continued)

| Address  | Symbol             |                                                  |   | ı <u>-</u> |   | it       |                                                  |   |   | Description                                                                                                            |

|----------|--------------------|--------------------------------------------------|---|------------|---|----------|--------------------------------------------------|---|---|------------------------------------------------------------------------------------------------------------------------|

|          | (# test register)  | 7                                                | 6 | 5          | 4 | 3        | 2                                                | 1 | 0 | -                                                                                                                      |

| 0x38     | RX_ALARM_HL        |                                                  |   |            |   |          |                                                  |   |   | RX FIFO empty level setting                                                                                            |

| 0x39     | PREAMBLE_SET       |                                                  |   |            |   |          |                                                  |   |   | Preamble pattern setting                                                                                               |

| 0x3a     | SFD1_SET1          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #1 1st byte setting (max 4byte)                                                                            |

| 0x3b     | SFD1_SET2          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #1 2 <sup>nd</sup> byte setting (max 4byte)                                                                |

| 0x3c     | SFD1_SET3          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #1 3 <sup>rd</sup> byte setting (max 4byte)                                                                |

| 0x3d     | SFD1_SET4          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #1 4 <sup>th</sup> byte setting (max 4byte)                                                                |

| 0x3e     | SFD1_SET1          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #2 1st byte setting (max 4byte                                                                             |

| 0x3f     | SFD2_SET2          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #2 2 <sup>nd</sup> byte setting (max 4byte)                                                                |

| 0x40     | SFD2_SET3          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #2 3 <sup>rd</sup> byte setting (max 4byte)                                                                |

| 0x41     | SFD2_SET4          |                                                  |   |            |   |          |                                                  |   |   | SFD pattern #2 4 <sup>th</sup> byte setting (max 4byte)                                                                |

| 0x42     | TX_PR_LEN          |                                                  |   |            |   |          |                                                  |   |   | TX preamble length setting                                                                                             |

| 0x43     | RX_PR_LEN/SFD_LEN  |                                                  |   |            |   |          |                                                  |   |   | RX preamble setting and SFD length setting                                                                             |

| 0x44     | SYNC_CONDITION     |                                                  |   |            |   |          |                                                  |   |   | Bit error tolerance setting in RX preamble and SFD detection                                                           |

| 0x45     | PACKET_MODE_SET    |                                                  |   |            |   |          |                                                  |   |   | Packet configuration                                                                                                   |

| 0x46     | FEC/CRC_SET        |                                                  |   |            |   |          |                                                  |   |   | FEC and CRC configuration                                                                                              |

| 0x47     | DATA_SET           |                                                  |   |            |   |          |                                                  |   |   | Data configuration                                                                                                     |

| 0x48     | CH0_FL             |                                                  |   |            |   |          |                                                  |   |   | Channel #0 frequency (F-counter) setting (low byte)                                                                    |

| 0x49     | CH0_FM             |                                                  |   |            |   |          |                                                  |   |   | Channel #0 frequency (F-counter) setting (middle byte)                                                                 |

| 0x4a     | CH0_FH             |                                                  |   |            |   |          |                                                  |   |   | Channel #0 frequency (F-counter) setting (high 4bits)                                                                  |

| 0x4b     | CH0_NA             |                                                  |   |            |   |          |                                                  |   |   | Channel #0 frequency (N-counter and A-counter) setting                                                                 |

| 0x4c     | CH_SPACE_L         |                                                  |   |            |   |          |                                                  |   |   | Channel space setting (low byte)                                                                                       |

| 0x4d     | CH_SPACE_H         |                                                  |   |            |   |          |                                                  |   |   | Channel space setting (high byte)                                                                                      |

| 0x4e     | F_DEV_L            |                                                  |   |            |   |          |                                                  |   |   | GFSK frequency deviation setting (low byte)                                                                            |

| 0x4f     | F_DEV_H            |                                                  |   |            |   |          |                                                  |   |   | GFSK frequency deviation setting (high byte)                                                                           |

| 0x50     | ACK_TIMER_L        |                                                  |   |            |   |          |                                                  |   |   | Ack timer setting (low byte)                                                                                           |

| 0x51     | ACK_TIMER_H        |                                                  |   |            |   |          |                                                  |   |   | Ack timer setting (high byte)                                                                                          |

| 0x52     | ACK_TIMER_EN       |                                                  |   |            |   |          |                                                  |   |   | Ack timer control setting                                                                                              |

| 0x53     | ACK_FRAME1         |                                                  |   |            |   |          |                                                  |   |   | Ack Frame Control Field (2bytes) setting (low byte)                                                                    |

| 0x54     | ACK_FRAME2         |                                                  |   |            |   |          |                                                  |   |   | Ack Frame Control Field (2bytes) setting (high byte)                                                                   |

| 0x55     | AUTO_ACK_SET       |                                                  |   |            |   |          |                                                  |   |   | Auto_Ack function setting                                                                                              |

| 0x56-x58 | Reserved           |                                                  |   |            |   |          |                                                  |   |   | Reserved                                                                                                               |

| 0x59     | GFIL00 / FSK_FDEV1 |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 1 / FSK 1st frequency deviation setting                                            |

| 0x5a     | GFIL01 / FSK_FDEV2 |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 2 / FSK 2 <sup>nd</sup> frequency deviation setting                                |

| 0x5b     | GFIL02 / FSK_FDEV3 |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 3 / FSK 3 <sup>rd</sup> frequency deviation setting                                |

| 0x5c     | GFIL03 / FSK_FDEV4 |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 4 / FSK 4th frequency deviation setting                                            |

| 0x5d     | GFIL04             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 5                                                                                  |

| 0x5e     | GFIL05             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 6                                                                                  |

| 0x5f     | GFIL06             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 7                                                                                  |

| 0x60     | GFIL07             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 8                                                                                  |

| 0x61     | GFIL08             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 9                                                                                  |

| 0x62     | GFIL09             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 10                                                                                 |

| 0x63     | GFIL10             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 11                                                                                 |

| 0x64     | GFIL11             |                                                  |   |            |   |          |                                                  |   |   | Gaussian filter coefficient setting 12                                                                                 |

|          |                    | <del>                                     </del> |   |            | _ |          | <del>                                     </del> |   |   | FSK 3 <sup>rd</sup> frequency deviation (FDEV3) hold time setting                                                      |

| 0x65     | FSK_TIME1          |                                                  |   |            |   |          |                                                  |   |   | FSK 3 frequency deviation (FDEV3) hold time setting  FSK 2 <sup>nd</sup> frequency deviation (FDEV2) hold time setting |

| 0x66     | FSK_TIME2          |                                                  |   |            |   |          |                                                  |   |   |                                                                                                                        |

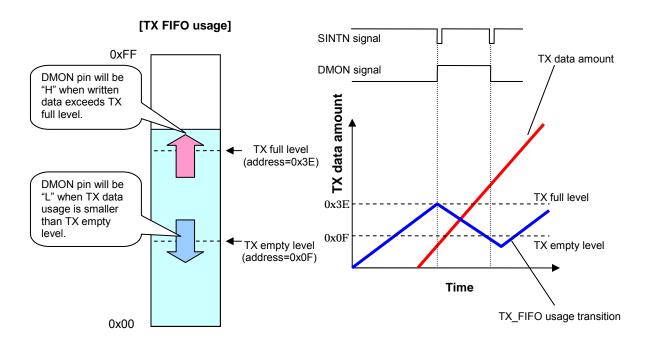

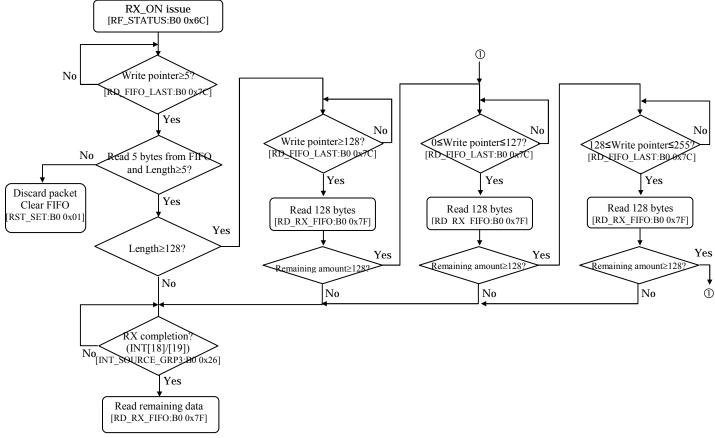

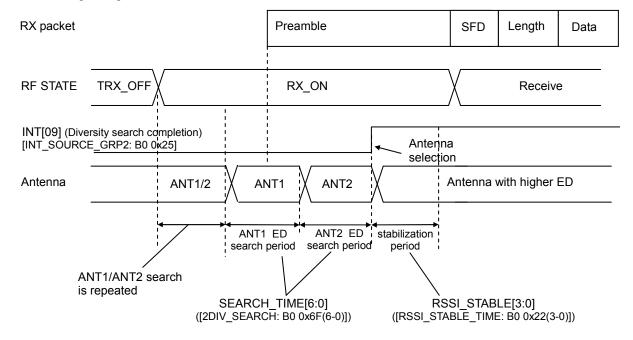

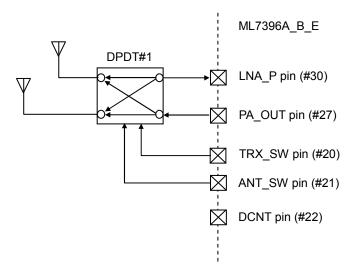

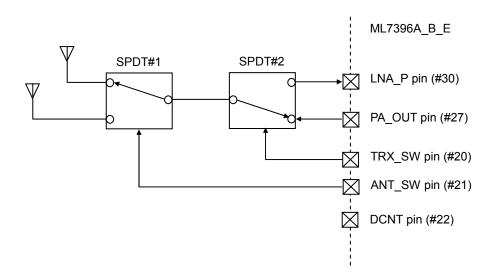

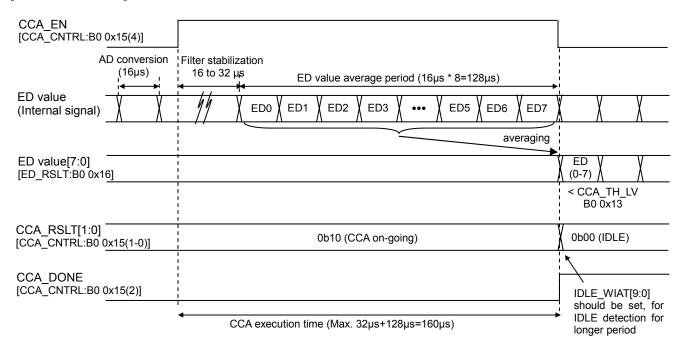

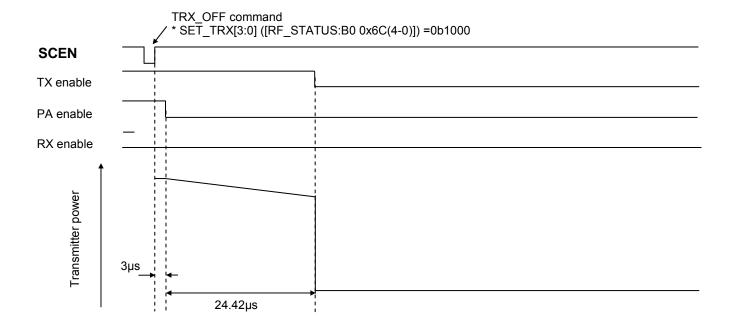

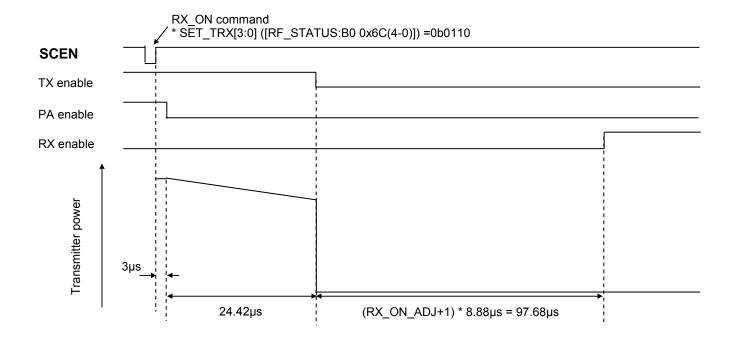

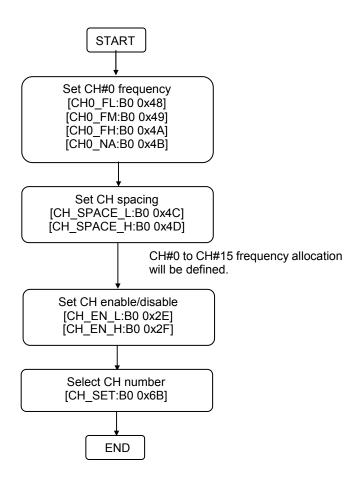

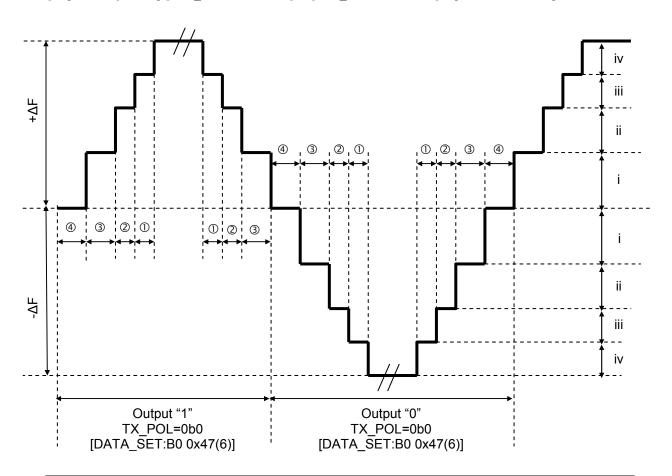

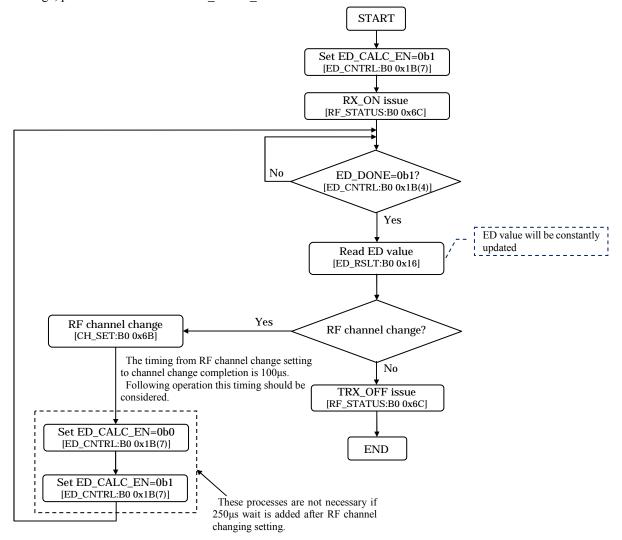

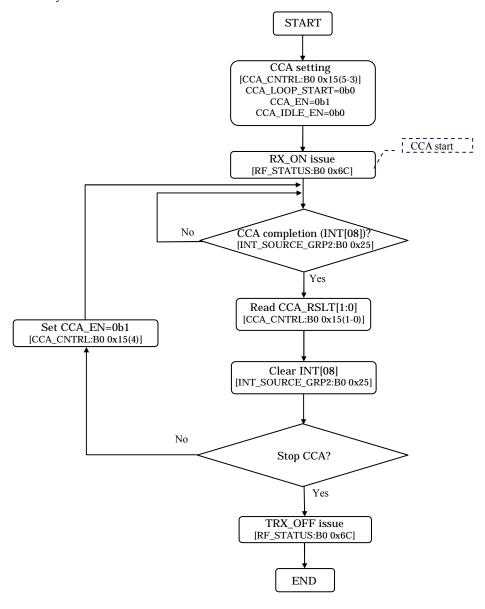

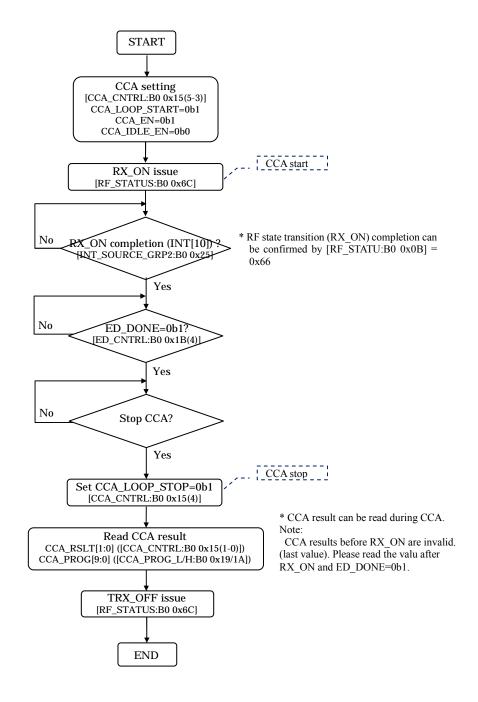

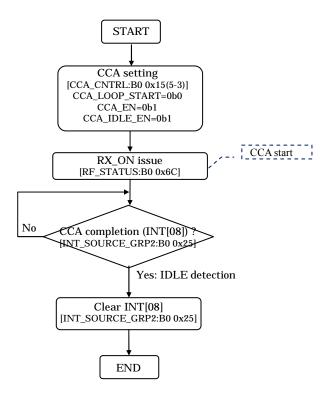

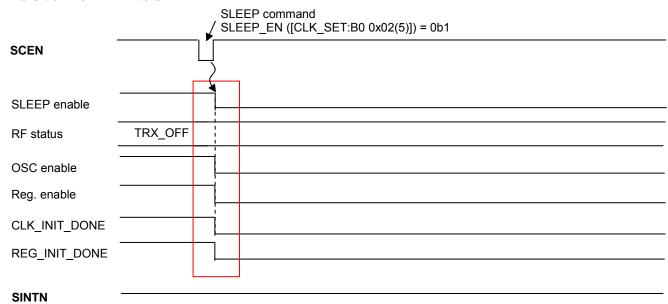

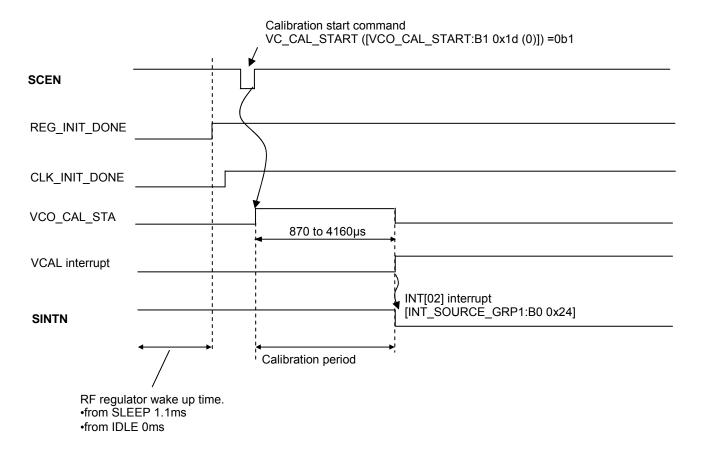

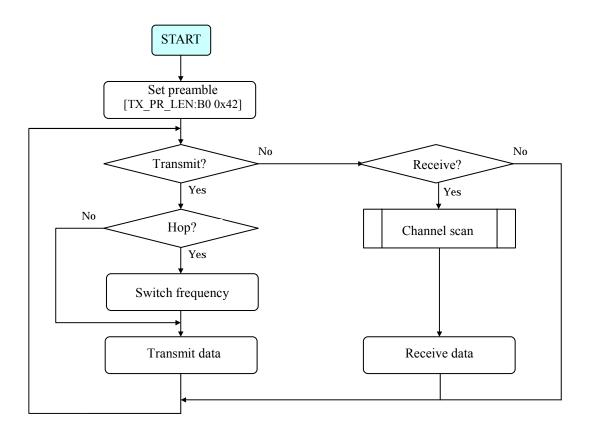

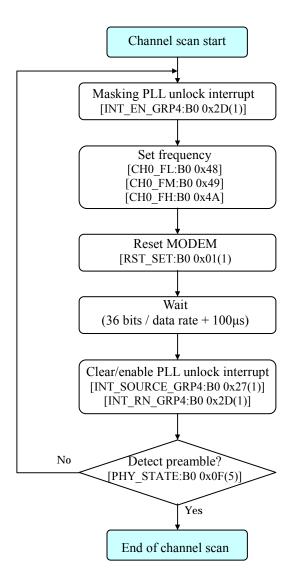

| 0x67     | FSK_TIME3          | -                                                |   |            |   | <u> </u> | -                                                |   |   | FSK 1 <sup>st</sup> frequency deviation (FDEV1) hold time setting                                                      |