# ML7416N-060

Sub-GHz (900 MHz Band) Broadband RF Transceiver IC with Built-in MCU

#### 1. General Description

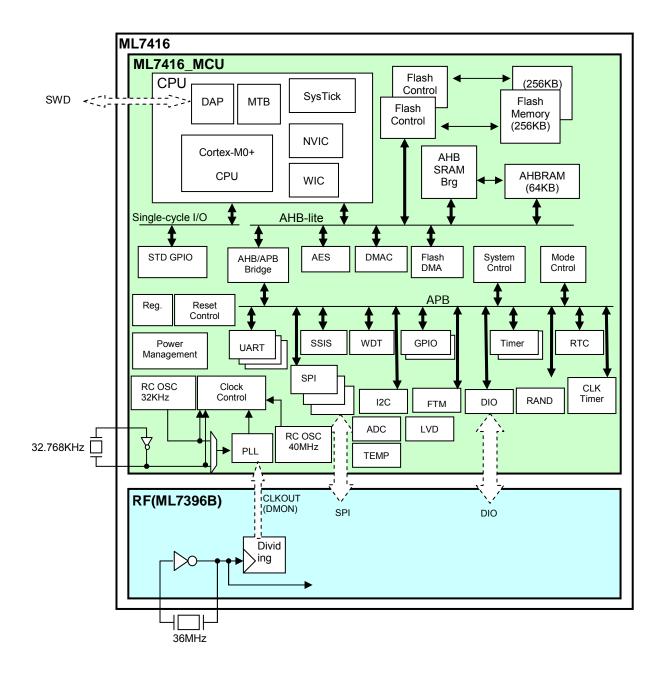

ML7416 is a low power consumption LSI for sub-GHz broadband radio communication, which integrates the MCU block and RF block in a single chip.

The features are shown below. \* For details of the RF block, refer to ML7396B Data Sheet (FJDL7396A\_B\_E).

- Industry-standard ARM Cortex-M0+ CPU core \* Maximum operating frequency: 40 MHz

- 512 KB flash memory (for program [256 KB x 2 bank configuration is possible]. Can be used as data flash)

- 64 KB RAM (for data. Whether to hold data in low power consumption mode can be selected)

- Start-stop synchronous serial communication interface (UART) \* Max. 3 ch

- Synchronous serial communication interface (SPI) \* Max. 2 ch (additionally, 1 ch for SPI dedicated to RF control, which does not exist on the external port)

- WDT

- General-purpose IO

- Timer \* 32-bit timer x 10 ch. Among them, 4 ch (2 sets) can be used as 64-bit timer by the cascade connection

- RTC

- Flexible timer (FTM) (PWM mode, etc.)

- I2C \* Master/slave supported

- RF control transmit/receive data interface (DIO) \* As this is dedicated to RF control, it does not have an external port

- Random number generation circuit (RAND)

- Clock correction counter (CLK Timer)

- SWD (2-wire serial wire debug port)

- X'tal OSC \* 32.768 KHz

- PLL \* Multiplying/dividing 32 KHz

- ADC \* 10 bits, Max. 3 ch (Max. 2 ch when using the temperature sensor function)

- Voltage drop detection (LVD)

- Temperature sensor (TEMP)

- RC OSC \* 40 MHz, 32 KHz

- AES \* ECB, CBC, CTR, CCM, and GCM supported

- DMA controller \* Transfer between SPI and RAM and between AES and RAM, 4 ch

- Flash DMA controller \* Write to flash, Verify

• Supply voltage 1.8 to 3.6 V (when the transmission power is set to 1 mW mode)

2.3 to 3.6 V (when the transmission power is set to 10 mW mode)

2.6 to 3.6 V (when the transmission power is set to 20 mW mode)

• Operating temperature -40 to 85 °C

### • Current consumption

At deepsleep  $2 \mu A(Typ.)$ At idle 11 mA(Typ.)At reception 24 mA (Typ.)At transmission 1 mW 22 mA (Typ.) 10 mW 33 mA(Typ.) 20 mW 41 mA(Typ.)

#### • Package

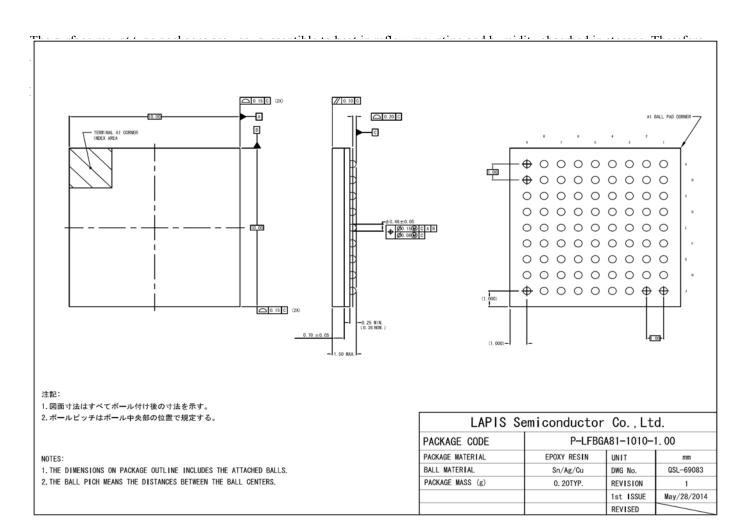

81-pin BGA (MCP product/P-LFBGA81-1010-1.00-1-MC)

10 mm x 10 mm (pin pitch: 1 mm)

Lead-free package conforming to RoHS

# 2. Block Diagram

# 3. Pin Layout

# \* The pin layout shown below is tentative. Please contact us before board design.

O81 BGA (10 mm x 10 mm, pin pitch: 1 mm)

1 2 3 4 5 6 7 8 9

| VDDIO_<br>RF | GPIOA<br>0 | GPIOA<br>1  | GPIOA<br>2       | GPIOA<br>4   | GPIOA<br>5  | GPIOA<br>6      | GPIOA<br>7      | GND_CP<br>U   | A |

|--------------|------------|-------------|------------------|--------------|-------------|-----------------|-----------------|---------------|---|

| DCNT         | VDD_PA     | GPIOA<br>3  | MODE0            | MODE1        | GPIOA<br>12 | GPIOA<br>8      | GND_CP<br>U     | GPIOA<br>9    | В |

| TRX_SW       | ANT_SW     | VDD_RE<br>G | REG_CO<br>RE_CPU | TEST_C<br>PU | RESETN      | GND_CP<br>U     | ADC0            | GPIOA<br>10   | С |

| REG_PA       | TEST       | A_MON       | GND_RF           | GND_RF       | REGPDI<br>N | GND_CP<br>U     | ADC1            | GPIOA<br>11   | D |

| GND_RF       | GND_RF     | GND_RF      | GND_RF           | GND_RF       | GND_RF      | VDDIO_<br>CPURF | ADC2            | CXOUT         | E |

| GND_RF       | GND_RF     | GND_RF      | GND_RF           | GND_RF       | GND_RF      | VPP             | VDD_RE<br>G_CPU | CXIN          | F |

| PA_OUT       | GND_RF     | VDD_CP      | GND_RF           | GND_RF       | GND_RF      | тсхо            | VDDIO_<br>CPU   | SWCK          | G |

| LNA_P        | GND_RF     | VDD_RF      | VDD_IF           | VDD_VC<br>O  | REG_OU<br>T | REG_CO<br>RE    | VDDIO_<br>CPU   | SWD           | н |

| GND_RF       | LP1        | IND1        | IND2             | VB_EXT       | VBG         | XIN             | XOUT            | VDDIO_<br>CPU | J |

**TOP View**

# 4. Pin Description

### \* The pin names and LSI numbers may be changed in the future.

### Input/output definition

$\begin{array}{ll} I_{RF} & :RF \ input \ pin \\ \\ O_{RF} & :RF \ output \ pin \\ \\ I_{A} & :Analog \ input \ pin \\ \\ O_{A} & :Analog \ output \ pin \end{array}$

$I_{OS}$  :36 MHz resonator circuit input pin  $O_{OS}$  :36 MHz resonator circuit output pin  $I_{OSL}$  :32.768 KHz resonator circuit input pin  $O_{OSL}$  :32.768 KHz resonator circuit output pin

I :Digital input pinO :Digital output pin

Is :Schmitt trigger input pin

O<sub>D</sub> :Open drain pin

# 4-1. Power Supply

| Pin name    | LSI         | I/O    | Active | Attribute/value | Functional description                         |

|-------------|-------------|--------|--------|-----------------|------------------------------------------------|

|             | number      | '      | level  | at reset        |                                                |

| VDDIO_CPU   | G8          | Power  | -      | -/-             | Power supply pin for the digital I/O (Typ. 3.3 |

|             | H8          | supply |        |                 | V)                                             |

|             | J9          |        |        |                 |                                                |

| VDDIO_RF    | A1          | Power  | -      | -/-             | Power supply pin for RF (Typ. 3.3 V)           |

|             |             | supply |        |                 |                                                |

| VDD_REG     | C3          | Power  | -      | -/-             | Regulator voltage supply pin (RF side/Typ.     |

|             |             | supply |        |                 | 3.3 V)                                         |

| VDD_REG_CPU | F8          | Power  | -      | -/-             | Regulator voltage supply pin (CPU side/Typ.    |

|             |             | supply |        |                 | 3.3 V)                                         |

| VDD_PA      | B2          | Power  | -      | -/-             | Power supply pin for PA (Typ. 3.3 V)           |

|             |             | supply |        |                 |                                                |

| VDDIO_CPURF | E7          | Power  | -      | -/-             | Power supply pin for supply from CPU to RF     |

|             |             | supply |        |                 | (Typ. 3.3 V)                                   |

| VDD_RF      | H3          | Power  | -      | -/-             | Power supply pin for LNA/MIX (Typ. 1.5 V)      |

|             |             | supply |        |                 |                                                |

| VDD_IF      | H4          | Power  | -      | -/-             | Power supply pin for IF (Typ. 1.5 V)           |

|             |             | supply |        |                 |                                                |

| VDD_VCO     | H5          | Power  | -      | -/-             | Power supply pin for VCO (Typ. 1.5 V)          |

|             |             | supply |        |                 |                                                |

| VDD_CP      | G3          | Power  | -      | -/-             | Power supply pin for CP (Typ. 1.5 V)           |

|             |             | supply |        |                 |                                                |

| GND_RF      | D4 to D5    | Ground | -      | -/-             | Ground pin (for RF)                            |

|             | E1 to E6    |        |        |                 |                                                |

|             | F1 to F6    |        |        |                 |                                                |

|             | G2,G4 to G6 |        |        |                 |                                                |

|             | H2          |        |        |                 |                                                |

|             | J1          |        |        |                 |                                                |

| GND_CPU     | A9          | Ground | -      | -/-             | Ground pin (for CPU)                           |

|             | В8          |        |        |                 |                                                |

|             | C7          |        |        |                 |                                                |

|             | D7          |        |        |                 |                                                |

# 4-2. Regulator Interface

| Pin name     | LSI    | I/O | Active | Attribute/value | Functional description                        |

|--------------|--------|-----|--------|-----------------|-----------------------------------------------|

|              | number |     | level  | at reset        |                                               |

| REG_OUT      | H6     | -   | -      | -/-             | Regulator output (Typ. 1.5 V)                 |

|              |        |     |        |                 | C connection (10 uF) * Outputs 0 V at sleep   |

|              |        |     |        |                 | state.                                        |

| REG_PA       | D1     | -   | -      | -/-             | PA regulator output pin * Outputs 0 V at      |

|              |        |     |        |                 | sleep state.                                  |

| VBG          | J6     | ı   | -      | -/-             | C connection pin (RF side/0.1 uF)             |

| REGPDIN      | D6     | 1   | Н      | 1/-             | Regulator power down pin                      |

|              |        |     |        |                 | * Fixed to "L" input in normal operation      |

| REG_CORE     | H7     | -   | -      | -/-             | Monitor pin for power supply for digital core |

|              |        |     |        |                 | (RF side                                      |

|              |        |     |        |                 | /Typ. 1.5V)/C connection(10 uF))              |

| REG_CORE_CPU | C4     | -   | -      | -/-             | Monitor pin for power supply for digital core |

|              |        |     |        |                 | (CPU side/Typ. 1.5 V/C connection (0.22       |

|              |        |     |        |                 | uF))                                          |

# 4-3. RF Interface

| Pin name | LSI    | I/O             | Active | Attribute/value | Functional description                       |

|----------|--------|-----------------|--------|-----------------|----------------------------------------------|

|          | number |                 | level  | at reset        |                                              |

| LNA_P    | H1     | I <sub>RF</sub> | -      | I               | RF antenna input pin                         |

| PA_OUT   | G1     | $O_{RF}$        | -      | 0               | RF antenna output pin                        |

| IND1     | J3     | -               | -      | -/-             | External inductor connection pin             |

| IND2     | J4     | ı               | -      | -/-             | External inductor connection pin             |

| LP1      | J2     | ı               | -      | -/-             | Loop filter connection pin                   |

| VB_EXT   | J5     | -               | -      | -/-             | Internal bias averaging capacitor connection |

|          |        |                 |        |                 | pin                                          |

| A_MON    | D3     | $O_{RF}$        | -      | Hi-Z            | Test pin for analog monitor, IF block, and   |

|          |        |                 |        |                 | analog circuit                               |

# 4-4. ADC Interface

| Pin name | LSI    | I/O            | Active | Attribute/value | Functional description                           |

|----------|--------|----------------|--------|-----------------|--------------------------------------------------|

|          | number |                | level  | at reset        |                                                  |

| ADC0     | C8     | I <sub>A</sub> | -      | 1/-             | ADC input pin 0                                  |

| ADC1     | D8     | I <sub>A</sub> | -      | 1/-             | ADC input pin 1                                  |

| ADC2     | E8     | I <sub>A</sub> | -      | 1/-             | ADC input pin 2                                  |

|          |        |                |        |                 | * Input from this pin is disabled when using the |

|          |        |                |        |                 | temperature sensor                               |

# 4-5. CPU Interface

| Pin name | LSI    | I/O                 | Active | Attribute/value | Functional description                           |

|----------|--------|---------------------|--------|-----------------|--------------------------------------------------|

|          | number |                     | level  | at reset        |                                                  |

| GPIOA0   | A2     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | I                   | -      |                 | Secondary function: UART data input pin (RXD)    |

|          |        | 1/0                 | P or N |                 | Tertiary function: SPI clock pin (SCK)           |

|          |        | Is / O <sub>D</sub> | P or N |                 | Quartic function: I2C clock pin (SCL)            |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin            |

| GPIOA1   | А3     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | 0                   | -      |                 | Secondary function: UART data output pin (TXD)   |

|          |        | 1/0                 | L      |                 | Tertiary function: SPI enable pin (SSN)          |

|          |        | Is / O <sub>D</sub> | -      |                 | Quartic function: I2C data I/O pin (SDA)         |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin            |

| GPIOA2   | A4     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | 1                   | L      |                 | Secondary function: UART CTS (Clear To Send) pin |

|          |        | 0                   | -      |                 | Tertiary function: SPI data I/O pin 1 (MISO)     |

|          |        | 1/0                 | -      |                 | Quartic function: FTM I/O pin                    |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin            |

| GPIOA3   | В3     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | 0                   | L      |                 | Secondary function: UART RTS (Ready To Send)     |

|          |        |                     |        |                 | pin                                              |

|          |        | 1/0                 | -      |                 | Tertiary function: SPI data I/O pin 2 (MOSI)     |

|          |        | 1/0                 | -      |                 | Quartic function: Reserved                       |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin            |

| Pin name | LSI    | I/O                 | Active | Attribute/value | Functional description                             |

|----------|--------|---------------------|--------|-----------------|----------------------------------------------------|

|          | number |                     | level  | at reset        |                                                    |

| GPIOA4   | A5     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | I                   | -      |                 | Secondary function: UART data input pin (RXD)      |

|          |        | 1/0                 | P or N |                 | Tertiary function: SSI slave clock pin (SSICK)     |

|          |        | Is / O <sub>D</sub> | P or N |                 | Quartic function: I2C clock pin (SCL)              |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| GPIOA5   | A6     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | ı                   | L      |                 | Secondary function: UART data output pin (TXD)     |

|          |        | ı                   | L      |                 | Tertiary function: SSI slave enable pin (SSIN)     |

|          |        | Is / O <sub>D</sub> | -      |                 | Quartic function: I2C data I/O pin (SDA)           |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| GPIOA6   | A7     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | ı                   | L      |                 | Secondary function: UART CTS (Clear To Send) pin   |

|          |        | 0                   | -      |                 | Tertiary function: SSI Slave data output pin (TXD) |

|          |        | Is / O <sub>D</sub> | -      |                 | Quartic function: I2C clock pin (SCL)              |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| GPIOA7   | A8     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | 0                   | L      |                 | Secondary function: UART RTS (Ready To Send)       |

|          |        |                     |        |                 | pin                                                |

|          |        | I                   | -      |                 | Tertiary function: SSI Slave data input pin (RXD)  |

|          |        | 1/0                 | -      |                 | Quartic function: Reserved                         |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| GPIOA8   | В7     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | I                   | -      |                 | Secondary function: UART data input pin (RXD)      |

|          |        | 1/0                 | P or N |                 | Tertiary function: SPI clock pin (SCK)             |

|          |        | Is / O <sub>D</sub> | P or N |                 | Quartic function: I2C clock pin (SCL)              |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| GPIOA9   | В9     | 1/0                 | -      | oZ / -          | Primary function: General-purpose pin              |

|          |        | 0                   | -      |                 | Secondary function: UART data output pin (TXD)     |

|          |        | 1/0                 | L      |                 | Tertiary function: SPI enable pin (SSN)            |

|          |        | Is / O <sub>D</sub> | -      |                 | Quartic function: I2C data I/O pin (SDA)           |

|          |        | 1/0                 | -      |                 | Quintic function: Single cycle IO pin              |

| Pin name | LSI    | I/O | Active | Attribute/value | Functional description                           |

|----------|--------|-----|--------|-----------------|--------------------------------------------------|

|          | number |     | level  | at reset        |                                                  |

| GPIOA10  | C9     | 1/0 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | I   | L      |                 | Secondary function: UART CTS (Clear To Send) pin |

|          |        | 0   | -      |                 | Tertiary function: SPI data I/O pin 1 (MISO)     |

|          |        | 1/0 | -      |                 | Quartic function: FTM I/O pin                    |

|          |        | 1/0 | -      |                 | Quintic function: Single cycle IO pin            |

| GPIOA11  | D9     | 1/0 | -      | oZ / -          | Primary function: General-purpose pin            |

|          |        | 0   | L      |                 | Secondary function: UART RTS (Ready To Send)     |

|          |        |     |        |                 | pin                                              |

|          |        | 1/0 | -      |                 | Tertiary function: SPI data I/O pin 2 (MOSI)     |

|          |        | 1/0 | -      |                 | Quartic function: Reserved                       |

|          |        | 1/0 | -      |                 | Quintic function: Single cycle IO pin            |

| GPIOA12  | В6     | 1/0 | -      | oZ / -          | 1Bank Mode: General-purpose pin                  |

|          |        |     |        |                 | 2Bank Mode: System mode input pin (for software) |

|          |        |     |        |                 | 0: User application mode                         |

|          |        |     |        |                 | 1: ISP mode                                      |

# 4-6. Debugger Interface

| Pin name | LSI    | I/O | Active  | Attribute/value | Functional description |

|----------|--------|-----|---------|-----------------|------------------------|

|          | number |     | level   | at reset        |                        |

| SWCK     | G9     | I   | -P or N | 1/-             | SWD clock input pin    |

| SWD      | Н9     | 1/0 | H or L  | 1/-             | SWD data I/O pin       |

# 4-7. Others

| Pin name | LSI    | I/O              | Active | Attribute/value | Functional description                           |

|----------|--------|------------------|--------|-----------------|--------------------------------------------------|

|          | number |                  | level  | at reset        |                                                  |

| RESETN   | C6     | Is               | L      | 1/-             | Hardware reset pin                               |

| XIN      | J7     | los              | P or N | I               | 36 MHz crystal oscillator connection pin 1       |

|          |        |                  |        |                 | * Connect this pin to GND when using an          |

|          |        |                  |        |                 | external clock.                                  |

| XOUT     | J8     | Oos              | P or N | 0               | 36 MHz crystal oscillator connection pin 2       |

|          |        |                  |        |                 | * Connect this pin to GND when using an          |

|          |        |                  |        |                 | external clock.                                  |

| TCXO     | G7     | I <sub>A</sub>   | -      | I               | External clock (TCXO) input pin                  |

|          |        |                  |        |                 | * Connect this pin to GND when using an          |

|          |        |                  |        |                 | oscillator.                                      |

| CXIN     | F9     | I <sub>OSL</sub> | P or N | I               | 32.768 KHz crystal oscillator connection pin 1   |

| CXOUT    | E9     | Oosl             | P or N | 0               | 32.768 KHz crystal oscillator connection pin 2   |

| TRX_SW   | C1     | 0                | H or L | O/L             | Transmit/receive switch pin                      |

|          |        |                  | or OD  |                 |                                                  |

| ANT_SW   | C2     | 0                | H or L | O/L             | Diversity switch pin                             |

|          |        |                  | or OD  |                 |                                                  |

| TEST     | D2     | I                | Н      | 1/-             | Test mode pin                                    |

|          |        |                  |        |                 | * Fixed to "L" input in normal operation         |

| TEST_CPU | C5     | I                | Н      | 1/-             | Test mode pin                                    |

|          |        |                  |        |                 | * Fixed to "L" input in normal operation         |

| MODE0    | B4     | I                | H or L | 1/-             | Remapping pin                                    |

|          |        |                  |        |                 | 0: The program executes from the address 0       |

|          |        |                  |        |                 | in the internal Flash ROM                        |

|          |        |                  |        |                 | 1: The program executes from the boot area       |

|          |        |                  |        |                 | in the internal Flash ROM                        |

| MODE1    | B5     | I                | H or L | 1/-             | Test mode pin                                    |

|          |        |                  |        |                 | * Fixed to "L" input in normal operation         |

| DCNT     | B1     | 0                | H or L | O/L             | External PA control pin                          |

|          |        |                  | or OD  |                 |                                                  |

| VPP      | F7     | -                | Н      | -/-             | High voltage application pin for flash core test |

|          |        |                  |        |                 | * Normally, leave this pin open.                 |

# 4-8. Handling of Unused Pins

See below for handling of unused pins.

| Pin name | Recommended treatment            |

|----------|----------------------------------|

| XOUT     | GND (when TCXO is used)          |

| XIN      | GND (when TCXO is used)          |

| TCXO     | GND (when an oscillator is used) |

| A_MON    | Open                             |

| ANT_SW   | Open                             |

| DCNT     | Open                             |

| VPP      | Open                             |

### 5. Electrical Characteristics

# **TBD**

# \* The electrical characteristics may be changed as a result of evaluation or any other reason.

# 5-1. Absolute Maximum Ratings

| Item                            | Symbol | Conditions     | Rating            | Unit |

|---------------------------------|--------|----------------|-------------------|------|

| Power supply voltage (I/O) (*1) | VDDIO  |                | -0.3 to +4.6      | V    |

| Power supply voltage (RF) (*2)  | VDDRF  |                | -0.3 to +2.0      | V    |

| Digital input voltage           | VDIN   |                | -0.3 to VDDIO+0.3 | V    |

| RF input voltage                | VRFIN  |                | -1.0 to +2.0      | V    |

| Analog input voltage            | VAIN   |                | -0.3 to VDDIO+0.3 | V    |

| Analog input voltage 2 (*3)     | VAIN2  |                | -0.3 to VDDRF+0.3 | V    |

| TCXO input voltage              | VTCXO  |                | -0.3 to +1.75     | V    |

| Digital output voltage          | VDO    | Ta=-40 to 85°C | -0.3 to VDDIO+0.3 | V    |

| RF output voltage               | VRFO   | GND=0V         | -0.3 to VDDRF+1.9 | V    |

| Analog output voltage           | VAO    |                | -0.3 to VDDIO+0.3 | V    |

| Analog output voltage 2 (*4)    | VAO2   |                | -0.3 to VDDRF+0.3 | V    |

| Digital input current           | IDI    |                | -10 to +10        | mA   |

| RF input current                | IRF    |                | -2 to +2          | mA   |

| Analog input current            | IAI    |                | -2 to +2          | mA   |

| Analog input current 2 (*3)     | IAI2   |                | -2 to +2          | mA   |

| TCXO input current              | ITCXO  |                | -2 to +2          | mA   |

| Digital output current          | IDO    |                | -8 to +8          | mA   |

| RF output current               | IRFO   |                | -2 to +60         | mA   |

| Analog output current           | IAO    |                | -2 to +2          | mA   |

| Analog output current 2 (*4)    | IAO2   |                | -2 to +2          | mA   |

| Power dissipation               | PD     | Ta=+25°C       | 300               | mW   |

| Storage temperature             | Tstg   | -              | -55 to +150       | °C   |

- (\*1) VDDIO\_CPU, VDDIO\_RF, VDD\_REG, VDD\_REG\_CPU, VDD\_PA, and VDDIO\_CPURF pins

- (\*2) VDD\_RF, VDD\_IF, VDD\_VCO, and VDD\_CP pins

- (\*3) XIN, TCXO, and CXIN pins

- (\*4) XOUT and CXOUT pins

# 5-2. Recommended Operating Conditions

| Item                                                | Symbol | Conditions                                         | Min.            | Тур.   | Max.            | Unit |

|-----------------------------------------------------|--------|----------------------------------------------------|-----------------|--------|-----------------|------|

| Power supply voltage (I/O)                          | VDDIO  | VDD_IO* pin and VDD_REG* pin                       | 1.8             | 3.3    | 3.6             | V    |

| Power supply voltage (PA)                           | VDD_PA | VDD_PA pin  Transmission power +1  mW mode         | 1.8             | 3.3    | 3.6             | V    |

|                                                     |        | VDD_PA pin 10 mW mode                              | 2.3             | 3.3    | 3.6             | V    |

|                                                     |        | VDD_PA pin 20 mW mode                              | 2.6             | 3.3    | 3.6             | V    |

| Power supply voltage (RF) (*2)                      | VDDRF  | VDD_RF pin, VDD_IF pin, VDD_VCO pin and VDD_CP pin | 1.4             | 1.5    | 1.6             | V    |

| Operational temperature                             | Та     | -                                                  | -40             | +25    | +85             | °C   |

| Digital input rise time                             | tIR1   | Digital input pins (*1)                            | -               | _      | 20              | ns   |

| Digital input fall time                             | tIF1   | Digital input pins (*1)                            | -               | -      | 20              | ns   |

| Digital output load                                 | CDL    | All digital output pins                            | -               | -      | 20              | pF   |

| Master clock 1  36 MHz crystal oscillator frequency | FMCK1  | XIN pin, XOUT pin                                  | -20 ppm<br>(*3) | 36     | +20 ppm<br>(*3) | MHz  |

| Master clock 2 36 MHz TCXO frequency                | FMCK2  | TCXO pin                                           | -20 ppm<br>(*3) | 36     | +20 ppm<br>(*3) | MHz  |

| тсхо                                                | VTCXO  | DC cut                                             | 0.8             | -      | 1.5             | Vpp  |

| Slow clock 32.768 kHz crystal oscillator frequency  | FSCK1  | CXIN pin, CXOUT pin                                | TBD             | 32.768 | TBD             | kHz  |

| RC clock 1 40 MHz RC clock frequency                | FRCK1  |                                                    | TBD             | 40     | TBD             | MHz  |

| RC clock 2 32 kHz RC clock frequency                | FRCK2  |                                                    | TBD             | 32     | TBD             | kHz  |

| SPI clock input frequency                           | FSCLK  | SCLK pin                                           |                 |        | CPUCLK/         | MHz  |

| SPI clock input duty ratio                          | DSCLK  | SCLK pin                                           | 45              | 50     | 55              | %    |

| RF channel frequency                                | FRF    | LNA_P and PA_OUT pins                              | 896             | -      | 960             | MHz  |

- (\*1) Pins described as I or Is in the Input/output column in "Pin Description".

- (\*2) Use the REG\_OUT output of this LSI.

- (\*3) If set to 10 kbps, the maximum is +10 ppm, and the minimum is -10 ppm.

### [Notices]

The electrical characteristics are measured under the recommended operating conditions above, unless otherwise specially noted.

The timings are measured at the 20% and 80% levels of VDDIO, unless otherwise specially noted.

# 5-3. Common Characteristics

| Item                      | Symbol | Conditions                         | Min.           | Typ. (*2) | Max.       | Unit |

|---------------------------|--------|------------------------------------|----------------|-----------|------------|------|

| Supply current (*1)       | IDD1   | Sleep state (*3)                   | -              | 2         | TBD        | μA   |

|                           | IDD2   | Idle state                         | -              | 11        | TBD        | mA   |

|                           | IDD3   | RF receiving state (*4)            | -              | 24        | TBD        | mA   |

|                           | IDD4   | RF transmitting state (1 mW) (*4)  | -              | 22        | TBD        | mA   |

|                           | IDD5   | RF transmitting state (10 mW) (*4) | -              | 33        | TBD        | mA   |

|                           | IDD6   | RF transmitting state (20 mW) (*4) | -              | 41        | TBD        | mA   |

| High level input voltage  | VIH1   | Digital input pin                  | VDDIOx0.75     | -         | VDDIO      | V    |

|                           | VIH2   | XIN pin                            | VDDRFx0.9      | -         | VDDRF      | V    |

| Low level input voltage   | VIL1   | Digital input pin                  | 0 - VDDIOx0.18 |           | V          |      |

|                           | VIL2   | XIN pin                            | 0              | -         | VDDRFx0.1  | V    |

| Schmitt trigger           |        |                                    |                |           |            |      |

| high level decision       | VT+    | Digital pins with schmitt trigger  | -              | 1.2       | VDDIOx0.75 | V    |

| threshold value           |        |                                    |                |           |            |      |

| Schmitt trigger           |        |                                    |                |           |            |      |

| low level decision        | VT-    | Digital pins with schmitt trigger  | VDDIOx0.18     | 0.8       | -          | V    |

| threshold value           |        |                                    |                |           |            |      |

| Input leakage current     | IIH1   | Digital input pin                  | -1             | -         | 1          | μΑ   |

|                           | IIH2   | XIN pin                            | -0.3           | -         | 0.3        | μΑ   |

|                           | IIL1   | Digital input pin                  | -1             | -         | 1          | μΑ   |

|                           | IIL2   | XIN pin                            | -0.3           | -         | 0.3        | μΑ   |

| Tri-state                 | IOZH1  | Digital I/O pin                    | -1             | -         | 1          | μΑ   |

| Output leakage current    | IOZL1  | Digital I/O pin                    | -1             | -         | 1          | μΑ   |

| High level output voltage | VOH    | IOH=-4mA /-2mA (*5)                | VDDIOx0.8      | -         | VDDIO      | ٧    |

| Low level output voltage  | VOL    | IOL=4mA /2mA (*5)                  | 0              | -         | 0.3        | ٧    |

| Pin capacitance           | CIN    | Input pin                          | -              | 6         | -          | pF   |

|                           | COUT   | Output pin                         | -              | 9         | -          | pF   |

|                           | CRFIO  | RF I/O pin                         | -              | 9         | -          | pF   |

|                           | CAI    | Analog input pin                   | -              | 20        | -          | pF   |

- (\*1) The power supply current is the total current of all power supply pins.

- (\*2) The "Typ." value is the center value under the condition of VDDIO = 3.3 V and  $25 \,^{\circ}\text{C}$ .

- (\*3) The "Typ." and "Max." values are under the condition of 25 °C.

- (\*4) Values when the data transfer speed is 100 kpbs and the frequency is 920 MHz.

- (\*5) For DMON pin, IOH is -2 mA/2 mA.

- (\*6) REG\_CORE pin and REG\_OUT pin. REG\_OUT outputs 0 V at sleep state.

### 5-4. RF Characteristics

Modulated data rate : 10 kbps/ 20 kbps/ 40 kbps/ 50 kbps / 100 kbps / 150 kbps/ 200 kbps/ 400 kbps

Modulation method : Binary GFSK

Channel spacing : 200 kHz / 400 kHz / 600 kHz

Frequency range : A frequency from 750 MHz to 1 GHz can be set by changing external circuit constants.

The measurement point is at antenna end specified in the recommended circuits.

Characteristics not described here and ones of 400 kbps (optional) will be provided separately as reference data.

# 5.4.1 [Transmission Characteristics]

| Item                             | Conditions                                       | Min. | Тур. | Max.   | Unit  |

|----------------------------------|--------------------------------------------------|------|------|--------|-------|

|                                  | When set to 20 mW (13 dBm) mode                  | 9    | 13   | 15     | dBm   |

| Transmitter power output         | When set to 10 mW (10 dBm) mode                  | 6    | 10   | 12     | dBm   |

|                                  | When set to 1 mW (0 dBm) mode                    | -4   | 0    | 2      | dBm   |

| Adjustment range of frequency    |                                                  |      |      | 0.050  | 1-11- |

| shift [Fdev] (*1)                |                                                  | -    | -    | 2,250  | kHz   |

| 920 MHz band (920.5 MHz to 928.1 | MHz)                                             |      |      |        |       |

| Occupied bandwidth               | n: Number of unit channels (n = 1, 2, 3, 4 or 5) | -    | -    | 200 *n | kHz   |

| Power at the edges of radio      | 20 mW mode (920.5 MHz to 922.3 MHz)              | -    | -    | -7     | dBm   |

| channel                          | 10 mW mode                                       | -    | -    | -10    | dBm   |

|                                  | 1 mW mode                                        | -    | -    | -20    | dBm   |

| Adjacent channel leakage [ACP]   | 20 mW mode ± 1 ch, bandwidth 200 kHz             | -    | -33  | -15    | dBm   |

|                                  | 10 mW mode ± 1 ch, bandwidth 200 kHz             | -    | -39  | -18    | dBm   |

|                                  | 1 mW mode ± 1 ch, bandwidth 200 kHz              | -    | -47  | -26    | dBm   |

| Unnecessary emission level (20   | 710 MHz or lower, 100 kHz band                   | -    | -65  | -36    | dBm   |

| mW mode)                         | Higher than 710 MHz to 900 MHz, 1 MHz            |      | 70   |        | dD.co |

|                                  | band                                             | 70   |      | -55    | dBm   |

|                                  | Higher than 900 MHz to 915 MHz, 100 kHz          |      | -72  | -55    | dBm   |

|                                  | band                                             | -    |      |        | UDIII |

|                                  | Higher than 915 MHz to 930 MHz, 100 kHz          |      |      |        |       |

|                                  | band                                             |      |      |        |       |

|                                  | (Excluding within 200 + 100xnkHz above and       |      |      |        |       |

|                                  | below the channel frequency, however, within     | -    | -51  | -36    | dBm   |

|                                  | 100 + 100xnkHz above and below for 920.5         |      |      |        |       |

|                                  | MHz to 922.3 MHz. n is the number of             |      |      |        |       |

|                                  | concurrently used channels)                      |      |      |        |       |

|                                  | Higher than 930 MHz to 1000 MHz, 100 kHz         |      | -70  | -55    | dBm   |

|                                  | band                                             | -    | -70  | -55    | dbiii |

|                                  | Higher than 1000 MHz to 1215 MHz, 1 MHz          | _    | -75  | -45    | dBm   |

|                                  | band                                             |      | -10  | -40    | GDIII |

|                                  | Higher than 1215 MHz, 1 MHz band                 | _    | -40  | -30    | dBm   |

|                                  | (Equal to or higher than the 2nd harmonics)      |      | ί)   | 30     | 35.11 |

| 915 MHz band (902 MHz to 928 MH         | z)                                                |     |     |     |     |

|-----------------------------------------|---------------------------------------------------|-----|-----|-----|-----|

| 6dB bandwidth                           | Frequency shift = 171 kHz                         | 500 | -   | -   | kHz |

| Power spectrum density                  | 20 mW mode, frequency shift = 171 kHz, 3 kHz band | -   | -   | 8   | dBm |

| Hannanan aminin lavel (20               | 900 MHz or below                                  | -   | -65 | -56 | dBm |

| Unnecessary emission level (20 mW mode) | Higher than 960 MHz (2nd harmonics or higher)     | -   | -50 | -41 | dBm |

| 868 MHz band (863 MHz to 870 MHz        | z) (*2)                                           |     |     |     |     |

| Unnecessary emission level (10 mW mode) | Higher than 1000 MHz (2nd harmonics or higher)    | -   | -35 | -30 | dBm |

<sup>\*1</sup> While the adjustment range is described as above, the possible maximum value depends on the RF channel frequency to be used. RF channel frequency ± frequency shift should not include a multiple of 36 MHz (864 MHz, 900 MHz, 936 MHz, and so on). Example) For 902 MHz, 2,000 kHz can be set at a maximum.

<sup>\*2 863.5</sup> MHz to 866.2 MHz cannot be used. For details, refer to "Setting channel frequency" in ML7396B Data Sheet.

# 5.4.2 [Reception Characteristics]

| Item                                      | Conditions                                    | Min. | Тур.  | Max. | Unit |

|-------------------------------------------|-----------------------------------------------|------|-------|------|------|

| 920 MHz band (920.5 MHz to 928            | 3.1 MHz)                                      |      | •     | 1    |      |

| Minimum receiver sensitivity              | 50 kbps mode (*1)                             | -    | -108  | -102 | dBm  |

| BER < 0.1%                                | 100 kbps mode (*1)                            | -    | -106  | -100 | dBm  |

|                                           | 200 kbps mode (*1)                            | -    | -102  | -97  | dBm  |

| Maximum receiver input level              | 50 kbps mode, 100 kbps mode, 200 kbps mode    | 0    | -     | -    | dBm  |

| Receiver C/I adjacent                     | 50 kbps mode                                  | 20   | 35    | -    | dB   |

| interference                              | 100 kbps mode                                 | 20   | 35    | -    | dB   |

|                                           | 200 kbps mode                                 | 20   | 35    | -    | dB   |

| Receiver C/I second adjacent              | 50 kbps mode                                  | 30   | 45    | -    | dB   |

| interference                              | 100 kbps mode                                 | 30   | 45    | -    | dB   |

|                                           | 200 kbps mode                                 | 30   | 45    | -    | dB   |

| Minimum energy detection level (ED value) |                                               | -    | -     | -100 | dBm  |

| Energy detection range                    | Dynamic range                                 | 60   | 70    | -    | dB   |

| Energy detection accuracy                 |                                               | -6   | -     | +6   | dB   |

| Collateral emission level                 | 710 MHz or lower, 100 kHz band                | -    | <-93  | -54  | dBm  |

| ARIB T108 measurement                     | Higher than 710 MHz to 900 MHz, 1 MHz band    | -    | <-83  | -55  | dBm  |

| condition                                 | Higher than 900 MHz to 915 MHz, 100 kHz band  | -    | <-93  | -55  | dBm  |

|                                           | Higher than 915 MHz to 930 MHz, 100 kHz band  | -    | -63   | -54  | dBm  |

| 915.9MHz to 916.9MHz                      | Higher than 930 MHz to 1000 MHz, 100 kHz band | -    | <-93  | -55  | dBm  |

| 920.5MHz to 929.7MHz                      | Higher than 1000 MHz, 1 MHz band              | -    | -57   | -47  | dBm  |

| 915 MHz band (902 MHz to 928 N            | ИHz)                                          |      |       |      |      |

|                                           | 100 kbps mode (modulation index = 1) (*1)     | -    | -106  | -99  | dBm  |

|                                           | 150 kbps mode (modulation index = 0.5) (*1)   | -    | -102  | -96  | dBm  |

| Minimum receiver sensitivity              | 200 kbps mode (modulation index = 1) (*1)     | -    | -102  | -96  | dBm  |

| BER < 0.1%                                | 100 kbps mode (frequency shift: 171 kHz)      | -    | -100  | -87  | dBm  |

|                                           | 150 kbps mode (frequency shift: 171 kHz)      | -    | -97.5 | -84  | dBm  |

|                                           | 200 kbps mode (frequency shift: 171 kHz)      | -    | -96.5 | -83  | dBm  |

| 868 MHz band (863 MHz to 870 M            | ИНz) (*2)                                     |      | T     |      | 1    |

| Minimum receiver sensitivity              | 50 kbps mode (*1)                             | -    | -108  | -102 | dBm  |

| BER < 0.1%                                | 100 kbps mode (*1)                            | -    | -106  | -100 | dBm  |

| DLIX > 0.170                              | 200 kbps mode (*1)                            | -    | -102  | -97  | dBm  |

| Collateral emission level                 | 1000 MHz or below (local frequency)           | -    | -63   | -57  | dBm  |

|                                           | Frequency over 1000 MHz                       | -    | -57   | -47  | dBm  |

<sup>\*1</sup> When normal bandwidth mode (NBO\_SEL = 0) is set. See the [DATA\_SET] register (B0 0x47).

<sup>\*2 863.5</sup> MHz to 866.2 MHz cannot be used. For details, refer to "Setting channel frequency" in ML7396B Data Sheet.

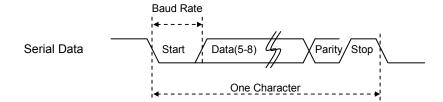

# 5-5. UART Interface Characteristics

| Item      | Symbol            | Conditions                     | Min | Тур    | Max | Unit |

|-----------|-------------------|--------------------------------|-----|--------|-----|------|

| Baud Rate | F <sub>BAUD</sub> | Load<br>capacitance<br>CL=20pF | -   | 115200 | -   | ns   |

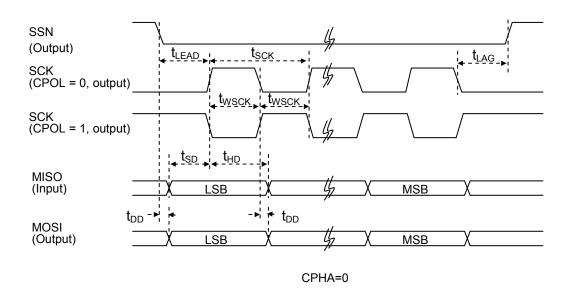

# 5-6. SPI Interface Characteristics

# 5-6-1.Master

| Item                          | Symbol                          | Conditions | Min                   | Тур | Max                   | Unit |

|-------------------------------|---------------------------------|------------|-----------------------|-----|-----------------------|------|

| Serial clock cycle time       | t <sub>SCK</sub>                | -          | 100                   | -   | -                     | ns   |

| Serial clock High/Low time    | t <sub>WSCK</sub>               | -          | 48                    | -   | -                     | ns   |

| Data delay time (output)      | t <sub>DD</sub>                 | -          | -                     | -   | 50                    | ns   |

| Data setup time (input)       | t <sub>SD</sub>                 | CL=20pF    | -                     | -   | 48                    | ns   |

| Data hold time (input)        | t <sub>HD</sub>                 | -          | 0                     | -   | -                     | ns   |

| SSN-SCK lead time             | t <sub>LEAD</sub>               | -          | 0.5* t <sub>SCK</sub> | -   | 1.6* t <sub>SCK</sub> | ns   |

| SCK-SSN lag time              | t <sub>LAG</sub>                | -          | 0.5* t <sub>SCK</sub> | -   | 1.5* t <sub>SCK</sub> | ns   |

| SSN H minimum guaranteed time | t <sub>WSSH</sub>               | -          | 1* t <sub>SCK</sub>   | -   | 511* t <sub>SCK</sub> | ns   |

| SPI bus input/output          | + +                             |            |                       |     | 25                    | 20   |

| rise/fall time                | t <sub>R</sub> , t <sub>F</sub> | -          | -                     | -   | 25                    | ns   |

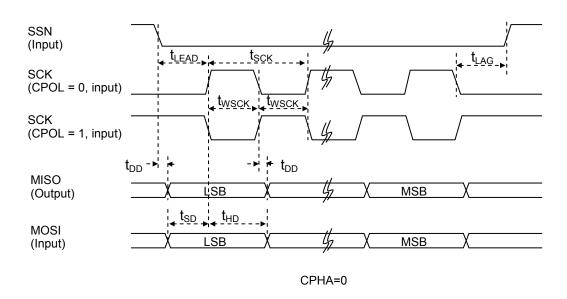

# O SPI master mode timing (CPHA = 0)

# O SPI master mode timing (CPHA = 1)

<sup>\*</sup>Note: For CPHA and CPOL, refer to the register descriptions in "7-8. SPI".

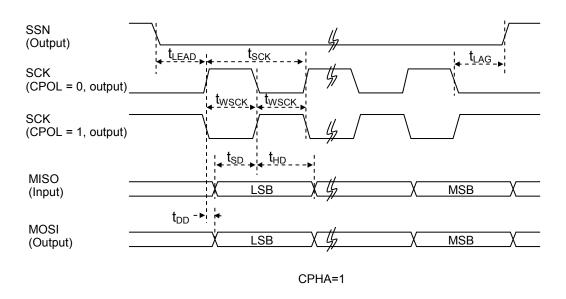

# 5-6-2.Slave

| Item                       | Symbol            | Conditions | Min                   | Тур | Max | Unit |

|----------------------------|-------------------|------------|-----------------------|-----|-----|------|

| Serial clock cycle time    | t <sub>sck</sub>  | -          | 100                   | -   | -   | ns   |

| Serial clock High/Low time | twsck             | -          | 50                    | -   | -   | ns   |

| Data delay time (output)   | t <sub>DD</sub>   | -          | -                     | ı   | 50  | ns   |

| Data setup time (input)    | t <sub>SD</sub>   | CL=20pF    | -                     | ı   | 50  | ns   |

| Data hold time (input)     | t <sub>HD</sub>   | -          | 10                    | ı   | ı   | ns   |

| SSN-SCK lead time          | t <sub>LEAD</sub> | -          | 0.5* t <sub>SCK</sub> | 1   | 1   | ns   |

| SCK-SSN lag time           | t <sub>LAG</sub>  | -          | 0.5* t <sub>SCK</sub> | -   | -   | ns   |

# O SPI slave mode timing (CPHA = 0)

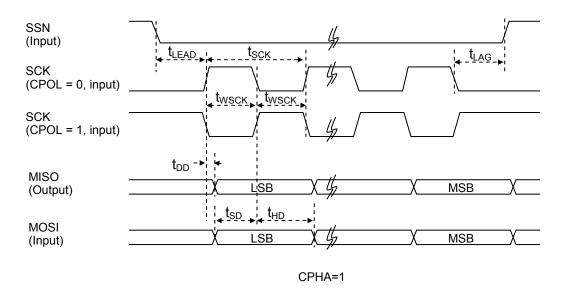

# O SPI slave mode timing (CPHA = 1)

<sup>\*</sup>Note: For CPHA and CPOL, refer to the register descriptions in "7-8. SPI".

### 5-7. I2C Interface Characteristics

| Item                      | Symbol | Conditions  | Min. | Тур. | Max. | Unit |

|---------------------------|--------|-------------|------|------|------|------|

| SCL clock frequency       | Fscl   |             | 1    | 1    | 400  | kHz  |

| SCL H pulse width         | Twsckh | Conditions  | 600  | -    | -    | ns   |

| SCL L pulse width         | Twsckl | of          | 1300 | -    | -    | ns   |

| Start condition hold time | TDSTAH | load        | 450  | -    | -    | ns   |

| Stop condition setup time | Tostos | capacitance | 575  | -    | -    | ns   |

| SDA output hold time      | TDSOH  | CL=         | 0    | -    | -    | ns   |

| SCL output delay time     | Tosos  | 20pF        | 600  | -    | -    | ns   |

| SDA input setup time      | Tosis  |             | 100  | -    | -    | ns   |

| SDA input hold time       | Tosih  |             | 0    | -    | -    | ns   |

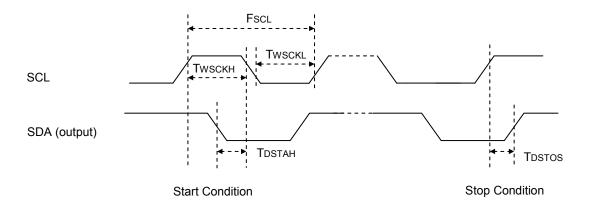

# O Stop condition (SDA fall at SCL = 1), Start condition (SDA rise at SCL = 1)

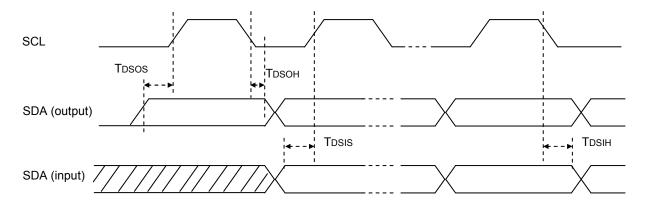

# O Transmission/reception

# 5-8. A/D Conversion Characteristics

| Item                       | Symbol | Conditions                  | Min. | Тур. | Max.  | Unit   |

|----------------------------|--------|-----------------------------|------|------|-------|--------|

| Number of bits             | Nsar   | Number of SAR register bits | -    | 10   | -     | bits   |

| Resolution                 | RES    | VIN=0 to VDDIO              | 1.8  | -    | 3.6   | mV/LSB |

| Input voltage range        | VIN    |                             | 0    | -    | VDDIO | V      |

| Zero-scale error           | Ezs    | 10-bit accuracy             | -2.0 | -    | 2.0   | LSB    |

| Full-scale error           | EFS    | 10-bit accuracy             | -2.0 | -    | 2.0   | LSB    |

| Differential non-linearity | DNS    | 10-bit accuracy             | -2.0 | -    | 2.0   | LSB    |

| Integral non-linearity     | INS    | 10-bit accuracy             | -2.0 | -    | 2.0   | LSB    |

| Conversion time            | TL     | Clock cycle<br>= 400 ns     | 10   | -    | -     | us     |

# 5-9. Temperature Sensor Characteristics

| Item                 | Symbol | Conditions              | Min. | Тур. | Max. | Unit  |

|----------------------|--------|-------------------------|------|------|------|-------|

| Accuracy             | ETS    | TBD                     | -5   | -    | +5   | °C    |

| Temperature gradient | Тс     | TBD                     | -    | -3.5 | -    | mV/°C |

| Output potential     | VTS    | 25°C                    | -    | 760  | -    | mV    |

| Conversion time      | TL     | Clock cycle<br>= 400 ns | 10   | -    | -    | us    |

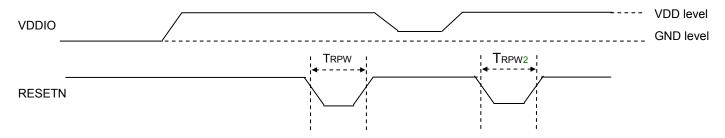

### 5-10. Reset Characteristics

| Item                                 | Symbol     | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------|------------|------------|------|------|------|------|

| RESETN activation time (pulse width) | т          |            | 200  |      |      | 20   |

| (When starting from VDDIO=0V)        | $T_RPW$    | -          | 200  | -    | _    | ns   |

| RESETN pulse time 2 (*1)             | <b>T</b>   | VDD-10V    | F00  |      |      |      |

| (When starting from VDDIO≠0V)        | $T_{RPW2}$ | VDD>1.8 V  | 500  | -    | -    | us   |

- (\*1) When starting from VDDIO≠0V, input a pulse to the RESETN signal after VDDIO exceeds 1.8 V.

- (\*2) This is reset by the power-on reset circuit built in the LSI at power-on.

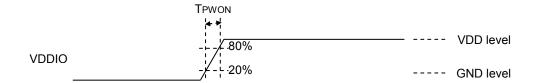

### 5-11. Power-On Characteristics

| Item                     | Symbol            | Conditions              | Min. | Typ. | Max. | Unit |

|--------------------------|-------------------|-------------------------|------|------|------|------|

| Power-on time difference | T <sub>PWON</sub> | At power on             | -    | -    | 5    | ms   |

|                          |                   | (All power supply pins) |      |      |      |      |

# 6. Functional Description

#### \* For the RF block, refer to ML7396B Data Sheet.

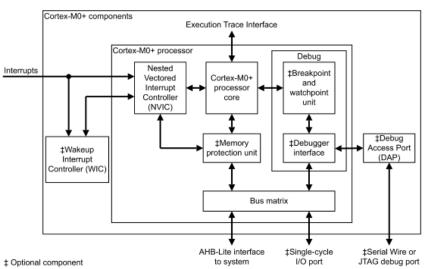

#### 6-1.CPU (Cortex-M0+)

A RISC processor manufactured by ARM.

It is a 32-bit processor for small size and low power consumption applications and has a 2-stage pipeline configuration. It implements the ARMv6-M architecture, and operates with 16-bit Thumb instructions and Thumb-2 instructions.

The configuration is as follows:

- Little-Endian

- Number of break points: 4

- Number of watch points: 2

- SysTick timer, a 24-bit system timer, is included

- NVIC (Nested Vectored Interrupt Controller) is included

- Multiplier: High-speed (1-cycle) hardware multiplier is provided

- SLEEP/DEEPSLEEP supported

- WFI (Wait for Interrupts)/WFE (Wait for Events) supported

- Relocatable vector table

- MTB-M0+ supported

Cortex-M0+ Schematic Diagram

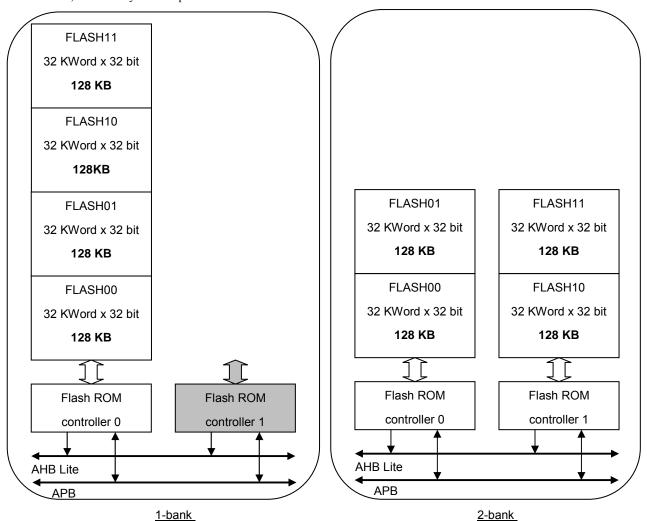

#### 6-2.Flash ROM Controller

Flash ROM controllers are included. The boot from the Flash ROM is possible.

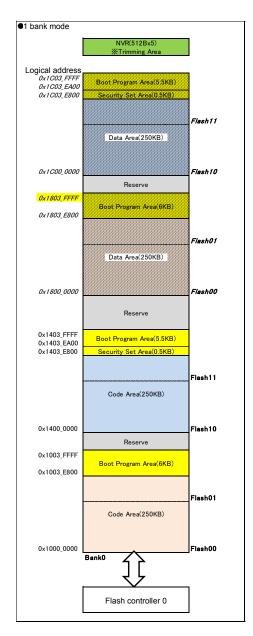

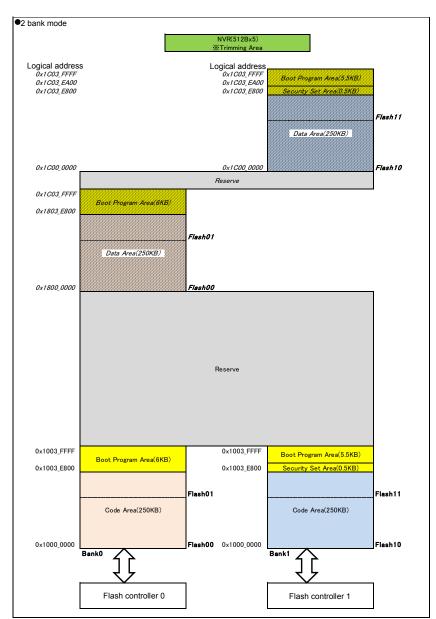

- For the Flash ROM area of 512 KB, the 256 KB x 2 bank configuration or the 512 KB x 1 bank configuration can be selected.

- For each bank, a Flash ROM controller is connected.

- Rewriting from the debugger through the debug port (SWD) is possible.

- In the 2-bank configuration, the program of one bank can be rewritten dynamically

- while the other CPU is running on another bank.

- In the 1-bank configuration, a rewriting program can be started from the ISP area or SRAM area.

- It is possible to perform the 1-word rewrite, sector erase, block erase, or chip erase.

- The bank can be assigned to the remapping area (4 Kbytes) starting at 0x00000000 by the remapping function.

- The ROM area is divided into the trimming area to store the trimming value of analog macro, boot program area to store the starting program such as ISP, security area to store the security setting, and user area, and the trimming area, boot program area, and security area are protected.

- \* At power-on, the system always starts in 1 bank mode.

- \* In 2 bank mode, only the bank 0 side can be rewritten from the debugger.

- \* Only when both of the two Flash ROM controllers are not executing the processing, the transition to Sleep or DeepSleep is possible.

### 6-3.Interrupt Controller

The NVIC (Nested Vector Interrupt Controller) is included in Cortex-M0+. The following interrupt sources are provided:

- 30 IRQs

#### 6-4.SRAM IF

The SRAM IF of 64 KB is provided.

#### 6-5.AHB-lite Bus

An AMBA 3 AHB-lite bus is included, to which an AHB slave can be connected.

### 6-6.APB Bus

An AMBA 2.0 APB bus is included, to which an APB slave can be connected.

### 6-7.Single-cycle I/O Port

A single-cycle I/O port which can be accessed in one cycle is included.

### 6-8.Debug Port

The SWD (2-wire serial wire debug port) is included as an interface for communicating with the debugger.

The internal resources can be accessed through this interface.

It also can be used for writing to on-chip memory such as a Flash ROM from the debugger.

#### 6-9.MTB

The MTB (Micro Trace Buffer) which enables the execution trace of Cortex-M0+ is included. This MTB shares the data RAM as the memory for trace.

### 6-10. Clock

This section describes the following three clocks:

- System clock system

- Debug port clock system

- Peripheral clock system

# 6.10.1 System Clock System

Clocks supplied to the CPU core and bus.

The maximum frequency is 40 MHz.

There are three derived clocks that are gated depending on the processor operation state.

| Clock | Name               | Description                                                                               |  |  |

|-------|--------------------|-------------------------------------------------------------------------------------------|--|--|

| CLK   | Source Clock       | The source clock.                                                                         |  |  |

|       |                    | This clock can operate at up to 40 MHz with the internal PLL (multiplying/dividing of N/M |  |  |

|       |                    | ratio) or internal RC OSC.                                                                |  |  |

| FCLK  | Free Running Clock | This clock can be stopped during the DEEPSLEEP state. It is supplied during the SLEEP     |  |  |

|       |                    | state. This is used by the Wakeup Interrupt Controller and Power Management Unit in the   |  |  |

|       |                    | Cortex-M0+.                                                                               |  |  |

| SCLK  | Processor System   | This clock is stopped during the DEEPSLEEP state. It is supplied during the SLEEP state.  |  |  |

|       | Clock              | This clock (or its derived clock) should be connected to any device that needs to operate |  |  |

|       |                    | during the SLEEP state.                                                                   |  |  |

| HCLK  | AHB Clock          | This clock is stopped during the DEEPSLEEP or SLEEP state. This clock (or its derived     |  |  |

|       |                    | clock) should be connected to any device that does not operate during the SLEEP state.    |  |  |

| DCLK  | Debug domain       | This clock is always supplied when the Debugger is connected.                             |  |  |

|       | clock              |                                                                                           |  |  |

#### **CPU Clock System**

#### 6.10.2 Debug Port Clock System

This clock system is supplied to JTAG I/F.

It is supplied from the debugger outside the chip.

The maximum frequency of the debug port clock system is 10 MHz.

### 6.10.3 Peripheral Clock System

This clock system is supplied to peripherals.

#### 6.10.3.1 UART Reference Clock

This is the reference clock for baud rate generation. <u>To reduce the baud rate error</u>, this clock frequency needs to be adjusted. <u>Example</u>) When the reference clock frequency = 40.57 MHz (32.768 KHz X'tal OSC multiplied by 1238 by PLL), the baud rate error is about 0.1% at 115.2 kbps.

#### 6.10.3.2 SPI Reference Clock

This clock is the source for generating the SPI(Master/Slave) serial clock. The frequency of the clock for serial communication is lower than 1/2 of the frequency of this reference clock.

#### 6.10.3.3 SSIS Sampling Clock

This clock is used for the data transmission/reception in SSIS (SSI Slave, which is available only in the ISP function). It is used in the ISP function. The frequency of the clock for serial communication is lower than 1/10 of the frequency of this reference clock.

#### 6.10.3.4 WDT Clock

This clock drives the watchdog timer.

It can measure the time of about hundreds of  $\mu sec$  to dozens of msec.

32.768 kHz input, 32 KHz CR input or source clock divide can be selected.

#### 6.10.3.5 GPIO Debounce Clock

The debounce circuit that performs sampling at a fixed interval is implemented to eliminate the effect of noise and chattering when using the input signal from GPIO as an external interrupt source. This clock is used by the debounce circuit.

#### 6.10.3.6 Timer Clock

This clock is used by the standard 32-bit timer.

32.768 kHz X'tal input, 32 KHz CR input or source clock divide can be selected.

#### 6.10.3.7 RTC Clock

This clock is used by the real time clock (RTC).

32.768 kHz X'tal input, 32 KHz RC input or source clock divide can be selected.

#### 6.10.3.8 Flexible Timer Clock

This clock is used by the flexible timer (FTM).

32.768 kHz input or 32 KHz RC input can be selected.

#### 6.10.3.9 I2C Reference Clock

The reference clock for generating a serial clock for I2C communication. The I2C clock depends on the serial communication mode (Standard mode, Fast mode) that it supports.

The frequency of I2C reference clock must be higher than that of system clock.

### Minimum Frequency of I2C Reference Clock

| Mode          | Minimum frequency | I2C bus ratio |

|---------------|-------------------|---------------|

| Standard mode | 2.7MHz            | 100kbps       |

| Fast mode     | 12MHz             | 400kbps       |

#### 6.10.3.10 Flash ROM Controller Clock

This clock is used by the flash ROM controller.

#### 6.10.3.11 DIO Clock

This clock is used by DIO.

### 6.10.3.12 RAND\_GEN Clock

This clock is used by RAND\_GEN (pseudo-random number generation circuit).

### 6.10.3.13 CLK\_Timer Reference Clock

This clock counts the low-speed clock with CLK\_Timer.

40 MHz RC clock output, RF clock output or PLL clock output can be selected.

### 6.10.3.14 SysTick Timer Clock

This clock drives the SysTick timer in Cortex-M0+.

It is usually 1 MHz. It is 32 KHz at the CPU low speed (32 KHz) mode.

#### 6.10.3.15 AES Clock

This clock is used by AES.

| 6 | 10 | 3 | 16 | ΔГ | C. | CI | ock |  |

|---|----|---|----|----|----|----|-----|--|

|   |    |   |    |    |    |    |     |  |

This clock is used by the ADC controller. It is the ADC sampling frequency (Max = 2.5 MHz) or less.

#### 6.10.3.17 TEMP Clock

This clock is used by the temperature sensor controller. It is the ADC sampling frequency (Max = 2.5 MHz) or less.

#### 6.10.3.18 LVD Clock

This clock is used by the low voltage detection controller.

#### 6.10.3.19 DMAC Clock

This clock is used by the DMA controller.

### 6.10.3.20 Flash DMA Clock

This clock is used by the flash DMA controller.

#### 6-11. Reset

The relationship between the reset system and the reset target is shown in the table "Reset Causes and Reset Targets" below.

The reset causes include hardware reset, SYSRESETREQ reset of Cortex-M0+, peripheral reset, debugger reset without the debugger connected, WDT reset, voltage detection reset and reset at CPU LOCKUP.

The hardware reset occurs during the initial operation of hardware including reset by an external pin or reset at power-on triggered by power-on detection. When a hardware reset occurs, the reset circuit asserts the reset systems connected to all initializable circuits and initializes those circuits.

The SYSRESETREQ reset of Cortex-M0+ occurs when the SYSRESETREQ bit of Application Interrupt and Reset Control Register (AIRCR) within Cortex-M0+ is set from the CPU or debugger. The CPU, peripherals, bus, and memory IF are initialized, while the program fetches the reset exception vector.

The peripheral reset resets only the target peripheral by setting the bit assigned to each peripheral in the peripheral reset registers.

When the debugger is not connected, the debug circuit is always in reset state to prevent unnecessary switching or malfunctions caused by the debug circuit.

The WDT reset, voltage detection reset and the automatic reset at CPU LOCKUP initialize all initializable circuits except the CPU status register and the debug circuit.

## **Reset Causes and Reset Targets**

| Reset           |          |       | Res             | set target     |            |           |

|-----------------|----------|-------|-----------------|----------------|------------|-----------|

| system          | Hardware | LVD   | WDT             | SYSRESETREQ    | Peripheral | When the  |

|                 | reset    | reset | reset/voltage   | bit set of     | reset      | debugger  |

|                 | Power-on |       | detection       | Cortex-M0+     |            | is not    |

|                 | reset    |       | reset/automatic | AIRCR register |            | connected |

|                 |          |       | reset at CPU    |                |            |           |

|                 |          |       | LOCKUP          |                |            |           |

| CPU_ST          | 0        | -     | -               | -              | -          | -         |

| register        |          |       |                 |                |            |           |

| Control         | 0        | 0     | 0               | -              | -          | -         |

| registers with  |          |       |                 |                |            |           |

| the Sticky      |          |       |                 |                |            |           |

| attribute,      |          |       |                 |                |            |           |

| excluding the   |          |       |                 |                |            |           |

| CPU_ST          |          |       |                 |                |            |           |

| register        |          |       |                 |                |            |           |

| System          | 0        | 0     | 0               | -              | -          | -         |

| hardware        |          |       |                 |                |            |           |

| such as clock   |          |       |                 |                |            |           |

| control circuit |          |       |                 |                |            |           |

| and power       |          |       |                 |                |            |           |

| management      |          |       |                 |                |            |           |

| circuit         |          |       |                 |                |            |           |

| CPU             | 0        | 0     | 0               | 0              | -          | -         |

| AHB             |          |       |                 |                |            |           |

| bus/peripheral  |          |       |                 |                |            |           |

| APB             | 0        | 0     | 0               | 0              | 0          | -         |

| bus/peripheral  |          |       |                 |                |            |           |

| SingleCycleIO   | 0        | 0     | 0               | 0              | 0          | -         |

| bus/peripheral  |          |       |                 |                |            |           |

| Flash ROM       | 0        | 0     | 0               | -              | -          | -         |

| RF              | 0        | 0     | -               | -              | 0          | -         |

| Debug reset     | 0        | -     | -               | -              | -          | 0         |

### 6-12. Power Management

Low power consumption is realized by clock control and power control.

### 6.12.1 Operation Mode

The power management function of this LSI has the following features:

- The low power consumption states, SLEEP and DEEPSLEEP, are supported.

- The clocks are stopped depending on each low power consumption state.

The following basic power states are defined in this LSI:

| Operation | Operation state | e                                                           | Current     | Return to Active | mode    |

|-----------|-----------------|-------------------------------------------------------------|-------------|------------------|---------|

| mode      |                 |                                                             | consumption |                  |         |

|           | Power mode      | LSI                                                         | Current     | Method           | Time    |

|           | of Cortex-M0+   |                                                             | consumption |                  |         |

| Active    | RUN             | All clocks are supplied. However, the clock delivery to     | 11mA        | -                | _       |

|           |                 | peripherals (including RF) can be set to on/off by the      |             |                  |         |

|           |                 | register.                                                   |             |                  |         |

| SLEEP     | Sleep           | AHB bus clock (FlashROM/RAM) is stopped. The clock          | 5mA         | Interrupt from a | 75nsec  |

|           |                 | delivery to peripherals (including RF) can be set to on/off |             | peripheral.      |         |

|           |                 | by the register.                                            |             | Start the        |         |

|           |                 |                                                             |             | debugger         |         |

| DEEPSLEEP | DeepSleep       | The main clock is stopped. The clock delivery to sub        | 2μΑ         | Interrupt from a | 150usec |

|           |                 | clock system peripherals (RTC, TIMER, etc.) can be set      |             | sub clock        |         |

|           |                 | to on/off by the register.                                  |             | system           |         |

|           |                 | The power supply to FlashROM/SRAM/non-sub clock             |             | peripheral.      |         |

|           |                 | system peripherals/RF can be set to on/off with the         |             | Start the        |         |

|           |                 | register setting.                                           |             | debugger         |         |

## 6.12.2 Power Separation

This LSI can operate at low power consumption by turning off some power supplies in the LSI during DEEPSLEEP state.

The following function blocks can be set to power on/off.

| Function | Target range                                     | Setting register       | Remarks |

|----------|--------------------------------------------------|------------------------|---------|

| block    |                                                  |                        |         |

| SRAM     | Unit of 32 KB (up to 64 KB)                      | SLEEP setting register |         |

|          |                                                  | (0x40050014) bits 8-9  |         |

| FLASH    | Whole 512 KB area                                | SLEEP setting register |         |

|          |                                                  | (0x40050014) bit 10    |         |

| RF       | Whole RF chip area                               | SLEEP setting register |         |

|          |                                                  | (0x40050014) bit 11    |         |

| Logic    | CPU, FlashCnt, STD GPIO, AES, DAMC, FlashDMA,    | SLEEP setting register |         |

|          | UART, SPI, I2C, RAND, SSIS, FTM, CLK Timer, DIO, | (0x40050014) bit 12    |         |

|          | ADC, TEMP                                        |                        |         |

### 6-13.System Control

System Control is a block which controls the whole system (including the control of clocks, reset, remapping, interrupt, and SysTick timer) and displays the ID information specific to each chip and the CPU status information.

### 6.13.1 Clock Control

- Selects the clock source (CR40M, RF clock, XTAL32K, CR32K, or PLL).

- Stops/resumes the clock of each peripheral.

- Sets the operation (automatically stops the clock) when the CPU goes to the low power consumption state (SLEEP or DEEPSLEEP) for each peripheral.

- Changes the frequency of system clock or clock supplied to each peripheral.

#### 6.13.2 Reset Control

- Able to reset individual peripherals.

- Sets the operation when the CPU goes to the LOCKUP state.

- Indicates that the CPU is initialized by the reset due to LOCKUP or the reset caused by low voltage detection or watchdog timer.

### 6.13.3 Information Display

Displays the ID information specific to each chip to distinguish individual chips.

### 6.13.4 Remapping Control

Selects a device to be placed in the remapping area on the address space.

### 6.13.5 Cortex-M0+ Control

Changes the settings of Nested Vectored Interrupt Controller (NVIC) and SysTick timer mounted in Cortex-M0+.

### 6.13.6 Boot Program

The boot program stored in the boot program area.

For details, refer to "ML7416 Boot\_Programing Function Specifications".

#### 6-14.Peripheral

This LSI implements the following peripherals: UART, SPI, SSIS, WDT, GPIO (APB GPIO), SingleCycleIO (STD GPIO), timer, RTC, flexible timer (FTM), I2C, Flash controller, DIO, RAND\_GEN, CLK\_Timer, AES, ADC, thermometer (TEMP), low voltage detection (LVD), DMAC, and Flash DMA.

#### 6.14.1 UART

A start-stop synchronous serial communication interface which has functions equivalent to the industry standard 16550. The features are shown below.

- Includes a 16-byte FIFO for each of transmission and reception.

- Full-duplex communication is possible.

- Includes a programmable baud rate generator. Note that the baud rate is the same for transmission and reception.