## 180-Channel LCD Driver with Built-in RAM for LCD Dot Matrix Displays

# **GENERAL DESCRIPTION**

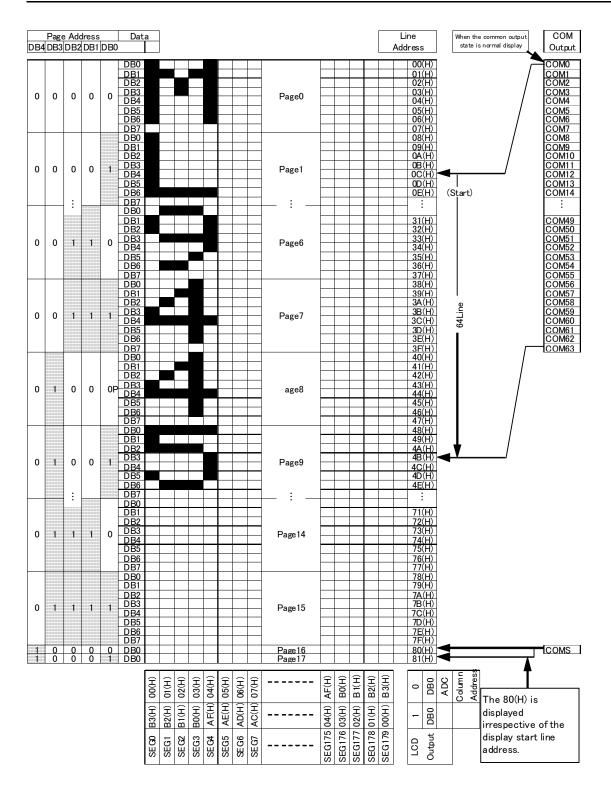

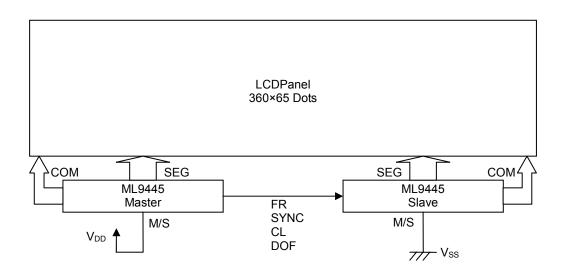

The ML9445 is an LSI for dot matrix graphic LCD devices carrying out bit map display. This LSI can drive a dot matrix graphic LCD display panel under the control of an 8- bit microcomputer (hereinafter des cribed MPU). Since all the functions necessary for driving a bit map type LCD device are incorporated in a single chip, using the ML9445 makes it possible to realize a bit map type dot matrix graphic LCD display system with only a few chips. Since the bit map method in which one bit of display RAM data turns ON or OFF one dot in the display panel, it is possible to carry out displays with a high degree of freedom such as Chinese character displays, etc. With one chip, it is possible to construct a graphic display system with a maximum of  $65 \times 180$  dots.

The ML9445 has 65 common signal outputs and 180 segment signal outputs and one chip can drive a display of up to  $65 \times 180$  dots.

# **FEATURES**

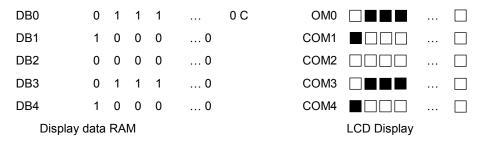

- Direct display of the RAM data using the bit map method Display RAM data "1" ... Dot is displayed Display RAM data "0" ... Dot is not displayed (during forward display)

- Dis play RAM capacity

- $65 \times 180 \times 2 = 23.400$  bits

- LCD Drive circuits

- 65 common outputs, 180 segment outputs

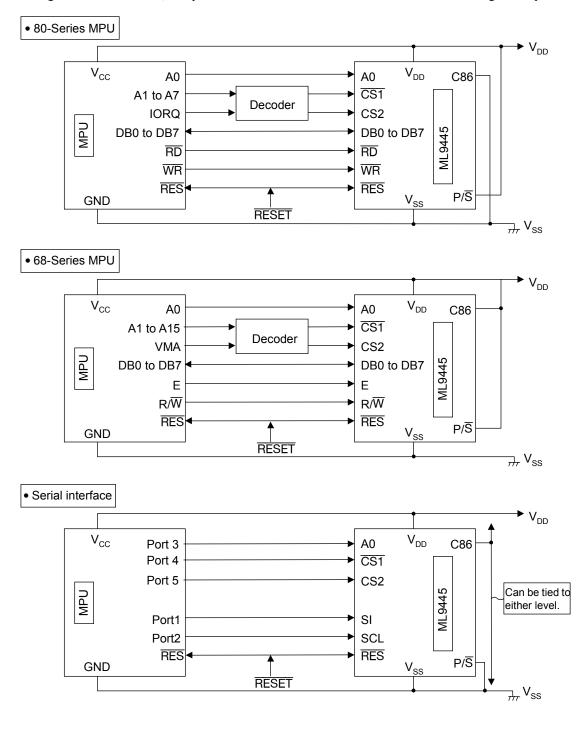

- MPU interface: Can select an 8-bit parallel or serial interface or  $I^2C$  (Write Only)

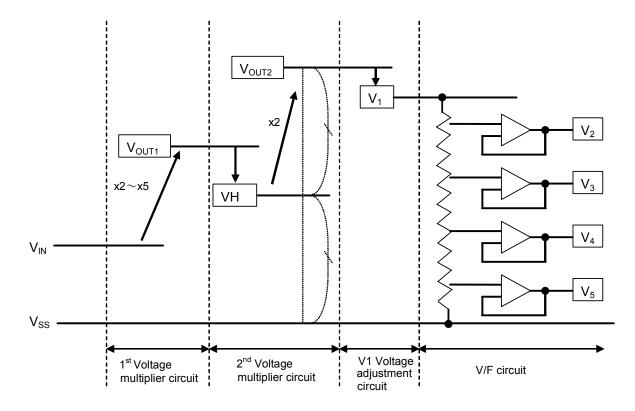

- Built-in voltage multiplier circuit for the LCD drive power supply

- Built-in LCD drive voltage adjustment circuit

- Built-in LCD drive bias generator circuit

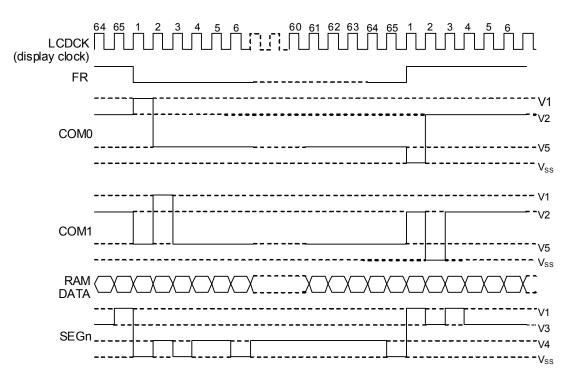

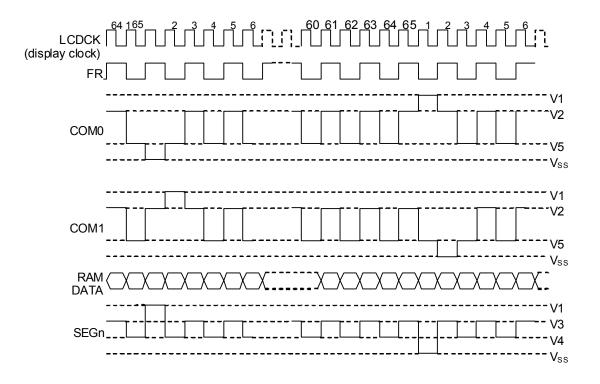

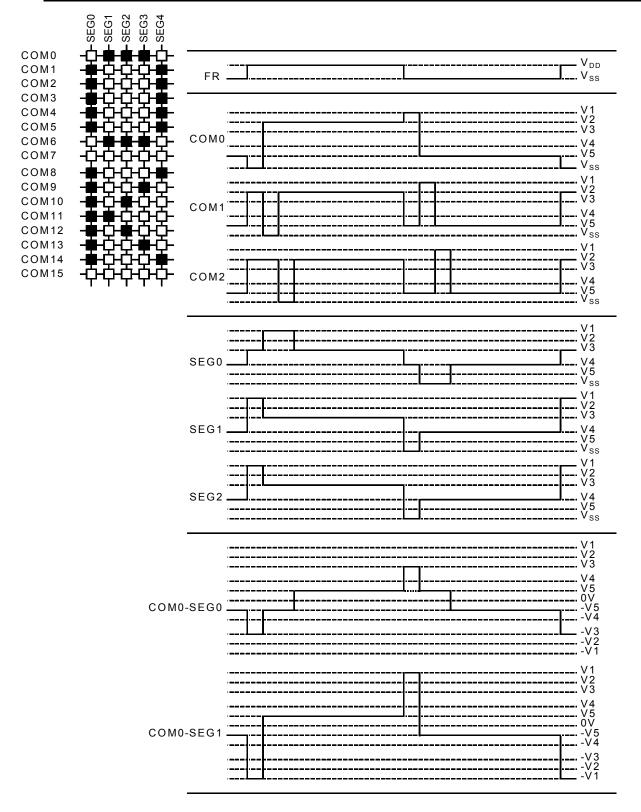

- Can select frame reversal drive or line reversal drive by command

- Built-in oscillator circuit (Internal RC oscillator/external clock input)

- A variety of commands Read/write of d isplay d ata, d isplay O N/OFF, forward/reverse d isplay, all d ots O N/all dots OFF, set p age address, set display start address, etc.

- P ower supply voltage Logic power supply:  $V_{DD}$ - $V_{SS} = 2.7$  V to 5.5 V Voltage multiplier reference voltage:  $V_{IN}$ - $V_{SS} = 2.7$  V to 5.5 V (2- to 5-time multiplier available) LCD Drive voltage:  $V_{BI}$ - $V_{SS}$  = 6.0 to 18.5 V

- Package: ML9445DVWA Gold bump chip (Bump hardness: Low, DV)

- This device is not resistant to radiation and light.

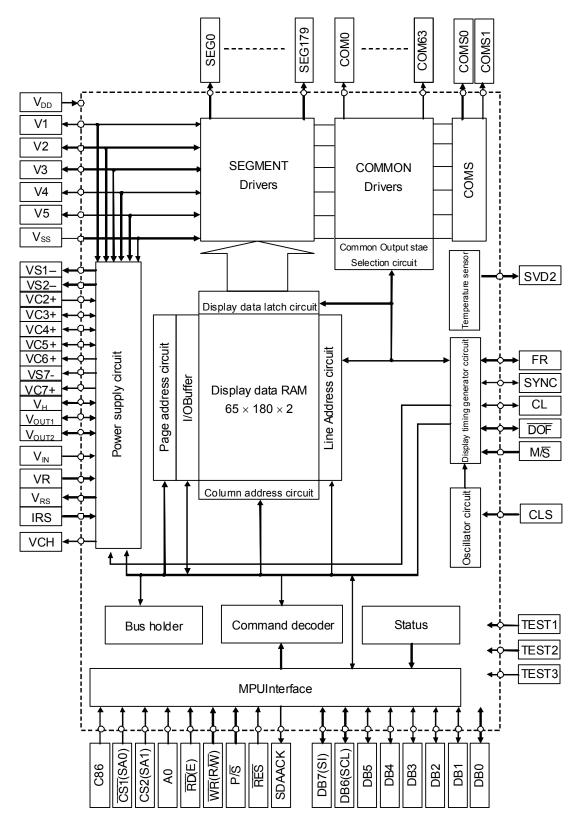

## **BLOCK DIAGRAM**

|                                   |                  | 36                    |                                |      |                                      |

|-----------------------------------|------------------|-----------------------|--------------------------------|------|--------------------------------------|

|                                   |                  |                       |                                |      | $V_{SS} = 0 V$                       |

| Parameter                         | Symbol           | Condition             | Rated value                    | Unit | Applicable pins                      |

| Power supply voltage              | V <sub>DD</sub>  | Ta= 25°C              | -0.3 to +6.5                   | V    | V <sub>DD</sub>                      |

| Bias voltage                      | V <sub>BI</sub>  | Ta = 25°C             | -0.3 to +20                    | V    | V1 to V5                             |

| Voltage multiplier output voltage | V <sub>OUT</sub> | Ta= 25°C              | –0.3 to +20                    | V    | V <sub>OUT1</sub> ,V <sub>OUT2</sub> |

|                                   |                  | 2-time multiplication | -0.3 to +5.5                   |      |                                      |

| Voltage multiplier reference      | N/               | 3-time multiplication | -0.3 to +5.5                   |      |                                      |

| voltage                           | Vin              | 4-time multiplication | -0.3 to +5.0                   | VV   | IN                                   |

|                                   |                  | 5-time multiplication | -0.3 to +4.0                   |      |                                      |

| Input voltage                     | VI               | Ta = 25°C             | –0.3 to V <sub>DD</sub> +0.3 V |      | All inputs                           |

| Output short-circuit current      | Is               | Ta = 25°C             | -2.0 to +2.0                   | mA   | All outputs                          |

| Chip temperature                  | T <sub>c</sub> — |                       | 125                            | °C   | _                                    |

| Storage temperature range         | T <sub>STG</sub> |                       | -55 to +150                    | °C   |                                      |

# **ABSOLUTE MAXIMUM RATINGS**

Note: Do not use the ML9445 by short-circuiting one output pin to another output pin as well as to other pin (input pin, input/output pin, or power supply pin).

# **RECOMMENDED OPERATING CONDITIONS**

|                                      |                    |                                                                                                  |                          |     |                            |          | $V_{SS} = 0 V$                       |

|--------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|--------------------------|-----|----------------------------|----------|--------------------------------------|

| Parameter Sy                         | mbol               | Condition                                                                                        | MIN                      | TYP | MAX                        | Uni<br>t | Applicable pins                      |

| Power supply voltage                 | $V_{DD}$           | —                                                                                                | 2.7 —                    | 5.5 |                            | V        | V <sub>DD</sub>                      |

| Bias voltage                         | V <sub>BI</sub>    | _                                                                                                | 6.0                      | 18  | 18.5                       | V        | V1 to V5                             |

| Voltage multiplier reference voltage | Vin                | 2-time multiplication<br>3-time multiplication<br>4-time multiplication<br>5-time multiplication | 3.0<br>2.7<br>2.7<br>2.7 | _   | 5.5<br>5.5<br>4.625<br>3.7 | vv       | IN                                   |

| Voltage multiplier output voltage    | V <sub>OUT</sub> E | xternal input                                                                                    | 6.0                      | 18  | 18.5                       | v        | V <sub>OUT1</sub> ,V <sub>OUT2</sub> |

| Operating temperature range          | Та —               |                                                                                                  | -40                      | _   | 105                        | °C       |                                      |

Note 1: The electrical characteristics are influenced by COG trace resistance. This LSI always has to be evaluated before using.

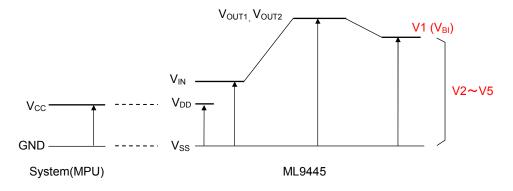

- The voltages  $V_{DD}$ ,  $V_{IN}$ , V1 to V5,  $V_{OUT1}$  and  $V_{OUT2}$  are values taking  $V_{SS}$  = 0 V as the reference. Note 2:

- The highest bias potential is V1 and the lowest is  $V_{SS}$ . Note 3:

- Note 4: Always maintain the relationship V1  $\geq$  V2  $\geq$  V3  $\geq$  V4  $\geq$  V5  $\geq$  Vss among these voltages.

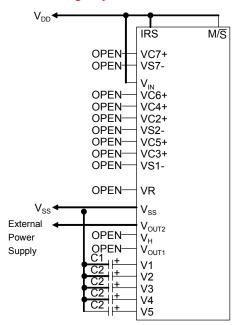

- Note 5: When using an external power supply, follow the procedure for power application. When applying external power to the  $V_{OUT1}$  pin only, apply  $V_{OUT1}$  after  $V_{DD.}$ When applying external power to the  $V_{OUT2}$  pin only, apply  $V_{OUT2}$  after  $V_{DD}$ . When applying external power to the V1 pin only, apply V1 after V<sub>DD</sub>. When applying external power to the V1 pin to V5 pin, apply V1 to V5 after  $V_{DD}$ . Note that the above (Note 4) must be satisfied including transient state at power application.

- When using an external power supply, follow the procedure for power removal described Note 6: bel OW. When external power is in use for the  $V_{OUT1}$  pin only, remove  $V_{OUT1}$  after  $V_{DD}$ .

- When external power is in use for the  $V_{OUT2}$  pin only, remove  $V_{OUT2}$  after  $V_{DD}$ .

- When external power is in use for the V1 pin only, remove V1 after  $V_{DD}$ .

When external power is in use for the V1 pin to V5 pin, remove V1 to V5 after  $V_{DD}$ . Note that the above (Note 4) must be satisfied including transient state at power removal.

## **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

|                           |                |                  |                                             | Įν                        | ′ <sub>SS</sub> =0V, ` | $V_{DD}=2.7$ to t          | 5.5V, Ta | =–40 to +105°C]        |

|---------------------------|----------------|------------------|---------------------------------------------|---------------------------|------------------------|----------------------------|----------|------------------------|

| Para                      | meter          | Symbol           | Condition                                   | Min                       | Тур М                  | ax U                       | nit      | Applicable<br>pins     |

| "H" Input vo              | oltage         | VIH              |                                             | $0.8\times V_{\text{DD}}$ | _                      | $V_{DD}$                   | Ň        | *1                     |

| "L" Input vo              | oltage         | VIL              |                                             | 0                         | _                      | $0.2 \times V_{\text{DD}}$ | V        |                        |

| "H" Output                | voltage        | V <sub>OH</sub>  | I <sub>он</sub> = –0.5 mA                   | $0.8\times V_{\text{DD}}$ |                        | _                          |          | *0                     |

| "L" Output                | voltage1       | V <sub>OL1</sub> | I <sub>OL</sub> = 0.5 mA                    | _                         | _                      | $0.2 \times V_{\text{DD}}$ | V        | *2                     |

| "L" Output                | voltage2       | V <sub>OL2</sub> | I <sub>OL</sub> = 0.5 mA                    |                           |                        | $0.2 \times V_{\text{DD}}$ | V        | SDAACK                 |

| Input curre               | nt 1           | I <sub>IL1</sub> |                                             | -1.0                      | _                      | +1.0                       | •        | *3                     |

| Input curre               | nt 2           | I <sub>IL2</sub> | $V_{I} = V_{DD}$ or $V_{I} = 0$ V           | -3.0                      |                        | +3.0                       | μA       | *4                     |

| Input capao               | citance        | Cı               | Ta=25°C,<br>F=10kHz                         | — 8                       |                        | 12                         | pF       | *1                     |

| V1 output v<br>temperatur | •              | V1TC             | Ta = 25°C<br>V1 = 12 V *50.06               |                           | _                      | %/°C                       | V1       |                        |

| Reference                 | voltage        | V <sub>REG</sub> | Ta = 25°C                                   | 2.925                     | 3.00                   | 3.075                      | V        | V <sub>RS</sub>        |

| V1 output v               | /oltage        | V1               | *6                                          | 10.59                     | 10.86                  | 11.13                      | V        | V1                     |

|                           |                |                  | 2-time<br>multiplication *7                 | 9 —                       |                        |                            |          |                        |

| Voltage mu                | ıltiplier      | V <sub>OUT</sub> | 3-time<br>multiplication *8                 | 13.5 —                    |                        |                            | v        | V <sub>OUT1</sub>      |

| output volta              | age            | VOUT             | 4-time<br>multiplication *9                 | 13.5 —                    |                        | _                          | v        | V OUT1                 |

|                           |                |                  | 5-time<br>multiplication *10                | 13.5 —                    |                        | _                          |          |                        |

| V <sub>OUT</sub> - V1 v   | voltage        | Vot1             | *11                                         | 0.6                       | —                      | _                          | V        | V <sub>OUT2,</sub> V1  |

| LCD driver                | I CD driver ON |                  | I <sub>O</sub> = ±50 μA,<br>V1=10V, 1/9bias | — 1.0                     |                        | 1.5                        | kO       | SEG0 to 179,<br>COMS0, |

| resistance                |                | R <sub>ON</sub>  | I <sub>O</sub> = ±50 μA,<br>V1=6V, 1/4bias  | <u> </u>                  |                        | 3.0                        | kΩ       | COMS1,<br>COM0 to 63   |

|                           | Internal       | f                | Ta = 25°C                                   | 799                       | 832                    | 865                        | kHz      | *10                    |

| Oscillator                | oscillation    | fosc             |                                             | 666                       | _                      | 998                        | kHz      | *12                    |

| frequency                 | External input | f <sub>EXT</sub> |                                             | _                         | 100                    | 250                        | kHz      | CL*12                  |

$[V_{SS} = 0V, V_{DD} = 2.7 \text{ to } 5.5V, Ta = -40 \text{ to } +105^{\circ}C]$

\*1: A0, DB0 to DB5, DB6 (SCL), DB7 (SI), RD (E), WR (R/W), CS1, CS2, CLS, CL, M/S, C86, P/S, RES, IRS, FR, DOF, SYNC Pins

\*2: DB0 to DB7, FR, DOF, SYNC, CL Pins

\*3: A0, RD (E), WR (R/W), CS1, CS2, CLS, M/S, C86, P/S, RES, IRS Pins

\*4: Applicable to the pins DB 0 to D B5, DB 6 (SCL), DB 7 (SI), CL, FR, DOF, SYNC in the high impedance state.

\*5: Temperature gradient select : (DB2, DB1, DB0)=(0, 1, 0)

\*6: Ta = 25°C, D7=0,α =57, (1+Rb/Ra) = 4, Voltage multiplier output voltage (V<sub>OUT</sub>) = 13.5 V (External input), LCD drive output = no-load, See Power Supply Circuit. (Page 39)

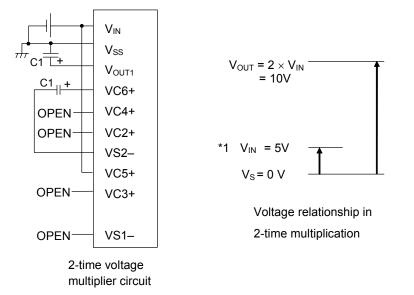

- \*7: V <sub>IN</sub> = 5.0 V, voltage multiplier capacitor C1 = 2.6 to 4.0 μF, voltage multiplier output load current I = 500 μA. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by power control set command.

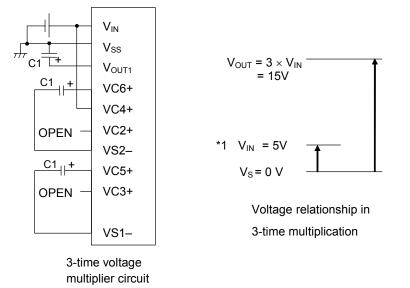

- \*8: V IN = 5.00 V, voltage multiplier capacitor C1 = 2.6 to 4.0 μF, voltage multiplier output load current I = 500 μA. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by power control set command.

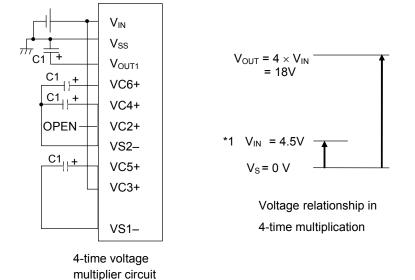

- \*9: V <sub>IN</sub> = 3.75 V, voltage multiplier capacitor C1 = 2.6 to 4.0 μF, voltage multiplier output load current I = 500 μA. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by power control set command.

- \*10: V IN = 3.0 V, voltage multiplier capacitor C1 = 2.6 to 4.0 μF, voltage multiplier output load current I = 500 μA. Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by power control set command.

- \*11: V1 load current I = 400  $\mu$ A. 8 V is externally input to V<sub>OUT2</sub>. The voltage adjustment circuit and V/F circuit operate by power control set command. LCD output = no load

- \*12: See Table 1 for the relationship between the oscillator frequency and the frame frequency.

# Table 1. Relationship among the oscillator frequency (fosc), external input frequency(fext)display clock frequency (fLCDCK), and LCD frame frequency (fFR)

| Deve   | -                                        | atar              | Display clock frequency       | LCD frame frequency               |  |

|--------|------------------------------------------|-------------------|-------------------------------|-----------------------------------|--|

| Parar  | n                                        | eter              | (f <sub>LCDCK</sub> )         | (f <sub>FR</sub> )                |  |

|        |                                          | 1/65 to 1/50 duty | Fosc/16/n                     | F <sub>OSC</sub> /(16*n*L)        |  |

|        | When the internal                        | 1/49 to 1/34 duty | F <sub>OSC</sub> * (2/3)/16/n | F <sub>OSC</sub> *(3/4) /(16*n*L) |  |

| ML9445 | oscillator is used                       | 1/33 to 1/18 duty | F <sub>OSC</sub> *(1/2)/16/n  | F <sub>OSC</sub> *(1/2) /(16*n*L) |  |

|        |                                          | 1/17 or less      | F <sub>osc</sub> * (1/4)/16/n | F <sub>OSC</sub> *(1/4) /(16*n*L) |  |

|        | When the internal oscillator is not used |                   | f <sub>EXT</sub> /16 f        | <sub>EXT</sub> /(16*L)            |  |

Ratio of dividing frequency: 1/n, Number of Display Line : L

ss=0V, Ta=25°C]

#### • Operating current consumption value

(1) During display operation, internal power supply OFF (The current flowing through  $V_{DD}$  with V1 to V5 externally applied when an external power supply is used, not including the current for the LCD drive)

|                 |                                               |                                               |     | [Vss      | =0 V, Ta | a = 25°C] |

|-----------------|-----------------------------------------------|-----------------------------------------------|-----|-----------|----------|-----------|

| Display mode    | Symbol                                        | Condition                                     | R   | ated valu | ue       | Unit      |

| Display mode    | Symbol                                        | Condition                                     | Min | Тур       | Max      | Unit      |

|                 |                                               | $V_{DD}$ = 5 V, V1- $V_{SS}$ = 11 V, no load  |     | 175       | 300      |           |

| All-white I DD  | $V_{DD}$ = 2.7 V, V1- $V_{SS}$ = 8 V, no load |                                               | 155 | 250       | μA       |           |

| Checker pattern |                                               | $V_{DD}$ = 5 V, V1- $V_{SS}$ = 11 V, no load  | _   | 175       | 300      |           |

| Checker pattern | I <sub>DD</sub>                               | $V_{DD}$ = 2.7 V, V1- $V_{SS}$ = 8 V, no load | _   | 155       | 250      | μA        |

[V

(2) During display operation, internal power supply ON (Total of currents flowing through  $V_{DD}$  and  $V_{IN}$ )

|                    |                   |                                                                                                                                     |       | 00 -      | ,    | -    |

|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------|------|

| Display            | Symbol            | C ondition                                                                                                                          | R     | ated valu | le   | Unit |

| mode               | Symbol            | ondition                                                                                                                            | Min T | ур        | Max  | Unit |

|                    |                   | Frame reversal,<br>$V_{DD}$ , $V_{IN}$ = 5 V, 3-time voltage multiplication<br>V1 - $V_{SS}$ = 11 V, no load                        | _     | 450       | 700  |      |

| All-white I        | DDIN              | Frame reversal, $V_{DD}$ , $V_{IN}$ = 2.7 V, 4-time voltage multiplication V1 - $V_{SS}$ = 8 V, no load                             | _     | 300       | 600  | μA   |

|                    |                   | 16-line reversal,<br>V <sub>DD</sub> , V <sub>IN</sub> = 5 V, 3-time voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load | — 60  | 0         | 800  |      |

|                    |                   | Frame reversal,<br>$V_{DD,} V_{IN} = 5 V$ , 3-time voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load                   | _     | 1450      | 1700 |      |

| Checker<br>pattern | I <sub>DDIN</sub> | Frame reversal,<br>$V_{DD,} V_{IN} = 2.7 V$ , 4-time voltage multiplication<br>V1 - V <sub>SS</sub> = 8 V, no load                  | _     | 1700      | 2000 | μA   |

|                    |                   | 16-line reversal, $V_{DD}$ , $V_{IN}$ = 5 V, 3-time voltage multiplication V1 - $V_{SS}$ = 11 V, no load                            |       | 1500      | 1700 |      |

• Power save mode current consumption

| [V <sub>SS</sub> =0V, Ta=25°C] |                   |                         |   |           |     |      |  |

|--------------------------------|-------------------|-------------------------|---|-----------|-----|------|--|

| Parameter Sy                   | mbol              | Condition               | R | ated valu | ie  | Unit |  |

| Falameter Sy                   | IOUII             | mbol Condition          |   | Тур       | Max | Unit |  |

| Sleep mode                     | I <sub>DDS1</sub> | V <sub>DD</sub> = 3.7 V |   | 4         | 20  | μA   |  |

FEDL9445-02

## ML9445

## **Temperature Sensor Characteristics**

| · · · · · · · · · · · · · · · · · · · |                     |                     | [V <sub>SS</sub> =0 V,  | V <sub>DD</sub> =2.7 to5 | .5 V, Ta=–40            | 0 to+105°C] |

|---------------------------------------|---------------------|---------------------|-------------------------|--------------------------|-------------------------|-------------|

| Deremeter Cu                          | inch o l            | Condition           |                         | Rated value              | 1                       | l lucit     |

| Parameter Sy                          | mbol                | Condition           | Min T                   | ур                       | Max                     | Unit        |

| Output voltage                        | $V_{SVD2}$          | -40℃<br>25℃<br>105℃ | 1.482<br>1.177<br>0.801 | 1.506<br>1.2<br>0.824    | 1.529<br>1.224<br>0.848 | V           |

| Output voltage temperature gradient   | $V_{\text{GRA}}$    | —                   | — -4.7                  |                          |                         | mV/°C       |

| Output voltage setup time             | t <sub>SEN</sub> —  |                     | 100                     | _                        | _                       | ms          |

| Operating current                     | I <sub>SEN</sub> 25 | — D°                |                         | 10                       | 30                      | μA          |

## **Switching Characteristics**

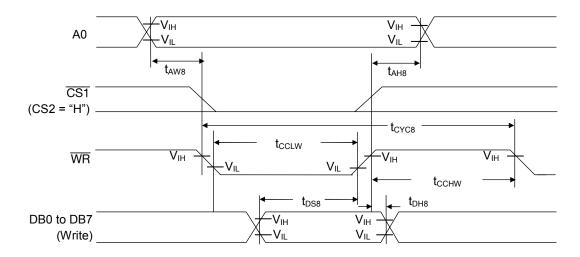

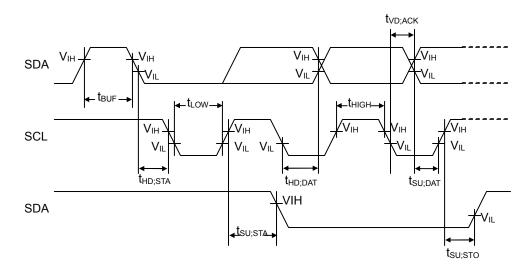

• System bus Write characteristics 1 (80-series MPU)

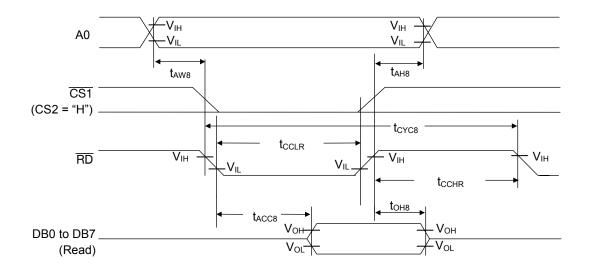

• System bus Read characteristics 1 (80-series MPU)

|                              |                     | [V <sub>DD</sub> =2.7 to | 5.5V, Ta= | =–40 to+ | +105°C] |

|------------------------------|---------------------|--------------------------|-----------|----------|---------|

| Decemptor Sy                 | mbol                | Condition                | Rated     | value    | Unit    |

| Parameter Sy                 | IIIU                | Condition                | Min       | Max      | Unit    |

| Address hold time            | t <sub>AH8</sub>    |                          | 5         | _        |         |

| Address setup time           | t <sub>AW8</sub>    |                          | 5         | _        |         |

| System cycle time            | t <sub>CYC8</sub>   |                          | 300       | _        |         |

| Control L pulse width (WR) t | CCLW                |                          | 60        | _        |         |

| Control L pulse width (RD)   | t <sub>CCLR</sub>   |                          | 240       | _        |         |

| Control H pulse width (WR)   | t <sub>сснw</sub>   |                          | 60        | _        | ns      |

| Control H pulse width (RD) t | CCHR                |                          | 60        | _        |         |

| Data setup time              | t <sub>DS8</sub>    |                          | 40        |          |         |

| Data hold time               | t <sub>DH8</sub>    |                          | 15        | _        |         |

| RD Access time               | t <sub>ACC8</sub> — | CL = 100  pE             |           | 240      | ]       |

| Output disable time          | t <sub>OH8</sub>    | CL = 100 pF              | 10 10     | 0        |         |

Note 1: The input signal rise and fall times are specified as 15ns or less. When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CVC8} - t_{CCLW} - t_{CCHW})$  or  $(tr + tf) \le (t_{CVC8} - t_{CCLR} - t_{CCHR})$ .

$(tr + tf) \leq (t_{CYC8} - t_{CCLW} - t_{CCHW}) \text{ or } (tr + tf) \leq (t_{CYC8} - t_{CCLR} - t_{CCHR}).$ Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

Note 3: The values of  $t_{CCLW}$  and  $t_{CCLR}$  are specified during the overlapping period of  $\overline{CS1}$  at "L" (CS2 = "H") and the "L" levels of  $\overline{WR}$  and  $\overline{RD}$ , respectively.

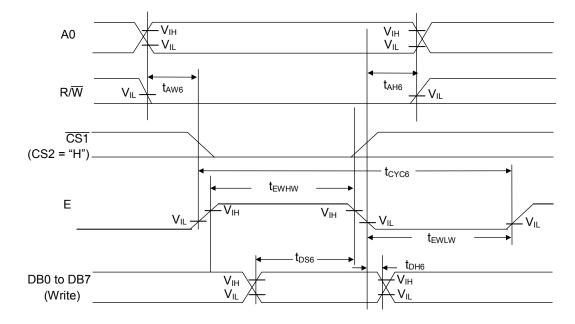

• System bus Write characteristics 2 (68-series MPU)

• System bus Read characteristics 2 (68-series MPU)

|--|

|                       |         |                   |               | ,     |       |      |

|-----------------------|---------|-------------------|---------------|-------|-------|------|

| Decemeter Sy          |         | mbal              | Condition     | Rated | value | Unit |

| Parameter Sy          |         | mbol              | Condition     | Min   | Max   | Unit |

| Address hold time     |         | t <sub>AH6</sub>  |               | 5     | _     |      |

| Address setup time    |         | t <sub>AW6</sub>  |               | 5     | _     |      |

| System cycle time     |         | t <sub>CYC6</sub> | 300           |       |       |      |

| Data setup time       |         | t <sub>DS6</sub>  | 40            |       | _     |      |

| Data hold time        |         | t <sub>DH6</sub>  |               | 15    | _     |      |

| Access time           |         | t <sub>ACC6</sub> |               | _     | 240   | ns   |

| Output disable time   |         | t <sub>OH6</sub>  | - CL = 100 pF | 10 10 | 0     | 1    |

| Enchla II nulae width | Read t  | EWHR              | 240           |       |       |      |

| Enable H pulse width  | Write t | EWHW              |               | 60    | _     | 1    |

| Enable L pulse width  | Read t  | EWLR              | 60            |       |       |      |

| Enable L pulse width  | Write t | EWLW              |               | 60    |       | ]    |

[V<sub>DD</sub>=2.7to5.5V, Ta=-40 to+105°C]

Note 1: The input signal rise and fall times are specified as 15ns or less. When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CYC6} - t_{EWLW} - t_{EWLW})$  or  $(tr + tf) \le (t_{CYC6} - t_{EWLP} - t_{EWLP})$ .

$\begin{array}{l} (tr+tf) \leq (t_{CYC6}-t_{EWLW}-t_{EWHW}) \text{ or } (tr+tf) \leq (t_{CYC6}-t_{EWLR}-t_{EWHR}). \\ \text{Note 2:} \quad \text{All timings are specified taking the levels of 20\% and 80\% of } V_{\text{DD}} \text{ as the reference.} \end{array}$

Note 3: The values of  $t_{\text{EWLW}}$  and  $t_{\text{EWLR}}$  are specified during the overlapping period of  $\overline{\text{CS1}}$  at "L" (CS2 = "H") and the "H" level of E.

FEDL9445-02

ML9445

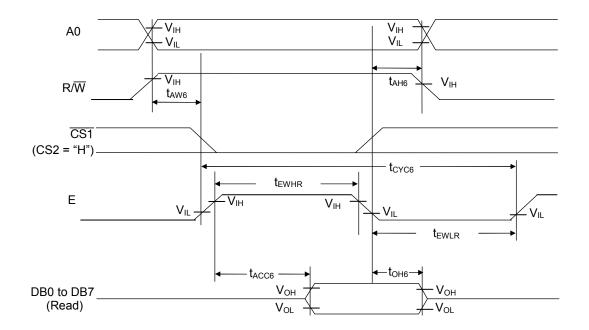

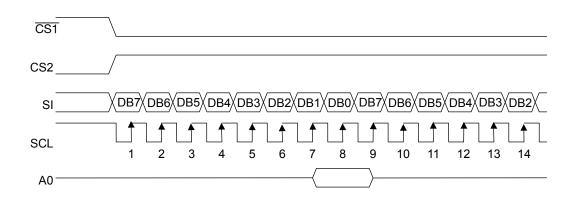

### • Serial interface

[V<sub>DD</sub>=2.7to4.5 V, Ta=-40 to+105°C]

| Deremeter Su        | mah a l          | Condition | Rated value |     | Unit |

|---------------------|------------------|-----------|-------------|-----|------|

| Parameter Sy        | mbol             | Condition | Min         | Max | Unit |

| Serial clock period | tscyc            | 250       |             |     |      |

| SCL "H" Pulse width | t <sub>sнw</sub> |           | 100         | _   |      |

| SCL "L" Pulse width | t <sub>SLW</sub> |           | 100         | _   |      |

| Address setup time  | t <sub>SAS</sub> | 150       |             | _   |      |

| Address hold time   | t <sub>SAH</sub> |           | 150         | _   | ns   |

| Data setup time     | t <sub>SDS</sub> | 100       |             |     |      |

| Data hold time      | t <sub>SDH</sub> |           | 100         | _   |      |

| CS setup time       | t <sub>css</sub> | 150       |             |     |      |

| CS hold time        | t <sub>CSH</sub> |           | 150         |     |      |

Note 1: The input signal rise and fall times are specified as 15ns or less.

Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

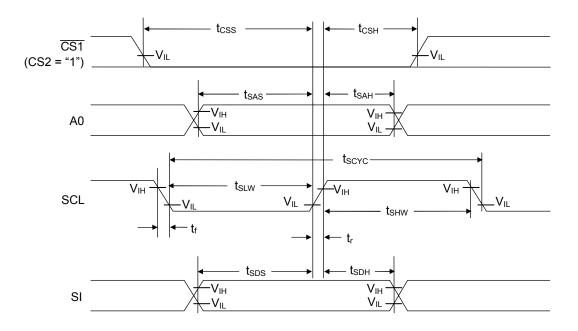

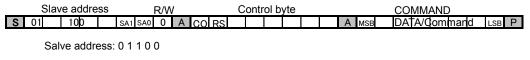

# • I<sup>2</sup>C interface timing

|                                                              |                     | (         | $V_{DD} = 2.7 \text{ to } 5$ | .5 V, Ta = -40 | $J to + 105^{\circ}C)$ |

|--------------------------------------------------------------|---------------------|-----------|------------------------------|----------------|------------------------|

| Item                                                         | Symbol              | Condition | Min. Ma                      | Х.             | Unit                   |

| SCL clock frequency                                          | f <sub>SCL</sub>    |           | — 3.4                        |                | MHz                    |

| Hold time (repeat) "STATRT" condition                        | t <sub>hd,sta</sub> | —         | 160                          | —              |                        |

| SCL "L" pulse width                                          | t <sub>LOW</sub>    |           | 160                          |                |                        |

| SCL "H" pulse width                                          | t <sub>ніGH</sub>   | _         | 60                           | _              |                        |

| Setup time for repeat "START" condition                      | t <sub>su,sta</sub> | —         | 160                          | -              | 20                     |

| Data hold time                                               | t <sub>HD,DAT</sub> |           | 0                            | 70             | ns                     |

| Data setup time                                              | t <sub>su,dat</sub> |           | 10                           | _              |                        |

| Setup time for "STOP" condition                              | t <sub>su,sto</sub> |           | 160                          |                |                        |

| Bus free time between "STOP" condition and "START" condition | t <sub>BUF</sub>    | _         | 160                          | Ι              |                        |

| Data valid acknowledge time                                  | t <sub>VD,ACK</sub> | _         | — 240                        |                |                        |

| Data bus load capacitance                                    | Cb                  | _         |                              | 100            | рF                     |

| Noise pulse width tolerance                                  | t <sub>wf</sub> —   |           | _                            | 10             | ns                     |

$\Lambda I$ = 2.7 to 5.5 V. Ta  $= -40 \text{ to } +105^{\circ}\text{C}$ )

Note 1: The input signal rise and fall times are specified as  $0.1 \mu s$  or less. Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

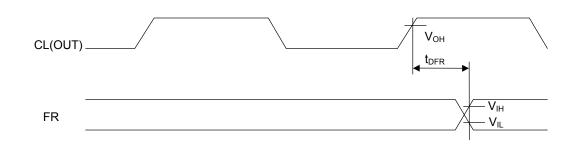

• Display control output timing

[V<sub>DD</sub>=2.7to5.5V, Ta=-40to+105°C]

| Parameter Sy  | mbol             | Condition  | F   | Rated valu | e   | Unit |

|---------------|------------------|------------|-----|------------|-----|------|

|               | mbol             | Condition  | Min | Тур        | Max | Unit |

| FR Delay time | t <sub>DFR</sub> | CL = 50 pF | _   | 20         | 80  | ns   |

Note 1: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference. Note 2: Valid only when the device operates in master mode.

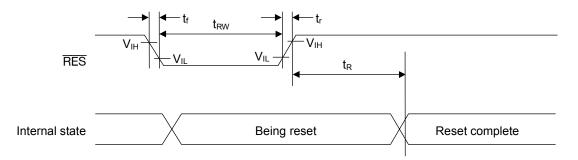

• Reset input timing

$[V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Ta} = -40 \text{ to } +105^{\circ}\text{C}]$

| Decemptor Sy                | mbal               | Condition | F   | Unit |     |      |  |

|-----------------------------|--------------------|-----------|-----|------|-----|------|--|

| Parameter Sy                | mbol               | Condition | Min | Тур  | Max | Unit |  |

| Reset time                  | t <sub>R</sub>     |           | _   | _    | 1   |      |  |

| Reset "L" pulse width       | t <sub>RW1</sub> 1 | —         |     | _    | _   | μs   |  |

| Noise pulse width tolerance | t <sub>RW2</sub>   |           |     |      | 50  | ns   |  |

Note 1: The input signal rise and fall times  $(t_r, t_f)$  are specified as 15 ns or less. Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

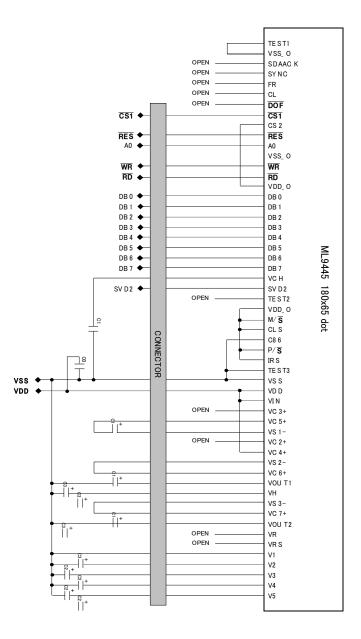

# PIN DESCRIPTION

| Function I       | Pin name             | Number<br>of pins | I/O D | escr iption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|----------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | DB0 to<br>DB7        | 2*8 I/O           |       | These are 8-bit bi-directional data bus pins that can be connected to<br>8-bit standard MPU data bus pins.<br>When a serial interface is selected ( $P/\overline{S} = "L", C86= "H"$ ):<br>DB7: Serial data input pin (SI)<br>DB6: Serial clock input pin (SCL)<br>When the serial interface and the 12C interface are selected,<br>DB0 to DB5 pins will be in the high impedance state.<br>Fix the DB0 to DB5 pins at "H" or "L" level.<br>DB0 to DB7 will be in the high impedance state when the chip select is<br>in the inactive state.            |

|                  | A0 2                 |                   | I     | Normally, the lowest bit of the MPU address bus is connected and used<br>for distinguishing between data and commands.<br>A0 = "H": Indicates that DB0 to DB7 is display data.<br>A1 = "L": Indicates that DB0 to DB7 is control data.                                                                                                                                                                                                                                                                                                                  |

|                  | RES                  | 2                 | I     | Initial setting is made by making $\overline{\text{RES}}$ = "L". The reset operation is made during the active level of the $\overline{\text{RES}}$ signal.                                                                                                                                                                                                                                                                                                                                                                                             |

| MPU<br>Interface | CS1(SA0)<br>CS2(SA1) | 2*2               |       | When the parallel interface and the serial interface are selected:<br>These are the chip select signals. The Chip Select of the LS I<br>becomes active when CS1 is "L" and also CS2 is "H" and allows<br>the input/output of data or commands.<br>When the I2C interface is selected:<br>These are the slave address input signals. They set the lower 2<br>bits of the slave address.                                                                                                                                                                  |

|                  | RD<br>(E)            | 21                |       | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{RD}$ signal of the 80-series MPU, and the data bus of the ML9445 goes into the output state when this signal is "L".<br>The active level of this signal is "H" when connected to a 68-series MPU. This pin will be the Enable and clock input pin when connected to a 68-series MPU.<br>When a serial interface and I <sup>2</sup> C interface are selected (P/S = "L"), fix this pin at "H" or "L" level.                           |

|                  | WR<br>(R/W)          | 21                |       | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{WR}$ signal of the 80-series MPU. The data on the data bus is latched into the ML9445 at the rising edge of the $\overline{WR}$ signal.<br>When connected to a 68-series MPU, this pin becomes the input pin for the Read/Write control signal.<br>$R/\overline{W} =$ "H": Read, $R/\overline{W} =$ "L": Write<br>When a serial interface and I <sup>2</sup> C interface are selected (P/S = "L"), fix this pin at "H" or "L" level. |

FEDL9445-02

| мт   | 9445  |

|------|-------|

| IVIL | ,9443 |

| Function                                  | Pin name | Number<br>of pins | I/O E | Descr iption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-------------------------------------------|----------|-------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                                           | C86 2    |                   | I     | This is the pin for selecting the MPU interface type.<br>When parallel interface is selected ( $P/\overline{S} = "H"$ ):<br>C86 = "H": 68-Series MPU interface.<br>C86 = "L": 80-Series MPU interface.<br>When serial interface and I <sup>2</sup> C interface are selected ( $P/\overline{S} = "L"$ ):<br>C86 = "H": Serial interface.<br>C86 = "L": I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| MPU<br>Interface                          | P/\$ 2   |                   | I     | $P/\overline{S} = "H"$ : Parallel interface. $P/\overline{S} = "L"$ : Serial interface or I <sup>2</sup> C interface.         The pins of the LSI have the following functions depending on the state of P/S input. $\underline{P/\overline{S}}$ Data/command       Data       Read/Write       Serial clock         "H"       A0       DB0 to DB7       RD, WR       —         "L" A0       SI/SDA (DB7)       —       SCL(DB6)         During serial data input, it is not possible to read the display data in the RAM                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

|                                           | SDAACK 2 |                   | I     | The I <sup>2</sup> C bus ac knowledge o utput signal. N ormally, use it as it is connected with the SD A pin. C onnect an external pull-up resistor whenever necessary, as it is an open drain pin. The pull-up connection destination supply voltage shall be the V <sub>DD</sub> supply voltage or less.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| Oscillator<br>circuit                     | CLS 2    |                   | I     | This is the p in for selecting whether to enable or disable the internal oscillator circuit for the display clock.<br>CLS = "H": The internal oscillator circuit is enabled.<br>CLS = "L": The internal oscillator circuit is disabled (External input).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Display<br>timing<br>generator<br>circuit | M/S 2    |                   | I     | When CLS = "L", the display clock is input at the pin CL.This is the pin for selecting whether master operation or slave operation<br>made towards the ML9445. During slave operation, the synchronizat<br>with the LCD display system is achieved by inputting the timing sign<br>necessary for LCD display.M/S = "H": Master operation<br>M/S = "L": Slave operationM/S = "L": Slave operation<br>The functions of the different circuits and pins will be as follows depend<br>on the states of M/S and CLS signals.M/SCLSOscillator<br>"H"Power<br>supply circuitCL FRSYNCDOF<br>"H""H"Enabled Ena<br>bledUputOutputOutputOutputUputUutput"L"Disabled Dis<br>abledInput Input InputInput Input"L"DisabledU"DisabledU"UsabledU"DisabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UsabledU"UU"UU"UU"UUUUUUUUUUUUUUUUU< |  |  |  |  |  |  |  |  |

| Function F                     | Pin name          | Number<br>of pins | I/O E | lescr iption                                                                                                                                            |  |  |  |  |  |

|--------------------------------|-------------------|-------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                |                   |                   |       | This is the clock input/output pin.<br>The function of this pin will be as follows depending on the states of M/S<br>and CLS signals.                   |  |  |  |  |  |

|                                |                   |                   |       | M/S CLS CL                                                                                                                                              |  |  |  |  |  |

|                                |                   |                   |       | "H" Output                                                                                                                                              |  |  |  |  |  |

|                                | CL 2              |                   | I/O   | "H" "L" Input                                                                                                                                           |  |  |  |  |  |

|                                |                   |                   |       | " " "H" Input                                                                                                                                           |  |  |  |  |  |

|                                |                   |                   |       | - "L" Inpμt                                                                                                                                             |  |  |  |  |  |

| Display                        |                   |                   |       | When the ML9445 is used in the master/slave mode, the corresponding CL pin has to be connected.                                                         |  |  |  |  |  |

| timing<br>generator<br>circuit | FR 2              |                   | I/O   | This is the input/output pin for LCD display frame reversal signal.<br>M/S = "H": Output<br>M/S = "L": Input                                            |  |  |  |  |  |

|                                |                   |                   |       | When the ML9445 is used in the master/slave mode, the corresponding                                                                                     |  |  |  |  |  |

|                                |                   |                   |       | FR pin has to be connected.                                                                                                                             |  |  |  |  |  |

|                                |                   |                   |       | This is the blanking control pin for the LCD display.                                                                                                   |  |  |  |  |  |

|                                |                   |                   | I/O   | M/S̄ = "H": Output                                                                                                                                      |  |  |  |  |  |

|                                | DOF 2             |                   |       | M/S = "L": Input                                                                                                                                        |  |  |  |  |  |

|                                |                   |                   |       | When the ML9445 is used in the master/slave mode, the corresponding DOF pin has to be connected.                                                        |  |  |  |  |  |

|                                |                   |                   |       | This is the input/output pin for LCD synchronize signal.                                                                                                |  |  |  |  |  |

|                                | SYNC 2            |                   | I/O   | When the ML9445 is used in the master/slave mode, the corresponding SYNC pin has to be connected.                                                       |  |  |  |  |  |

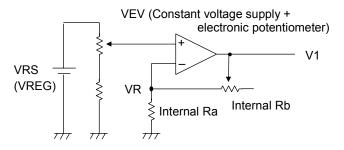

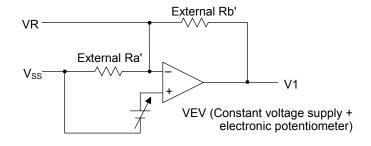

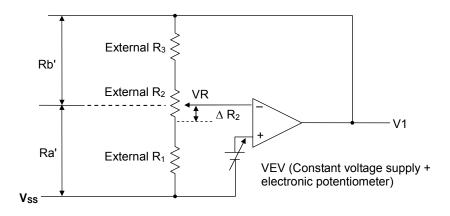

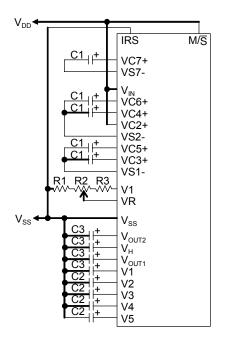

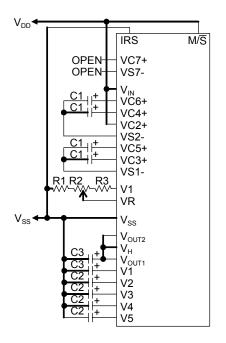

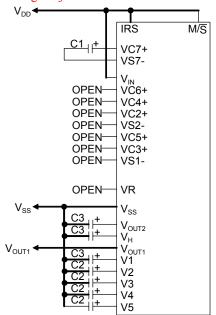

|                                |                   |                   |       | This is the pin for selecting the resistor for adjusting the voltage V1.                                                                                |  |  |  |  |  |

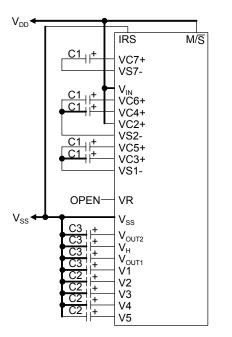

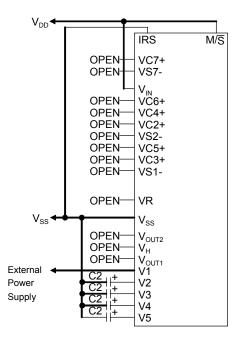

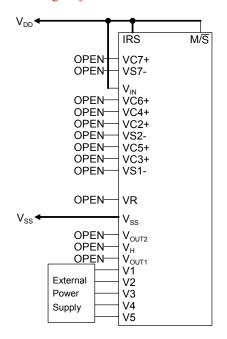

|                                |                   |                   |       | IRS = "H": The internal resistor is used.                                                                                                               |  |  |  |  |  |

|                                | IRS 2             |                   | I     | IRS = "L": The internal resistor is not used. The voltage V1 is adjusted                                                                                |  |  |  |  |  |

|                                |                   |                   |       | using the external potential divider resistors connected to the pins VR.<br>This pin is effective only in the master operation. This pin is tied to the |  |  |  |  |  |

| Power                          |                   |                   |       | "H" or the "L" level during slave operation.                                                                                                            |  |  |  |  |  |

| supply                         | V <sub>DD</sub>   | 10                |       | These pins are tied to the MPU power supply pin V <sub>CC</sub> .                                                                                       |  |  |  |  |  |

| circuit                        | V <sub>SS</sub>   | 12                | —     | These are the 0 V pins connected to the system ground (GND).                                                                                            |  |  |  |  |  |

|                                | VCH 3             |                   |       | These pins are internal logic power supply pin.                                                                                                         |  |  |  |  |  |

|                                |                   |                   |       | Connect capacitors between V <sub>SS</sub> pin.                                                                                                         |  |  |  |  |  |

|                                | V <sub>IN</sub> 3 |                   | _     | These are the reference power supply pins of the voltage multiplier circuit for driving the LCD.                                                        |  |  |  |  |  |

| Function I                 | Pin name                   | Number<br>of pins | I/O E | escr iption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|----------------------------|----------------------------|-------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                            | V <sub>RS</sub> 2          |                   |       | These are the output pins for the LCD power supply voltage adjustment circuit. Leave these pins open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

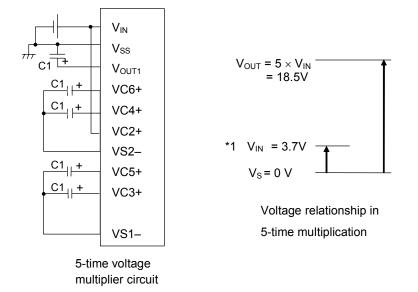

|                            | V <sub>OUT1</sub> 4        |                   | I/O   | These are the output pins during 1 <sup>st</sup> voltage multiplication.<br>Connect a capacitor between these pins and V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|                            | V <sub>H</sub> 4           |                   | I/O   | These are the power input/output pins during $2^{nd}$ voltage multiplication. Connect a capacitor between these pins and V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                            | V <sub>OUT2</sub> 3        |                   | I/O   | These are the output pins during 2 <sup>nd</sup> voltage multiplication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Power<br>supply<br>circuit | V1<br>V2<br>V3<br>V4<br>V5 | 4*5 I/O           |       | Connect a capacitor between these pins and V <sub>SS</sub> .<br>These are the multiple level power supply pins for the LCD power<br>supply. The voltages specified for the LCD cells are applied to these<br>pins after resistor network voltage division or after impedance<br>transformation using operational amplifiers. The voltages are specified<br>taking V <sub>SS</sub> as the reference, and the following relationship should be<br>maintained among them.<br>$V1 \ge V2 \ge V3 \ge V4 \ge V5 \ge V_{SS}$<br>Master operation: When the power supply is ON, the following voltages<br>are applied to V2 to V5 from the built-in power supply circuit. The<br>selection of voltages is determined by the LCD bias set command.<br>$\frac{Bias 1/4 1/5 1/6 1/7 1/8 1/9}{V2 3/4 \times V1 4/5 \times V1 5/6 \times V1 6/7 \times V1 7/8 \times V1 8/9 \times V1}$ $\frac{V3 2/4 \times V1 3/5 \times V1 4/6 \times V1 5/7 \times V1 6/8 \times V1 7/9 \times V1}{V4 2/4 \times V1 2/5 \times V1 2/6 \times V1 2/7 \times V1 2/8 \times V1 2/9 \times V1}$ $\frac{V4 2/4 \times V1 1/5 \times V1 1/6 \times V1 1/7 \times V1 1/8 \times V1 1/9 \times V1}{V5 1/4 \times V1 1/5 \times V1 1/6 \times V1 1/7 \times V1 1/8 \times V1 1/9 \times V1}$ |  |  |  |  |  |  |  |

|                            | VR                         | 2                 |       | Voltage adjustment pins. Vol tages between V1 and V <sub>SS</sub> are app lied<br>using a resistance voltage divider. These pins are effective only when<br>the internal resistors for voltage V1 adjustment are not used (IRS = "L").<br>Do not use these pins when the internal resistors for voltage V1<br>adjustment are used (IRS = "H").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

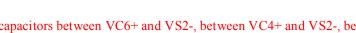

|                            | VS1-                       | 7                 | 0     | These are the pins for connecting the negative side of the capacitors for 1 <sup>st</sup> voltage multiplication.<br>Connect capacitors between these pins and VC3+, VC5+.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                            | VS2-                       | 7                 | 0     | These are the pins for connecting the negative side of the capacitors for 1 <sup>st</sup> voltage multiplication.<br>Connect capacitors between these pins and VC4+, VC6+.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                            | VC2+                       | 5                 | I     | These are the input pins for 1 <sup>st</sup> voltage multiplication.<br>This pin inputs voltage which is open or same with V <sub>IN</sub> depending on voltage multiplication scaling factor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                            | VC3+                       | 5                 | I/O   | These are the input pins for $1^{st}$ voltage multiplication.<br>Apply the voltage equal to $V_{IN}$ to the pins or leave them open, depending<br>on voltage multiplication values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| Function          | Pin name         | Number<br>of pins | I/O E | Desc                                                                                                                                                                                                                                                      | r                           |                             | İ                  | iption                                           |                                                                |  |

|-------------------|------------------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|--------------------|--------------------------------------------------|----------------------------------------------------------------|--|

|                   | VC4+             | 5                 | I/O   | 1 <sup>s</sup><br>pii                                                                                                                                                                                                                                     | <sup>t</sup> voltage multip | lication. Con<br>voltage mi | nect o<br>ultiplic | apacitors betwee                                 | f the capacitors for<br>en VS2– and these<br>are configured as |  |

| Power             | VC5+             | 5                 | I/O   | These are the pins for connecting the positive side of the capacitors 1 <sup>st</sup> voltage multiplication. Connect capacitors between VS1– and the pins. For 2-time voltage multiplication, the pins are configured as inp for voltage multiplication. |                             |                             |                    |                                                  |                                                                |  |

| supply<br>circuit | VC6+             | 5                 | ο     | 1 <sup>st</sup>                                                                                                                                                                                                                                           | voltage multipli            | cation.                     | •                  |                                                  | f the capacitors for                                           |  |

|                   | VS3-             | 4                 | 0     | Connect capacitors between VS2– and these pins.<br>These are the pins for connecting the positive side of the capa<br>O 2 <sup>nd</sup> voltage multiplication.<br>Connect capacitors between VC7+ and these pins.                                        |                             |                             |                    |                                                  |                                                                |  |

|                   | VC7+             | 4                 | 0     | These are the pins for connecting the positive side of the capacitors for 2 <sup>nd</sup> voltage multiplication.<br>Connect capacitors between VS3- and these pins.                                                                                      |                             |                             |                    |                                                  |                                                                |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           |                             | among V1, \                 | /3, V4             | , and $V_{SS}$ is sele content and the           | -                                                              |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           | RAM Data                    | FR                          |                    |                                                  | it voltage<br>y Reverse display                                |  |

|                   | SEG0 to          |                   |       |                                                                                                                                                                                                                                                           | Н                           | н                           |                    | V1                                               | V3                                                             |  |

|                   | SEG010<br>SEG179 | 180 O             |       |                                                                                                                                                                                                                                                           | H                           | L                           |                    | Vss                                              | V4                                                             |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           | L                           | Н                           |                    | V3                                               | V1                                                             |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           | L                           | L                           |                    | V4                                               | V <sub>SS</sub>                                                |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           | Power save                  | _                           |                    | ,                                                | V <sub>SS</sub>                                                |  |

| LCD<br>Drive      |                  |                   |       |                                                                                                                                                                                                                                                           | The output vo<br>executed.  | Itage is V <sub>SS</sub>    | 3 whe              | n the Display C                                  | OFF command is                                                 |  |

| output            |                  |                   |       | The                                                                                                                                                                                                                                                       | ese are the LCI             | D common d                  | lrive o            | utputs.                                          |                                                                |  |

|                   |                  |                   |       |                                                                                                                                                                                                                                                           |                             | -                           |                    | and V <sub>SS</sub> is selec<br>d the FR signal. | ted depending on                                               |  |

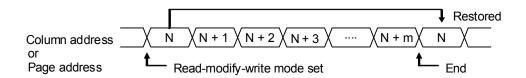

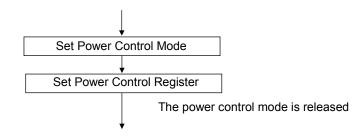

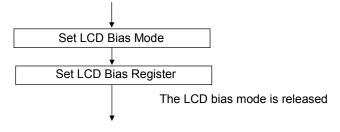

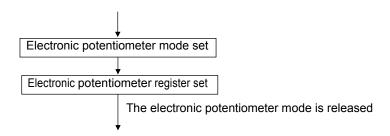

|                   |                  |                   |       | Ī                                                                                                                                                                                                                                                         | Scan data                   | FR                          | 0                  | utput voltage                                    |                                                                |  |