# **MLKHN1500**

# Fully compliant IEEE 1901 HD-PLC Power line Communications (PLC) IC

# **Datasheet**

KDS-HANFF02EAA

Rev. 1.00

**MegaChips**

# MegaChips' Proprietary and Confidential

This information shall not be shared or distributed outside the company and will be exchanged based on the signed proprietary information exchange agreement. MegaChips reserves the right to make any change herein at any time without prior notice. MegaChips does not assume any responsibility or liability arising out of application or use of any product or service described herein except as explicitly agreed upon.

# Contents

| 1. | Product  | Overview                             | 6  |

|----|----------|--------------------------------------|----|

|    | 1.1. Fur | ctional Overview                     | 6  |

|    | 1.1.1.   | Key Features                         | 6  |

|    | 1.1.2.   | Applications                         | 7  |

|    | 1.2. Blo | ck Diagram                           | 7  |

| 2. | Pins     |                                      | 8  |

|    | 2.1. Pin | out                                  | 8  |

|    | 2.2. Pin | Descriptions                         | 9  |

|    | 2.2.1.   | Analog Front-end Connection Pins     | 9  |

|    | 2.2.2.   | Ethernet Connection Pins             | 9  |

|    | 2.2.3.   | SDRAM Connection Pins                | 10 |

|    | 2.2.4.   | Serial Flash Connection Pins         | 12 |

|    | 2.2.5.   | Serial Communication Connection Pins | 12 |

|    | 2.2.6.   | General-purpose Ports                | 12 |

|    | 2.2.7.   | CPU Peripheral Connection Pin        | 13 |

|    | 2.2.8.   | AC Synchronous Detection Pin         | 14 |

|    | 2.2.9.   | Clock and Reset Pins                 | 14 |

|    | 2.2.10.  | DAC Pins                             | 14 |

|    | 2.2.11.  | ADC Pins                             | 15 |

|    | 2.2.12.  | Test Setting Pin                     | 15 |

|    | 2.2.13.  | Debugger Connection Pins             | 15 |

|    | 2.2.14.  | Hardware Revision Setting Pins       | 16 |

|    | 2.2.15.  | Power Supply and VSS Pins            | 16 |

|    | 2.2.16.  | Shared Pins                          | 17 |

| 3. | Operatir | ng Conditions                        | 18 |

|    | 3.1. Abs | olute Maximum Ratings                | 18 |

|    | 3.2.  | Pov           | wer Supply Specifications                                | . 19 |  |  |  |  |  |  |  |

|----|-------|---------------|----------------------------------------------------------|------|--|--|--|--|--|--|--|

|    | 3.3.  | The           | ermal Information                                        | . 19 |  |  |  |  |  |  |  |

| 4. | . Bas | Baseband Part |                                                          |      |  |  |  |  |  |  |  |

|    | 4.1.  | Blo           | ck Diagram                                               | . 20 |  |  |  |  |  |  |  |

|    | 4.2.  | List          | of Functions                                             | . 20 |  |  |  |  |  |  |  |

|    | 4.2   | .1.           | Microcontroller and Peripherals                          | . 20 |  |  |  |  |  |  |  |

|    | 4.2   | .2.           | PLC-PHY Function                                         | . 21 |  |  |  |  |  |  |  |

|    | 4.2   | .3.           | PLC-MAC Processing Function                              | . 21 |  |  |  |  |  |  |  |

|    | 4.2   | .4.           | SPI FLASH Interface Function                             | . 21 |  |  |  |  |  |  |  |

|    | 4.2   | .5.           | Ethernet PHY Interface Functions                         | . 21 |  |  |  |  |  |  |  |

|    | 4.2   | .6.           | Clock and Reset Control Functions                        | . 21 |  |  |  |  |  |  |  |

|    | 4.3.  | Exa           | ample System Architectures                               | . 22 |  |  |  |  |  |  |  |

|    | 4.3   | .1.           | Normal Mode                                              | . 22 |  |  |  |  |  |  |  |

|    | 4.3   | .2.           | ICE Mode                                                 | . 23 |  |  |  |  |  |  |  |

|    | 4.4.  | Ele           | ctrical Characteristics                                  | . 24 |  |  |  |  |  |  |  |

|    | 4.5.  | AC            | Characteristics                                          | . 25 |  |  |  |  |  |  |  |

|    | 4.5   | .1.           | Ethernet Connection Pins (MII/TMII Specification) Timing | . 25 |  |  |  |  |  |  |  |

|    | 4.5   | .2.           | Ethernet Connection Pins (RMII Specification) Timing     | . 27 |  |  |  |  |  |  |  |

|    | 4.5   | .3.           | Serial Flash Connection Pins Timing (Write)              | . 28 |  |  |  |  |  |  |  |

|    | 4.5   | .4.           | Serial Flash Connection Pins Timing (Read)               | . 29 |  |  |  |  |  |  |  |

|    | 4.6.  | Des           | scription of Operating Modes                             | . 30 |  |  |  |  |  |  |  |

|    | 4.6   | .1.           | Normal and Test Modes                                    | . 30 |  |  |  |  |  |  |  |

|    | 4.6   | .2.           | Normal Mode                                              | . 30 |  |  |  |  |  |  |  |

|    | 4.6   | .3.           | ICE Mode                                                 | . 30 |  |  |  |  |  |  |  |

|    | 4.7.  | Pov           | wer Supply Activation                                    | . 30 |  |  |  |  |  |  |  |

|    | 4.8.  | Res           | set Sequence                                             | . 30 |  |  |  |  |  |  |  |

|    | 4.9.  | Set           | ting Methods                                             | . 31 |  |  |  |  |  |  |  |

|    | 4.9  | .1.    | Special Pin Settings              | 31 |

|----|------|--------|-----------------------------------|----|

|    | 4.9  | .2.    | Normal and Test Modes Setting     | 32 |

| 5. | Ana  | alog F | Front-End(AFE) Part               | 32 |

|    | 5.1. | Ger    | neral Description                 | 32 |

|    | 5.2. | Spe    | ecifications                      | 34 |

|    | 5.2  | .1.    | TX Path specifications            | 34 |

|    | 5.2  | .2.    | RX Path Specifications            | 35 |

|    | 5.2  | .3.    | PLL Specifications                | 36 |

|    | 5.2  | .4.    | Digital Interface Specifications  | 36 |

|    | 5.3. | Fun    | ction Descriptions                | 37 |

|    | 5.3  | .1.    | Rx Path                           | 37 |

|    | 5.3  | .2.    | Tx Path                           | 43 |

|    | 5.3  | .3.    | Clock Synthesizer                 | 48 |

|    | 5.3  | .4.    | Serial Peripheral Interface (SPI) | 50 |

| 6. | Pad  | ckage  | 9                                 | 63 |

| 7. | Orc  | dering | g Information                     | 63 |

| 8. | App  | pendi  | X                                 | 64 |

|    | 8.1. | Seri   | ial Flash ROM Specifications      | 64 |

|    | 8.2. | Ethe   | ernet PHY Specifications          | 64 |

|    | 8.3. | Crys   | stal Oscillator Specifications    | 64 |

|    | 8.4. | PLL    | Board Design Recommendations      | 65 |

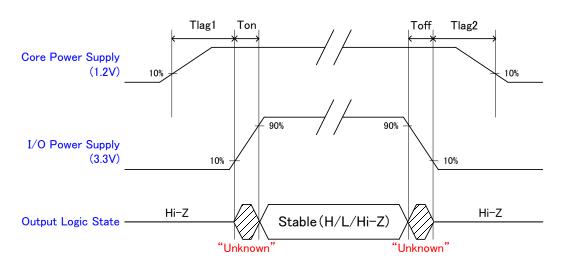

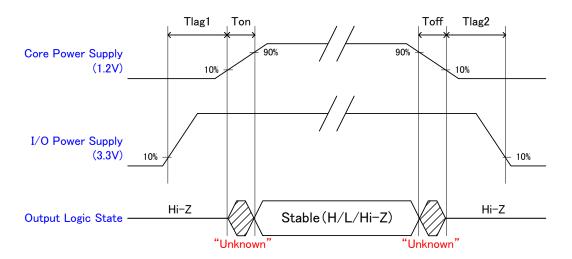

|    | 8.5. | Pow    | ver Up/Down Sequence              | 66 |

# **Revision History**

| Date       | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2016/8/5   | 0.2.0    | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2016/8/26  | 0.3.0    | Modified the errors in Figure 2: Pinout /page 6 Unified the word "Turbo-MII" into TMII and added the description "TMII (Turbo-MII)" in page 9 Modified the errors and K_SDCKE, K_SDCSN description in Table 3: List of SDRAM Connection Pins/ page 10 Added VDD33_K's explanation in Table 14: List of Power Supply and VSS Pins / page 16 Added VDD33_K's Absolute maximum ratings and modified parameters description in Table 16: Absolute Maximum Ratings / page 18 Modified AGCGAIN to REVISION in Section 4.9.1Special Pin Settings / page 31 Modified D12VDD to CVDD in Section 5.2 Specifications  Removed "KS8721BL", "KSZ8051MNL" from recommended device in Section 8.2 Ethernet PHY Specifications / page 64 |

| 2016/8/29  | 0.4.0    | Editorial changes Removed the description of "VD12VDD" to unity it into CVDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2016/9/12  | 0.5.0    | Added the description about pull-up/pull down in Section 2.2 Pin Descriptions Added V <sub>VDD33 K</sub> into Section 3.2 Power Supply Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2017/03/02 | 0.6.0    | Modified package name to "LBGA 238 pin" / page 6 Modified the description about TXC, RXC, COL, CRS in 0 Table 2: List of Ethernet Connection Pins / page 9 Changed from Tc to Ambient temperature 0 Table 17: Power Supply Specifications / page 19 Added thermal resistance in 3.3 Thermal Information / page 16 Modified Section 1.1 Functional Overview Modified Section 3.2 Power Supply Specifications Modified Allowable deviation of Oscillation Editorial changes Remove table 32 Add power consumption value Add refresh cycle of SDRAM                                                                                                                                                                         |

| 2017/03/03 | 0.6.1    | Editorial changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2017/03/23 | 0.6.2    | Change parts number typo "MLMLKHNxx" to "MLKHNxx"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2017/03/27 | 1.0.0    | Official release version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# 1. Product Overview

#### 1.1. Functional Overview

MegaChips MLKHN1500 is a state-of-the-art single-chip broadband over power line (BPL) solution based on IEEE 1901 standard (HD-PLC). It delivers bi-directional, IP based, high-speed communication over AC/DC power lines, COAX and twisted pair wiring where wider bandwidths, robustness, long-range, support for larger number of nodes, and highly secure network is required.

The highly integrated MLKHN1500 combines the physical (PHY) and media access control (MAC) layers using an ARM946E microcontroller, 128Mbit (MLKHN1500A) or 256Mbit SDRAM (MLKHN1500B), UART, MII/RMII, and integrated analog-front-end (AFE) in a single compact package to reduce cost, size and complexity.

The MLKHN1500 uses a high-performance wavelet conversion OFDM modulation and advanced forward error correction (FEC) schemes to enable robust data communication using the existing electrical lines. With 432 sub-carriers in the 2 MHz - 28 MHz operating frequency band, the MLKHN1500 provides a maximum PHY rate of 240Mbps. A channel estimation technique is used to determine the optimal data rate according to the power line channel characteristics with the multi-level modulation for each sub-carrier. Optional sub-carrier masking function is adapted to meet individual country's regulations.

The MLKHN1500 uses a 128-bit AES encryption engine for the highest security at every node meeting today's Internet-of-Things (IoT) requirements.

#### 1.1.1. Key Features

- Supports up to 16 nodes on a single network

- HD-PLC/Ethernet bridge functionality

- Lowest power in the industry

- On-chip PLL multiplier and synthesizer provides a single clock source

- Advanced network diagnostics and management

- HD-PLC network bridge function compatible with Ethernet address system

- Industrial operating temperature (-40°C to +85°C)

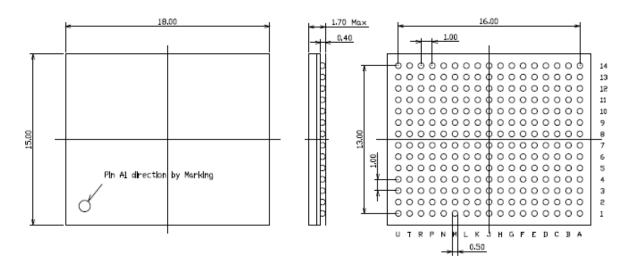

- Package LBGA 238pin (15mmx18mm)

- Meets EN50561-1 EMC regulations

## 1.1.2. Applications

- Home Networking (IPTV, gaming, Internet)

- Audio/Video Streaming

- Security/Surveillance (IP Cameras)

- Wi-Fi/Ethernet/RS485 Extenders

- Smart Homes

## 1.2. Block Diagram

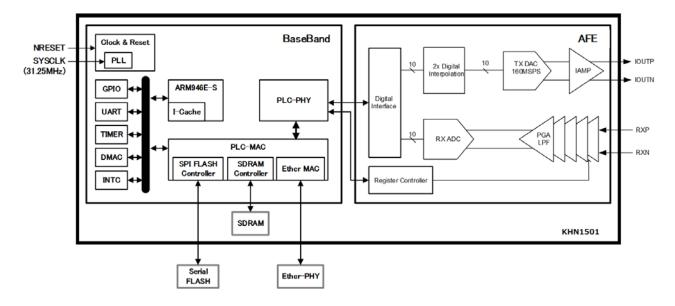

The figure below is a block diagram of the MLKHN1500.

Figure 1: MLKHN1500 Block Diagram

## 2. Pins

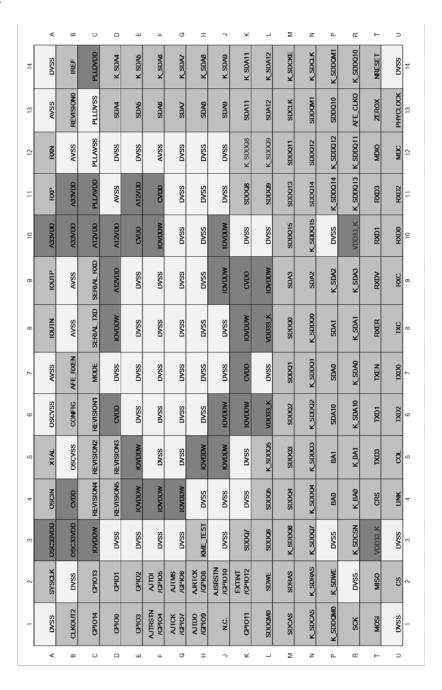

## 2.1. Pinout

Figure 2: Pinout

## 2.2. Pin Descriptions

This section describes the MLKHN1500's pins. In the pin list, initial values for pins are given as "RST initial value", and "---" indicates that the initial values are undefined since those pins are inputs in the initial state (following reset de-assertion). "Pull-up/Pull-down" column shows internal PU/PD information. Pins names that are followed by "(shared)" are shared pins and are not shown in the pinout.

Pin name which are marked with (\*) are 5V Tolerant.

#### 2.2.1. Analog Front-end Connection Pins

The table below shows a list of analog front-end connection pins.

Table 1: List of Analog Front-end Connection Pins

| No. | Pin Name     | I/O | RST<br>Initial Value | Pull-up/<br>Pull-down | Description                               |

|-----|--------------|-----|----------------------|-----------------------|-------------------------------------------|

| R13 | AFE_CLKO     | 0   | Low                  |                       | A/D / D/A sampling clock output.(62.5MHz) |

| B7  | AFE_RXEN (*) | 0   | Low                  | Pull-down             | Active high receive enable output.        |

#### 2.2.2. Ethernet Connection Pins

The MLKHN1500's Ethernet connection pins comply with MII and RMII specifications and also support TMII (Turbo-MII) specification. Register settings can be used to select the desired specification set.

The table below shows a list of Ethernet connection pins.

**Table 2: List of Ethernet Connection Pins**

| No. | Pin Name | I/O | RST<br>Initial Value | Pull-up/<br>Pull-down | Description                                                                                                               |

|-----|----------|-----|----------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| U7  | TXD0     |     | Low                  |                       | When MII/TMII is selected, act as 4-bit transmission data                                                                 |

| T6  | TXD1     | 0   | Low                  |                       | output.                                                                                                                   |

| U6  | TXD2     |     | Low                  |                       | When RMII is selected, TXD0 and TXD1 act as 2-bit transmission data output pins. Do not connect anything to               |

| T5  | TXD3     |     | Low                  |                       | TXD2 or TXD3 in this configuration.                                                                                       |

| T7  | TXEN     | 0   | Low                  |                       | Active high transmission data enable output.                                                                              |

| U8  | TXC (*)  | I   |                      |                       | Transmission clock input. When RMII is selected and connects w/ Ether PHY LSI, Pull-down resistor is required externally. |

| U10 | RXD0 (*) | ı   |                      |                       | When MII/TMII is selected, act as 4-bit receive data input.                                                               |

| No. | Pin Name | I/O | RST<br>Initial Value | Pull-up/<br>Pull-down | Description                                                                                                                                                                                                                                                        |

|-----|----------|-----|----------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T10 | RXD1 (*) |     |                      |                       | When RMII is selected, RXD0 and RXD1 act as 2-bit receive data input.                                                                                                                                                                                              |

| U11 | RXD2 (*) |     |                      |                       | RXD2 and RXD3 act as monitor pins as described below:                                                                                                                                                                                                              |

| T11 | RXD3 (*) |     |                      |                       | RXD2 : 10M/100M communications mode information RXD3 : LINK status                                                                                                                                                                                                 |

| Т9  | RXDV (*) | I   |                      |                       | Active high receive data valid input.  When RMII is selected, connect to the Ether PHY LSI's CRS_DV pin.                                                                                                                                                           |

| U9  | RXC (*)  | I   |                      |                       | Receive clock input. When RMII is selected and connects w/ Ether PHY LSI, Pull-down resistor is required externally.                                                                                                                                               |

| T8  | RXER (*) | I   |                      |                       | Active high receive error indicator input.                                                                                                                                                                                                                         |

| U5  | COL (*)  | I   |                      | Pull-down             | Active high collision detection input.  Not used when RMII is selected. Requires pull-down.                                                                                                                                                                        |

| T4  | CRS (*)  | I   |                      | Pull-down             | Active high carrier sense input.  Not used when RMII is selected. Requires pull-down.                                                                                                                                                                              |

| T12 | MDIO (*) | Ю   |                      | Pull-down             | Control data input/output.                                                                                                                                                                                                                                         |

| U12 | MDC      | 0   | Low                  |                       | Control data clock output.                                                                                                                                                                                                                                         |

| U13 | PHYCLOCK | 0   | Low                  |                       | Acts as the Ethernet clock output. The clock precision is the same as for the clock input to the SYSCLK pin. When MII is selected, outputs 25MHz. When RMII, TMII are selected, outputs 50MHz.                                                                     |

| U4  | LINK (*) | I   |                      | Pull-up               | Acts as the link state input. For more information about the pin level (indicating the presence of the link state), see the specifications for the EtherPHY LSI to which the pin will be connected. A toggle signal indicates that communications are in progress. |

#### 2.2.3. SDRAM Connection Pins

The table below shows a list of SDRAM connection pins, which are supposed to connect to internal SDRAM externally. These pins are used in MP test only.

Table 3: List of SDRAM Connection Pins

| No. | Pin<br>Name | I/O | RST<br>Initial<br>Value | Pull-<br>up/<br>Pull-<br>down | Connected<br>SDRAM<br>Pin No. | Connected<br>SDRAM<br>Pin Name | Description                  |

|-----|-------------|-----|-------------------------|-------------------------------|-------------------------------|--------------------------------|------------------------------|

| M8  | SDDQ0       |     |                         |                               | N8                            | K_SDDQ0                        |                              |

| M7  | SDDQ1       | 10  |                         |                               | N7                            | K_SDDQ1                        | 16-bit data bus input/output |

| M6  | SDDQ2       | Ю   |                         |                               | N6                            | K_SDDQ2                        | for SDRAM.                   |

| M5  | SDDQ3       |     |                         |                               | N5                            | K_SDDQ3                        |                              |

| No. | Pin<br>Name | I/O | RST<br>Initial<br>Value | Pull-<br>up/<br>Pull-<br>down | Connected<br>SDRAM<br>Pin No. | Connected<br>SDRAM<br>Pin Name | Description                                    |

|-----|-------------|-----|-------------------------|-------------------------------|-------------------------------|--------------------------------|------------------------------------------------|

| M4  | SDDQ4       |     |                         |                               | N4                            | K_SDDQ4                        |                                                |

| L4  | SDDQ5       |     |                         |                               | L5                            | K_SDDQ5                        |                                                |

| L3  | SDDQ6       |     |                         |                               | M3                            | K_SDDQ6                        |                                                |

| K3  | SDDQ7       |     |                         |                               | N3                            | K_SDDQ7                        |                                                |

| K11 | SDDQ8       |     |                         |                               | K12                           | K_SDDQ8                        |                                                |

| L11 | SDDQ9       |     |                         |                               | L12                           | K_SDDQ9                        |                                                |

| P13 | SDDQ10      |     |                         |                               | R14                           | K_SDDQ10                       |                                                |

| M12 | SDDQ11      |     |                         |                               | R12                           | K_SDDQ11                       |                                                |

| N12 | SDDQ12      |     |                         |                               | P12                           | K_SDDQ12                       |                                                |

| M11 | SDDQ13      |     |                         |                               | R11                           | K_SDDQ13                       |                                                |

| N11 | SDDQ14      |     |                         |                               | P11                           | K_SDDQ14                       |                                                |

| M10 | SDDQ15      |     |                         |                               | N10                           | K_SDDQ15                       |                                                |

| P7  | SDA0        |     | Low                     |                               | R7                            | K_SDA0                         |                                                |

| P8  | SDA1        |     | Low                     |                               | R8                            | K_SDA1                         |                                                |

| N9  | SDA2        |     | Low                     |                               | P9                            | K_SDA2                         |                                                |

| M9  | SDA3        |     | Low                     |                               | R9                            | K_SDA3                         |                                                |

| D13 | SDA4        |     | Low                     |                               | D14                           | K_SDA4                         |                                                |

| E13 | SDA5        |     | Low                     |                               | E14                           | K_SDA5                         |                                                |

| F13 | SDA6        | 0   | Low                     |                               | F14                           | K_SDA6                         | 13-bit address bus output for SDRAM.           |

| G13 | SDA7        |     | Low                     |                               | G14                           | K_SDA7                         | ODITAIN.                                       |

| H13 | SDA8        |     | Low                     |                               | H14                           | K_SDA8                         |                                                |

| J13 | SDA9        |     | Low                     |                               | J14                           | K_SDA9                         |                                                |

| P6  | SDA10       |     | Low                     |                               | R6                            | K_SDA10                        |                                                |

| K13 | SDA11       |     | Low                     |                               | K14                           | K_SDA11                        |                                                |

| L13 | SDA12       |     | Low                     |                               | L14                           | K_SDA12                        |                                                |

| P4  | BA0         |     | Low                     |                               | R4                            | K_BA0                          | Bank address output                            |

| P5  | BA1         | 0   | Low                     |                               | R5                            | K_BA1                          | for SDRAM.                                     |

| M13 | SDCLK       | 0   | Low                     |                               | N14                           | K_SDCLK                        | SDRAM transfer clock output.                   |

| M2  | SDRAS       | 0   | High                    |                               | N2                            | K_SDRAS                        | Bank select / row address strobe output.       |

| M1  | SDCAS       | 0   | High                    |                               | N1                            | K_SDCAS                        | Command select / column address strobe output. |

| L2  | SDWE        | 0   | High                    |                               | P2                            | K_SDWE                         | Write enable output.                           |

| L1  | SDDQM0      | 0   | Low                     |                               | P1                            | K_SDDQM0                       | Data mask southed actions                      |

| N13 | SDDQM1      | 0   | Low                     |                               | P14                           | K_SDDQM1                       | Data mask control output.                      |

| -   | -           | -   | -                       |                               | M14                           | K_SDCKE                        | SDRAM Clock Enable,                            |

| No. | Pin<br>Name | I/O | RST<br>Initial<br>Value | Pull-<br>up/<br>Pull-<br>down | Connected<br>SDRAM<br>Pin No. | Connected<br>SDRAM<br>Pin Name | Description                               |

|-----|-------------|-----|-------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------------------|

|     |             |     |                         |                               |                               |                                | Tied to 3.3V externally                   |

| -   | -           | -   | -                       |                               | R3                            | K_SDCSN                        | SDRAM Chip Select, Tied to GND externally |

#### 2.2.4. Serial Flash Connection Pins

The table below shows a list of serial flash connection pins.

Table 4: List of Serial Flash Connection Pins

| No. | Pin Name | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                  |

|-----|----------|-----|-------------------------|-----------------------|------------------------------|

| U2  | CS       | 0   | High                    |                       | Chip select output.          |

| T2  | MISO (*) | I   |                         | Pull-down             | Serial data input.           |

| R1  | SCK      | 0   | Low                     |                       | Serial clock output. (50MHz) |

| T1  | MOSI (*) | 0   | Low                     | Pull-down             | Serial data output           |

#### 2.2.5. Serial Communication Connection Pins

The table below shows a list of serial communication connection pins.

| No. | Pin Name       | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description         |

|-----|----------------|-----|-------------------------|-----------------------|---------------------|

| C9  | SERIAL_RXD (*) | I   |                         | Pull-up               | Serial data input.  |

| C8  | SERIAL_TXD (*) | 0   | Low                     |                       | Serial data output. |

## 2.2.6. General-purpose Ports

The table below shows a list of general-purpose ports.

Table 5: List of General-purpose ports

| No. | Pin Name   | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                                         |

|-----|------------|-----|-------------------------|-----------------------|-----------------------------------------------------|

| D1  | GPIO0 (*)  | Ю   |                         | Pull-down             | General-purpose port.                               |

| D2  | GPIO1 (*)  | Ю   |                         | Pull-down             | General-purpose port.                               |

| E2  | GPIO2 (*)  | Ю   |                         | Pull-down             | General-purpose port.                               |

| E1  | GPIO3 (*)  | Ю   |                         | Pull-down             | General-purpose port.                               |

| F1  | GPIO4 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJTRSTN pin. |

| F2  | GPIO5 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJTDI pin.   |

| G2  | GPIO6 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJTMS pin.   |

| G1  | GPIO7 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJTCK pin.   |

| H2  | GPIO8 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJRTCK pin.  |

| H1  | GPIO9 (*)  | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJTDO pin.   |

| J2  | GPIO10 (*) | Ю   |                         | Pull-up               | General-purpose port. (*1) Shared with AJSRSTN pin. |

| K1  | GPIO11 (*) | Ю   |                         | Pull-up               | General-purpose port.                               |

| K2  | GPIO12 (*) | Ю   |                         | Pull-up               | General-purpose port. (*2) Shared with EXTINT pin.  |

| C2  | GPIO13 (*) | Ю   |                         | Pull-up               | General-purpose port.                               |

| C1  | GPIO14 (*) | Ю   |                         | Pull-up               | General-purpose port.                               |

| J1  | N.C.       | -   |                         |                       | (Not Connected). Leave this pin open.               |

Note: In normal mode, all ports are configured as input ports.

\*1 : When ICE mode is selected, acts as the ICE JTAG pin.

\*2 : Enabled by register settings.

# 2.2.7. CPU Peripheral Connection Pin

The table below shows a list of CPU peripheral connection pin.

Table 6: List of CPU Peripheral Connection Pin

| No. | Pin Name   | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                                                |

|-----|------------|-----|-------------------------|-----------------------|------------------------------------------------------------|

| K2  | EXTINT (*) | I   |                         | Pull-up               | Active Low external interrupt input. * Shared with GPIO12. |

#### 2.2.8. AC Synchronous Detection Pin

The table below shows a list of AC synchronous detection pin.

Table 7: List of AC Synchronous Detection Pin

| No. | Pin Name  | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                     |

|-----|-----------|-----|-------------------------|-----------------------|---------------------------------|

| T13 | ZEROX (*) | I   |                         | Pull-up               | AC synchronous detection input. |

#### 2.2.9. Clock and Reset Pins

The table below shows a list of clock and reset connection pins.

Table 8: List of Clock and Reset Connection Pins

| No. | Pin Name   | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                          |

|-----|------------|-----|-------------------------|-----------------------|--------------------------------------|

| A2  | SYSCLK (*) | I   |                         |                       | System clock input. (31.25MHz)       |

| A5  | XTAL       | 0   |                         |                       | Crystal Oscillator Inverter Output   |

| A4  | OSCIN      | I   |                         |                       | Crystal Oscillator Inverter Input    |

| B1  | CLKOUT2    | 0   |                         |                       | fosc/L Clock Output (L=1,2,4,8)      |

| T14 | NRESET (*) | I   |                         | Pull-up               | Active low asynchronous reset input. |

#### 2.2.10. DAC Pins

The table below shows a list of DAC connection pins.

Table 9: List of DAC Connection Pins

| No. | Pin<br>Name | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                                         |

|-----|-------------|-----|-------------------------|-----------------------|-----------------------------------------------------|

| A9  | IOUTP       | 0   |                         |                       | IAMP+ Current Output Sink                           |

| A8  | IOUTN       | 0   |                         |                       | IAMP- Current Output Sink                           |

| B14 | IREF        | I   |                         |                       | Reference Current DAC, connect to 8.2k ohm resistor |

#### 2.2.11. ADC Pins

The table below shows a list of ADC connection pins.

Table 10: List of ADC Connection Pins

| No. | Pin Name | I/O | RST<br>Initial Value | Pull-up/<br>Pull-<br>down | Description                   |

|-----|----------|-----|----------------------|---------------------------|-------------------------------|

| A11 | RXP      | I   |                      |                           | Receive Path Analog Input pin |

| A12 | RXN      | I   |                      |                           | Receive Path Analog Input pin |

#### 2.2.12. Test Setting Pin

The table below shows a list of test pins.

Table 11: List of Test Setting Pin

| No. | Pin Name     | I/O | RST<br>Initial Value | Pull-up/<br>Pull-<br>down | Description                                                                                |

|-----|--------------|-----|----------------------|---------------------------|--------------------------------------------------------------------------------------------|

| НЗ  | KME_TEST (*) | I   |                      | Pull-down                 | Production test mode setting input. In normal operation, this input should be tied to low. |

| C7  | MODE         | I   |                      |                           | Vendor test purpose only, Fixed to "Low"                                                   |

| B6  | CONFIG       | I   |                      |                           | Vendor test purpose only, Fixed to "Low"                                                   |

#### 2.2.13. Debugger Connection Pins

The table below shows a list of debugger connection pins.

Table 12: List of Debugger Connection Pins

| No. | Pin Name        | I/O | RST<br>Initial Value | Pull-up/<br>Pull-down | Description                                                    |

|-----|-----------------|-----|----------------------|-----------------------|----------------------------------------------------------------|

| F1  | AJTRSTN(Shared) | I   |                      | Pull-up               | JTAG reset signal. * Shared with GPIO4.                        |

| F2  | AJTDI(Shared)   | I   |                      | Pull-up               | JTAG test data input. * Shared with GPIO5.                     |

| G2  | AJTMS(Shared)   | I   |                      | Pull-up               | JTAG TAP controller mode selection signal. *Shared with GPIO6. |

| G1  | AJTCK(Shared)   | 1   |                      | Pull-up               | JTAG test clock. * Shared with GPIO7.                          |

| H2  | AJRTCK(Shared)  | 0   | Low                  | Pull-up               | JTAG Return TCK output to ICE.                                 |

| No. | Pin Name        | I/O | RST<br>Initial Value | Pull-up/<br>Pull-down | Description                                    |

|-----|-----------------|-----|----------------------|-----------------------|------------------------------------------------|

|     |                 |     |                      |                       | *Shared with GPIO8.                            |

| H1  | AJTDO(Shared)   | 0   | Hi-Z                 | Pull-up               | JTAG test data output. * Shared with GPIO9.    |

| J2  | AJSRSTN(Shared) | ı   |                      | Pull-up               | JTAG system reset signal. *Shared with GPIO10. |

Note: GPIO10 to GPIO4 cannot be used as general-purpose ports during ICE mode operation.

#### 2.2.14. Hardware Revision Setting Pins

The table below shows a list of hardware revision setting pins. For more information, see Section 4.9.1 Special Pin Settings.

Table 13: List of Hardware Revision Setting Pins

| No. | Pin Name      | I/O | RST<br>Initial<br>Value | Pull-up/<br>Pull-down | Description                 |

|-----|---------------|-----|-------------------------|-----------------------|-----------------------------|

| B13 | REVISION0 (*) | I   |                         |                       | Revision setting            |

| C6  | REVISION1 (*) | I   |                         |                       | Revision setting            |

| C5  | REVISION2 (*) | I   |                         |                       | Revision setting            |

| D5  | REVISION3 (*) | I   |                         |                       | Revision setting            |

| C4  | REVISION4 (*) | I   |                         |                       | Used as ICEMODE setting pin |

| D4  | REVISION5 (*) | I   |                         |                       | Reserved. Fixed to "Low"    |

Note: Do not open these pins. Pull-up or pull-down resistors are required externally.

## 2.2.15. Power Supply and VSS Pins

The table below shows a list of power supply and VSS pins.

Table 14: List of Power Supply and VSS Pins

| No.                                                                              | Pin Name | Description                        |

|----------------------------------------------------------------------------------|----------|------------------------------------|

| C3,D8,E4,E5,F4,F10,G4,H5,<br>J5,J6,J9,J10,K6,K8,L9                               | IOVDDW   | 3.3-V I/O Buffer power supply pins |

| L6,L8,R10,T3                                                                     | VDD33_K  | 3.3V SDRAM power supply            |

| B4,D6,E10,F11,K7,K9                                                              | CVDD     | 1.2-V (core) power supply pins     |

| A1,A14,B2,D3,D7,D12,E3,<br>E6,E7,E8,E9,E12,F3,F5,F6,<br>F7,F8,F9,G3,G5,G6,G7,G8, | DVSS     | Digital Ground                     |

| No.                                                                                                            | Pin Name | Description                                     |

|----------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------|

| G9,G10,G11,G12,H4,H6,H7,<br>H8,H9,H10,H11,H12,J3,J4,<br>J7,J8,J11,J12,K4,K5,K10,L7,<br>L10,P3,P10,R2,U1,U3,U14 |          |                                                 |

| A10,B10,B11                                                                                                    | A33VDD   | 3.3V Analog Power Supply pins                   |

| C10,D9,D10,E11                                                                                                 | A12VDD   | 1.2V Analog Power Supply pins                   |

| A7,A13,B8,B9,B12,D11,F12                                                                                       | AVSS     | Analog Ground                                   |

| C11                                                                                                            | PLLAVDD  | 1.2V Analog VDD pin for Baseband PLL            |

| C12                                                                                                            | PLLAVSS  | Analog Ground pin for Baseband PLL              |

| C14                                                                                                            | PLLDVDD  | 1.2V Digital VDD pin for Baseband PLL           |

| C13                                                                                                            | PLLDVSS  | Digital Ground for Baseband PLL                 |

| A3,B3                                                                                                          | OSC33VDD | Crystal Oscillator Buffer 3.3V Power Supply pin |

| A6,B5                                                                                                          | OSCVSS   | Crystal Oscillator Buffer Ground                |

#### 2.2.16. Shared Pins

The table below shows a list of shared pins.

**Table 15: List of Shared Pins**

| No. | Pin Name | Shared<br>Pin Name | Description                                            |

|-----|----------|--------------------|--------------------------------------------------------|

| F1  | GPIO4    | AJTRSTN            | Switchable with normal mode/ICE mode settings.         |

| F2  | GPIO5    | AJTDI              | Switchable with normal mode/ICE mode settings.         |

| G2  | GPIO6    | AJTMS              | Switchable with normal mode/ICE mode settings.         |

| G1  | GPIO7    | AJTCK              | Switchable with normal mode/ICE mode settings.         |

| H2  | GPIO8    | AJRTCK             | Switchable with normal mode/ICE mode settings.         |

| H1  | GPIO9    | AJTDO              | Switchable with normal mode/ICE mode settings.         |

| J2  | GPIO10   | AJSRSTN            | Switchable with normal mode/ICE mode settings.         |

| K2  | GPIO12   | EXTINT             | Can be switched with GPIO selection register settings. |

# 3. Operating Conditions

## 3.1. Absolute Maximum Ratings

The table below shows absolute maximum ratings.

**Table 16: Absolute Maximum Ratings**

| Parameter                                                                 | Symbol                                                | Rating                                                                                | Unit   |

|---------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------|--------|

| 3.3V supply voltage for I/O                                               | Viovddw                                               | -0.3 to 4.0                                                                           | V      |

| 3.3V supply voltage for SDRAM                                             | V <sub>VDD33_K</sub>                                  | -0.3 to 4.0                                                                           | V      |

| 3.3V supply voltage for Analog                                            | V <sub>A33VDD</sub>                                   | -0.3 to 4.0                                                                           | V      |

| 3.3V supply voltage for OSC                                               | Vosc33VDD                                             | -0.3 to 4.0                                                                           | V      |

| 1.2V supply voltage for Baseband,<br>AFE digital                          | Vcvdd                                                 | -0.3 to 1.32                                                                          | V      |

| 1.2V supply voltage for AFE analog                                        | V <sub>A12VDD</sub>                                   | -0.3 to 1.6                                                                           | V      |

| Input pin voltage<br>Standard<br>SDRAM signals (Vendor test purpose only) | Vı                                                    | -0.3 to V <sub>IOVDDW</sub> + 0.3 (≤4.0)<br>-0.3 to V <sub>VDD33_K</sub> + 0.3 (≤4.0) | V      |

| Input pin voltage (5V tolerant)<br>(3.0V ≤ V <sub>IOVDDW</sub> ≤ 3.6V)    | Vı                                                    | -0.3 to 5.6                                                                           | V      |

| Input pin voltage (5V tolerant)<br>(VIOVDDW < 3.0V)                       | Vı                                                    | -0.3 to 4.0                                                                           | V      |

| Analog Input/Output Voltage RXP,RXN,IREF IOUTP, IOUTN OSCIN, XTAL         | V <sub>A1</sub><br>V <sub>A2</sub><br>V <sub>A3</sub> | -0.3 to V <sub>A33VDD</sub> +0.3<br>-0.3 to 6.0<br>-0.3 to V <sub>OSC33VDD</sub> +0.3 | V<br>V |

| Output current (2mA)                                                      | Io                                                    | -5.2/+15.9                                                                            | mA     |

| Output current (4mA)                                                      | lo                                                    | -10.6/+31.7                                                                           | mA     |

| Output current (8mA)                                                      | Io                                                    | -21.2/+63.4                                                                           | mA     |

Note: The absolute maximum ratings are the limit values beyond which the IC may be damaged. Operation is not guaranteed under these conditions.

Directly connect all VDD pins to external power supplies and ground all VSS pins.

Ensure that the junction temperature (Tj) is 125°C or less during use.

# 3.2. Power Supply Specifications

**Table 17: Power Supply Specifications**

| Parameter            | Symbol                                   | Conditions   | Min. | Тур.       | Max. | Unit     |

|----------------------|------------------------------------------|--------------|------|------------|------|----------|

| 3.3V supply voltage  | VIOVDDW VA33VDD VOSC33VDD VVDD33_K       |              | 3.1  | 3.3        | 3.5  | V        |

| 1.2V supply voltage  | V <sub>CVDD</sub><br>V <sub>D12VDD</sub> |              | 1.1  | 1.2        | 1.3  | V        |

| Idle Mode Current    | lidle                                    | 3.3V<br>1.2V |      | 86<br>231  |      | mA<br>mA |

| Tx Mode Current      | Itx                                      | 3.3V<br>1.2V |      | 145<br>218 |      | mA<br>mA |

| Rx Mode Current      | Irx                                      | 3.3V<br>1.2V |      | 96<br>258  |      | mA<br>mA |

| Standby Mode Current | Istby                                    | 3.3V<br>1.2V |      | 20<br>12   |      | mA<br>mA |

Note: Typical values are at Ta = +25°C.

The current is measured with MLKHN1500B (256Mbit), Terminal mode.

## 3.3. Thermal Information

**Table 18: Thermal Information**

| Parameter                                | Symbol           | Conditions                                      | Min. | Тур. | Max. | Unit |

|------------------------------------------|------------------|-------------------------------------------------|------|------|------|------|

| Storage temperature                      | T <sub>stg</sub> |                                                 | -55  |      | 125  | °C   |

| Operating case temperature (Top of case) | Тс               | JESD51-7<br>(2s2p, 76.2mm x 114.3mm)<br>P=0.81W | -40  |      | 105  | °C   |

#### 4. Baseband Part

#### 4.1. Block Diagram

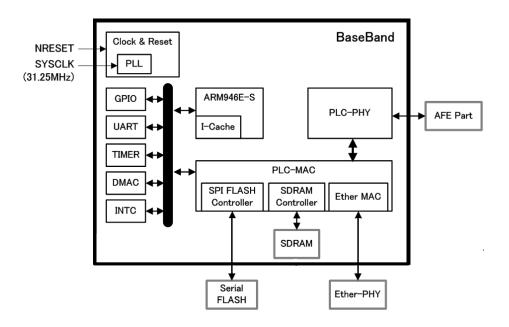

The figure below provides a block diagram for the MLKHN1500 Baseband part.

Figure 3: MLKHN1500 Block Diagram

#### 4.2. List of Functions

#### 4.2.1. Microcontroller and Peripherals

- CPU: ARM946E-S with 16 Kbyte Instruction Cache

- System Clock: 125MHz

- Interrupt Controller

- 16bit Timer: 8 Channels

- Serial Communication Controller: 1 Channel

- GPIO

- DMAC

- Debug Function: Embedded ICE

#### 4.2.2. PLC-PHY Function

- Frequency bandwidth: 2 MHz to 28 MHz

- Transmission scheme: Wavelet OFDM

- Sampling frequency: 62.5 MHz

- Sub carrier: 360 carriers (without notch filter: 432 carriers) including flexible notch function

- Primary modulation scheme: 32-PAM to 2-PAM

- Transmission speed: 240Mbps

- Error correction schemes: LDPC-CC, Reed-Solomon encoding and decoding / convolutional encoding +Viterbi decoding

#### 4.2.3. PLC-MAC Processing Function

- Multiple access control method: CSMA/CA

- Data encryption functionality: 128bit AES

- Channel estimation control functionality

- Integrated IEEE 802.3 compliant MAC

- Integrated SDRAM controller

#### 4.2.4. SPI FLASH Interface Function

- SPI (Serial Peripheral Interface): Flash memory control functionality

- Clock frequency: 50MHz

- Boot RAM: 4Kbyte integrated boot RAM

#### 4.2.5. Ethernet PHY Interface Functions

- Supported interface: MII/RMII/TMII

- Clock frequency: 25MHz(MII)/50MHz(RMII, TMII)

#### 4.2.6. Clock and Reset Control Functions

- Clock generation: 25MHz / 31.25MHz / 50MHz / 62.5MHz / 125MHz / 250MHz

- Reset control functionality

- Low-power mode control functionality

- Link signal monitoring function

#### 4.3. Example System Architectures

This section illustrates example normal mode and ICE mode system architectures for the MLKHN1500. For more information about these modes, see Section 4.6.1 Normal and Test Modes.

#### 4.3.1. Normal Mode

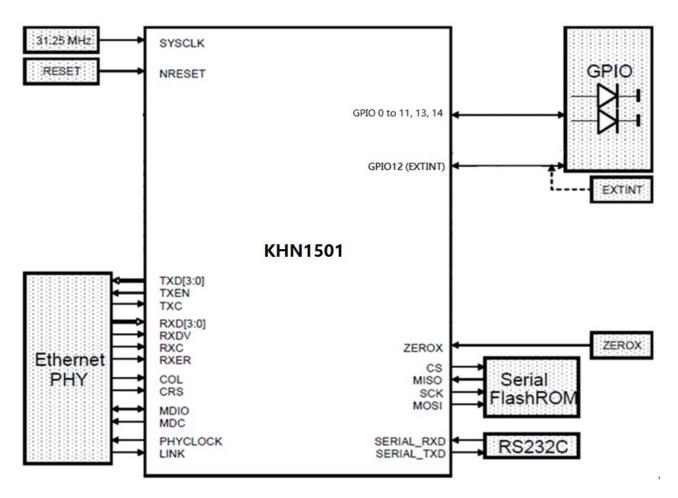

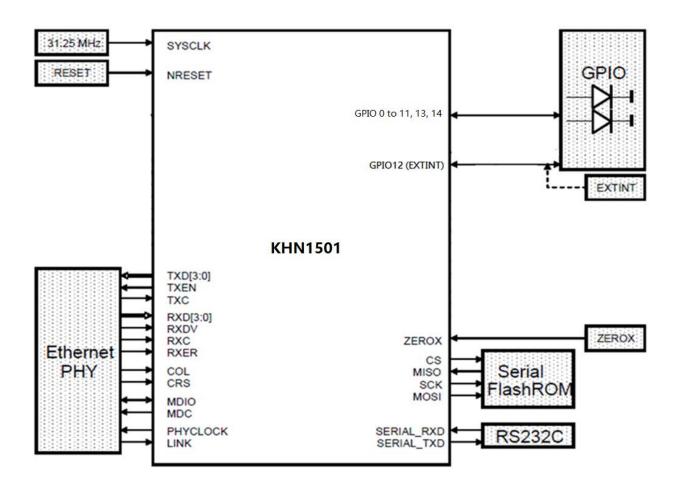

The figure below illustrates an example of normal mode system architecture.

Figure 4: Normal Mode Connection Diagram

#### 4.3.2. ICE Mode

The figure below illustrates an example of ICE mode system architecture. See Section 4.9.2 for Normal mode/ICE mode settings.

Figure 5: ICE Mode Connection Diagram

Note: GPIO10 to GPIO4 cannot be used as general-purpose ports during ICE mode operation.

The rest of GPIO can be used as GPO, but not as GPI.

After reset, GPIO is set to the input, and turn into the output immediately.

\*GPIO12's EXTINT function is available even during ICE mode operation.

#### 4.4. Electrical Characteristics

The table below show electrical characteristics.

**Table 19: Electrical Characteristics**

| Parameter               | Symbol           | Conditions                                                                                                         | Min. | Тур. | Max. | Unit |

|-------------------------|------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input high voltage      | VIH              |                                                                                                                    | 2.0  |      |      | V    |

| Input low voltage       | V <sub>IL</sub>  |                                                                                                                    |      |      | 0.8  | V    |

| Input threshold voltage | VT               |                                                                                                                    | 1.30 | 1.40 | 1.50 | V    |

| Schmitt Trigger         | V <sub>T+</sub>  | Low to High                                                                                                        | 1.56 | 1.68 | 1.77 | V    |

| Input threshold voltage | V <sub>T</sub> - | High to Low                                                                                                        | 1.14 | 1.23 | 1.33 | V    |

| Input leakage current   | ILI              | VI = VIOVDDW or VSS                                                                                                |      |      | ±10  | μΑ   |

| Pull-up resistor        | Rıн              | V <sub>I</sub> = V <sub>SS</sub>                                                                                   | 26   | 38   | 59   | kΩ   |

| Pull-down resistor      | RıL              | VI = VIOVDDW or Vss                                                                                                | 33   | 47   | 81   | kΩ   |

| Output high voltage     | Vон              |                                                                                                                    | 2.4  |      |      | ٧    |

| Output low voltage      | V <sub>OL</sub>  |                                                                                                                    |      |      | 0.4  | V    |

| Output leakage current  | O <sub>LI</sub>  | V <sub>I</sub> = V <sub>IOVDDW</sub> or V <sub>SS</sub><br>V <sub>O</sub> = V <sub>IOVDDW</sub> or V <sub>SS</sub> |      |      | ±10  | μA   |

| Power dissipation       | Pd               |                                                                                                                    |      | *590 |      | mW   |

Note: \*includes whole blocks' (AFE, BB, SDRAM, etc) power dissipation

Conditions:  $VIOVDDW = VVDD33_K = VA33VDD = VOSC33VDD = 3.3 V \pm 0.3 V$

$VCVDD = VA12VDD = 1.2 V \pm 0.12 V$

-40°C < Tj < 125°C

#### 4.5. AC Characteristics

The following shows AC characteristics.

Note: 5pF load capacitance is assumed.

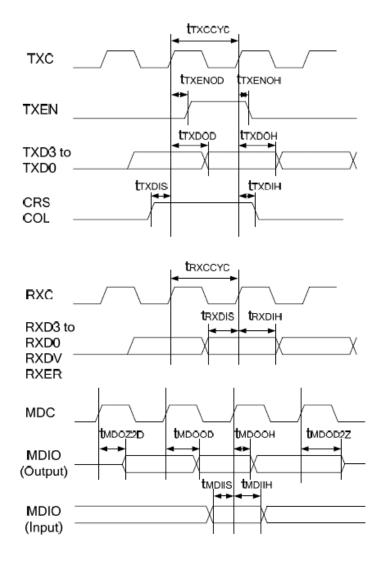

## 4.5.1. Ethernet Connection Pins (MII/TMII Specification) Timing

Table 20: Ethernet Connection Pins (MII Specification) Timing Parameters

| Parameter                                              | Symbol              | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|---------------------|------------|------|------|------|------|

| MII clock cycle time (TXC)                             | txccyc              |            |      | 40.0 |      | ns   |

| MII signal output delay time (TXEN)                    | t <sub>TXENOD</sub> |            | 3.5  |      | 10.5 | ns   |

| MII signal output hold time (TXEN)                     | tтхемон             |            | 3.5  |      |      | ns   |

| MII signal output delay time (TXD3 to TXD0)            | t <sub>TXDOD</sub>  |            | 3.5  |      | 10.5 | ns   |

| MII signal output hold time (TXD3 to TXD0)             | tтхрон              |            | 3.5  |      |      | ns   |

| MII signal input setup time (CRS, COL)                 | t <sub>TXDIS</sub>  |            |      |      |      | ns   |

| MII signal input hold time (CRS, COL)                  | <b>t</b> TXDIH      |            |      |      |      | ns   |

| MII clock cycle time (RXC)                             | trxccyc             |            |      | 40.0 |      | ns   |

| MII signal input setup time (RXD3 to RXD0, RXDV, RXER) | trxdis              |            | 5.0  |      |      | ns   |

| MII signal input hold time (RXD3 to RXD0, RXDV, RXER)  | trxdih              |            | 5.0  |      |      | ns   |

| MII signal drive delay time (MDIO)                     | t <sub>MDOZ2D</sub> |            | 30.0 |      | 33.0 | ns   |

| MII signal disable delay time (MDIO)                   | t <sub>MDOD2Z</sub> |            | 30.0 |      | 33.0 | ns   |

| MII signal output delay time (MDIO)                    | t <sub>MDOOD</sub>  |            | 30.0 |      | 33.0 | ns   |

| MII signal output hold time (MDIO)                     | tмдоон              |            | 30.0 |      |      | ns   |

| MII signal input setup time (MDIO)                     | t <sub>MDIIS</sub>  |            | 3.0  |      |      | ns   |

| MII signal input hold time (MDIO)                      | tmdiih              |            | 0.0  |      |      | ns   |

Table 21: Ethernet Connection Pins (TMII Specification) Timing Parameters

| Parameter                                              | Symbol              | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------|---------------------|------------|------|------|------|------|

| MII clock cycle time (TXC)                             | t <sub>TXCCYC</sub> |            |      | 20.0 |      | ns   |

| MII signal output delay time (TXEN)                    | t <sub>TXENOD</sub> |            | 3.5  |      | 10.5 | ns   |

| MII signal output hold time (TXEN)                     | ttxenoh             |            | 3.5  |      |      | ns   |

| MII signal output delay time (TXD3 to TXD0)            | txxdod              |            | 3.5  |      | 10.5 | ns   |

| MII signal output hold time (TXD3 to TXD0)             | tтхрон              |            | 3.5  |      |      | ns   |

| MII clock cycle time (RXC)                             | trxccyc             |            |      | 20.0 |      | ns   |

| MII signal input setup time (RXD3 to RXD0, RXDV, RXER) | t <sub>RXDIS</sub>  |            | 5.0  |      |      | ns   |

| MII signal input hold time (RXD3 to RXD0, RXDV, RXER)  | t <sub>RXDIH</sub>  |            | 5.0  |      |      | ns   |

| MII signal drive delay time (MDIO)                     | t <sub>MDOZ2D</sub> |            | 30.0 |      | 33.0 | ns   |

| MII signal disable delay time (MDIO)                   | t <sub>MDOD2Z</sub> |            | 30.0 |      | 33.0 | ns   |

| MII signal output delay time (MDIO)                    | t <sub>MDOOD</sub>  |            | 30.0 |      | 33.0 | ns   |

| MII signal output hold time (MDIO)                     | tмдоон              |            | 30.0 |      |      | ns   |

| MII signal input setup time (MDIO)                     | t <sub>MDIIS</sub>  |            | 3.0  |      |      | ns   |

| MII signal input hold time (MDIO)                      | t <sub>MDIIH</sub>  |            | 0.0  |      |      | ns   |

Figure 6: Ethernet Connection Pins (MII/TMII Specifications) Timing Chart

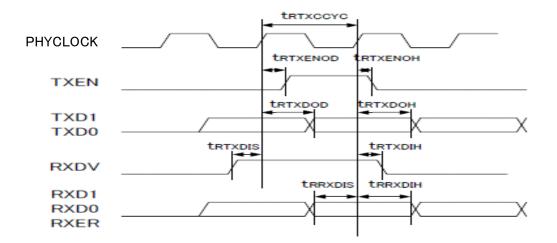

## 4.5.2. Ethernet Connection Pins (RMII Specification) Timing

Table 22: Ethernet Connection Pins (RMII Specification) Timing Parameters

| Parameter                            | Symbol   | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------|----------|------------|------|------|------|------|

| RMII clock cycle time (PHYCLOCK)     | trtxccyc |            |      | 20.0 |      | ns   |

| RMII signal output delay time (TXEN) | trtxenod |            | 2.0  |      | 7.5  | ns   |

| RMII signal output hold time (TXEN)  | trtxenoh |            | 2.0  |      |      | ns   |

| Parameter                                       | Symbol          | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|-----------------|------------|------|------|------|------|

| RMII signal output delay time (TXD1, TXD0)      | trtxdod         |            | 2.0  |      | 7.5  | ns   |

| RMII signal output hold time (TXD1, TXD0)       | <b>t</b> rtxdoh |            | 2.0  |      |      | ns   |

| RMII signal input setup time (RXDV)             | trtxdis         |            | 2.5  |      |      | ns   |

| RMII signal input hold time (RXDV)              | <b>t</b> rtxdih |            | 1.5  |      |      | ns   |

| RMII signal input setup time (RXD1, RXD0, RXER) | trrxdis         |            | 2.5  |      |      | ns   |

| RMII signal input hold time (RXD1, RXD0, RXER)  | trrxdih         |            | 2.0  |      |      | ns   |

Figure 7: Ethernet Connection Pins (RMII Specifications) Timing Chart

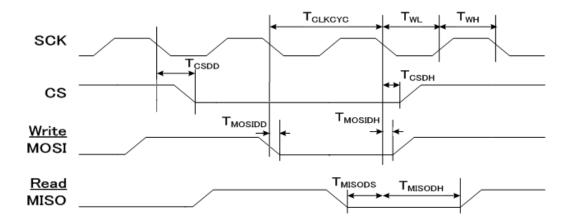

# 4.5.3. Serial Flash Connection Pins Timing (Write)

Table 23: Serial Flash Connection Pins Timing (Write) Parameters

| Parameter                           | Symbol                                   | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------------------|------------------------------------------|------------|------|------|------|------|

| Flash serial clock cycle time (SCK) | Тськсус                                  |            |      | 20.0 |      | ns   |

| Flash serial clock<br>duty (SCK)    | Tclkwh/<br>Tclkcyc<br>Tclkwl/<br>Tclkcyc |            | 45   |      | 55   | %    |

| Flash Chip Select output            | T <sub>CSDD (*1)</sub>                   |            | -1.0 |      | 2.0  | ns   |

| Parameter                                  | Symbol                 | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------------|------------------------|------------|------|------|------|------|

| Delay time                                 |                        |            |      |      |      |      |

| Flash Chip Select output<br>Hold time      | T <sub>CSDH (*1)</sub> |            | -1.0 |      |      | ns   |

| Flash serial data output delay time (MOSI) | TMOSIDD (*1)           |            | -2.0 |      | 4.6  | ns   |

| Flash serial data output hold time (MOSI)  | TMOSIDH (*1)           |            | -2.0 |      |      | ns   |

Note: (\*1) Minus values may prior to the negative edge of SCK.

## 4.5.4. Serial Flash Connection Pins Timing (Read)

Table 24: Serial Flash Connection Pins Timing (Read) Parameters

| Parameter                                 | Symbol                                                                            | Conditions | Min. | Тур. | Max. | Unit |

|-------------------------------------------|-----------------------------------------------------------------------------------|------------|------|------|------|------|

| Flash serial clock cycle time (SCK)       | T <sub>CLKCYC</sub>                                                               |            |      | 20.0 |      | ns   |

| Flash serial clock<br>duty (SCK)          | T <sub>CLKWH</sub> / T <sub>CLKCYC</sub> T <sub>CLKWL</sub> / T <sub>CLKCYC</sub> |            | 45   |      | 55   | %    |

| Flash serial data input setup time (MISO) | T <sub>MISODS</sub>                                                               |            | 9.5  |      |      | ns   |

| Flash serial data input hold time (MISO)  | T <sub>MISODH</sub>                                                               |            | 0.0  |      |      | ns   |

Figure 8: Serial Flash Connection Pins Timing Chart

# 4.6. Description of Operating Modes

#### 4.6.1. Normal and Test Modes

Lists the modes provided by the MLKHN1500.

Table 25: List of Normal and Test Modes

| Normal / Test Mode | Description                                           |

|--------------------|-------------------------------------------------------|

| Normal mode        | This mode is used to operate the system.              |

| ICE mode           | This mode is used to troubleshoot issues experienced. |

#### 4.6.2. Normal Mode

Normal mode is used to operate the system. Use this mode during normal operation.

#### 4.6.3. ICE Mode

ICE mode is used to troubleshoot issues experienced during normal mode operation. GPIO [10:4] are connected to an ICE during ICE mode operation and cannot be used as general-purpose ports in this configuration. For this reason, functionality utilizing GPIO [10:4] cannot be debugged. For more information, see Section 2.2.16 Shared Pins and Section 4.9.2 Normal and Test Modes Setting.

Note: If the AJTRSTN pin is pulled down, it will be continuously in the reset assert state while no debugger is connected in ICE mode, effectively disabling MLKHN1500 operation.

## 4.7. Power Supply Activation

Activate the 3.3V and 1.2V power supplies simultaneously.

\* As a guideline, allow no more than 100ms between the activation of the 3.3V and 1.2V power supplies.

Note: The upper limit of 100ms is a sample value derived from internal evaluations.

## 4.8. Reset Sequence

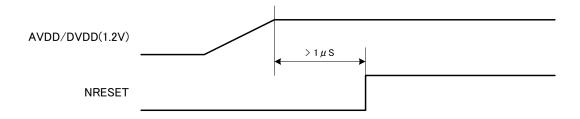

The figure below provides a power-on reset timing chart. Assert reset pin (NRESET) input for at least 1µs after AVDD/DVDD power supplies are stable.

Figure 9: Power-on reset timing chart

## 4.9. Setting Methods

#### 4.9.1. Special Pin Settings

These settings are implemented by connecting external pull-up or pull-down resistors to the REVISION5 to REVISION0 pins. They are used to set the LSI version as well as pin settings for user applications (for use in managing board versions, etc.).

When a reset is activated (NRESET = "L" level), initial values for REVISION5 to REVISION0 pins (the states of their external pull-up/pull-down resistors) are loaded internally. The loaded values can be accessed using the initial value loading register.

Table 26: Special Pin Settings

| Pin Name  | Description                                                  |

|-----------|--------------------------------------------------------------|

| REVISION5 | Fix this pin's setting as follows:<br>External pull-down     |

| REVISION4 | Set ICEMODE.(see 4.9.2) Set as desired. Pull-down or Pull-up |

| REVISION3 | Set as desired. Pull-down or Pull-up                         |

| REVISION2 | Set as desired.<br>Pull-down or Pull-up                      |

| REVISION1 | Set as desired. Pull-down or Pull-up                         |

| REVISION0 | Set as desired. Pull-down or Pull-up                         |

Note: Connect external pull-up or pull-down resistors to all 6 pins. REVISION5 should always be pulled down as described in the table above.

#### 4.9.2. Normal and Test Modes Setting

The setting of the normal and test modes is controlled by REVISION4 input. These settings are sampled during internal reset state. So these pins should remain stable after 300µs from NRESET is de-asserted.

The table below shows Normal mode/ICE mode settings by REVISION4 input.

Table 27: Test Mode Setting by REVISION4 input

| Normal / Test Mode | ICEMODE   |

|--------------------|-----------|

| Normal mode        | "L" level |

| ICE mode           | "H" level |

# 5. Analog Front-End(AFE) Part

#### 5.1. General Description

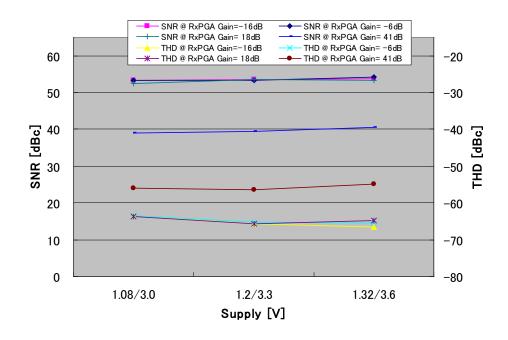

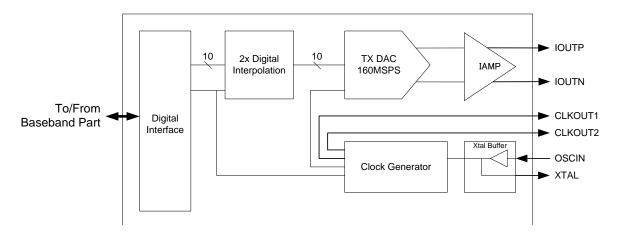

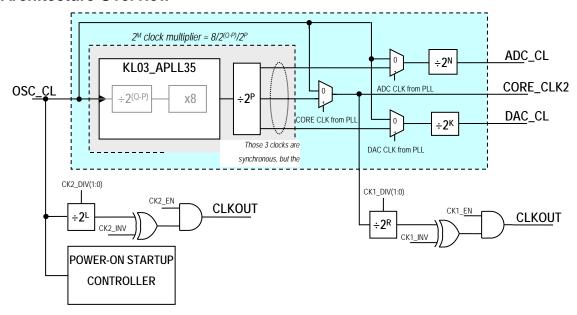

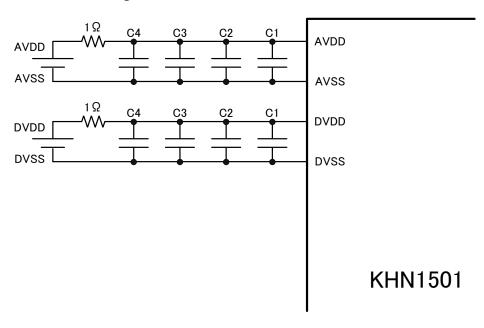

The MLKHN1500 has highly integrated analog front-end part for PLC. Data rate is supported up to 80 MSPS and 160 MSPS in Rx path and Tx path, respectively. Interfacing can be either binary or twos compliment, LSB or MSB first. A serial peripheral interface (SPI) allows software programmability of the front-end. An on-chip PLL multiplier and synthesizer provide all the required clock signals from a single crystal or clock source.

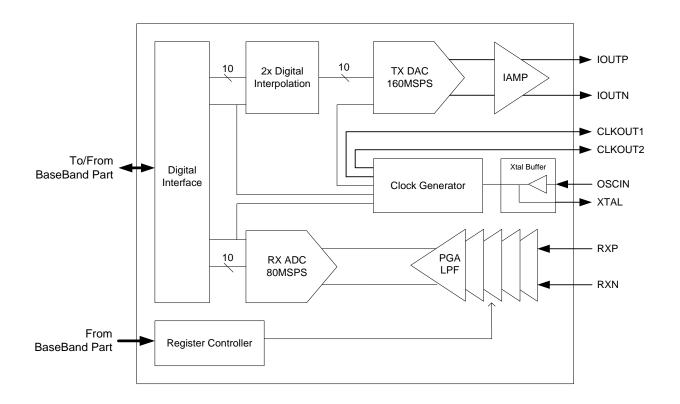

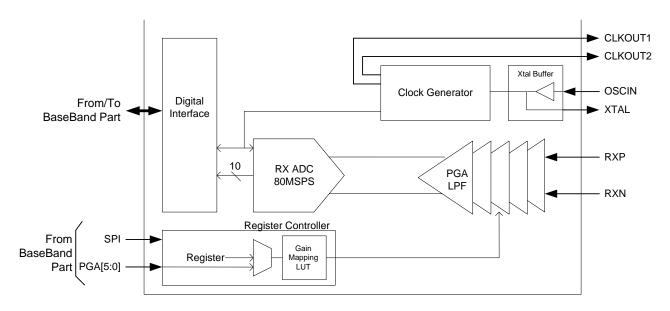

Figure 10: AFE Functional Block Diagram

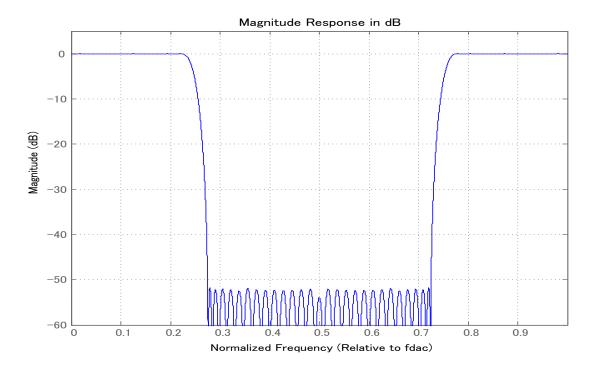

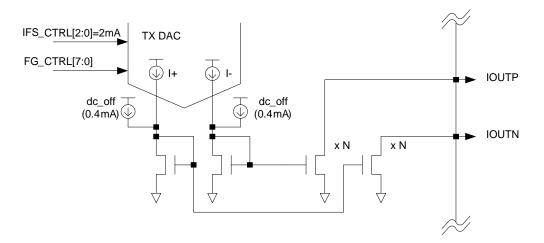

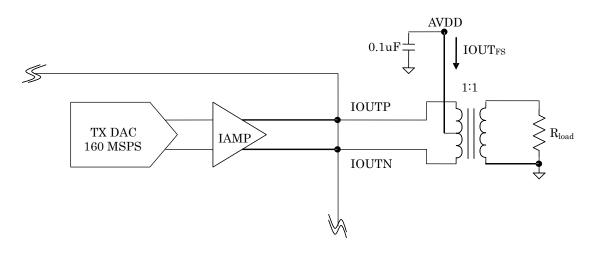

The functional block diagram of the AFE part is shown in the figure above. The Tx signal path consists of a bypassable 2x low pass interpolation filter, a 10-bit TxDAC and a current amplifier (IAMP). The transmit signal path bandwidth is qualified up to frequencies of 36MHz.

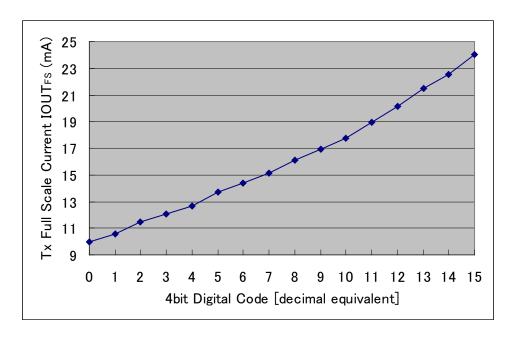

The current amplifier can deliver up to 20mA signal power. Tx power can be controlled over a 7.5dB range with 0.5dB steps.

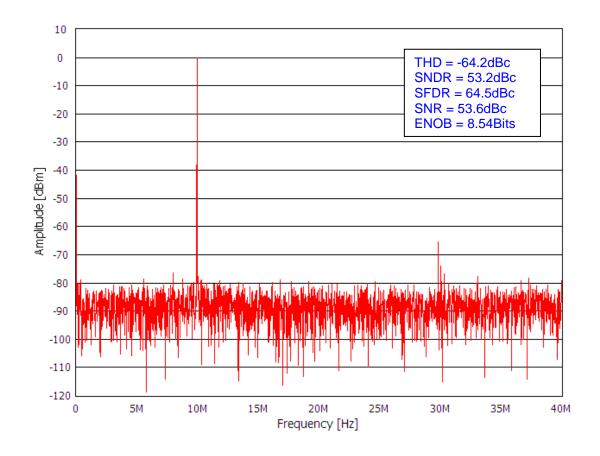

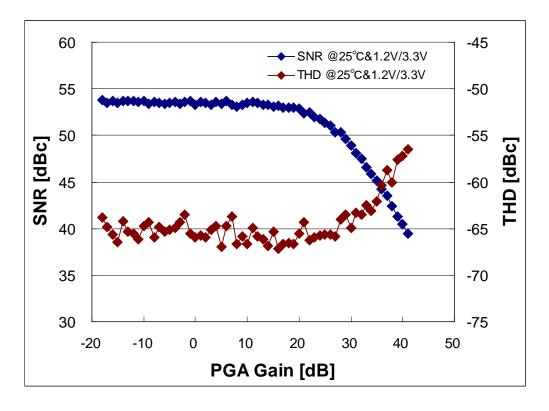

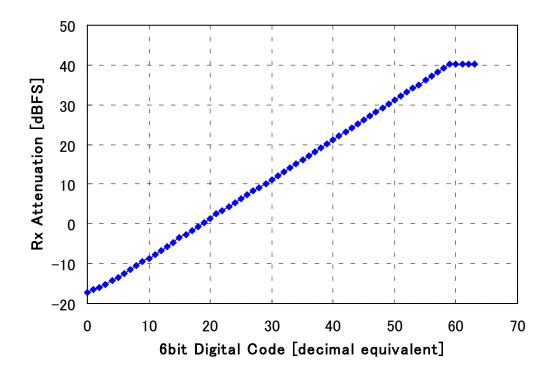

The Rx signal path consists of a programmable amplifier (RxPGA), a low pass filter (LPF) and a 10 bit ADC. The low-noise RxPGA has a programmable gain range of -18dB to +41dB in 1dB steps. Its input referred noise is less than 7.5nV/rtHz for gain settings beyond 30dB. The cutoff frequency of LPF is programmable.

# 5.2. Specifications

# 5.2.1. TX Path specifications

**Table 28: TX Path Specifications**

| Parameter                                             | Temp | Min  | Тур       | Max  | Unit              |

|-------------------------------------------------------|------|------|-----------|------|-------------------|

| Tx DAC DC CHARACTERISTICS                             |      |      | •         |      |                   |

| Resolution                                            | Full |      | 10        |      | Bits              |

| Update Rate                                           | Full |      |           | 160  | MSPS              |

| Full-Scale Output Current                             | Full |      | 2         |      | mA                |

| Gain Error                                            | Full |      |           | ±6.5 | % of FS           |

| Offset Error                                          | Full |      |           | ±0.1 | % of FS           |

| IAMP OUTPUT CHARACTERISTICS                           |      |      |           |      |                   |

| Output Capacitance                                    | 25°C |      | 6.7       |      | pF                |

| Tx DC CHARACTERISTICS                                 |      |      |           |      |                   |

| Full-Scale Output Current (IFS)                       | Full | 8.4  |           | 20   | mA                |

| DC offset current(dc_off)                             |      |      | 0.4       |      | mA                |

| AC Voltage Compliance Range                           |      | 1.15 |           | 6    | V                 |

| Tx CONTROL CHARACTERISTICS                            |      |      |           |      |                   |

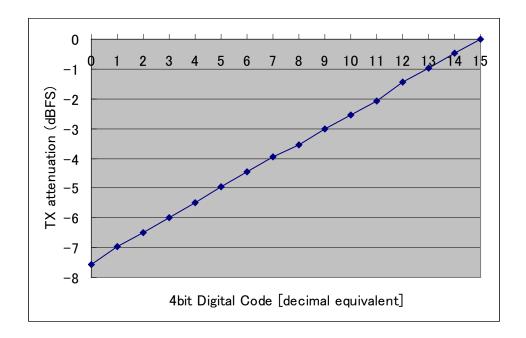

| Minimum Gain                                          | 25°C |      | -7.5      |      | dB                |

| Maximum Gain                                          | 25°C |      | 0         |      | dB                |

| Gain Step Size                                        | 25°C |      | 0.5       |      | dB                |

| Gain Step Accuracy                                    | Full |      | Monotonic |      | dB                |

| Gain Range Error                                      | Full |      |           | 0.5  | dB                |

| Tx AC CHARACTERISTICS                                 |      |      |           |      |                   |