Figure 1

# Intelligent relay driver for automotive applications ROM version for series production

#### 1. Features

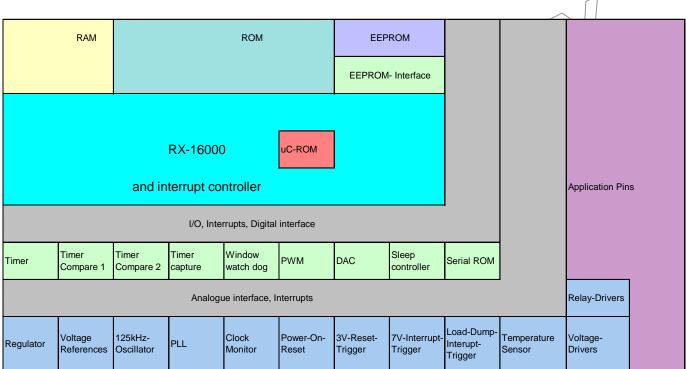

### **CPU** and Interrupts

- WORD- (16 Bit), BYTE- (8 Bit), and BIT- (1Bit) Operations possible

- 11 different user interrupt sources (including RESET)

#### **Memories**

- 8k\*8 user ROM

- 256\*8 RAM

- 128\*16 EEPROM

#### **Periphery**

- 1 On-Chip-Timer

- 1 Timer-Capture-Register (16 bits)

- 2 Timer-Compare-Register (16 bits)

- Window watch dog (5ms/10ms)

- 1 PWM output 20.8 kHz, 7-Bit+1 (duty cycle from 0 to 100%)

- 1 A/D converter (8 bits, 16µs) internal and external reference possible

- 8 ADC-channels analogue multiplexer

- On-Chip-Temperature-Sensor

- · 2 Relay driver outputs, integrated free wheel function

- 2 voltage outputs for driving external circuitry

- 8 bi-directional ports with different possible thresholds, 5V output function

- · 2 Interrupt inputs for timer capture

#### Additional features

- On-Chip-8 MHz-Oscillator (No external components)

- 4V to 26V voltage range, 80V load dump protected,

- typical 150 μA sleep mode current

- Small SO20 package

#### **Development tools**

- Development Environment available with the 10108xy:

- Assembler, Linker, Object-File-Generator, HEX-File Generator, C-Compiler

- ROM-Emulator, In-Circuit-Emulator

- PLCC68 for external ROM-Possibility, ROM-Emulation and In-Circuit-Emulation

- SO24 as OTP for SW development and SW evaluation

- MLX-Programmer for OTPs

The 16201-Jxx is a multiple purpose intelligent relay driver ASIC designed for automotive applications. It uses the RX16000-16 Bit parallel µC of Melexis.

A lot of integrated analogue and digital features allow to design different automotive applications using only a few external components.

10 different interrupts allow to act on real time events, 4 interrupts are accessible via the pins.

The circuit is load dump protected for a 80V load dump pulse.

Due to License agreements with Melexis customers, the 16201Jxx is not free to use in electronic window lifter applications.

# Intelligent relay driver for automotive applications ROM version for series production

### 2. Table of contents

|                                                                                                                                                                                | $\sim$ 11 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1Features                                                                                                                                                                      |           |

| 2Table of contents                                                                                                                                                             |           |

| 3                                                                                                                                                                              | 3/        |

| 4. Device coding encryption                                                                                                                                                    |           |

| 5. Mechanical data                                                                                                                                                             | 4         |

| 5. Mechanical data<br>6. Pinout: SQ20 package                                                                                                                                  | 6         |

| 7. Absolute maximum ratings                                                                                                                                                    | 7         |

| 7. Absolute maximum ratings                                                                                                                                                    | 8         |

| 9. Eeprom characteristics                                                                                                                                                      | 12        |

| 10. Quality and Reliability targets                                                                                                                                            | 12        |

| 11CPU-core description                                                                                                                                                         | 12        |

| 8. Electrical characteristics 9. Eeprom characteristics 10. Quality and Reliability targets 11. CPU-core description 12. Description of Periphery 12.1 Memory mapping 12.2 ROM | 13        |

| 12.1 Memory mapping                                                                                                                                                            | 13        |

| 12.2 ROM                                                                                                                                                                       | 14        |

| 12.2.1                                                                                                                                                                         | 14        |

| 12.2.2                                                                                                                                                                         | 14        |

| 12.3Portsmap description                                                                                                                                                       |           |

| 12.4Periphery access, Timing                                                                                                                                                   | 18        |

| 12.5Description of important peripheral blocks                                                                                                                                 | 20        |

| 12.5.1. Eeprom interface                                                                                                                                                       | 20        |

| 12.5.2Window Watch dog                                                                                                                                                         | 20        |

| 12.5.3                                                                                                                                                                         |           |

| 12.5.4The configuration possibilities of the Key-Thresholds and the Key-Interrupt                                                                                              |           |

| 13                                                                                                                                                                             | 22        |

| 13.1Reset of the periphery                                                                                                                                                     | 22        |

| 13.2Load dump protection                                                                                                                                                       |           |

| 13.3Trimming                                                                                                                                                                   | 22        |

| 13.4 Short circuit protection on application pins                                                                                                                              | 24        |

| 14. Debugging facilities                                                                                                                                                       |           |

| 15. History record                                                                                                                                                             | 25        |

Intelligent relay driver for automotive applications ROM version for series production

### 3. Typical Application

Figure 2 shows a typical application.

Figure 2

KEY2

KEY3

KEY4

KEY5

AD1

TC2

KEY7

TC1

KEY6

TST

PS1

HALL

HALL

SUPL

## 4. Device coding encryption

The coding of the device is encrypted in the following way:

### 16202.Jxx

with:

16201: Chip name

J: Hardware version, Melexis counts this letter up, in case of a major change in the chip design xx: Internal SW- (ROM-) version, encryption is linked to a given application and to a given customer

# Intelligent relay driver for automotive applications ROM version for series production

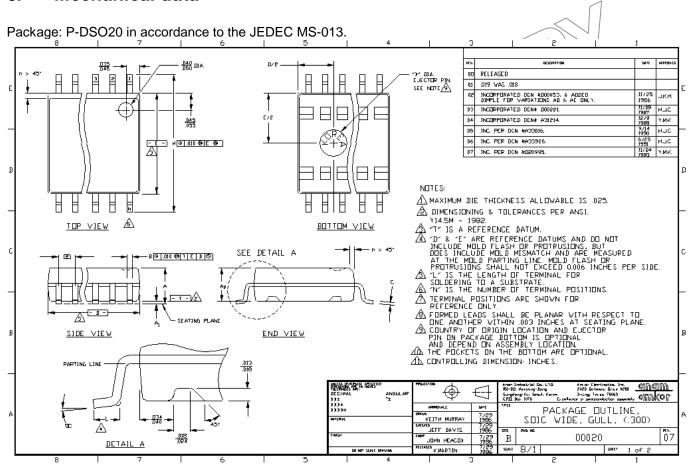

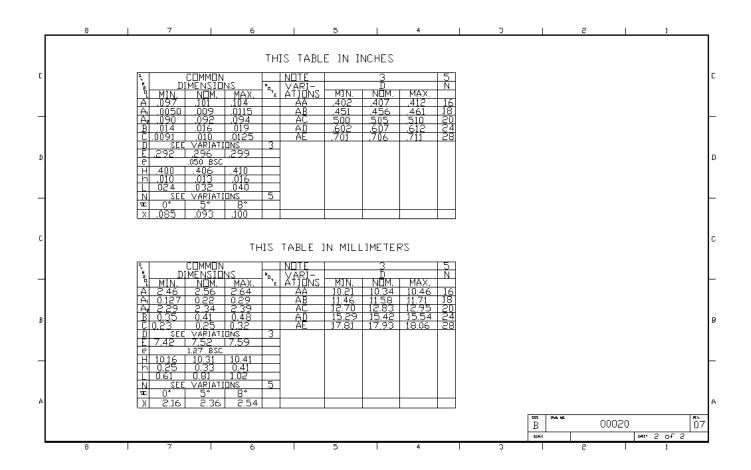

### 5. Mechanical data

# Intelligent relay driver for automotive applications ROM version for series production

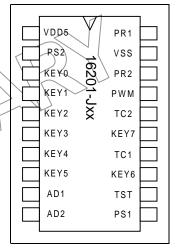

## 6. Pinout: SO20 package

|        | 1    |                                                                                                                                                                                                                          |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin    | Name | Function                                                                                                                                                                                                                 |

| Pin 1  | VDD5 | <ul> <li>Supply voltage pin</li> <li>Connected to 3V-Reset (WBB)</li> <li>Connected to Power On Reset (CBB)</li> </ul>                                                                                                   |

|        |      | Connected to Load Dump Interrupt                                                                                                                                                                                         |

| Pin 2  | PS2  | <ul> <li>5V-supply output for external components, together with software short circuit protected</li> <li>ADC-input with 6V-range for diagnosis</li> <li>External ADC-reference input</li> <li>Digital input</li> </ul> |

| Pin 3  | KEY0 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and undebounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>                 |

| Pin 4  | KEY1 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and undebounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>                 |

| Pin 5  | KEY2 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and undebounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>                 |

| Pin 6  | KEY3 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and not debounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>               |

| Pin 7  | KEY4 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and not debounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>               |

| Pin 8  | KEY5 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and not debounced available</li> <li>Push pull output with 5V</li> <li>Connected to key interrupt</li> </ul>               |

| Pin 9  | AD1  | <ul> <li>ADC-input with 22V range</li> <li>Reference for all ratio-metric threshold levels of the KEY-inputs</li> <li>Digital input</li> <li>Connected to 7V-Interrupt</li> </ul>                                        |

| Pin 10 | AD2  | <ul><li>ADC-input with 6V range</li><li>Digital input</li></ul>                                                                                                                                                          |

| Pin 11 | PS1  | <ul> <li>Supply output for external components, follows VDD5 but max. 23V, short circuit protected</li> <li>ADC-input with 22V range for diagnosis</li> <li>Digital input</li> </ul>                                     |

| Pin 12 | TST  | Test pin, internally pulled down                                                                                                                                                                                         |

| Pin 13 | KEY6 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and undebounced available</li> </ul>                                                                                       |

# Intelligent relay driver for automotive applications ROM version for series production

|        |      | Push pull output with 5V                                                                                                                                                                          |

|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |      | Connected to key interrupt                                                                                                                                                                        |

| Pin 14 | TC1  | <ul><li>Digital input , internally pulled up to 5V</li><li>Capture interrupt</li></ul>                                                                                                            |

| Pin 15 | KEY7 | <ul> <li>Bi-directional port pin</li> <li>Input function with different thresholds, debounced and undebounced available</li> <li>Open drain output</li> <li>Connected to key interrupt</li> </ul> |

| Pin 16 | TC2  | <ul> <li>Digital input, internally pulled up to 5V</li> <li>Capture interrupt</li> </ul>                                                                                                          |

| Pin 17 | PWM  | PWM 5V push pull output     Digital input                                                                                                                                                         |

| Pin 18 | PR1  | <ul> <li>Open drain relay driver output with free wheel function, together with software short circuit protected</li> <li>ADC-input with 22V range for diagnosis</li> </ul>                       |

| Pin 19 | VSS  | Ground pin                                                                                                                                                                                        |

| Pin 20 | PR2  | <ul> <li>Open drain relay driver output with free wheel function, together with software short circuit protected</li> <li>ADC-input with 22V range for diagnosis</li> </ul>                       |

## 7. Absolute maximum ratings

| Parameter                                           | Symbol   | Condition | Min  | Max      | Unit |

|-----------------------------------------------------|----------|-----------|------|----------|------|

| Power supply                                        | VDD5     | DC        |      | 26       | V    |

|                                                     |          | max. 0.5s |      | 80       | V    |

| Maximum input current in any pin                    | lin      |           | -10  | 10       | mA   |

| Maximum input voltage on any pin                    | Vin      |           | -0.3 | VDD5+0.3 | V    |

| Maximum input voltage on PS2,                       | Vinps2   |           |      | 12       | V    |

| in case external input voltage is used              |          |           |      |          |      |

| Maximum input voltage on PS1,                       | Vinps1   |           |      | 12       | V    |

| in case external input voltage is used              |          |           |      |          |      |

| Maximum input voltage on KEY[7:0],                  | Vinkey   |           |      | 22       | V    |

| in case they are <b>not</b> protected with external |          |           |      |          |      |

| 100k protection resistor                            |          |           |      |          |      |

| Maximum input voltage on AD1, in case it is         | Vinad1   |           |      | 22       | V    |

| <b>not</b> protected with external 50k protection   |          |           |      |          |      |

| resistor                                            |          |           |      |          |      |

| Maximum input voltage on pins TC[2:1]               | Vintc    |           |      | 18       | V    |

| Thermal resistance SO20 (Junction to                | Rtrj-a   |           |      | 86       | K/W  |

| Ambient)                                            |          |           |      |          |      |

| Maximum junction temperature                        | Tjunc    |           |      | 150      | °C   |

| Maximum junction temperature in case of             | Tjunc/EE |           |      | 140      | °C   |

| EEPROM WRITE                                        |          |           |      |          |      |

| Maximum power dissipation SO20                      | Ptot     | at 85 °C  |      | 755      | mW   |

| Maximum storage temperature                         | Tstor    |           | -55  | 155      | °C   |

| Maximum soldering temperature (t=10s),              | Tsold    |           |      | 300      | °C   |

| the manufacturing requirements defined in the       |          |           |      |          |      |

| "General Specification for Semiconductor            |          |           |      |          |      |

| Devices" of Bosch are met                           |          |           |      |          |      |

# Intelligent relay driver for automotive applications ROM version for series production

### 8. Electrical characteristics

Following characteristics are valid over the full temperature range of  $T = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$  and a supply range of  $26\text{V} \ge \text{VDD5} > 5\text{V}$  unless otherwise noted.

With 5V ≥ VDD5 > v3vreset the controller works correctly, analogue parameters can not be guaranteed. RAM content is guaranteed till vpor < VDD5.

If several pins are charged with transients above VDD5 and below VSS, the summary of all substrate currents of

the influenced pins should not exceed 20mA for correct work of the device.

| Parameter                   | Symbol Conditions |                      |        | Limits   |        | Units           |

|-----------------------------|-------------------|----------------------|--------|----------|--------|-----------------|

|                             |                   |                      | Min    | Тур      | Max    |                 |

|                             |                   | Global parameters    | ;      |          |        |                 |

| Working current during      | iddhvn            | VDD5=80V, all        |        | 20       | 40     | mA              |

| 80V load dump               |                   | pins are inputs      |        |          |        |                 |

| Normal working current      | iddn /            | √DD5=13V, all        | 1.5    | 4        | 8      | mA              |

|                             |                   | pins are inputs,     |        |          |        |                 |

|                             |                   | trimmed              |        |          |        |                 |

|                             |                   | PLL to 8MHz          |        |          |        |                 |

| Sleep mode current          | idds              | VDD5=13V, all        |        | 150      | 200    | μΑ              |

|                             |                   | pins are inputs,     |        |          |        |                 |

|                             |                   | trimmed main         |        |          |        |                 |

|                             |                   | oscillator to        |        |          |        |                 |

|                             |                   | 125kHz, T=25°C       |        |          |        |                 |

| Sleep mode current          | iddsht            | VDD5=13V, all        |        |          | 300    | μΑ              |

|                             |                   | pins are inputs,     |        |          |        |                 |

|                             |                   | trimmed main         |        |          |        |                 |

|                             |                   | oscillator to        |        |          |        |                 |

|                             |                   | 125kHz               |        |          |        |                 |

|                             | T .               | Frequencies          |        | <u> </u> |        |                 |

| Frequency of the trimmed    | fmain             | main oscillator is   | 118.75 | 125      | 131.25 | kHz             |

| main oscillator             |                   | trimmed              |        | _        |        |                 |

| Frequency of the PLL        | fpll              | main oscillator is   | 7.6    | 8        | 8.4    | MHz             |

|                             |                   | trimmed              |        |          |        |                 |

| Frequency of the PWM        | fpwm              | main oscillator is   | 19.76  | 20.8     | 21.84  | kHz             |

|                             |                   | trimmed              |        |          |        |                 |

|                             |                   | DC related paramet   |        |          | 1      | 1               |

| relative error of DAC       | relerrdac         |                      | -1/2   |          | +1/2   | LSB             |

| relative monotonic error of | monerrdac         |                      | 0      |          | 0      | LSB             |

| DAC and ADC                 |                   |                      |        | _        |        |                 |

| Accuracy of temperature     | terr              | sensor is            | -10    | 0        | +10    | °C              |

| measurement with            |                   | calibrated on edge   |        |          |        |                 |

| internal sensor             |                   | temperatures         |        |          | _      | 24 44 11        |

| Accuracy of ADC             | ad1err            | V(AD1) max.          | -7     | 0        | 7      | % of full range |

| measurement on AD1          |                   | 16.5V,               |        |          |        |                 |

| (22V range)                 |                   | ADC is trimmed on    |        |          |        |                 |

|                             |                   | AD1, ADC             |        |          |        |                 |

|                             |                   | correction factor at |        |          |        |                 |

| A                           | a da 00:          | 4001h is used        | 40     |          | 40     | 0/ -f f         |

| Accuracy of ADC             | adc22verr         | V (channel) max.     | -10    | 0        | 10     | % of full range |

| measurements on PS1,        |                   | 16.5V, ADC is        |        |          |        |                 |

| PR1, PR2, SUPPLY            |                   | trimmed on PR1,      |        |          |        |                 |

| (00) (                                   | T           | ADO                                       | 1         | T           |                           | T                                     |

|------------------------------------------|-------------|-------------------------------------------|-----------|-------------|---------------------------|---------------------------------------|

| (22V range)                              |             | ADC correction factor at                  |           |             |                           |                                       |

|                                          |             | 4004h is used                             |           |             |                           |                                       |

| Accuracy of ADC                          | adc6verr    | V (channel) max.                          | -10       | 0           | 10 <                      | % of full range                       |

| measurements on PS2,                     | aucoven     | 4.5V, ADC is                              | -10       | U           | 10                        | 70 Of full farige                     |

| AD2                                      |             | trimmed on AD2,                           |           |             |                           |                                       |

| (6V range)                               |             | correction factor at                      |           |             | /                         |                                       |

| · 3 /                                    |             | 4005h is used                             |           | (       > ) | $\langle   \   \ \rangle$ | >                                     |

| Accuracy ratiometric                     | ad2raterr   |                                           | -5        | 0/          | 5                         | % of fraction                         |

| measurement on AD2 in                    |             |                                           |           | · 1         |                           | between PS2                           |

| case external DAC                        |             |                                           | /    /  / | ~           |                           | and AD2                               |

| reference on PS2 is used                 |             | D4 related research                       |           |             |                           |                                       |

| Input registance on AD1                  | rinad1      | D1 related paramete                       |           | 2           | 1                         | MO                                    |

| Input resistance on AD1                  |             | VIDDE: 71                                 | 0.85      | 2           | 1.25                      | MΩ<br>V                               |

| Digital input threshold level H => L     | vipnomlad1  | VDD5>7V                                   | 0.75      | 1           |                           |                                       |

| Digital input threshold                  | vipnomhad1  | VDD5>7V                                   | 3.75      | 4           | 4.25                      | V                                     |

| level L => H                             |             | \(\mathbb{D} = \mathbb{D} \(\mathbb{C} \) |           |             |                           | .,                                    |

| Hysteresis                               | vhystnomad1 | VDD5>7V                                   | 2.5       | 3           | 3.5                       | V                                     |

| Lastrana summent in ADO                  |             | D2 related paramete                       | ers       | T           |                           |                                       |

| Leakage current in AD2                   | ileakad2    | \/DD5_7\/                                 | 0.75      | 4           | 2                         | μΑ                                    |

| Digital input threshold level H => L     | vipnomlad2  | VDD5>7V                                   | 0.75      | 1           | 1.25                      | V                                     |

| Digital input threshold level L =>H      | vipnomhad2  | VDD5>7V                                   | 3.75      | 4           | 4.25                      | V                                     |

| Hysteresis                               | vhystnomad2 | VDD5>7V                                   | 2.5       | 3           | 3.5                       | V                                     |

| •                                        | Р           | S2 related paramete                       | ers       |             |                           |                                       |

| Voltage on PS2 in case of                | vps2sh      | PS2 loaded with                           |           |             | 1                         | V                                     |

| short circuit                            |             | 100mA,                                    |           |             |                           |                                       |

| (short circuit protection)               |             | tmax=10ms                                 |           |             |                           |                                       |

| Input resistance on PS2                  | rinps2      |                                           | 30        | 150         | 450                       | kΩ                                    |

| Output voltage on PS2                    | vps2h       | VDD5>7V,<br>PS2 loaded with<br>5mA        | 3.2       | 5           | 5.5                       | V                                     |

| Digital input threshold                  | vipnomlps2  | VDD5>7V                                   | 0.75      | 1           | 1.25                      | V                                     |

| level H => L                             |             | \/DD5_3\/                                 | 0.75      | 4           | 4.05                      | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Digital input threshold level L => H     | vipnomhps2  | VDD5>7V                                   | 3.75      | 4           | 4.25                      | V                                     |

| Hysteresis                               | vhystnomps2 | VDD5>7V                                   | 2.5       | 3           | 3.5                       | V                                     |

| Maximum analogue input                   | viadcref    |                                           |           |             | 6                         | V                                     |

| voltage for external ADC                 |             |                                           |           |             |                           |                                       |

| reference                                |             | C4 malatad manager                        |           |             |                           |                                       |

| Chart aircuit protection as              |             | S1 related paramete                       |           |             | 200                       | l m A                                 |

| Short circuit protection on PS1          | ips1prot    |                                           | 100       |             | 200                       | mA                                    |

| Input resistance on PS1                  | rinps1      |                                           | 183       | 550         | 1650                      | kΩ                                    |

| Maximum output voltage on PS1            | vps1h       | VDD5=26V                                  | 13        |             | 23                        | V                                     |

| Maximum voltage drop on PS1 seen to VDD5 | vdiffps1    | 13V>VDD5>5V<br>PS1 loaded with<br>20mA    |           |             | 800                       | mV                                    |

|                                          |             | ZUIIIA                                    |           |             |                           |                                       |

| Digital input threshold   vipnomhps1   VDD5>7V   3.75   4   4.25   V   vipnomhps1   VDD5>7V   2.5   3   3.5   V   vipnomhps1   VDD5>7V   2.5   3   3.5   V   vipnomhps1   VDD5>7V   VD     | level H => L                                                 |                    |                                                  |       |       | 1    |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|--------------------------------------------------|-------|-------|------|---------|

| Public   Section   Process   Section   Process   Section   Section   Process   Section   Secti   |                                                              | vin n a na la na 4 | \/DDE. 7\/                                       | 0.75  | 4     | 4.05 | M       |

| TST related parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | level L => H                                                 | vipnomnps1         | VUU5>/V                                          | 3.75  | 4     | 4.25 |         |

| Pull down resistance on TST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Hysteresis                                                   | vhystnomps1        | VDD5>7V                                          | 2.5   | 3     | 3.5  | V       |

| TC[2:1] related parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              | Т                  | ST related parameter                             | ers   |       |      |         |

| Output voltage of TC[2:1]   vtc[2:1]   VDD5>7V   4.2   6   7   V   VDD5+10   VDD5+1    | Pull down resistance on TST                                  | rtst               |                                                  | 0.5   | 1     | 2.5  | kΩ<br>> |

| Pull up current of TC[2:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                              | TC                 | [2:1] related parame                             | eters |       |      |         |

| TC[2:1] conhected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Output voltage of TC[2:1]                                    | vtc[2:1]           | VDD5>7V                                          | 4.2   |       | 7    | V       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Pull up current of TC[2:1]                                   | itc[2:1]           | TC[2:1] connected                                | X.0   | 2.5   | 4.3  |         |

| Physteresis   Vhystriomtc[2:1]   VDD5>7V   2.5   3   3.5   V   V   V   V   V   V   V   V   V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Digital input threshold level H => L                         |                    | VDD5>7V                                          | 0.75  | 1     | 1.25 | V       |

| PWM related parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Digital input threshold level L => H                         | vipnomhtc[2:1]     |                                                  | 3.75  | 4     | 4.25 | V       |

| Leakage current in PWM   Iteakpwm   Iteak    | Hysteresis                                                   |                    |                                                  |       | 3     | 3.5  | V       |

| In case PWM is as input   Voltage on PWM in case of H   Voltage on PWM in case of H   Voltage on PWM in case of L   Voltage in case of    |                                                              |                    | WM related paramet                               | ers   |       |      |         |

| PWM loaded with 5mA   SmA      | Leakage current in PWM in case PWM is as input               | ileakpwm           |                                                  |       |       | 2    | μΑ      |

| PWM loaded with 5mA   SmA      | Voltage on PWM in case of H output                           | vhpwm              | PWM loaded with                                  | 4     | 5.0   | 6.5  | V       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Voltage on PWM in case of L output                           | vlpwm              | PWM loaded with                                  |       |       | 0.5  | V       |

| Nominal input threshold level H => L   Nominal input threshold level L => H   Nominal hysteresis   Vipodikey[7:0]   Vicodity   Vipodikey[7:0]   Vicodikey[7:0]   Vipodikey[7:0]   Vipodikey[7:    | Digital input threshold level H => L                         | vipnomlpwm         | VDD5>7V                                          | 0.75  | 1     | 1.25 | V       |

| Companies   Com    | Digital input threshold level L => H                         | vipnomhpwm         | VDD5>7V                                          | 3.75  | 4     | 4.25 | V       |

| Leakage current in case   KEY[7:0]   are inputs   Vhkey[6:0]   VDD5>7V,   EY[6:0] loaded with 1mA   Voltage in case of L output   Vlkey[7:0]   VDD5>7V,   KEY[6:0] loaded with 1mA   Voltage in case of L output   Vlkey[7:0]   VDD5>7V,   KEY[6:0] loaded with 1mA,   KEY7 loaded with 1mA,   KEY7 loaded with 20mA,   VDD5>7V   V    | Hysteresis                                                   | vhystnompwm        | VDD5>7V                                          | 2.5   | 3     | 3.5  | V       |

| KEY[7:0] are inputs         Voltage in case of Houtput         Vhkey[6:0]         VDD5>7V, KEY[6:0] loaded with 1mA         4         5.0         5.5         V           Voltage in case of Loutput         Vlkey[7:0]         VDD5>7V, KEY[6:0] loaded with 1mA, KEY7 loaded with 20mA, K                                                                                                                                   |                                                              | KEY                | [7:0] related param                              | eters |       |      |         |

| Nominal input threshold   vipnomlkey[7:0]   VDD5>7V   Several threshold level H => L   Nominal hysteresis   vhystnomkey[7:0]   VDD5>7V   2.5   3   3.5   V   Special threshold level H => L   vipndlkey[7:0]   V(AD1)   V   | Leakage current in case KEY[7:0] are inputs                  | ileakkey[7:0]      |                                                  |       |       | 2    | μΑ      |

| output $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Voltage in case of H output                                  | vhkey[6:0]         | KEY[6:0] loaded                                  | 4     | 5.0   | 5.5  | V       |

| Nominal input threshold vipnomhkey[7:0] VDD5>7V 3.75 4 4.25 V level L => H Vhystnomkey[7:0] VDD5>7V 2.5 3 3.5 V Special threshold level H => L in case of external pull down $V(AD1) = V(AD1) =$ | Voltage in case of L output                                  | vlkey[7:0]         | KEY[6:0] loaded<br>with 1mA,<br>KEY7 loaded with |       |       | 0.5  | V       |

| Nominal hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Nominal input threshold level H => L                         | vipnomlkey[7:0]    | VDD5>7V                                          | 0.75  | 1     | 1.25 | V       |

| Nominal hysteresis vhystnomkey[7:0 VDD5>7V 2.5 3 3.5 V  Special threshold level H => L in case of external pull down V(AD1) V(AD1) V(AD1) V(AD1) V(AD1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Nominal input threshold level L => H                         | vipnomhkey[7:0]    | VDD5>7V                                          | 3.75  | 4     | 4.25 | V       |

| H => L in case of external                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Nominal hysteresis                                           | vhystnomkey[7:0    | VDD5>7V                                          | 2.5   | 3     | 3.5  | V       |

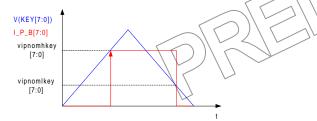

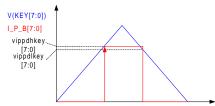

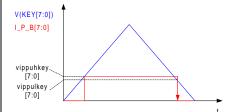

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Special threshold level H => L in case of external pull down | vippdlkey[7:0]     | V(AD1)<18V                                       |       |       |      | V       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Special threshold level                                      | vippdhkey[7:0]     | V(AD1)<18V                                       | 0.5*  | 0.66* | 0.8* | V       |

| L => H in case of external                |                 |                                         | V(AD1) | V(AD1) | V(AD1)  |            |

|-------------------------------------------|-----------------|-----------------------------------------|--------|--------|---------|------------|

| pull down                                 |                 |                                         | V(AD1) | V(ADT) | V(ADI)  |            |

| Special hysteresis in case                | vhystsppdkey[7: | V(AD1)<18V                              | 0.01*  | 0.03*  | 0.06*   | W)         |

| of                                        | 0]              | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | V(AD1) | V(AD1) | V(AD1)  |            |

| external pull down                        | -1              |                                         | (,     | . ( ,  |         | 1          |

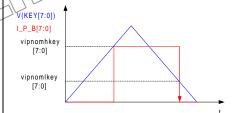

| Special threshold level                   | vippulkey[7:0]  | V(AD1)<18V                              | 0.2*   | 0.37*  | 0.5*    | <b>V</b> \ |

| H => L in case of external                | '' ''           |                                         | V(AD1) | V(AD1) | V(AD1)  |            |

| pull up                                   |                 |                                         |        |        |         |            |

| Special threshold level                   | vippuhkey[7:0]  | V(AD1)<18V                              | 0.2*   | 0.4*   | 0.5*    | V          |

| L => H in case of external                |                 |                                         | ((AD1) | V(AD1) | V(AD1)  |            |

| pull up                                   |                 |                                         |        | ~      |         |            |

| Special hysteresis in case                | vhystsppukey[7: | V(AD1)<18V\\\                           | 0.01*  | 0.03*  | 0.06*   | V          |

| of                                        | [0]             | <i>-</i> /// /////                      | V(AD1) | V(AD1) | V(AD1)  |            |

| external pull up                          |                 |                                         |        |        |         |            |

| 71/ 144                                   |                 | interrupt related pa                    |        | I      | 7.075   | 1 \ /      |

| 7V-interrupt level 1                      | 7vint1          |                                         | 5.0    |        | 7.275   | V          |

| 7V-interrupt level 2                      | 7vint2          |                                         | 4.9    |        | 7.15    | V          |

| 7V-interrupt level 3                      | 7vint3          |                                         | 4.8    |        | 7.025   | V          |

| 7V-interrupt level 4                      | 7vint4          |                                         | 4.7    |        | 6.9     | V          |

| 7V-interrupt level 5                      | 7vint5          |                                         | 4.6    |        | 6.775   | V          |

| 7V-interrupt level 6                      | 7vint6          |                                         | 4.5    |        | 6.65    | V          |

| 7V-interrupt level 7                      | 7vint7          |                                         | 4.4    |        | 6.625   | V          |

| 7V-interrupt level 8                      | 7vint8          |                                         | 4.3    |        | 6.4     | V          |

| Hysteresis level for 7V-                  | v7vhyst         |                                         | 7.3V   |        | 7.9V    | V          |

| interrupt                                 | _               |                                         |        |        |         |            |

|                                           |                 | RESET related parar                     |        |        |         | 1 > 7      |

| Power on reset level (CBB)                | vpor            |                                         | 1.5    | 2.0    | 3       | V          |

| 3V-reset level (WBB),                     | v3vupreset      |                                         | 3.0    | 3.5    | 4.2     | V          |

| if VDD5 is ramped up                      |                 |                                         |        |        |         |            |

| Hysteresis on 3V-reset                    | v3vhyst         |                                         | 0.2    | 0.5    | 1.2     | V          |

|                                           |                 | ump-interrupt relate                    |        | eters  |         |            |

| Level for load dump interrupt             | vldi            |                                         | 27     |        | 40      | V          |

|                                           |                 | PR[2:1] related para                    | meters |        |         |            |

| Input leakage of PR[2:1] in case of sleep | ileakpr[2:1]    |                                         |        |        | 2       | μΑ         |

| On resistance of PR[2:1]                  | rdson[2:1]      | VDD5>7V                                 |        |        | 8       | Ω          |

|                                           |                 |                                         |        |        | 13(tmax | Ω          |

|                                           |                 |                                         |        |        | )       |            |

| Free wheel diode voltage                  | vwheel[2:1]     |                                         | 24     |        | 31      | V          |