### **Features and Benefits**

- □ 3DLF interface for low power wake-up

- Backup mode for battery less operations

- □ RSSI information for LF and RF interfaces

- LF/ RF intelligent self-polling modes for low power operations

- Multi-band frequency coverage from 300MHz up to 960MHz

- Modulation schemes supported: (G)FSK, (G)MSK, OOK

- Transmitter power of -20 to 13dBm, 64 steps

- Receiver sensitivity of -120dBm (FSK, 433MHz, 15kHz CHBW)

- □ Supply voltage range of 2.1 to 3.6V

- PLL synthesizer with 60Hz resolution

- □ Channel filter bandwidth of 9 to 600kHz

- Data rate of 0.3 to 250kbps (GFSK)

- Frequency deviation up to 125kHz

- □ 32MHz crystal frequency

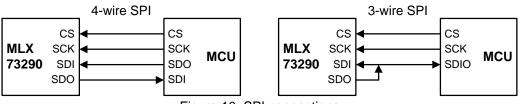

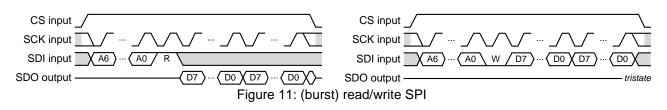

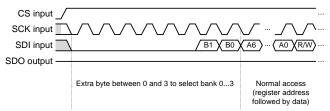

- SPI interface with embedded FIFO, 256bytes for RF and 8bytes for LF interfaces 4 programmable GPIO ports

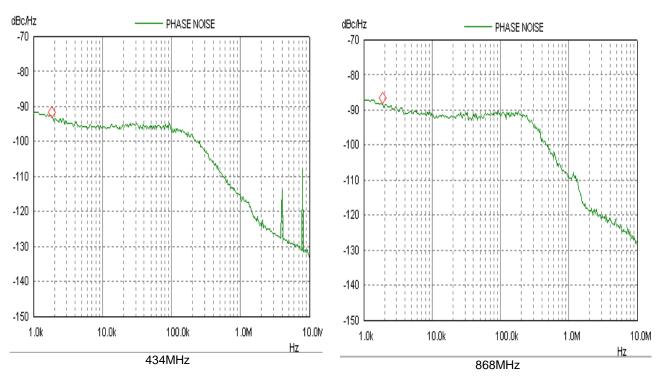

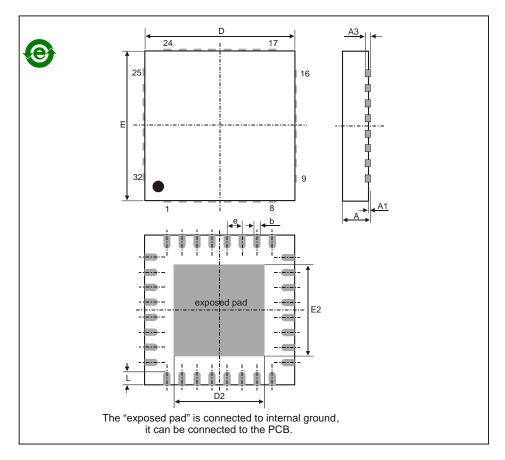

- 32L QFN5x5 package

- □ Conform to EN 300 220, DASH7, FCC part 15, Japan ARIB STD-T67, Korean and other standards

### **Application Examples**

- Low-power tracking systems

- Secure access systems

- Passive Keyless Entry / Start (PKES)

### **Ordering Code**

| Product           | <b>Temperature</b> | <b>Package</b>    | <b>Option</b> | <b>Packaging Form</b>   |

|-------------------|--------------------|-------------------|---------------|-------------------------|

| MLX73290          | R                  | LQ                | ABA-000       | RE or TU                |

| Legend: R for -40 | )°C to 105°C       | LQ for 32L QFN5x5 |               | RE for reel (5000 pcs.) |

### Introduction

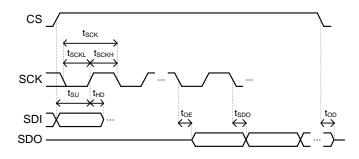

The MLX73290-A combines a highly integrated Radio Frequency transceiver for long range, high speed communication and a 3 dimensional low frequency interface (3DLF) for low power wake-up. This unique combination makes the MLX73290-A suitable for applications requiring a very low power wake-up function together with long range, high speed RF feedback.

The transceiver part allows for multi-channel operation including frequency hopping in the European bands (433MHz and 868MHz) as well as in North America or Asia bands (315MHz or 915MHz). The output power, frequency channel, modulation type and frequency deviation are programmable. Thanks to the high frequency resolution and phase noise performance of its fractional-N PLL, the MLX73290-A is fit for narrow-band operation. There are two selectable modulation schemes: binary on-off keying (OOK) and binary frequency shift keying (FSK) as well as their Gaussian filtered versions. The low-IF receiver part comprises fully digital demodulation and self-polling features together with channel scanning and built-in packet recognition.

The 3DLF interface features an automatic and programmable wake-up algorithm together with an integrated data decoder to receive the payload. Monitoring independently the RSSI information from the 3-axis LF frontends allows precise monitoring of the received LF field. Thanks to its internal rectifier, power management and load modulator, the MLX73290-A is capable of battery-less LF RFID tag operation.

# **MLX73290-A** 300 to 960MHz Multi-channel Transceiver

With 3DLF Low Power Interface

| 1 Glossary of Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                          |

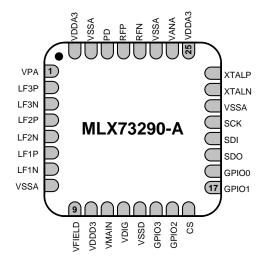

| 3 Pin Definitions and Pin-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |

| 4 Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5                                                                                                                                                                                                        |

| 4.1 Normal operating conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                          |

| 4.2 General Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

| 4.3 RF Characteristics<br>4.4 LF Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

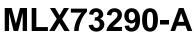

| 4.5 SPI Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                          |

| 5 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| 5.1 Frequencies and standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |

| 5.2 Block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                                                                                                                                       |

| 5.3 Detailed description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| 5.4 3DLF interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                                                                                       |

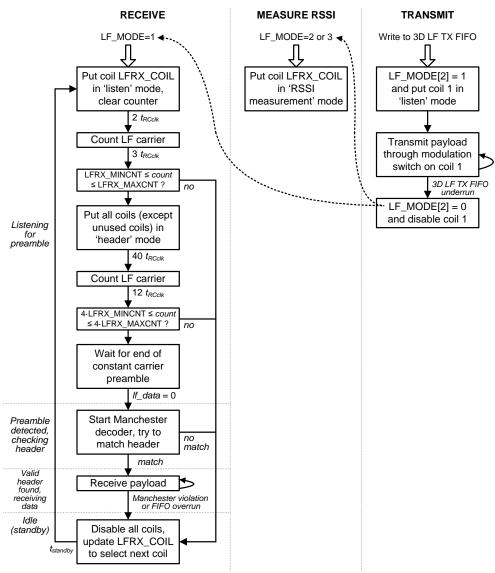

| 5.4.1 Reception mode (self-polling mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| 5.4.2 Data format<br>5.4.3 Preamble definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 5.4.4 Header definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                          |

| 5.4.5 Min/Max Threshold definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          |

| 5.4.6 RSSI Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                          |

| 5.4.7 Transmission Mode (TX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                          |

| 5.4.8 LF Backup Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                          |

| 5.4.9 LF FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |

| 5.5 RF Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                          |

| 5.5.1 Frequency synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |

| 5.5.2 Transmit mode (TX)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

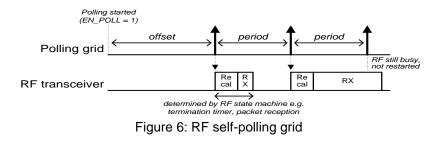

| 5.5.3.1 Automatic Polling Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                          |

| 5.5.3.2 RSSI Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| 5.5.4 State Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                          |

| 5.6 Modulation Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                          |

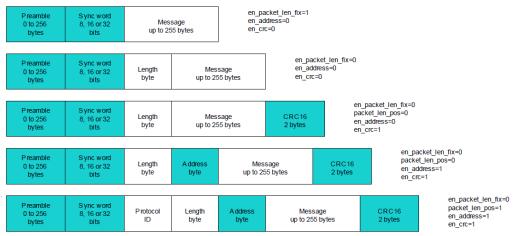

| 5.7 Packet Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                                                                                       |

| 5.7.1.1 Preamble                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                          |

| E 7 1 0 Suna Mard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                                                                                                                                                                                                       |

| 5.7.1.2 Sync Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                          |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21                                                                                                                                                                                                       |

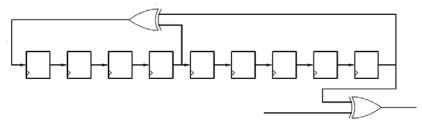

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21<br>21                                                                                                                                                                                                 |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21<br>21<br>22                                                                                                                                                                                           |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 21<br>21<br>22<br>22                                                                                                                                                                                     |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16<br>5.7.1.7 Multi-frame<br>5.7.1.8 Data whitening                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21<br>21<br>22<br>22<br>22<br>22<br>                                                                                                                                                                     |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16<br>5.7.1.7 Multi-frame<br>5.7.1.8 Data whitening<br>5.8 Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21<br>21<br>22<br>22<br>22<br>22<br>                                                                                                                                                                     |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16<br>5.7.1.7 Multi-frame<br>5.7.1.8 Data whitening<br>5.8 Power Management Unit<br>5.9 Programmable Timer / Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>23                                                                                                                                                       |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16<br>5.7.1.7 Multi-frame<br>5.7.1.8 Data whitening<br>5.8 Power Management Unit<br>5.9 Programmable Timer / Clock Generator<br>5.10 System timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>23                                                                                                                                                       |

| 5.7.1.3 Packet Length<br>5.7.1.4 Manchester Encoder/Decoder<br>5.7.1.5 Address<br>5.7.1.6 CRC16<br>5.7.1.7 Multi-frame<br>5.7.1.8 Data whitening<br>5.8 Power Management Unit<br>5.9 Programmable Timer / Clock Generator<br>5.10 System timer<br>5.11 General Purpose ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>24                                                                                                                                                 |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24                                                                                                                                           |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>24<br>24                                                                                                                               |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>26<br>29                                                                                                                         |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>24<br>24<br>24<br>24<br>26<br>29<br>29<br>29                                                                                                       |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                          |

| <ul> <li>5.7.1.3 Packet Length</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| <ul> <li>5.7.1.3 Packet Length</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>26<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                                           |

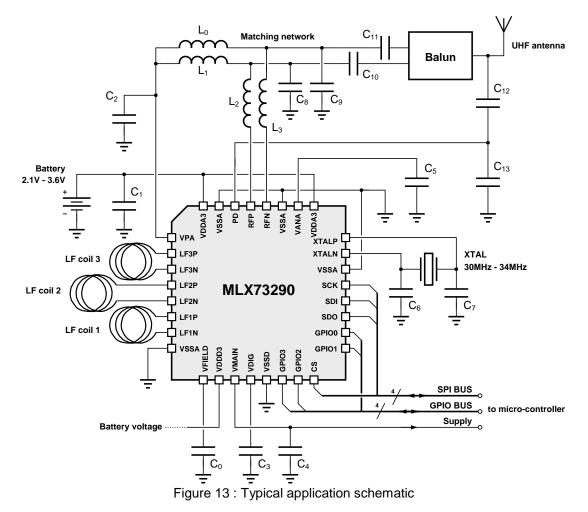

| <ul> <li>5.7.1.3 Packet Length.</li> <li>5.7.1.4 Manchester Encoder/Decoder</li> <li>5.7.1.5 Address</li> <li>5.7.1.5 Address</li> <li>5.7.1.6 CRC16.</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.8 Data whitening.</li> <li>5.8 Power Management Unit</li> <li>5.9 Programmable Timer / Clock Generator</li> <li>5.10 System timer</li> <li>5.11 General Purpose ADC</li> <li>5.12 SPI communication</li> <li>5.13 GPIO Pins</li> <li>6 Register settings</li> <li>6.1 RF Transceiver (0x02 to 0x33)</li> <li>6.2 Status Byte &amp; GPIOS (0x34 to 0x3B)</li> <li>6.3 General purpose ADC (0x3C to 0x3F)</li> <li>6.4 Timers (0x40 to 0x4F)</li> <li>6.5 3DLF Transceiver (0x50 to 0x5F)</li> <li>6.6 Chip ID and soft Reset (register 0x7F)</li> <li>6.7 Bank 0.</li> <li>7 Application Information</li> <li>7.1 Typical application schematic</li> </ul>                                                                                                                                                                                                                                                                          | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>26<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                                                 |

| <ul> <li>5.7.1.3 Packet Length</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

| <ul> <li>5.7.1.3 Packet Length.</li> <li>5.7.1.4 Manchester Encoder/Decoder</li> <li>5.7.1.5 Address</li> <li>5.7.1.5 Address</li> <li>5.7.1.6 CRC16.</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.8 Data whitening.</li> <li>5.8 Power Management Unit</li> <li>5.9 Programmable Timer / Clock Generator</li> <li>5.10 System timer</li> <li>5.11 General Purpose ADC</li> <li>5.12 SPI communication</li> <li>5.13 GPIO Pins</li> <li>6 Register settings</li> <li>6.1 RF Transceiver (0x02 to 0x33)</li> <li>6.2 Status Byte &amp; GPIOS (0x34 to 0x3B)</li> <li>6.3 General purpose ADC (0x3C to 0x3F)</li> <li>6.4 Timers (0x40 to 0x4F)</li> <li>6.5 3DLF Transceiver (0x50 to 0x5F)</li> <li>6.6 Chip ID and soft Reset (register 0x7F)</li> <li>6.7 Bank 0.</li> <li>7 Application Information</li> <li>7.1 Typical application schematic</li> </ul>                                                                                                                                                                                                                                                                          | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>42<br>29<br>29<br>42<br>54<br>44<br>56<br>56<br>56<br>56<br>57       |

| <ul> <li>5.7.1.3 Packet Length</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                          |

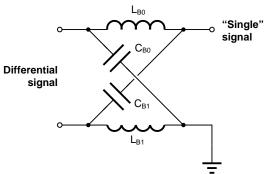

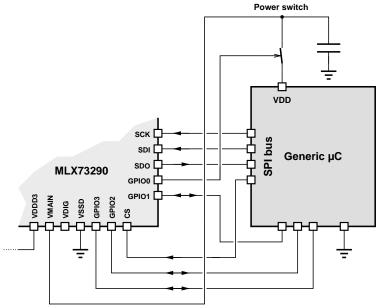

| <ul> <li>5.7.1.3 Packet Length.</li> <li>5.7.1.4 Manchester Encoder/Decoder</li> <li>5.7.1.5 Address</li> <li>5.7.1.6 CRC16</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.8 Data whitening.</li> <li>5.8 Power Management Unit</li> <li>5.9 Programmable Timer / Clock Generator</li> <li>5.10 System timer</li> <li>5.11 General Purpose ADC</li> <li>5.12 SPI communication</li> <li>5.13 GPIO Pins</li> <li>6 Register settings</li> <li>6.1 RF Transceiver (0x02 to 0x33)</li> <li>6.2 Status Byte &amp; GPIOs (0x34 to 0x3B)</li> <li>6.3 General purpose ADC (0x3C to 0x3F)</li> <li>6.4 Timers (0x40 to 0x4F)</li> <li>6.5 3DLF Transceiver (0x50 to 0x5F)</li> <li>6.6 Chip ID and soft Reset (register 0x7F)</li> <li>6.7 Bank 0.</li> <li>7 Application Information</li> <li>7.1.1 TX/RX Combining Network</li> <li>7.1.2 Balun</li> <li>7.1.3 External power switch usage.</li> </ul>                                                                                                                                                                                                          | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>26<br>29<br>29<br>29<br>29<br>42<br>29<br>29<br>42<br>29<br>42<br>29<br>53<br>54<br>56<br>56<br>56<br>57<br>57<br>57             |

| 5.7.1.3 Packet Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>24<br>26<br>29<br>29<br>29<br>42<br>29<br>42<br>29<br>42<br>29<br>42<br>29<br>54<br>56<br>56<br>56<br>57<br>57<br>57<br>58<br>58 |

| 5.7.1.3 Packet Length         5.7.1.4 Manchester Encoder/Decoder         5.7.1.5 Address.         5.7.1.6 CRC16         5.7.1.7 Multi-frame         5.7.1.8 Data whitening.         5.8 Power Management Unit.         5.9 Programmable Timer / Clock Generator         5.10 System timer         5.11 General Purpose ADC         5.12 SPI communication         5.13 CPIO Pins         6 Register settings.         6.1 RF Transceiver (0x02 to 0x33)         6.2 Status Byte & GPIOS (0x34 to 0x3B).         6.3 General purpose ADC (0x32 to 0x3F).         6.4 Timers (0x40 to 0x4F).         6.5 3DLF Transceiver (0x50 to 0x5F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21<br>22<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                               |

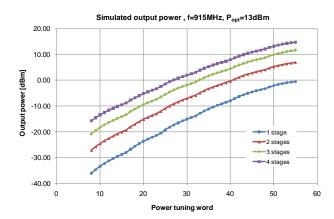

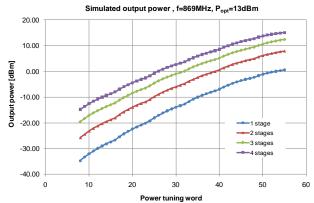

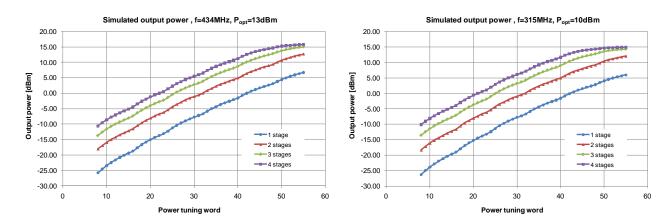

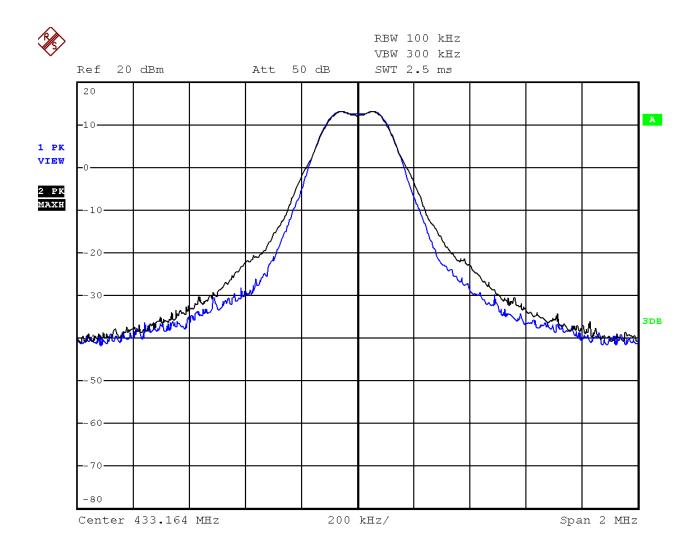

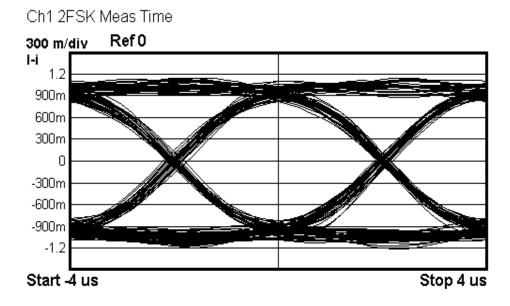

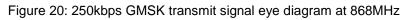

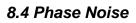

| <ul> <li>5.7.1.3 Packet Length.</li> <li>5.7.1.4 Manchester Encoder/Decoder</li> <li>5.7.1.5 Address.</li> <li>5.7.1.6 CRC16.</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.8 Data whitening.</li> <li>5.8 Power Management Unit.</li> <li>5.9 Programmable Timer / Clock Generator</li> <li>5.10 System timer</li> <li>5.11 General Purpose ADC.</li> <li>5.12 SPI communication</li> <li>5.13 GPIO Pins.</li> <li>6.1 RF Transceiver (0x02 to 0x33)</li> <li>6.2 Status Byte &amp; GPIOs (0x34 to 0x3B)</li> <li>6.3 General purpose ADC (0x3C to 0x3F).</li> <li>6.4 Timers (0x40 to 0x4F)</li> <li>6.5 3DLF Transceiver (0x50 to 0x5F)</li> <li>6.6 Chip ID and soft Reset (register 0x7F).</li> <li>6.7 Bank 0.</li> <li>7 Application Information</li> <li>7.1.1 TX/RX Combining Network</li> <li>7.1.2 Balun</li> <li>7.1.3 External power switch usage.</li> <li>8 Performance Plots</li> <li>8.1 Simulated output power</li> <li>8.2 Spectrum Plots</li> <li>8.3 Eye Diagram.</li> <li>8.4 Phase Noise.</li> </ul>                                                                                                            | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>26<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                               |

| <ul> <li>5.7.1.3 Packet Length.</li> <li>5.7.1.4 Manchester Encoder/Decoder</li> <li>5.7.1.5 Address</li> <li>5.7.1.6 CRC16.</li> <li>5.7.1.7 Multi-frame</li> <li>5.7.1.8 Data whitening.</li> <li>5.8 Power Management Unit.</li> <li>5.9 Programmable Timer / Clock Generator</li> <li>5.10 System timer</li> <li>5.11 General Purpose ADC.</li> <li>5.12 SPI communication</li> <li>5.13 GPIO Pins</li> <li>6 Register settings.</li> <li>6.1 RF Transceiver (0x02 to 0x33)</li> <li>6.2 Status Byte &amp; GPIOS (0x34 to 0x3B).</li> <li>6.3 General purpose ADC (0x3C to 0x3F).</li> <li>6.4 Timers (0x40 to 0x4F).</li> <li>6.5 3DLF Transceiver (0x50 to 0x5F)</li> <li>6.6 Chip ID and soft Reset (register 0x7F).</li> <li>6.7 ABank O.</li> <li>7.1 Typical application schematic.</li> <li>7.1.1 TX/RX Combining Network</li> <li>7.1.3 External power switch usage.</li> <li>8 Performance Plots</li> <li>8.1 Simulated output power.</li> <li>8.2 Spectrum Plots.</li> <li>8.3 Eye Diagram</li> <li>8.4 Phase Noise.</li> <li>9 Manufacturability of Melexis Products with Different Soldering Processes.</li> </ul>   | 21<br>22<br>22<br>22<br>22<br>23<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>24<br>24<br>24<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29<br>29                               |