### Features and Benefits

Dual low noise, low offset, fully programmable amplifier chain 12 bit on-chip ADC

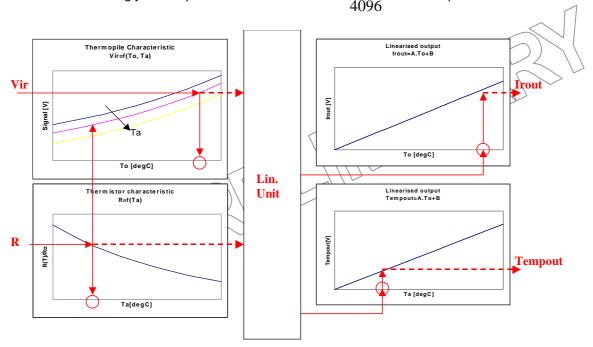

Powerful signal conditioning and linearisation unit

Multiple output options: 12 bit digital through SPI, 8 bit resolution analog linear signal outputs or 10 bit PWM, both for ambient and object temperature.

On-chip programmable digital moving average LPF for ultimate low holse performance ISP I/O-configuration and analog settings, accessible by SPI serial interface. Wide supply voltage range from 4.5V-80V

# **Applications**

Thermopile + thermistor amplification chain

Digital or analog, linear, ambient-compensated IR sensor interface General purpose programmable sensor amplifier/ signal conditioner

# Ordering Information

| Part No. | Temperature Suffix | Package | Temperature Range       |

|----------|--------------------|---------|-------------------------|

| MLX90313 | K                  | DF      | -40C to 125C Automotive |

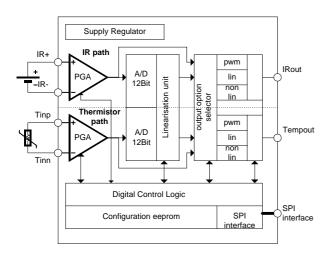

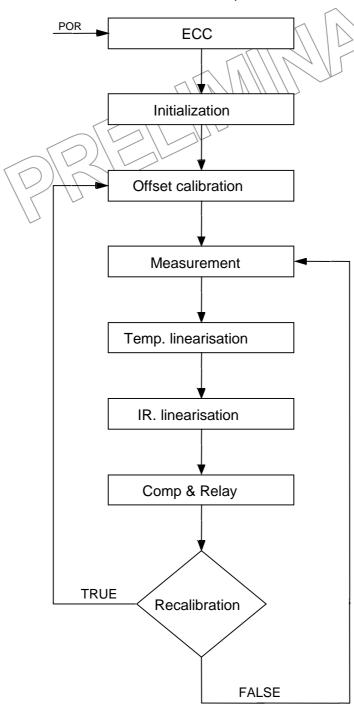

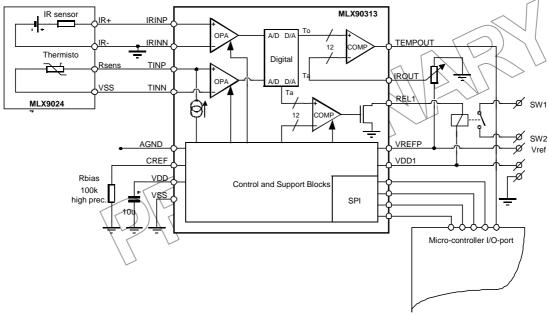

### **Functional Diagram**

### **Description**

The MLX90313 is a versatile in-circuit programmable interface, which performs signal conditioning, linearisation and ambient temperature compensation, particularly for infrared sensors combined with a thermistor. Other types of sensors can also be used in various configurations. Sensors that can be used include pressure sensors, strain gauges, acceleration sensors etc.

The amplifier chains in MLX90313 are programmable in very broad ranges of gain. Both chains consist of high performance, chopper-stabilized amplifiers, providing excellent noise performance and low offset. The I/O configuration as well as analog settings are incircuit programmable by means of the SPI-serial interface. This serial link can also be used to read out the output signals digitally. The circuit can either provide linear analog or PWM (Pulse Width Modulated) signal outputs. Additional the circuit can perform simple control applications using on-board comparators

## **MLX90313 Electrical Specifications**

| DC Operating Parameters $T_A$ Parameter     | Symbol | Test Conditions       | Min  | Тур      | Max         | Unit                                   |

|---------------------------------------------|--------|-----------------------|------|----------|-------------|----------------------------------------|

| Regulator and consumption                   |        |                       |      |          |             |                                        |

| Supply voltage range                        | Vin1   | VDD1                  | 7    | _        | 80 \        | A <                                    |

| Supply voltage range                        | Vin    | VDD                   | 4.5  | 5        | 5.5         | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| Supply current                              | ldd    | @ Ta=25°C             |      | 2//      | 5.6         | mA                                     |

| Regulated supply voltage                    | Vreg   | VDD, 10uF ext, cap    | 4.7  | 5        | 5.3         | ٧                                      |

| Regulated voltage temperature coefficient   | TCvr   |                       | N/V  | -2.35    |             | mV/°                                   |

| POR threshold voltage                       | Vpor   |                       | 1.1  | 1.3      | 1.5         | V                                      |

| Band-gap reference                          | 101    |                       |      |          |             |                                        |

| Analog ground voltage \                     | Agnd   | 7                     | 2.3  | 2.5      | 2.7         | V                                      |

| Analog ground thermal coefficient           | TCbg   |                       |      | 15       | 50          | μV/°                                   |

| Reference current mirror load drive voltage | Vcref  |                       | 1.8  | 2        | 2.2         | V                                      |

| IR-chain amplifier and output driv          | er     |                       |      |          |             |                                        |

| Common mode input range                     | CMIR   |                       | -0.1 |          | Vdd-3       | V                                      |

| Common mode rejection ratio                 | CMRR   | f ≤ 100kHz            | 75   |          |             | dB                                     |

|                                             |        | Rsens < $60k\Omega$ * |      |          |             |                                        |

| Power supply rejection ratio                | PSSR   | f ≤ 100kHz            | 75   |          |             | dB                                     |

| Available gain settings                     | Air    |                       | 55   |          | 5500        | V/V                                    |

| Gain tolerance                              | δGir   |                       | -6.5 |          | +6.5        | %                                      |

| Amplifier offset                            | Voff   |                       |      |          | 4           | μV                                     |

| Input referred white noise                  | Vnir   | rms-value             |      |          | 25          | nV/√Hz                                 |

| Chopper frequency                           | fc     |                       |      | 8        |             | KHz                                    |

| Output voltage range                        |        | IROUT                 | 0    |          | Vdd-<br>0.2 | V                                      |

| Output source current                       | lod    | IROUT                 | 1    |          |             | mA                                     |

| Output sink current                         | los    | IROUT                 | 20   |          |             | μΑ                                     |

| DC Output impedance, drive                  | rod    | IROUT                 |      |          | 10          | Ω                                      |

| DC Output impedance, sink                   | ros    | IROUT                 |      |          | 100         | Ω                                      |

| Capacitive load IROUT pin                   | Cmax   | IROUT                 |      |          | 50          | pF                                     |

| Amplifier bandwidth                         | BW     |                       |      | 500      |             | Hz                                     |

| Temp-chain amplifier and output             | driver |                       |      | <u> </u> | <u> </u>    | <u> </u>                               |

| Common mode input range                     | CMIR   |                       | 0.1  |          | Vdd-        | V                                      |

| ataSheet4LL.com                             |        |                       |      |          | 3V          |                                        |

| Common mode rejection ratio                 | CMRR   | f ≤ 100kHz            | 75   |          |             | dB                                     |

| Power supply rejection ratio                | PSSR   | f ≤ 100kHz            | 75   |          |             | dB                                     |

| TINP bias current                           | Itpb   | bias current enabled  | 1/7  |          | .1          | iCref*                                 |

| Available gain settings                     | Atemp  |                       | 1    |          | 40          | V/V                                    |

|                                             |        |                       |      |          |             | 1                                      |

# Programmable IR Sensor Interface

| Parameter                    | Symbol  | <b>Test Conditions</b> | Min      | Тур       | Max         | Unit          |

|------------------------------|---------|------------------------|----------|-----------|-------------|---------------|

| Gain tolerance               | δGtemp  | bias current enabled   | -6.5     |           | +6.5        | %             |

| Amplifier offset             | Voff    |                        |          |           | 4           | μV            |

| Input referred white noise   | Vntemp  | rms-value              |          |           | 400         | nV/√Hz        |

| Chopper frequency            | fc      |                        |          | 8         | ^ \         | kHz           |

| Output voltage range         | ORtemp  | TEMPOUT                | 0        |           | Vdd-<br>0.2 | N             |

| Output source current        | lod     | TEMPOUT                | 1\\\\\   | 1/4/      |             | mA            |

| Output sink current          | los     | TEMPOUT ///            | 20 \\ \  |           |             | uA            |

| DC Output impedance, drive   | rod     | TEMPOUT \\\            | 177      | 3         | 10          | Ω             |

| DC Output impedance, sink    | ros     | TEMPOUT                |          |           | 100         | Ω             |

| Capacitive load TEMPOUT pin  | Cmax    | TEMPOUT                |          |           | 50          | pF            |

| Amplifier bandwidth          | BW      |                        |          | 500       |             | Hz            |

| Rel1 open drain relay driver |         |                        |          |           |             |               |

| High voltage protection      | 7       |                        | 32       |           |             | V             |

| output impedance             | Ro      |                        |          | 10        |             | Ω             |

| Comp1 comparator             |         |                        |          |           |             |               |

| Potentiometer input range    | IRirout | IROUT                  | 0        |           | 100         | % of<br>Vrefp |

| ADC                          |         |                        |          |           |             |               |

| Input stage gain             |         |                        | 2.95     | 3         | 3.05        | V/V           |

| External Reference voltage   | Vrefpex |                        | 1        |           | 3.3         | V             |

| Internal Reference voltage   | Vrefp   |                        | 2.4      | 2.5       | 2.6         | V             |

| Vrefp input leakage current  | llvrefp | @150°C                 |          |           | 5           | uA            |

| Resolution                   |         |                        |          | 12        |             | bit           |

| Monotonicity                 |         |                        | guarante | eed by de | sign        |               |

| Differential non-linearity   | DNL     |                        |          |           | 0.4         | LSB           |

| Integral non-linearity       | INL     |                        |          |           | 1/2         | LSB           |

| Gain error                   |         | full scale             |          |           | 1           | LSB           |

| Total input-referred noise   |         | Vref=3V                |          |           | 0.2         | LSB           |

| DAC                          |         |                        |          |           |             |               |

| Resolution                   |         |                        |          | 8         |             | bit           |

| Monotonicity                 |         |                        | guarante | eed by de | sign        |               |

| Differential non-linearity   | DNL     |                        |          |           | 1/2         | LSB           |

| Integral non-linearity       | INL     |                        |          |           | 1/2         | LSB           |

<sup>\*</sup>Rsens is the impedance of the sensor connected between IRINP and IRINN for the IR-chain amplifier.

www.DataSheet4U.com

\*\*Icref is the current flowing out of pin CREF

### **General Description**

The MLX90313 is a versatile in-circuit programmable interface, which performs signal conditioning, linearisation and ambient temperature compensation, particularly for infrared sensors combined with a thermistor. Other types of sensors can also be used in various configurations. Sensors that can be used include pressure sensors, strain gauges, acceleration sensors etc.

The amplifier chains in MLX90313 are programmable in very broad ranges of gain, between 50 and 12000 for the IR-chain and between 1 and 120 for the Temp-chain. Both chains consist of high performance, chopper-stabilized amplifiers, providing excellent noise performance and low offset. The I/O configuration as well as analog settings are in-circuit programmable by means of the SPI-serial interface. This serial link can also be used to read out the output signals digitally. The circuit can either provide linear analog or PWM (Pulse Width Modulated) signal outputs, relative to an analog ground, or several combinations of analog and digital comparator driven outputs. Two comparators controlled by either one of the two linearised signals are available on chip with different possibilities for the threshold level, polarity and switching hysteresis. One of the comparators drives the open drain output. The user can provide the threshold for this comparator at the IROUT I/O pin with a simple potentiometer.

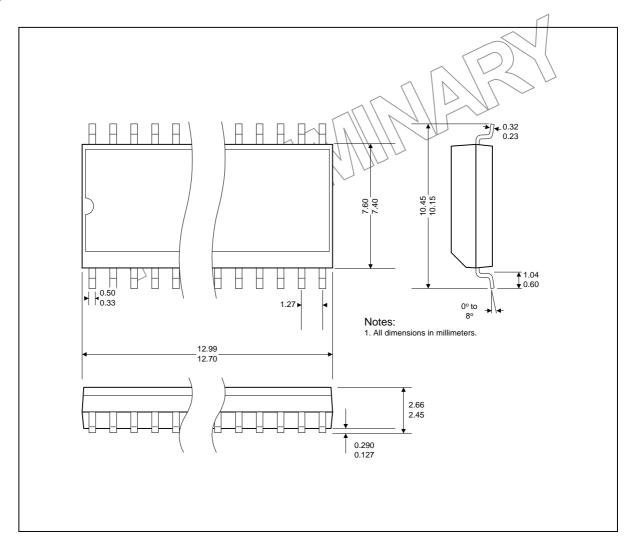

A bias current for the thermistor can be obtained at the TINP input by connecting an external resistor between the CREF pin and VSS. The standard package is SOIC-20.

### **Unique Features**

The MLX90313 integrates dual low noise programmable gain amplifier stages. Both thermistor and IR signal path can be configured to suit a large number of components and applications. The onboard analog to digital converter (ADC) combined with the digital linearisation unit results in linear output signals. These output signals are available as analog or digital output signal. Applications requiring digital temperature information can use single wire PWM output or SPI serial communication. The complete configuration and calibration is in-system programmable through the SPI interface. Combination of all these integrated features combined with a thermopile sensor make the MLX90313 a true high accuracy automotive grade single-chip infrared thermometer.

### Absolute Maximum Ratings

| Supply Voltage, V <sub>in1</sub> (overvoltage) | 80V           |

|------------------------------------------------|---------------|

| Supply Voltage, V <sub>in</sub> (overvoltage)  | 6V            |

| Supply Voltage, V <sub>in1</sub> (operating)   | 16V           |

| Supply Voltage, V <sub>in</sub> (operating)    | 5.5V          |

| Reverse Voltage Protection                     | -5V           |

| Supply Current, IDD                            | 5.6 mA        |

| Output Current, IouT                           | 3 mA          |

| Operating Temperature Range, T <sub>A</sub>    | -40C to +125C |

| Operating Temperature Range, Ts                | -55C to +150C |

| ESD Susceptibility                             | 2 kV          |

| Rel1 output impedance                          | 10 ohms       |

### Pin-out

| TINP  | (1         | 20 TEMPOUT  |

|-------|------------|-------------|

| TINN  | ₫ 2        | 19 CSB      |

| IRINP | ₫ 3        | 18 SDOUT    |

| IRINN | 4          | 17 SCLK     |

| VSS   | <b>4</b> 5 | 16 TSTCLK   |

| REL1  | ₫ 6        | 15 VPR      |

| IROUT | ₫ 7        | 14 VDD1     |

| SDIN  | ₫ 8        | 13 DAGNO\\\ |

| TOUT1 | <b>4</b> 9 | 12 VREFP    |

| TOUT2 | <b>1</b> 0 | 11 CREE     |

|       | 11/        | $\square$   |

| Pin | Symbol  | Description                               |

|-----|---------|-------------------------------------------|

| 1   | TINP    | Temp-chain amplifier positive input       |

| 2   | TINN    | Temp-chain amplifier negative input       |

| 3   | IRINP   | IR-chain amplifier positive input         |

| 4   | IRINN   | IR-chain amplifier negative input         |

| 5   | VSS     | Supply pin                                |

| 6   | REL1    | Open-drain relay driver output            |

| 7   | IROUT   | IR-chain amplifier output                 |

| 8   | SDIN    | SPI data input                            |

| 9   | TOUT1   | Test pin/ Oscillator output               |

| 10  | TOUT2   | Test pin, leave open                      |

| 11  | CREF    | Bias current reference                    |

| 12  | VREFP   | Reference voltage input/output            |

| 13  | AGND    | Analog ground, band-gap reference voltage |

| 14  | VDD1    | Automotive Ignition supply pin            |

| 15  | VDD     | Regulated supply pin                      |

| 16  | TSTCLK  | Clock for test mode; leave open           |

| 17  | SCLK    | SPI clock input                           |

| 18  | SDOUT   | SPI data output                           |

| 19  | CSB     | SPI chip select active low                |

| 20  | TEMPOUT | Temp-chain amplifier output               |

### **Pin Descriptions**

#### **TINP**

Temperature sensor positive input pin. The pin connects to the temp-chain amplifier and the on-chip biasing current source. The source is a mirrored version of the current running into CREF with programmable ratio. The current source can be switched off for use of external current biasing.

#### TINN

Temperature sensor negative input.

#### IRINP - IRINN

Thermopile sensor input pins

VSS: Supply pin

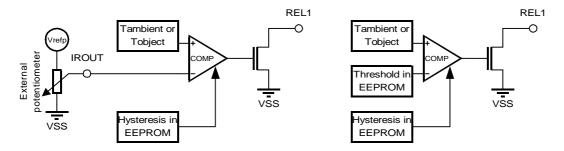

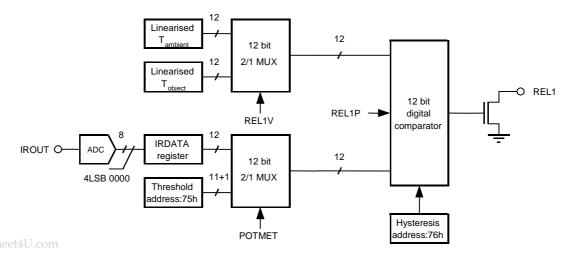

#### REL1

Open drain relay driver output. The typical on-resistance of this driver is  $<10\Omega$  with a supply voltage of VDD=5V. Different configurations are possible as shown below.

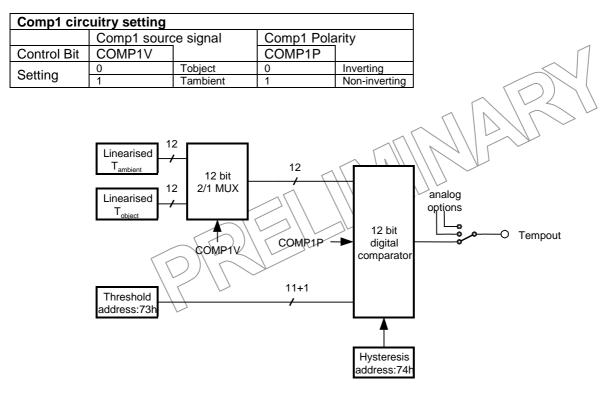

The comparator is a 12 bit digital comparator. The input polarity can be inverted or not. The threshold and hysteresis registers are 16 bit registers of which the 11 MSBs are used in the comparator circuitry. The voltage on the IROUT pin is sampled with 8 bit ADC referred between VREFP and VSS pins. Note. In case of potentiometer use the linearised analog output is not available. In this case the DAC is used as 8-Bit ADC for potentiometer (or other voltage source) monitoring.

### **IROUT**

IROUT/POTin analog/digital I/O pin. This pin can be configured as analog output of the IR sensor or as input for an external potentiometer. (see pin description of REL1). As analog output, this pin can either be connected to the analog amplified IR sensor signal or to the linearised object temperature by means of the DAC. The driver can source at least 1mA and sink at least 20µA to/from an external load. If the capacitive load on this pin exceeds 50pF, this load should be de-coupled by means of a series resistor. This pin can be configured also as digital output to transmit the IR temperature in PWM format.

The pin is protected for over-voltage and can withstand 16V.

#### **SDIN**

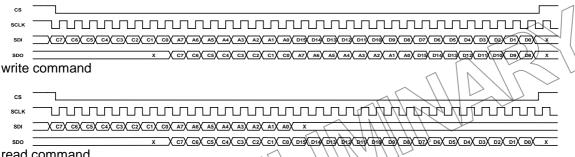

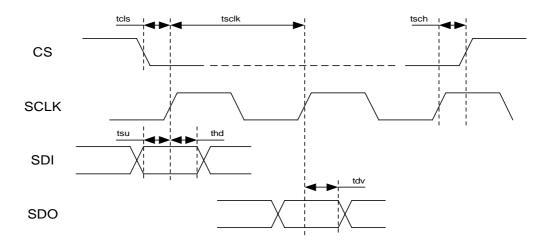

Serial data input pin for the SPI. Data is accepted on the rising edge of the serial data clock (SCLK)

#### **SDOUT**

### Programmable IR Sensor Interface

Serial data output pin for the SPI. Data is valid on the rising edge of the serial data clock (SCLK)

#### **SCLK**

Serial data clock from the external master to be supplied to this pin. Maximum frequency = 125kHz.

#### **CSB**

Active low, chip select pin for the SPI. Communication is started on the falling edge of CS and ended on the rising edge of CS.

#### TOUT1 - TOUT2:

Test pins. In normal mode, the internal clock signal of Whz is present on TOUT1 and the clock of the chopper amplifier is present on TOUT2.

#### **CREF**

Current reference output. CREF is the reference voltage output for the temperature independent current source. The requirements for the resistor to be connected between CREF and VSS depend on the required accuracy and range of the ambient temperature measurement. The voltage level at CREF depends directly on the internal band-gap.

#### **VREFP**

Voltage reference I/O pin. This level is by default dependent on the on-chip band-gap reference source and can be programmed in range 2-4.5V from eeprom . This voltage is used as reference for the DAC, external applied potentiometer and 8-bit ADC. The chip can be configured to use an external reference voltage instead of the on-chip reference.

The pin is protected from over-voltage and can withstand 16V

#### **AGND**

Analog ground reference pin. This voltage is derived from the on-chip band-gap and has a typical level of 2.5V for maximum output range of the amplifiers. When IROUT and/or TEMPOUT are connected directly to the amplified analog signals, then these signals are referred to AGND. The regulator can be stopped from the eeprom configuration register. In this case the pin can be used for external reference for the 12-bit ADC.

The pin is protected from over voltage and can withstand 16V

### VDD1

High voltage supply pin. This supply pin can be connected directly to an automotive ignition supply voltage. The internal regulator can operate with voltages between 7V and 80V.

#### **VDD**

5V regulated supply pin. The 5V regulated voltage from the on-chip regulator is available on this pin. The internal regulator can supply up to 20mA to external circuitry. VDD can also be used to supply the chip directly with an external 5V regulated supply.

#### **TEMPOUT**

TEMPOUT analog output/Comparator output pin. This pin can be configured as analog output of the

# Programmable IR Sensor Interface

temperature sensor or as output of the internal comparator circuit. As analog output, this pin can either be connected to the analog amplified temperature sensor signal or to the linearised ambient temperature by means of the DAC.

When used as comparator output, different configurations are possible as shown below.

The driver can source at least ImA and sink at least 20µA to an external load. If the capacitive load on this pin exceeds 50pF, the load should be de-coupled by means of a series resistor. The pin is also output for linearised Tambient in PWM mode. The pin is protected from over-voltage and can withstand 16V

### **Analog Section**

### Supply regulator and Power-ON Reset

The on-chip supply regulator and can be powered by an automotive ignition supply line (7V-80V). The chip can withstand SAE standard ignition transients. The resulting voltage of the regulator is available on VDD (5V±300mV). The VDD pin can source up to 20mA to external circuitry. The chip can also be supplied directly with a 5V regulated supply on pin VDD.

The power-on reset (POR) circuitry is completely internal. The chip is fully operational 16ms from the time the supply crosses 1.3V. The POR circuit will issue another POR if the supply voltage goes below 1.3V.

### Band-gap, DAC and ADC references

The on-chip trimmable, curvature compensated band-gap circuitry provides a stable reference level (less than 10ppm per °C) for several derived reference potentials used for normal operation in MLX90313. The analog ground at the AGND pin is directly derived from this band-gap voltage. The output voltages from both amplifier chains are relative to this potential. The AGND reference can be trimmed internally to (2.5V±20mV). The regulator at AGND pin can be switched off to minimize the current consumption. The pin can be also used as external input for the internal 12-bit ADC.

The reference voltages for ADC and DAC are also derived from the band-gap. The DAC reference is available at pin VREFP. The MLX90313 DAC reference voltage can be programmed on chip to one of the following values: 2, 2.5, 3, 3.5, 4 and 4.5 V. Depending on the customer application Melexis can program the linearised analog outputs for object and ambient temperatures providing absolute voltage/temperature dependence. The internal regulator for the DAC reference voltage can be switched off to minimize the consumption (if linearised analog output is not in use) or to use externally supplied reference for DAC reference in range 2 to 5V

The ADC reference is 2.5V typically. The chip can be also programmed to use external ADC reference connected to pin AGND. The current reference bias voltage (present at CREF pin) is also derived from the on-chip band-gap reference.

### IR-amplifier chain

MLX90313 is available with gain settings for the IR-amplifier chain ranging from 55 to 5500. The gain can be selected by setting the appropriate bits of the 'Irgain1'-register (EEPROM address 00h) according to the table below. Any gain between the abovementioned limits can be obtained within an accuracy of  $\pm 6.5\%$ . The amplifier input-referred white noise level is below 23nVrms/ $\sqrt{\text{Hz}}$ . In the application with IR-sensors, with output resistance of  $50\text{k}\Omega$  typical, the total system noise will however depend mainly on the noise of the sensor and will rise up to  $45\text{nVrms}/\sqrt{\text{Hz}}$ . The offset for the chopper stabilized amplifier path can be largely calibrated out and amounts to maximum  $4\mu\text{V}$ .

The common mode input range of the amplifier is -100 mV to VDD - 3V. The output range of the amplifier is 0V to VDD-0.2V. The output of the amplifier is referred to the potential on AGND.

### IR chain gain settings

| $G_{IR} = G_{pr} \times G_b \times G_{pa} \times G_l$ |              |     |       |      |      |    |              |   |       |      |      |       |       |

|-------------------------------------------------------|--------------|-----|-------|------|------|----|--------------|---|-------|------|------|-------|-------|

| stage                                                 | $G_{\it pr}$ |     | $G_b$ |      |      |    | $G_{\it pa}$ |   | $G_l$ |      |      |       |       |

| contr.<br>bits                                        | GCI0         |     | GCI3  | GCI2 | GCI1 |    | GCI4         |   | GCI7  | GCI6 | GCI5 |       |       |

| w. Data                                               | taShee       | e   | 0     | Χ    | Χ    | 5  |              |   |       | 0    | 0    | 0     | 1.067 |

|                                                       | 0            | 10  | 1     | 0    | 0    | 10 | 0            | 4 | 0     | 0    | 1    | 1.143 |       |

|                                                       | U            | 10  | 1     | 0    | 1    | 15 | U            | I | 0     | 1    | 0    | 1.231 |       |

| setting                                               |              |     | 1     | 1    | 0    | 20 |              |   | 0     | 1    | 1    | 1.333 |       |

| Setting                                               |              |     |       |      |      |    |              |   |       | 1    | 0    | 0     | 1.455 |

|                                                       | 1            | 20* | 1     | 1    | 1    | 25 | 1            | 5 | 1     | 0    | 1    | 1.600 |       |

|                                                       | '            | 20  | ·     | '    | '    | 23 | '            | 3 | 1     | 1    | 0    | 1.778 |       |

|                                                       |              |     |       |      |      |    |              |   | 1     | 1    | 1    | 2.000 |       |

\* This option is available only if ENLN=1

The pin ENLN controls both the noise level and distortion of the amplifier. If ENLN=1 the noise of the amplifier is 23nVrms/ $\sqrt{\text{Hz}}$ , the gain of 20 in first stage is available but the input signal must be less than 4 mV for less than 0.05% full scale distortion.

If ENLN is 0 then the span of the input signal can be  $\pm$  40mV with distortion less than 0.1% full scale. In this case the noise floor of the amplification chain increases 3 times.

#### Temp-amplifier chain

MLX90313 is available with gain settings for the Temp-amplifier ranging from 5 to 50. The gain can be selected by setting the appropriate bits of the 'Temp gain and current control'-register (EEPROM address 02h) according to the table below. Any gain between the abovementioned limits can be obtained within an accuracy of ±6.5%. It is also possible to completely bypass the temperature amplifier and force the input signal directly to the ADC. The amplifier input-referred white noise level is below 400nVrms/√Hz. The common mode input range of the amplifier is -100mV to VDD-3V. The output of the amplifier is referred to the potential on AGND.

### Temp chain gain settings

| remp           | Orium g          | Julii Juli     | iiigo \ | \  |       |       |      |       |        |        |        |     |  |

|----------------|------------------|----------------|---------|----|-------|-------|------|-------|--------|--------|--------|-----|--|

| $G_T =$        | $G_{pr} 	imes G$ | $G_l \times M$ |         |    |       |       |      |       |        |        |        |     |  |

| stage $G_{pr}$ |                  |                |         |    | $G_l$ | $G_l$ |      |       |        | M      |        |     |  |

| contr.<br>bits | GCT2             | GCT1           | GCT0    |    | GCT5  | GCT4  | GCT3 |       | IRSEL2 | IRSEL1 | IRSEL0 |     |  |

|                | 0                | 0              | 0       | 1  | Χ     | Χ     | Х    |       |        |        |        |     |  |

|                | 0                | 1              | 1       | 5  | 0     | 0     | 0    | 1.067 | 0      | 0      | 0      | off |  |

|                | 0                | '              | '       | 5  | 0     | 0     | 1    | 1.143 | 0      | 0      | 1      | 1/7 |  |

|                | 1                | 0              | 0       | 10 | 0     | 1     | 0    | 1.231 | 0      | 1      | 0      | 2/7 |  |

| settin         | 1                | 0              | 1       | 15 | 0     | 1     | 1    | 1.333 | 0      | 1      | 1      | 3/7 |  |

| g              | 4                | 4              | 0       | 20 | 1     | 0     | 0    | 1.455 | 1      | 0      | 0      | 4/7 |  |

|                | '                | '              | 0       | 20 | 1     | 0     | 1    | 1.600 | 1      | 0      | 1      | 5/7 |  |

|                | 1                | 1              | 1       | 25 | 1     | 1     | 0    | 1.778 | 1      | 1      | 0      | 6/7 |  |

|                |                  |                |         |    | 1     | 1     | 1    | 2.000 | 1      | 1      | 1      | 1   |  |

Note: When the current mirror is on (all settings except IRSEL[2:0] = 000b) the gain is defined as follows:

$$G_T = \frac{Vout}{Rsens \cdot Icref}$$

where Vout is the output of the analog amplifier chain, Rsens is the resistance of the sensor connected between TINP and TINN and Icref is the current out of CREF.

When the current mirror is off (IRSEL[2:0]=000b), M should be replaced by 1 and the gain is defined as follows:

$$G_T = \frac{Vout}{Vin}$$

where Vin is the voltage difference between TINP and TINN

If GCT[2:0]=0 then the temp chain will be completely off, the Timp pin will be connected directly to the ADC input, providing Gain=1

#### **Current Reference**

www.DaThe thermistor (or sensor) connected to TINP must be biased with a current source. This bias current is mirrored from the current through the external resistor between CREF and VSS. The voltage maintained at the CREF pin is derived from internal band-gap voltage, and thus constant. The typical value of the voltage at CREF pin is 2V.

The current mirror ratio can be set between 1/7 and 1 according to the table for the Temp-chain gain settings. The setting with IRSEL[2:0]=000b switches the current mirror off. In this case the thermistor must be biased by external circuitry.

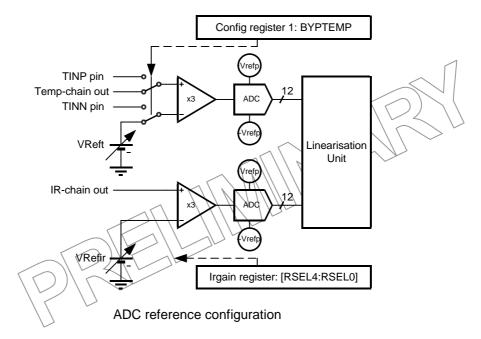

### Analog-to-Digital Converter (ADC)

MLX90313 contains a 12-bit internal analog to digital converter. Real 12 bit conversion is achieved by a fully differential signal path of the converter. The input amplifier of the ADC has a fixed gain of 3. Automatic calibration is implemented in the background, which allows precise conversion in a very wide temperature range. The ADC sampling rate is 7k samples/second. The reference voltage for the ADC is normally a scaled version of the internal band-gap reference and is fixed to be 2.5V. Alternatively MLX90313 can be configured to work with an external reference potential, applied to the AGND pin. In this case the appropriate bit in the configuration register (SELADREF bit in Confreg1) must be cleared. Internal ADC can work with references down to 1 V keeping the 12-bit resolution.

The ADC contains an interface circuit to scale and offset the analog signals in order to make the most efficient use of the available resolution. After amplification the IR and Temp sensor signals are referred to AGND voltage level (typical value 2.5V). The additional offset is scaled version of the AGND. The ADC interface circuit is given below. The output of the Temp-chain is amplified relative to the voltage

reference VrefT, which can be controlled with 2 bits (bit10 and bit9, EEPROM address 02h). The possible values for VrefT can be calculated according to the equation:

$$VrefT = \frac{VAgnd \times 1.4 \times (63 + K)}{70}$$

, where K =0 to 3, corresponding to the value of the control bits.

The typical values are 3.15, 3.20, 3.25 and 3.3V. If the temp path amplifier is bypassed then VrefT will be fixed to: Agnd x 0.28 = 0.7V typical.

The output of the IR-chain is amplified relative to Refir and can be calculated according to the following equation:

$$Vrefir = \frac{VAgnd \times 1.4 \times (34 + K)}{70}$$

, Where K=0:31 depending on the selected value of Rsel[4:0]

The typical values (for Agnd=2.5V) are listed in the table below:

| ADC interface setting |           |           |           |           |           |           |           |  |  |

|-----------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|

| RSEL[4:0]             | Refir [V] | RSEL[4:0] | Refir [V] | RSEL[4:0] | Refir [V] | RSEL[4:0] | Refir [V] |  |  |

| 11111b                | 3.25      | 10111b    | 2.85      | 01111b    | 2.45      | 00111b    | 2.05      |  |  |

| 11110b                | 3.20      | 10110b    | 2.80      | 01110b    | 2.40      | 00110b    | 2.00      |  |  |

| 11101b                | 3.15      | 10101b    | 2.75      | 01101b    | 2.35      | 00101b    | 1.95      |  |  |

| 11100b                | 3.10      | 10100b    | 2.70      | 01100b    | 2.30      | 00100b    | 1.90      |  |  |

| 11011b                | 3.05      | 10011b    | 2.65      | 01011b    | 2.25      | 00011b    | 1.85      |  |  |

| 11010b                | 3.00      | 10010b    | 2.60      | 01010b    | 2.20      | 00010b    | 1.80      |  |  |

| 11001b                | 2.95      | 10001b    | 2.55      | 01001b    | 2.15      | 00001b    | 1.75      |  |  |

| 11000b                | 2.90      | 10000b    | 2.50      | 01000b    | 2.10      | 00000b    | 1.70      |  |  |

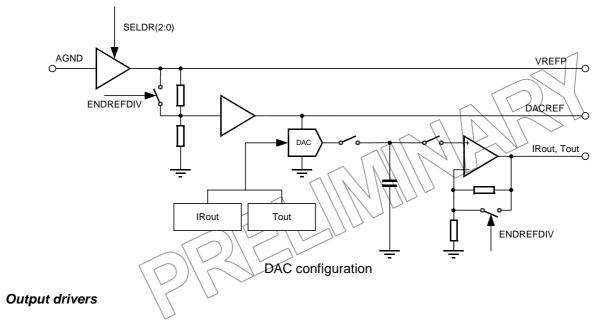

#### Digital-to-Analog Converter (DAC)

A 8 bit digital to analog converter can be used to output the data for the linearised Tobject- and Tambient signals. The DAC can work with a internal programmable reference voltage, as well as with an external one. In case the internal reference voltage is used, this voltage can be monitored on the VREFP pin. If one wants to use his own reference voltage, this can be done by applying this voltage to the VREFP pin, and setting the appropriate configuration bit.

The result from D/A conversion is stored on hold capacitors and buffered. The signals are available at IROUT and TEMPOUT respectively, if the appropriate bits are set in the configuration register (EEPROM address 04h).

The reference value for the D/A can be programmed with 3 bits: SELDR[2:0] (register Irgain2) according to the table below:

| SELDR2 | SELDR1 | SELDR0 | ELDRO ENDREFDIV |     |

|--------|--------|--------|-----------------|-----|

| 0      | 0      | 0      | 0               | 2   |

| 0      | 0      | 1      | 0               | 2.5 |

| 0      | 1      | 0      | 0               | 3   |

| 0      | 1      | 1      | 1               | 3.5 |

| 1      | 0      | 0      | 1               | 4   |

| 1      | 0      | 1      | 1               | 4.5 |

For reference voltages higher than 3V the ENDREFDIV bit must be set. In this case the ASIC will divide internally the reference by 2 to provide proper input common mode for the output buffer amplifiers at pins IROUT and TEMPOUT. In this case the result of the D/A conversion result will be amplified times 2 by the output amplifiers, which will ensure the requested signal swing.

Melexis can rescale the DAC reference and eeprom table for the linearisation unit to provide absolute analog output. This way, at maximum calibrated temperature, the voltage of IROUT or TEMPOUT pin will always correspond to the requested D/A reference voltage.

The regulator for the VREFP voltage can be stopped and an external reference voltage can be forced and used from the D/A. The regulator for DAC reference voltage can also be stopped (bit ENDACREF=0) when DAC is not in use. This will save some supply current.

The IROUT and TEMPOUT outputs can be connected to various signals available: The amplified analog signals (IRINP-IRINN and TINP-TINN), the linearised object respectively ambient temperature signals, or to the comparator circuitry. The IROUT and TEMPOUT pin drivers can source 1mA and sink 20µA and are reverse voltage protected down to -5V relative to VSS. The available configurations are described in table below.

| Input/Output Setting |             |                      |            |                 |  |  |  |  |  |

|----------------------|-------------|----------------------|------------|-----------------|--|--|--|--|--|

| I/O pin              | IROUT       |                      | TEMPOUT    |                 |  |  |  |  |  |

| Control              | IROUTC[1:0] | Configuration        | TOUTC[1:0] | Configuration   |  |  |  |  |  |

| Bits                 |             |                      |            |                 |  |  |  |  |  |

|                      | 00b         | IR-chain out         | 00b        | Temp-chain out  |  |  |  |  |  |

| Sotting              | 01b         | Linear Tobject       | 01b        | Linear Tambient |  |  |  |  |  |

| Setting              | 10b         | Threshold Rel1 input | 10b        | Comp1 out       |  |  |  |  |  |

|                      | 11b         | PWM out              | 11b        | PWM out         |  |  |  |  |  |

REL1 is an open drain relay driver output controlled by the on-chip comparator circuitry. The available configurations are described in the section on the comparator circuitry.

### **Digital Section**

The digital unit on board of MLX90313 realizes all functions for control, configuration, measurements and linearisation. It contains several registers, ALU and control logic. All functions of the ASIC are hardware fixed and controlled by different state machines, which execute in sequence all procedures necessary for normal chip operation.

### Internal registers overview

The table below contains all internal registers, their addresses for access via SPI serial interface and short functional description. Depending on their function they can be divided in 3 groups:

- Control registers: they keep the configuration of the chip including all gain settings of the amplifiers. analog ground level, band-gap and oscillator trimming data, etc. All this data is stored in eeprom and after POR the system leads it in the corresponding peripheral registers.

- Data registers: they keep all data for offsets, results from measurements and linearisation of both chains. This registers can be read vis spi in normal mode and are write accessible during test mode.

- Computation registers. These registers support the computation unit and keep all temporary data necessary for digital low pas filtering, linearisation and comparator functions. They are not accessible via SPI in normal mode.

| Internal Register Table. |                             |           |             |                |        |  |  |  |

|--------------------------|-----------------------------|-----------|-------------|----------------|--------|--|--|--|

| Dogistor                 | Function                    | Addres    | SS          | Access via spi |        |  |  |  |

| Register                 | Function                    | Dec       | Hex         | Write          | Read   |  |  |  |

| IRGAIN1                  | IR-chain settings           | 0         | 00h         | Test mode      | No     |  |  |  |

| IRGAIN2                  | IR-chain settings           | 1         | 01h         | Test mode      | No     |  |  |  |

| TEMPGAIN                 | Temp-chain settings         | 2         | 02h         | Test mode      | No     |  |  |  |

| CONFREG1                 | Configuration               | 3         | 03h         | Test mode      | Always |  |  |  |

| CONFREG2                 | Configuration               | 4         | 04h         | Test mode      | Always |  |  |  |

| OSCILLATOR               | Oscillator                  | 5         | 05h         | Test mode      | No     |  |  |  |

| BGCONTROL                | Bandgap control             | 6         | 06h         | Test mode      | No     |  |  |  |

| LPF                      | Low Pass Filter             | 7         | 07h         | Test mode      | No     |  |  |  |

| ADCREG                   | ADC output data             | 8         | 08h         | Test mode      | Always |  |  |  |

| IROUT                    | Tobject (lin)               | 9         | 09h         | Test mode      | Always |  |  |  |

| TOUT                     | Tambient (lin)              | 10        | 0Ah         | Test mode      | Always |  |  |  |

| IRDATA                   | IR-chain output             | 11        | 0Bh         | Test mode      | Always |  |  |  |

| TDATA                    | Temp-chain output           | 12        | 0Ch         | Test mode      | Always |  |  |  |

| IROS                     | IR-chain offset             | 13        | 0Dh         | Test mode      | Always |  |  |  |

| TOS                      | Temp-chain offset           | 14        | 0Eh         | Test mode      | Always |  |  |  |

| MAINSTM                  | Main state machine          | 15        | 0Fh         | Test mode      | No     |  |  |  |

| TEST                     | Test mode control           | 16        | 10h         | Always         | No     |  |  |  |

| REG TEMP                 | Temporary register for test |           |             | Test mode      | No     |  |  |  |

| REG A                    | Accumulator A               |           |             | Test mode      | No     |  |  |  |

| REG B                    | Accumulator B               |           |             | Test mode      | No     |  |  |  |

| TESTCTRL 1               | Test control                | 20        | 14h         | Test mode      | No     |  |  |  |

| REG C                    | Accumulator C               |           |             | Test mode      | No     |  |  |  |

| REG E                    | Accumulator E               |           |             | Testmode       | No     |  |  |  |

| TESTCTRL 2               | ADC test control            | 23        | 17h         | Test mode      | No     |  |  |  |

| WP                       | Eeprom write protect        | 24-<br>31 | 18h-<br>1Fh | Always         | No     |  |  |  |

Configuration and control registers overview and bit functions as they are read from the module

| Bit functio | ns        |               |         |           |              |        |           |         |

|-------------|-----------|---------------|---------|-----------|--------------|--------|-----------|---------|

| REGISTERH   | B15       | B14           | B13     | B12       | B11          | B10    | B9        | B8      |

| REGISTERL   | B7        | B6            | B5      | B4        | B3           | B2     | B1        | B0      |

| IRGAIN1H    | ENDREFDIV | ENDAC         | ENLN    | GCI7      | GCI6         | GCI5   | GCI4      | √G¢I3   |

| IRGAIN1L    | GCI2      | GCI1          | GCI0    |           |              |        |           |         |

| IRGAIN2H    | AGNDC3    | AGNDC2        | AGNDC1  | AGNDC0    | SELDR2       | SELDR1 | \$ELDRÓ < | RSEL3   |

| IRGAIN2L    | RSEL2     | RSEL1         | RSEL0   |           |              |        |           |         |

| TEMPGAINH   | TRSEL1    | TRSEL0        | IRSEL2  | IRSEL1    | IRSEL0 _     | GÇTŞ \ | GCT4\     | GCT3    |

| TEMPGAINL   | GCT2      | GCT1          | GCT0    |           |              |        |           |         |

| CONFREG1H   | ERROR     | ENVR          | HVSUP   | SELADREF  | POTMÈT \ \ ' | COMP1V | COMP1P    | BYPTEMP |

| CONFREG1L   | REL1V     | REL1P         | EEWREN  | TESTMODE  |              |        |           |         |

| CONFREG0H   | IROUTC1   | IROUTC0       | TOUTC1  | TOUTÇO\\\ | SUBINC \\    | SUBDEC | NTC       | TIMEOS3 |

| CONFREG0L   | TIMEOS2   | TIMEOS1       | TIMEOS0 | n         |              |        |           |         |

| OSCH        |           |               |         |           |              |        |           | ENAGNDB |

| OSCL        |           |               |         |           |              |        |           |         |

| BGH         |           |               |         |           |              |        |           |         |

| BGL         |           |               |         | $\sqrt{}$ |              |        |           |         |

| LPFH        | RSEL4     | ENOSM \       | ENTAV\  | JŔŎS      | TOS          | LPFIR2 | LPFIR1    | LPFIR0  |

| LPFL        | LPFT2     | \LP(FT1) )\ • | TPETO   |           |              |        |           |         |

| TESTH       | 1         | 0             | \1      | 1         | 0            | 0      | 1         |         |

| TESTL       |           | 1             |         |           |              |        |           |         |

| TESTCTRL1H  |           |               |         |           |              |        |           |         |

| TESTCTRL1L  |           |               |         |           |              |        |           |         |

| TESTCTRL 2H |           |               |         |           |              |        |           |         |

| TESTCTRL 2L |           |               |         |           |              |        |           |         |

| WPH         |           |               |         |           |              |        |           |         |

| WPL         |           | 1             | 1       | 0         | 0            | 1      | 0         | 1       |

### Register Descriptions

#### IRGAIN1

Read access: No. The data is accessible for read via SPI only from eeprom address 00h. Write access: Directly to the register in test mode. To eeprom if WP-register is correctly set.

| IRGAIN1 bit functions |     |                       |                                                                                                                                    |  |  |  |  |  |

|-----------------------|-----|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name                  | POR | val                   | Function                                                                                                                           |  |  |  |  |  |

| ENDREFDIV             | Х   | 1                     | Divide the reference for the DAC and enable output amplification by 2 of the To and Ta outputs. Must be set for Vref=3.5V,4V,4.5V. |  |  |  |  |  |

| ENDAC                 | X   | 1                     | Enable the DAC regulator                                                                                                           |  |  |  |  |  |

| ENLIN                 | X   | 1                     | Enable low noise.                                                                                                                  |  |  |  |  |  |

| GCI[7:0]              | Х   | 00000000-<br>11111111 | Control the gain of the IR amplifier chain (see 'IR amplifier chain')                                                              |  |  |  |  |  |

### IRGAIN2

Read access: No. The data is accessible for read via SPI only from eeprom address 01h. Write access: Directly to internal register in test mode. To EEprom if WP-register is correctly set.

| H    | IRGAIN2 bit functions |     |           |                                  |  |  |  |  |

|------|-----------------------|-----|-----------|----------------------------------|--|--|--|--|

| Е    | Bit                   | POR | val       | Function                         |  |  |  |  |

| Α    | GNDC [3:0]            | Χ   | 0000-1111 | Reserved                         |  |  |  |  |

| LPas | SELDR [2:0]           | ľΧ  |           | Adjustment of the DAC reference. |  |  |  |  |

|      |                       | Χ   | 000       | Vref = 2V                        |  |  |  |  |

|      |                       | Χ   | 001       | Vref =2.5V                       |  |  |  |  |

|      |                       | Χ   | 010       | Vref = 3V                        |  |  |  |  |

|      |                       | Χ   | 011       | Vref = 3.5V                      |  |  |  |  |

# Programmable IR Sensor Interface

| IRGAIN2 bit functions |     |           |                                                                                                                     |  |  |  |  |  |

|-----------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit                   | POR | val       | Function                                                                                                            |  |  |  |  |  |

|                       | Χ   | 100       | Vref = 4V                                                                                                           |  |  |  |  |  |

|                       | Χ   | 101       | Vref = 4.5V                                                                                                         |  |  |  |  |  |

| RSEL[3:0]             | Х   | 0000-1111 | Select the value of the analog ground for IR signal path. The bits are 5, RSEL4 is in LPF register (see 'ADC' part) |  |  |  |  |  |

#### **TEMPGAIN**

Read access: No. The data is accessible for read via SPI only from exprom address 02h. Write access: Directly to internal register in test mode. To Exprom if WP-register is correctly set.

| <b>TEMPGAIN</b> | bit fund | ctions            |                                                                                                                                    |

|-----------------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Bit             | POR      | val               | Function                                                                                                                           |

| TRSEL[1:0]      | Х        | 00-11             | Reference voltage for Tambient measurement at ADC interface input.                                                                 |

| IRSEL[2:0]      | Х        | 000-111           | Current mirror ratio: See under M in table 'Temp chain gain settings' in the section on the Temp-amplifier chain (analog features) |

| GCT[5:0]        | Х        | 000000-<br>111111 | Temp-gain: See table 'Temp-chain gain settings' in the section on the temp-amplifier chain (analog features)                       |

#### CONFREG1

Read access: Directly from internal registers or EEprom.

Write access: Directly to internal register in test mode. To EEprom if WP-register is correctly set.

| CONFREG1               | bit fun | ctions |                                                                                                                                                                                                                              |

|------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit                    | POR     | val    | Function                                                                                                                                                                                                                     |

| Fatal Error            | Х       | 1      | Flags Multiple eeprom failure. Hamming coding can detect and correct only one bit per address. Bit will be cleared when going in test mode, disabling EEPROM protection and returning in normal mode. (for diagnostics only) |

| ENVR                   | Х       | 1      | Stops the internal reference for DAC (Pin VREF). The reference voltage can be supplied externally. If ENDAC=0 then VREF is input.                                                                                            |

| HVSUP                  | 1       | 1      | Enable the regulator for battery supply. NOTE!!! After POR this regulator will be always on. It can be stopped from EEPROM data.                                                                                             |

| SELADREF               | Χ       | 0      | External supply of ADC reference to AGND pin.                                                                                                                                                                                |

|                        |         | 1      | Enable the internal ADC reference (connected to AGND pin).                                                                                                                                                                   |

| POTMET                 | Χ       | 0      | Sets threshold level for Rel1 to THRel1 in EEprom (address 75h)                                                                                                                                                              |

| POTIVIET               |         | 1      | Sets potentiometer input (pin IROUT) as threshold level                                                                                                                                                                      |

| COMP1V                 | Χ       | 0      | Sets Tobject as target voltage for comparator Comp1                                                                                                                                                                          |

| COMPTV                 |         | 1      | Sets Tambient as target voltage for comparator Comp1                                                                                                                                                                         |

| COMP1P                 | Χ       | 0      | Sets polarity of Comp1: Inverting                                                                                                                                                                                            |

|                        |         | 1      | Sets polarity of Comp1: Non-inverting                                                                                                                                                                                        |

| BYPTEMP                | Χ       | 0      | Output of Temp amplifier path is connected to ADC                                                                                                                                                                            |

| DIFICIVIF              |         | 1      | Connects TINP-TINN directly to the ADC, bypassing the Temp-chain                                                                                                                                                             |

| DEL 1V                 | Χ       | 0      | Sets Tobject as target voltage for Rel1                                                                                                                                                                                      |

| REL1V<br>ataSheet4U.co | m       | 1      | Sets Tambient as target voltage for Rel1                                                                                                                                                                                     |

| REL1P                  | Χ       | 0      | Sets polarity of Rel1: Inverting                                                                                                                                                                                             |

| KELIP                  |         | 1      | Sets polarity of Rel1: Non-inverting                                                                                                                                                                                         |

| EEWREN                 | 0       | 1      | Enables write access in EEPROM *write protect                                                                                                                                                                                |

| TESTMODE               | 0       | 1      | Indicates chip is in test mode *write protect                                                                                                                                                                                |

<sup>\*</sup>control bits EEWREN and TESTMODE are write protected. Their values can be set only with writing the appropriate data in 'Test' and 'WP' registers. These bits are flags which indicate the system operation

## Programmable IR Sensor Interface

mode.

#### CONFREG0

| CONFDE      | \ L:4 f | -4!-n-  |                                                                         |

|-------------|---------|---------|-------------------------------------------------------------------------|

| CONFREGO    |         |         |                                                                         |

| Bit         | POR     | val     | Function                                                                |

| IROUTC[1:0] |         | 00b     | IROUT pin function: IR-chain out                                        |

|             |         | 01b     | IROUT pin function: Linear Tobject                                      |

|             |         | 10b     | IROUT pin function: Threshold Rel1 input                                |

| TOUT 014 01 |         | 11b     | IROUT pin function: PWM out                                             |

| TOUTC[1.0]  |         | 00b     | TEMPOUT pin function: Temp-chain out                                    |

|             |         | 01b     | TEMPOUT pin function. Linear Tambient                                   |

|             |         | 10b     | TEMPOUT pin function: Comp1 out                                         |

|             |         | 11b     | TEMPOUT pin function.\PWM out                                           |

| SUBINC      |         | 0       | 2nd order derivative of thermistor function is positive (used if NTC=0) |

|             |         | 1 \     | 2nd order derivative of thermistor function is negative (used if NTC=0) |

| SUBDEC      |         | 0 \     | 2nd order derivative of thermistor function is positive (used if NTC=1) |

|             |         | 1 \ \ \ | 2nd order derivative of thermistor function is negative (used if NTC=1) |

| NTC         |         | 0 🗸     | Used thermistor is PTC                                                  |

|             |         | 1       | Used thermistor is NTC                                                  |

| TIMEOS[3:0] |         | 0000    | Offset calibration interval: 0'00"                                      |

|             |         | 0001    | Offset calibration interval: 0'02"                                      |

|             |         | 0010    | Offset calibration interval: 0'17"                                      |

|             |         | 0011    | Offset calibration interval: 0'19"                                      |

|             |         | 0100    | Offset calibration interval: 1'07"                                      |

|             |         | 0101    | Offset calibration interval: 1'09"                                      |

|             |         | 0110    | Offset calibration interval: 1'24"                                      |

|             |         | 0111    | Offset calibration interval: 1'26"                                      |

|             |         | 1000    | Offset calibration interval: 2'14"                                      |

|             |         | 1001    | Offset calibration interval: 2'16"                                      |

|             |         | 1010    | Offset calibration interval: 2'31"                                      |

|             |         | 1011    | Offset calibration interval: 2'33"                                      |

|             |         | 1100    | Offset calibration interval: 3'21"                                      |

|             |         | 1101    | Offset calibration interval: 3'23"                                      |

|             |         | 1110    | Offset calibration interval: 3'38"                                      |

|             |         | 1111    | Offset calibration interval: 3'40"                                      |

### **OSCCTRL**

Read access: No. The data is accessible for read via SPI only from eeprom address 05h. Write access: Only in test mode for both writing directly to internal registers and writing to Eeprom if WP register is correctly set.

#### BGO: Reserved

Read access: No. The data is accessible for read via SPI only from eeprom address 06h.

White access: Only in test mode for both writing directly to internal registers and writing to Eeprom if the WP register is correctly set.

#### LPF

Read access: No. The data is accessible for read via SPI only from eeprom address 07h.

Microelectronic Integrated Systems

# MLX90313

# Programmable IR Sensor Interface

Write access: Only in test mode for both writing directly to internal registers and writing to Eeprom if the WP register is correctly set.

This register keeps the calibration data for the time constants of digital low pass filters of both channels (see section Linearisation Unit).

| LPF bit fund | ctions |              |                                                                 |

|--------------|--------|--------------|-----------------------------------------------------------------|

| Bit          | POR    | Val          | Function                                                        |

| RSEL4        |        | 0            | Refer to ADC interface setting                                  |

| ENOSMB       |        | 0            | Enable offset measurement of both IR & Temp channels.           |

|              |        | 1            | Disable offset measurement of both IR & Temp channels.          |

| ENTAV        |        | 0            | Reserved for future development. Reset it for all applications. |

|              |        | 1            | Reserved for future development. Reset it for all applications. |

| IROS* 0 Num  |        |              | Number of averaged offset measurements for IR chain: 512        |

|              |        | 1 /          | Number of averaged offset measurements for IR chain: 1024       |

|              |        |              | Number of averaged offset measurements for Temp chain: 512      |

|              |        | 1( ) \ ,     | Number of averaged offset measurements for Temp chain: 1024     |

| LPFIR[2:0]   |        | Number of a  | eraged points for IR measurement                                |

|              |        | 00b/ \       | 64                                                              |

|              |        | 01b 🗸        | 128                                                             |

|              |        | 10b          | 256                                                             |

|              |        | 11b          | 512                                                             |

|              |        | 100b         | 1024                                                            |

| LPFT[2:0]    |        | Number of av | veraged points for Temp measurement                             |

|              |        | 00b          | 64                                                              |

|              |        | 01b          | 128                                                             |

|              |        | 10b          | 256                                                             |

|              |        | 11b          | 512                                                             |

|              |        | 100b         | 1024                                                            |

### **ADCREG**

Read access: Directly via SPI in all modes.

Write access: Directly to internal register in test mode.

This register keeps the result from last analog to digital conversion..

#### **IROUT**

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the linearised object temperature. (Tobject)

Register format:

| Bit  | 15  | 14  | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3   | 2   | 1  | 0   |

|------|-----|-----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|-----|

| Name | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | OVH | OVL | FE | Res |

www.DataSheet4U.com

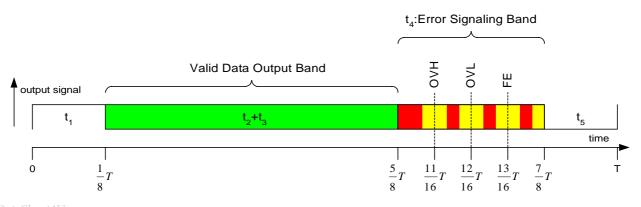

D11..D0: 12 bit temperature data

OVH: Overflow flag for Tambient measurement, Ta>Tamax, D[11:0] set to FFFh OVL: Underflow flag for Tambient measurement, Ta<Tamin, D[11:0] set to 000h

FE: Fatal Error in eeprom.

Res Not used, always zero.

# Programmable IR Sensor Interface

Note that the last 4 bits are the status register.

#### **TOUT**

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the linearised ambient temperature. (Tambient)

Register format:

| Ī | Bit  | 15  | 14  | 13 | 12 | 11 | 10 | 9  | 8  | $\lambda$ | 6   | 5      | 4    | 3   | 2   | 1  | 0   |

|---|------|-----|-----|----|----|----|----|----|----|-----------|-----|--------|------|-----|-----|----|-----|

| Ī | Name | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3,       | D2\ | \ D\1\ | \ D0 | OVH | OVL | FE | Res |

D11..D0: 12 bit temperature data

OVH: Overflow flag for Tambient measurement, Ta>Tamax, D[11:0] set to FFFh OVL: Underflow flag for Tambient measurement, Ta<Tamin, D[11:0] set to 000h

FE: Fatal Error in ee prom.

Res Not used, always zero.

Note that the last 4 bits are the status register. These bits are identical to the last 4 bits of the IROUT register.

#### **IRDATA**

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the measured IR data, compensated with the current offset of the amplifier (stored in Iros register).

#### TDATA

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the measured Temp data, compensated with the current offset of the Temp amplifier (stored in Tos register).

#### **IROS**

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the offset of the IR amplifier. Each measurement from IR amplifier will be compensated with this offset.

### TOS

Read access: Directly from internal register.

Write access: Directly to internal register in test mode.

This register keeps the offset of the Temp amplifier. Each measurement from Temp amplifier will be compensated with this offset.

## Programmable IR Sensor Interface

MAINSTM: Reserved

Read access: No

Write access: Directly to internal register in test mode

**TEST**

Read access: No.

Write access: Directly to internal register.

This register determines the chip mode. It is cleared after POR which corresponds to normal mode. Writing the proper data in this register will put the chip in test mode which will be indicated with bit 'Test' from confreg0.

| Test registe | er        |           |                          |

|--------------|-----------|-----------|--------------------------|

| Bit          | POR /     | val\\ \   | Function                 |

| B[15:9]      | 0000000b  | 1011001b  | Forces chip in test mode |

| Б[15.9]      | 00000000  | any other | Normal mode (default)    |

| B[8:0]       | 000000000 | X         |                          |

|              | b         |           |                          |

WP

Read access: No.

Write access: Directly to internal register via SPI.

The register controls the write access to the eeprom. After POR this register is cleared and the eeprom is protected, no write access available. Writing the proper data in this register will remove the write protection of the eeprom and bit EEWREN (bit 1 in Confreg1) will be set.

| EEprom wr | EEprom write protect register |           |                                 |  |  |  |  |

|-----------|-------------------------------|-----------|---------------------------------|--|--|--|--|

| Bit       | POR                           | val       | Function                        |  |  |  |  |

| B[15:9]   | 000000000<br>b                | Х         |                                 |  |  |  |  |

| DIGIOI    | 0000000h                      | 1100101b  | Enables write access to Eeprom* |  |  |  |  |

| B[6:0]    | 0000000b                      | any other | Sets EEprom write protect       |  |  |  |  |

<sup>\*</sup> The addresses 00-07h and 79-7Fh will be still protected. Write access here requires also 'Test mode'.

#### **Eeprom Description**

MLX90313 contains 128 x 16 EEPROM memory. The memory can be accessed through the serial interface. The 11 most significant bits are data bits and the 5 less significant bits are control bits used for the Error Check and Correction system (ECC). After POR the ASIC reads the full eeprom contents, checks it and corrects the single errors (1 wrong bit per address). If higher order error is discovered then the bit 'fatal error' will be set (see Confreg1 description in previous section).

The memory has two levels of protection. After POR the write access to the eeprom will be disabled. The external unit can remove this level of protection writing proper data in WP register. In this case all addresses in range 08-77h will be available for write access. The first and last 8 addresses will still be disabled. The write access to these cells is available only if the write protection is removed and the chip is in test mode.

Eeprom map overview

| Address list eeprom |                                   |         |           |             |  |  |  |  |

|---------------------|-----------------------------------|---------|-----------|-------------|--|--|--|--|

|                     | Function                          | Address | Address   |             |  |  |  |  |

| Register name       | FullCiloff \                      | Dec     | Hex       |             |  |  |  |  |

| IRGAIN1             | IR-chain settings                 | 0       | 00h       | test mode** |  |  |  |  |

| IRGAIN2             | IR-chain settings                 | 1       | 01h       | test mode   |  |  |  |  |

| TEMPGAIN            | Temp-chain settings               | 2       | 02h       | test mode   |  |  |  |  |

| CONFREG1            | Configuration                     | 3       | 03h       | test mode   |  |  |  |  |

| CONFREG2            | Configuration                     | 4       | 04h       | test mode   |  |  |  |  |

| OSCCTRL             | Oscillator control                | 5       | 05h       | test mode   |  |  |  |  |

| BGCTRL              | Bandgap control                   | 6       | 06h       | test mode   |  |  |  |  |

| LPF                 | Low Pass Filter                   | 7       | 07h       | test mode   |  |  |  |  |

| CALIBRATION         | Look up table                     | 8-111   | 08h-6Fh   | WP*         |  |  |  |  |

| CALIBRATION         | linearisation.                    | 0-111   | 0011-0111 |             |  |  |  |  |

| IOS-TEMP            | Initial offset Temp-chain         | 112     | 70h       | WP          |  |  |  |  |

| IOS-IR              | Initial offset IR-chain           | 113     | 71h       | WP          |  |  |  |  |

| RESERVED            |                                   | 114     | 72h       | WP          |  |  |  |  |

| THCOMP1             | Threshold for comparator Comp1    | 115     | 73h       | WP          |  |  |  |  |

| HSCOMP1             | Hysteresis for comparator Comp1   | 116     | 74h       | WP          |  |  |  |  |

| THREL1              | Threshold for comparator of Rel1  | 117     | 75h       | WP          |  |  |  |  |

| HSREL1              | Hysteresis for comparator of Rel1 | 118     | 76h       | WP          |  |  |  |  |

| RESERVED            |                                   | 119     | 77h       |             |  |  |  |  |

| CHIP-ID             | Data                              | 120-127 | 78h-7Fh   | test mode   |  |  |  |  |

<sup>\*</sup>WP: Write access to EEprom is controlled by the content of the internal register WP

The last 8 addresses 0x78 to 0x7F are free to use for the user. They can hold some calibration data or identification number. All data programmed into the eeprom must pass the error checking. Therefore, one must add 5 hamming bits to the eeprom data, in the 5 least significant bits.

<sup>\*\*</sup>Test mode: Write access controlled by the internal register WP and only available in test mode

### Eeprom bit definitions

Following table gives the bit definitions for all addresses that can be modified by the user. All other addresses contain specific calibration data and should be left unchanged.

Note that some bits marked "RES" are reserved and should never not be changed by the user, If other bits in such an address must be changed, read original contents first to get the status of the reserved bits.

| EEDDOM DIE  | DEFENITION O |                    |         |           |           | 1        | 4 1    | 1///    | <u>///                                   </u> |

|-------------|--------------|--------------------|---------|-----------|-----------|----------|--------|---------|-----------------------------------------------|

|             | DEFENITIONS  |                    |         |           |           | $\sim$   | 111    | 7///    |                                               |

| ADDRESS     | REGISTERH    | B15                | B14     | B13       | B12\      | B11      | B10    | B9      | B8                                            |

| (HEX)       | REGISTERL    | В7                 | B6      | B5        | B4\ \     | // B3/ / | B2     | B1      | В0                                            |

| 0x00        | IRGAIN1H     | ENDREFDIV          | ENDAC   | ENDV /    | /GCU      | /@CJ6/_  | GCI5   | GCI4    | GCI3                                          |

|             | IRGAIN1L     | GCI2               | GCI1    | \ GCI0\ \ | / /k/ " / | \\H4     | Н3     | H2      | H1                                            |

| 0x01        | IRGAIN2H     | AGNDC3             | AGNDC2  | AGNDC1\   | AGNDCO    | SELDR2   | SELDR1 | SELDR0  | RSEL3                                         |

|             | IRGAIN2L     | RSEL2              | RSEL1   | RSELO     | ∨ K       | H4       | H3     | H2      | H1                                            |

| 0x02        | TEMPGAINH    | TRSELIZ            | TRSELO  | RSEL2     | IRSEL1    | IRSEL0   | GCT5   | GCT4    | GCT3                                          |

|             | TEMPGAINL    | )\GC <del>T2</del> | GCT1    | GCT0      | K         | H4       | H3     | H2      | H1                                            |