# MICROCOMPUTER MN1500

# MN150222/P0222

# LSI User's Manual

Pub.No.20122-030E

www.DataSheet4U.com

www.DataSheet4U.com

PanaXSeries is a trademark of Matsushita Electric Industrial Co., Ltd.

The other corporation names, logotype and product names written in this book are trademarks or registered trademarks of their corresponding corporations.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The contents of this book are subject to change without notice in matters of improved function. When finalizing your design, therefore, ask for the most up-to-date version in advance in order to check for any changes.

- (3) We are not liable for any damage arising out of the use of the contents of this book, or for any infringement of patents or any other rights owned by a third party.

- (4) No part of this book may be reprinted or reproduced by any means without written permission from our company.

- (5) This book deals with standard specifications. Ask for the latest individual Product Standards or Specifications in advance for more detailed information required for your design, purchasing and applications.

If you have any inquiries or questions about this book or our semiconductors, please contact one of our sales offices listed at the back of this book or Matsushita Electronics Corporation's Sales Department. www.DataSheet4U.com

— Contents —

www.DataSheet4U.com

CHAPTER 1 OVERVIEW

- 1.1 Overview

- 1.2 Features

- 1.3 Pin Assignment

- 1.4 Pin Descriptions

- 1.5 Unused Pins

- 1.6 Block Diagram

- 1.7 Electrical Characteristics

- 1.8 Package

#### CHAPTER 2 CPU CORE FUNCTIONS

- 2.1 Clock Generator and CPU Basic Timing

- 2.2 ROM and RAM

- 2.3 Stack Area

- 2.4 Flag Status

- 2.5 Backup Mode

- 2.6 Reset

- 2.7 Clock Switching Function

#### CHAPTER 3 I/O REGISTER FUNCTIONS

- 3.1 I/O Registers List

- 3.2 Allocation and Description of Registers

- 3.3 Available Instructions

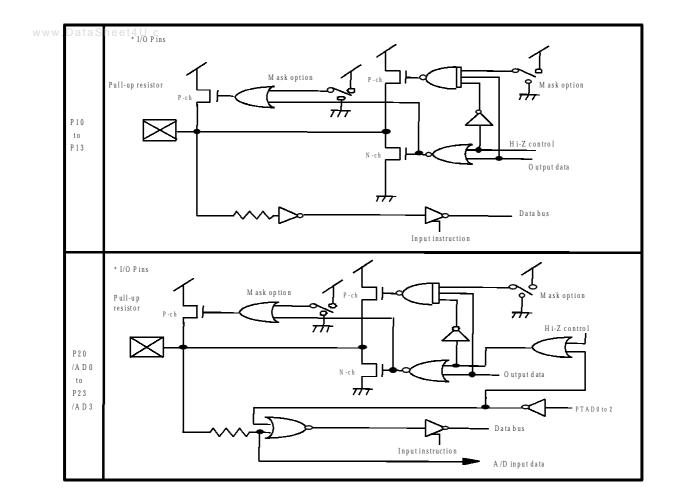

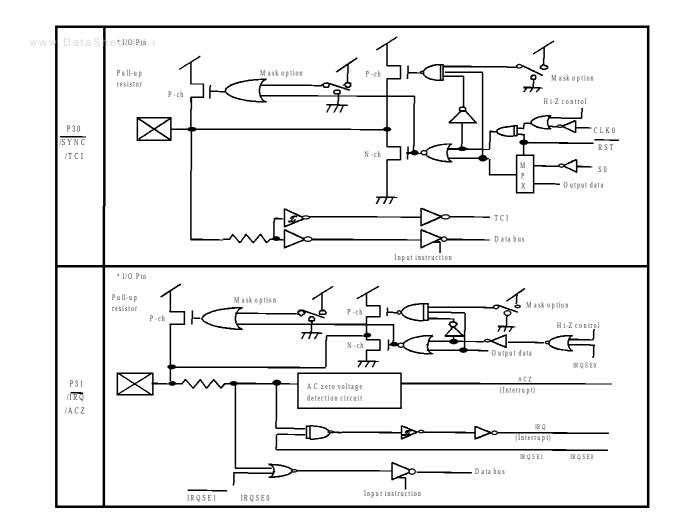

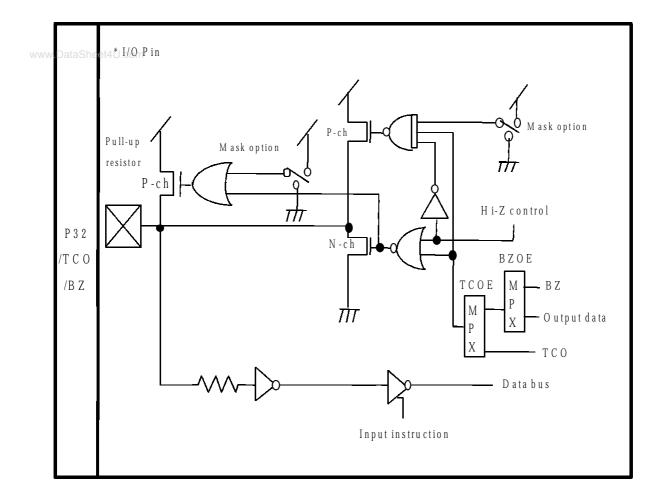

- 3.4 Pin Structure Diagram

#### CHAPTER 4 INTERRUPT FUNCTIONS

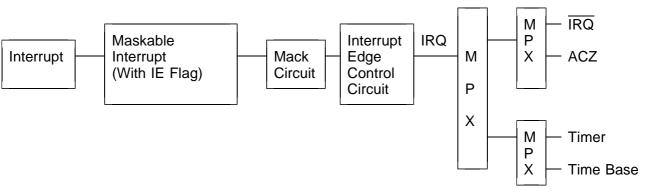

- 4.1 Interrupt Control

- 4.2 Interrupt Receiving Operation

- 4.3 Interrupt Return Operation

- 4.4 Stack upon Interrupt

CHAPTER 5 TIMER FUNCTION

CHAPTER 6 TIME BASE FUNCTION

CHAPTER 7 A/D CONVERSION FUNCTION

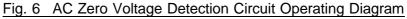

CHAPTER 8 AC ZERO VOLTAGE DETECTION FUNCTION

CHAPTER 9 WATCHDOG TIMER FUNCTION

CHAPTER 10 INSTRUCTION SETS

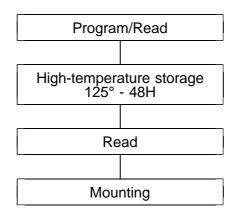

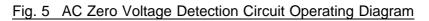

CHAPTER 11 PRODUCT WITH ON-CHIP EPROM

\* This document is based on an equivalent Japanese document that was revised on Dec. 1999.

#### CHAPTER 1 OVERVIEW

#### 1.1 Overview

This is a high-performance, low power-consuming, 4-bit, single-chip CMOS microcomputer LSI with each 2-Kbyte ROM and 96-nibble RAM.

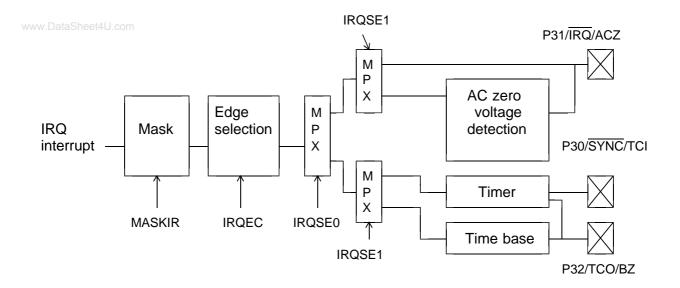

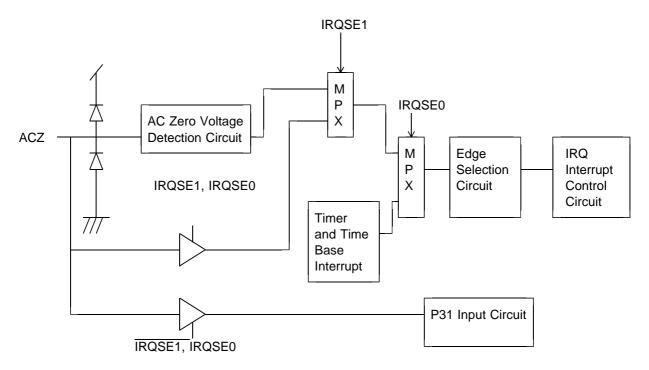

For peripheral devices, the LSI incorporates a 10-bit A/D converter, AC zero voltage detection circuit, each 8-bit timer/counter, time base block, LED direct drive pin, Hi-Z output port control circuit, auto reset circuit and watchdog timer. The auto reset circuit and watchdog timer are mask optional functions.

#### 1.2 Features

[Hardware Features]

| ROM capacity             | : 2048 × 8 bits   |                                                        |

|--------------------------|-------------------|--------------------------------------------------------|

| RAM capacity             | : 96 × 4 bits     |                                                        |

| Instruction execution f  | requency: 1/8 for | SC                                                     |

| Machine cycle            | : 1.00 µs 1/      | /8 × 8.00 MHz                                          |

|                          | V                 | DD=4.5 V to 5.5V                                       |

|                          |                   | /8 × 2.00 MHz                                          |

|                          |                   | DD=2.0 V to 5.5 V without auto reset circuit           |

|                          |                   | /dd=VRstl1 to 5.5 V with auto reset circuit)           |

|                          | •                 | /8 × 1.00 MHz                                          |

|                          |                   | DD=1.8 V to 5.5 V without auto reset circuit           |

|                          |                   | /dd=Vrstl1 or Vrstl2 to 5.5 V with auto reset circuit) |

| Interrupt                | : 1 level         |                                                        |

|                          |                   | elected with timer, time base, external interrupt or   |

|                          |                   | ge detection interrupt.)                               |

| Backup mode              | : STOP/HALT       |                                                        |

| Timer/Counter            | : Timer/Event o   |                                                        |

| Time base                |                   | nd buzzer outputs function                             |

| Watchdog timer           |                   | approx. 33-ms cycle (at fosc=8.00 MHz) (Mask option)   |

| A/D converter            |                   | el A/D conversion input, dividing into 1024 between    |

|                          | VDD and Vss       | Voltages                                               |

| AC zero voltage detec    |                   | I pin (shared with P31/IRQ)                            |

| LED direct drive pin     |                   |                                                        |

| Auto reset circuit       |                   | used when one machine cycle is 4 ms or more.           |

|                          |                   | used when one machine cycle is 8 ms or more.           |

| I/O pins Hi-Z control    | (Mask option)     |                                                        |

| Pull-up resistor setting |                   |                                                        |

| I/O pin output type      |                   | N-ch open-drain type) (Mask option)                    |

| I/O pins: General-purp   |                   | 15 pins                                                |

| A/D converte             |                   | Max. 4 pins (used in common with general-purpose I/O)  |

|                          | /Buzzer output    | 1 pin (used in common with general-purpose I/O)        |

| IRQ/ACZ inp              | ut                | 1 pin (used in common with general-purpose I/O)        |

| LED direct di            |                   | 4 pins (N-ch open-drain output)                        |

|                          |                   | (used in common with general-purpose input)            |

| SYNC pin/Tir             | mer input         | 1 pin (used in common with general-purpose I/O)        |

| Oscillator pin           |                   | 2 pins                                                 |

|                          | -                 | - F                                                    |

| Package : 20-pin SOI     | P, 22-pin SDIP    |                                                        |

| Process : Silicon gate   |                   |                                                        |

|                          |                   |                                                        |

#### [Software Features]

- Total 51 instructions

- Direct addressing computation for all RAM areas

- Non-page program counter

- 4-/1-bit operational instructions

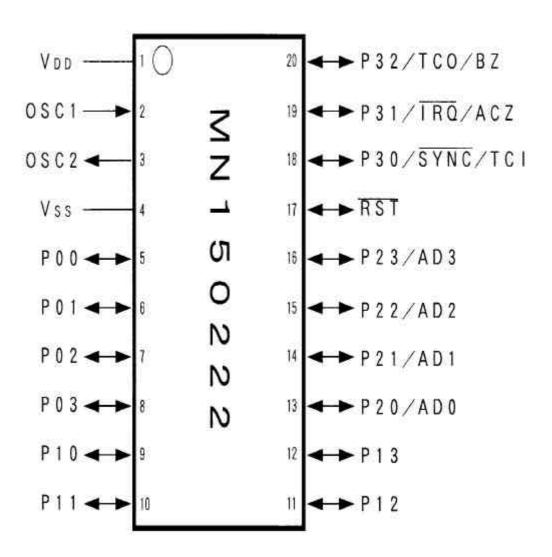

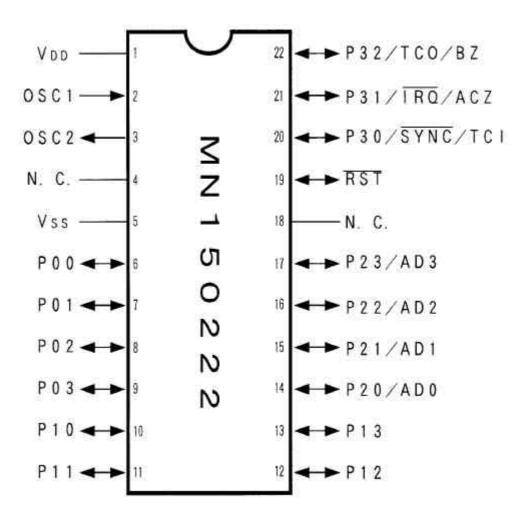

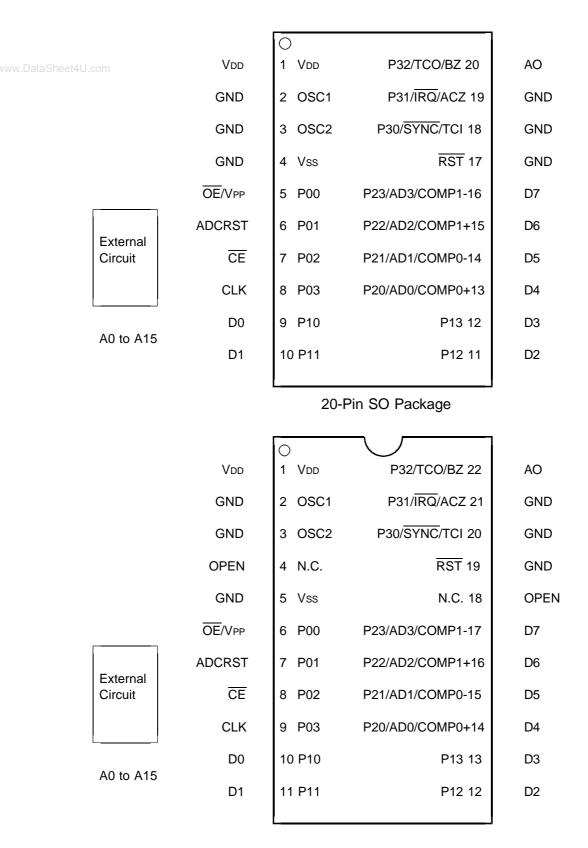

#### 1.3 Pin Assignment

www.DataShee

20-PIN SOP TOP VIEW MN150222 Pin Assignment 1

Note) No device is connected to the N.C. pin. 22-PIN SDIP TOP VIEW MN150222 Pin Assignment 2

- 5 -

### 1.4 Pin Descriptions

ww.DataSheet4U.com

| Symbol                   | Name                                          | I/O        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Initial<br>State |

|--------------------------|-----------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Vdd<br>Vss               | Power supply pins                             |            | Apply +1.8 V to +5.5 V to V <sub>DD</sub> , and 0 V to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |

| OSC1<br>OSC2             | Clock input<br>Clock output                   | I<br>O     | Oscillator connection pins. A feedback resistor is built in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |

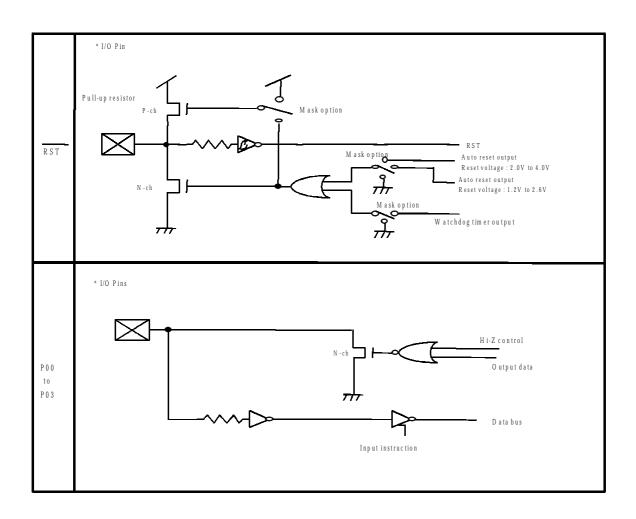

| RST                      | Reset input                                   | Ι/Ο        | The LSI is reset with low-level input<br>into this pin. In order to reset the LSI<br>without fail,it is recommendable to turn<br>on low-level input into this pin for one<br>machine cycle or more.<br>The pin incorporates a Schmitt input<br>circuit.<br>The pull-up resistor connection is<br>specified according to the mask option.<br>Whenever reset input is cleared, the<br>LSI waits for a certain period for the<br>stabilization of oscillation.<br>After that, the internal reset status of<br>the LSI is cleared.<br>This pin is used as an output pin of the<br>mask optional auto reset circuit and<br>watchdog timer circuit as well. |                  |

| P00 to<br>P03            | Parallel data I/O                             | I/O        | 4-bit parallel data I/O ports. Output type is N-ch open-drain. Capable of directly driving the LED.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Port input       |

| P10 to<br>P13            | Parallel data I/O                             | I/O        | 4-bit parallel data I/O ports. Output<br>type<br>of N-ch open-drain or push-pull and a<br>pull-up resistor connection can be<br>specified by mask option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Port input       |

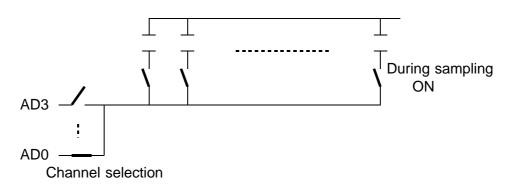

| P20/AD0<br>to<br>P23/AD3 | Parallel data I/O<br>(A/D converter<br>input) | I/O<br>(I) | 4-bit parallel data I/O ports. Output<br>type of N-ch open-drain or push-pull<br>and a pull-up resistor connection can<br>be specified by mask option.<br>Each of these pins is switched in<br>single-bit increments with software so<br>that these pins will be available to A/D<br>conversion input for a maximum of four<br>channels.                                                                                                                                                                                                                                                                                                              | Port input       |

| www.DSymbol.                 | om Name                                                                       | I/O               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Initial<br>State                                                                |

|------------------------------|-------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| P <u>30</u><br>/SYNC<br>/TCI | Parallel data I/O<br>(Sync signal<br>output)<br>(Timer input)                 |                   | Parallel data I/O port. Output type of<br>N-ch open-drain or push-pull and a<br>pull-up resistor connection can be<br>specified by mask option.<br>The SYNC internal timing signal is<br>output from this pin when the LSI is<br>reset or within two machine cycles after<br>the internal reset status of the LSI is<br>cleared.<br>The pin has push-pull output<br>regardless of mask optional<br>specifications while the SYNC timing<br>signal is output.<br>The TCI timer input pin incorporates a<br>Schmitt input circuit.<br>If the clock source of the timer is set to<br>the TCI input with software, the output<br>of P30/SYNC/TCI will be Hi-Z state. | CPU<br>timing<br>output at<br>reset<br>Port input<br>after<br>clearing<br>reset |

| P <u>31</u><br>/IRQ<br>/ACZ  | Parallel data I/O<br>(External<br>interrupt)<br>(AC zero<br>voltage<br>input) | I/O<br>(I)<br>(I) | Para <u>llel</u> data I/O port.<br>The IRQ external interrupt pin<br>incorporates a Schmitt input circuit.<br>Output type of N-ch open-drain or<br>push-pull and a pull-up resistor<br>connection can be specified by mask<br>option.<br>The output of P31/IRQ/ACZ pin will be<br>Hi-Z state if the external interrupt<br>function or AC zero voltage detection<br>interrupt function is selected with<br>software.                                                                                                                                                                                                                                              | Port input                                                                      |

| Р32<br>/TCO<br>/BZ           | Parallel data I/O<br>(Timer output)<br>(Buzzer output)                        | I/O<br>(O)<br>(O) | Parallel data I/O port. Output type of<br>N-ch open-drain or push-pull and a<br>pull-up resistor connection can be<br>specified by mask option.<br>This pin is switched over with software<br>so that timer or buzzer output from this<br>pin will be enabled.                                                                                                                                                                                                                                                                                                                                                                                                   | Port input                                                                      |

Note) The port input as an initial status described in the above table is applicable while the LSI is under Hi-Z control. After the Hi-Z status is cleared, each pin has output according to the mask option.

#### 1.5 Unused Pins

It is recommendable to fix each unused pin to the status shown in the following table.

| Pin name                                                  | Output type                        | Pull-up resistor            | Fixation method                             |

|-----------------------------------------------------------|------------------------------------|-----------------------------|---------------------------------------------|

| P00 to P03                                                | N-ch open-drain                    | Selection disabled          | Fixed to "L"                                |

| P10 to P13                                                | N-ch open-drain                    | ON                          | Open                                        |

|                                                           | N-ch open-drain                    | OFF                         | Fixed to "L"                                |

| P20/AD0 to P23/AD3                                        | N-ch open-drain                    | ON                          | Open                                        |

| I/O port selection                                        | N-ch open-drain                    | OFF                         | Fixed to "L"                                |

| P30/SYNC/TCI                                              | N-ch open-drain<br>N-ch open-drain | ON<br>OFF                   | Open<br>Fixed to "L" via<br>a 1-kW resistor |

| P31/IRQ/ACZ                                               | N-ch open-drain                    | ON                          | Open                                        |

| I/O port selection                                        | N-ch open-drain                    | OFF                         | Fixed to "L"                                |

| P32/TCO/BZ                                                | N-ch open-drain                    | ON                          | Open                                        |

| I/O port selection                                        | N-ch open-drain                    | OFF                         | Fixed to "L"                                |

| P10 to P13, P20 to<br>P23P30 to P32<br>I/O port selection | CMOS push-pull                     | Selection disabled<br>(OFF) | Open                                        |

Make the above settings, provided that the LSI is not under Hi-Z control.

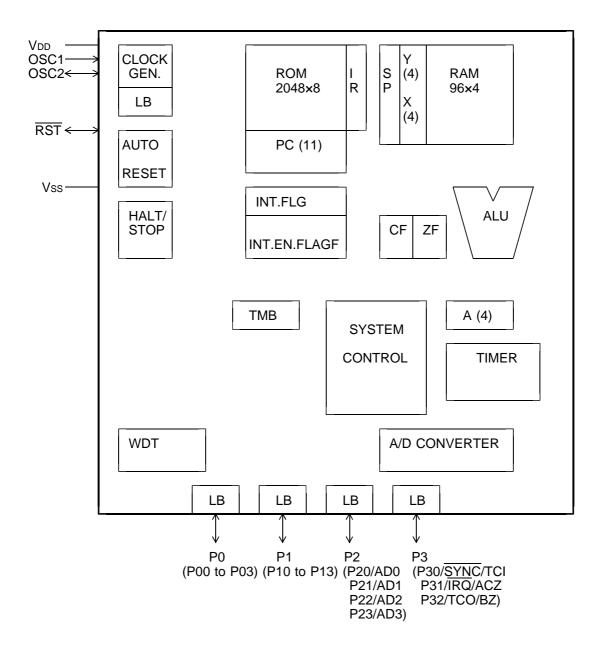

#### 1.6 Block Diagram

www.DataSheet4U.com

Description of Block Diagram

| /.DataSheet4U.com<br>Block          |                    | Function                                                                                                                                                                                                                                                                                      |

|-------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Execution<br>Control | IR                 | An instruction, which the CPU is about to execute, is read from the ROM and latched into the instruction register.                                                                                                                                                                            |

| Block                               | ROM                | The read only memory (ROM) is a program memory and stores a program to be run.                                                                                                                                                                                                                |

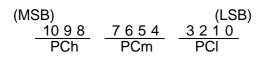

|                                     | PC                 | The program counter is a 11-bit register which controls the execution sequence of the instructions in the program memory. See Note.                                                                                                                                                           |

| Register<br>Block                   | SP                 | The stack pointer (SP) is a 4-bit register indicating the address of the stack area which uses a part of the data RAM. The stack area is used to save the PC, etc. when a subroutine call or interrupt occurs.                                                                                |

|                                     | Х                  | X is a 4-bit register for indirect addressing of the RAM space.                                                                                                                                                                                                                               |

|                                     | Y                  | Y is a 4-bit register for indirect addressing of the RAM space.                                                                                                                                                                                                                               |

| Arithmetic<br>Block                 | ALU                | The arithmetic and logic unit (ALU) performs arithmetic operations (addition, subtraction, increment, decrement and comparison) and logical operations (AND, OR, XOR, complement and rotate).                                                                                                 |

| Flag Block                          | FS<br>(CF)<br>(ZF) | The flag status (FS) consists of two kinds of flags which indicate<br>the running condition of the CPU. The carry flag (CF) is set when<br>an ALU operation result either overflows or underflows. The zero<br>flag (ZF) is set when an ALU operation result is zero, or otherwise,<br>reset. |

| Data Memory<br>Block                | RAM                | The random access memory (RAM) is used both as a stack area<br>and a data area which accumulates the data required for running<br>the program.                                                                                                                                                |

| Interrupt<br>Control Block          | IF<br>IE           | This block controls an interrupt using the interrupt control flag (IF) and interrupt enable flag (IE).                                                                                                                                                                                        |

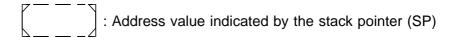

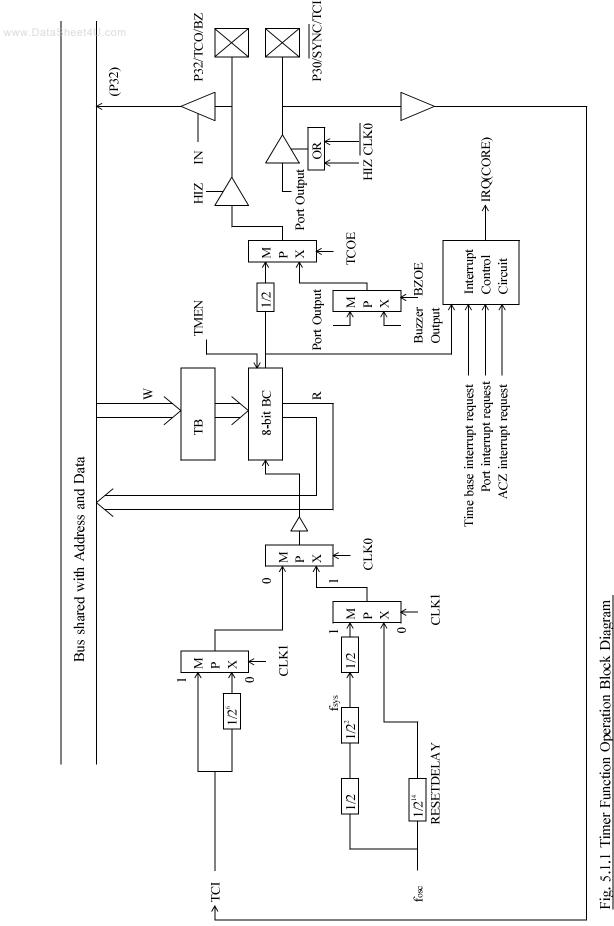

| Timer/Counter<br>Block              | TM<br>TB<br>BC     | The timer/counter consists of TM which sets either the timer or<br>event count mode and frequency dividing ratio, TB which sets a<br>timer value and BC, a binary counter, which counts pulses.                                                                                               |

| Time Base<br>Block                  | TMB                | The time base block divides the frequency of the clock signal $f_{osc}$ by the frequency dividing ratio selected with software.                                                                                                                                                               |

Note) Set the bits of the program counter as indicated below.

| ww.DataSheet4U.com   | ζ                        | Function                                                                                                                                                                                                           |  |  |  |

|----------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Oscillation<br>Block | CLOCK<br>GENE-<br>RATOR  | Connect a system clock oscillator between OSC1 and OSC2.                                                                                                                                                           |  |  |  |

| Auto Reset           | AUTO<br>RESET            | The auto reset function <u>enables</u> the low-voltage detection circuit o operate and sets the RST pin to low level when the $V_{DD}$ drops o or below $V_{RSTL}$ voltage.                                        |  |  |  |

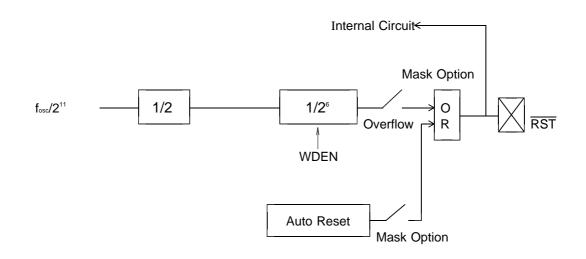

| Watchdog<br>Timer    | WDT                      | The clock of $f_{osc}/2^{12}$ is divided by $2^6$ through the watch <u>dog</u> timer. The watchdog timer outputs a low-level signal to the RST pin if an overflow occurs.                                          |  |  |  |

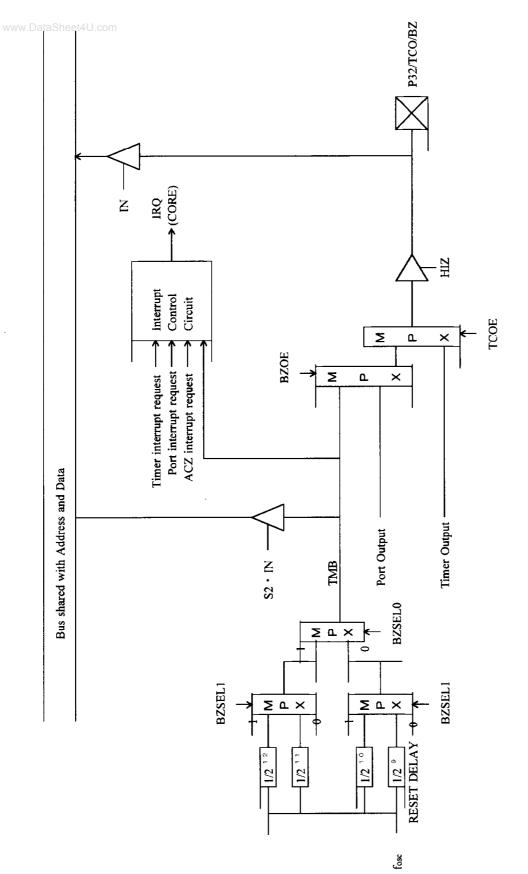

| A/D Converter        | A/D<br>CON-<br>VERTER    | The A/D converter has a resolution of 10 bits with a maximum of four analog input channels. The analog input between the VDD and Vss voltages are divided by 1024 to convert the analog input into digital values. |  |  |  |

| Others               | Vss<br><u>Vdd</u><br>RST | Vss and V <sub>DD</sub> are power supply pins. Apply +1.8 V to +5.5 V to $\frac{V_{DD.}}{RST}$ is a reset pin and activated when the $\overline{RST}$ pin is at high level.                                        |  |  |  |

#### 1.7 Electrical Characteristics (See Note 1.)

| ISI | eet4U.com<br><b>Type</b> | MOS LSI                              |

|-----|--------------------------|--------------------------------------|

|     | Function                 | CMOS 4-bit single-chip microcomputer |

#### A. Absolute Maximum Ratings

Ta = 25 °C Vss = 0 V

|     | Parameter                                                  | Symbol               | Rating                                                          | Unit |

|-----|------------------------------------------------------------|----------------------|-----------------------------------------------------------------|------|

| A1  | Supply voltage                                             | Vdd                  | -0.3 to +7.0                                                    | V    |

| A2  | Input <u>clam</u> p current<br>(P31/IRQ/ACZ)               | lc                   | -0.5 to +0.5                                                    | mA   |

| A3  | Input pin voltage                                          | Vı                   | -0.3 to V <sub>DD</sub> +0.3<br>* Not applicable to P31/IRQ/ACZ | V    |

| A4  | Output pin voltage                                         | Vo                   | -0.3 to VDD +0.3                                                | V    |

| A5  | High-current output<br>pin voltage                         | Vон                  | -0.3 to +7.0                                                    | V    |

| A6  | I/O pin voltage                                            | Vio                  | -0.3 to VDD +0.3                                                | V    |

| A7  | Peak output current<br>(Other than P0)                     | OH(Peak)<br>OL(Peak) | -10<br>20                                                       | mA   |

| A8  | Peak output current<br>(P0)                                | OL(Peak)             | 40                                                              | mA   |

| A9  | Average output<br>current (See Note 2.)<br>(Other than P0) | IOH(avg)<br>IOL(avg) | -2<br>10                                                        | mA   |

| A10 | Average output<br>current (See Note 2.)<br>(P0)            | IOL(avg)             | 15                                                              | mA   |

| A11 | Power dissipation                                          | PD                   | See Note 3.                                                     | mW   |

| A12 | Operating ambient temperature                              | Topr                 | -40 to +85                                                      | °C   |

| A13 | Storage temperature                                        | Tstg                 | -55 to +125                                                     | °C   |

Note 1) Those electrical characteristics are reference values. For details, refer to the Product Standards.

Note 2) Applied to any 100 ms period.

Make sure that the total output current value of all output pins is 30 mA or less for 20-pin SOP and 50 mA or less for 22-pin SDIP. Note 3) 22-pin SDIP:  $P_D = 350 \text{ mW}$

20-pin SOP : P<sub>D</sub> = 180 mW

#### B. Operating Conditions Ta = -40 °C to +85 °C, V<sub>DD</sub> = 1.8 V to 5.5 V (V<sub>RSTL1</sub> or V<sub>RSTL2</sub> to 5.5 V), V<sub>SS</sub> = 0 V See Note.

| Sheet4 | U-com          |        |                                                                                             |                  | 000 | nole. |      |

|--------|----------------|--------|---------------------------------------------------------------------------------------------|------------------|-----|-------|------|

|        | Parameter      | Symbol | Conditions                                                                                  | Limits           |     |       | Unit |

|        | Falameter      | Symbol | Conditions                                                                                  | min              | typ | max   | UIII |

| B1     | Supply voltage | Vdd1   | Machine cycle: 1.0 μs<br>High-speed oscillation<br>mode                                     | 4.5              | 5.0 | 5.5   |      |

|        |                | Vdd2   | Machine cycle: 4.0 μs<br>High-speed oscillation<br>mode without auto reset                  | 2.0              |     | 5.5   |      |

|        |                | Vdd3   | Machine cycle: 8.0 µs<br>High-speed oscillation<br>mode without auto reset                  | 1.8              |     | 5.5   | V    |

|        |                | Vdd4   | Machine cycle: 64.0 μs<br>Low-speed oscillation<br>mode without auto reset                  | 1.8              |     | 5.5   |      |

|        |                | Vdd5   | Machine cycle: 4.0 µs<br>or more<br>High-/low-speed<br>oscillation modes with<br>auto reset | Vrstl1           |     | 5.5   |      |

|        |                | Vdd6   | Machine cycle: 8.0 µs<br>or more<br>High-/low-speed<br>oscillation modes with<br>auto reset | Vrstl1<br>Vrstl2 |     | 5.5   |      |

Note) V<sub>RSTL1</sub> and V<sub>RSTL2</sub> voltages refer to the supply voltages that are detected to reset the LSI, which are applicable if the auto reset circuit is selected as a mask option.

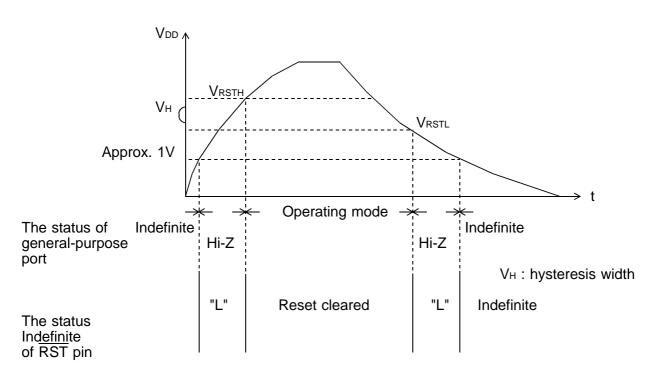

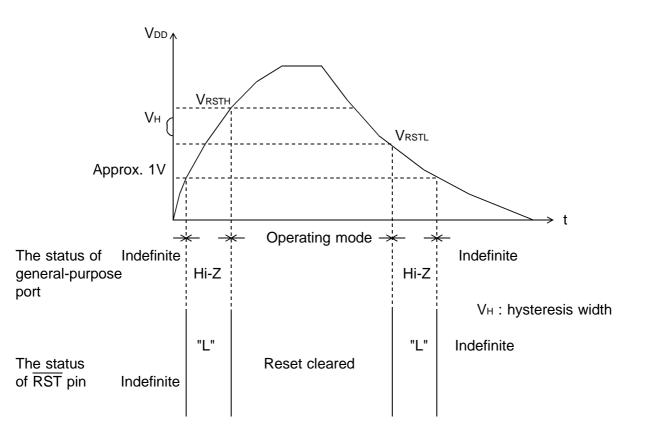

Auto Reset Circuit 1

| B2 | Voltage<br>detection level | Vrsth1                 |        |      | 3.1 | 4.0 |      |

|----|----------------------------|------------------------|--------|------|-----|-----|------|

|    |                            | Vrstl1                 | Fig. 1 | 2.0  | 3.0 |     | V    |

| B3 | Hysteresis width           | Vн                     |        | 0.05 | 0.1 |     |      |

| B4 | Supply voltage change rate | $\Delta$ t/ $\Delta$ V |        | 1.00 |     |     | ms/V |

\* The above values are applied when use of the auto reset function is selected as a mask option and the LSI is operated by the normal 5-V supply voltage.

| B5 | Voltage<br>detection level | Vrsth2                 |        |      | 2.0 | 2.6 |      |

|----|----------------------------|------------------------|--------|------|-----|-----|------|

|    |                            | Vrstl2                 | Fig. 1 | 1.2  | 1.9 |     | V    |

| B6 | Hysteresis width           | Vн                     | Fig. 1 | 0.05 | 0.1 |     |      |

| B7 | Supply voltage change rate | $\Delta$ t/ $\Delta$ V |        | 1.00 |     |     | ms/V |

Auto Reset Circuit 2

\* The above values are applied when use of the auto reset function is selected as a mask option and the LSI is operated by the normal 3-V supply voltage.

Operating Speed Ta= -40 °C to +85 °C, V\_DD=1.8 V to 5.5 V (VRSTL1 or VRSTL2 to 5.5V), www.DataShVss=0.V

|    | Parameter Symbol                 |                 | Conditions                                                                                                                                 |     | Limits |     | Unit |

|----|----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|------|

| Г  |                                  |                 | Conditions                                                                                                                                 | min | typ    | max | Unit |

|    |                                  | t <sub>c1</sub> | V <sub>DD</sub> =4.5 V to 5.5 V<br>High-speed oscillation mode<br>f <sub>osc</sub> =8.0 MHz                                                |     | 1.0    |     |      |

| B8 | Instruction<br>execution<br>time | tc2             | V <sub>DD</sub> =2.0 V (V <sub>RSTL1</sub> ) to 5.5 V<br>High-speed oscillation mode<br>f <sub>osc</sub> =2.0 MHz<br>( ): At auto reset ON |     | 4.0    |     | μs   |

|    |                                  | tсз             | VDD=1.8 V(VRSTL1 OF VRSTL2)<br>to 5.5 V<br>High-speed oscillation mode<br>fosc=1.0 MHz<br>( ): At auto reset ON                            |     | 8.0    |     |      |

|    |                                  | tc4             | VDD=1.8 V (VRSTL1 or VRSTL2)<br>to 5.5 V<br>Low-speed oscillation mode<br>fosc=125 kHz<br>( ): At auto reset ON                            |     | 64.0   |     |      |

|    |                                  |                 |                                                                                                                                            |     |        |     |      |

Oscillation

#### OSC1, OSC2 (See Note.)

| B9 | Oscillator<br>frequency | fXtal1             | VDD=1.8 V to 5.5 V<br>High-speed oscillation<br>mode             | 0.5 | 8.0 | MHz |

|----|-------------------------|--------------------|------------------------------------------------------------------|-----|-----|-----|

|    |                         | f <sub>Xtal2</sub> | V <sub>DD</sub> =1.8 V to 5.5 V<br>Low-speed oscillation<br>mode | 32  | 125 | kHz |

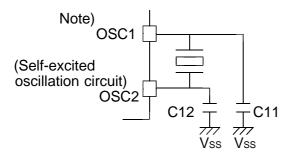

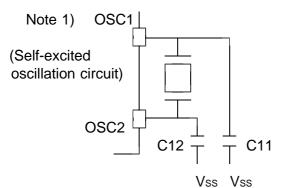

- Have the sample of the above circuits evaluated by oscillator manufacturer to determine the external capacitance each of C11 and C12. In most cases, the appropriate value of each capacitor seems to be approx. 30 pF.

- The LSI has an on-chip feedback resistor.

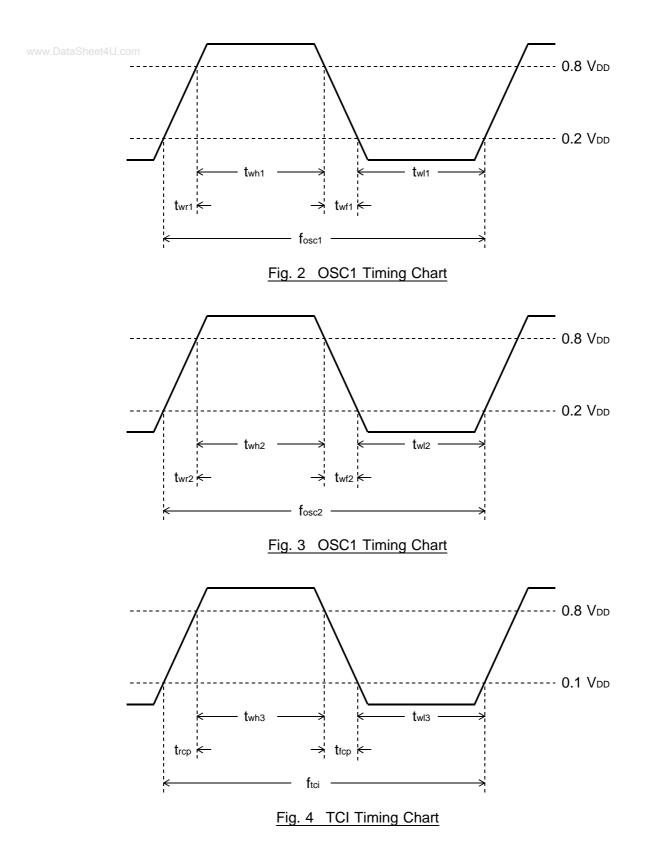

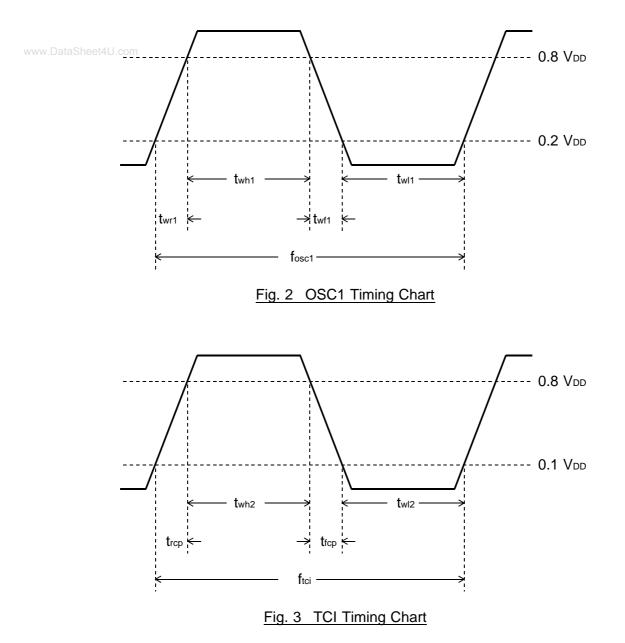

External Clock Input 1 OSC1 (High-speed oscillation mode. OSC2 is open.) w.DataSheet4U.com Ta= -40 °C to +85 °C, VDD=1.8 V to 5.5 V (VRSTL1 or VRSTL2 to 5.5 V), Vss=0 V

|     | Derometer                   | Symbol           | Conditions                                        |        | Limits |        | Unit |

|-----|-----------------------------|------------------|---------------------------------------------------|--------|--------|--------|------|

|     | Parameter                   | Symbol           | Conditions                                        | min    | typ    | max    | Unit |

| B10 | Clock frequency             | fosc1            |                                                   | 1.0    |        | 8.0    | MHz  |

|     | High-level pulse<br>width * | <b>t</b> wh1     | Fig. 2<br>A clock duty ratio<br>should be 45 % to | 40     |        |        |      |

|     | Low-level pulse width *     | t <sub>wl1</sub> | 55 %.                                             | 40     |        |        | ns   |

|     | Rise time                   | twr1             |                                                   |        |        | 20     |      |

|     | Fall time                   | <b>t</b> wf1     |                                                   |        |        | 20     |      |

|     | Input voltage high<br>level | VIH1             | Fig. 2                                            | 0.8Vdd |        | Vdd    | V    |

|     | Input voltage low<br>level  | VIL1             |                                                   | Vss    |        | 0.2Vdd |      |

External Clock Input 2

OSC1 (Low-speed oscillation mode. OSC2 is open.)

| B11 | Clock frequency             | fosc2            |                                                   | 32     | 125    | MHz |

|-----|-----------------------------|------------------|---------------------------------------------------|--------|--------|-----|

|     | High-level pulse width *    | twh2             | Fig. 3<br>A clock duty ratio<br>should be 45 % to | 0.8    |        |     |

|     | Low-level pulse width *     | t <sub>wl2</sub> | 55 %.                                             | 0.8    |        | ns  |

|     | Rise time                   | <b>t</b> wr2     |                                                   |        | 20     |     |

|     | Fall time                   | <b>t</b> wf2     |                                                   |        | 20     |     |

|     | Input voltage high<br>level | VIH2             | Fig. 3                                            | 0.8Vdd | Vdd    | V   |

|     | Input voltage low<br>level  | VIL2             |                                                   | Vss    | 0.2Vdd |     |

#### External Clock Input 3

TCI Ta= -40 °C to +85 °C, VDD=1.8 V to 5.5 V (VRSTL1 or VRSTL2 to 5.5 V), VSS=0 V

|     | Deremeter                   | Cumb al          | Conditions                       |        | Limits |        | L Incit |

|-----|-----------------------------|------------------|----------------------------------|--------|--------|--------|---------|

|     | Parameter                   | Symbol           | Conditions                       | min    | typ    | max    | Unit    |

| B12 | Clock frequency             | f <sub>tci</sub> | V <sub>DD</sub> = 1.8 V to 5.5 V |        |        | 5      | MHz     |

|     | High-level pulse<br>width * | twh3             | Fig. 4                           | 100    |        |        | ns      |

|     | Low-level pulse width *     | twi3             |                                  | 100    |        |        |         |

|     | Clock frequency             | f <sub>tci</sub> |                                  |        |        | 2.5    | MHz     |

|     | High-level pulse<br>width * | twh3             | VDD = VRSTL to 1.8 V<br>Fig. 4   | 200    |        |        |         |

|     | Low-level pulse<br>width *  | twi3             |                                  | 200    |        |        | ns      |

|     | Rise time                   | trcp             |                                  |        |        | 20     |         |

|     | Fall time                   | <b>t</b> fcp     |                                  |        |        | 20     |         |

|     | Input voltage<br>high level | Vінз             | Fig. 4                           | 0.8Vdd |        | Vdd    | V       |

|     | Input voltage low level     | VIL3             |                                  | Vss    |        | 0.1Vdd |         |

#### Fig. 1 Auto Reset Voltage

#### C. Electrical Characteristics (DC Characteristics)

www.DataSheet4U.com Ta= -40 °C to +85 °C, VDD=1.8 V to 5.5 V (VRSTL1 or VRSTL2 to 5.5 V), VSS=0 V

| Parameter | Symbol | Conditions |     | Limits |     | Unit |

|-----------|--------|------------|-----|--------|-----|------|

| Falameter | Symbol | Conditions | min | typ    | max | Onit |

Supply Current

| C1 |                                      | IDD1 | f <sub>osc</sub> = 8.0 MHz<br>V <sub>DD</sub> = 5.0 V    | 4.0  | 8.0  | mA |

|----|--------------------------------------|------|----------------------------------------------------------|------|------|----|

|    | Operating supply<br>current          | IDD2 | f <sub>osc</sub> = 2.0 MHz<br>V <sub>DD</sub> = 3.0 V    | 1.2  | 2.5  | ША |

|    |                                      | Іддз | f <sub>osc</sub> = 32.768 kHz<br>V <sub>DD</sub> = 5.0 V | 30.0 | 60.0 |    |

| C2 | Supply current in HALT mode          | Idd4 | f <sub>osc</sub> = 32.768 kHz<br>V <sub>DD</sub> = 5.0 V | 15.0 | 30.0 | μΑ |

| C3 | Supply current in STOP mode          | Idd5 | Vdd = 5.0 V                                              | 0.5  | 5.0  |    |

| C4 | Auto reset<br>current<br>consumption | Idd6 | Vdd = 5.0 V                                              | 30.0 | 80.0 |    |

\* Make measurement at Ta = 25 °C while under no-load condition.

\* To measure the operating supply current, IDD1, fix the I/O pins to VDD level in the RESET mode, input an 8-MHz square wave, which swings between VDD and VSS voltage levels, into the OSC1 pin.

- \* To measure the operating supply current, IDD2, fix the I/O pins to VDD level in the RESET mode, input a 2-MHz square wave, which swings between VDD and VSS voltage levels, into the OSC1 pin.

- \* To measure the operating supply current, IDD3, clear the reset mode and fix the I/O pins to VDD level during execution of NOP instruction, input a 32.768-kHz square wave, which swings between VDD and Vss voltage levels, into the OSC1 pin.

- \* To measure the supply current in HALT mode, IDD4, clear the RESET mode and set to the HALT mode, and, after fixing the I/O pins to VDD level, input a 32.768-kHz square wave, which swings between VDD and Vss voltage levels, into the OSC1 pin.

- \* To measure the supply current in STOP mode, IDD5, clear the RESET mode and set to the STOP mode. Then fix the I/O pins to VDD level and open OSC1 pin.

- \* Auto reset current consumption, IDD6, refers to the constant current consumption of the auto reset circuit with the auto reset function ON selected as a mask option. Therefore, the value of current consumption is added to each supply current rating if the auto reset circuit is enabled.

#### Ta= -40 °C to +85 °C, V\_DD=1.8 V to 5.5 V (V\_RSTL1 or V\_RSTL2 to 5.5 V), V\_SS=0 V

| www.D | lataSheet4LL.com |        |            |     |        |     |      |

|-------|------------------|--------|------------|-----|--------|-----|------|

|       | Parameter        | Symbol | Conditions |     | Limits |     | Unit |

|       | Falameter        | Symbol | Conditions | min | typ    | max | Unit |

High-Current I/O Pins P00 to P03 (N-ch open-drain)

| C5 | Input voltage high<br>level | Vih1 |                                 | 0.7Vdd | Vdd    | V  |

|----|-----------------------------|------|---------------------------------|--------|--------|----|

| C6 | Input voltage low<br>level  | VIL1 |                                 | Vss    | 0.3Vdd |    |

| C7 | Output leakage current      | Olk1 | Output: Hi-Z<br>Vıℕ =0 V to 6 V |        | ±10    | μA |

| C8 | Output voltage low level    | Vol1 | Iol =20.0 mA<br>Vdd =5.0 V      | Vss    | 2.0    | V  |

I/O Pins P10 to P13 P20/<u>AD0 to P23/AD3 (When the pins are used as P20 to P23 pins)</u> P30/SYNC/TCI, P31/IRQ/ACZ, P<u>32/TCO/BZ</u> (When the pins are used as P30/SYNC, P31, P32/TCO/BZ pins)

| C9  | Input voltage high<br>level | VIH2 |                                                                                | 0.7Vdd |      | Vdd    | V  |

|-----|-----------------------------|------|--------------------------------------------------------------------------------|--------|------|--------|----|

| C10 | Input voltage low<br>level  | VIL2 |                                                                                | Vss    |      | 0.3Vdd |    |

| C11 | Input current               | lı2  | With pull-up<br>resistor<br>V <sub>IN</sub> = 1.5 V<br>V <sub>DD</sub> = 5.0 V | -50    | -120 | -300   | μΑ |

| C12 | Input leakage current       | Ilk2 | Without pull-up<br>resistor<br>Viℕ = 0 V to Vdd                                |        |      | ±1     |    |

| C13 | Output voltage high level   | Vон2 | Іон = -500 µA<br>Vdd = 5.0 V                                                   | 4.5    |      | Vdd    | V  |

| C14 | Output voltage low level    | Vol2 | Iol = 3.5 mA<br>Vdd = 5.0 V                                                    | Vss    |      | 0.5    |    |

Note) Use the P30/SYNC/TCI pin under the following condition:

The load <u>must be set so that the output voltage high level will be more than 0.8 VDD</u> while the SYNC timing signal is output. That is, at the time the LSI is reset or within two machine cycles after the reset status of the LSI is cleared.

#### Ta= -40 °C to +85 °C, VDD=1.8 V to 5.5 V (VRSTL1 or VRSTL2 to 5.5 V), VSS=0 V

| www.Da | taSheet4U.com |        |            |     |        |     |      |

|--------|---------------|--------|------------|-----|--------|-----|------|

|        | Parameter     | Symbol | Conditions |     | Limits |     | Unit |

|        | Falanielei    | Symbol | Conditions | min | typ    | max | Unit |

#### Input Pins P20/AD0 to P23/AD3 (When the pins are used as A/D input pins)

| C15 | Converted voltage range         | Vad   |                                                                                | Vss |                        | Vdd                    | V   |

|-----|---------------------------------|-------|--------------------------------------------------------------------------------|-----|------------------------|------------------------|-----|

| C16 | Resolution                      |       |                                                                                |     |                        | 10                     | bit |

| C17 | Relative precision              |       | V <sub>DD</sub> = 5.0 V<br>Vss = 0.0 V                                         |     |                        | ±3                     | LSB |

| C18 | Zero transition voltage         | Vот   | VSS = 0.0 V                                                                    |     | 10                     | 30                     | mV  |

| C19 | Full-scale transition voltage   | Vfst  |                                                                                |     | V <sub>DD</sub><br>-10 | V <sub>DD</sub><br>-30 |     |

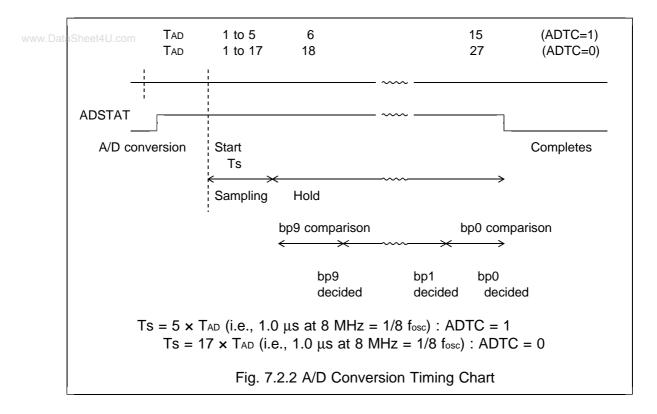

| C20 | A/D conversion time             |       | f <sub>osc</sub> = 8 MHz<br>V <sub>DD</sub> = 5.0 V<br>V <sub>SS</sub> = 0.0 V |     | 15.00                  | 27.00<br>See<br>Note.  | μs  |

| C21 | Sampling time                   |       | f <sub>osc</sub> = 8 MHz<br>V <sub>DD</sub> = 5.0 V<br>V <sub>SS</sub> = 0.0 V |     | 5.00                   | 17.00<br>See<br>Note.  | μs  |

| C22 | Analog input<br>voltage         | Vadin |                                                                                | Vss |                        | Vdd                    | V   |

| C23 | Analog input<br>leakage current |       | VADIN= 0 V to VDD<br>(VADIN when<br>channel is off.)                           |     | ±.001                  | ±1                     | μA  |

| C24 | Ladder resistance               | Rladd |                                                                                | 10  | 50                     | 100                    | kΩ  |

Note) The value is applied when bp3 (ADTC) of the A/D control register ADCL is set to zero.

Relative precision:

The deviation of the converted straight line from the ideal straight line that results after both the zero transition voltage and full-scale transition voltage are adjusted to zero.

Zero transition voltage:

Indicates the difference between the analog input voltage and the nominal value when the digital output code changes from 0 (000h) to 1 (001h).

Full-scale transition voltage:

Indicates the difference between the analog input voltage and the nominal value when the digital output code (3FEh) reaches the full-scale value (3FFh).

## Ta= -40 °C to +85 °C, Vdd=1.8 V to 5.5 V (Vrstl1 or Vrstl2 to 5.5 V), Vss=0 V

| Parameter | Symbol | Conditions |     | Limits |     |      |

|-----------|--------|------------|-----|--------|-----|------|

| Falameter | Symbol | Conditions | min | typ    | max | Unit |

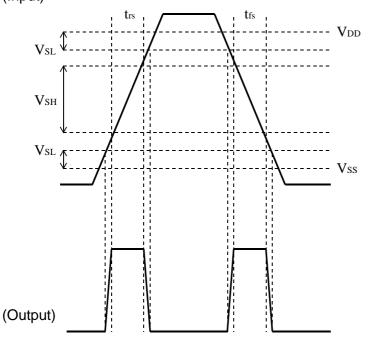

# Input Pin P31/IRQ/ACZ (When this pin is used as ACZ pin)

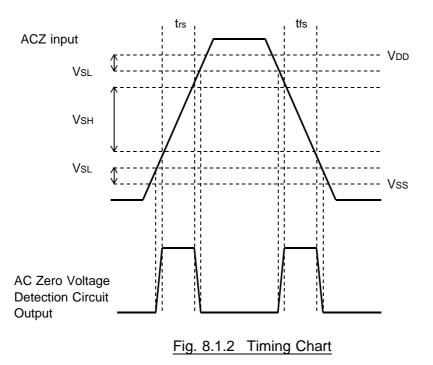

| C25 | ACZ input<br>(high-level output) | Vsн  | Fig. 5                                          | 1.5                     | V <sub>DD</sub><br>-1.5 | V  |

|-----|----------------------------------|------|-------------------------------------------------|-------------------------|-------------------------|----|

| C26 | ACZ input<br>(low-level output)  | Vsl  | V <sub>DD</sub> =4.5 V to 5.5 V                 | Vss                     | 0.5                     | v  |

|     |                                  |      |                                                 | V <sub>DD</sub><br>-0.5 | Vdd                     |    |

| C27 | Input leakage<br>current         | Іікз | Without pull-up<br>resistor<br>Vıℕ = 0 V to Vɒɒ |                         | ±1                      | μΑ |

| C28 | Input clamp<br>current           | Ісз  | Vin > Vdd<br>Vin > Vss<br>Vdd = 5.0 V           |                         | ±400                    |    |

### I/O Pin P31/ $\overline{IRQ}$ /ACZ (Schmitt input when this pin is used as $\overline{IRQ}$ pin)

| C29 | Input voltage high<br>level | VIH4        |                                                                                | 0.8Vdd |      | Vdd    | V  |

|-----|-----------------------------|-------------|--------------------------------------------------------------------------------|--------|------|--------|----|

| C30 | Input voltage low<br>level  | VIL4        |                                                                                | Vss    |      | 0.1Vdd | V  |

| C31 | Input current               | <b> </b> 14 | With pull-up<br>resistor<br>V <sub>IN</sub> = 1.5 V<br>V <sub>DD</sub> = 5.0 V | -50    | -120 | -300   | μΑ |

| C32 | Input leakage<br>current    | Ilk4        | Without pull-up<br>resistor<br>V <sub>IN</sub> = 0 V to V <sub>DD</sub>        |        |      | ±1     |    |

### I/O Pin P30/SYNC/TCI (Schmitt input when this pin is used as TCI pin)

| C33 | Input voltage high<br>level | Vih5 |                                                                                | 0.8Vdd |      | Vdd    | V  |

|-----|-----------------------------|------|--------------------------------------------------------------------------------|--------|------|--------|----|

| C34 | Input voltage low<br>level  | VIL5 |                                                                                | Vss    |      | 0.1Vdd | v  |

| C35 | Input current               | l15  | With pull-up<br>resistor<br>V <sub>IN</sub> = 1.5 V<br>V <sub>DD</sub> = 5.0 V | -50    | -120 | -300   | μΑ |

| C36 | Input leakage<br>current    | Ilk5 | Without pull-up<br>resistor<br>VIN = 0 V to VDD                                |        |      | ±1     |    |

| Ta= -40 °C to +85 °C, V <sub>DD</sub> =1.8 V to 5.5 | 5 V (VRSTL1 or VRSTL2 to 5.5 V), VSS=0 V |

|-----------------------------------------------------|------------------------------------------|

|-----------------------------------------------------|------------------------------------------|

| ataSheet | 4LLcom                      |        |                                                                                | ,      |        | ,,     |      |

|----------|-----------------------------|--------|--------------------------------------------------------------------------------|--------|--------|--------|------|

|          | Deremeter                   |        | Symbol Conditions                                                              |        | Limits |        |      |

|          | Parameter                   | Symbol | Conditions                                                                     | min    | typ    | max    | Unit |

| I/O      | Pin RST (Schmitt            | input) |                                                                                |        |        |        |      |

| C38      | Input voltage high<br>level | Vih6   |                                                                                | 0.8Vdd |        | Vdd    | V    |

| C39      | Input voltage low<br>level  | Vil6   |                                                                                | Vss    |        | 0.1Vdd | V    |

| C40      | Input current               | 116    | With pull-up<br>resistor<br>V <sub>IN</sub> = 1.5 V<br>V <sub>DD</sub> = 5.0 V | -50    | -120   | -300   | μΑ   |

| C41      | Input leakage<br>current    | Ilk6   | Without pull-up<br>resistor<br>VIN = 0 V to VDD                                |        |        | ±1     |      |

| C42      | Output voltage low level    | Vol6   | V <sub>DD</sub> = 2 V,<br>I <sub>OL</sub> = 0.3 mA                             | Vss    |        | 0.4    | V    |

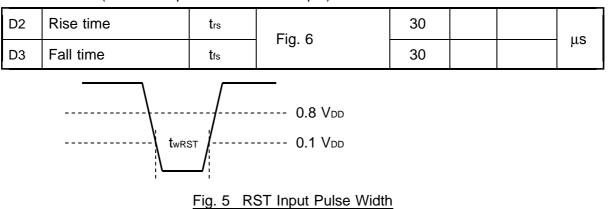

D. Electrical Characteristics (AC Characteristics) Ta= -40 °C to +85 °C, V<sub>DD</sub>=1.8 V to 5.5 V (V<sub>RSTL1</sub> or V<sub>RSTL2</sub> to 5.5 V), V<sub>SS</sub>=0 V

| Parameter | Symbol | Conditions | Limits |     |     | Unit |

|-----------|--------|------------|--------|-----|-----|------|

| Farameter | Symbol | Conditions | min    | typ | max | Onit |

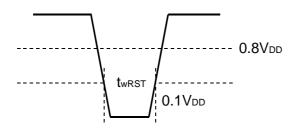

RST Pin

| D1 | Effective pulse width | twrst | Fig. 5 | 1 |  |  | mc |  |

|----|-----------------------|-------|--------|---|--|--|----|--|

|----|-----------------------|-------|--------|---|--|--|----|--|

\* The above pin may not be reset if the pulse width is shorter than the effective pulse width.

(mc: Machine cycle)

P31/IRQ/ACZ (When this pin is used as ACZ pin)

(Input) trs tfs Vdd Ŷ Vsl Vsн  $V_{\text{SL}}$ -- Vss (Output)

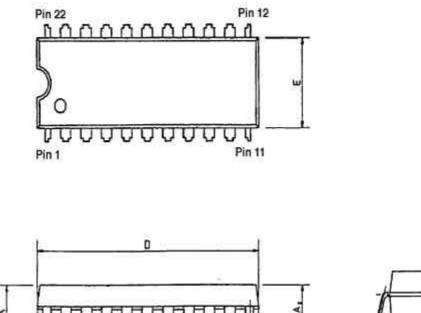

#### 1.8 Package

www.p.Package\_1

#### 12.6 ±0.20 1.10 ±0.70 20 11 F B Ħ B A H B E Н 5.50 ±0.20 7.70 ±0.30 0.15 -0.10 ..... E Ħ Ħ Ħ B E E E 10 HI 1 0 to 10\* 0.30 min 1.50 ±0.70 1.90 max THAT 11 11 11 0.10 ±0.10 (0.60) 1.27 0.40 ±0.10 SEATING PLANE SEATING PLANE

PACKAGE CODE: SOP020-P-0300

#### PACKAGE CODE: SDIP022-P-0300

| Symbol  | Dimens | ion in Will | imeters      |

|---------|--------|-------------|--------------|

| JUDUL - | min    | typ         | max          |

| A       |        |             | 4.8          |

| A,      | 0.7    |             |              |

| A, '    | 3.1    | 3.3         | 3.5          |

| D,      | 0.4    | 0.5         | 0.6          |

| b,      | 0.6    | 0.7         | 0.8          |

| b,      | 0.8    | 0.9         | 1.0          |

| C       | 0.2    | 0.25        | 0.45         |

| D       | 18.8   | 19.2        | 19.6         |

| Ε       | 6.2    | 6.4         | 6:5          |

| Ð       |        | (1.778)     |              |

| e,      | 7.42   | 7.62        | 7.82         |

| L       | 3.15   | 3.45        | 3.75         |

| 8       | 0      |             | 15(0. 262rd) |

|         |        |             | <u>)</u>     |

#### Mask Option Check List

www.DataSheet4U.com

Part No. MN150222

#### 1. Operating supply voltage range

|                   | Operating<br>voltage | Usa | ige    | Oscillatio<br>n mode     | Xta                                 | al                                   |

|-------------------|----------------------|-----|--------|--------------------------|-------------------------------------|--------------------------------------|

|                   | range                |     | Unused | Oscillator               | 32 kHz to<br>125 kHz                | 0.5 MHz to<br>8 MHz                  |

| Operating<br>mode | V to V               |     |        | frequency in lo<br>oscil | in low-speed<br>oscillation<br>mode | in high-speed<br>oscillation<br>mode |

| HALT mode         | V to V               |     |        |                          | mode                                | mode                                 |

| STOP mode         | V to V               |     |        | Remarks                  |                                     |                                      |

- 3. Auto reset function

- \* Use the LSI in auto reset function ON mode with one machine cycle set to 4.0 ms or more when V<sub>RSTL1</sub> reset voltage is selected and 8.0 ms or more when V<sub>RSTL2</sub> reset voltage is selected.

| Auto rese | et function |                    | Reset                                                               | voltage                                                             |

|-----------|-------------|--------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|

| ON        | OFF         | Mark "√" on the    | Vrstl1                                                              | Vrstl2                                                              |

|           |             | if ON is selected. | 2.0 V to 4.0 V<br>(Use the LSI at<br>normal 5-V<br>supply voltage.) | 1.2 V to 2.6 V<br>(Use the LSI at<br>normal 3-V<br>supply voltage.) |

4. Pull-up resistor at reset pin

| ON | OFF |

|----|-----|

|    |     |

6. A/D conversion function

| ON | OFF |

|----|-----|

|    |     |

#### 5. Watchdog timer function

| ON | OFF |

|----|-----|

|    |     |

7. AC zero voltage detection function

| ON | OFF |

|----|-----|

|    |     |

# 8.1 Pin Structure

| Pin name           |                                         | Function              |                       |                 |              | _         |

|--------------------|-----------------------------------------|-----------------------|-----------------------|-----------------|--------------|-----------|

| P10                |                                         | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

| P11                |                                         | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

| D40                |                                         | Output type selection | Output type selection |                 |              | Push-pull |

| P12                |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

| D40                |                                         | Output type selection |                       | N-ch open-drain |              | Push-pull |

| P13                |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

|                    | P20                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

| P20/AD0            | P20                                     | Pull-up resistor      |                       | ON              |              | OFF       |

| Note 1)            | AD0                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    |                                         | Pull-up resistor      | X                     | ON              | $\checkmark$ | OFF       |

|                    | P21                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

| P21/AD1<br>Note 1) |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

| Note I)            | AD1                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    |                                         | Pull-up resistor      | igee                  | ON              | $\checkmark$ | OFF       |

|                    | P22                                     | Output type selection |                       | N-chopen-drain  |              | Push-pull |

| P22/AD2            |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

|                    | AD2                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    | AD2                                     | Pull-up resistor      | $\boxtimes$           | ON              | $\checkmark$ | OFF       |

| P23/AD3<br>Note 1) | P23                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    |                                         | Pull-up resistor      |                       | ON              |              | OFF       |

|                    | AD3                                     | Output type selection |                       | N-ch open-drain |              | Push-pull |

|                    | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Pull-up resistor      | $\mid$                | ON              | $\checkmark$ | OFF       |

Note 1) A pull-up resistor cannot be connected to the pin when AD pin is selected on PTAD2-0 of ADCH X 'A' , A/D Control Register.

### 8.2 Pin Structure

| Pin name               | Function              |  |                 |           |

|------------------------|-----------------------|--|-----------------|-----------|

| P30/SYNC/TCI           | Output type selection |  | N-ch open-drain | Push-pull |

|                        | Pull-up resistor      |  | ON              | OFF       |

| P31/IRQ/ACZ<br>Note 2) | Output type selection |  | N-ch open-drain | Push-pull |

|                        | Pull-up resistor      |  | ON              | OFF       |

| P32/TCO/BZ             | Output type selection |  | N-ch open-drain | Push-pull |

|                        | Pull-up resistor      |  | ON              | OFF       |

Note 2) A pull-up resistor cannot be connected when the AC zero voltage detection function is used.

### CHAPTER 2 CPU CORE FUNCTIONS

ww.DataSheet4U.com

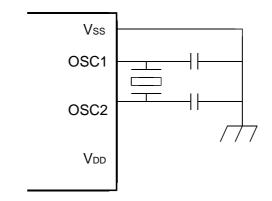

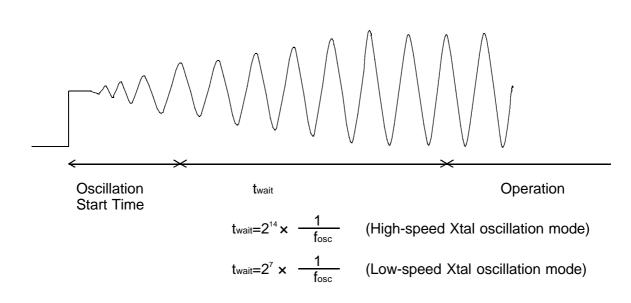

2.1 Clock Generator and CPU Basic Timing

This LSI incorporates the system clock oscillation circuits (OSC1 and OSC2). The circuit has an oscillation element and capacitors connected externally. A Xtal oscillator or a ceramic oscillator is utilized as the oscillation element.

When mounting the LSI on PCB, design a pattern so that the oscillation elements and capacitors will be arranged as physically close to the LSI as possible.

Also provide a thick ground line that can be connected to Vss with the LSI at the shortest distance possible. Note that long wiring pattern is susceptible to noise interference and results in unstable oscillation. Fig. 2.1.1 shows a connection diagram. Optimum values for the capacitors differ depending on the oscillator used. Use the values specified by each oscillator maker.

Fig. 2.1.1 Oscillation Circuit Connection Diagram

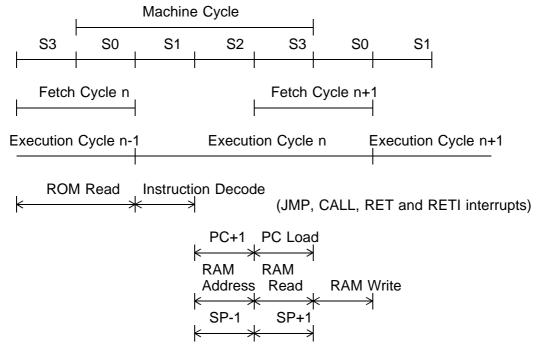

This LSI constitutes a machine cycle (state) with 4-phase clocks, S0, S1, S2 and S3, generated from the oscillation source (OSC1 and OSC2). One machine cycle is  $1.0 \ \mu s$  when oscillation source, fosc, is  $8.0 \ MHz$ .

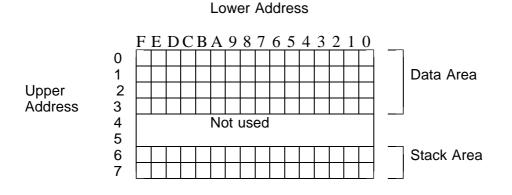

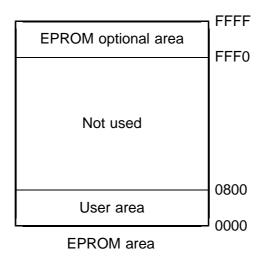

This LSI has a 2-Kbyte instruction memory space (ROM) to store instructions, and a 96-nibble (including a 32-nibble stack area) data memory space (RAM) to store data separately from each other.

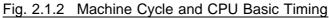

Fig. 2.2.1 shows the ROM address space and Fig. 2.2.2 shows the RAM address space.

Fig. 2.2.2 RAM Address Space

#### 2.3 Stack Area

ww.DataSheet4U.com

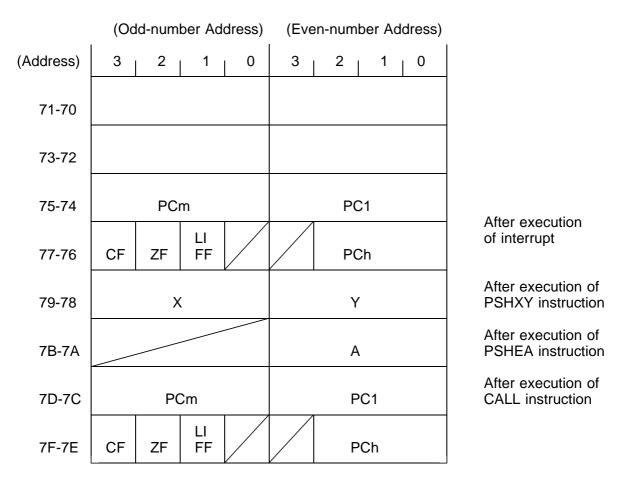

This LSI has assigned as a stack area the addresses (6, 0) to (7, F) in the RAM area. The stack area is used to save the PC (Program Counter), flag statuses (ZF and CF) and A, X and Y registers at the time of the CALL instruction, PSH instruction or an interrupt. When the entire stack area is not used, it is also available as regular RAM. When only the CALL instruction is executed, up to 8 levels can be used.

Fig. 2.3.1 shows the stack condition when the CALL instruction, PSH instruction or an interrupt sequence is executed.

Fig. 2.3.1 Stack Area Condition

- Note 1) At reset time, the SP (Stack Pointer) points to 60. The stack data are used sequentially, starting at address 7F to 60.

- Note 2) The RET instruction does not return the flags (CF, ZF and LIFF). Only the RETI instruction is returned.

- Note 3) LIFF: This is FF to memorize that the instruction just before was LI. It is used for an LI instruction stacking function.

- Note 4) The values in the oblique-lined cells in Fig. 2.3.1 are indefinite.

#### 2.4 Flag Status

ww.DataSheet4U.com

The flag status is composed of a 2-bit register consisting of the arithmetic flags, that is, carry flag (CF) and zero flag (ZF). CF is set when an arithmetic result of the ALU overflows or underflows, or is otherwise reset. ZF is set when the arithmetic result of the ALU is zero, or is otherwise reset.

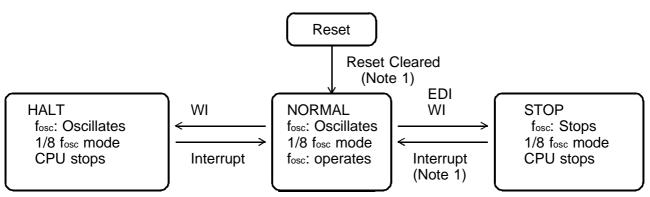

2.5 Backup Mode

In order to reduce power consumption, there are two kinds of backup modes provided, which can be controlled by the program.

- HALT mode: The system clock frequency divider is operating. However, system clock is not supplied. It is returned by a reset operation or an interrupt.

- STOP mode: The power consumption can be reduced further because the system clock frequency divider is also stopped. As with the HALT mode, it is returned by a reset operation or an interrupt. (Software option)

Table 2.5.1 shows the STOP and HALT functions.

| Mode<br>Operation        | STOP                                                                                                                                | HALT                                                                                                                                                                                                                                          |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operating condition      | <ol> <li>The system clock oscillation circuit stops.</li> </ol>                                                                     | <ol> <li>The system clock oscillation circuit<br/>is operating.<br/>(System clock frequency divider<br/>is operating. However, system<br/>clock is not supplied.)</li> </ol>                                                                  |  |  |

|                          | <ul> <li>2) Timer/Counter</li> <li>It is operating in event count mode.</li> <li>It is stopped in timer mode.</li> </ul>            | <ul> <li>2) Timer/Counter <ul> <li>It is operating in event count mode.</li> <li>It is operating when the clock is fosc/2<sup>14</sup> in timer mode.</li> <li>It is operating when the clock is fsys/2 in timer mode.</li> </ul> </li> </ul> |  |  |

| 3) Time base is stopped. |                                                                                                                                     | 3) Time base is operating.                                                                                                                                                                                                                    |  |  |

| Register/RAM condition   | Holds the contents of the RAM and all registers.                                                                                    |                                                                                                                                                                                                                                               |  |  |

| Mode setting method      | Executes a WI instruction just after an EDI instruction.<br>(Refer to Example: 2.5.1.)                                              | Executes the WI instruction after an instruction other than an EDI instruction. (Refer to Example: 2.5.2.)                                                                                                                                    |  |  |

| Return                   | <ul> <li>Interrupt: Identical operation with a normal interrupt</li> <li>Reset : Identical operation with a normal reset</li> </ul> |                                                                                                                                                                                                                                               |  |  |

#### Table 2.5.1 STOP and HALT Functions

Example: 2.5.1 Using the STOP Mode

1

| ED 0.4<br>WI | Exits from the STOP mode when an IRQ (external interrupt) occurs.                                       |

|--------------|---------------------------------------------------------------------------------------------------------|

| NOP          | Be sure to insert one or more NOPs next to the EDI and WI instructions in order to stabilize operation. |

Note) Following is an interrupt which enables return from the STOP mode.

IRQ (External interrupt, ACZ interrupt or timer in the event count mode.)

#### Example: 2.5.2 Using the HALT Mode

www.DataSheet4U.com

EDI 0.4 Returns from the HALT mode when an interrupt occurs. (Instruction other than EDI instruction)

WI NOP

Note) Be sure to insert one or more NOPs next to the WI instruction. The currently provided cross assembler inserts an NOP automatically.

Table 2.5.2 shows the comparison of STOP and HALT modes.

|           | OSC          | IRQ        | CPU | RESET        |

|-----------|--------------|------------|-----|--------------|

| STOP mode | -            | ✓ (Note 1) | -   | $\checkmark$ |

| HALT mode | $\checkmark$ | √ (Note 2) | -   | $\checkmark$ |

Table 2.5.2 STOP and HALT Modes Comparison Table

✓ : Operates - : Stops

Unless the MASKIR bit is set to zero, IRQ does not operate.

- Note 1) The timer interrupt function operates in event count mode and does not operate in timer mode. The time base interrupt function does not operate in STOP mode.

- Note 2) The timer interrupt function operates in event count mode or timer mode with the clock source of fosc/2<sup>14</sup> selected but does not operate in timer mode with the clock source of fsys/2 selected. The time base interrupt function, however, operates.

Precautions for using the Backup Mode

- www.DataSheet4U.com

- 1. Handling of the output ports

In the backup mode, the port level can be made floating in order to reduce power consumption at the output ports. The port status can be set by controlling the corresponding bit of the control register. (Refer to Table 2.5.3.)

### Table 2.5.3 Interrupt Mode Register (CPUM: X'4' R/W) versus Output Ports

| HIZC | Port Status                                                                                                                         |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | All output pins are floating (Hi-Z)<br>Note) The voltage level is set to "H" if a pull-up<br>resistor is selected as a mask option. |  |  |  |

| 0    | Normal output                                                                                                                       |  |  |  |

(Set to "1" in RESET mode)

2. Handling of the input ports

A pull-up resistor for the input port should be specified according to the external circuit voltage level in the backup operation, in order to reduce power consumption at the port. Set the input port voltage level externally so that it will be turned to either "L" or "H" level in the backup operation. When the port is at the middle level, a current flows internally and the microcomputer consumes more power.

3. Return from the STOP mode

When the supply voltage is less than 1.8 V at the time of return, the RAM data cannot be guaranteed after return. If this is the case, reset by means of an external circuit or use the auto reset function.

4. Handling of the I/O ports

After first setting to the Hi-Z state, set the I/O ports externally so that the pin levels will be turned to "L" or "H" level. When they are at the middle level, the microcomputer consumes more power.

5. Handling of the A/D Control Registor

Setting from outside is not needed when A/D input is unused on AD, because P2 input gate is fixed to stop feedthrough current. The pin which selects AD cannot be connected to a pull-up resistor as a mask option.

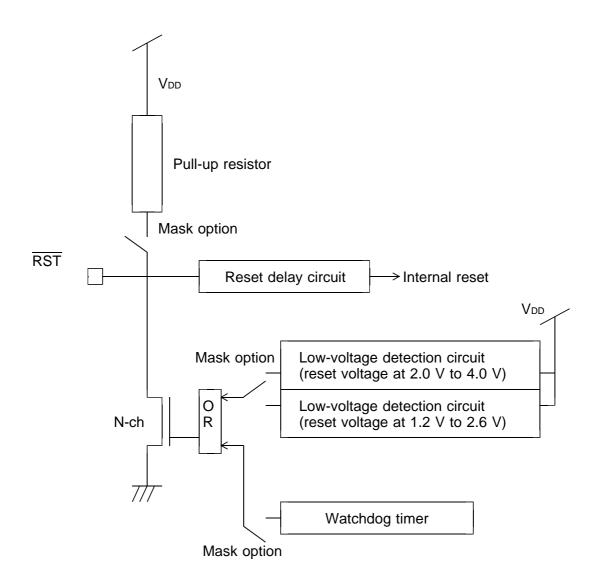

### 2.6 Reset

ww.DataSheet4U.com

The LSI is reset with the  $\overline{RST}$  pin set to "L" level. When the LSI is reset, the register and outp<u>ut port latch are initialized as shown in table 2.6.1</u>.

The RST pin should be set to "L" level for a machine cycle or more for stabilized reset operation, otherwise the LSI may not be reset.

| Register/Memory | Symbol | Initial Value | Register/Memory       | Symbol | Initial Value |

|-----------------|--------|---------------|-----------------------|--------|---------------|

| Program counter | PC     | $\checkmark$  | Interrupt accept flag | IF     | $\checkmark$  |

| Accumulator     | А      | $\checkmark$  | intorrupt             |        | Disabled      |

| Register X      | х      | $\checkmark$  | enable/disable flag   |        |               |

| Register Y      | Y      | ✓             | Output port latch     |        | 1             |

|                 | 1      | •             | I/O register          | IR     | 1             |

| Carry flag      | CF     | $\checkmark$  | <i>"с.с.</i>          |        |               |

| Zero flag       | ZF     | $\checkmark$  |                       |        |               |

| RAM             |        | Indefinite    |                       |        |               |

| Stack pointer   | SP     | 60            |                       |        |               |

Table 2.6.1 Initial Values of Registers and Data Memories

[Reset Clearing Timing]