MICROCOMPUTER

MN15G

MN15G0202/0402 LSI User's Manual

Pub.No.20302-020E

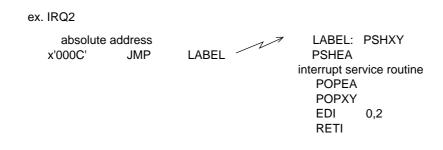

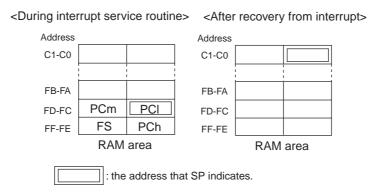

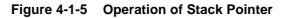

Panasonic

PanaXSeries is a trademark of Matsushita Electric Industrial Co., Ltd. The other corporation names, logotype and product names written in this book are trademarks or registered trademarks of their corresponding corporations.

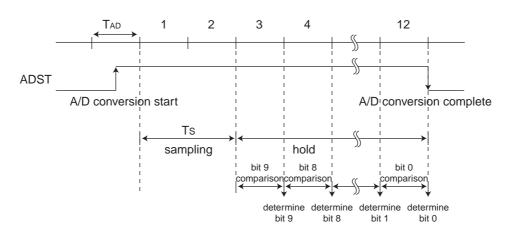

#### Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this book and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The contents of this book are subject to change without notice in matters of improved function. When finalizing your design, therefore, ask for the most up-to-date version in advance in order to check for any changes.

- (3) We are not liable for any damage arising out of the use of the contents of this book, or for any infringement of patents or any other rights owned by a third party.

- (4) No part of this book may be reprinted or reproduced by any means without written permission from our company.

- (5) This book deals with standard specification. Ask for the latest individual Product Standard or Specifications in advance for more detailed information required for your design, purchasing and applications.

If you have any inquiries or questions about this book or our semiconductors, please contact one of our sales offices listed at the back of this book.

## **About This Manual**

#### Organization

In this LSI manual, this LSI functions are presented in the following order : overview, basic CPU functions, interrupt functions, port functions, timer functions, serial functions, and other peripheral hardware functions. Each section contains overview of function, block diagram, control register, operation, and setting example.

#### Manual Configuration

Each section of this manual consists of a title, summary, main text, key information, precautions and warnings, and references.

The layout and definition of each section are shown below.

#### Finding Desired Information

This manual provides three methods for finding desired information quickly and easily.

- (1) Consult the index at the front of the manual to locate the beginning of each section.

- (2) Consult the table of contents at the front of the manual to locate desired titles.

- (3) Chapter names are located at the top outer corner of each page, and section titles are located at the bottom outer corner of each page.

#### Related Manuals

Note that the following related documents are available.

"MN1500 Series Instruction Manual"

<Describes the instruction set.>

"MN1500 Series Cross-assembler User's Manual"

<Describes the assembler syntax and notation.>

"MN1500 Series Source Code Debugger User's Manual"

<Describes the use of source code debugger.>

"MN1500 Series PanaX Series Installation Manual"

<Describes the installation of cross-assembler and source code debugger and the procedure for bringing up the in-circuit emulator.>

#### ■Where to Send Inquires

We welcome your questions, comments, and suggestions. Please contact the semiconductor design center closest to you. See the last page of this manual for a list of addresses and telephone numbers.

| Chapter 1  | Overview                   | 1  |

|------------|----------------------------|----|

| Chapter 2  | Basic CPU                  | 2  |

| Chapter 3  | Ports                      | 3  |

| Chapter 4  | Interrupts                 | 4  |

| Chapter 5  | Timers                     | 5  |

| Chapter 6  | A/D Converter              | 6  |

| Chapter 7  | AC Zero-Cross<br>Detection | 7  |

| Chapter 8  | Watchdog Timer             | 8  |

| Chapter 9  | Automatic Reset            | 9  |

| Chapter 10 | Appendices                 | 10 |

# Contents

## Chapter 1 Overview

| 1-1 | Overviev  | v I - 2                              |

|-----|-----------|--------------------------------------|

|     | 1-1-1     | Product Summary I - 2                |

| 1-2 | Hardware  | e Functions I - 3                    |

| 1-3 | Block Di  | agram I - 5                          |

|     | 1-3-1     | Overview I - 5                       |

|     | 1-3-2     | Block Diagram I - 6                  |

| 1-4 | Pin Desc  | ription I - 7                        |

|     | 1-4-1     | Pin Configuration I - 7              |

|     | 1-4-3     | Pin Functions I - 8                  |

| 1-5 | Special F | Function Registers I - 11            |

|     | 1-5-1     | Register Map I - 11                  |

|     | 1-5-2     | Special Function Registers I - 12    |

| 1-6 | Electrica | I Characteristics I - 13             |

|     | 1-6-1     | Absolute Maximum Ratings I - 13      |

|     | 1-6-2     | Operating Conditions I - 14          |

|     | 1-6-3     | DC Characteristics I - 18            |

|     | 1-6-4     | A/D Converter Characteristics I - 22 |

| 1-7 | External  | Dimension I - 23                     |

| 1-8 | Option    |                                      |

|     | 1-8-1     | Mask Option I - 24                   |

|     | 1-8-2     | Mask Option Form (Ver. 0.05) I - 25  |

## Chapter 2 Basic CPU

| 2-1 | Clock Ge   | nerator                  | II - 2  |

|-----|------------|--------------------------|---------|

|     | 2-1-1      | Clock Generator          | II - 2  |

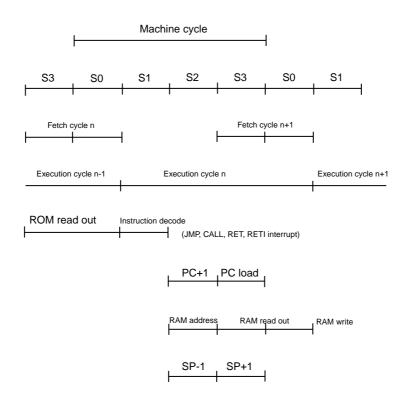

|     | 2-1-2      | CPU Basic Timing         | II - 3  |

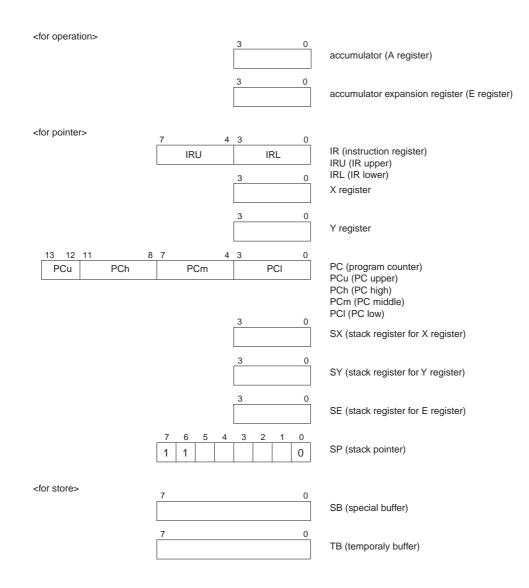

| 2-2 | Register S | Set                      | II - 4  |

| 2-3 | Memory     | Space                    | II - 8  |

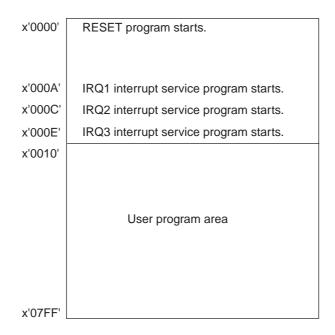

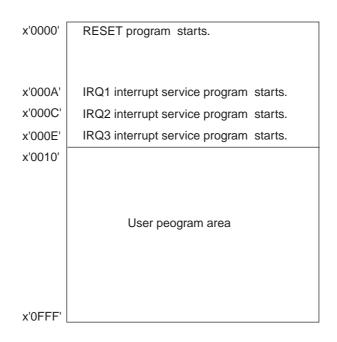

|     | 2-3-1      | ROM Address Space (2 KB) | II - 8  |

|     | 2-3-2      | ROM Address Space (4 KB) | II - 10 |

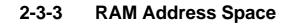

|     | 2-3-3      | RAM Address Space        | II - 12 |

|     | 2-3-4      | Stacked Area             | II - 13 |

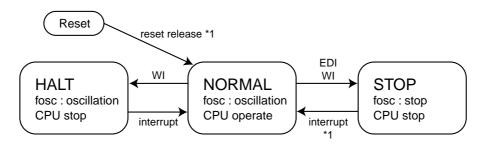

| 2-4 | Clock Sw   | vitching                 | II - 14 |

|     | 2-4-1      | Clock Switching          | II - 14 |

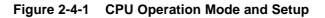

|     | 2-4-2      | CPU Mode Reigster        | II - 15 |

| 2-5 | Back Up | Mode                     | II - 16 |

|-----|---------|--------------------------|---------|

|     | 2-5-1   | Cautions on Back Up Mode | II - 18 |

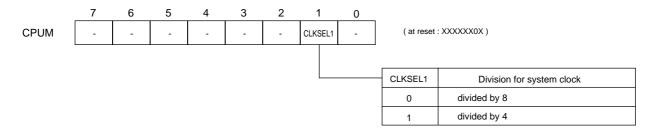

| 2-6 | Reset   |                          | II - 19 |

|     | 2-6-1   | Reset Operation          | II - 19 |

## Chapter 3 Ports

| 3-1 | Overview   | ,                       | III - 2  |

|-----|------------|-------------------------|----------|

|     | 3-1-1      | Port Diagram            | III - 2  |

|     | 3-1-2      | Port Functions          | III - 3  |

|     | 3-1-3      | Port Status at Reset    | III - 4  |

|     | 3-1-4      | Port Disposal at Unused | III - 5  |

|     | 3-1-5      | Setup Example           | III - 6  |

|     | 3-1-6      | Control Registers       | III - 7  |

| 3-2 | Port 0, Po | ort 1                   | III - 8  |

|     | 3-2-1      | Description             | III - 8  |

|     | 3-2-2      | Registers               | III - 9  |

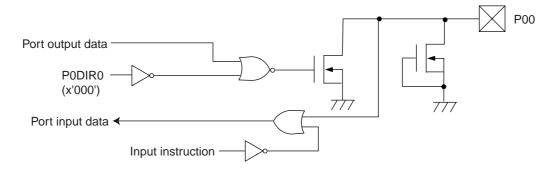

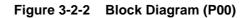

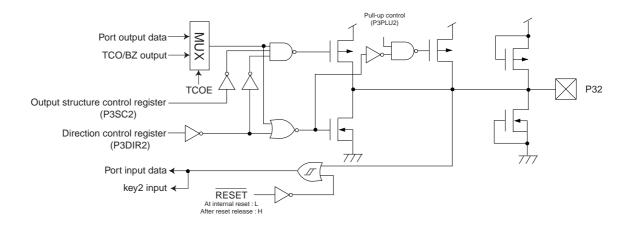

|     | 3-2-3      | Block Diagram           | III - 10 |

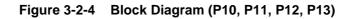

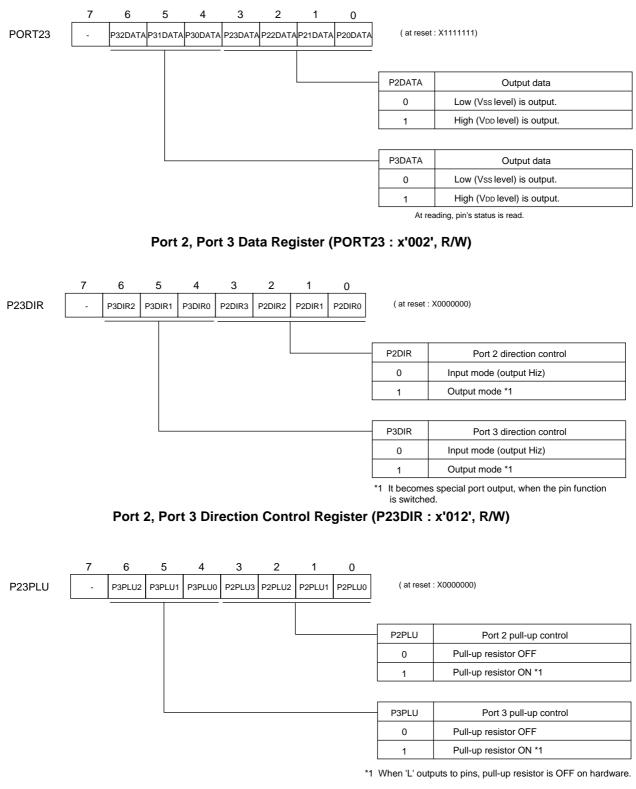

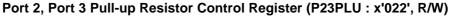

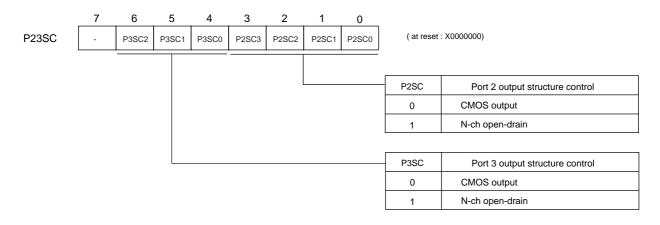

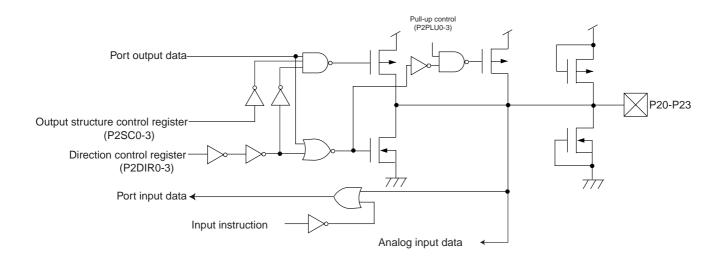

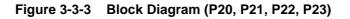

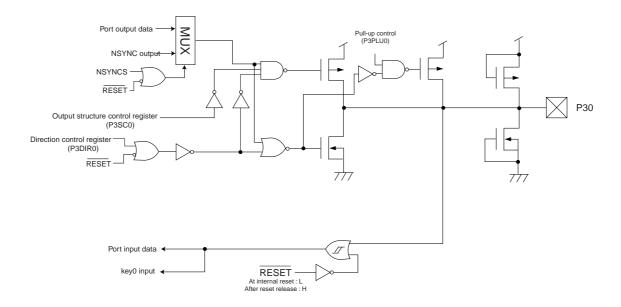

| 3-3 | Port 2, Po | ort 3                   | III - 11 |

|     | 3-3-1      | Description             | III - 11 |

|     | 3-3-2      | Registers               | III - 13 |

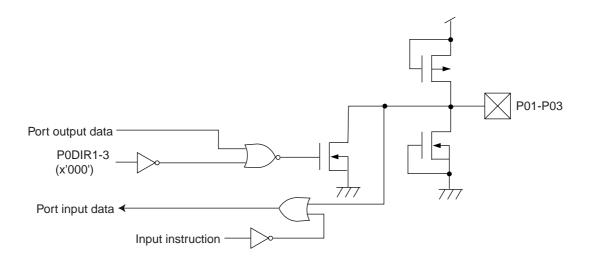

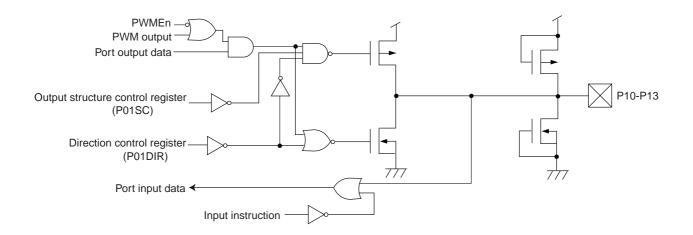

|     | 3-3-3      | Block Diagram           | III - 15 |

|     |            |                         |          |

## Chapter 4 Interrupts

| 4-1 | Overview  | 7                           | IV - 2  |

|-----|-----------|-----------------------------|---------|

|     | 4-1-1     | Functions                   | IV - 2  |

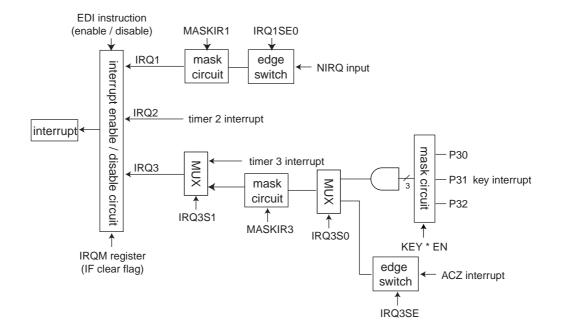

|     | 4-1-2     | Block Diagram               | IV - 3  |

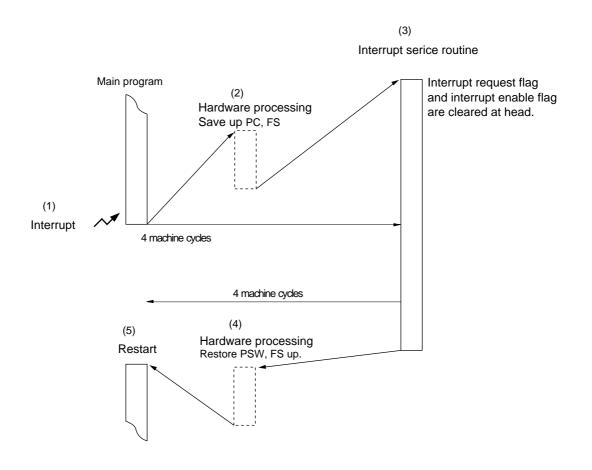

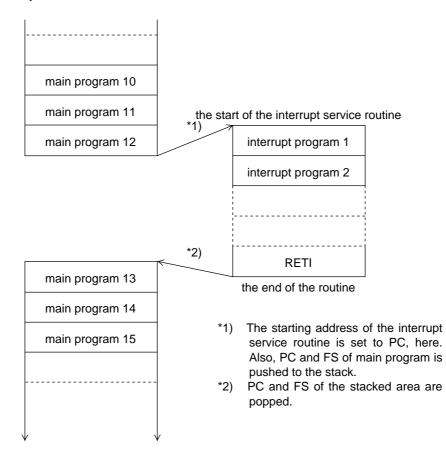

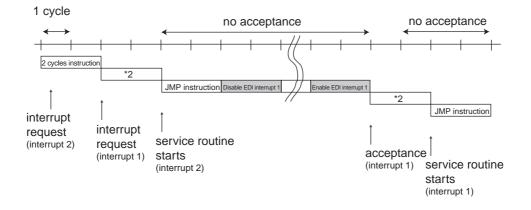

|     | 4-1-3     | Operation                   | IV - 4  |

|     | 4-1-4     | Interrupt Flag Setup        | IV - 13 |

| 4-2 | Control R | egisters                    | IV - 15 |

|     | 4-2-1     | Registers List              | IV - 15 |

|     | 4-2-2     | Interrupt Control Registers | IV - 16 |

|     |           |                             |         |

## Chapter 5 Timers

| 5-1 | 8-bit Timer                   |               |       |

|-----|-------------------------------|---------------|-------|

|     | 5-1-1                         | Functions     | V - 3 |

|     | 5-1-2                         | Block Diagram | V - 4 |

| 5-2 | 8-bit Timer Control Registers |               | V - 8 |

| 5-2-1     | Registers                                                                                                                                                                                                                            | V - 8                                                                                       |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 5-2-2     | Compare Registers                                                                                                                                                                                                                    | V - 9                                                                                       |

| 5-2-3     | Binary Counters                                                                                                                                                                                                                      | V - 10                                                                                      |

| 5-2-4     | Timer Control Registers                                                                                                                                                                                                              | V - 11                                                                                      |

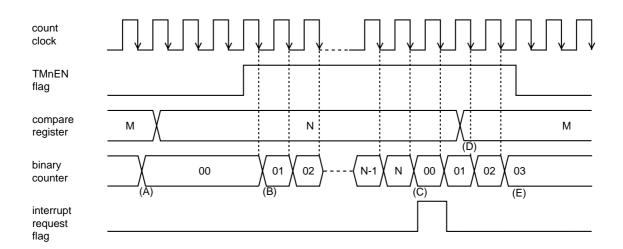

| 8-Bit Tim | er Operation                                                                                                                                                                                                                         | V - 15                                                                                      |

| 5-3-1     | Operation                                                                                                                                                                                                                            | V - 15                                                                                      |

| 5-3-2     | Setup Example                                                                                                                                                                                                                        | V - 17                                                                                      |

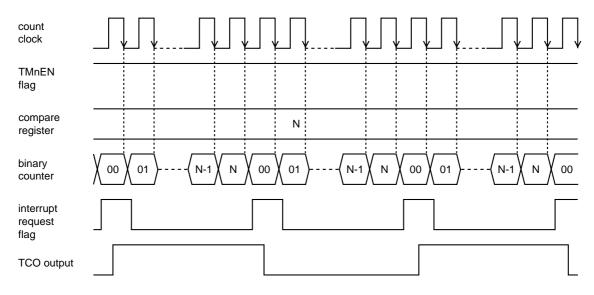

| 8-Bit Tim | er Pulse Output                                                                                                                                                                                                                      | V - 18                                                                                      |

| 5-4-1     | Operation                                                                                                                                                                                                                            | V - 18                                                                                      |

| 5-4-2     | Setup Example                                                                                                                                                                                                                        | V - 19                                                                                      |

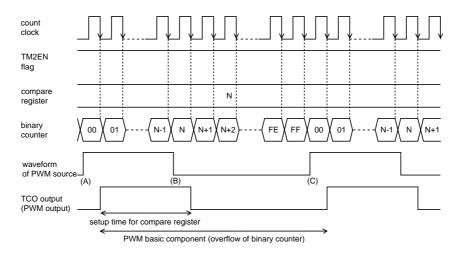

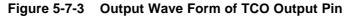

| 8-Bit PW  | M Output                                                                                                                                                                                                                             | V - 21                                                                                      |

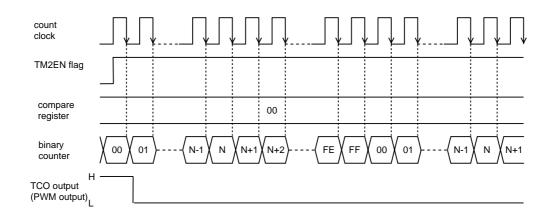

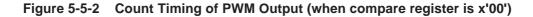

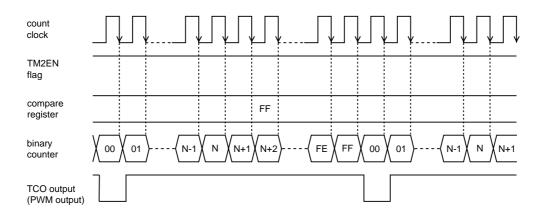

| 5-5-1     | Operation                                                                                                                                                                                                                            | V - 21                                                                                      |

| 5-5-2     | Setup Example                                                                                                                                                                                                                        | V - 23                                                                                      |

| 8-Bit Tim | er Cascade Connection                                                                                                                                                                                                                | V - 25                                                                                      |

| 5-6-1     | Operation                                                                                                                                                                                                                            | V - 25                                                                                      |

| 5-6-2     | Setup Example                                                                                                                                                                                                                        | V - 26                                                                                      |

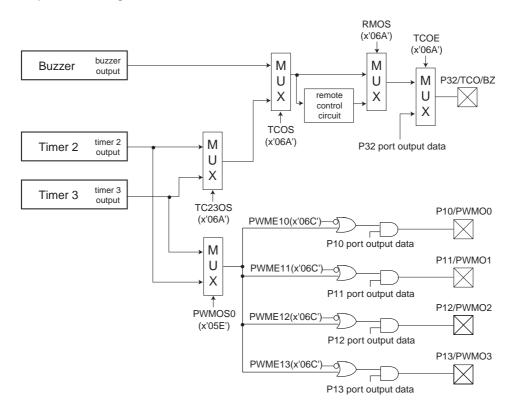

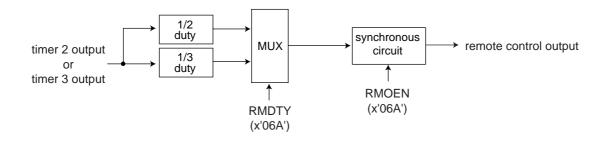

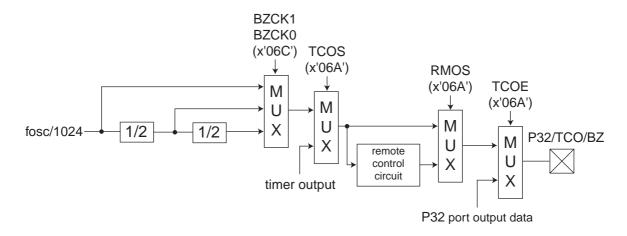

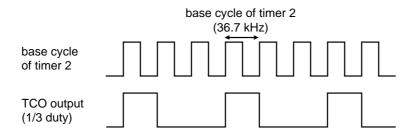

| Remote C  | Control Career Output                                                                                                                                                                                                                | V - 28                                                                                      |

| 5-7-1     | Operation                                                                                                                                                                                                                            | V - 28                                                                                      |

| 5-7-2     | Setup Example                                                                                                                                                                                                                        | V - 29                                                                                      |

| High Prec | cision PWM Output                                                                                                                                                                                                                    | V - 31                                                                                      |

| 5-8-1     | Operation                                                                                                                                                                                                                            | V - 31                                                                                      |

| 5-8-2     | Setup Example                                                                                                                                                                                                                        | V - 32                                                                                      |

| Buzzer O  | utput                                                                                                                                                                                                                                | V - 34                                                                                      |

| 5-9-1     | Operation                                                                                                                                                                                                                            | V - 34                                                                                      |

| 5-9-2     | Setup Example                                                                                                                                                                                                                        | V - 35                                                                                      |

|           | 5-2-2<br>5-2-3<br>5-2-4<br>8-Bit Tim<br>5-3-1<br>5-3-2<br>8-Bit Tim<br>5-4-1<br>5-4-2<br>8-Bit PW<br>5-5-1<br>5-5-2<br>8-Bit Tim<br>5-6-1<br>5-6-2<br>Remote C<br>5-7-1<br>5-7-2<br>High Prec<br>5-8-1<br>5-8-2<br>Buzzer O<br>5-9-1 | 5-2-2Compare Registers5-2-3Binary Counters5-2-4Timer Control Registers8-Bit Timer Operation |

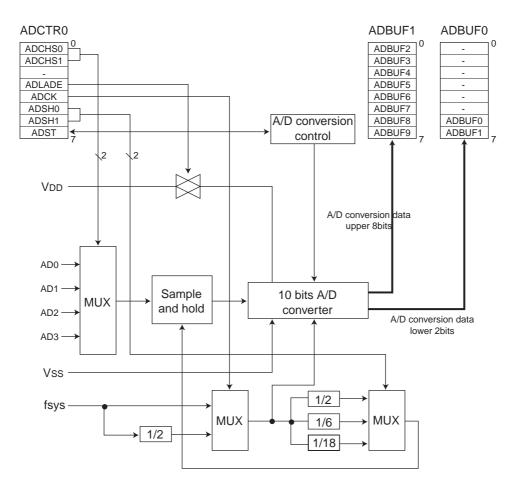

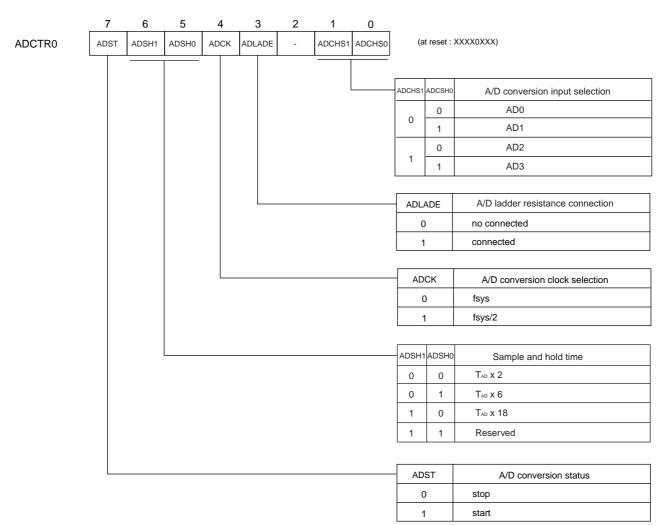

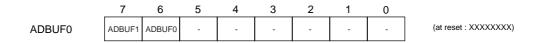

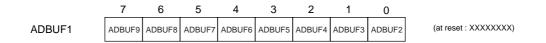

## Chapter 6 A/D Converter

| 6-1 | Overview  | ·                 | VI - 2  |

|-----|-----------|-------------------|---------|

|     | 6-1-1     | Functions         | VI - 2  |

|     | 6-1-2     | Block Diagram     | VI - 3  |

| 6-2 | Control R | egisters          | VI - 4  |

|     | 6-2-1     | Registers         | VI - 4  |

|     | 6-2-2     | Control Registers | VI - 5  |

|     | 6-2-3     | Data Buffers      | VI - 6  |

| 6-3 | Operation | l                 | VI - 7  |

|     | 6-3-1     | Setup             | VI - 9  |

|     | 6-3-2     | Setup Example     | VI - 11 |

|     | 6-3-3     | Cautions          | VI - 12 |

### Chapter 7 AC Zero-Cross Detection

| 7-1 | Overview  |               | VII - 2 |

|-----|-----------|---------------|---------|

|     | 7-1-1     | Overview      | VII - 2 |

|     | 7-1-2     | Block Diagram | VII - 3 |

|     | 7-1-3     | Operation     | VII - 4 |

| 7-2 | Control R | egisters      | VII - 5 |

## Chapter 8 Watchdog Timer

| 8-1 | Overview             |               | VIII - 2 |

|-----|----------------------|---------------|----------|

|     | 8-1-1                | Overview      | VIII - 2 |

|     | 8-1-2                | Block Diagram | VIII - 3 |

| 8-2 | -2 Control Registers |               | VIII - 4 |

### Chapter 9 Automatic Reset

| 9-1 | Overview |                            | IX -   | • 2 |

|-----|----------|----------------------------|--------|-----|

|     | 9-1-1    | Overview                   | . IX - | • 2 |

|     | 9-1-2    | Electrical Characteristics | . IX - | . 3 |

### Chapter 10 Appendices

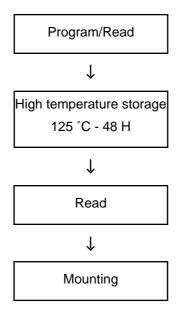

| 10-1 | EPROM '                                    | Version                                                | X - 2  |  |  |  |

|------|--------------------------------------------|--------------------------------------------------------|--------|--|--|--|

|      | 10-1-1                                     | Overview                                               | X - 2  |  |  |  |

|      | 10-1-2                                     | Cautions on Use                                        | X - 3  |  |  |  |

|      | 10-1-3                                     | Differences between Mask ROM version and EPROM version | X - 4  |  |  |  |

|      | 10-1-4                                     | Writing to Microcomputer with Internal EPROM           | X - 5  |  |  |  |

|      | 10-1-5                                     | Cautions on Operation of ROM Writer                    | X - 6  |  |  |  |

| 10-2 | Instructio                                 | n Set                                                  | X - 7  |  |  |  |

| 10-3 | Instructio                                 | n Map                                                  | X - 9  |  |  |  |

| 10-4 | Differences between MN1500 and MN15G X - 1 |                                                        |        |  |  |  |

| 10-5 | Special Function Registers List X - 1      |                                                        |        |  |  |  |

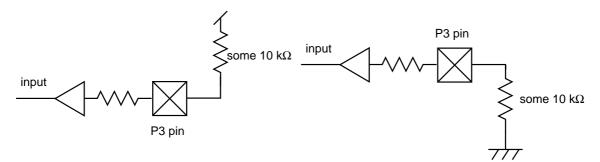

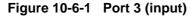

| 10-6 | Circuit Se                                 | etup                                                   | X - 13 |  |  |  |

|      | 10-6-1                                     | General Usage                                          | X - 13 |  |  |  |

|      | 10-6-2                                     | Unused Pins                                            | X - 14 |  |  |  |

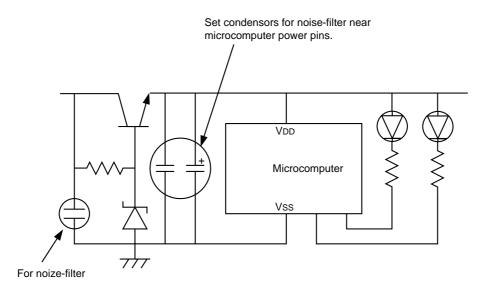

|      | 10-6-3                                     | Power Supply                                           | X - 16 |  |  |  |

|      | 10-6-4                                     | Power Supply Circuit                                   | X - 17 |  |  |  |

|      |                                            |                                                        |        |  |  |  |

Chapter 1 Overview

### 1-1 Overview

This LSI is 4-bit single-chip microcomputer. The MN15G0202 has an internal 2 KB of ROM and 128 nibble of RAM and the MN15G0402 has an internal 4 KB of ROM and 128 nibble of RAM. Peripheral functions include 2 sets of 8-bit timer counters (They can be used as 16-bit counter on cascade connection.), 10-bit A/D converter, AC zero-cross detection circuit, buzzer output circuit and LED driver pins.

### 1-1-1 Product Summary

This manual describes the following models of the MN15GXX02 series. These products have identical functions.

| Model        | ROM Size | RAM Size   | Classification   |

|--------------|----------|------------|------------------|

| MN15G0202    | 2 KB     | 128 nibble | Mask ROM version |

| MN15G0402    | 4 KB     | 128 nibble | Mask ROM version |

| MN15GP0402SJ | 4 KB     | 128 nibble | EPROM version    |

Table 1-1-1

Product Summary

| Parar                         | neter                      | MN15G0202                                                    | MN15G0402                                                    | MN15GP0402SJ     |

|-------------------------------|----------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------------------|

| Power sup                     | ply voltage                | 2.0 V to 5.5 V                                               | 2.0 V to 5.5 V                                               | 2.3 V to 5.5 V   |

| Ambient operating temperature |                            | -40 °C to +85 °C                                             | -40 °C to +85 °C                                             | -20 °C to +70 °C |

| Mask option                   | Automatic reset<br>circuit | 1 : unused<br>2 : Automatic reset 1<br>3 : Automatic reset 2 | 1 : unused<br>2 : Automatic reset 1<br>3 : Automatic reset 2 | 1 : unused       |

For mask option, refer to 1-8 Option.

# **1-2 Hardware Functions**

| Model       | MN15G0202 MN15G0402 |               | MN15GP0402 |

|-------------|---------------------|---------------|------------|

| ROM version | Mask RO             | EPROM version |            |

| ROM         | 2 KB                | 4KB           | 4KB        |

| RAM         | 128 nibble          | 128 nibble    | 128 nibble |

#### Table 1-2-1 Basic Specification

#### Package 20SOP

| Machine cycle   | le When automatic reset is not used : |                  |                                         |  |

|-----------------|---------------------------------------|------------------|-----------------------------------------|--|

|                 | 0.50 µs / 8 MHz                       | divided by 4     | (3.0 V to 5.5 V)                        |  |

|                 | 1.00 µs/ 4 MHz                        | divided by 4     | (2.4 V to 5.5 V)                        |  |

|                 | 2.00 µs/ 4 MHz                        | divided by 8     | (2.0 V to 5.5 V)                        |  |

|                 | When automatic reset circ             | uit 1 is used :  |                                         |  |

|                 | 0.50 µs / 8 MHz                       | divided by 4     | $(V_{RSTL1} \text{ to } 5.5 \text{ V})$ |  |

|                 | 1.00 µs/ 4 MHz                        | divided by 4     | (V <sub>RSTL1</sub> to 5.5 V)           |  |

|                 | 2.00 µs/ 4 MHz                        | divided by 8     | (V <sub>RSTL1</sub> to 5.5 V)           |  |

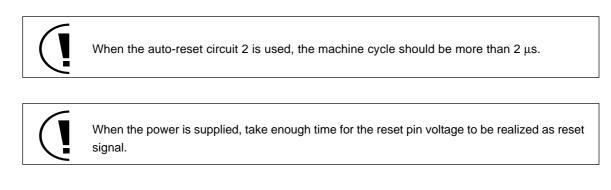

|                 | When automatic reset circ             | uit 2 is used :  |                                         |  |

|                 | 2.00 µs / 4 MHz                       | divided by 8     | $(V_{RSTL2} \text{ to } 5.5 \text{ V})$ |  |

|                 |                                       |                  |                                         |  |

| Back up mode    | HALT mode                             |                  |                                         |  |

|                 | STOP mode                             |                  |                                         |  |

|                 |                                       |                  |                                         |  |

| Ambient operati | ng temperature                        |                  |                                         |  |

|                 | -40 °C to +85 °C                      |                  |                                         |  |

|                 | (-20 °C to +70                        | °C for MN15GP040 | 2SJ)                                    |  |

| Interrupts      | 3 levels                              |                  |                                         |  |

|                 | - Interrupt 1 (IRQ1)                  |                  |                                         |  |

|                 | - Interrupt 2 (IRQ2)                  |                  |                                         |  |

|                 | - Interrupt 3 (IRQ3)                  |                  |                                         |  |

|                 |                                       |                  |                                         |  |

| Timers / Counter | Timers / Counters                                                 |                                                      |  |  |  |  |

|------------------|-------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|

|                  | 3 timers                                                          |                                                      |  |  |  |  |

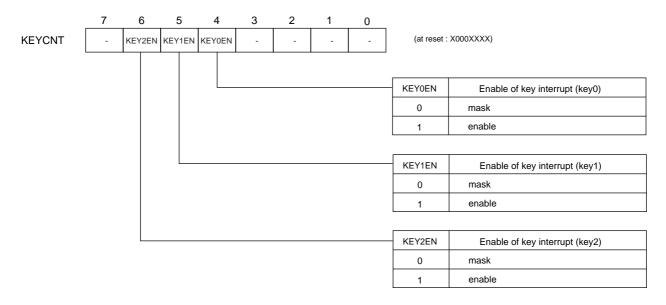

|                  | Timer 2 ( 8-Bit timer for general use )                           |                                                      |  |  |  |  |

|                  |                                                                   | itput, Remote control carrier output                 |  |  |  |  |

|                  | - Clock source                                                    |                                                      |  |  |  |  |

|                  | fsys/2, fsys/8, fsys/32, fsys/128, fosc, fosc/4, fosc/16, fosc/64 |                                                      |  |  |  |  |

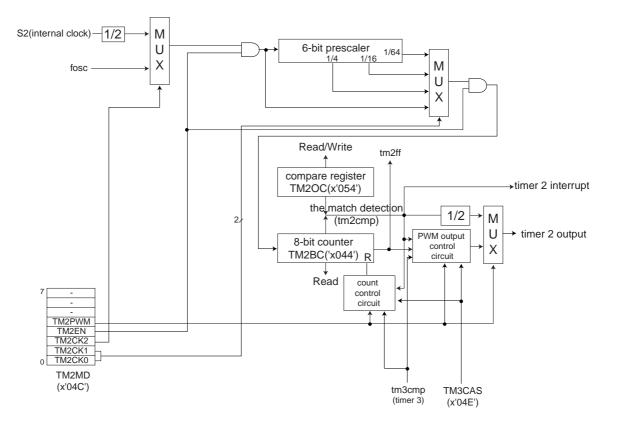

|                  | Timer 3(8-Bit timer for general use)                              |                                                      |  |  |  |  |

|                  | - Timer pulse output, High pre                                    | cision PWM output, Remote control carrier            |  |  |  |  |

|                  | output, 16-Bit cascade conne                                      | ection function (connected to timer 2)               |  |  |  |  |

|                  | - Clock source                                                    |                                                      |  |  |  |  |

|                  | fsys/2, fosc, fosc/26, fos                                        | SC/2 <sup>14</sup>                                   |  |  |  |  |

|                  | Watchdog timer                                                    |                                                      |  |  |  |  |

| A/D converter    | 10 hito X 4 shonnolo                                              |                                                      |  |  |  |  |

| A/D converter    | 10 bits X 4 channels                                              |                                                      |  |  |  |  |

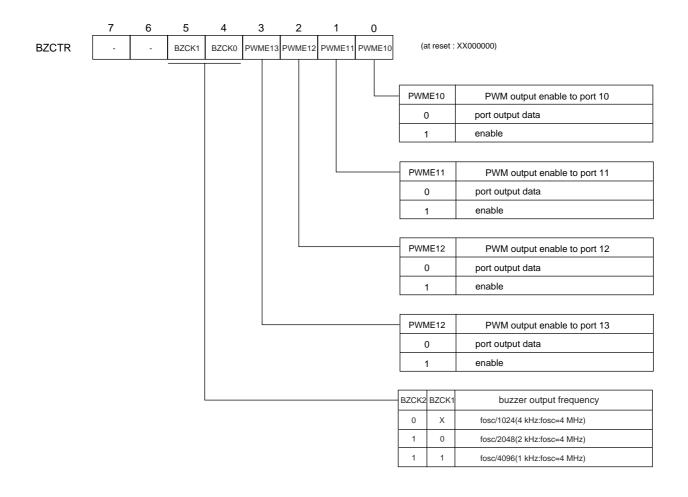

| Buzzer output    | Output frequency can be sele                                      | cted from fosc/1024, fosc/2048,                      |  |  |  |  |

|                  | fosc/4096.                                                        |                                                      |  |  |  |  |

|                  |                                                                   |                                                      |  |  |  |  |

| PWM output       |                                                                   |                                                      |  |  |  |  |

|                  |                                                                   |                                                      |  |  |  |  |

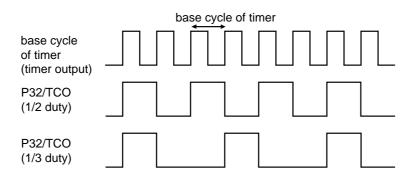

| Remote control   | output Duty cycle of 1/2, or 1/3                                  | 3.                                                   |  |  |  |  |

| ACZ input        | 1 set                                                             |                                                      |  |  |  |  |

| Mask option      | Automatic reset is available.                                     |                                                      |  |  |  |  |

| ·                |                                                                   |                                                      |  |  |  |  |

| Port             | General I/O ports                                                 | 15 ports (11 ports can be used for other func tions) |  |  |  |  |

|                  | - Buzzer output                                                   | 1 ports (for timer output and key input, too)        |  |  |  |  |

|                  | - Timer output                                                    | 1 ports (for buzzer output and key input, too)       |  |  |  |  |

|                  | - NSYNC output                                                    | 1 ports (for key input, too)                         |  |  |  |  |

|                  | - ACZ input                                                       | 1 ports (for NIRQ input and key input, too)          |  |  |  |  |

|                  | - NIRQ input                                                      | 1 ports (for ACZ input and key input, too)           |  |  |  |  |

|                  | - A/D converter input                                             | 4 ports                                              |  |  |  |  |

|                  | - Key input                                                       | 3 ports (for NSYNC output, NIRQ input,               |  |  |  |  |

|                  |                                                                   | ACZ input, timer output and                          |  |  |  |  |

|                  |                                                                   | buzzer output, too)                                  |  |  |  |  |

|                  | - PWM output                                                      | 4 ports                                              |  |  |  |  |

| EPROM version    | MN15GP0402SJ                                                      |                                                      |  |  |  |  |

| Emulator         | PX-ICE1500+PX-PRB15G040                                           | 12                                                   |  |  |  |  |

|                  |                                                                   |                                                      |  |  |  |  |

| Process          | CMOS                                                              |                                                      |  |  |  |  |

# 1-3 Block Diagram

### 1-3-1 Overview

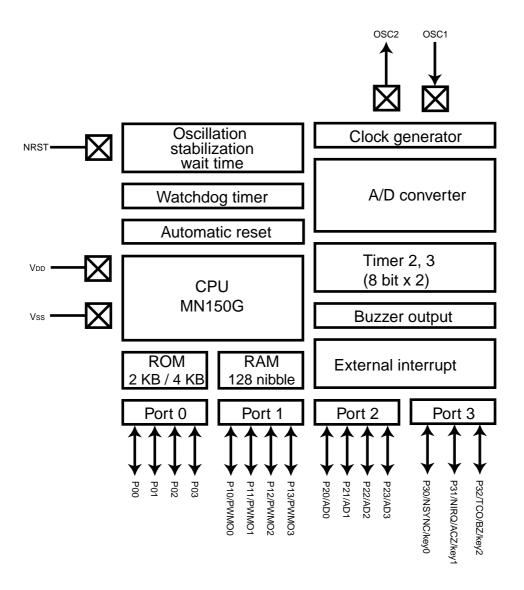

| Name                                 | Block                            | Description                                                                                                                        |

|--------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| CPU(MN150G)                          | Instruction execution controller | Controls CPU block operations in response to the result decoded by the instruction decoder and interrupt requests.                 |

| ROM                                  |                                  | Read Only Memory can be used as an area where instructions that CPU executes are stored.                                           |

| RAM                                  | Memory data                      | Random Access Memory can be used as an data area where data that are needed on program execution are stored and as the stack area. |

| Timer 2, 3<br>Buzzer output          | Timer controller                 | Used as timer operation, timer pulse output, PWM output, cascade connection, remote control carrier output, buzzer output.         |

| A/D converter                        | A/D controller                   | Includes a set of A/D converter with 10-bits resolution.<br>Analog input is switched channel 0 to 3(AD0 to AD3) by<br>software.    |

| External interrupt                   | Interrupt controller             | Controls interrupt by interrupt request flag (IF) and interrupt enable flag (IE).                                                  |

| Port 0<br>Port 1<br>Port 2<br>Port 3 | I/O controller                   | Port 0, port 1, port 2, port 3 are <i>V</i> O port.                                                                                |

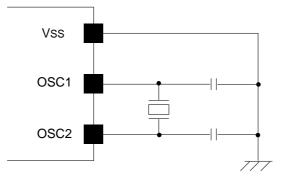

| Clock generator                      | Clock generator                  | Connect resonator to OSC1, OSC2 to generate systemclock.                                                                           |

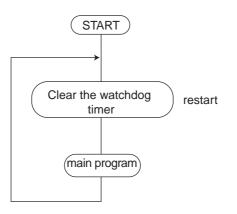

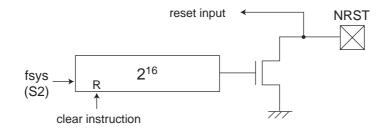

| Watchdog timer                       | Error detector                   | Counts watchdog timer.<br>When counter is overflow, output "L" from NRST pin and reset.                                            |

| Automatic reset                      | Low voltage detector             | When low voltage is detected, output "L" from NRST pin and reset.                                                                  |

#### Table 1-3-1 Functions on Blocks

### 1-3-2 Block Diagram

Figure 1-3-1 Block Function Diagram

## **1-4 Pin Description**

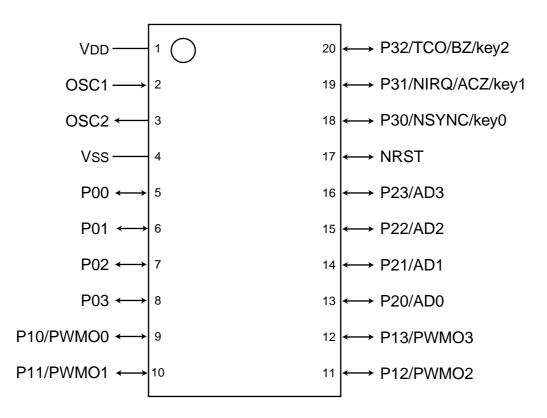

### **1-4-1 Pin Configuration**

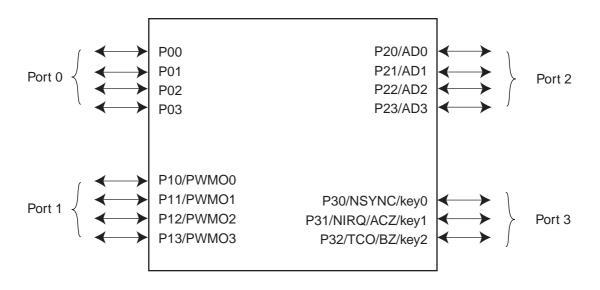

Figure 1-4-1 Pin Configuration (20SOP : Top view )

### 1-4-2 **Pin Functions**

| Name                     | Pin<br>No.           | ٧O              | Dual Function                    | Function                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------|----------------------|-----------------|----------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vss<br>Vdd               | 4<br>1               | -               |                                  | Power supply pin                    | Apply 2.0 V to 5.5 V to VDD and 0 V to Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OSC1<br>OSC2             | 2<br>3               | Input<br>Output |                                  | Clock input pin<br>Clock output pin | Connect these oscillation pins to oscillators for clock<br>operation. Feed back resistor is buit-in.<br>If the clock is an external input, connect it to OSC1 and<br>leave OSC2 open.                                                                                                                                                                                                                                                                                                                                              |

| NRST                     | 17                   | VO              |                                  | Reset input pin<br>[Schmitt]        | Reset by inputting "L" to NRST pin.<br>After reset is cleared, internal reset is cleared after 2 <sup>14</sup> counts of OSC input clock. The output configuration is<br>N-ch open-drain. Reset can be selected by watchdog<br>timer or low voltage detector(*1) by automatic reset<br>circuit.<br>*1 Autoreset circuit is mask option.                                                                                                                                                                                            |

| P00<br>P01<br>P02<br>P03 | 5<br>6<br>7<br>8     | VO              |                                  | VO port 0                           | Parallel data I/O port.<br>Each bit can be set individually as either an input or<br>output by the P01DIR register.<br>The output configuration is N-ch open-drain.<br>At reset, the input mode (high impedance output) is<br>selected.                                                                                                                                                                                                                                                                                            |

| P10<br>P11<br>P12<br>P13 | 9<br>10<br>11<br>12  | VO              | PWMO0<br>PWMO1<br>PWMO2<br>PWMO3 | VO port 1                           | Parallel data I/O port.<br>Each bit can be set individually as either an input or<br>output by the P01DIR register.<br>The output configuration is CMOS push-pull or N-ch<br>open-drain. Each bit can be switched individually by the<br>P01SC register.<br>At reset, the input mode (high impedance output) is<br>selected.<br>They can be also used for PWM output (PWMO0 to 3).                                                                                                                                                 |

| P20<br>P21<br>P22<br>P23 | 13<br>14<br>15<br>16 | VO              | AD0<br>AD1<br>AD2<br>AD3         | VO port 2                           | Parallel data I/O port.<br>Each bit can be set individually as either an input or<br>output by the P23DIR register.<br>A pull-up resistor for each bit can be selected<br>individually by the P23PLU register.<br>The output configuration is CMOS push-pull or N-ch<br>open-drain. Each bit can be switched individually by the<br>P23SC register.<br>At reset, the input mode is selected and pull-up<br>resistors are disabled (high impedance output).<br>P20 / AD0, P21 / AD1, P22 / AD2 and P23 / AD3 are<br>dual functions. |

| Table 1-4-1 | Pin Function Summary (1/3) |

|-------------|----------------------------|

|-------------|----------------------------|

| Name                     | Pin<br>NO.           | ٧O     | Dual Function                                     | Function                          | Description                                                                                                                                                                                                                                                                                                                 |

|--------------------------|----------------------|--------|---------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

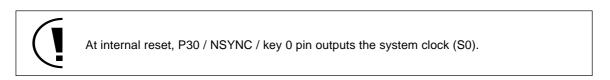

| P30<br>P31<br>P32        | 18<br>19<br>20       | VO     | NSYNC<br>key0<br>NIRQ<br>ACZ<br>key1<br>TCO<br>BZ | I/O port 3<br>[Schmitt]           | Parallel data I/O port.<br>Each bit can be set individually as either an input or<br>output by the P23DIR register.<br>A pull-up resistor for each bit can be selected<br>individually by the P23PLU register.<br>The output configuration is CMOS push-pull or N-ch<br>open-drain. Each bit can be set individually by the |

|                          |                      |        | key2                                              |                                   | P23SC register.<br>At reset, the input mode is selected and pull-up<br>resistors are disabled (high impedance output), but<br>P30 outputs system clock during the internal reset.<br>P30 / NSYNC, P31 / NIRQ/ACZ and P32 / TCO/BZ are<br>dual functions.<br>These can be used as key interrupt input.                       |

| AD0<br>AD1<br>AD2<br>AD3 | 13<br>14<br>15<br>16 | Input  | P20<br>P21<br>P22<br>P23                          | Analog input pin                  | Analog input pins for 4 channels.<br>Set pin's direction to input by the P23DIR resister.<br>When not used for analog input, these pins can be used<br>as normal port.                                                                                                                                                      |

| NSYNC                    | 18                   | Output | P30<br>key0                                       | Systemclock<br>synchronous output | At internal reset, synchronous signal of system clock is<br>output.<br>At operation, the initial status is port, but NSYNC output<br>/ port data output can be selected by the ACZCNT<br>register.<br>These can be used as key interrupt input.                                                                             |

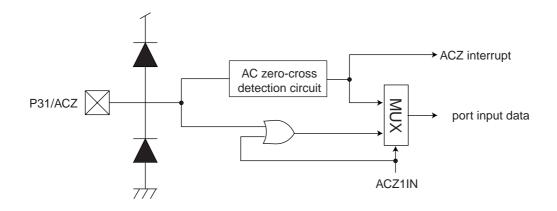

| ACZ                      | 18                   | Input  | P31<br>NIRQ<br>key1                               | AC zero-cross<br>detection input  | AC zero-cross detection circuit input pin.<br>AC zero-cross detection circuit is connected to ACZ<br>interrupt input and P31 input circuit.<br>P31 ACZ input / port input can be selected by the<br>ACZCNT register.<br>These can be used as key interrupt input.                                                           |

| ΒΖ                       | 20                   | Output | P32<br>TCO<br>key2                                | Buzzer output                     | Buzzer output pin.<br>Buzzer output / port data output can be selected by the<br>BZCTR register.<br>When not used for buzzer output, this can be used as<br>normal port.<br>This can be used as Key interrupt input.                                                                                                        |

| NIRQ                     | 19                   | Input  | P31<br>ACZ<br>key1                                | Interrupt input                   | Interrupt 1 (IRQ1) input pin.<br>When not used for interrupt input, this can be used as<br>normal port.<br>This can be used as key interrupt input.                                                                                                                                                                         |

| тсо                      | 20                   | Output | P32<br>BZ<br>key2                                 | Timer output                      | Timer output pins.<br>Timer output / port data output can be selected by the<br>TCOCNT register.<br>When not used for timer output, this pin can be used as<br>normal port.<br>This can be used as key interrupt input.                                                                                                     |

### Table 1-4-2 Pin Function Summary (2/3)

| Name  | Pin<br>NO. | ٧O     | Dual Function      | Function            | Description                                                                                                                               |

|-------|------------|--------|--------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| key0  | 18         | Input  | P30<br>NSYNC       | Key interrupt input | Key interrupt input.<br>Each bit can be set individually as either an enable or                                                           |

| key1  | 19         |        | P31<br>NIRQ<br>ACZ |                     | disable by the KEYCNT register.<br>When not used for key interrupt input, these pins can<br>be used as normal port.                       |

| key2  | 20         |        | P32<br>TCO<br>BZ   |                     |                                                                                                                                           |

| PWMO0 | 9          | Output | P10                | PWM output          | PWM output pins.                                                                                                                          |

| PWMO1 | 10         |        | P11                |                     | Each bit can be set individually PWM output as either                                                                                     |

| PWMO2 | 11         |        | P12                |                     | an enable or disable by the BZCTR register.                                                                                               |

| PWMO3 | 12         |        | P13                |                     | When PWM output is enabled, the conjunction of the timer output selected by the MODCNT register and the port output latch data is output. |

#### Table 1-4-3 Pin Function Summary (3/3)

# **1-5** Special Function Registers

### 1-5-1 Register Map

This special function registers of this LSI are located as shown below.

| (   | Page  | 0)          |       |       |     |             |     |             |     |                  |     |             |     |             |     |             |

|-----|-------|-------------|-------|-------|-----|-------------|-----|-------------|-----|------------------|-----|-------------|-----|-------------|-----|-------------|

|     | 0     | 1           | 2     | 3     | 4   | 5           | 6   | 7           | 8   | 9                | Α   | В           | С   | D           | E   | F           |

| 0 x | PORT0 | PORT1       | PORT2 | PORT3 |     | ,<br>,<br>, |     |             |     |                  |     |             |     |             |     | ,<br>,<br>, |

| 1 x | P01   | DIR         | P23   | DIR   |     | 1<br> <br>  |     | 1           |     | 1<br> <br>       |     | 1<br>1<br>1 |     | 1           |     | <br> <br>   |

| 2 x |       | ,<br>,<br>, | P23   | PLU   |     | ,<br>,<br>, |     |             | P01 | ISC              | P23 | SC          |     | ,<br>,<br>, |     | '<br> <br>  |

| 3 x | CP    | UM          | IRC   | QM    | IRG | CO          | IRC | C1          | KEY | CNT              | ACZ | CNT         |     | 1<br>1<br>1 |     | 1<br>1<br>1 |

| 4 x |       | ,<br>,<br>, |       |       | TM2 | ZBC         | TM  | 3BC         |     | ,<br>,<br>,      |     |             | TM2 | MD          | TM  | BMD         |

| 5 x |       |             |       |       | TM2 | 200         | TM3 | 300         |     |                  |     | ,<br>,<br>, |     |             | MOE | CNT         |

| 6 x |       | ,<br>,<br>, |       |       |     | ,<br>,<br>, |     | 1<br>1<br>1 |     | 1<br>1<br>1      | TCC | CNT         | BZC | TR          | WD  | CTR         |

| 7 x | ADE   | UF0         | ADB   | UF1   | ADC | TR0         |     |             |     | ,<br>,<br>,<br>, |     | ,<br>,<br>, |     |             |     | ,<br>,<br>, |

| 8 x |       |             |       |       |     |             |     |             |     |                  |     |             |     |             |     |             |

| 9 x |       |             |       |       |     |             |     |             |     |                  |     | i<br>i      |     |             |     |             |

| Аx  |       |             |       |       |     | <br>        |     |             |     |                  |     | !<br>!      |     | <br>        |     | <br>        |

| Вx  |       |             |       |       |     |             |     |             |     |                  |     |             |     |             |     |             |

| Сх  |       |             |       |       |     | I           |     | i<br>i      |     |                  |     | i<br>i      |     |             |     | I<br>I      |

| Dх  |       |             |       |       |     | <br>        |     |             |     | <br>             |     |             |     | 1           |     | <br>        |

| Еx  |       |             |       |       |     | i<br>i      |     |             |     | i<br>i           |     |             |     |             |     | i<br>i      |

| Fх  |       | I<br>I      |       |       |     | I<br>I      |     | I<br>I      |     | <br>             |     | I<br>I      |     | I           |     | <br>        |

#### Table 1-5-1 Register Map

Note : Access to x000' to x00F' is by 4-bit (I/O instruction on each port) and 8-bit. Access to x010' to x07F is by only 8-bit.

### 1-5-2 Special Function Registers

| Address | Register | R/W | Function                                         | Page           |

|---------|----------|-----|--------------------------------------------------|----------------|

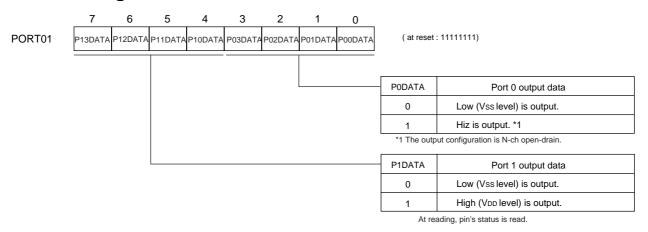

| x'000'  | PORT01   | R/W | Port 0, port 1 data register                     | III - 9        |

| x'002'  | PORT23   | R/W | Port 2, port 3 data register                     | III - 13       |

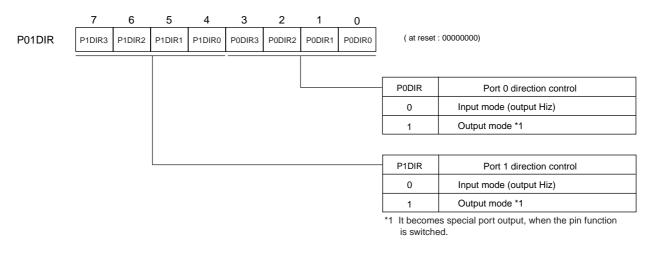

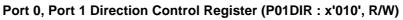

| x'010'  | P01DIR   | R/W | Port 0, port 1 direction control register        | III - 9        |

| x'012'  | P23DIR   | R/W | Port 2, port 3 direction control register        | III - 13       |

| x'022'  | P23PLU   | R/W | Port 2, port 3 pull-up resistor control register | III - 13       |

| x'028'  | P01SC    | R/W | Port 1 output structure control register         | III - 9        |

| x'02A'  | P23SC    | R/W | Port 2, port 3 output structure control register | III - 14       |

| x'030'  | CPUM     | R/W | CPU mode register                                | <b>II</b> - 15 |

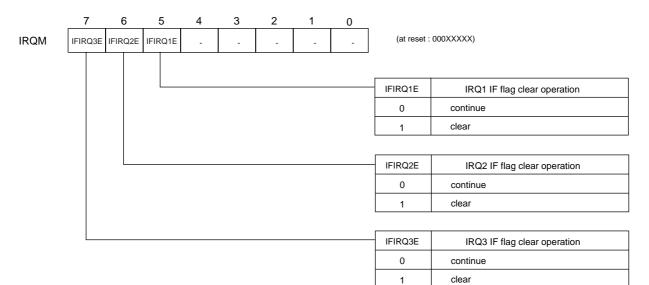

| x'032'  | IRQM     | W   | IRQ mode register                                | IV - 16        |

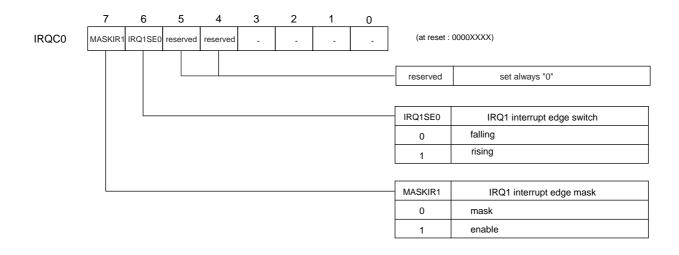

| x'034'  | IRQC0    | R/W | Interrupt 0 control register                     | IV - 16        |

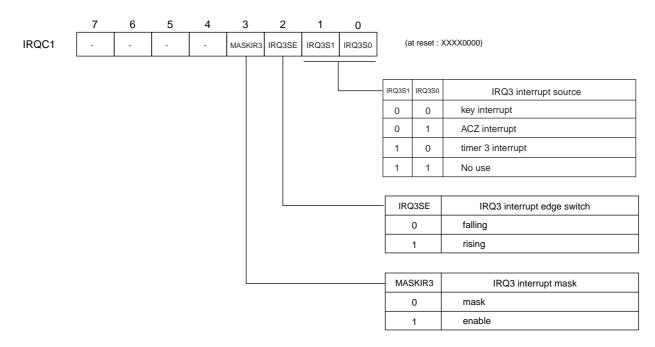

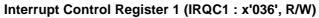

| x'036'  | IRQC1    | R/W | Interrupt 1 control register                     | IV - 17        |

| x'038'  | KEYCNT   | R/W | Key interrupt 1 control register                 | IV - 17        |

| x'03A'  | ACZCNT   | R/W | ACZ control register                             | VII - 5        |

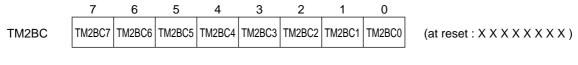

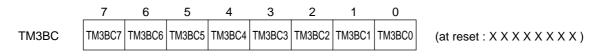

| x'044'  | TM2BC    | R   | Timer 2 binary counter                           | V - 10         |

| x'046'  | ТМЗВС    | R   | Timer 3 binary counter                           | V - 10         |

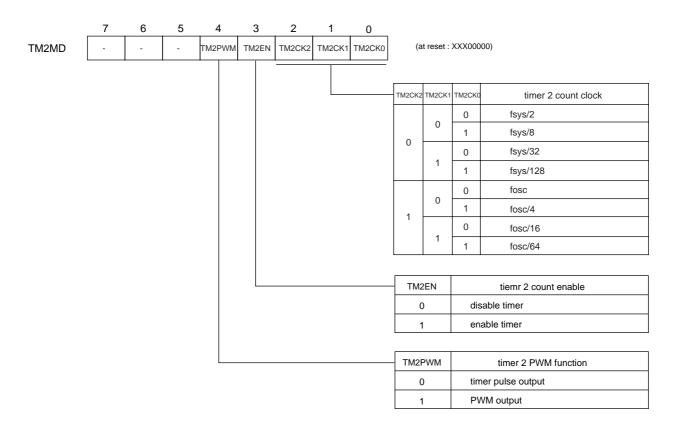

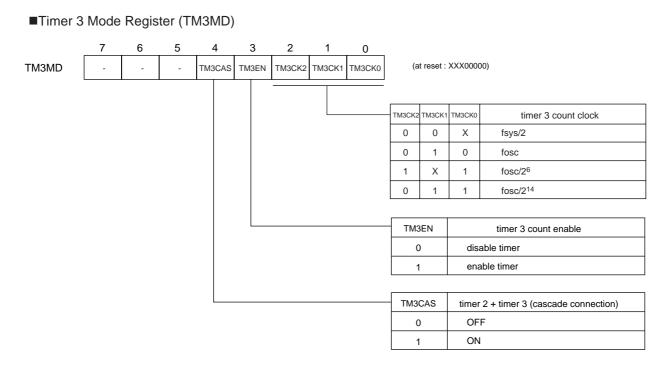

| x'04C'  | TM2MD    | R/W | Timer 2 mode register                            | V - 11         |

| x'04E'  | TM3MD    | R/W | Timer 3 mode register                            | V - 12         |

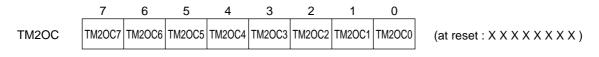

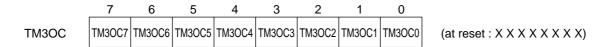

| x'054'  | TM2OC    | R/W | Timer 2 compare register                         | V - 9          |

| x'056'  | ТМЗОС    | R/W | Timer 3 compare register                         | V - 9          |

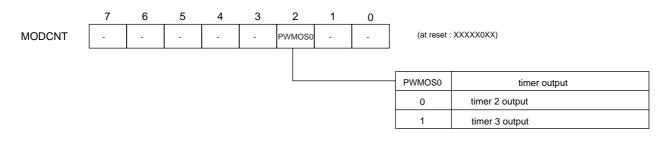

| x'05E'  | MODCNT   | R/W | Timer mode control register                      | V - 12         |

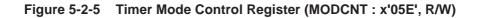

| x'06A'  | TCOCNT   | R/W | Timer output control register                    | V - 13         |

| x'06C'  | BZCTR    | R/W | Buzzer output control register                   | V - 14         |

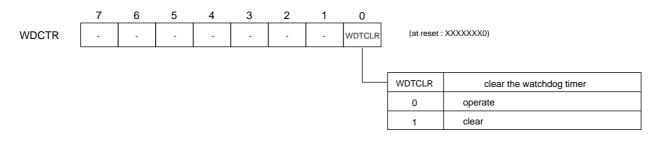

| x'06E'  | WDCTR    | W   | Watchdog timer control register                  | VIII - 4       |

| x'070'  | ADBUF0   | R   | A/D converter data storage buffer 0              | VI - 6         |

| x'072'  | ADBUF1   | R   | A/D converter data storage buffer 1              | VI - 6         |

| x'074'  | ADCTR0   | R/W | A/D control register                             | VI - 5         |

R/W : Readable / Writable

R : Readable only

W : Writable only

# **1-6 Electrical Characteristics**

This LSI user's manual describes the standard specification. Please ask our sales offices for its own product specifications.

| Model<br>Contents | MN15G0202, MN15G0402                     |

|-------------------|------------------------------------------|

| Structure         | CMOS integrated circuit                  |

| Application       | General purpose                          |

| Function          | CMOS, 4-bit, single-chip microcontroller |

### **1-6-1** Absolute Maximum Ratings \*2 \*3

|    |                              |                | U        | Vss                             | = 0 V |

|----|------------------------------|----------------|----------|---------------------------------|-------|

|    | Paramete                     | er             | Symbol   | Rating                          | Unit  |

| 1  | Power supp                   | ly voltage     | Vdd      | -0.3 to +7.0                    | V     |

| 2  | Input clamp cu               | urrent (ACZ)   | k        | -0.5 to +0.5                    | mA    |

| 3  | l∕O pin v                    | oltage         | Vю       | -0.3 to VDD+0.3<br>(except ACZ) | V     |

| 4  |                              | P0             | OL(peak) | 40                              |       |

| 5  | Peak output<br>current       | Other than P0  | OL(peak) | 20                              |       |

| 6  |                              | all            | OH(peak) | -10                             |       |

| 7  |                              | P0             | OL(avg)  | 15                              |       |

| 8  | Average output<br>current *1 | Other than P0  | OL(avg)  | 10                              |       |

| 9  |                              | all            | Юн(avg)  | -2                              | mA    |

| 10 |                              | P0             | ITOL1    | 60-hol2                         |       |

| 11 | Total output                 | Other than P0  | ITOL2    | 20                              |       |

| 12 | current *1                   | P0             | Птон1    | 60-Ітон2                        |       |

| 13 |                              | Other than P0  | Ітон2    | 20                              |       |

| 14 | Power dissipation            |                | Po       | 180(Ta=85 °C)                   | mW    |

| 15 | Ambient operati              | ng temperature | Topr     | -40 to +85                      | °C    |

| 16 | Storage ter                  | nperature      | Tstg     | -55 to +125                     | °C    |

\*1 Applied to any 100-ms period.

\*2 Connect at least one bypass capacitor of 0.1µF or larger between the power supply pin and the ground, near the LSI, for latch-up prevention.

\*3 The absolute maximum ratings are the limit values beyond which the LSI may be damaged and proper operation is not assured. They do not assure operation.

# 1-6-2 Operating Conditions

|      | Doverneter                  | Currente al | Canditiana                                                              |                  | Rating |      | 1.1  |

|------|-----------------------------|-------------|-------------------------------------------------------------------------|------------------|--------|------|------|

|      | Parameter                   | Symbol      | Conditions                                                              | MIN              | TYP    | MAX  | Unit |

| Pow  | er supply voltage           |             |                                                                         |                  |        |      |      |

| 1    |                             | Vdd1        | fosc≤8 MHz(divided by 4)<br>No automatic reset                          | 3.0              | -      | 5.5  |      |

| 2    |                             | Vdd2        | fosc≤4 MHz(divided by 4)<br>No automatic reset                          | 2.4              | -      | 5.5  |      |

| 3    | Power supply voltage        | Vdd3        | fosc≤4 MHz(divided by 8)<br>No automatic reset                          | 2.0              | -      | 5.5  | V    |

| 4    |                             | Vdd4 *1     | fosc≤8 MHz(divided by 4)<br>fosc≤4 MHz(divided by 4)<br>Automatic reset | Vrstl1           | -      | 5.5  |      |

| 5    |                             | Vdd5        | fosc≤4 MHz(divided by 8)<br>Automatic reset                             | Vrstl1<br>Vrstl2 | -      | 5.5  |      |

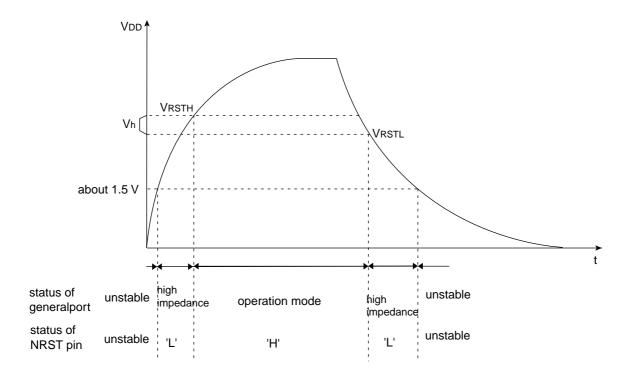

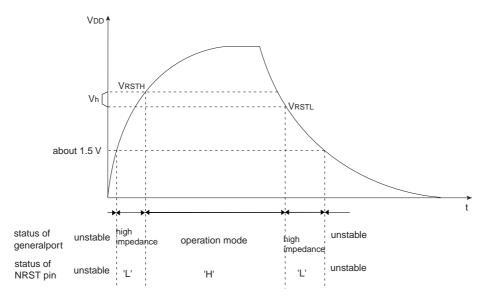

| Auto | matic reset circuit 1       |             |                                                                         |                  |        |      |      |

| 6    | Power supply detection      | VRSTH1      |                                                                         | -                | 3.90   | 4.40 |      |

| 7    | level                       | Vrstl1      | -                                                                       | 3.20             | 3.70   | -    | V    |

| 8    | Hysteresis width            | Vh          | figure 1-6-1.                                                           | 0.05             | 0.20   | -    |      |

| 9    | Power supply voltage change | Δt/Δv       |                                                                         | 1.00             | -      | -    | ms/V |

| Auto | matic reset circuit 2       |             |                                                                         |                  |        |      |      |

| 10   | Power supply detection      | VRSTH2      |                                                                         | -                | 2.20   | 2.40 |      |

| 11   | level                       | Vrstl2      |                                                                         | 1.80             | 2.05   | -    | V    |

| 12   | Hysteresis width            | Vh          | figure 1-6-1.                                                           | 0.05             | 0.15   | -    |      |

| 13   | Power supply voltage change | Δt/Δv       |                                                                         | 1.00             | -      | -    | ms/V |

#### Ta = -40 °C to +85 °C Vdd = 2.0 V to 5.5 V(VrstL1,2 to 5.5 V) Vss = 0 V

|      | Devementer                 | Currente e l      | Canditiana                                                                 | Rating |     | Unit |      |

|------|----------------------------|-------------------|----------------------------------------------------------------------------|--------|-----|------|------|

|      | Parameter                  | Symbol Conditions |                                                                            | MIN    | TYP | MAX  | Unit |

| Oper | ation speed                |                   |                                                                            |        | -   |      |      |

| 14   | Instruction execution time | tc1               | VDD=3.0 V to 5.5 V<br>(): At automatic reset                               | 0.5    | -   | 16   |      |

| 15   |                            | tc2               | VDD=2.4 V(VRSTL1) to 5.5 V<br>(): At automatic reset                       | 1.0    | -   | 16   | μs   |

| 16   |                            | tc3               | VDD=2.0 V(VRSTL1,2) to 5.5 V<br>High oscillation<br>(): At automatic reset | 2.0    | -   | 16   |      |

Ta = -40 °C to +85 °C VDD = 2.0 V to 5.5 V(VRSTL1,2 to 5.5 V) VSS = 0 V

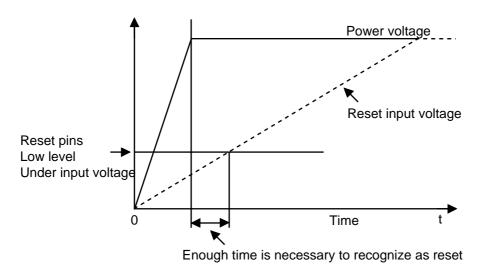

Figure 1-6-1 Automatic Reset Voltage

|     | Devenueter                     | Cumhal             | Symbol Conditions Rating                                                 |     |       | Unit |     |  |  |  |

|-----|--------------------------------|--------------------|--------------------------------------------------------------------------|-----|-------|------|-----|--|--|--|

|     | Parameter                      | Symbol             | Conditions                                                               | MIN | TYP   | MAX  |     |  |  |  |

| Osc | Dscillation (High oscillation) |                    |                                                                          |     |       |      |     |  |  |  |

| 17  | Oscillation frequency          | f <sub>xtal1</sub> |                                                                          | 0.5 | -     | 8.0  | MHz |  |  |  |

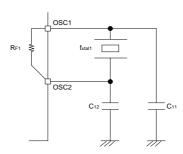

| 18  |                                | C11                | VDD=2.0 V to 5.5 V                                                       | -   | 30.0  | -    | ~F  |  |  |  |

| 19  | External capacitors            | C12                | VDD=VRSTL1, 2 to 5.5 V *1           figure 1-6-2.         -         30.0 |     | -     | pF   |     |  |  |  |

| 20  | Internal feedback resistor     | R <sub>F1</sub>    |                                                                          | -   | 500.0 | -    | kΩ  |  |  |  |

| Ta = -40 °C to +85 °C | $V_{DD} = 2.0 \text{ V to } 5.5 \text{ V}$ | V(VRSTL1,2 to 5.5 V) | Vss = 0 V |

|-----------------------|--------------------------------------------|----------------------|-----------|

|-----------------------|--------------------------------------------|----------------------|-----------|

\*1 When automatic reset is available

Figure 1-6-2 Oscillation

Connect the external capacitor suits the used pin. When crystal oscillator or ceramic oscillator is used , frequency is changed depending on the condenser rate. Therefore, please consult the manufacturer the external capacitors suits the used pin.

| Parameter Syn |                            |            | Conditions       | Rating |   |     | Unit |

|---------------|----------------------------|------------|------------------|--------|---|-----|------|

| Exter         | nal clock input OSC 1(OSC2 | is unconne | cted.)           |        |   |     |      |

| 21            | Clock frequency            | fosc1      |                  | 0.5    | - | 8.0 | MHz  |

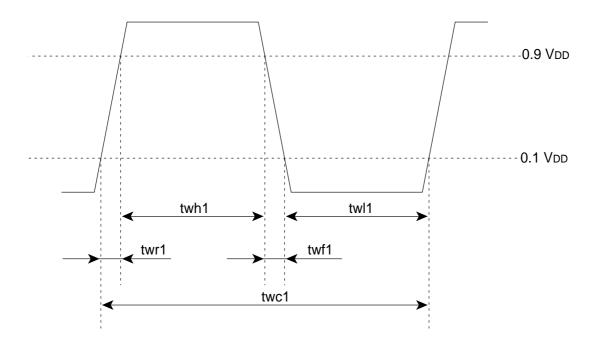

| 22            | High level pulse width     | twh1       | figure 1 6 2 *1  | 56     | - | -   |      |

| 23            | Low level pulse width      | twl1       | figure 1-6-3. *1 | 56     | - | -   |      |

| 24            | Rise time                  | twr1       | figure 1.6.2     | -      | - | 20  | ns   |

| 25            | Fall time                  | twf1       | figure 1-6-3.    | -      | - | 20  |      |

Ta = -40 °C to +85 °C Vdd = 2.0 V to 5.5 V(VRSTL1,2 to 5.5 V) Vss = 0 V

\*1 The clock duty cycle should be 45 % to 55 %.

Figure 1-6-3 OSC1 Timing Chart (External clock input)

### 1-6-3 DC Characteristics

|      | Parameter Power supply current *1          1         2 | Symbol | Conditions                                                              |     | Rating |      | - Unit |

|------|--------------------------------------------------------|--------|-------------------------------------------------------------------------|-----|--------|------|--------|

|      | Falameter                                              |        |                                                                         | MIN | TYP    | MAX  | Ofilt  |

| Powe | er supply current *1                                   |        |                                                                         | •   |        |      |        |

| 1    | Dower output                                           |        | fosc=8.0 MHz (divided by 8)<br>VpD=5.0 V                                | -   | 1.5    | 3.0  |        |

| 2    |                                                        |        | fosc=4.0 MHz (divided by 8)<br>VpD=5.0 V                                | -   | 1.2    | 2.5  | mA     |

| 3    | Supply current during<br>HALT mode                     | Іодз   | fosc=4.0 MHz (divided by 8)<br>VpD=5.0 V                                | -   | 0.3    | 0.6  | mA     |

| 4    |                                                        | DD4    | V <sub>DD</sub> =5 V<br>ACZ=1/2V <sub>DD</sub><br>Ta=25 °C              | -   | 3.0    | 10.0 |        |

| 5    | Supply current during                                  | IDD5   | V <sub>DD</sub> =5 V<br>ACZ=1/2V <sub>DD</sub><br>Ta = -40 °C to +85 °C | -   | -      | 20.0 |        |

| 6    |                                                        |        | V <sub>DD</sub> =5 V<br>Ta=25 °C                                        | -   | -      | 1.0  | μΑ     |

| 7    |                                                        | ldd7   | V <sub>DD</sub> =5 V<br>Ta=-40 °C to +85 °C                             | -   | -      | 5.0  |        |

| 8    | Automatic reset current consumption *2                 | IDD8   | VDD=5 V                                                                 | -   | 4.0    | 8.0  |        |

Ta = -40 °C to +85 °C Vdd = 2.0 V to 5.5 V(VRSTL1,2 to 5.5 V) Vss = 0 V

\*1 Measured under conditions of no load, Ta = 25 °C.

\*2 The automatic reset current consumption IDD10 indicates the consumption, normally spent in automatic reset circuit, when automatic reset is used in mask option. So, if automatic reset circuit is selected, each rating is added.

- The supply current during operation, IDD1, is measured under the following conditions : After reset is released and the oscillation is set to <NORMAL mode>, the I/O pin is fixed at VDD, and a 8-MHz square wave of amplitude VDD, Vss is input to the OSC1 pin.

- The supply current during operation, IDD2, is measured under the following conditions : After reset is released and the oscillation is set to <NORMAL mode>, the I/O pin is fixed at VDD, and a 4-MHz square wave of amplitude VDD, Vss is input to the OSC1 pin.

- The supply current during HALT mode, IDD3, is measured under the following conditions :

- After reset is released and the oscillation is set to <HALT mode>, the I/O pin is fixed at VDD, and a 4-MHz square wave of amplitude VDD, Vss is input to the OSC1 pin.

- During STOP mode, The supply current IDD4, IDD5 and IDD6 are applied to the circuit other than the auto reset circuit.

- The supply current during STOP mode, IDD4, IDD5 are measured under the following conditions :

- After reset is released and the oscillation is set to <STOP mode>, the I/O pin is fixed at VDD, the ACZ pin is fixed at 1/2 VDD and the OSC1 is unconnected.

- The supply current during STOP mode, IDD6, IDD7 are measured under the following conditions : After reset is released and the oscillation is set to <STOP mode>, the I/O pin is fixed at VDD and the OSC1 is unconnected.

|       | Deveryor               | Complete       | Condition                                        |        | Rating |          | 1 1  |

|-------|------------------------|----------------|--------------------------------------------------|--------|--------|----------|------|

|       | Parameter              | Symbol         | Condition                                        | MIN    | TYP    | MAX      | Unit |

| Input | pin NRST (Schmitt inp  | ut. Pull-up re | sistor built-in.)                                |        |        |          |      |

| 9     | Input high voltage     | VIH1           |                                                  | 0.8Vdd | -      | Vdd      | V    |

| 10    | Input low voltage      | VIL1           |                                                  | Vss    | -      | 0.15 Vdd | V    |

| 11    | Input current          | In             | Pull-up resistor ON<br>V⊫1.5 V, V⊳⊳=5.0 V        | -50    | -140   | -200     | μA   |

| I∕O p | in P00 to P03(N-ch ope | en-drain outp  | ut)                                              |        |        |          |      |

| 12    | Input high voltage     | VIH2           |                                                  | 0.8Vdd | -      | Vdd      | V    |

| 13    | Input low voltage      | VIL2           |                                                  | Vss    | -      | 0.2Vdd   | V    |

| 14    | Input leakage current  | IL12           | V⊫0 V to V <sub>DD</sub>                         | -      | ±0.01  | ±1       | μA   |

| 15    | Output low voltage     | Vol2           | loL=15 mA,VDD=5.0 V                              | Vss    | 0.4    | 1.0      | V    |

| I∕O p | in P10/PWMO0 to P13/   | PWMO3          |                                                  | •      |        |          |      |

| 16    | Input high voltage     | V⊪з            |                                                  | 0.8Vdd | -      | Vdd      | V    |

| 17    | Input low voltage      | VIL3           |                                                  | Vss    | -      | 0.2Vdd   | v    |

| 18    | Input leakage current  | Lıз            | V⊫0 V to V <sub>DD</sub>                         | -      | ±0.01  | ±1       | μA   |

| 19    | Output high voltage    | Vонз           | юн=-0.5 mA,Vod=5.0 V                             | 4.5    | 4.9    | Vdd      | V    |

| 20    | Output low voltage     | Vol3           | IOL=15 mA,VDD=5.0 V                              | Vss    | 0.4    | 1.0      | V    |

| I∕O p | in P20/AD0, P21/AD1, I | P22/AD2, P2    | 23/AD3 (as port)                                 |        |        |          |      |

| 21    | Input high voltage     | VIH4           |                                                  | 0.8Vdd | -      | Vdd      | V    |

| 22    | Input low voltage      | VIL4           |                                                  | Vss    | -      | 0.2Vdd   | V    |

| 23    | Input current          | <b>I</b> 4     | Pull-up resistor ON<br>V⊫1.5 V, V⊳⊳=5.0 V        | -50    | -140   | -200     |      |

| 24    | Input leakage current  | IL14           | Pull-up resistor OFF<br>V⊫0 V to V <sub>DD</sub> | -      | ±0.01  | ±1       | μA   |

| 25    | Output high voltage    | VOH4           | юн=-0.5 mA,Vod=5.0 V                             | 4.5    | 4.9    | Vdd      |      |

| 26    | Output low voltage     | Vol4           | lo∟=3.5 mA,Vod=5.0 V                             | Vss    | 0.1    | 0.5      | V    |

#### Ta=-40 °C to +85 °C $\,$ Vdd=2.0 V to 5.5 V(VrstL1,2 to 5.5 V) Vss=0 V $\,$

|                | Parameter                                         | Cumbal      | Condition                                                 |         | Rating |         | - Unit |  |

|----------------|---------------------------------------------------|-------------|-----------------------------------------------------------|---------|--------|---------|--------|--|

|                | Parameter                                         | Symbol      | Condition                                                 | MIN     | TYP    | MAX     | Unit   |  |

| l/O p<br>(as F |                                                   |             | CZ/key1, P32/TCO/BZ/key2<br>2/TCO/BZ/key2, schmitt input) |         |        |         |        |  |

| 27             | Input high voltage                                | VIH5        |                                                           | 0.8Vdd  | -      | Vdd     | V      |  |

| 28             | Input low voltage                                 | VIL5        |                                                           | Vss     | -      | 0.1Vdd  | v      |  |

| 29             | Input current                                     | lı5         | Pull-up resistor ON<br>V⊨1.5 V, Vɒɒ=5.0 V                 | -50     | -140   | -200    |        |  |

| 30             | Input leakage current                             | IL15        | Pull-up resistor OFF<br>V⊨0 V to Vpb                      | -       | ±0.01  | ±1      | μA     |  |

| 31             | Output high voltage                               | Voh5        | юн=-0.5 mA,Vpd=5.0 V                                      | 4.5     | 4.9    | Vdd     | V      |  |

| 32             | Output low voltage                                | Vol5        | IOL=3.5 mA,VDD=5.0 V                                      | Vss     | 0.1    | 0.5     | V      |  |

| Note           | : When P30/NSYNC/key0<br>output voltage should be |             | at timing signal (NSYNC) output.                          |         |        |         |        |  |

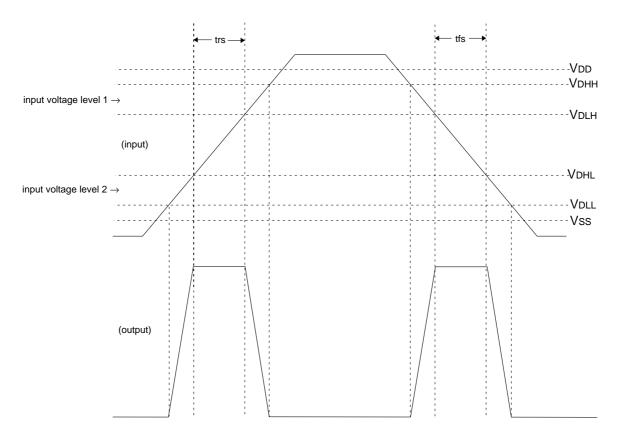

| Input          | pin P31/NIRQ/ACZ/ke                               | ey1 (as ACZ | input)                                                    |         |        |         |        |  |

| 33             | Input high voltage                                | Vdhh        |                                                           | Vdd-0.5 | -      | Vdd     |        |  |

| 34             | Input low voltage                                 | Vdlh        | VDD = 4.5 V to 5.5 V                                      | Vss     | -      | Vdd-1.5 | Ň      |  |

| 35             | Input high voltage                                | Vdhl        | figure 1-6-4.                                             | 1.5     | -      | Vdd     | V      |  |

| 36             | Input low voltage                                 | Vdll        |                                                           | Vss     | -      | 0.5     |        |  |

| 37             | Input leakage current                             | IL16        | VI=0 V to VDD                                             | -       | ±0.01  | ±1      |        |  |

| 38             | Input clamp current                               |             | VI> VDD, VI< 0 V                                          | -       | -      | ±500    | μA     |  |

| 39             | Rise time                                         | trs         | formed C.A.                                               | 30      | -      | -       |        |  |

| 40             | Fall time                                         | tfs         | figure 1-6-4.                                             | 30      | -      | -       | μs     |  |

#### Ta=-40 °C to +85 °C VDD=2.0 V to 5.5 V(VRSTL1,2 to 5.5 V) VSS=0 V

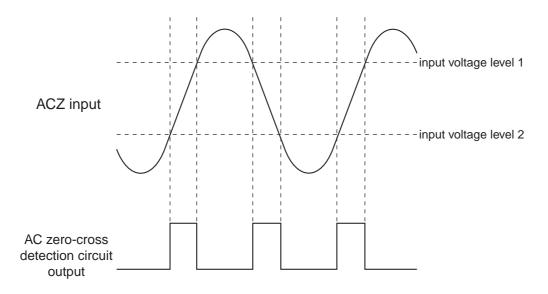

Figure 1-6-4 AC Zero-cross Detection Circuit Operation

### 1-6-4 A/D Converter Characteristics

| Parameter |                                     | Symbol | Conditions                                                                 | Rating |       |      | Linit |

|-----------|-------------------------------------|--------|----------------------------------------------------------------------------|--------|-------|------|-------|

|           |                                     |        |                                                                            | MIN    | TYP   | MAX  | Unit  |

| 1         | Resolution                          |        |                                                                            | -      | -     | 10   | Bits  |

| 2         | Non-linearity error                 |        | Vdd=5.0 V, Vss=0.0 V<br>fosc=8 MHz (divided by 8)<br>Tad=1.0 µs, Ts=2.0 µs | -      | -     | ±3   | LSB   |

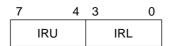

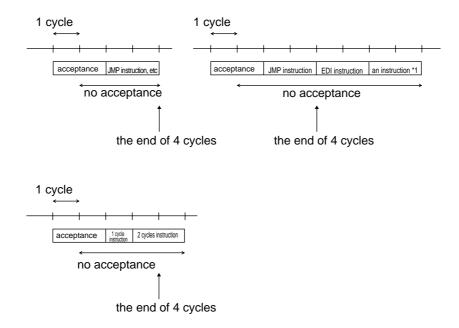

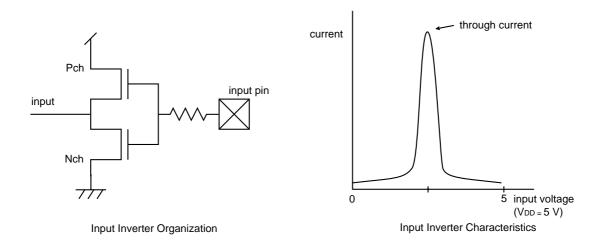

| 3         | Differential non-linearity<br>error |        |                                                                            | -      | -     | ±3   | LSB   |