### 1.1 Product Summary

#### Outline

This is a MOS-type sensor of 1/3 type offering 2.1 mega pixels. This product consists of embedded photodiode, pixel block by MOS transistor, column AD converter, built-in timing generator (TG), high speed serial output I/F and functional circuits of various kinds. High definition 12-bit digital image signals offering 2.1 mega pixels are obtained with high speed of 60 fps and with low power consumption.

#### Feature

Features of this MOS type image sensor are follows.

| Item                                               | Description                                                          |

|----------------------------------------------------|----------------------------------------------------------------------|

| Scan mode                                          | progressive scan                                                     |

| Optical size                                       | 1/3 type (inch)                                                      |

| Number of active pixels                            | 1944 (H) × 1092 (V) = 2,122,848 (pixel)                              |

| Total number of pixels                             | 2010 (H) × 1108 (V) = 2,227,080 (pixel)                              |

| Pixel size                                         | 2.75 (H)μm × 2.75 (V)μm                                              |

| Number of pins                                     | 104 Pins (including pins of "NC")                                    |

| Actual imaging area dimensions (active pixel area) | 5.346 (H)mm × 3.003 (V)mm                                            |

| Color filter arrangement                           | Bayer arrangement of primary colors: R, G, B                         |

| Power supply voltage                               | 3.3V / 1.8V / 1.2V                                                   |

| Master clock                                       | 27 MHz / 37.125MHz                                                   |

| Bit number of internal ADC                         | 12 bit                                                               |

| Output signal type                                 | subLVDS DDR method 486Mbps(MCLK=27MHz)<br>445.5Mbps (MCLK=37.125MHz) |

| Register I / F                                     | 3-lines Serial I/F                                                   |

| Output frame rate per second (Full scan)           | 2ch 2port 12bit : 60fps                                              |

|                                                    | 2ch 2port 16bit : 30fps ※1                                           |

| Electronic shutter (Full scan)                     | 60fps: 1 / 60s ~ 1 / 67500s (1 / 67500s step)                        |

| Variable gain (Column amplifier)                   | Full scan : Standard +0/+6/+12dB                                     |

| Variable gain (Analog)                             | Full scan : 0dB/6dB                                                  |

| Variable digital gain (Digital processing)         | 0dB ~ 12dB                                                           |

|                                                    | Full scan mode:2.1Mpixel output                                      |

| Functions                                          | Flip %2                                                              |

|                                                    | Long exposure mode                                                   |

Table 1.1.1 List of Features

1 This drive mode is available in chip set with Panasonic DSP (MN2PS00003RF) only.

2 Apply mirror function in DSP.

#### Application

This product is ideal for the field of security camera, network camera, broadcasting camera and industrial camera.

#### Element Configuration

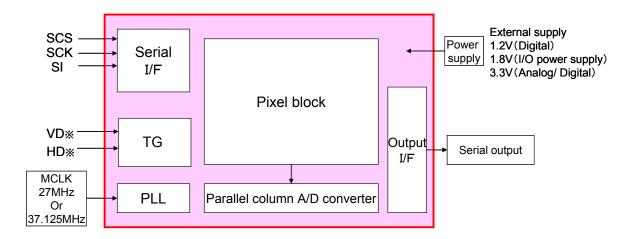

The block configuration and pixel array of this product are described below.

Block configuration

This product consists of pixel block, high speed serial I/F, LVDS output, PLL, Timing generator (TG), Parallel column AD converter and functional circuits of various kinds.

Figure 1.1.1 Block Diagram

In sensor slave mode, VD and HD are external input.

In sensor master mode, make these terminals open.

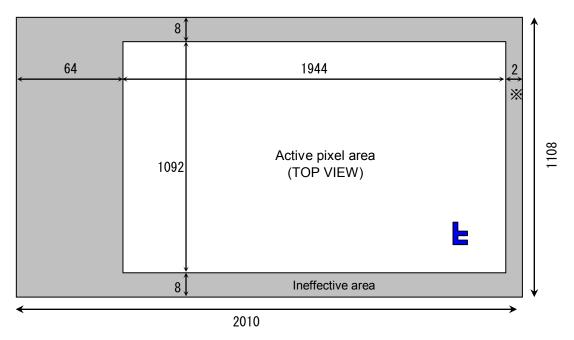

#### Pixel Array Format

Pixel array format is described below.

A1 pin (Upper left)

Figure 1.1.2 Pixel Array Configuration

X In physical pixel array configuration (2010H), 2 lines of right side are ineffective area.

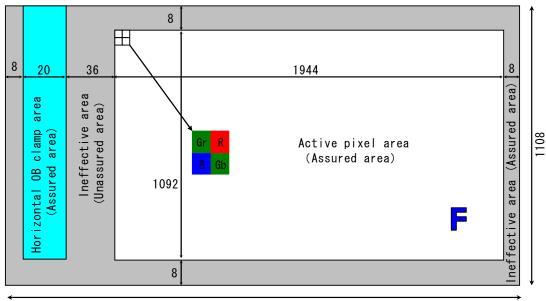

In LVDS output (2016H), it includes dummy (6 lines) as ineffective data. Totally 8 lines of ineffective data is output. (Refer to the following figure)

<Reference>

2016

Figure 1.1.3 Pixel Array Configuration (LVDS output)

## Panasonic \_\_\_

Pins

| j  |      |          |           |       |                 |        |                         |       |        |         |             |          |

|----|------|----------|-----------|-------|-----------------|--------|-------------------------|-------|--------|---------|-------------|----------|

| ۲  | A1   |          | RSTN      | TOUT3 | TOUT4           | TOUT5  | GND                     | AGND  | AGNDSH | тезтю   |             |          |

| 2  |      |          | so        | PSV   | MSSEL           | MCLK   | VDD                     | AVDD  | GND    | GND     |             |          |

| 3  | NC   | SI       | DDV       | GND   | VDD18           | VDD18  | VDD18                   | VDD33 | DDV    | SDODBOP | SDODBOM     | GND      |

| 4  | sos  | sck      | VDD33     | (MRK) |                 |        |                         |       |        | SDOCBP  | SDOCBM      | GND      |

| 5  | дн   | d        | GND       |       | l               | 2      |                         |       |        | VDD33   | VDD33       | VDD33    |

| 9  | AVDD | AGND     | AGNDSH    | •     |                 |        | MN34041PL (BUITOM VIEW) |       |        | SDODB1P | SD ODB 1M   | DDV      |

| 7  | ТМ   | GND      | <b>DD</b> | •     |                 |        |                         |       |        | SDODB2P | SDODB2M     | GND      |

| 8  | TB   | GND      | VDD       | •     |                 | č<br>Z | чг<br>В                 |       |        | SDODA2P | SD OD A 2 M | VREFRES1 |

| 6  | AVDD | AGND     | AGNDSH    | •     |                 |        | 134041                  |       |        | SDODA1P | SDODA1M     | DDV      |

| 10 | TBS0 | GND      | GND       | •     |                 |        | ž                       |       |        | VDD33   | VDD33       | VDD33    |

| 11 | TBS1 | VDD33    | VDD33     | •     |                 |        |                         |       |        | SDOCAP  | SDOCAM      | GND      |

| 12 | TBS2 | VDDCELL0 | VDD       | AGND  | N_NIQA          | S'NIQA | VDD18                   | VDD33 | VDD    | SDODA0P | SDODA0M     | GND      |

| 13 |      |          | VREFRES2  | AVDD  | <b>VREFRES3</b> | VCHP2  | DDV                     | AVDD  | GND    | GND     |             |          |

| 14 |      |          | TBS3      | TOUTO | τουτι           | VCHP1  | GND                     | AGND  | AGNDSH | TOUT2   |             |          |

|    | ۷    | ш        | Ö         | ۵     | ш               | Ŀ      | g                       | т     | J      | ¥       | L           | Σ        |

Figure 1.1.4 Pin Connection (BOTTOM VIEW)

Do not connect to the unused pin "NC". Make it OPEN electrically.

D4 (MRK) is a recognition mark of package and it is not a pin.

Pin specifications, process and functions list Specifications and functions of pins showed in Figure 1.1.4 are the following. Explanation of symbols: I: INPUT, O: OUT, P: POWER, G: GND

| Pin No. | Pin name | I/O | Process                                                                  | Functions                                                                   |

|---------|----------|-----|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| A3      | NC       | -   | OPEN                                                                     | None(Not connected to device)                                               |

| A4      | SCS      | Ι   | Input chip select signal (Low : Select)                                  | Serial chip select                                                          |

| A5      | HD I     |     | Sensor master : OPEN                                                     | Horizontal synchronous signal input                                         |

|         |          | I/O | Sensor slave : Horizontal synchronous signal input                       |                                                                             |

| A6      | AVDD     | Р   | Connect analog 3.3V power supply                                         | Analog 3.3V power supply                                                    |

| A7      | ТМ       | Ι   | Connect DGND                                                             | Test                                                                        |

| A8      | ТВ       | 0   | OPEN                                                                     | Test                                                                        |

| A9      | AVDD     | Р   | Connect analog 3.3V power supply                                         | Analog 3.3V power supply                                                    |

| A10     | TBS0     | 0   | OPEN                                                                     | Test                                                                        |

| A11     | TBS1     | 0   | OPEN                                                                     | Test                                                                        |

| A12     | TBS2     | 0   | OPEN                                                                     | Test                                                                        |

| B3      | SI       | Ι   | Input serial data                                                        | Serial data input                                                           |

| B4      | SCK      | Ι   | Input serial clock                                                       | Serial clock input                                                          |

| B5      | VD       | I/O | Sensor master : OPEN<br>Sensor slave : Vertical synchronous signal input | Vertical synchronous signal                                                 |

| B6      | AGND     | G   | Connect AGND                                                             | AGND                                                                        |

| B7      | GND      | G   | Connect DGND                                                             | DGND                                                                        |

| B8      | GND      | G   | Connect DGND                                                             | DGND                                                                        |

| B9      | AGND     | G   | Connect AGND                                                             | AGND                                                                        |

| B10     | GND      | G   | Connect DGND                                                             | DGND                                                                        |

| B11     | VDD33    | Р   | Connect digital 3.3V power supply                                        | Digital 3.3V power supply                                                   |

| B12     | VDDCELL0 | I/O | OPEN                                                                     | Test                                                                        |

| C1      | RSTN     | I   | Input reset signal (Low: Reset)                                          | Reset signal                                                                |

| C2      | SO       | I/O | Connect 10kΩ between DGND                                                | Serial signal output(Not guaranteed)<br>Register read : output, Others:Hi-z |

| C3      | VDD      | Р   | Connect 1.2V power supply                                                | Digital core 1.2V power supply                                              |

| C4      | VDD33    | Р   | Connect digital 3.3V power supply                                        | Digital 3.3V power supply                                                   |

| C5      | GND      | G   | Connect DGND                                                             | DGND                                                                        |

| C6      | AGNDSH   | G   | Connect AGND                                                             | AGND                                                                        |

| C7      | VDD      | Р   | Connect 1.2V power supply                                                | Digital core 1.2V power supply                                              |

| C8      | VDD      | Р   | Connect 1.2V power supply                                                | Digital core 1.2V power supply                                              |

| C9      | AGNDSH   | G   | Connect AGND                                                             | AGND                                                                        |

| C10     | GND      | G   | Connect DGND                                                             | DGND                                                                        |

| C11     | VDD33    | Р   | Connect digital 3.3V power supply                                        | Digital 3.3V power supply                                                   |

| C12     | VDD      | Р   | Connect 1.2V power supply                                                | Digital core 1.2V power supply                                              |

| C13     | VREFRES2 | I   | Connect 12kΩ between AGND *1                                             | Reference resistance for internal circuit                                   |

| C14     | TBS3     | 0   | OPEN                                                                     | Test                                                                        |

| Table 1.1.2 | List of Pin Specifications, Process and Functions |

|-------------|---------------------------------------------------|

|-------------|---------------------------------------------------|

# Panasonic \_\_\_\_\_

| Pin No.    | Pin name       | I/O      | Process                                                                | Functions                                              |

|------------|----------------|----------|------------------------------------------------------------------------|--------------------------------------------------------|

| D1         | TOUT3          | 0        | OPEN                                                                   | Test                                                   |

| <b>D</b> 0 |                | 1        | Input power save signal                                                | Devuer eque signal                                     |

| D2         | PSV            |          | (Low: Power save)                                                      | Power save signal                                      |

| D3         | GND            | G        | Connect DGND                                                           | DGND                                                   |

| D4         | (MRK)          | -        | OPEN(This is not a pin)                                                | Package recognition mark                               |

| D12        | AGND           | G        | Connect AGND                                                           | AGND                                                   |

| D13        | AVDD           | Р        | Connect analog 3.3V power supply                                       | Analog 3.3V power supply                               |

| D14        | TOUT0          | 0        | OPEN                                                                   | Test                                                   |

| E1         | TOUT4          | 0        | OPEN                                                                   | Test                                                   |

| 50         |                |          | Sensor mode                                                            |                                                        |

| E2         | MSSEL          |          | (High:Slave, Low:Master)                                               | Sensor mode select signal                              |

| E3         | VDD18          | Р        | Connect 1.8V power supply                                              | Digital 1.8V power supply                              |

| E12        | ADIN_N         | 0        | OPEN                                                                   | Test                                                   |

| E13        | VREFRES3       |          | Connect 12kΩ between AGND *1                                           | Reference resistance for internal circuit              |

| E14        | TOUT1          | 0        | OPEN                                                                   | Test                                                   |

| F1         | TOUT5          | 0        | OPEN                                                                   | Test                                                   |

| F2         | MCLK           |          | Input master clock                                                     | Master clock input                                     |

| F3         | VDD18          | Р        | Connect 1.8V power supply                                              | Digital 1.8V power supply                              |

| F12        | ADIN_S         | 0        | OPEN                                                                   | Test                                                   |

| F13        | VCHP2          | Р        | Connect 2.2µF bypath capacitance                                       | Down converter                                         |

| 1 10       | VOIII 2        | <u>'</u> | Connect 2.2µ1 bypath capacitance                                       | (Voltage is generated internally)                      |

| F14        | VCHP1          | Р        | Connect 2.2µF bypath capacitance                                       | Power supply for pixel                                 |

| G1         | GND            | G        | Connect DGND                                                           | (Voltage is generated internally)<br>DGND              |

| G1<br>G2   | VDD            | P        | Connect 1.2V power supply                                              | Digital core 1.2V power supply                         |

| G2<br>G3   | VDD<br>VDD18   | P        | Connect 1.2V power supply<br>Connect 1.8V power supply                 | Digital 1.8V power supply                              |

| G3<br>G12  | VDD18<br>VDD18 | P        | Connect 1.8V power supply                                              | Digital 1.8V power supply<br>Digital 1.8V power supply |

| G12<br>G13 | VDD18          | P        | Connect 1.2V power supply                                              | Digital core 1.2V power supply                         |

| G13<br>G14 | GND            | G        | Connect DGND                                                           | Digital core 1.2V power supply<br>DGND                 |

| H1         | AGND           | G        | Connect AGND                                                           | AGND                                                   |

| H2         | AGND           | P        | Connect analog 3.3V power supply                                       | Analog 3.3V power supply                               |

| HZ<br>H3   | VDD33          | P        | Connect analog 3.3V power supply<br>Connect digital 3.3V power supply  | Digital 3.3V power supply                              |

| нз<br>H12  | VDD33          | P        | Connect digital 3.3V power supply<br>Connect digital 3.3V power supply | Digital 3.3V power supply<br>Digital 3.3V power supply |

| H12<br>H13 | AVDD           | P        | Connect analog 3.3V power supply                                       | Analog 3.3V power supply                               |

| H13<br>H14 | AVDD           | Р<br>G   | Connect analog 3.3V power supply<br>Connect AGND                       | Analog 3.3V power supply                               |

| H14<br>J1  | AGND           | -        | Connect AGND<br>Connect AGND                                           |                                                        |

|            |                | G        |                                                                        | AGND                                                   |

| J2<br>J3   | GND            | G<br>P   | Connect DGND                                                           | DGND                                                   |

| J3<br>J12  | VDD<br>VDD     | P        | Connect 1.2V power supply                                              | Digital core 1.2V power supply                         |

| -          |                | Р<br>G   | Connect 1.2V power supply                                              | Digital core 1.2V power supply                         |

| J13        | GND            | G        | Connect DGND                                                           |                                                        |

| J14        | AGNDSH         | G        | Connect AGND                                                           | AGND                                                   |

## Panasonic \_\_\_\_\_

| Pin No. | Pin name | I/O | Process                           | Functions                                 |

|---------|----------|-----|-----------------------------------|-------------------------------------------|

| K1      | TESTIO   | I/O | OPEN                              | Test                                      |

| K2      | GND      | G   | Connect DGND                      | DGND                                      |

| K3      | SDODB0P  | 0   | Connect latter device             | LVDS output(ch2 port0 data+)              |

| K4      | SDOCBP   | 0   | Connect latter device             | LVDS output(ch2 clock data+)              |

| K5      | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| K6      | SDODB1P  | 0   | Connect latter device             | LVDS output(ch2 port1 data+)              |

| K7      | SDODB2P  | 0   | OPEN                              | LVDS output(ch2 port2 data+)              |

| K8      | SDODA2P  | 0   | OPEN                              | LVDS output(ch1 port2 data+)              |

| K9      | SDODA1P  | 0   | Connect latter device             | LVDS output(ch1 port1 data+)              |

| K10     | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| K11     | SDOCAP   | 0   | Connect latter device             | LVDS output(ch1 clock data+)              |

| K12     | SDODA0P  | 0   | Connect latter device             | LVDS output(ch1 port0 data+)              |

| K13     | GND      | G   | Connect DGND                      | DGND                                      |

| K14     | TOUT2    | 0   | OPEN                              | Test                                      |

| L3      | SDODB0M  | 0   | Connect latter device             | LVDS output(ch2 port0 data-)              |

| L4      | SDOCBM   | 0   | Connect latter device             | LVDS output(ch2 clock data-)              |

| L5      | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| L6      | SDODB1M  | 0   | Connect latter device             | LVDS output(ch2 port1 data-)              |

| L7      | SDODB2M  | 0   | OPEN                              | LVDS output(ch2 port2 data-)              |

| L8      | SDODA2M  | 0   | OPEN                              | LVDS output(ch1 port2 data-)              |

| L9      | SDODA1M  | 0   | Connect latter device             | LVDS output(ch1 port1 data-)              |

| L10     | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| L11     | SDOCAM   | 0   | Connect latter device             | LVDS output(ch1 clock data-)              |

| L12     | SDODA0M  | 0   | Connect latter device             | LVDS output(ch1 port0 data-)              |

| M3      | GND      | G   | Connect DGND                      | DGND                                      |

| M4      | GND      | G   | Connect DGND                      | DGND                                      |

| M5      | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| M6      | VDD      | Р   | Connect 1.2V power supply         | Digital core 1.2V power supply            |

| M7      | GND      | G   | Connect DGND                      | DGND                                      |

| M8      | VREFRES1 | Ι   | Connect 12kΩ between DGND *1      | Reference resistance for internal circuit |

| M9      | VDD      | Р   | Connect 1.2V power supply         | Digital core 1.2V power supply            |

| M10     | VDD33    | Р   | Connect digital 3.3V power supply | Digital 3.3V power supply (LVDS)          |

| M11     | GND      | G   | Connect DGND                      | DGND                                      |

| M12     | GND      | G   | Connect DGND                      | DGND                                      |

\*1) Connect resistive element ( $12 \text{ k}\Omega \pm 0.5 \text{ \%}$ ) between VREFRES 1, 2, 3 pin and GND shown as Figure 1.2.1.

| Name        | Unit | Absolute Maximum<br>Ratings |             | Operati | Remarks  |         |                                        |

|-------------|------|-----------------------------|-------------|---------|----------|---------|----------------------------------------|

|             |      | Lower limit                 | Upper limit | Minimum | Standard | Maximum |                                        |

| AVDD        | V    | - 0.3                       | 4.5         | 3.15    | 3.3      | 3.45    | -                                      |

| VDD33       | V    | - 0.3                       | 4.5         | 3.15    | 3.3      | 3.45    | -                                      |

| VDD18       | V    | - 0.3                       | 2.5         | 1.62    | 1.8      | 1.98    | -                                      |

| VDD         | V    | - 0.3                       | 1.6         | 1.08    | 1.2      | 1.32    | -                                      |

| VCHP1       | v    | -                           | -           | -       | -        | -       | Voltage is<br>internally<br>generated. |

| VCHP2       | v    | -                           | -           | -       | -        | -       | Voltage is<br>internally<br>generated. |

| AGND<br>GND | V    | GND                         |             | -       | 0        | -       | -                                      |

#### Absolute Maximum Ratings and Operating Voltage Condition

Table 1.1.3 Values for Absolute Maximum Ratings and Operating Voltage Condition

• The absolute maximum ratings are the limit values applied to the chip, which do not lead to damage.

They shall not guarantee proper operation.

• Connect bypath ceramic capacitance  $(0.1\mu F)$  between all of power supply pins and GND nearby these pins. Connect also bypath ceramic capacitance (2.2 $\mu$ F or more) together.

#### Drive current

| Table 1.1.4 | Power supply current |

|-------------|----------------------|

|-------------|----------------------|

| Item          | Unit | Lower<br>limit | Standard | Upper<br>limit | Remarks                                                                                                                                                  |

|---------------|------|----------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDD current  | mA   | -              | 64       | 87             | VDD33 = AVDD = 3.3V、                                                                                                                                     |

| VDD33 current | mA   | -              | 20       | 22             | VDD18 = 1.8V、VDD=1.2V、                                                                                                                                   |

| VDD18 current | mA   | -              | 0.1      | 1              | Full scan, 60fps, 25°C,                                                                                                                                  |

| VDD current   | mA   | -              | 143      | 153            | Column amplifier gain = Standard,<br>Analog gain = 0dB,<br>Digital gain = 0dB, MCLK=27MHz,<br>Saturating illuminance,<br>Measured by tester of Panasonic |

#### Temperature Conditions

| Item                              | Unit | Lower limit | Standard | Upper limit | Remarks |

|-----------------------------------|------|-------------|----------|-------------|---------|

| Operating temperature             | °C   | -10         | 25       | 75          | (*1)    |

| Performance assurance temperature | °C   | 0           | 25       | 60          | (*2)    |

| Storage temperature               | °C   | -30         | 25       | 85          | (*3)    |

#### Table 1.1.5 Temperature Conditions

\*1 Operating temperature and storage temperature are defined by the temperature around the sensor. Operating temperature shall not guarantee the characteristics.

\*2 Performance assurance temperature is defined by the temperature of wafer. Characteristics are measured in 60°C (Wafer inspection), standard (Room temperature), 25°C (Final inspection). Other temperatures are assured as design guarantee.

\*3 Storage temperature is defined by the temperature of around the sensor.

### 1.2 Operation

### 1.2.1 List of Drive Mode

### Drive Mode

|           |        | Outp                   | ut                    |                                   | Frame Number of active Frame |          |           |            |           | rame format      |  |

|-----------|--------|------------------------|-----------------------|-----------------------------------|------------------------------|----------|-----------|------------|-----------|------------------|--|

| Mode      | MCLK   | ICLK Data<br>rate(MHz) |                       | Number of<br>ADC<br>output<br>bit | rate<br>(fps)                | H<br>pix | V<br>line | H<br>clock | V<br>line | HCYCLE<br>(MCLK) |  |

| Full acon | 27     | 162                    | 12bit<br>2ch<br>2port | 12                                | 60p                          | 1944     | 1092      | 2400       | 1125      | 400              |  |

| Full scan | 37.125 | 148.5                  | 12bit<br>2ch<br>2port | 12                                | 60p                          | 1944     | 1092      | 2200       | 1125      | 550              |  |

Table 1.2.1 Drive Mode (General)

X LVDS output data rate 486Mbps (MCLK:27MHz), 445.5Mbps (MCLK:37.125MHz)

\* HCYCLE in frame format shows the number of clock in pixel rate.

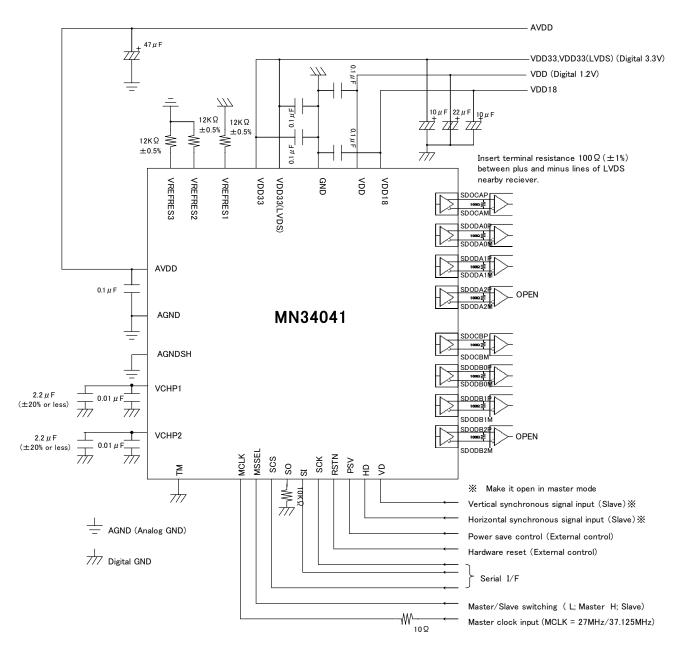

### 1.2.2 Reference Circuit

Figure 1.2.1 Reference circuit

Recommended Coupling Parts for Each Power Supply Pin (decoupling capacitor)

Apply decoupling capacitance (about  $0.1\mu$ F) with small parasitic series inductance to a pair of power supply and GND near the pin as possible to cut high-frequency noise.

For example, decoupling capacitances in four corners of the chip in each four pairs of AVDD and AGND are recommended.

Connect SO pin if need to read registers though it is not guaranteed.

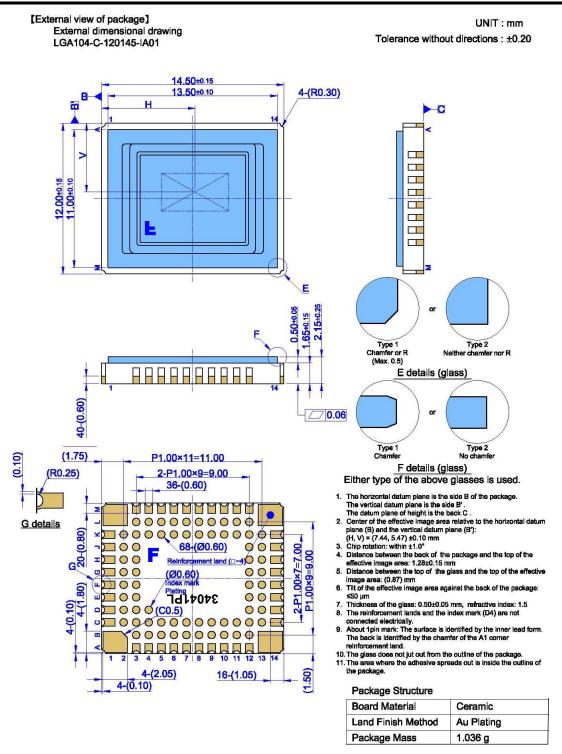

### 1.3 Package

### 1.3.1 Dimensions

Figure 1.3.1 Package Dimensions (LGA104-C-120145-IA01)

### Documents

**Panasonic**

This product has documents of data sheet, product detail specifications, specification of registers, and application notes necessary to set design.

If you need more information, please download documents from the web page or request it from semiconductor support system.

| Title                      | Explanation                                                  | MN34041                           |

|----------------------------|--------------------------------------------------------------|-----------------------------------|

| Datasheet                  | Product overview, application circuit, package outline, etc. | Download                          |

| Product specifications     | Detailed specifications, function, characteristic            | Contact Us (For Registered Users) |

| Register<br>specifications | Detailed specifications of registers                         | Contact Us (For Registered Users) |

| Application note           | Notes on the design for applications, etc.                   | Contact Us (For Registered Users) |

### Contact Us

### **Technical Inquiry**

If you want to ask about technical information in this document, please request from the contact with user registration.

Semiconductor Support (For Registered Users)

If you are not registered yet or access the page at first time, please click here.

### Sales Inquiry

As for the purchase, our worldwide sales companies are responsible for your support individually. (Such as delivery, last order, custom OEM business, quality, and environment, so on)

Sales Offices

If you want to learn more information, please visit to

Panasonic Imagesensor Homepage

## About Registration for Semiconductor Support Page

User ID (e-mail address) registration is needed for inquiry.

You are prohibited from using the products and the technical information on this Web site for development, production, use and storage of the Weapons of Mass Destruction (the nuclear weapons, the biological weapons, the chemical weapons and the missiles).

This Page...

...is for exclusive use by partners who trade in the OEM products described on "www.semicon.panasonic.co.jp", customer production facilities, and all related businesses.

Scope of Inquiries and Replies

On your first visit, register customer information and organizational affiliation so that we can supply better-tailored advice on customer design and development. Your personal information will never be divulged outside of the relevant industry group.

Replies are valid only for the customer and company concerned.

Passing the replies in whole or in part to a third party or for secondary use is strictly prohibited by copyright.

After you confirm the description of the above, please proceed to the user registration link below.

Click here to become a registered user

## Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for general applications (such as office equipment, communications equipment, measuring instruments and household appliances), or for specific applications as expressly stated in this book. Consult our sales staff in advance for information on the following applications:

• Special applications (such as for airplanes, aerospace, automotive equipment, traffic signaling equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

It is to be understood that our company shall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this book for any special application, unless our company agrees to your using the products in this book for any special application.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

(6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

(7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20100202