## **MN7100**

## 8 BIT 8 CHANNEL DATA ACQUISITION SYSTEM

## **FEATURES**

- Complete System Multiplexer Sample/Hold A/D Converter **Control Logic**

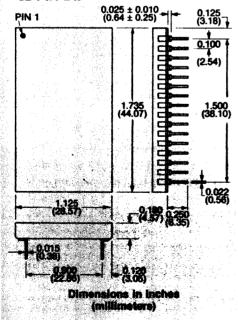

- Small 32 Pin DIP

- ± 1/2 LSB Linearity and No **Missing Codes Guaranteed Over Temperature**

- Random or Sequential Addressing

- 75.000 Channels/Sec Guaranteed

- Full Mil Operation -55°C to +125°C Available Fully Screened and **Processed to Method 5008** of MIL-STD-883

#### 32 PIN DIP

## DESCRIPTION

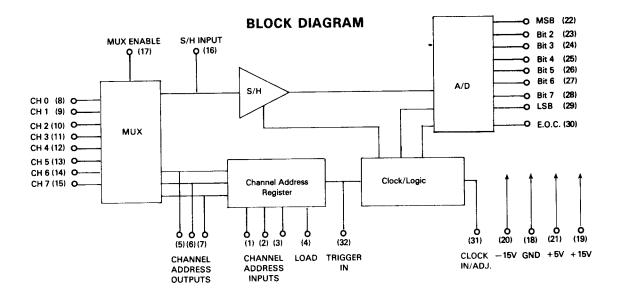

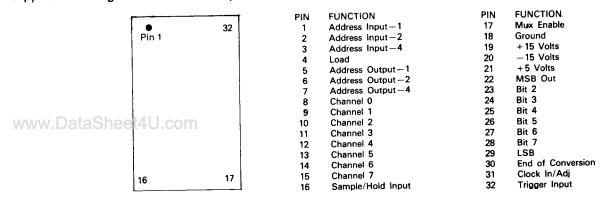

The MN7100 was the first complete, 8 Bit Data Acquisition System (DAS) ever offered in a Dual-In-Line package. It is a complete system including input Multiplexer with address register, Sample/Hold Amplifier (S/H), A/D Converter, clock and necessary controlling logic. Its eight input channels are either randomly or sequentially addressable and have an input impedance greater than 10 meg ohms.

The MN7100 is actively laser trimmed as a complete device eliminating normally annoying DAS errors such as S/H pedestal error. The system is adjustment-free. No external gain or offset adjusting potentiometers are required to guarantee an overall system error of better than  $\pm 1$  LSB at  $\pm 25$  °C and better than  $\pm 2$  LSB's over the entire operating temperature range.

The MN7100's S/H has an acquisition time of 6  $\mu$ Sec and the A/D conversion time of 7  $\mu$ Sec allows an overall throughput rate of over 75,000 channels/sec. Units may be ordered for either 0°C to +70°C or -55°C to +125°C operation and high reliability processing, screening, and qualification to the requirements of MIL-STD-883 Method 5008 are available for military/aerospace applications.

## **APPLICATIONS**

The MN7100 is easily expandable up to 256 channels using MN7110 multiplexer expanders or external multiplexers. Its small size and low power consumption make it ideally suited for industrial control and monitoring systems. Highly reliable thin-film hybrid construction, optional MIL-STD-883 screening, and performance specifications guaranteed from -55°C to +125°C make it the right choice for low resolution military/aerospace data acquisition requirements.

licro Networks Corporation 324 Clark Street, Worcester, Massachusetts 01606 • (617) 852-5400 A SUBSIDIARY OF UNITRODE CORPORATION

# MN7100 8 BIT 8 CHANNEL DATA ACQUISITION SYSTEM

## **ABSOLUTE MAXIMUM RATINGS**

Operating Temperature

Storage Temperature Positive Supply (Pin 19) Negative Supply (Pin 20) Logic Supply (Pin 21) Analog Inputs (Pins 8-15) Digital Inputs (Pins 1-4, 32) 0°C to +70°C

-55°C to +125°C ("H" Models)

-65°C to +150°C -0.5 to +18 Volts +0.5 to -18 Volts -0.5 to +7 Volts

±20 Volts -0.5 to +5.5 Volts ORDERING INFORMATION

MIL-STD-883.

- MN7100 H/B PART NUMBER -Standard device is specified for 0°C to +70°C operation. Add "H" suffix for -55°C to +125°C operation. -Add "/B" for 100% screening according to Method 5008 of

| SPECIFICATIONS (TA = 25°C, Voltage $\pm$ 15                                                                                                                | , +5, Unless Otherwise                                           | Noted)                               |                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------|--------------------------------------------|

|                                                                                                                                                            |                                                                  |                                      |                                            |

| Number of Channels<br>Input Voltage Range (Note 2)<br>Input Impedance<br>Direct S/H Input Impedance                                                        | 8 Single Ended<br>— 10 to + 10 Volts<br>10 meg Ohm<br>10 meg Ohm |                                      |                                            |

| TRANSFER CHARACTERSTICS:                                                                                                                                   |                                                                  |                                      |                                            |

| Resolution Quantization Error Linearity (0 to 70°C) Note 1 Zero Error (0 to 70°C) Note 1 Absolute Accuracy Absolute Accuracy (0 to 70°C) Note 1 Cross Talk | <b>-65</b>                                                       | 8<br>± ½<br>± ½<br>± 1<br>± 1<br>± 2 | Bits LSB LSB LSB LSB LSB LSB               |

| Cluss rain                                                                                                                                                 |                                                                  |                                      | <b>并是一种主持</b> 。于18                         |

| DYNAMIC CHARACTERISTICS:  Acquisition Time Aperature A/D Conversion Time Throughput Rate                                                                   | 5<br>50<br>6<br>90,000                                           | 6 7                                  | μ Sec<br>η Sec<br>μ Sec<br>Conversions/Sec |

| POWER REQUIREMENTS:                                                                                                                                        |                                                                  | Paragraph that                       |                                            |

| Current Drain + 15V Current Drain - 15V Current Drain + 5V                                                                                                 | 10<br>12<br>70                                                   | 16<br>25<br>110                      | mA<br>mA<br>mA<br>%FS/%PS                  |

| Supply Rejection + 15V<br>Supply Rejection - 15V<br>Supply Rejection + 5V                                                                                  | .04<br>.001<br>.001                                              |                                      | %FS/%PS<br>%FS/%PS                         |

| Power Consumption                                                                                                                                          | 680                                                              | 1165                                 | <b>mW</b>                                  |

Note 1. For "H" models, this specification applies over the  $-55^{\circ}$  C to  $+125^{\circ}$  C operating

Note 2. Contact factory for other available input voltage ranges.

## **LOGIC CODING**

|                                                 | (DC Volts) | 1 | MSB       | LSB   |  |

|-------------------------------------------------|------------|---|-----------|-------|--|

|                                                 | +10.000    |   | 1111 1111 |       |  |

| + 9.922                                         |            |   | 1111      | 1110* |  |

|                                                 | + 0.078    |   | 1000 (    | 0000* |  |

|                                                 | 0.000      |   | 0000      | 7000* |  |

|                                                 | - 0.078    |   | 0111      | 1110* |  |

|                                                 | - 9.922    |   | 0000      | 0000* |  |

| - 9.922<br>vvv DataSI <del>-</del> 10.000 I com |            |   | 0000 0000 |       |  |

\*Voltages given are the theoretical values for the transitions indicated. Ideally, with the system continuously sampling and converting, the output bits indicated as 0 will change from a "1" to a "0" or vice versa as the input voltage passes through the level indicated. The transition from digital output 0000 0000 to digital output 0000 0001 (or vice versa) will ideally occur at -9.922V. Subsequently, an input voltage more negative than 9.922V will give an output of all "0's". The transition from digital output 0111 1111 to digital output 1000 0000 (or vice versa) will ideally occur at an input of zero volts. The 1111 1110 to 1111 1111 transition should occur at +9.922V. An input greater than +9.922V should give all "1's".

IMPORTANT NOTICE: Micro Networks Corporation reserves the right to make improvements and changes in their products at any time, and cannot assume any responsibility for any circuits shown, or represent that they are free from patent infringement.

## **OPERATION**

## INPUTS:

The analog input signals are connected to the eight input channels. Input levels should not exceed  $\pm 10$  volts and it is recommended that unused channel inputs be grounded. Multiplex inputs may be expanded to 256 channels by addition of multiplexers and logic.

## ADDRESSING:

Both sequential and random addressing are available in the MN7100. For sequential addressing connect LOAD to logic "1", and the channels will sequence from Channel 0 to Channel 7, advancing one channel on the leading edge of each TRIGGER pulse. For random operation the desired channel address (in 4 2 1 binary coding) is applied to the CHANNEL ADDRESS inputs, and LOAD set to logic "0". The rising edge of the next TRIGGER input will update the channel address. The CHANNEL ADDRESS OUTPUTS provided indicate the last channel selected.

#### TRIGGERING:

The rising edge of a positive TRIGGER input pulse updates the channel address, the falling edge commands the sample-and-hold amplifier to the track mode and disables the system clock. E.O.C. is low. Turning off the clock reduces noise during signal acquisition. 6  $\mu$ Sec later the S/H goes into the hold mode and A/D conversion begins. E.O.C. now goes high. 7  $\mu$ Sec later the conversion is complete and E.O.C. drops low again.

#### CLOCK:

The MN7100 can be operated from its internal clock or from a user clock applied to the clock input. The internal clock is disabled during the analog acquisition time to reduce noise. External clocks should not exceed 400 nSec pulse widths or a 1.5 MHz repetition rate. In addition, the frequency of the internal clock can be varied by connection of one external resistor or capacitor. A resistor (20k Ohms or higher) connected from Pin 31 to the +5V Supply will increase the clock repetition rate inversely with resistance. A capacitor connected from Pin 31 to ground will decrease the clock rate directly with capacitance. The clock rate may be observed on Pin 31 as an RC charging waveform of approximately 0.5Vp. Loading at this point should be greater than 10 meg Ohms to avoid shifting the clock rate.

## **EXPANSION**

The MN7100 Data Aquisition System can be expanded to over 256 analog input channels with Micro Networks MN7110 Multiplexer Expanders. One MN7100 and one MN7110 form a complete 24 channel DAS in two small 32 pin dual-in-line packages, and additional MN7110's and a minimum of TTL Logic may be used for further expansion. Applications diagrams for channel expansion are shown on the MN7110 Data Sheet.

| TRIG IN -                                         |                           |                           |  |  |

|---------------------------------------------------|---------------------------|---------------------------|--|--|

|                                                   | RANDOM                    |                           |  |  |

| LOAD                                              | SEQUENTIAL MODE           | MODE                      |  |  |

|                                                   | - Sampling - Converting - | Output Valid              |  |  |

| EOC                                               |                           |                           |  |  |

| MSB                                               |                           |                           |  |  |

| BIT 2                                             |                           |                           |  |  |

| LSB                                               |                           |                           |  |  |

| CHANNEL<br>ADDRESS<br>INPUT<br>CHANNEL<br>ADDRESS | X                         | // Must Be Valid //////// |  |  |

| OUTPUT                                            |                           |                           |  |  |

| Digital<br>Inputs          | Logic<br>Signal       | Description                                           | Load<br>Presented        | Min.<br>Pulse<br>Width                                                                                                | Notes                                                                                                 |

|----------------------------|-----------------------|-------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Mux Enable                 | "1"                   | Enables Internal Mux                                  | 1 uA                     | Level                                                                                                                 | Tie to Logic "1" unless additional external MUX's are used for expansion.                             |

|                            | ''0''                 | Disables Internal MUX                                 | 1 uA                     |                                                                                                                       | Logic "0" < 0.4V<br>Logic "1" > 4.0V                                                                  |

| Channel Address<br>Inputs  | 3 Lines 421<br>Binary | Selects desired channel in random address mode        | TTL                      | 125 nSec.                                                                                                             | Must be set up 100 nSec<br>before clocking trigger and<br>be valid through rising edge<br>of trigger. |

| Load                       | "1"<br>"0"            | Sequential Address Mode<br>Random Address Mode        | TTL                      | Level                                                                                                                 | Data will be loaded on the first rising edge of trigger.                                              |

| Trigger                    | "0" to "1"            | Starts Data Acquisition<br>Process                    | TTL                      | 100 nSec.                                                                                                             |                                                                                                       |

| Clock                      |                       | System Clock                                          | 20 pf<br>Parallel<br>30k |                                                                                                                       | 1.5 MHz Max. Clock rate can be varied or an external clock used.                                      |

| Digital<br>Outputs         | Logic<br>Signal       | Description                                           | Max.<br>Load             | Notes                                                                                                                 |                                                                                                       |

| Data Outputs               | True Binary           | Parallel digital data outputs<br>8 lines MSB thru LSB | 6 TTL                    | Output data is valid after E.O.C. goes low.                                                                           |                                                                                                       |

| Channel Address<br>Outputs | 421 Binary            | Channel address outputs 3 lines                       | 3 TTL                    | Indicates channel being converted.                                                                                    |                                                                                                       |

| E.O.C.                     | "0"                   | Conversion process complete output data valid         | 6 TTL                    | E.O.C. goes to logic "1" 5 uSec after trigger<br>returns low and returns to logic "0" when<br>conversion is complete. |                                                                                                       |