# MP6630H 16V, 3-Phase Fan Driver with Integrated Hall Sensor

### DESCRIPTION

The MP6630H is a 3-phase brushless DC motor driver with integrated power MOSFETs and single Hall-effect sensor. The input voltage ranges from 2V to 16V.

The device controls the motor speed through the PWM signal on the PWM pin. It features a single, embedded Hall-effect sensor for robust start-up performance. It also features 180° full-wave sinusoidal drive for high efficiency, and lowspeed ripple and vibration over the full speed range.

The MP6630H also has a rotational speed detector. The rotational speed detector (the FG/RD pin) is the output of an open drain. This pin is also selectable for lock indication output.

Rich protections are implemented in the MP6630H, such as under-voltage lockout (UVLO), locked-rotor protection, over-current protection (OCP), and thermal shutdown protection.

The MP6630H is available in a UTQFN-8 (2mmx3mm) package.

### **FEATURES**

- Wide 2V to 16V Operating Input Range •

- 180° Full-Wave Sinusoidal Drive for High Efficiency and Low-Speed Vibration

- Embedded Single Hall Sensor to Ensure • Robust Start-Up

- Integrated Power MOSFETs: About 400mΩ • Each

- 0.5s/5s Rotor Lock and Retry Protection

- 1kHz to 100kHz PWM Input Range

- **Direction Input** •

- Soft Start

- Fixed 25kHz Output Switching Frequency •

- Selectable Output for Speed Indication (FG) and Lock Indication (RD)

- Standby Mode to Save Power

- Thermal Protection and Auto-Recovery •

- Typically 2.3A of Maximum Peak Current

- Available in a UTQFN-8 (2mmxmm) Package

## APPLICATIONS

- **3-Phase BLDC Fans**

- Gaming Fans

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

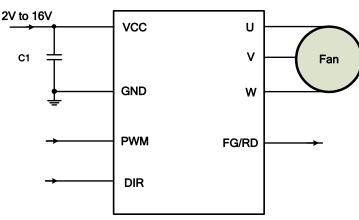

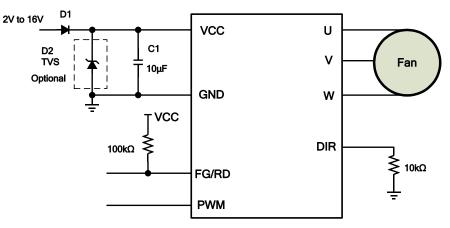

### TYPICAL APPLICATION

### **ORDERING INFORMATION**

| Part Number*      | Package           | Top Marking | MSL Rating |

|-------------------|-------------------|-------------|------------|

| MP6630HGDU-xxxx** | UTQFN-8 (2mmx3mm) | See Below   | 1          |

\* For Tape & Reel, add suffix -Z (e.g. MP6630HGDU-xxxx-Z).

\*\* "xxxx" is the configuration code identifier. The first four digits of the suffix (xxxx) can be a hexadecimal value between 0 and F. Work with an MPS FAE to create this unique number for non-default functionality. The default function value is -0000.

# TOP MARKING

# BLTY

LLL

BLT: Product code of MP6630HGDU-xxxx Y: Year code LLL: Lot number

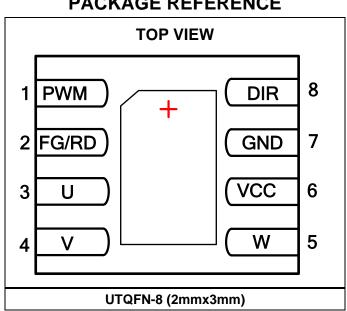

### PACKAGE REFERENCE

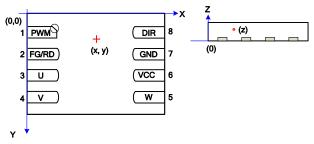

### **PIN FUNCTIONS**

| Pin #                                                                                                                       | Name | Description                                                                                                                                                                           |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1                                                                                                                           | PWM  | <b>Rotational speed control and PWM input pin.</b> 1kHz to 100kHz is the recommended maximum PWM resolution. Internally pull PWM up to the internal LDO with a $100k\Omega$ resistor. |  |  |  |  |  |

| 2 FG/RD Speed or rotor lock indication. Open-drain output. FG/RD can be used for spe<br>(FG) or rotor lock indication (RD). |      |                                                                                                                                                                                       |  |  |  |  |  |

| 3                                                                                                                           | U    | U phase terminal.                                                                                                                                                                     |  |  |  |  |  |

| 4                                                                                                                           | V    | V phase terminal.                                                                                                                                                                     |  |  |  |  |  |

| 5                                                                                                                           | W    | W phase terminal.                                                                                                                                                                     |  |  |  |  |  |

| 6                                                                                                                           | VCC  | Input power pin. VCC requires a bypass capacitor placed as close to VCC and GND as possible.                                                                                          |  |  |  |  |  |

| 7                                                                                                                           | GND  | Ground pin.                                                                                                                                                                           |  |  |  |  |  |

| 8                                                                                                                           | DIR  | <b>Direction control pin.</b> Internally pull DIR low with a $100k\Omega$ resistor.                                                                                                   |  |  |  |  |  |

### ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>CC</sub> , V <sub>U/V/W</sub> , FG/RD, PWM, DIR0.3V to +18V |

|--------------------------------------------------------------------|

| Continuous power dissipation $(T_A = 25^{\circ}C)^{(2)}$           |

|                                                                    |

| hunstion to management und                                         |

| Junction temperature | 150°C           |

|----------------------|-----------------|

| Lead temperature     | 260°C           |

| Storage temperature  | -60°C to +150°C |

### ESD Rating

| Human body model (HBM)     | ±1500V |

|----------------------------|--------|

| Charged device model (CDM) | ±2000V |

#### **Recommended Operating Conditions** <sup>(3)</sup>

| Supply voltage (V <sub>CC</sub> ) | 2V to 16V                       |

|-----------------------------------|---------------------------------|

| Operating junction temp           | (T <sub>J</sub> )40°C to +125°C |

# **Thermal Resistance** (4) $\theta_{JA}$ $\theta_{JC}$

UTQFN-8 (2mmx3mm).....65.....13....°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-toambient thermal resistance,  $\theta_{JA}$ , and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) - T<sub>A</sub>) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 12V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameters                                        | Symbol              | Condition                                       | Min  | Тур | Max  | Units |

|---------------------------------------------------|---------------------|-------------------------------------------------|------|-----|------|-------|

| Input UVLO rising threshold                       | Vuvlo               |                                                 |      | 1.7 | 1.8  | V     |

| Input UVLO hysteresis                             |                     |                                                 |      | 0.1 |      | V     |

| Operating supply current                          | lcc                 |                                                 |      | 6   | 7    | mA    |

| Standby supply current                            | Icc                 | PWM = low > 100ms                               |      | 225 | 300  | μA    |

| PWM/DIR input high voltage                        | Vlogic_h            |                                                 | 1.5  |     |      | V     |

| PWM/DIR input low voltage                         | VLOGIC_L            |                                                 |      |     | 0.4  | V     |

| PWM input internal pull-high resistance           | Rpwm                |                                                 |      | 100 |      | kΩ    |

| DIR internal pull-down resistance                 | R <sub>DIR</sub>    |                                                 |      | 100 |      | kΩ    |

|                                                   | R <sub>HSON_U</sub> |                                                 |      | 400 |      |       |

| HS switch on resistance                           | RHSON_V             | l₀ = 100mA, TJ = 25°C                           |      | 390 |      | mΩ    |

|                                                   | Rhson_w             |                                                 |      | 358 |      |       |

|                                                   | RLSON_U             |                                                 |      | 434 |      |       |

| LS switch on resistance                           | RLSON_V             | $I_0 = 100 \text{mA}, T_J = 25^{\circ}\text{C}$ |      | 405 |      | mΩ    |

|                                                   | RLSON_W             |                                                 |      | 402 |      |       |

| Phase A zero-current detection                    | Izcd                |                                                 | -2   | 0   | +2   | mA    |

| Maximum current limit                             | ILMT                | Full scale                                      |      | 2.3 |      | Α     |

| PWM output frequency                              | f <sub>S₩</sub>     | $T_J = 25^{\circ}C$                             | 24.5 | 25  | 25.5 | kHz   |

| FG output low-level voltage                       | $V_{FG_L}$          | $I_{FG/RD} = 3mA, V_{PULL} = 5V$                |      |     | 0.35 | V     |

| Rotor-lock detection time                         | t <sub>RD</sub>     |                                                 |      | 0.5 |      | S     |

| Minimum recommended magnetic field <sup>(5)</sup> |                     |                                                 |      |     | ±2   | mT    |

| Thermal shutdown threshold                        |                     |                                                 |      | 160 |      | °C    |

| Thermal shutdown<br>hysteresis <sup>(5)</sup>     |                     |                                                 |      | 20  |      | °C    |

Note:

5) Guaranteed by design.

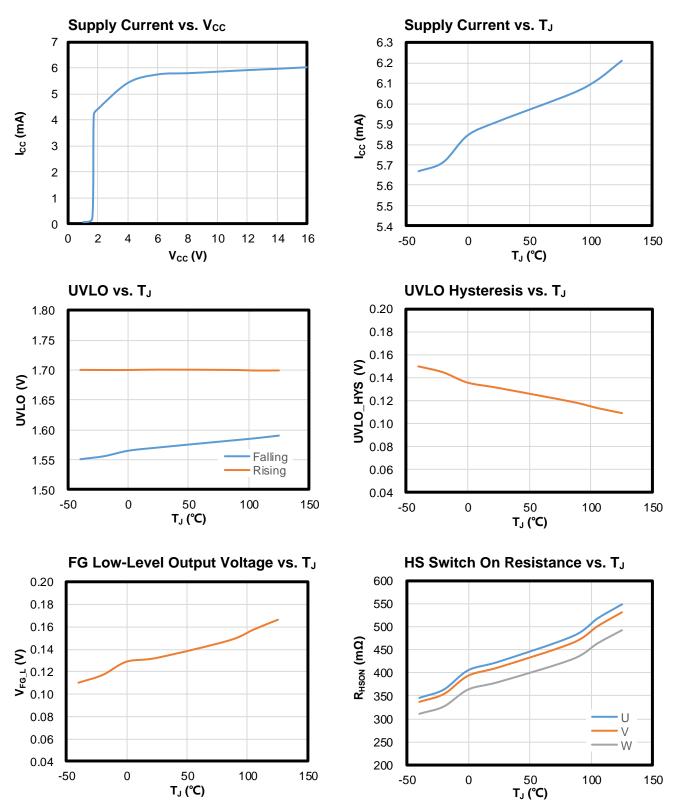

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

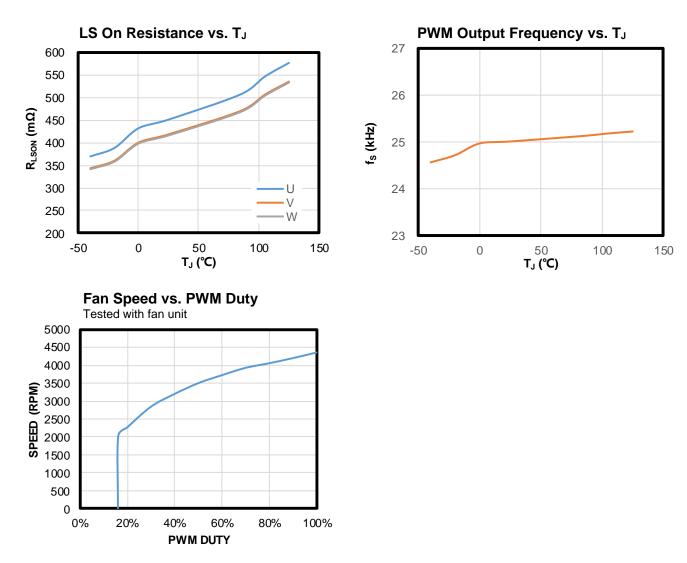

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{CC}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

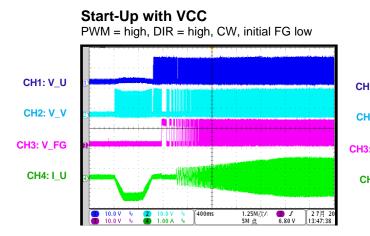

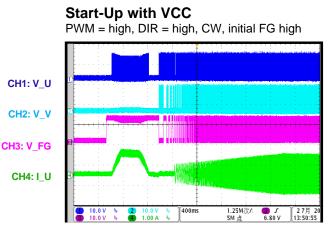

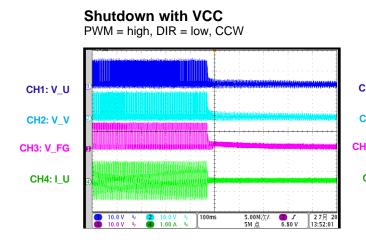

$V_{CC}$  = 12V,  $T_A$  = 25°C, unless otherwise noted.

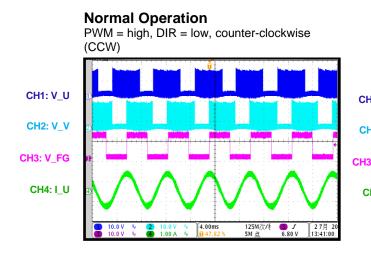

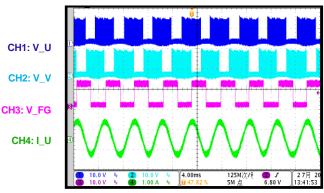

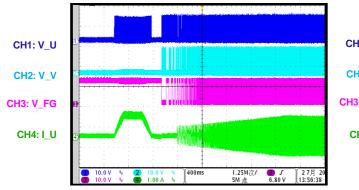

**Normal Operation**

PWM = high, DIR = high, clockwise (CW)

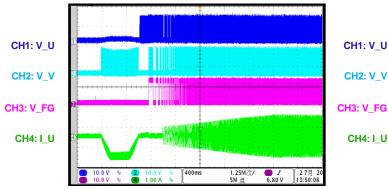

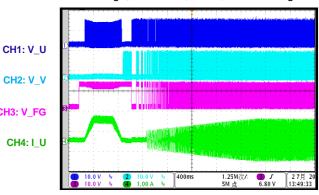

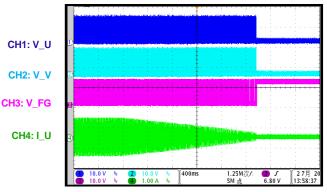

Start-Up with VCC PWM = high, DIR = low, CCW, initial FG low

Start-Up with VCC PWM = high, DIR = low, CCW, initial FG high

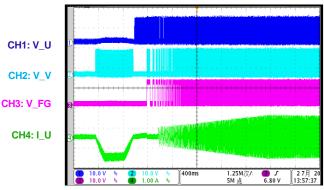

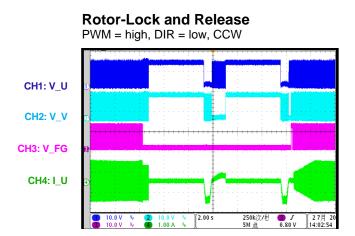

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{CC} = 12V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

Start-Up with PWM

PWM duty jumps from 1% to 100%, DIR = low, CCW, initial FG low

# Start-Up with PWM

PWM duty jumps from 1% to 100%, DIR = high, CW, initial FG high

#### Shutdown with PWM

PWM duty jump from 100% to 0, DIR = low, CCW, IC enters standby mode

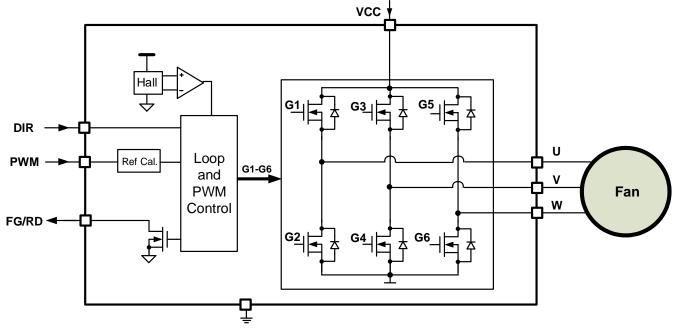

# FUNCTIONAL BLOCK DIAGRAM

# **OPERATION**

The MP6630H is a three-phase, brushless DC motor driver with integrated power MOSFETs and a single Hall-effect sensor. The IC detects the PWM duty on the PWM pin for speed control. This optimizes efficiency and ripple speed over the full speed range. The embedded Hall-effect sensor provides robust start-up performance.

Speed indication and rotor-lock indication signals are selectable outputs on the FG/RD pin.

Rich protection functions are embedded in the MP6630H, such as under-voltage lockout (UVLO), rotor-lock protection, over-current protection (OCP), and thermal shutdown protection.

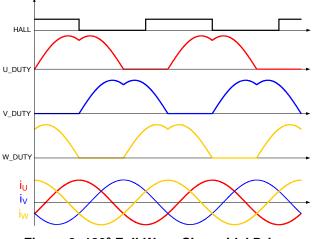

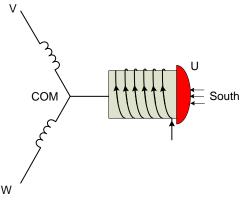

#### 180° Full-wave Sinusoidal Drive

An embedded Hall sensor is integrated in MP6630H, which is used to rotor position detection. The 180° full-wave sinusoid drive is employed as showing in figure 2.

Figure 2: 180° Full-Wave Sinusoidal Drive

#### **Speed Control**

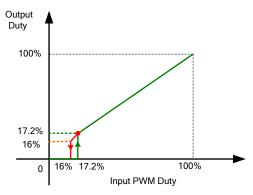

The PWM signal on the PWM pin accepts a wide input frequency range (1kHz to 100kHz). The IC adjusts motor speed by detecting the PWM signal duty cycle.

In this mode, the OUTU/V/W maximum output duty cycle directly depends on the PWM input duty. When the PWM input duty exceeds the starting duty set by DMIN[5:0], the fan keeps rotating. When the PWM input duty is below the starting duty with 1.2% hysteresis, the fan stops rotating, or keeps the minimum speed depending the SPD\_ZERO bit.

For example, if SPD\_ZERO = 1, and DMIN[5:0] = 0x16 (17.2%), the fan stops rotating when the input duty is below 16%. If the input duty exceeds 17.2% (hysteresis 1.2%), the fan starts rotating.

Figure 3: Minimum Duty when SPD\_ZERO = 1

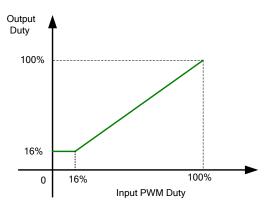

If SPD\_ZERO = 0 in the previous example, the fan maintains a minimum speed when the input duty is below 16%.

Figure 4: Minimum Duty when SPD\_ZERO = 0

#### Soft-Start Time

To smoothly change the fan speed and reduce the input inrush current during start-up, the MP6630H provides a soft-start time and speed reference. The output duty ramps up or down by following the TSS bit. The soft-start timer can be configured to 2.6s (default) or 5.2s.

#### **Initial Rotor Positioning**

At the beginning of start-up, the MP6630H initiates rotor positioning to align the rotor with a known position. The aligning time is about 320ms.

#### **Pre-Startup**

After rotor alignment, the MP6630H enters a prestartup stage, and a certain voltage vector is used to make fan rotate. In the pre-startup stage, the output duty is increased step by step. The time between two steps is 5.13ms.

#### **Speed Indication Output**

The FG signal on the FG/RD pin outputs an internal Hall change signal for speed indication. A 1x or 1/2x Hall frequency output can be selected. The FG/RD pin is an open drain, and must be externally pulled high during normal operation.

#### **Direction Control**

The DIR pin is used to control the rotating direction. If DIR is pulled low, the fan moves in forward rotation. If DIR is pulled high, the fan moves in reverse rotation.

The DIR pin is internally pulled low by a resistor. To stop noise from affecting the DIR pin's polarity, pull DIR low or high with a resistor.

Do not change the fan's direction while it is rotating. This could cause the fan to vibrate or stop entirely.

#### **Maximum Current Limit Protection**

If a phase current exceeds 2.3A for a 1.5µs blanking time, all MOSFETs turn off immediately. The IC is re-enabled automatically after a minimum 93ms.

#### **Rotor-Lock Protection**

If the motor's rotor is locked, the MP6630H shuts down all high-side MOSFETs (HS-FETs). The HS-FETs turn on once a Hall edge goes undetected for 0.5ms. Meanwhile, if FG/RD is set as rotor-lock indicator, the FG/RD output is pulled low for fault indication. The IC autorestarts after a 5s recovery time.

#### **Thermal Shutdown**

If the die temperature of MP6630H exceeds 160°C, all MOSFETs turn off. Once the die temperature drops below 140°C, the IC resumes normal operation.

#### Under-Voltage Lockout (UVLO)

If the voltage on the VCC pin falls below the under-voltage lockout (UVLO) threshold, all circuitry in the device is disabled and the internal logic is reset. Normal operation resumes when V<sub>CC</sub> rises above the UVLO threshold.

#### Standby Mode

If the PWM input is kept low for longer than 100ms, the MP6630H enters standby mode when the fan stops rotating. In standby mode, only PWM input detection and online test mode detection are active. When the IC detects PWM at a high level again, the IC restarts and resumes normal operation.

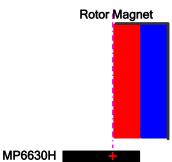

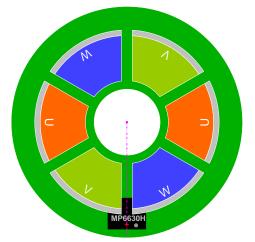

#### Hall Sensor Location

Figure 5 shows the internal Hall sensor cell location.

#### Figure 5: Hall Position

Where x =  $1500\mu m \pm 30\mu m$ , y =  $550\mu m \pm m0\mu m$ , and z =  $380\mu m \pm 25\mu m$ .

# **APPLICATION INFORMATION**

#### Selecting the Input Capacitor

Place an input capacitor (C1) near VCC to keep the input voltage stable and reduce input switching voltage noise and ripple. The input capacitor impedance must be low at the switching frequency. Ceramic capacitors with X7R dielectrics are recommended for their low ESR.

Ensure that the ceramic capacitance is dependent on the voltage rating. The DC bias voltage can lose as much as 50% of its capacitance at its rated voltage rating. Leave a sufficient voltage rating margin when selecting the component.

For most applications, a  $10\mu$ F ceramic capacitor is sufficient. If required for the application, add an additional, large electrolytic capacitor to absorb inductor energy.

#### Input Clamping TVS

High-voltage spikes are caused by the energy stored in the motor inductor charging back to the input capacitor side. To avoid these spikes, add a voltage-clamping transient voltage suppressor (TVS) diode. For a 12V application, an 15V/SOD-123 package TVS diode is sufficient.

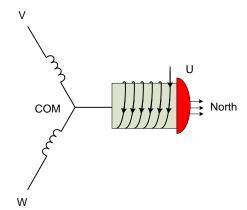

#### Hall Polarity Selection

The Hall polarity can be configured. The Hall polarity depends on the winding direction and where the is IC mounted (the top or bottom of the PCB). Magnetic south is generated at the stator if the winding direction is normal and the current goes from U to the common node (COM) (see Figure 6).

Figure 6: Magnetic South with Winding Direction

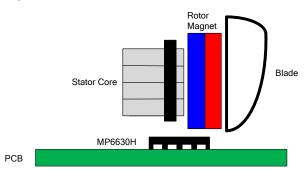

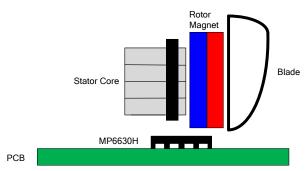

If the IC is mounted to the top side of the PCB, use the default Hall polarity  $(HAL_POL = 0)$  (see Figure 7).

Figure 7: Side View of MP6630H on Top of PCB

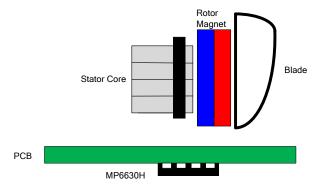

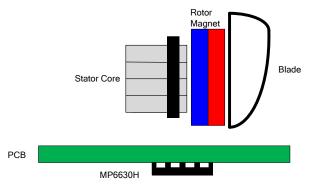

If the IC is mounted on the bottom side of the PCB, use the opposite Hall polarity (HAL\_POL = 1) (see Figure 8).

# Figure 8: Side View of MP6630H on Bottom of PCB

If the winding direction is different, and the current flows from U to the common node (COM), magnetic north is generated at stator (see Figure 9).

Figure 9: Magnetic North with Winding Direction

If the IC is mounted on the top of the PCB with different winding, use opposite Hall polarity  $(HAL_POL = 1)$  (see Figure 10).

Figure 10: Side View of MP6630H on Top of PCB with Different Winding

If the IC is mounted on the bottom of the PCB with different winding, use the default Hall polarity  $(HAL_POL = 0)$  (see Figure 11).

Figure 11: Side View of MP6630H on Bottom of PCB with Different Winding

#### **PCB Layout Guidelines**

The internal Hall element requires the correct magnetic field for normal operation. For the best results, refer to Figure 12 and Figure 13, and follow the guidelines below:

1. Ensure the MP6630H is aligned with the highest magnetic field possible. Generally,

the inner surface of the rotor magnet provides the highest magnetic field strength.

2. Align the internal Hall element with the inner surface of the rotor magnet (see Figure 12).

#### Figure 12: Aligning the Hall Element with Inner Surface of Rotor Magnet (Side View)

3. Align the internal Hall element with the central line of winding V and winding W to achieve maximum operating efficiency (see Figure 13).

Figure 13: Aligning the Hall Element along the Central Line of Winding V and Winding W (Top View)

### **REGISTER MAP**

| Add  | Default | D7  | D6       | D5   | D4 | D3      | D2 | D1  | D0 |

|------|---------|-----|----------|------|----|---------|----|-----|----|

| 0x00 | 0x56    | TSS | SPD_ZERO | DMIN |    |         |    |     |    |

| 0x01 | 0x60    |     | NA       |      |    | HAL_POL | NA | FGF | RD |

#### Register Table 1

|     | Addr: 0x00 |         |         |                                                                                                                                                                                                                                                              |  |  |  |  |  |

|-----|------------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit | Bit Name   | Access  | Default | Description                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 7   | TSS        | OTP/REG | 0       | Soft-start timer. The timer for the output duty reference, from 0% to 100%, or 100% to 0%.<br>0: 2.6s<br>1: 5.2s                                                                                                                                             |  |  |  |  |  |

| 6   | SPD_ZERO   | OTP/REG | 1       | <ul><li>Zero-speed enable bits. There is 1.2% hysteresis for the starting duty.</li><li>0: Disable. The motor does not stop when the duty is below the starting duty</li><li>1: Enable. The motor stops when the duty is below the starting duty</li></ul>   |  |  |  |  |  |

| 5:0 | DMIN[5:0]  | OTP/REG | 0x16    | Starting duty set bits. U/V/W starts to output duty when the input<br>duty exceeds the starting duty. The default duty is 17.2% with a<br>1.2% hysteresis. The starting duty can be calculated with the<br>following equation:<br>Starting duty = DMIN / 128 |  |  |  |  |  |

#### Register Table 2

|     | Addr: 0x01 |          |         |                                                                  |  |  |  |  |  |

|-----|------------|----------|---------|------------------------------------------------------------------|--|--|--|--|--|

| Bit | Bit Name   | Access   | Default | Description                                                      |  |  |  |  |  |

| 7:4 | N/A        | RESERVED | 0110    | Reserved.                                                        |  |  |  |  |  |

|     |            |          |         | Hall polarity set bit (see page 12 for more details).            |  |  |  |  |  |

| 3   | HAL_POL    | OTP/REG  | 0       | 0: Default<br>1: Opposite Hall output                            |  |  |  |  |  |

| 2   | N/A        | RESERVED | 0       | Reserved.                                                        |  |  |  |  |  |

|     |            |          |         | FG/RD set bit. This bit sets the output signal on the FG/RD pin. |  |  |  |  |  |

| 1:0 | FGRD[1:0]  | OTP/REG  | 00      | 00: 1x FG output<br>01: 1/2x FG output<br>10: RD                 |  |  |  |  |  |

.

# **TYPICAL APPLICATION CIRCUIT**

Figure 14: Typical Application Circuit

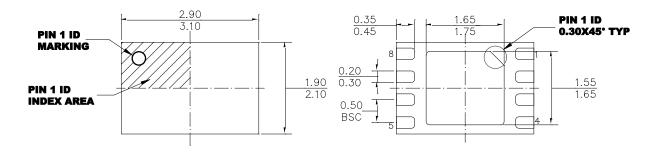

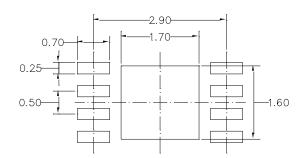

### PACKAGE INFORMATION

UTQFN-8 (2mmx3mm)

TOP VIEW

<u>SIDE VIEW</u>

**RECOMMENDED LAND PATTERN**

#### NOTE:

ALL DIMENSIONS ARE IN MILLIMETERS.

EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

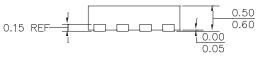

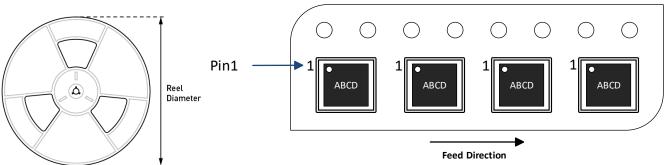

# **CARRIER INFORMATION**

| Part Number       | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch | Trailer<br>Leader/<br>Reel |

|-------------------|------------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|----------------------------|

| MP6630HGDU-xxxx** | UTQFN-8<br>(2mmx3mm)   | 5000              | N/A               | 13in             | 12mm                     | 8mm                      | 125 & 125                  |

# **REVISION HISTORY**

| Revision # | <b>Revision Date</b> | Description                                                              | Pages Updated         |

|------------|----------------------|--------------------------------------------------------------------------|-----------------------|

| 1.0        | 4/27/2020            | Initial Release                                                          | -                     |

| 1.01       | 8/17/2020            | Add "180° full-wave sinusoidal drive" description                        | 1, 10                 |

|            | 40/4/0000            | Updated "Typically 2.3A of Maximum Peak Current" in the Features section | 1                     |

| 1.1        | 12/4/2023            | Updated "–Z" to "-Z"                                                     | 2                     |

|            |                      | Corrected formatting in Revision History                                 | 1, 10<br>1<br>2<br>18 |

**Notice:** The information in this document is subject to change without notice. Users should warrant and guarantee that thirdparty Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.