Triple 10-bit High Speed Analog-to-Digital Converter with Digitally Controlled References

#### FEATURES

- 3 Independent 10-bit ADCs

- Simultaneous Sampling @ 1.25 MSPS

- Independent Digitally Controlled References

- 9-bit Positive Reference and 6-bit Negative Reference Adjustment per Sample

- Low Power: 500mW (typ)

- Internal Track and Hold

- Single 5 V Supply

- Fast Mode for OCR

- AIN Input Range: 1.3 V to 2.6 V p-p

- Black Level Clamp

- Latch-Up Free

- ESD Protection: 2000 V Minimum

#### BENEFITS

- Pixel-to-Pixel Correction

- Improves Effective Resolution over Software Correction Schemes

- Reduced DSP/Processor Demands

- Reduction of Parts Count and System Cost

#### APPLICATIONS

- Precision CCD Systems

- Color and B&W Scanners

- Digital Copiers

- IR Cameras

#### **GENERAL DESCRIPTION**

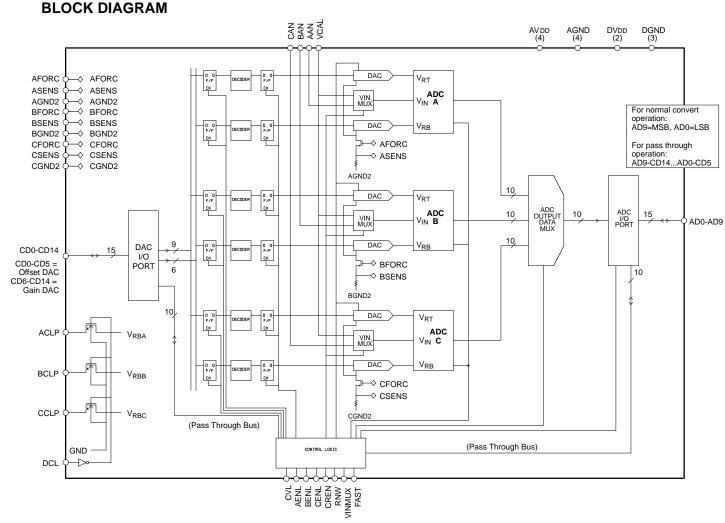

The MP8830 is a simultaneous sampling 1.25 MSPS triple 10-bit A/D Converter. It provides pixel-to-pixel correction of CCD or other inputs by updating gain and offset parameters supplied from an external correction memory. Each ADC has a 9-bit DAC driving its positive reference voltage and a 6-bit DAC driving its negative reference to independently adjust the gain and offset of each channel.

The MP8830 uses ADCs with a subranging architecture to maintain low power consumption at high conversion rates. Our proprietary comparator design achieves a low analog input ca-

pacitance and performs an on-chip sample and hold function. The MP8830 uses proprietary high speed DACs to drive the ADC references which allows reference adjustment on every conversion at a 1.25 MHz rate. An internal clamp is available for DC restoration of  $A_{\rm IN}$  black level.

The MP8830 operates from a single 5 V supply and an external 1 V reference, and consumes only 500mW of power (typ).

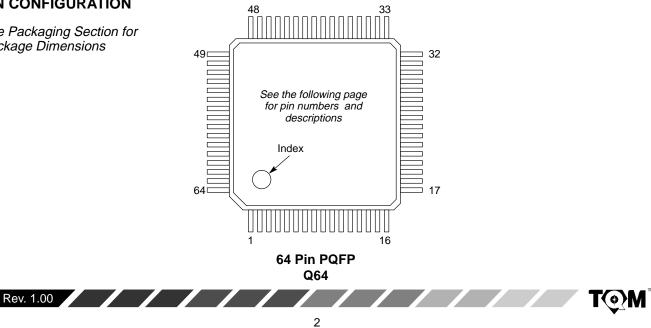

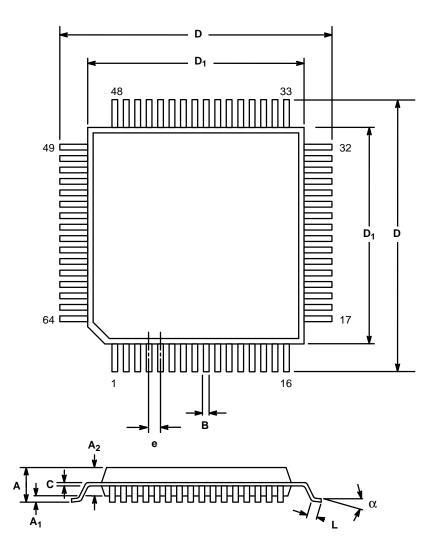

Specified for operation over the temperature range 0 to 60°C, the MP8830 is available in a 64 lead Plastic Quad Flat Pack (PQFP) package.

#### **ORDERING INFORMATION**

| Package<br>Type | Temperature<br>Range | Part No. |  |  |

|-----------------|----------------------|----------|--|--|

| PQFP            | 0 to +60°C           | MP8830AE |  |  |

## **MP8830 XPEXAR**

## **PIN CONFIGURATION**

See Packaging Section for Package Dimensions

## **PIN OUT DEFINITIONS**

| PIN NO. | NAME             | DESCRIPTION                                  | PIN NO. | NAME             | DESCRIPTION                                  |

|---------|------------------|----------------------------------------------|---------|------------------|----------------------------------------------|

| 1       | DV <sub>DD</sub> | Digital Positive Power Supply                | 33      | ASENS            | Sensing Voltage for Biasing the              |

| 2       | CD14             | DAC Input Pin 14                             | 24      | AFORC            | A Channel                                    |

| 3       | CD13             | DAC Input Pin 13                             | 34      | AFORC            | Forcing Voltage for Biasing the<br>A Channel |

| 4       | CD12             | DAC Input Pin 12                             | 35      | AAN              | A Channel Analog Input                       |

| 5       | CD11             | DAC Input Pin 11                             | 36      | AGND1            | Analog Negative Power Supply                 |

| 6       | CD10             | DAC Input Pin 10                             | 37      | ACLP             | Clamp Voltage A                              |

| 7       | CD9              | DAC Input Pin 9                              | 38      | VCAL             | Calibration Input Voltage                    |

| 8       | CD8              | DAC Input Pin 8                              | 39      | VINMX            | Analog Mux Control                           |

| 9       | CD7              | DAC Input Pin 7                              | 40      | DGND             | Digital Negative Power Supply                |

| 10      | CD6              | DAC Input Pin 6                              | 41      | DCL              | Black Level Clamp Control                    |

| 11      | CD5              | DAC Input Pin 5                              |         |                  | (Active Low)                                 |

| 12      | CD4              | DAC Input Pin 4                              | 42      | N/C              | No Connection                                |

| 13      | CD3              | DAC Input Pin 3                              | 43      | DGND             | Digital Negative Power Supply                |

| 14      | CD2              | DAC Input Pin 2                              | 44      | DV <sub>DD</sub> | Digital Positive Power Supply                |

| 15      | CD1              | DAC Input Pin 1                              | 45      | FAST             | FAST Mode Enable                             |

| 16      | CD0              | DAC Input Pin 0                              | 46      | GND3             | Analog Negative Power Supply                 |

| 17      | CV <sub>DD</sub> | Analog Positive Power Supply                 | 47      | V <sub>DD3</sub> | Analog Positive Power Supply                 |

| 18      | CSENS            | Sensing Voltage for Biasing the              | 48      | CREN             | Pass Through Mode Enable                     |

|         |                  | C Channel                                    | 49      | RNW              | READ not WRITE                               |

| 19      | CFORC            | Forcing Voltage for Biasing the<br>C Channel | 50      | CENL             | Channel C Data Clock                         |

| 20      | CAN              | C Channel Analog Input                       | 51      | BENL             | Channel B Data Clock                         |

| 21      | CGND2            | Analog Ground Related to                     | 52      | AENL             | Channel A Data Clock                         |

|         | 00.122           | DAC Bias                                     | 53      | CVL              | Cycle Clock                                  |

| 22      | CCLP             | Clamp Voltage C                              | 54      | AD9              | ADC Data Output 9                            |

| 23      | CGND1            | Analog Negative Power Supply                 | 55      | AD8              | ADC Data Output 8                            |

| 24      | BV <sub>DD</sub> | Analog Positive Power Supply                 | 56      | AD7              | ADC Data Output 7                            |

| 25      | BSENS            | Sensing Voltage for Biasing the              | 57      | AD6              | ADC Data Output 6                            |

|         |                  | B Channel                                    | 58      | AD5              | ADC Data Output 5                            |

| 26      | BFORC            | Forcing Voltage for Biasing the<br>B Channel | 59      | AD4              | ADC Data Output 4                            |

| 27      | BAN              | B Channel Analog Input                       | 60      | AD3              | ADC Data Output 3                            |

| 28      | BGND2            | Analog Ground Related to                     | 61      | AD2              | ADC Data Output 2                            |

|         |                  | DAC Bias                                     | 62      | AD1              | ADC Data Output 1                            |

| 29      | BCLP             | Clamp Voltage B                              | 63      | AD0              | ADC Data Output 0                            |

| 30      | BGND1            | Analog Negative Power Supply                 | 64      | DGND             | Digital Negative Power Supply                |

| 31      | $AV_{DD}$        | Analog Positive Power Supply                 |         |                  |                                              |

| 32      | AGND2            | Analog Ground Related to<br>DAC Bias         |         |                  |                                              |

|         |                  |                                              |         |                  |                                              |

Note: All digital signals are active high unless otherwise noted.

## ELECTRICAL CHARACTERISTICS

# Unless otherwise specified: AV\_{DD} = DV\_{DD}= 5 V, DGND = AGND = 0 V, V\_{REF} = AV\_{DD} \times 0.2 Temperature = 0 to 60°C<sup>1</sup>

/ / / / / /

| A/D Converters                                                 |                  |              |       |                           |       |                                                                                                                                                                                                                          |

|----------------------------------------------------------------|------------------|--------------|-------|---------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                      | Symbol           | Min          | Тур   | Мах                       | Units | Test Conditions/Comments                                                                                                                                                                                                 |

| Resolution                                                     | N                | 10           |       |                           | Bits  |                                                                                                                                                                                                                          |

| Differential Non-Linearity                                     | DNL              | -1           | ±0.75 | 2                         | LSB   | Gain DAC = 000 (hex), offset DAC = 00 (hex).<br>Monotonicity guaranteed.                                                                                                                                                 |

| Differential Non-Linearity                                     | DNL              | -1           | ±0.5  | 2                         | LSB   | Gain DAC = 1FF (hex), offset DAC = 00 (hex).<br>Monotonicity guaranteed.                                                                                                                                                 |

| Integral Non-Linearity                                         | INL              |              | 2     | 2.75                      | LSB   | Gain DAC = 000 (hex), offset DAC = 00 (hex),<br>Best fit straight line.                                                                                                                                                  |

| Integral Non-Linearity                                         | INL              |              | 1.5   | 2                         | LSB   | Gain DAC = 1FF (hex), offset DAC = 00 (hex),<br>Best fit straight line.                                                                                                                                                  |

| Zero Scale Error                                               | ZSE              | -15          |       | 9                         | mV    | Measured with offset and gain DACs set to<br>000. Offset is defined as the difference be-<br>tween the clamp voltage and the analog input<br>voltage which results in the transition of the<br>ADC code from 004 to 005. |

| Zero Scale Drift <sup>2</sup>                                  | ZSD              |              | 50    |                           | μV/°C | Measured as the change in the ZSE over temperature. This error does not include the error introduced by the external $V_{REF}$ amplifier or external $V_{REF}$ resistor divider.                                         |

| DC Input Range                                                 | A <sub>IN</sub>  | VCLP<br>–5mV |       | 2.92 V +<br>VCLP<br>-5 mV | V     | The digitizing range is set with the Gain DAC and offset DAC. Please note $A_{IN}$ (min) is VCLP – 4 LSB = $V_{RB}$ and $A_{IN}$ (max) is GFS (max) + ZSR (max) + VCLP – 4 LSB.                                          |

| Data Rate                                                      | FS               | 1.25         |       |                           | MSPS  | The conversion rate is determined by the tim-<br>ing diagram and timing specifications. Set by<br>the CVL period.                                                                                                        |

| Analog Input Voltage Change from Sample to Sample <sup>2</sup> | ΔA <sub>IN</sub> | 0            |       | ±FS                       | V     | Assuming A <sub>IN</sub> voltage remains within the spe-<br>cified digitizing range based on the offset and<br>gain DAC codes.                                                                                           |

| Input Capacitance <sup>2</sup>                                 | C <sub>IN</sub>  |              |       | 45                        | pF    | Measured with $A_{IN}$ DC = 2.5 V and AENL = low.                                                                                                                                                                        |

| Gain DAC                                                       |                  |              |       |                           |       |                                                                                                                                                                                                                          |

| Resolution                                                     | N                |              | 9     |                           | Bits  |                                                                                                                                                                                                                          |

| Differential Non-Linearity                                     | DNL              | -1           |       | +2.25                     | LSB   |                                                                                                                                                                                                                          |

| Integral Non-Linearity                                         | INL              |              |       | +2                        | LSB   |                                                                                                                                                                                                                          |

| Gain DAC Full Scale<br>(V <sub>RT</sub> – V <sub>RB</sub> )    | GFS              | 2.6          | 2.68  | 2.76                      | V     | Gain DAC = 1FF<br>$V_{RT}$ is the top of the ADC reference ladder.<br>Refer to block diagram.                                                                                                                            |

| Gain DAC Zero Scale<br>(V <sub>RT</sub> – V <sub>RB</sub> )    | GZS              | 1.22         | 1.26  | 1.3                       | V     | Gain DAC = 000 $V_{RB}$ is the bottom of the ADC reference ladder. Refer to block diagram.                                                                                                                               |

| Maximum Gain Change per Cycle <sup>2</sup>                     | MGC              |              |       | 50                        | % FSR | After the specified maximum change in gain DAC setting, the ADC should output the same code $\pm 1$ LSB for all of the following conversions assuming the analog input remains fixed, i.e. DC.                           |

| Settling Time (MGC) <sup>2</sup>                               | ts-gd            |              | 200   |                           | ns    |                                                                                                                                                                                                                          |

| Parameter                                            | Symbol            | Min              | Тур              | Мах              | Units | Test Conditions/Comments                                                                                                                                                                                           |

|------------------------------------------------------|-------------------|------------------|------------------|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset DAC                                           | -,                |                  | -71              |                  |       |                                                                                                                                                                                                                    |

| Resolution                                           | N                 |                  | 6                |                  | Bits  |                                                                                                                                                                                                                    |

| Differential Non-Linearity                           | DNL               | -0.5             | 0                | 0.5              | LSB   |                                                                                                                                                                                                                    |

| Integral Non-Linearity                               | INL               | 0.0              |                  | 1                | LSB   |                                                                                                                                                                                                                    |

| V <sub>RB</sub> Range                                | ZSR               | 152              | 158              | 164              | mV    | This is measured as the voltage difference at                                                                                                                                                                      |

| v <sub>RB</sub> Kange                                | ZOR               | 152              | 136              | 104              |       | the clamp pin of the selected channel when<br>the offset DAC changed from 000 (hex) to 3F<br>(hex) with the gain DAC at 1FF (hex). Refer<br>to $V_{RT}$ and $V_{RB}$ EQNs in the theory of opera-<br>tion section. |

| Maximum Offset Change per Cycle <sup>2</sup>         | MOC               |                  |                  | 100              | % FSR | After the specified maximum change in offset DAC setting, the ADC should output the same code $\pm 1$ LSB for all of the following conversions assuming the analog input remains fixed, i.e. DC.                   |

| Full Scale Settling Time <sup>2</sup>                | ts-od             |                  | 200              |                  | ns    | For a 00 (hex) to 3F (hex) change of offset DAC code.                                                                                                                                                              |

| Black Level Clamp Switch                             |                   |                  |                  |                  |       |                                                                                                                                                                                                                    |

| On Resistance                                        | R <sub>ON</sub>   |                  | 100              | 150              | Ω     | Effective R <sub>IN</sub> at clamp pin.                                                                                                                                                                            |

| Input Leakage                                        | IL <sub>CLP</sub> |                  |                  | 25               | nA    | Offset DAC at 00 (hex) (worst case condition)                                                                                                                                                                      |

| Clamp Switching Charge Injection <sup>2</sup>        | Q <sub>CLP</sub>  |                  |                  | 50               | рС    | Offset DAC at 00 (hex) (worst case condition)                                                                                                                                                                      |

| Voltage at Clamp Pin                                 | V <sub>CLP</sub>  | 170              | 180              | 190              | mV    | Offset by 4 LSB from bottom tap of ADC lad-<br>der. Gain = 000 (H). Offset DAC = 00.                                                                                                                               |

| Reference Voltage Requirement                        | s (See Th         | eory of Op       | eration)         |                  |       | •                                                                                                                                                                                                                  |

| Reference Voltage                                    | V <sub>REF</sub>  | 0.93             | 1                | 1.07             | V     | All linearity specifications assume the reference voltage = $AV_{DD} X ( 0.2 )$ .                                                                                                                                  |

|                                                      |                   | 0.5              |                  | 1.15             | V     | Functional.                                                                                                                                                                                                        |

| Calibration Voltage                                  | VCAL              | AGND             |                  | AV <sub>DD</sub> | V     |                                                                                                                                                                                                                    |

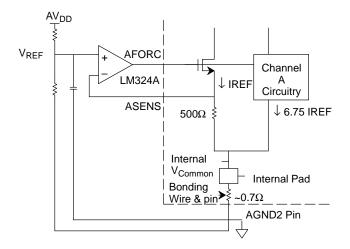

| Sense Pins Input Resistance<br>(ASENS, BSENS, CSENS) | RINS              |                  | 560              |                  | Ω     | RINS is measured from the sense pin to<br>AGND2, BGND2, CGND2 with the power<br>turned off and test voltage less than 250 mV.                                                                                      |

| Power Supplies (Note: All GND                        | pins are          | substrate)       |                  |                  |       | 1                                                                                                                                                                                                                  |

| Analog Positive Supply                               | AV <sub>DD</sub>  | 4.75             | 5                | 5.25             | V     | Bypass power supply pins.                                                                                                                                                                                          |

| Digital Positive Supply                              | DV <sub>DD</sub>  | AV <sub>DD</sub> | AV <sub>DD</sub> | AV <sub>DD</sub> | V     | Bypass power supply pins.                                                                                                                                                                                          |

| Analog Negative Supply                               | AGND              | 0                | 0                | 0                | V     |                                                                                                                                                                                                                    |

| Digital Negative Supply                              | DGND              | 0                | 0                | 0                | V     |                                                                                                                                                                                                                    |

| Power Supply Rejection                               | PSRR              |                  |                  | -60              | dB    | f=1 KHz.                                                                                                                                                                                                           |

| Supply Current                                       | I <sub>DD</sub>   |                  | 100              | 130              | mA    | During specified operation.                                                                                                                                                                                        |

| Digital Characteristics                              |                   |                  |                  |                  |       |                                                                                                                                                                                                                    |

| Digital Input High Voltage for Control<br>Pins       | V <sub>IH</sub>   | 3.5              |                  |                  | V     | All digital input pins other than DAC data inputs.                                                                                                                                                                 |

| Digital Input Low Voltage for Control<br>Pins        | VIL               |                  |                  | 1.5              | V     | All digital input pins other than DAC data inputs.                                                                                                                                                                 |

| Digital Input High Voltage for DAC<br>Input Pins     | V <sub>IH</sub>   | 2.4              |                  |                  | V     | DAC data inputs, CD0-CD14                                                                                                                                                                                          |

| Digital Input Low Voltage for DAC<br>Input Pins      | VIL               |                  |                  | 0.4              | V     | DAC data inputs, CD0-CD14                                                                                                                                                                                          |

| V <sub>OL</sub>                                      | V <sub>OL</sub>   |                  |                  | 0.5              | V     | @ I <sub>OL</sub> = 4 mA                                                                                                                                                                                           |

| V <sub>OH</sub>                                      | V <sub>OH</sub>   | 4.5              |                  |                  |       | @ I <sub>OH</sub> = 4 mA                                                                                                                                                                                           |

| Digital Input Leakage Current                        | I <sub>IN</sub>   | -10              |                  | 10               | μA    |                                                                                                                                                                                                                    |

TⓒM<sup>™</sup>

| Parameter                                                                                                                    | Symbol          | Min | Тур | Max | Units | Test Conditions/Comments                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-State Leakage                                                                                                              | I <sub>OZ</sub> | -10 |     | 10  | μA    | In pass-through mode                                                                                                                                                                                             |

| Digital Timing Specifications <sup>2</sup>                                                                                   |                 |     |     |     |       | For testing, rise time = fall time =<br>10 ns. Output loading = 60 pF except for<br>AD0-AD9 for which loading is 40 pF. Rise<br>and fall times faster than 5 ns should be<br>avoided.                            |

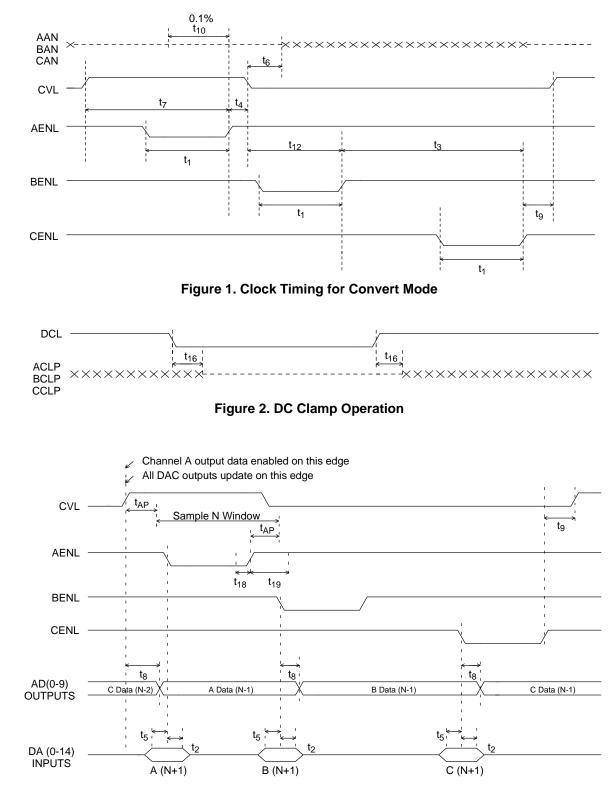

| AENL, BENL, CENL<br>Pulse Width                                                                                              | t <sub>1</sub>  | 125 |     |     | ns    |                                                                                                                                                                                                                  |

| D/A Data Hold Time                                                                                                           | t <sub>2</sub>  | 20  |     |     | ns    |                                                                                                                                                                                                                  |

| BENL Rising Edge to CENL Rising<br>Edge                                                                                      | t <sub>3</sub>  | 270 |     |     | ns    |                                                                                                                                                                                                                  |

| AENL Rising Edge to CVL Falling<br>Edge                                                                                      | t <sub>4</sub>  | 30  |     |     | ns    |                                                                                                                                                                                                                  |

| D/A Data Setup Time                                                                                                          | t <sub>5</sub>  | 20  |     |     | ns    |                                                                                                                                                                                                                  |

| Analog Input Hold Time                                                                                                       | t <sub>6</sub>  | 20  |     |     | ns    | Measured as part of analog feedthrough test.<br>Note, $t_{tapmax} < t_{4min} + t_{6min}$ .                                                                                                                       |

| CVL Rising Edge to AENL Rising<br>Edge                                                                                       | t <sub>7</sub>  | 230 |     |     | ns    |                                                                                                                                                                                                                  |

| A/D Data Enable Time                                                                                                         | t <sub>8</sub>  |     |     | 40  | ns    | CVL to Channel A data.<br>BENL to Channel B data.<br>CENL to Channel C data.                                                                                                                                     |

| CENL Rising Edge to CVL Rising Edge                                                                                          | t <sub>9</sub>  | 40  |     |     | ns    |                                                                                                                                                                                                                  |

| Analog Input Settled to 0.1%                                                                                                 | t <sub>10</sub> | 50  |     |     | ns    | Assumes the sample is taken at the rising edge of AENL.                                                                                                                                                          |

| A/D Data Hold Time                                                                                                           | t <sub>11</sub> | 20  |     |     | ns    |                                                                                                                                                                                                                  |

| Aperture Delay                                                                                                               | t <sub>AP</sub> |     | 20  | 40  | ns    | Analog sampling window delay from CVL rising $(\uparrow)$ edge (start) or AENL rising $(\uparrow)$ edge (end).                                                                                                   |

| CVL Falling Edge to BENL Rising<br>Edge                                                                                      | t <sub>12</sub> | 180 |     |     | ns    |                                                                                                                                                                                                                  |

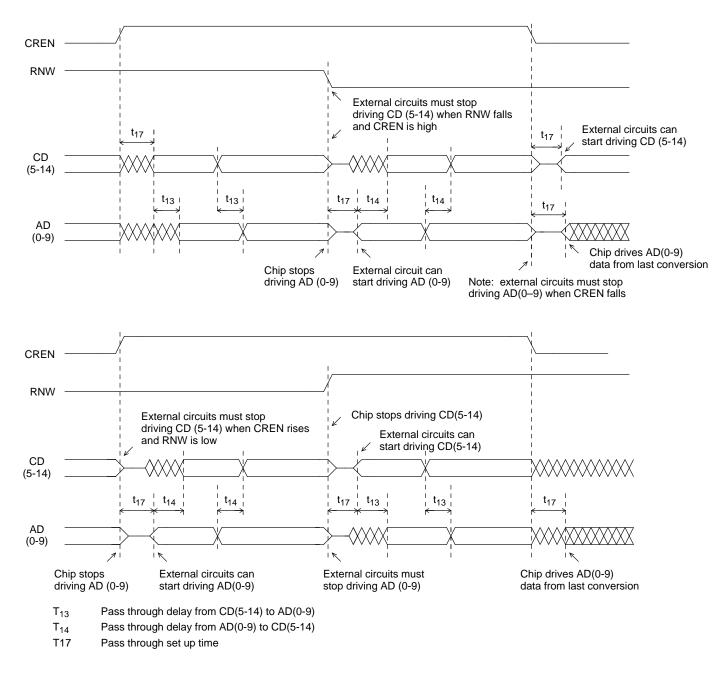

| Delay from CD5-14 to AD0-9 with<br>CREN=1                                                                                    | t <sub>13</sub> |     |     | 50  | ns    |                                                                                                                                                                                                                  |

| Delay from AD0-9 to CD5-14 with<br>CREN = 1                                                                                  | t <sub>14</sub> |     |     | 50  | ns    |                                                                                                                                                                                                                  |

| Delay from DCL Falling Edge to<br>Clamp on.                                                                                  | t <sub>15</sub> |     |     | 40  | ns    | External analog clamp voltage settling de-<br>pends on external circuitry.                                                                                                                                       |

| Delay from DCL Rising Edge to<br>Clamp off.                                                                                  | t <sub>16</sub> |     |     | 40  | ns    | External analog clamp voltage settling de-<br>pends on external circuitry.                                                                                                                                       |

| Time for AD0-9 and CD5-14 to switch<br>from normal operation to pass<br>through mode or vise versa (i.e. bus<br>contention). | t <sub>17</sub> | 0   |     | 40  | ns    | User should stop driving the bus before<br>changing the mode and data will not be valid<br>for 40 ns after a change of mode.                                                                                     |

| Digital Quiet Time                                                                                                           | t <sub>18</sub> | 15  |     |     | ns    | This quiet time is necessary to reduce digital crosstalk during the critical sampling time.<br>The accuracy of each conversion may be corrupted due to digital noise on the board during this period.            |

| Digital Quiet Time                                                                                                           | t <sub>19</sub> | 40  |     |     | ns    | This quiet time is necessary to reduce digital<br>crosstalk during the critical sampling time.<br>The accuracy of each conversion may be cor-<br>rupted due to digital noise on the board during<br>this period. |

Notes

Production testing performanced at 25°C. Not production tested. 2

Rev. 1.00

/ / / / / / / /

# ABSOLUTE MAXIMUM RATINGS (TA = $+25^{\circ}$ C unless otherwise noted) <sup>1, 2</sup>

| AV <sub>DD</sub> to GND6 V                    |

|-----------------------------------------------|

| DV <sub>DD</sub> to GND                       |

| AV <sub>DD</sub> – DV <sub>DD</sub> 150 mV DC |

| All Inputs V <sub>DD</sub> +0.5 to GND –0.5 V |

| Storage Temperature                           |

| Lead Temperature 300°C                        |

| ESD Rating 2000 V on all pins.          |

|-----------------------------------------|

| Package Power Dissipation Rating @ 75°C |

| PQFP1100 mW                             |

| Derates above 75°C 15 mW/°C             |

| T <sub>JMAX</sub> 150°C                 |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup> Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All logic inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

#### **TRUTH TABLE**

| Function                                     | CVL        | AENL         | BENL         | CENL         | CREN | RNW | VINMX | FAST | DCL |

|----------------------------------------------|------------|--------------|--------------|--------------|------|-----|-------|------|-----|

| Start AIN tracking                           | 1          | 1            | 1            | 1            | 0    | Х   | 0     | X    | Х   |

| Sample A <sub>IN</sub>                       | 1          | <b>↑</b>     | 1            | 1            | 0    | X   | 0     | X    | X   |

| MSB convert                                  | 0          | 1            | 0            | 1            | 0    | X   | 0     | X    | X   |

| LSB convert                                  | 0          | 1            | 1            | 0            | 0    | X   | 0     | X    | X   |

| Output A ADC data from<br>previous sample    | 1          | 1            | 1            | 1            | 0    | X   | 0     | X    | X   |

| Output B ADC data from<br>previous sample    | X          | 1            | $\downarrow$ | 1            | 0    | X   | 0     | X    | Х   |

| Output C ADC data from previous sample       | Х          | 1            | 1            | $\downarrow$ | 0    | X   | 0     | X    | Х   |

| Load channel A data to first A DAC register  | X          | $\downarrow$ | 1            | 1            | 0    | X   | 0     | X    | Х   |

| Load channel B data to first B DAC register  | X          | 1            | $\downarrow$ | 1            | 0    | X   | 0     | X    | Х   |

| Load channel C data to first C DAC register  | Х          | 1            | 1            | V            | 0    | X   | 0     | X    | Х   |

| Update second register for all DACs          | $\uparrow$ | 1            | 1            | 1            | 0    | X   | 0     | X    | X   |

| Turn on all black level clamp switches       | X          | Х            | Х            | X            | X    | X   | Х     | X    | 0   |

| Pass-through mode: ADC port in, DAC port out | X          | Х            | X            | X            | 1    | 0   | Х     | X    | Х   |

| Pass-through mode: DAC port in, ADC port out | Х          | Х            | X            | X            | 1    | 1   | Х     | X    | Х   |

| ADC inputs connect to VCAL                   | Х          | Х            | Х            | X            | X    | X   | 1     | X    | X   |

| Put ADCs in 4-bit mode                       | X          | Х            | Х            | X            | X    | X   | Х     | 1    | X   |

# MP8830 **X\*EX4R**

## **TIMING DIAGRAMS**

Figure 3. DAC Input and ADC Output Timing for Normal Convert Operation (CREN = 0)

#### **Pass Through Mode**

- 1. AENL, BENL & CENL should be held high during pass-through mode. ADCs and DACs will not work properly during pass-through.

- 2. Pass-through mode enable. When CREN is high, pass-through mode between the ADC and DAC ports is enabled. RNW controls the direction of pass-through operation.

3. READ not WRITE signal. RNW controls the direction of the pass-through operation when CREN is high, and has no impact when CREN is low. When RNW is high, data passes from the DAC port to the ADC port. When RNW is low, data passes from the ADC port to the DAC port. Note the port connections are: CD5; AD0; CD6; AD1;...;CD14; AD9.

Figure 4. Timing for Pass Through Mode Operation

#### THEORY OF OPERATION

The MP8830 is composed of three ADC converters with dynamic gain and offset control along with their associated analog and digital support circuitry. The three converters are intended to be used in a simultaneous sampling configuration. The only external circuits required are a reference and reference buffer amp.

The ADC gain and offset DAC inputs, ADC output data, and the A<sub>IN</sub> sampling time are related to the four clock inputs, CVL, AENL, BENL and CENL.

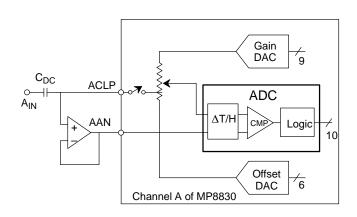

In applications which require rejecting a bias level from the analog input, a zero clamp is provided for each channel. With the addition of a buffer input amp and blocking capacitor, this function rejects the bias present during DCL = 0 time on the analog input.

ADC calibration or test can be performed using the built-in VCAL /  $A_{IN}$  MUX which will switch the ADC  $A_{IN}$  from the channel input voltage, AAN, BAN, CAN to VCAL.

A fast mode is provided, where only the four ADC MSBs are produced while the remaining data is set to 00(hex).

To simplify board layout, a data pass-through configuration is provided to allow bi-directional communication between the ADC data port and the 10 MSBs of the DAC I/O port.

#### ADC System Overall Sequence

The following section describes the events which take place during one conversion cycle (*Figures 1-4*). Assume at power up, or in the previous cycle, that the values for the gains and offsets needed for this sample set have been loaded into the first DAC registers. This data is loaded into the second registers for all three channels <u>on the rising edge of CVL</u>. A<sub>IN</sub> tracking for all channels is also started after t<sub>AP</sub> delay. Note that the AENL, BENL and CENL were at "1" states.

At the <u>falling edge of AENL</u>, the channel A gain and offset data for the next cycle is loaded into the channel A first DAC register. The analog input sample for all three channels is taken at the <u>rising edge of AENL</u> after  $t_{AP}$  delay.

At the <u>falling edge of BENL</u>, the channel B gain and offset data for the next cycle is loaded into the channel B first DAC register. The MSB comparators are also enabled at this time. At <u>the</u> <u>rising edge of BENL</u>, the MSB value is latched, and the range for the LSBs is selected. Note that the gain and offset DAC must be settled by this time in order for the MSB value to be correct ( $t_7 + t_4 + t_1$  ensure this.)

At <u>the falling edge of CENL</u>, the channel C gain and offset data for the next cycle is loaded into the channel C first DAC register. The LSB comparators are also enabled at this time. At <u>the</u> <u>rising edge of CENL</u>, the LSB value is latched.

**XPEXAR**

During the time  $(t_9)$  when CENL =1 and CVL = 0, the MSB data is corrected (if necessary) and then propagated along with the LSB data to the ADC outputs. On the rising edge of CVL, channel A data is enabled at the output port.

Since the actual ADC samples are taken at the rising edge of AENL after  $t_{AP}$  delay, this period of time is the most sensitive to transition noise from digital components. Keep all transitions outside of the  $t_{18}$ ,  $t_{19}$  digital quiet time window around the AENL rising edge. Since the ADC output bus will change states at the rising edge of CVL, the time from CVL rising to AENL rising is important. The delay from CVL rising to channel A valid on the ADC bus is  $t_8$ . This requires that AENL rising edge must not occur until at least  $t_8$  after CVL rising.

#### **CVL** Functions

CVL rising edge performs three functions. The first is to update the gain and offset DACs from their respective first registers simultaneously. The second function is to initiate the sample window. The third function is to latch the results of the previous conversions into the ADC output register.

The A channel ADC data is presented at the ADC data port after CVL rising edge. CVL falling edge does not change any internal state.

#### **DAC Data Port Operation**

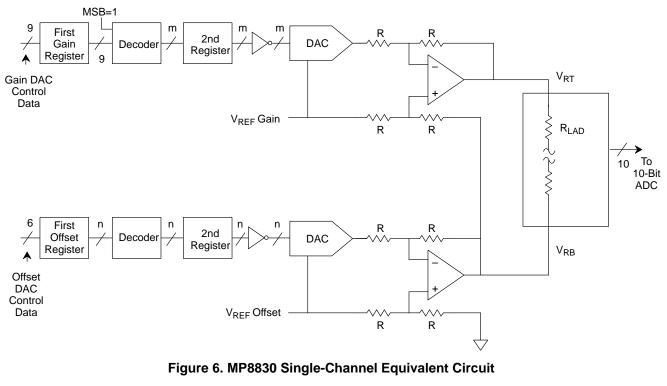

DAC data is loaded first into an input register and then loaded into the DAC register.

The input register allows sequential loading of the next conversion settings for all the channels through the 15-bit DAC data bus while the ADC data is being clocked out of the ADC data port. The second register allows for simultaneous updating of all channels at the beginning of the analog sample period. This timing gives the ADC reference levels adequate time to settle before being used to convert the sampled  $A_{IN}$ . Note that the DAC data must be presented at each cycle, since there is no provision for holding DAC data after each cycle.

At power up, the DAC states should be set for the first sample's required gain and offset settings. This is accomplished by setting CVL = 1, and cycling each of the AENL, BENL, and CENL clocks from their 1 to 0 to 1 states sequentially with each channel's respective data present at the DAC data port.

#### Figure 5. Simplified Diagram Channel A Example

#### **Black Level Switch Operation**

The MP8830 is equipped with a black level setting switch. The function of the black level setting switch is to store the DC offset value of the ADC as well as the common mode value of A<sub>IN</sub> across the external C<sub>DC</sub>-hold capacitor. This is a cost effective method to store the black level of A<sub>IN</sub> or the offset of the system. Note that the ACLP, BCLP, and CCLP level is DC shifted to accommodate for the distribution of ADC offset.

One terminal of each clamp switch is connected at the ladder tap voltage which corresponds to +4 LSB from the ADC 000(hex) to 001(hex) transition. This 4 LSB offset allows the ADC to measure as low as -4 LSB of the analog input voltage relative to the clamp voltage. To increase the negative input detectable range, clamp with the offset DAC at a code higher than 00(hex).

The second terminal of the clamp switch is connected to a pin with its corresponding channel prefix. For channel A, the pin is named ACLP.

The control of the all the switches is provided by a separate unlatched logic input called DCL. The delay from DCL falling edge to switch on is specified as  $t_{16}$ . The actual time required to store the bias voltage depends on the external C value, and bias variation from sample to sample. The equivalent impedance of the clamp is  $100\Omega$  typical, spec name of R<sub>ON</sub>, and must be included in the analysis of the zero sample time considerations.

The black level is a function of the offset DAC, and therefore requires that the value of the offset DAC be loaded into the offset DAC second register before the clamp is turned on. This value can be set from 00(hex) to 3F(hex) corresponding to a clamp level change of ZSR.

The voltage swing at the ACLP, BCLP, CCLP pin after clamp should be limited to the range of  $AV_{DD}$  to AGND. This will prevent the stored charge on the holding cap from being changed by the input protection devices.

A  $50\Omega$  to  $100\Omega$  resistor in series with the ACLP, BCLP, CCLP pin will limit the current induced in the protection and parasitic diodes due to over-voltages induced by the source. Limit this current with the use of external protection diodes.

Rev. 1.00

#### ADC Gain and Offset Control

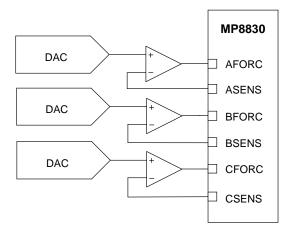

Each channel of the MP8830 contains a 10-bit ADC, a 10-bit DAC with MSB = 1 (9 active bits) driving the positive reference, and a 6-bit DAC driving the negative reference of the ADCs ladder network.

The relationship between the ADC gain and offset and the DAC data can be expressed mathematically.

Assign the terms  $V_{RT}$  and  $V_{RB}$  to represent the voltages for the ADC full scale and black levels. DgainA and DoffsetA represent the digital value for the gain and offset parameters set by the DACs for channel A.

V<sub>RT</sub> and V<sub>RB</sub> are defined by the equation:

$$V_{RT} = \left\{ (1 + \frac{DgainA}{2^9}) * 1.3 \right\} * V_{REF} + V_{RB}$$

$$V_{RB} = \left\{ (1 + \frac{DoffsetA}{2^6}) * 0.16 \right\} * V_{REF}$$

$$V_{RT} - V_{RB} = \left\{ (1 + \frac{DgainA}{2^9}) * 1.3 \right\} * V_{REF}$$

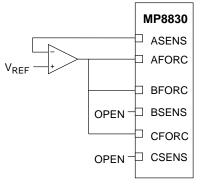

#### **Channel Bias Circuitry**

The gain DAC and the offset DAC for each channel have a combined bias generator for setting their full scale range. An external op amp is required and is connected per *Figure 7*. The

$V_{REF}$  range for each channel can be either the same or different depending on the application and nominal channel gain required. A higher  $V_{REF}$  provides lower channel gain.

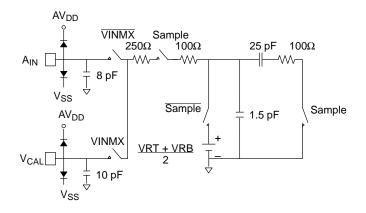

Figure 8. ADC Input Equivalent Circuit

#### **ADC Analog Input**

This part has a switched capacitor type input circuit. This means that the input impedance changes with the phase of the input clock. *Figure 8.* shows an equivalent input circuit.

#### VCAL and VINMX

VCAL voltage is connected through an analog mux to all 3 channel inputs at VINMX=1. VCAL can then be used to normalize all three ADC input voltage to output states. It can be used for testing as well as building calibration tables for all three channels.

#### Supply and Grounds

AGND1, BGND1, CGND1, and GND3 should be connected under the package to make their common impedance as low as possible. AGND2, BGND2, CGND2 should also be connected to this ground.

Use a single supply to drive all of the V<sub>DD</sub> pins. AV<sub>DD</sub>, BV<sub>DD</sub>, CV<sub>DD</sub>, V<sub>DD3</sub> should be connected to a common supply plane which forms a supply / ground plane with the analog ground plane. In addition, local decoupling (preferably 0.1 uFchip type) should be connected between each analog V<sub>DD</sub> pin and its closest analog ground.

A decoupling capacitor (preferably 0.1 uFchip type) should be connected across pin 1 and 64 and between pin 44 and 43. A  $DV_{DD}$  to DGND supply/ground plane should also be provided.

## **PIN OUT DEFINITIONS**

| Pin #                | Pin Name                                                                           | Function                                                                                                                                                                                                                                                                                                                             |

|----------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 44                | DV <sub>DD</sub> (2)                                                               | Digital positive power supplies. 5 V. Should be decoupled to digital GND plane. The two DV <sub>DD</sub> pins both connect to the ESD ring as well as the control logic, data port logic, and the internal ADC output data bus drivers.                                                                                              |

| 43, 64               | DGND (2)                                                                           | Digital negative power supplies. 0 V. The two DGND pins both connect to the ESD ring as well as the control logic and data port logic.                                                                                                                                                                                               |

| 31<br>24<br>17<br>47 | AV <sub>DD</sub> ,<br>BV <sub>DD</sub> ,<br>CV <sub>DD</sub> ,<br>V <sub>DD3</sub> | Analog positive power supplies. 5 V. Should be star connected to the analog supply post or direct connection to analog supply plane. Decouple to AGND, BGND, CGND. $V_{DD}$ 3 powers the ADC internal logic only.                                                                                                                    |

| 36<br>30<br>23<br>46 | AGND1,<br>BGND1,<br>CGND1,<br>GND3                                                 | Analog negative power supplies. 0 V. Should be star connected to analog ground post or direct connection to the analog ground plane. These GNDs power the analog sections of the ADC and the circuitry in the DACs. GND3 pin connects to the internal ADC data bus and the ADC internal logic.                                       |

| 32<br>28<br>21       | AGND2,<br>BGND2,<br>CGND2                                                          | Analog grounds related to DAC bias are the common voltage for the reference. The ADC ladder resistor terminates to this pin as well as the internal bias resistor used for setting the DAC reference. These pins should be used as the reference ground voltage for all analog measurements.                                         |

| 52                   | AENL                                                                               | Channel A data clock, active low. A DAC data loaded into first register bank on the falling edge of AENL.                                                                                                                                                                                                                            |

| 51                   | BENL                                                                               | Channel B data clock, active low. B DAC data loaded into the first register on the falling edge of BENL. B ADC data loaded to the ADC output port on falling edge (and should be read on the rising edge).                                                                                                                           |

| 50                   | CENL                                                                               | Channel C data clock, active low. C DAC data loaded into the first register on the falling edge of CENL. C ADC data loaded to the ADC output port on falling edge (and should be read on the rising edge).                                                                                                                           |

| 53                   | CVL                                                                                | Cycle clock. All DACs loaded on rising edge. Begin sample of analog input on rising edge. A ADC data is loaded to the ADC output port on the rising edge of CVL (and should be read on the rising edge of AENL).                                                                                                                     |

| 48                   | CREN                                                                               | Pass through mode enable. When CREN is high, passthrough mode between the ADC and DAC ports is enabled. RNW controls the direction of pass through operation.                                                                                                                                                                        |

| 49                   | RNW                                                                                | READ not WRITE signal. RNW controls the direction of the pass through operation when CREN is high and has no impact when CREN is low. When RNW is high data passes from the DAC port to the ADC port. When RNW is low, data passes from the ADC port to the DAC port. Note, the port connections are: CD5; AD0; CD6; AD1;;CD14; AD9. |

| 39                   | V <sub>IN</sub> MX                                                                 | Analog mux control. $V_{IN}MX$ controls the analog mux on the input of all three ADCs. When $V_{IN}MX$ is high, all ADC inputs are connected to VCAL. When low, each ADC is connected to its particular analog input pin.                                                                                                            |

| 45                   | FAST                                                                               | Fast mode enable. The FAST pin controls the mode of the ADCs. When low, the part func-<br>tions as specified for 10-bit resolution. When high, the ADC's resolution becomes 4-bit and<br>the LSBs are forced low. The clock rate can be increased in this mode to 3 MHz.                                                             |

| 37                   | ACLP                                                                               | Clamp voltage A. Black level clamp pin for the A channel.                                                                                                                                                                                                                                                                            |

| 29                   | BCLP                                                                               | Clamp voltage B. Black level clamp pin for the B channel.                                                                                                                                                                                                                                                                            |

| 22                   | CCLP                                                                               | Clamp voltage C. Black level clamp pin for the C channel.                                                                                                                                                                                                                                                                            |

| 41                   | DCL                                                                                | Black level clamp control (active low). Black level clamp enable for all pins. All Black level clamps are turned on when DCL is low.                                                                                                                                                                                                 |

| 35                   | AAN                                                                                | A channel analog input.                                                                                                                                                                                                                                                                                                              |

| 27                   | BAN                                                                                | B channel analog input.                                                                                                                                                                                                                                                                                                              |

| 20                   | CAN                                                                                | C channel analog input.                                                                                                                                                                                                                                                                                                              |

| 38                   | VCAL                                                                               | Calibration input voltage.                                                                                                                                                                                                                                                                                                           |

| 34    | AFORC    | Forcing voltage for biasing the internal DACs. This is the gate of the N-Channel biasing tran-<br>sistor for the A channel.                                                    |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33    | ASENS    | Sensing voltage for biasing the internal DACs. This is the source of the N-channel biasing transistor and the top terminal of the internal biasing resistor for the A channel. |

| 26    | BFORC    | Forcing voltage for biasing the internal DACs. This is the gate of the N-Channel biasing tran-<br>sistor for the B channel.                                                    |

| 25    | BSENS    | Sensing voltage for biasing the internal DACs. This is the source of the N-Channel biasing transistor and the top terminal of the internal biasing resistor for the B channel. |

| 19    | CFORC    | Forcing voltage for biasing the internal DACs. This is the gate of the N-Channel biasing tran-<br>sistor for the C channel.                                                    |

| 18    | CSENS    | Sensing voltage for biasing the internal DACs. This is the source of the N-Channel biasing transistor and the top terminal of the internal biasing resistor for the C channel. |

| 54-63 | AD9-AD0  | ADC data output pins. AD9 is the MSB.                                                                                                                                          |

| 2-16  | CD14-CD0 | DAC input pins. CD14-CD6 are the Gain DAC MSB to LSB. CD5-CD0 are the offset DAC MSB to LSB.                                                                                   |

| 42    | N/C      | No connection.                                                                                                                                                                 |

| 40    | DGND     | Digital Ground.                                                                                                                                                                |

Note: All digital signals are active high unless otherwise noted.

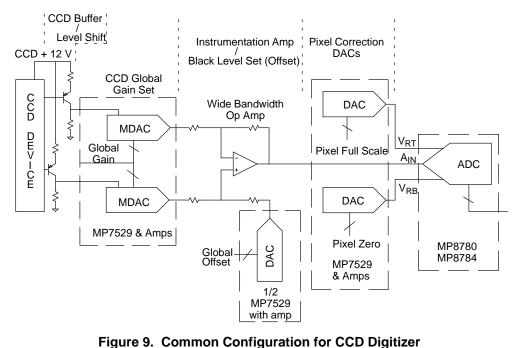

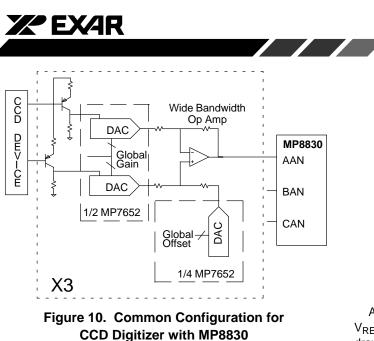

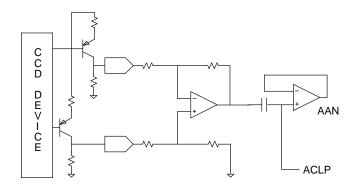

## **APPLICATION NOTES FOR CCD SYSTEMS**

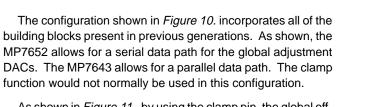

A typical CCD digitizing configuration is shown in *Figure 9.*, which incorporates global gain and offset adjustment as well as pixel-to-pixel variation correction. The MP8830 can greatly simplify this type of system by replacing the ADCs, the pixel correction DACs, and the global offset DACs as shown in *Figure 10.* One main advantage of the MP8830 is the way the offset and

span for each pixel are controlled. In the traditional application, the offset and span settings interact requiring additional computations for each pixel adjustment. With the MP8830, the offset and span settings can be calibrated separately simplifying the computations necessary.

1 Channel Shown

#### Figure 12. Simplified Reference **Buffer Amp Configuration**

**MP8830**

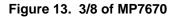

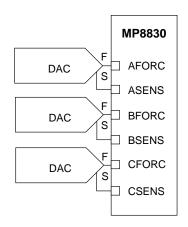

Additional gain adjustment is possible by varying the channel V<sub>RFF</sub> voltage during calibration. *Figure 13.* shows a general drawing for this approach. By using the MP7643, the buffer amplifiers can be eliminated as shown in Figure 14.

As shown in Figure 11., by using the clamp pin, the global offset (black level) can be AC coupled to the ADC in order to simplify the offset calibration and eliminate thermal and power supply induced errors.

## Figure 11. Configuration for CCD Digitizer using **Black Level Clamp Channel A Shown**

The amount of adjustment range available with the standard configuration may allow for the use of only one V<sub>REF</sub> buffer amp by connecting the A, B, CFRC pins together on the MP8830 and using the ASENS pin as the feedback point to the buffer. BSENS and CSENS are open in this case. See Figure 12.

#### Rev. 1.00 T(\$)M 15

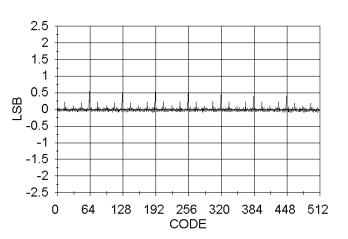

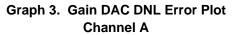

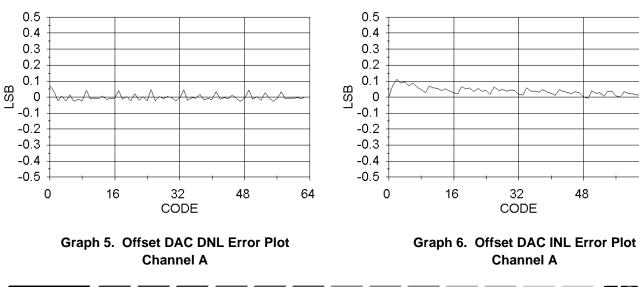

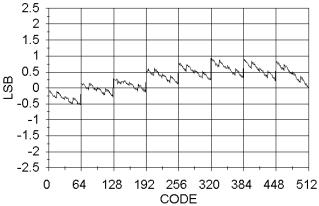

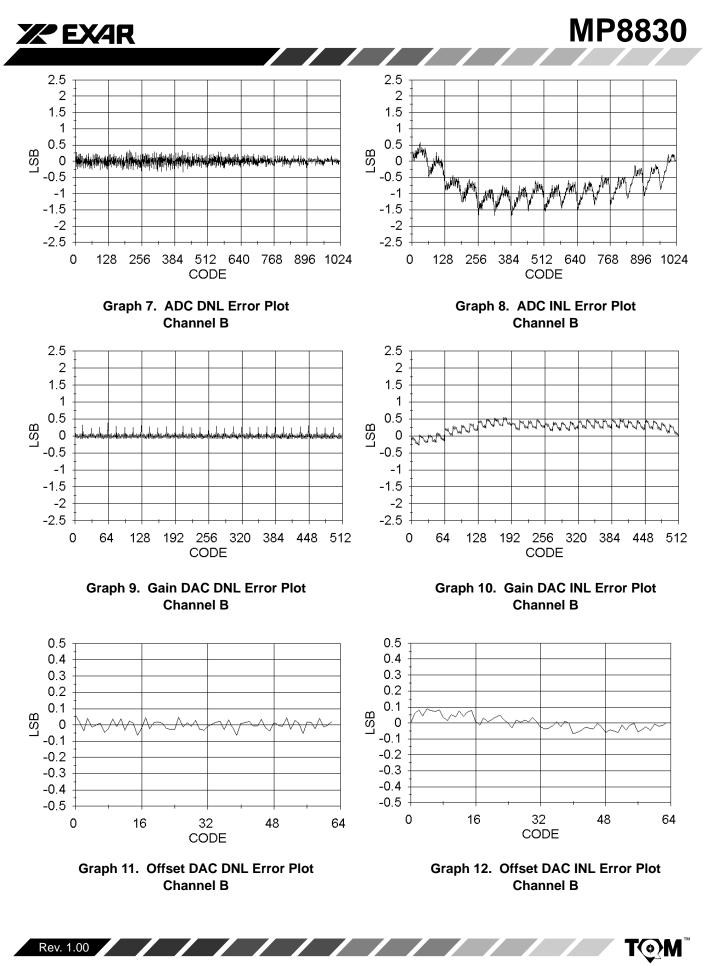

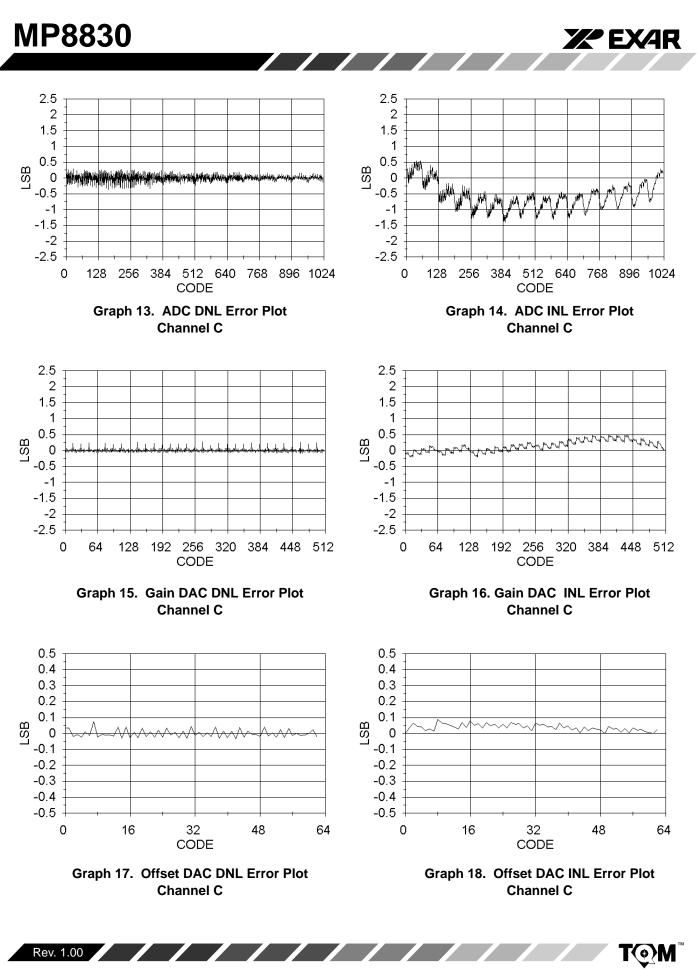

#### PERFORMANCE CHARACTERISTICS

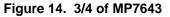

Graph 2. ADC INL Error Plot Channel A

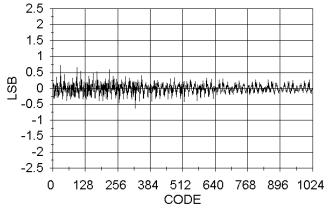

Graph 4. Gain DAC INL Error Plot Channel A

64

64 LEAD PLASTIC QUAD FLAT PACK (14mm x 14mm PQFP, METRIC) Q64

|                | MILLI        | METERS | INC   | CHES    |

|----------------|--------------|--------|-------|---------|

| SYMBOL         | MIN          | MAX    | MIN   | MAX     |

| А              |              | 3.15   |       | 0.124   |

| A <sub>1</sub> | 0.25         |        | 0.01  | _       |

| A <sub>2</sub> | 2.6          | 2.8    | 0.102 | 0.110   |

| В              | 0.3          | 0.4    | 0.012 | 0.016   |

| С              | 0.13         | 0.23   | 0.005 | 0.009   |

| D              | 16.95        | 17.45  | 0.667 | 0.687   |

| D <sub>1</sub> | 13.9         | 14.1   | 0.547 | 0.555   |

| е              | 0.8          | 0 BSC  | 0.03  | 315 BSC |

| L              | 0.65         | 1.03   | 0.026 | 0.040   |

| α              | 0°           | 7°     | 0°    | 7°      |

| Coplanarity    | / = 4 mil ma | х.     |       |         |

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contains here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1994 EXAR Corporation Datasheet April 1995 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.