## **MPC555**

### **USER'S MANUAL**

Revised 1 March 1999

# **MPC555**

### **USER'S MANUAL**

Revised 1 March 1999

#### Paragraph Number

#### TABLE OF CONTENTS

#### Page Number

#### **PREFACE**

# Section 1 OVERVIEW

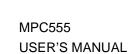

| 1.1 | Block Diagram                                                |

|-----|--------------------------------------------------------------|

| 1.2 | MPC555 Features                                              |

|     | 1.2.1 RISC MCU Central Processing Unit (RCPU)                |

|     | 1.2.2 Four-Bank Memory Controller                            |

|     | 1.2.3 U-Bus System Interface Unit (USIU)                     |

|     | 1.2.4 Flexible Memory Protection Unit                        |

|     | 1.2.5 448 Kbytes of CDR MoneT Flash EEPROM Memory (CMF) 1-3  |

|     | 1.2.6 26 Kbytes of Static RAM 1-3                            |

|     | 1.2.7 General-Purpose I/O Support                            |

|     | 1.2.8 Two Time Processor Units (TPU3) 1-4                    |

|     | 1.2.9 18-Channel Modular I/O System (MIOS1)                  |

|     | 1.2.10 Two Queued Analog-to-Digital Converter Modules (QADC) |

|     | 1.2.11 Two CAN 2.0B Controller Modules (TouCANs)             |

|     | 1.2.12 Queued Serial Multi-Channel Module (QSMCM)            |

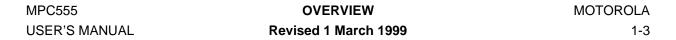

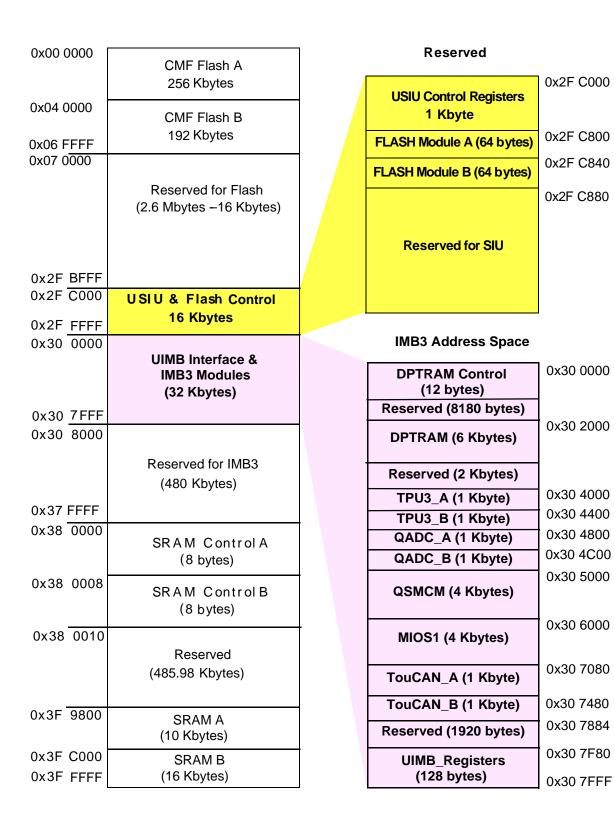

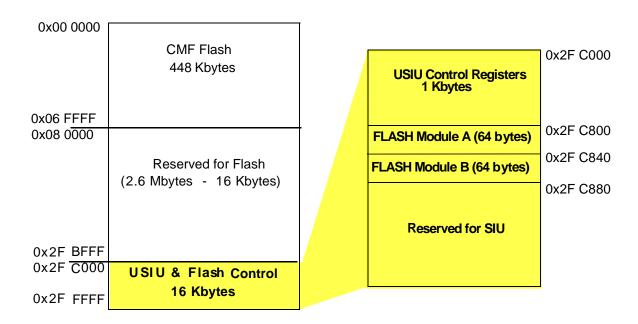

| 1.3 | MPC555 Address Map 1-5                                       |

|     | Section 2                                                    |

|     | SIGNAL DESCRIPTIONS                                          |

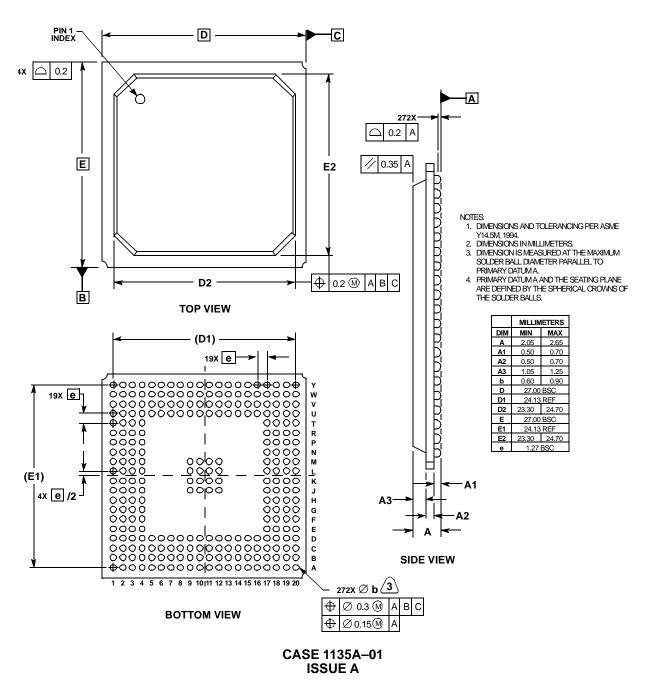

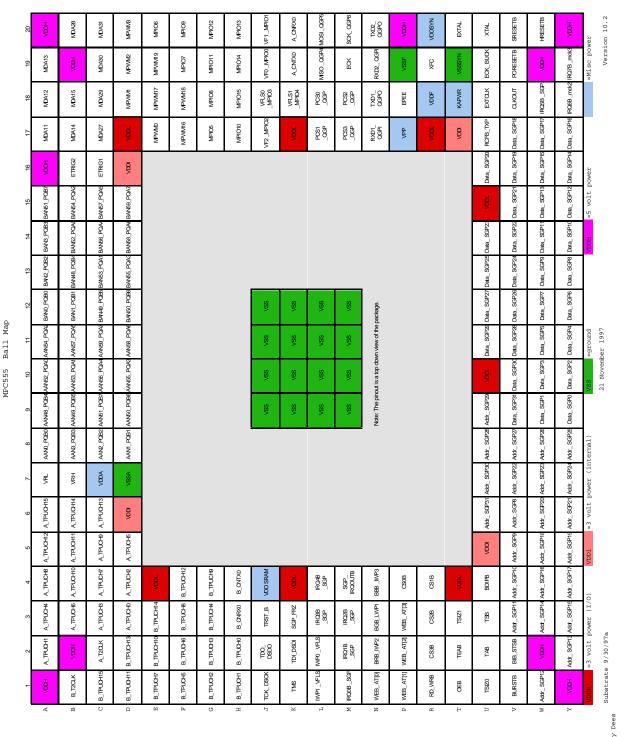

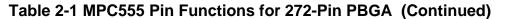

| 2.1 | Packaging and Pinout Descriptions                            |

| 2.2 | Pin Functionality                                            |

| 2.3 | Signal Descriptions 2-13                                     |

|     | 2.3.1 USIU Pads                                              |

|     | 2.3.1.1 ADDR[8:31]/SGPIOA[8:31]2-14                          |

|     | 2.3.1.2 DATA[0:31]/SGPIOD[0:31]2-14                          |

|     | 2.3.1.3 <u>IRQ[0]</u> /SGPIOC[0]                             |

|     | 2.3.1.4 IRQ[1]/RSV_B/SGPIOC[1]2-14                           |

|     | 2.3.1.5 TRQ[2]/CR_B/SGPIOC[2]/MTS                            |

|     | 2.3.1.6 IRQ[3]/KR/RETRY/SGPIOC[3]2-15                        |

|     | 2.3.1.7 IRQ[4]/AT[2]/SGPIOC[4]2-15                           |

|     | 2.3.1.8 IRQ[5]/SGPIOC[5]/MODCK[1]                            |

|     | 2.3.1.9 TRQ[6:7]/MODCK[2:3]2-15                              |

|     | 2.3.1.10 TSIZ[0:1]                                           |

|     | 2.3.1.11 RD/WR                                               |

|     | 2.3.1.12 BURST                                               |

|     | 2.3.1.13 BDIP                                                |

|     | 2.3.1.14 TS 2-16                                             |

|     | 2.3.1.15 TA 2-16                                             |

| Paragraph  |                               | Page   |

|------------|-------------------------------|--------|

| Number     |                               | lumber |

|            | TEA                           |        |

| 2.3.1.17   | RSTCONF/TEXP                  | 2-17   |

| 2.3.1.18   | <u>OE</u>                     | 2-17   |

| 2.3.1.19   | BI/STS                        | 2-17   |

| 2.3.1.20   | <u>CS[0:3]</u>                | 2-18   |

| 2.3.1.21   | WE[0:3]/AT[0:3]               | 2-18   |

| 2.3.1.22   | PORESET                       | 2-18   |

| 2.3.1.23   | HRESET                        | 2-18   |

| 2.3.1.24   | SRESET                        | 2-18   |

| 2.3.1.25   | SGPIOC[6]/FRZ/PTR             | 2-19   |

| 2.3.1.26   | SGPIOC[7]/IRQOUT/LWP[0]       | 2-19   |

| 2.3.1.27   | BG/VF[0]/LWP[1]               | 2-19   |

| 2.3.1.28   | BR/VF[1]/IWP[2]               | 2-19   |

| 2.3.1.29   | BB/VF[2]/IWP[3]               | 2-20   |

| 2.3.1.30   | IWP[0:1]/VFLS[0:1]            | 2-20   |

| 2.3.1.31   | TMS                           | 2-20   |

| 2.3.1.32   | TDI/DSDI                      | 2-20   |

| 2.3.1.33   | TCK/DSCK                      | 2-20   |

| 2.3.1.34   | TDO/DSDO                      | 2-21   |

| 2.3.1.35   | TRST                          | 2-21   |

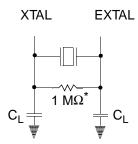

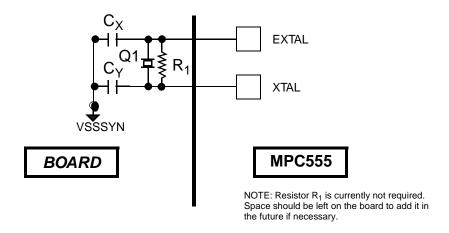

| 2.3.1.36   | XTAL                          | 2-21   |

| 2.3.1.37   | EXTAL                         | 2-21   |

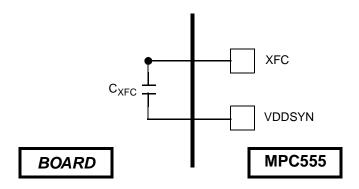

| 2.3.1.38   | XFC                           | 2-21   |

| 2.3.1.39   | CLKOUT                        | 2-21   |

| 2.3.1.40   | EXTCLK                        | 2-21   |

| 2.3.1.41   | VDDSYN                        | 2-22   |

| 2.3.1.42   | VSSSYN                        | 2-22   |

| 2.3.1.43   | ENGCLK/BUCLK                  | 2-22   |

| 2.3.2 QSM  | CM PADS                       | 2-22   |

| 2.3.2.1    | PCS0/ <del>SS</del> /QGPIO[0] | 2-22   |

| 2.3.2.2    | PCS(1:3)/QGPIO[1:3]           | 2-22   |

| 2.3.2.3    | MISO/QGPIO[4]                 | 2-22   |

| 2.3.2.4    | MOSI/QGPIO[5]                 | 2-23   |

| 2.3.2.5    | SCK/QGPIO[6]                  | 2-23   |

| 2.3.2.6    | TXD[1:2]/QGPO[1:2]            | 2-23   |

| 2.3.2.7    | RXD[1:2]/QGPI[1:2]            | 2-23   |

| 2.3.2.8    | ECK                           | 2-23   |

| 2.3.3 MIOS | PADS                          | 2-24   |

| 2.3.3.1    | MDA[11], [13]                 | 2-24   |

| 2.3.3.2    | MDA[12], [14]                 | 2-24   |

| 2.3.3.3    | MDA[15], [27:31]              | 2-24   |

| 2.3.3.4    | MPWM[0:3], [16:19]            | 2-24   |

| 2335       | \/FI0·21/MPI032BI0·21         | 2-24   |

| Paragraph                                                                    | Page    |

|------------------------------------------------------------------------------|---------|

| Number                                                                       | Number  |

| 2.3.3.6 VFLS[0:1]/MPIO32B[3:4]                                               | 2-24    |

| 2.3.3.7 MPIO32B[5:15]                                                        | 2-25    |

| 2.3.4 TPU_A/TPU_B PADS                                                       | 2-25    |

| 2.3.4.1 TPUCH[0:15]                                                          | 2-25    |

| 2.3.4.2 T2CLK                                                                | 2-25    |

| 2.3.5 QADC_A/QADC_B PADS                                                     | 2-25    |

| 2.3.5.1 ETRIG[1:2]                                                           | 2-25    |

| 2.3.5.2 AN[0]/ANW/PQB[0]                                                     | 2-25    |

| 2.3.5.3 AN[1]/ANX/PQB[1]                                                     | 2-26    |

| 2.3.5.4 AN[2]/ANY/PQB[2]                                                     | 2-26    |

| 2.3.5.5 AN[3]/ANZ/PQB[3]                                                     | 2-26    |

| 2.3.5.6 AN[48:51]/PQB[4:7]                                                   | 2-26    |

| 2.3.5.7 AN[52:54]/MA[0:2]/PQA[0:2]                                           | 2-27    |

| 2.3.5.8 AN[55:59]/PQA[3:7]                                                   | 2-27    |

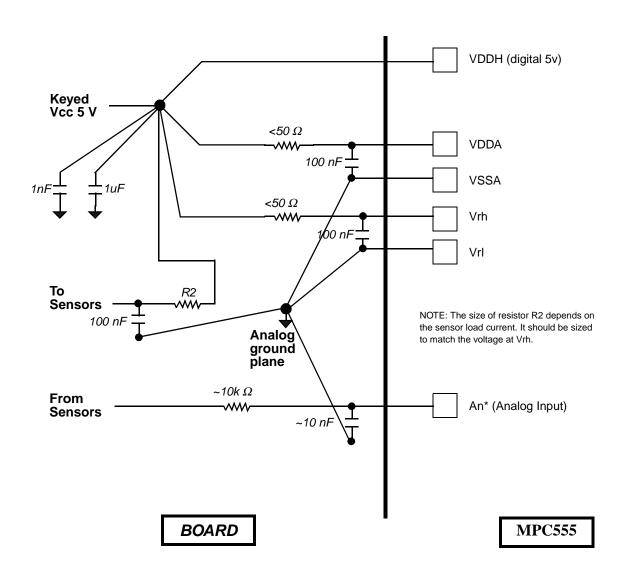

| 2.3.5.9 VRH                                                                  | 2-27    |

| 2.3.5.10 VRL                                                                 | 2-27    |

| 2.3.5.11 VDDA                                                                | 2-27    |

| 2.3.5.12 VSSA                                                                | 2-27    |

| 2.3.6 TOUCAN_A/TOUCAN_B PADS                                                 | 2-27    |

| 2.3.6.1 CNTX0                                                                | 2-27    |

| 2.3.6.2 CNRX0                                                                | 2-28    |

| 2.3.7 CMF PADS                                                               | 2-28    |

| 2.3.7.1 EPEE                                                                 | 2-28    |

| 2.3.7.2 VPP                                                                  | 2-28    |

| 2.3.7.3 VDDF                                                                 | 2-28    |

| 2.3.7.4 VSSF                                                                 | 2-28    |

| 2.3.8 GLOBAL POWER SUPPLIES                                                  | 2-28    |

| 2.3.8.1 VDDL                                                                 | 2-28    |

| 2.3.8.2 VDDH                                                                 | 2-28    |

| 2.3.8.3 VDDI                                                                 | 2-29    |

| 2.3.8.4 VSSI                                                                 | 2-29    |

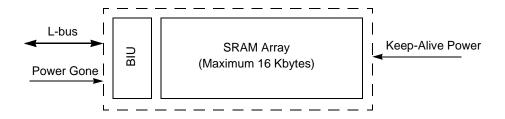

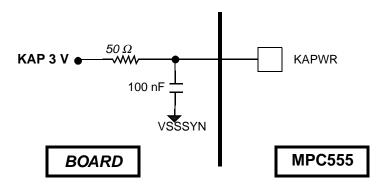

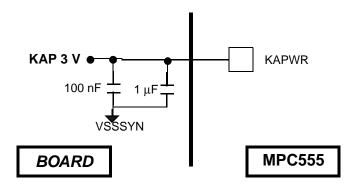

| 2.3.8.5 KAPWR                                                                | 2-29    |

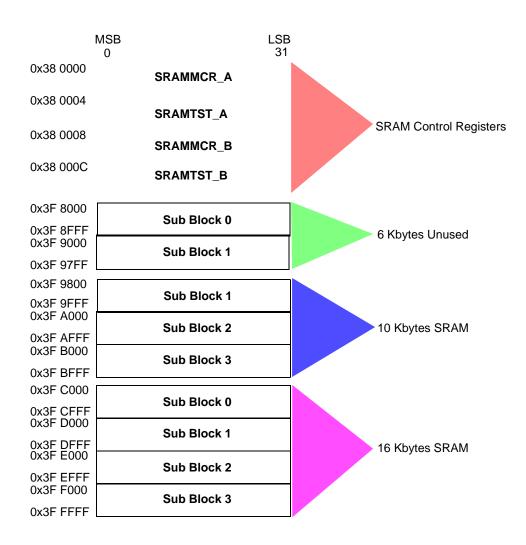

| 2.3.8.6 VDDSRAM                                                              | 2-29    |

| 2.3.8.7 VSS                                                                  | 2-29    |

| 2.4 Reset State                                                              | 2-29    |

| 2.4.1 Pin Functionality out of Reset                                         | 2-29    |

| 2.4.2 Pad Module Configuration Register (PDMCR)                              | 2-30    |

| 2.4.3 Pin State During Reset                                                 | 2-31    |

| 2.4.4 Power-On Reset and Hard Reset                                          | 2-31    |

| 2.4.5 Pull-Up and Pull-Down Enable and Disable for 5-V Only Pins             | 2-31    |

| 2.4.6 Pull-Up and Pull-Down Enable and Disable for 3-V / 5-V Multiplexed Pin | ıs 2-31 |

| 2.4.6.1 PRDS Signal                                                          | 2-31    |

| 2.4.6.2 Encoded 3-V / 5-V Select                                             | 2-33    |

| arayrapır                                           | raye                                  |

|-----------------------------------------------------|---------------------------------------|

| Number                                              | Number                                |

| 2.4.6.3 Examples                                    |                                       |

| 2.4.7 Special Pull Resistor Disable Control (SPRDS) |                                       |

| 2.4.8 Pin Reset States                              |                                       |

| 2.5 Pad Types                                       |                                       |

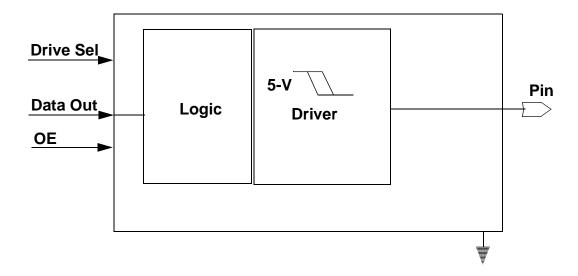

| 2.5.1 Pad Interface Signals                         |                                       |

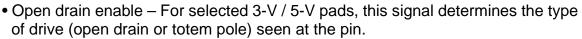

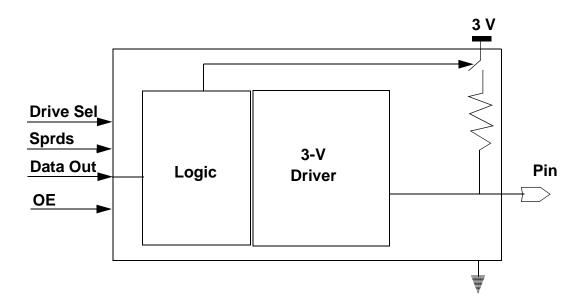

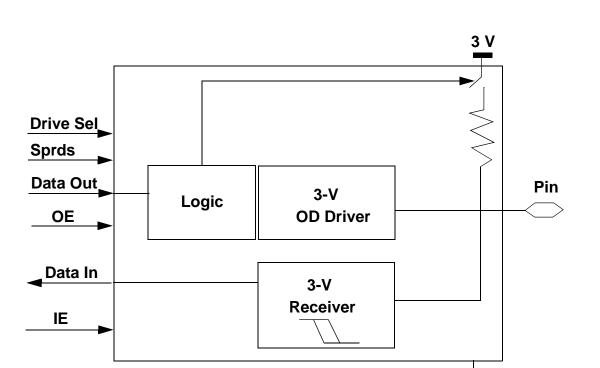

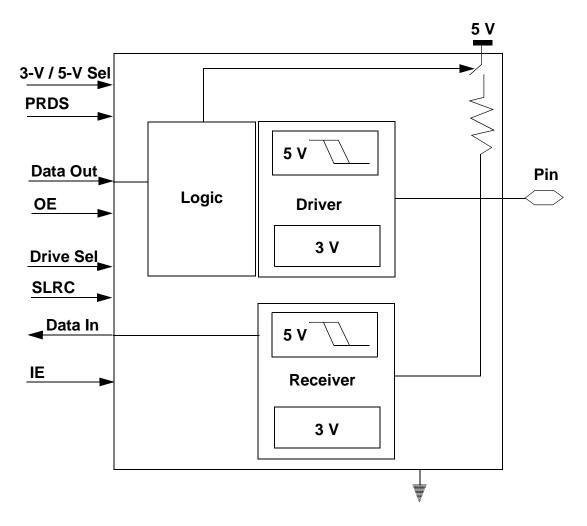

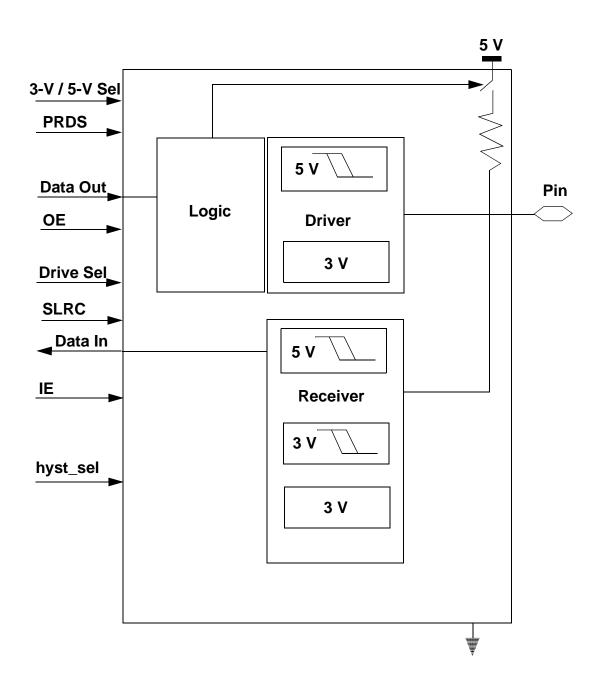

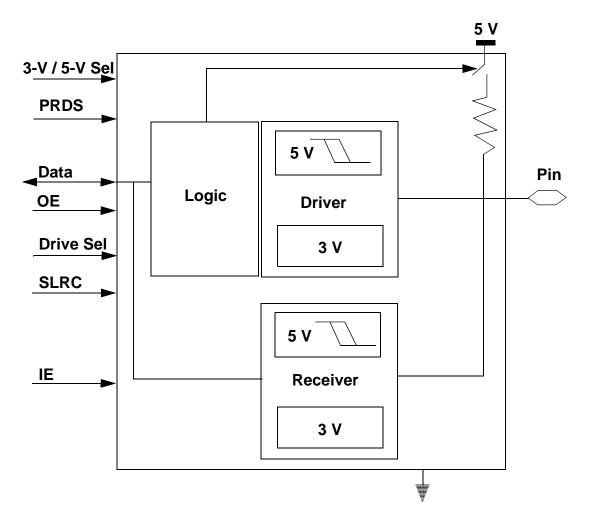

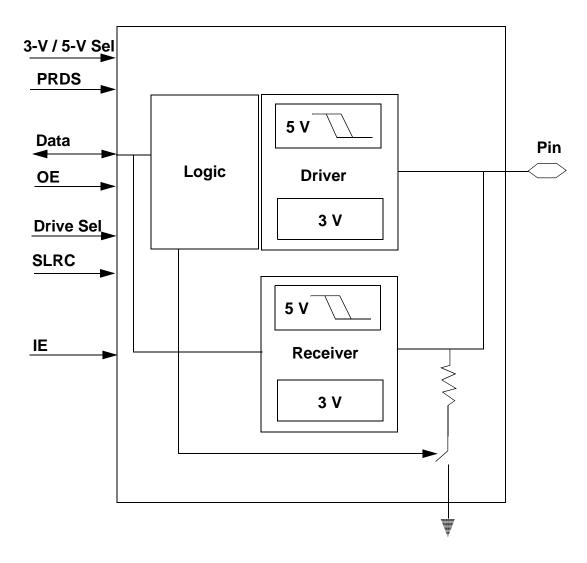

| 2.5.2 Three-Volt Output Pad                         |                                       |

| 2.5.2.1 Type A Interface                            |                                       |

| 2.5.2.2 Type B Interface (Clock Pad)                |                                       |

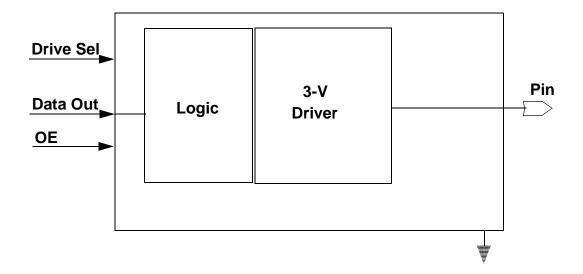

| 2.5.3 Three-Volt Input Pad                          |                                       |

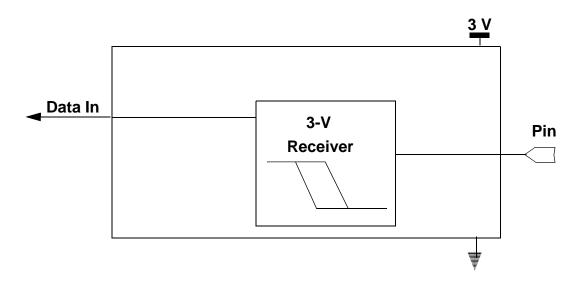

| 2.5.3.1 Type C Interface                            |                                       |

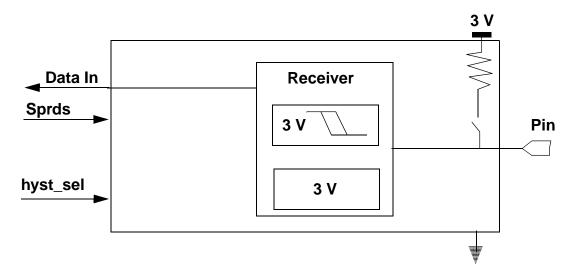

| 2.5.3.2 Type CH Interface                           |                                       |

| 2.5.3.3 Type CNH Interface                          |                                       |

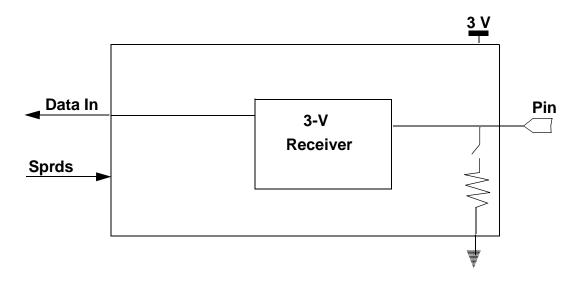

| 2.5.3.4 Type D Interface                            |                                       |

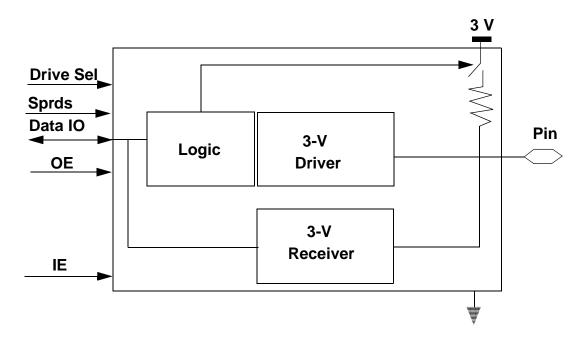

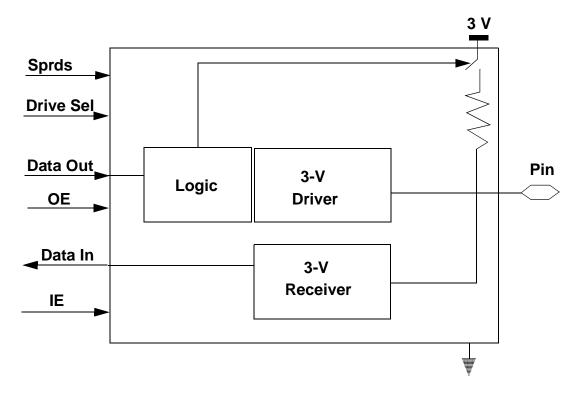

| 2.5.4 Three-Volt Input/Output Pad                   |                                       |

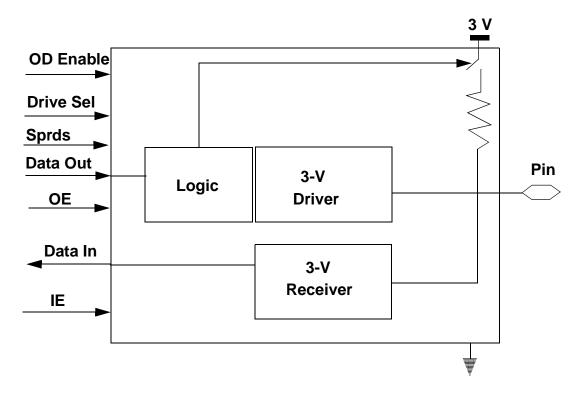

| 2.5.4.1 Type E Interface                            |                                       |

| 2.5.4.2 Type EOH Interface                          |                                       |

| 2.5.4.3 Type F Interface                            |                                       |

| 2.5.4.4 Type G Interface                            |                                       |

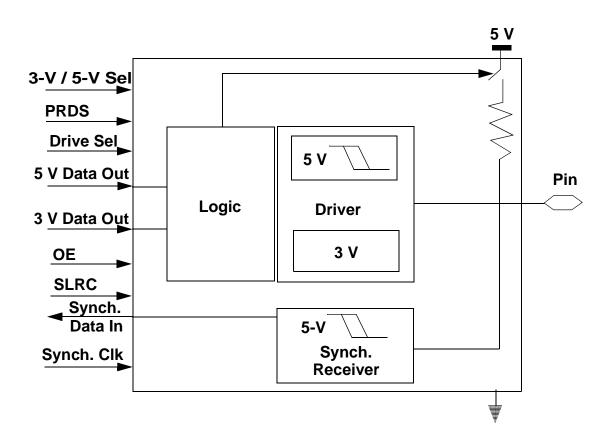

| 2.5.5 Five-Volt Input/Output Pad                    |                                       |

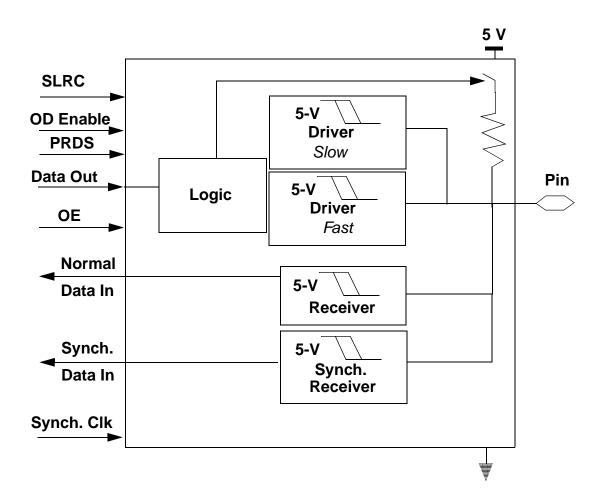

| 2.5.5.1 Type H Interface                            |                                       |

| 2.5.5.2 Type I Interface                            |                                       |

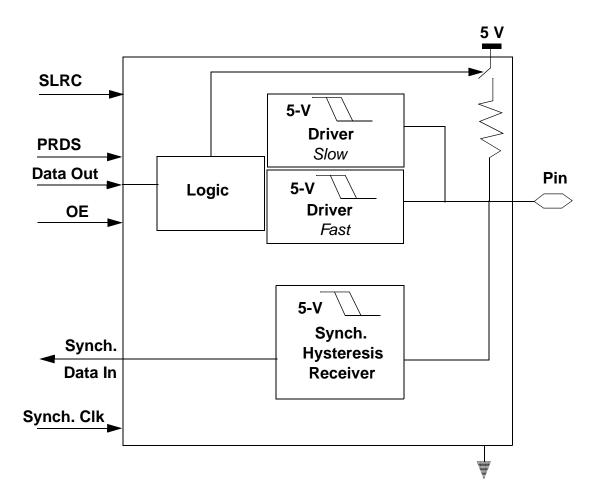

| 2.5.5.3 Type IH Interface                           |                                       |

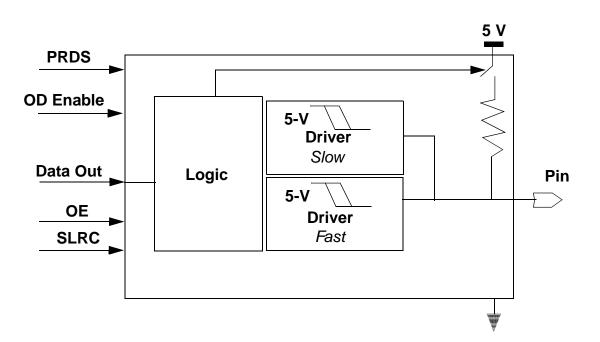

| 2.5.5.4 Type J Interface                            |                                       |

| 2.5.5.5 Type JD Interface                           |                                       |

| 2.5.6 Type K Interface (EPEE Pad)                   |                                       |

| 2.5.7 Analog Pads                                   |                                       |

| 2.5.7.1 Type L Interface (QADC Port A)              |                                       |

| 2.5.7.2 Type M Interface (QADC Port B)              |                                       |

| 2.5.7.3 Type N Interface (ETRIG)                    |                                       |

| 2.5.8 Pads with Fast Mode                           |                                       |

| 2.5.8.1 Type O Interface (QSMCM Pads)               |                                       |

| 2.5.8.2 Type P Interface (TPU and MIOS Pads)        |                                       |

| 2.5.9 5V Input, 5V Output Pads                      |                                       |

| 2.5.9.1 5V Output (Type Q)                          |                                       |

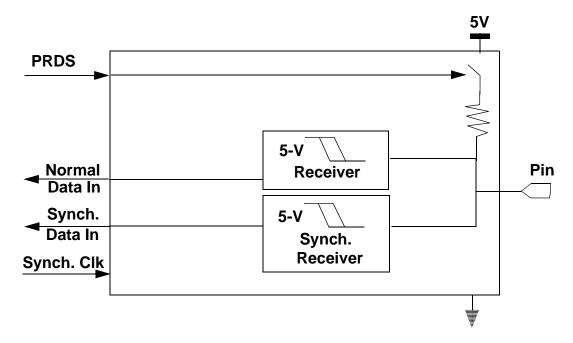

| 2.5.9.2 Type R Interface                            |                                       |

| 2.5.9.3 5V Output for Clock Pad                     |                                       |

| 2.6 Pad Groups                                      |                                       |

| 2.7 Pin Names and Abbreviations                     | 2-59                                  |

| Section 3                                           |                                       |

| CENTRAL PROCESSING UNIT                             | Γ                                     |

| 3.1 RCPU Features                                   |                                       |

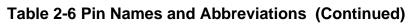

| 3.2 RCPU Block Diagram.                             |                                       |

| •                                                   | · · · · · · · · · · · · · · · · · · · |

| Paragraph                                                  | Page    |

|------------------------------------------------------------|---------|

| Number                                                     | Number  |

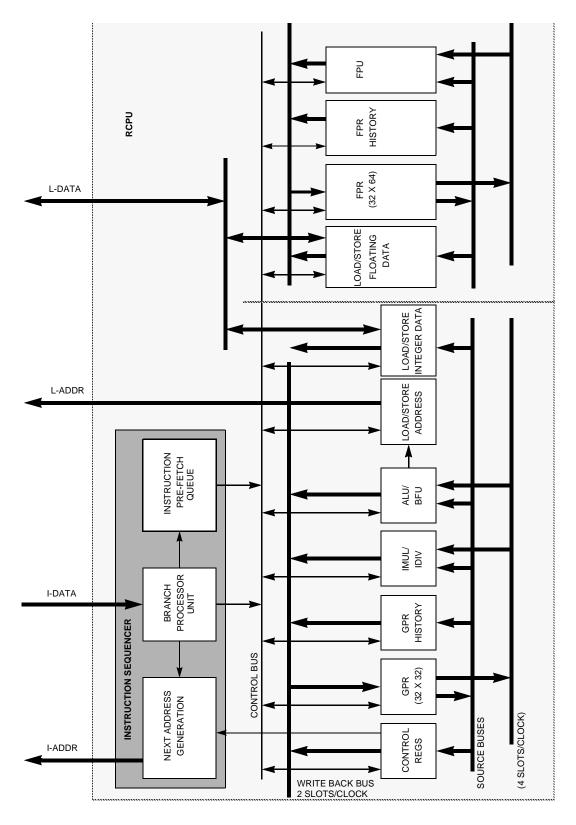

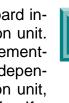

| 3.3 Instruction Sequencer                                  |         |

| 3.4 Independent Execution Units                            |         |

| 3.4.1 Branch Processing Unit (BPU)                         |         |

| 3.4.2 Integer Unit (IU)                                    |         |

| 3.4.3 Load/Store Unit (LSU)                                |         |

| 3.4.4 Floating-Point Unit (FPU)                            |         |

| 3.5 Levels of the PowerPC Architecture                     |         |

| 3.6 RCPU Programming Model                                 |         |

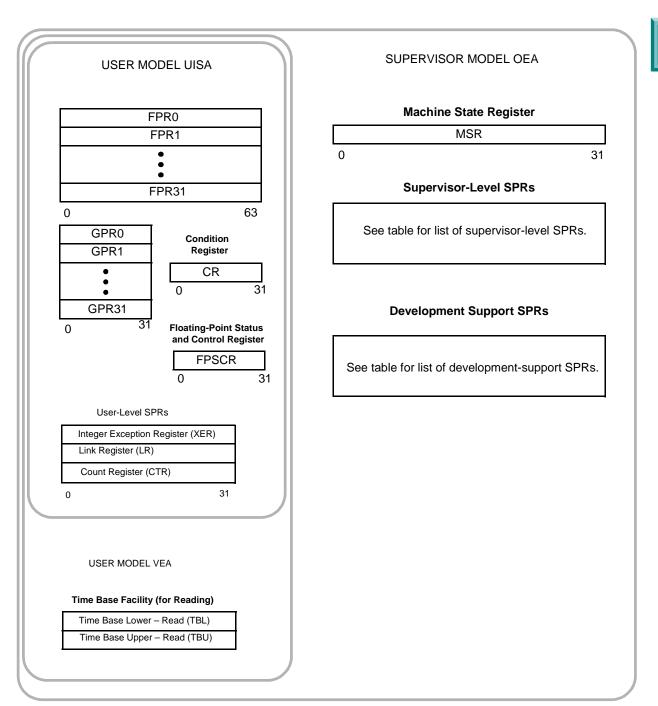

| 3.7 PowerPC UISA Register Set                              |         |

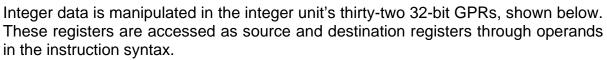

| 3.7.1 General-Purpose Registers (GPRs)                     |         |

| 3.7.2 Floating-Point Registers (FPRs)                      |         |

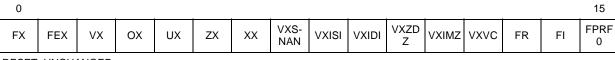

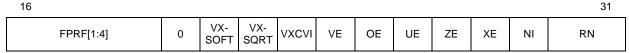

| 3.7.3 Floating-Point Status and Control Register (FPSCR)   |         |

| 3.7.4 Condition Register (CR)                              |         |

| 3.7.4.1 Condition Register CR0 Field Definition            |         |

| 3.7.4.2 Condition Register CR1 Field Definition            |         |

| 3.7.4.3 Condition Register CRn Field — Compare Instruction | on 3-17 |

| 3.7.5 Integer Exception Register (XER)                     |         |

| 3.7.6 Link Register (LR)                                   |         |

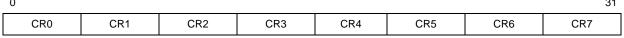

| 3.7.7 Count Register (CTR)                                 |         |

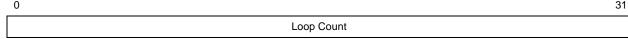

| 3.8 PowerPC VEA Register Set — Time Base                   |         |

| 3.9 PowerPC OEA Register Set                               |         |

| 3.9.1 Machine State Register (MSR)                         |         |

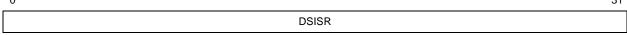

| 3.9.2 DAE/Source Instruction Service Register (DSISR)      |         |

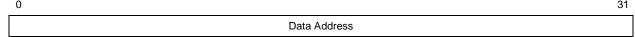

| 3.9.3 Data Address Register (DAR)                          |         |

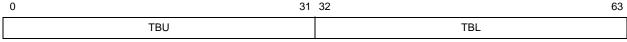

| 3.9.4 Time Base Facility (TB) — OEA                        |         |

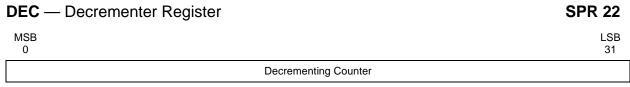

| 3.9.5 Decrementer Register (DEC)                           |         |

| 3.9.6 Machine Status Save/Restore Register 0 (SRR0)        |         |

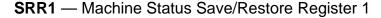

| 3.9.7 Machine Status Save/Restore Register 1 (SRR1)        |         |

| 3.9.8 General SPRs (SPRG0–SPRG3)                           |         |

| 3.9.9 Processor Version Register (PVR)                     |         |

| 3.9.10 Implementation-Specific SPRs                        |         |

| 3.9.10.1 EIE, EID, and NRI Special-Purpose Registers       |         |

| 3.9.10.2 Floating-Point Exception Cause Register (FPECR)   | )       |

| 3.9.10.3 Additional Implementation-Specific Registers      |         |

| 3.10 Instruction Set                                       |         |

| 3.10.1 Instruction Set Summary                             |         |

| 3.10.2 Recommended Simplified Mnemonics                    |         |

| 3.10.3 Calculating Effective Addresses                     |         |

| 3.11 Exception Model                                       |         |

| 3.11.1 Exception Classes                                   |         |

| 3.11.2 Ordered Exceptions                                  |         |

| 3.11.3 Unordered Exceptions                                |         |

| 3.11.4 Precise Exceptions                                  | 3-35    |

| Paragraph                                                                  | Page   |

|----------------------------------------------------------------------------|--------|

| Number                                                                     | Number |

| 3.11.5 Exception Vector Table                                              |        |

| 3.12 Instruction Timing                                                    |        |

| 3.13 PowerPC User Instruction Set Architecture (UISA)                      |        |

| 3.13.1 Computation Modes                                                   |        |

| 3.13.2 Reserved Fields                                                     |        |

| 3.13.3 Classes of Instructions                                             |        |

| 3.13.4 Exceptions                                                          |        |

| 3.13.5 The Branch Processor                                                |        |

| 3.13.6 Instruction Fetching                                                |        |

| 3.13.7 Branch Instructions                                                 |        |

| 3.13.7.1 Invalid Branch Instruction Forms                                  |        |

| 3.13.7.2 Branch Prediction                                                 |        |

| 3.13.8 The Fixed-Point Processor                                           |        |

| 3.13.8.1 Fixed-Point Instructions                                          | 3-40   |

| 3.13.9 Floating-Point Processor                                            |        |

| 3.13.9.1 General                                                           |        |

| 3.13.9.2 Optional instructions                                             |        |

| 3.13.10 Load/Store Processor                                               |        |

| 3.13.10.1 Fixed-Point Load With Update and Store With Update Instructions. |        |

| 3.13.10.2 Fixed-Point Load and Store Multiple Instructions                 |        |

| 3.13.10.3 Fixed-Point Load String Instructions                             |        |

| 3.13.10.4 Storage Synchronization Instructions                             |        |

| 3.13.10.5 Floating-Point Load and Store With Update Instructions           |        |

| 3.13.10.6 Floating-Point Load Single Instructions                          |        |

| 3.13.10.7 Floating-Point Store Single Instructions                         |        |

| 3.13.10.8 Optional Instructions                                            |        |

| 3.13.10.9 Little-Endian Byte Ordering                                      |        |

| 3.14 PowerPC Virtual Environment Architecture (VEA)                        |        |

| 3.14.1 Atomic Update Primitives                                            |        |

| 3.14.2 Effect of Operand Placement on Performance                          | 3-42   |

| 3.14.3 Storage Control Instructions                                        |        |

| 3.14.4 Instruction Synchronize (isync) Instruction                         | 3-43   |

| 3.14.4.1 Enforce In-Order Execution of I/O (eieio) Instruction             | 3-43   |

| 3.14.5 Timebase                                                            | 3-43   |

| 3.15 POWERPC Operating Environment Architecture (OEA)                      | 3-43   |

| 3.15.1 Branch Processor Registers                                          | 3-43   |

| 3.15.1.1 Machine State Register (MSR)                                      | 3-43   |

| 3.15.1.2 Branch Processors Instructions                                    | 3-43   |

| 3.15.2 Fixed-Point Processor                                               | 3-44   |

| 3.15.2.1 Special Purpose Registers                                         | 3-44   |

| 3.15.3 Storage Control Instructions                                        |        |

| 3.15.4 Interrupts                                                          | 3-44   |

| 3.15.4.1 System Reset Interrupt                                            | 3-44   |

| aragraph                                                                         | rage   |

|----------------------------------------------------------------------------------|--------|

| Number                                                                           | Number |

| 3.15.4.2 Machine Check Interrupt                                                 |        |

| 3.15.4.3 Data Storage Interrupt                                                  |        |

| 3.15.4.4 Instruction Storage Interrupt                                           |        |

| 3.15.4.5 Alignment Interrupt                                                     |        |

| 3.15.4.6 Floating-Point Enabled Exception Type Program Interrupt                 | 3-47   |

| 3.15.4.7 Illegal Instruction Type Program Interrupt                              |        |

| 3.15.4.8 Privileged Instruction Type Program interrupt                           |        |

| 3.15.4.9 Floating-Point Unavailable Interrupt                                    | 3-47   |

| 3.15.4.10 Trace Interrupt                                                        | 3-47   |

| 3.15.4.11 Floating-Point Assist Interrupt                                        | 3-48   |

| 3.15.4.12 Implementation-Dependent Software Emulation Interrupt                  | 3-49   |

| 3.15.4.13 Implementation-Specific Instruction Storage Protection Error Interrupt | 3-50   |

| 3.15.4.14 Implementation-Specific Data Storage Protection Error Interrupt        | 3-51   |

| 3.15.4.15 Implementation-Specific Debug Interrupts                               | 3-52   |

| 3.15.4.16 Partially Executed Instructions                                        | 3-53   |

| 3.15.5 Timer Facilities                                                          | 3-54   |

| 3.15.6 Optional Facilities and Instructions                                      | 3-54   |

| Section 4                                                                        |        |

| BURST BUFFER                                                                     |        |

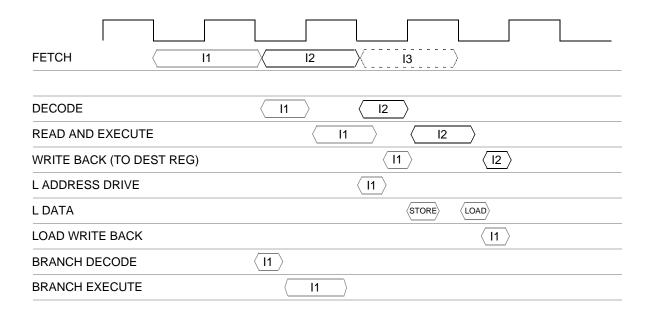

| 4.1 Burst Buffer Block Diagram                                                   | 4-1    |

| 4.2 Burst Buffer Features                                                        | 4-2    |

| 4.3 Little-Endian Support                                                        | 4-3    |

| 4.4 Modes Of Operation                                                           | 4-3    |

| 4.4.1 Normal Operation                                                           | 4-3    |

| 4.4.2 Slave Operation                                                            | 4-4    |

| 4.4.3 Reset Operation                                                            | 4-4    |

| 4.4.4 Debug Mode Operation                                                       | 4-4    |

| 4.4.5 Standby Mode Operation                                                     | 4-4    |

| 4.4.6 Burst Operation                                                            | 4-4    |

| 4.4.7 Error Detection.                                                           | 4-4    |

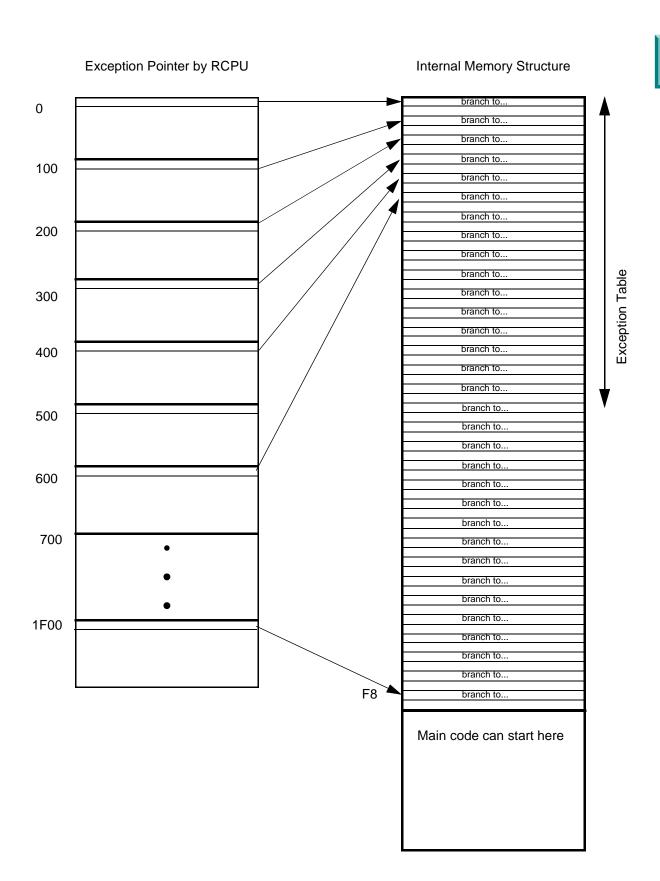

| 4.5 Exception Table Relocation                                                   | 4-5    |

| 4.5.1 Exception Table Relocation Operation                                       | 4-5    |

| 4.6 Burst Buffer Programming Model                                               | 4-8    |

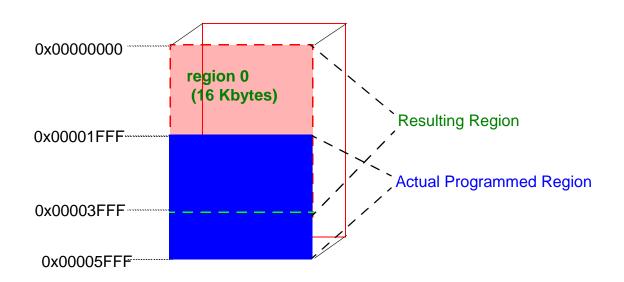

| 4.6.1 Region Base Address Registers                                              | 4-9    |

| 4.6.2 Region Attribute Registers MI_RA[0:3] Description                          | 4-9    |

| 4.6.3 Global Region Attribute Register Description (MI_GRA)                      | 4-10   |

| 4.6.4 BBC Module Configuration Register (BBCMCR)                                 | 4-11   |

| Section 5                                                                        |        |

| UNIFIED SYSTEM INTERFACE UNIT                                                    |        |

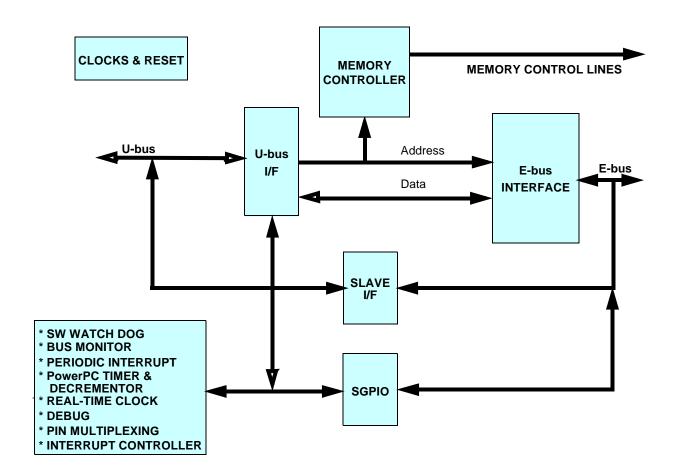

| 5.1 Module Overview                                                              | 5-1    |

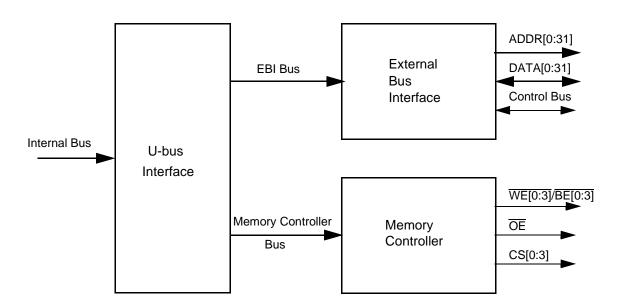

| 5.2 SIU Architecture                                                             | 5-2    |

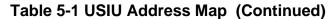

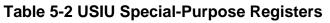

| 5.3 USIU Address Map                                                             | 5-2    |

|                                                                                  |        |

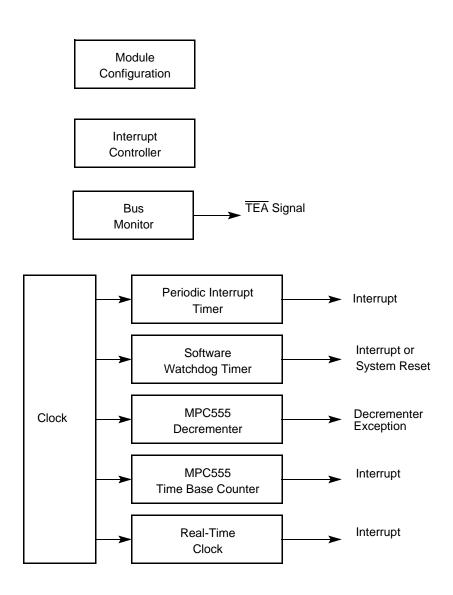

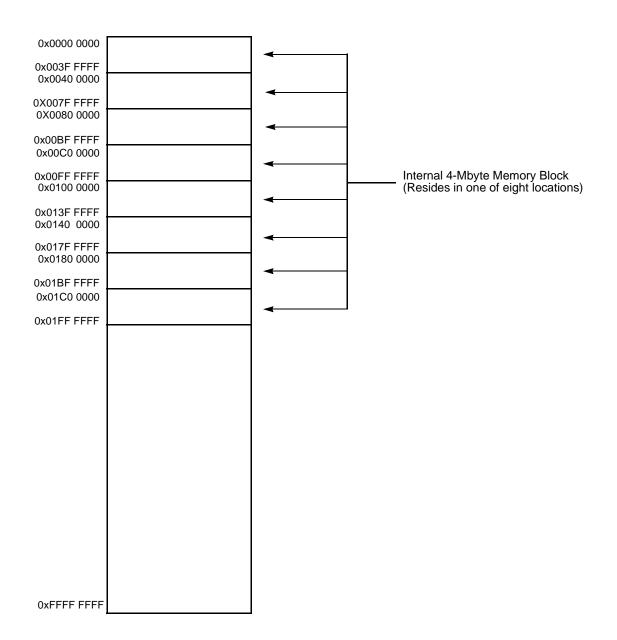

# Section 6 SYSTEM CONFIGURATION AND PROTECTION

| 6.1  | System Configuration                                 | . 6-3 |

|------|------------------------------------------------------|-------|

|      | 6.1.1 USIU Pins Multiplexing                         | . 6-4 |

|      | 6.1.2 Memory Mapping                                 | . 6-4 |

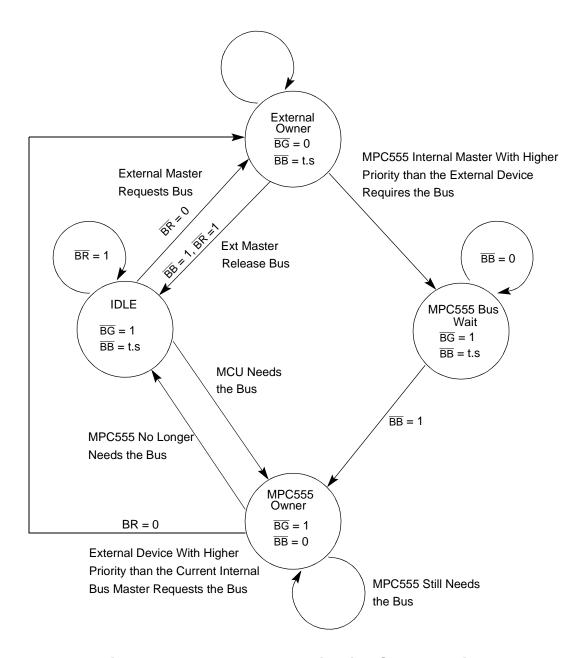

|      | 6.1.3 Arbitration Support                            | . 6-5 |

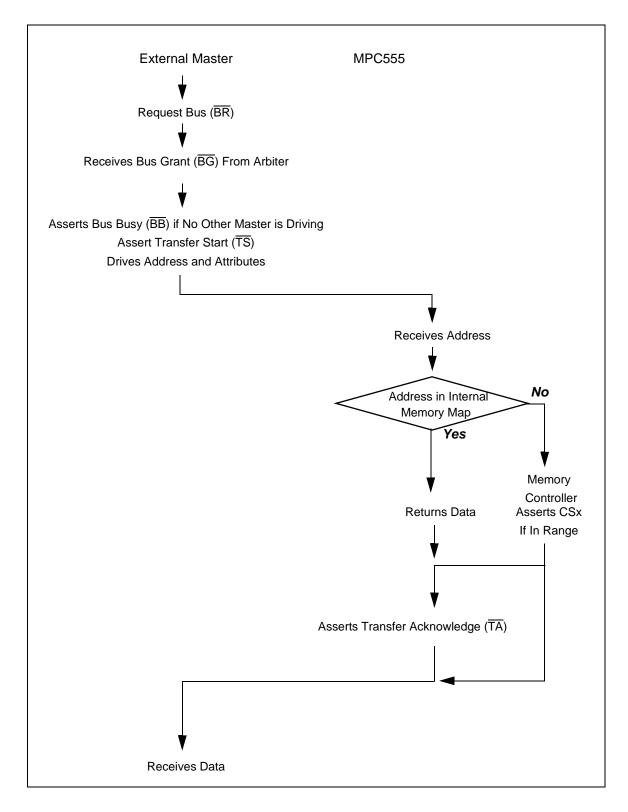

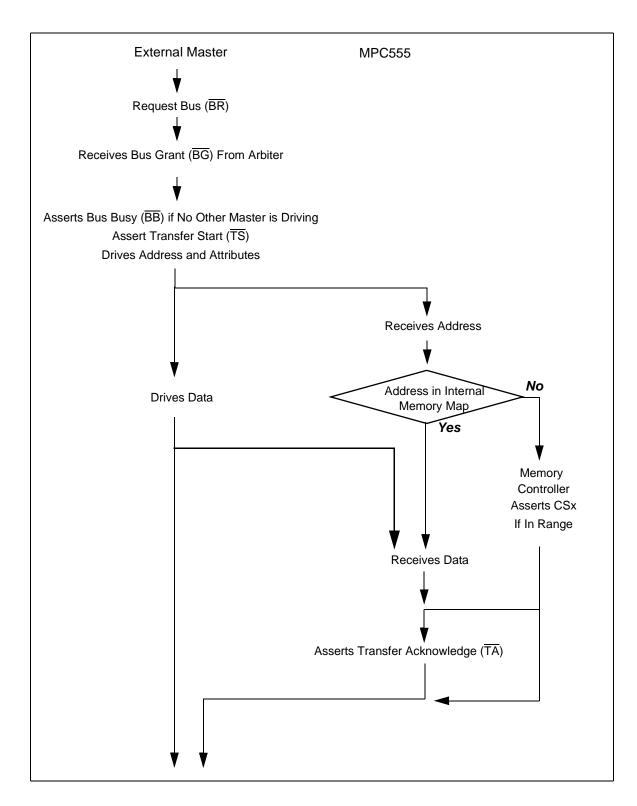

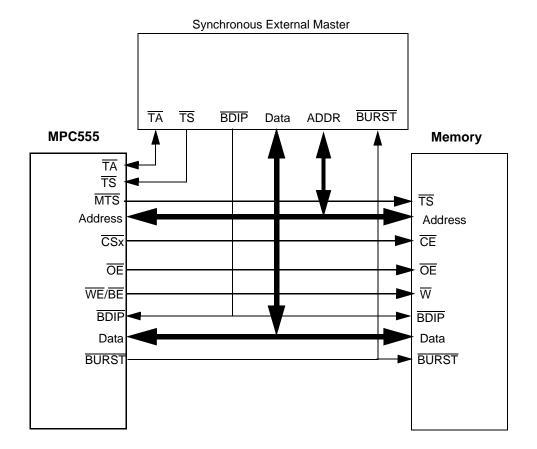

| 6.2  | External Master Modes                                | . 6-5 |

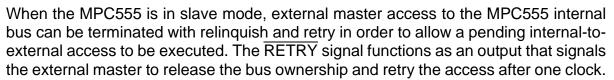

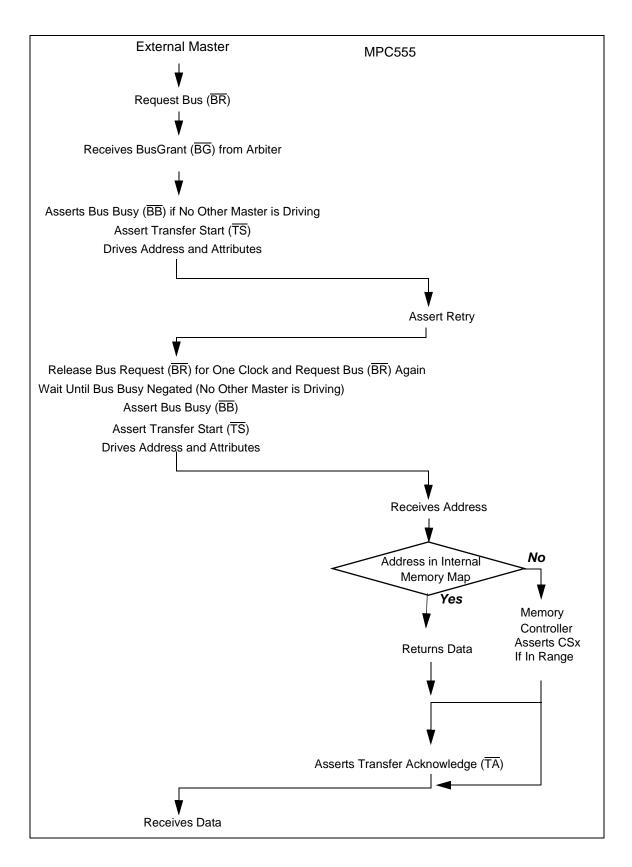

|      | 6.2.1 Operation of External Master Modes             | . 6-6 |

|      | 6.2.2 Address Decoding for External Accesses         | . 6-7 |

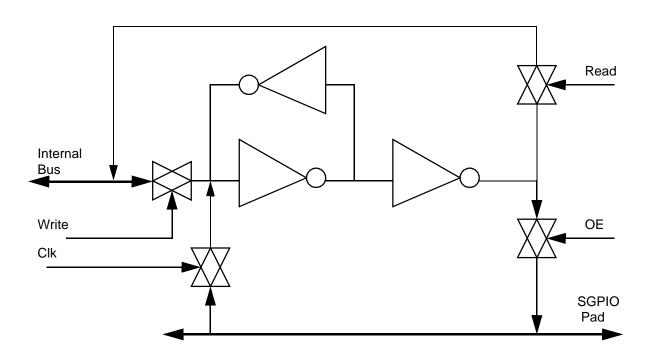

| 6.3  | USIU General-Purpose I/O                             | . 6-7 |

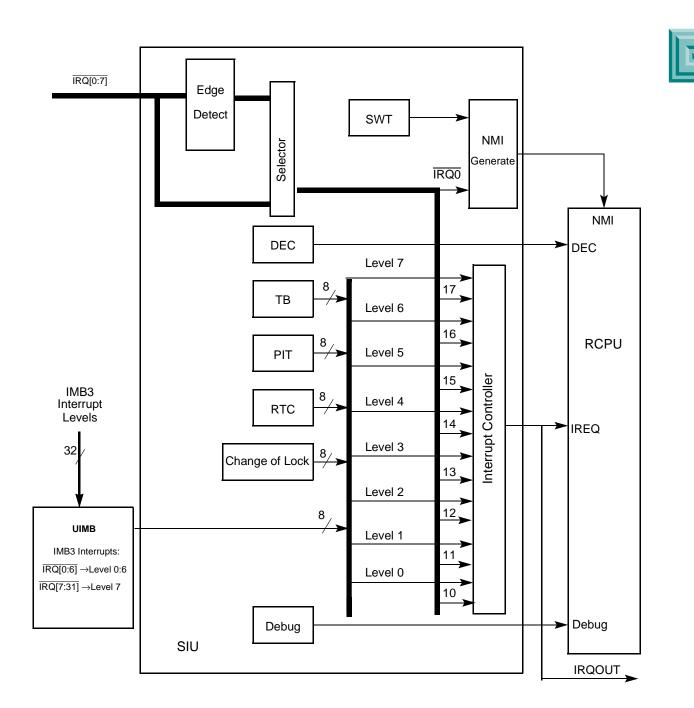

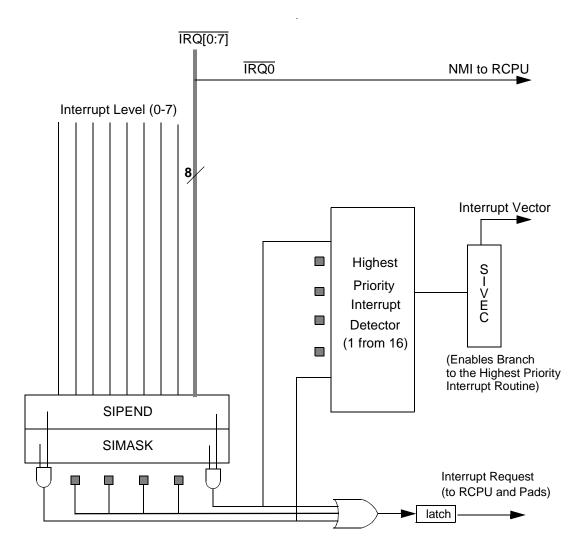

| 6.4  | Interrupt Controller                                 | . 6-9 |

|      | 6.4.1 SIU Interrupt Sources Priority                 | 6-12  |

| 6.5  | Hardware Bus Monitor                                 | 6-13  |

| 6.6  | MPC555 Decrementer                                   | 6-13  |

| 6.7  | MPC555 Time Base (TB)                                | 6-14  |

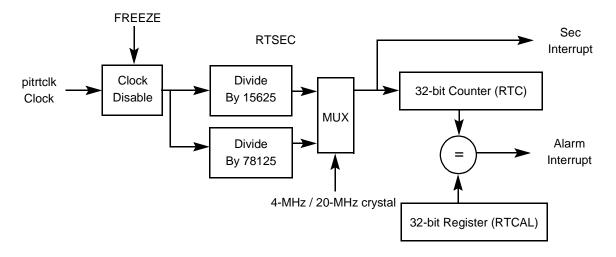

|      | Real-Time Clock (RTC)                                |       |

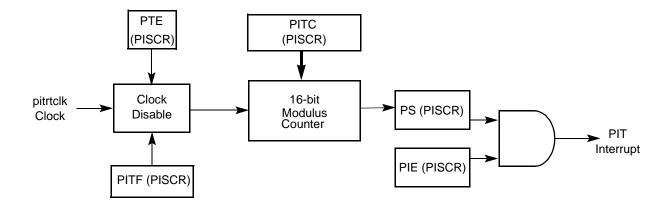

| 6.9  | Periodic Interrupt Timer (PIT)                       | 6-16  |

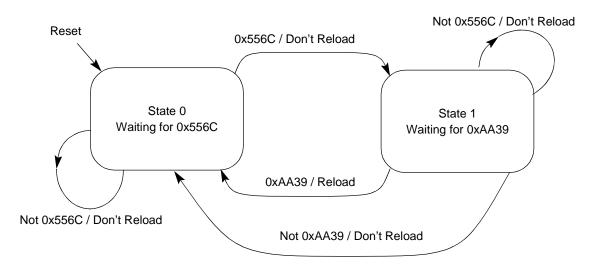

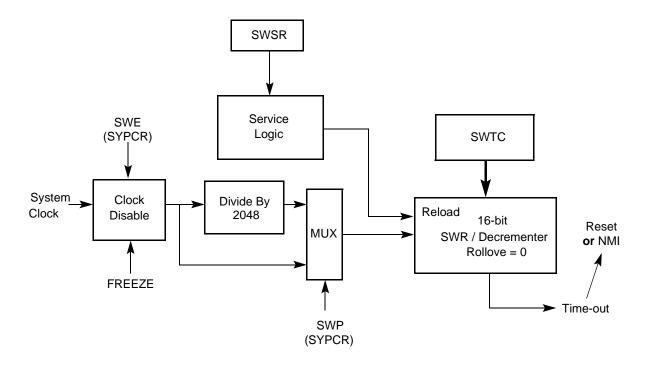

| 6.10 | Software Watchdog Timer (SWT)                        | 6-17  |

| 6.11 | Freeze Operation                                     | 6-18  |

| 6.12 | 2 Low Power Stop Operation                           | 6-18  |

| 6.13 | System Configuration and Protection Registers        | 6-19  |

|      | 6.13.1 System Configuration Registers                | 6-19  |

|      | 6.13.1.1 SIU Module Configuration Register           | 6-19  |

|      | 6.13.1.2 Internal Memory Map Register                | 6-22  |

|      | 6.13.1.3 External Master Control Register (EMCR)     | 6-23  |

|      | 6.13.2 SIU Interrupt Registers                       | 6-24  |

|      | 6.13.2.1 SIPEND Register                             | 6-24  |

|      | 6.13.2.2 SIU Interrupt Mask Register (SIMASK)        | 6-25  |

|      | 6.13.2.3 SIU Interrupt Edge Level Register (SIEL)    | 6-26  |

|      | 6.13.2.4 SIU Interrupt Vector Register               | 6-26  |

|      | 6.13.3 System Protection Registers                   | 6-27  |

|      | 6.13.3.1 System Protection Control Register (SYPCR)  | 6-27  |

|      | 6.13.3.2 Software Service Register (SWSR)            | 6-27  |

|      | 6.13.3.3 Transfer Error Status Register (TESR)       | 6-28  |

|      | 6.13.4 System Timer Registers                        | 6-29  |

|      | 6.13.4.1 Decrementer Register                        | 6-29  |

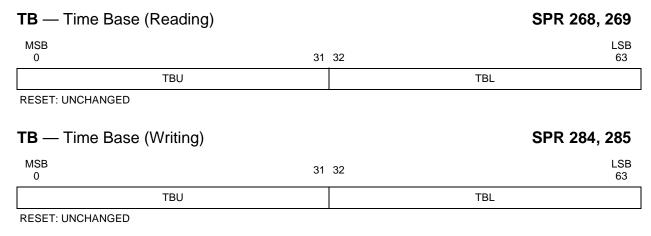

|      | 6.13.4.2 Time Base SPRs                              | 6-29  |

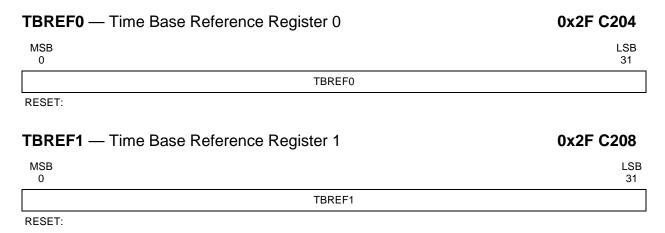

|      | 6.13.4.3 Time Base Reference Registers               | 6-30  |

|      | 6.13.4.4 Time Base Control and Status Register       | 6-30  |

|      | 6.13.4.5 Real-Time Clock Status and Control Register | 6-31  |

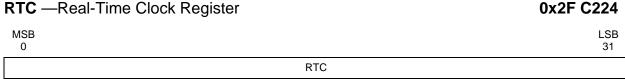

|      | 6.13.4.6 Real-Time Clock Register (RTC)              | 6-32  |

| Parag | ıraph                                                           | Page   |

|-------|-----------------------------------------------------------------|--------|

| _     | nber                                                            | Number |

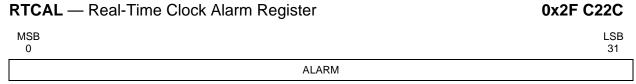

|       | 6.13.4.7 Real-Time Clock Alarm Register (RTCAL)                 |        |

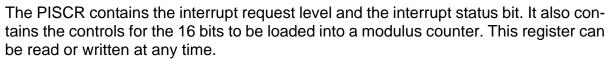

|       | 6.13.4.8 Periodic Interrupt Status and Control Register (PISCR) | 6-33   |

|       | 6.13.4.9 Periodic Interrupt Timer Count Register (PITC)         | 6-33   |

|       | 6.13.4.10 Periodic Interrupt Timer Register (PITR)              | 6-34   |

|       | 6.13.5 General-Purpose I/O Registers                            | 6-35   |

|       | 6.13.5.1 SGPIO Data Register 1 (SGPIODT1)                       | 6-35   |

|       | 6.13.5.2 SGPIO Data Register 2 (SGPIODT2)                       | 6-35   |

|       | 6.13.5.3 SGPIO Control Register (SGPIOCR)                       | 6-36   |

|       | Section 7                                                       |        |

|       | RESET                                                           |        |

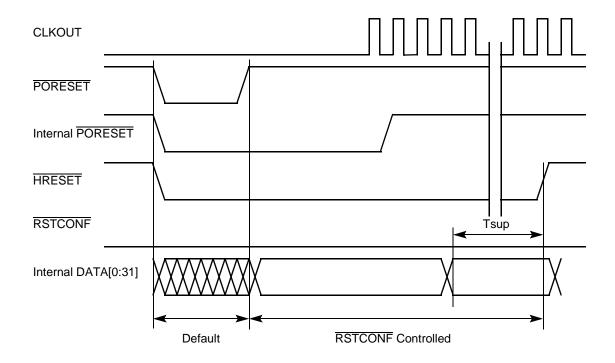

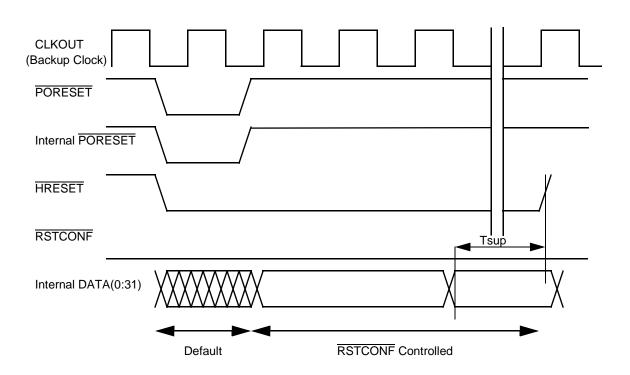

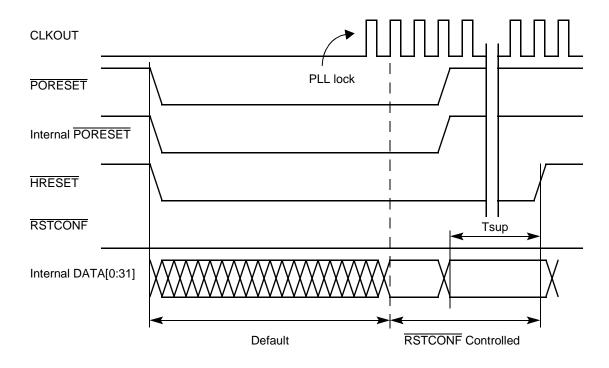

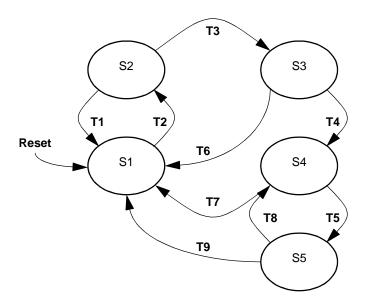

| 7.1   | Reset Operation                                                 | 7-1    |

|       | 7.1.1 Power On Reset                                            | 7-1    |

|       | 7.1.2 Hard Reset                                                | 7-2    |

|       | 7.1.3 Soft Reset                                                | 7-2    |

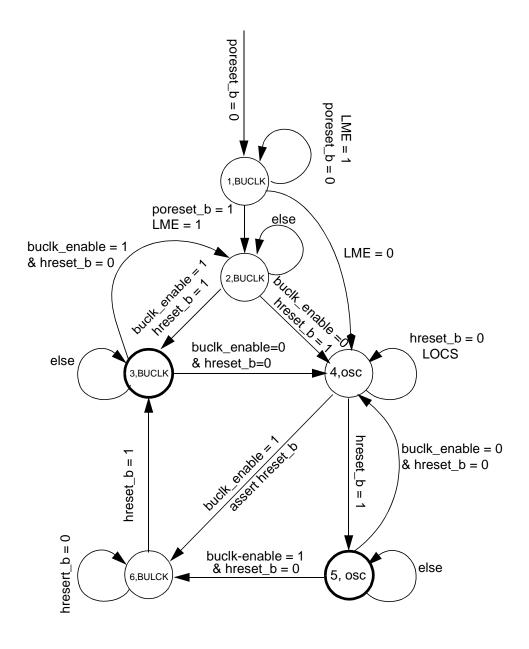

|       | 7.1.4 Loss of Lock                                              | 7-2    |

|       | 7.1.5 On-Chip Clock Switch                                      | 7-3    |

|       | 7.1.6 Software Watchdog Reset                                   | 7-3    |

|       | 7.1.7 Checkstop Reset                                           | 7-3    |

|       | 7.1.8 Debug Port Hard Reset                                     | 7-3    |

|       | 7.1.9 Debug Port Soft Reset                                     | 7-3    |

|       | 7.1.10 JTAG Reset                                               | 7-3    |

| 7.2   | Reset Actions Summary                                           | 7-3    |

| 7.3   | Data Coherency During Reset                                     | 7-4    |

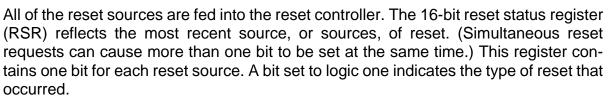

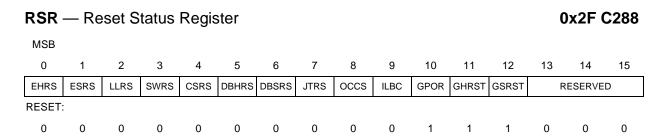

| 7.4   | Reset Status Register                                           | 7-5    |

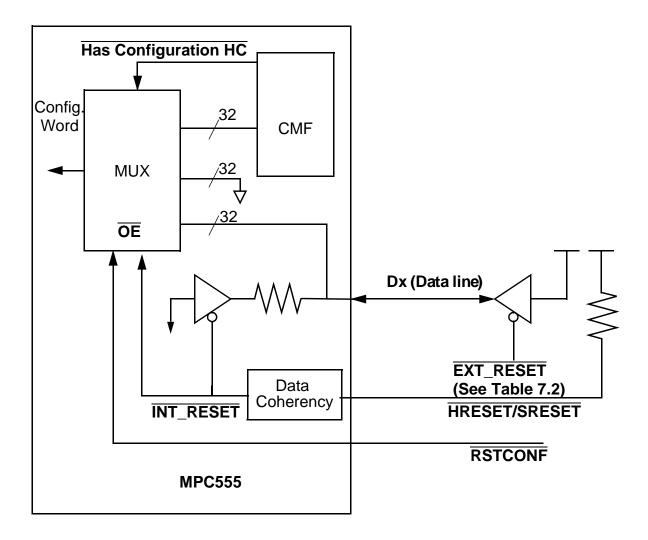

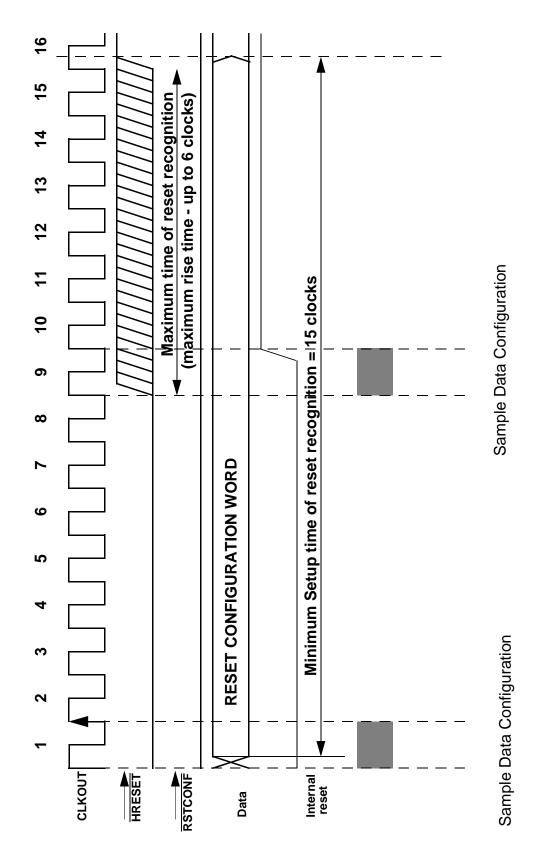

| 7.5   | Reset Configuration                                             | 7-6    |

|       | 7.5.1 Hard Reset Configuration                                  | 7-6    |

|       | 7.5.2 Hard Reset Configuration Word                             | 7-11   |

|       | 7.5.3 Soft Reset Configuration                                  | 7-12   |

|       | Section 8                                                       |        |

|       | CLOCKS AND POWER CONTROL                                        |        |

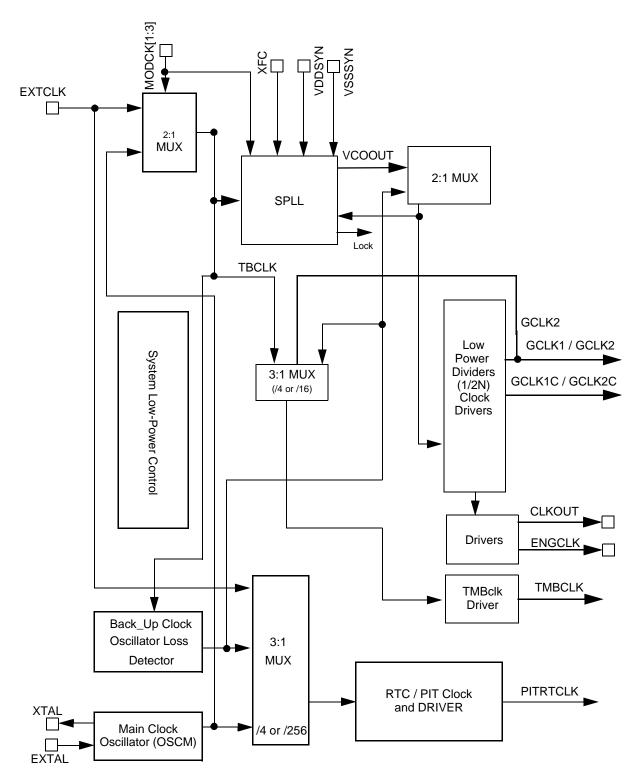

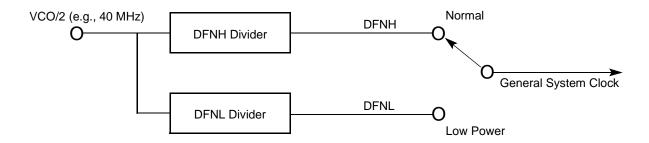

|       | Overview                                                        |        |

|       | System Clock Sources                                            |        |

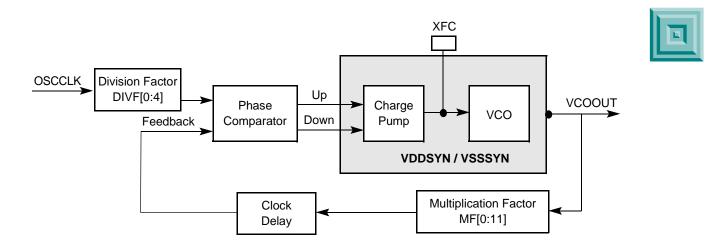

| 8.3   | System PLL                                                      |        |

|       | 8.3.1 Frequency Multiplication                                  |        |

|       | 8.3.2 Skew Elimination                                          |        |

|       | 8.3.3 Pre-Divider                                               |        |

|       | 8.3.4 PLL Block Diagram                                         |        |

|       | 8.3.5 PLL Pins                                                  |        |

|       | System Clock During PLL Loss of Lock                            |        |

|       | Low-Power Divider                                               |        |

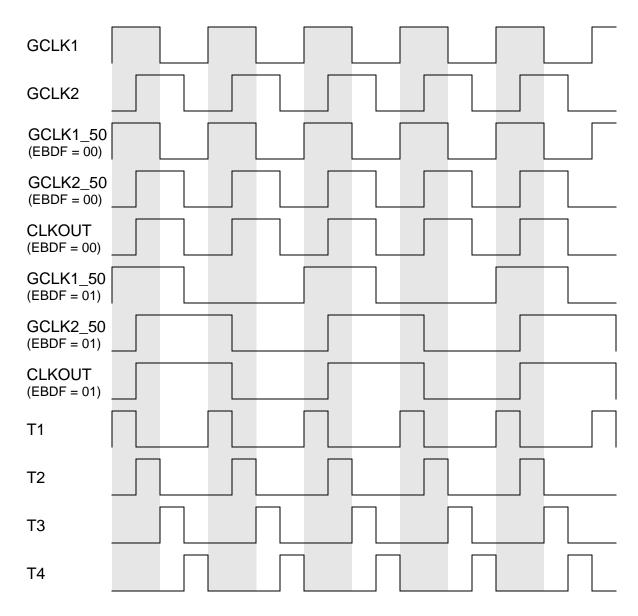

| 8.6   | MPC555 Internal Clock Signals                                   |        |

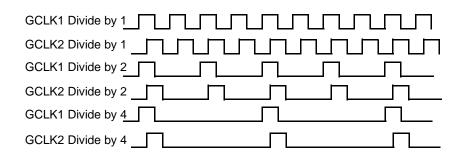

|       | 8.6.1 General System Clocks                                     | 8-9    |

| arayrapır                                                  | rage   |

|------------------------------------------------------------|--------|

| Number                                                     | Number |

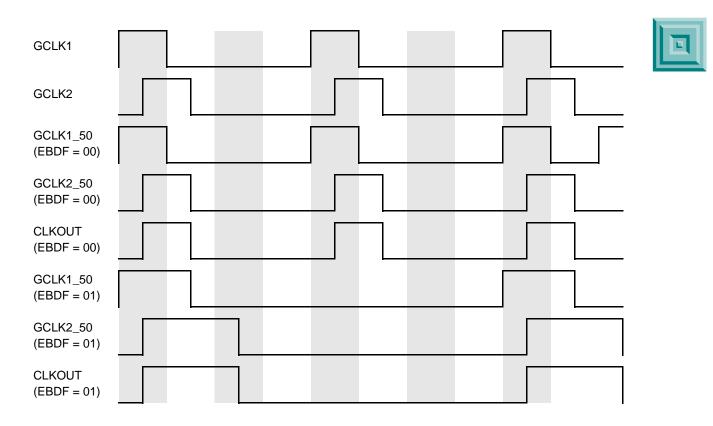

| 8.6.2 CLKOUT                                               |        |

| 8.6.3 Engineering Clock                                    |        |

| 8.7 Clock Source Switching                                 |        |

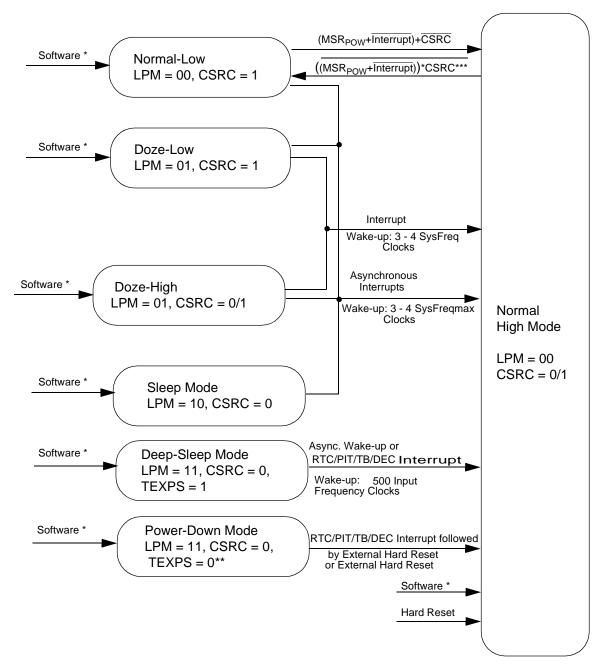

| 8.8 Low-Power Modes                                        |        |

| 8.8.1 Entering a Low-Power Mode                            |        |

| 8.8.2 Power Mode Descriptions                              |        |

| 8.8.3 Exiting from Low-Power Modes                         |        |

| 8.8.3.1 Exiting from Normal-Low Mode                       |        |

| 8.8.3.2 Exiting from Doze Mode                             |        |

| 8.8.3.3 Exiting from Deep-Sleep Mode                       |        |

| 8.8.3.4 Exiting from Power-Down Mode                       |        |

| 8.8.3.5 Low-Power Modes Flow                               |        |

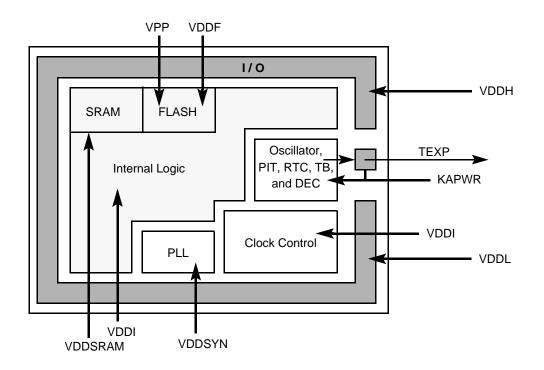

| 8.9 Basic Power Structure                                  |        |

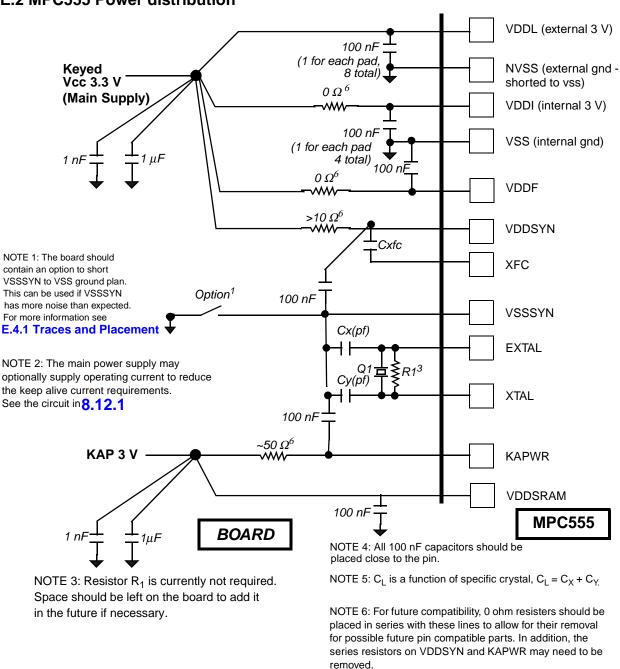

| 8.9.1 Clock Unit Power Supply                              |        |

| 8.9.2 Chip Power Structure                                 |        |

| 8.9.2.1 VDDL                                               |        |

| 8.9.2.2 VDDI                                               |        |

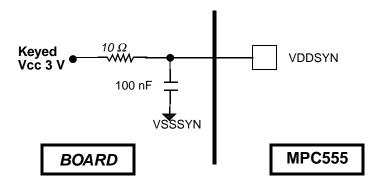

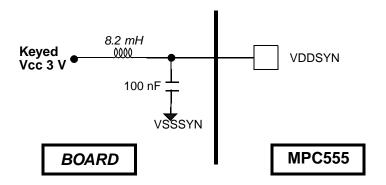

| 8.9.2.3 VDDSYN, VSSSYN                                     |        |

| 8.9.2.4 KAPWR                                              |        |

| 8.9.2.5 VDDA, VSSA                                         |        |

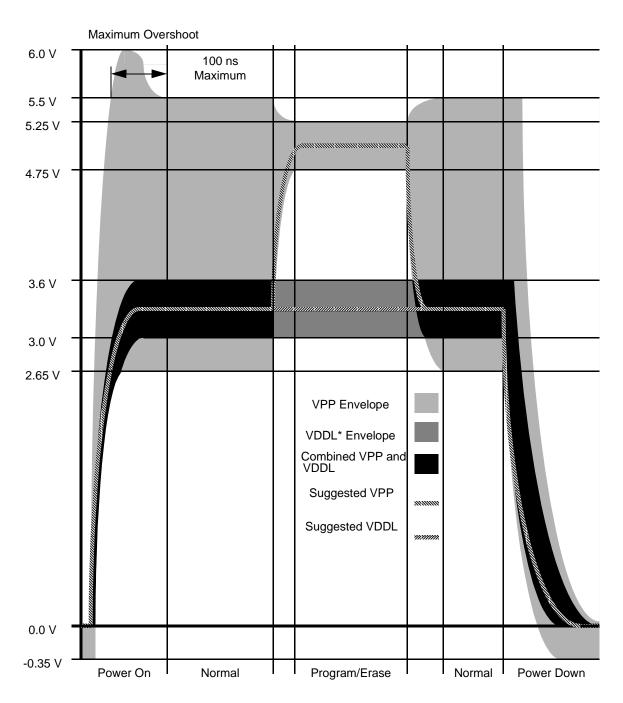

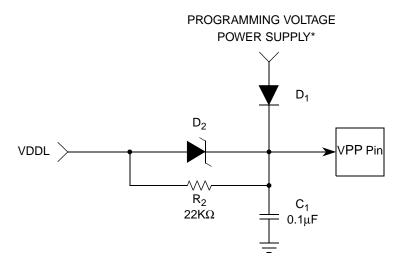

| 8.9.2.6 VPP                                                |        |

| 8.9.2.7 VDDF, VSSF                                         |        |

| 8.9.2.8 VDDH                                               |        |

| 8.9.2.9 VDDSRAM                                            |        |

| 8.9.2.10 VSS                                               |        |

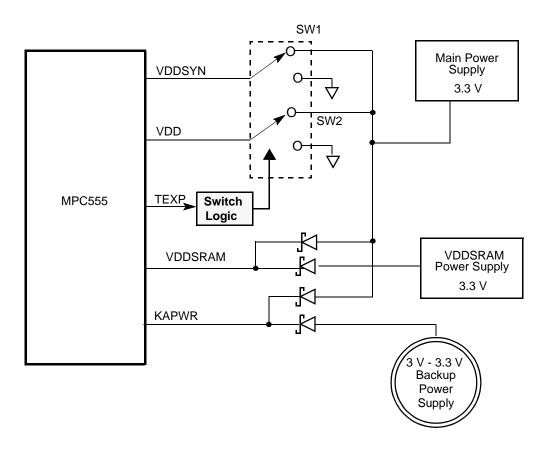

| 8.9.3 Keep Alive Power                                     |        |

| 8.9.3.1 Keep Alive Power Configuration                     | 8-22   |

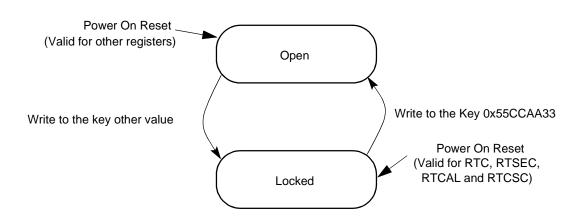

| 8.9.3.2 Keep Alive Power Registers Lock Mechanism          |        |

| 8.10 VDDSRAM Supply Failure Detection                      |        |

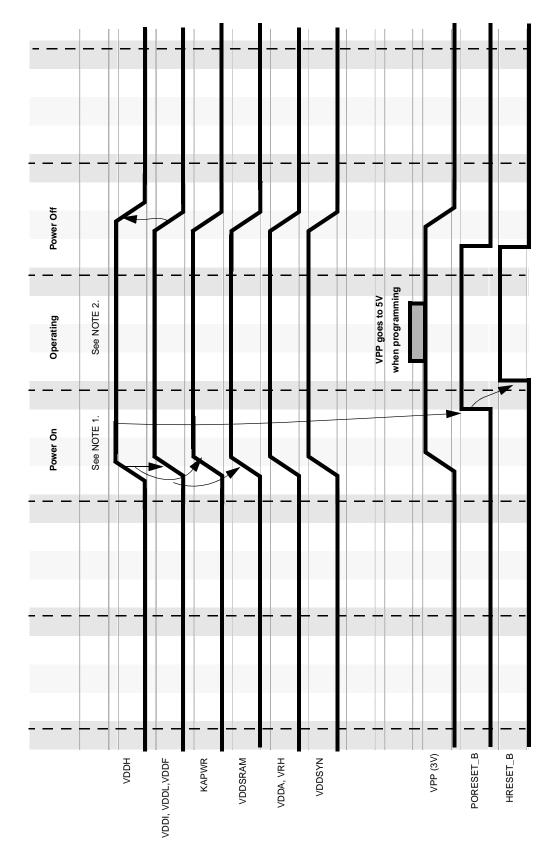

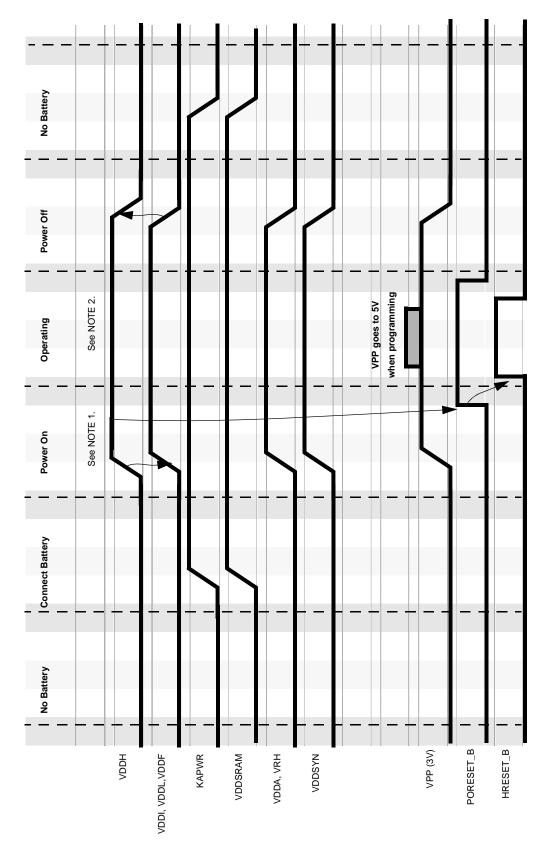

| 8.11 Power Up/Down Sequencing                              |        |

| 8.12 Clocks Unit Programming Model                         |        |

| 8.12.1 System Clock Control Register (SCCR)                |        |

| 8.12.2 PLL, Low-Power, and Reset-Control Register (PLPRCR) | 8-31   |

| 8.12.3 Change of Lock Interrupt Register (COLIR)           | 8-33   |

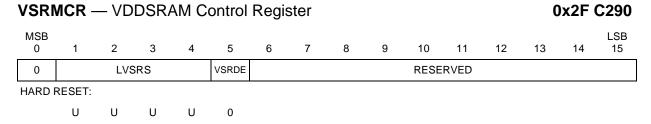

| 8.12.4 VDDSRAM Control Register (VSRMCR)                   | 8-34   |

| Section 9                                                  |        |

| EXTERNAL BUS INTERFACE                                     | •      |

| 9.1 Features                                               | 9-1    |

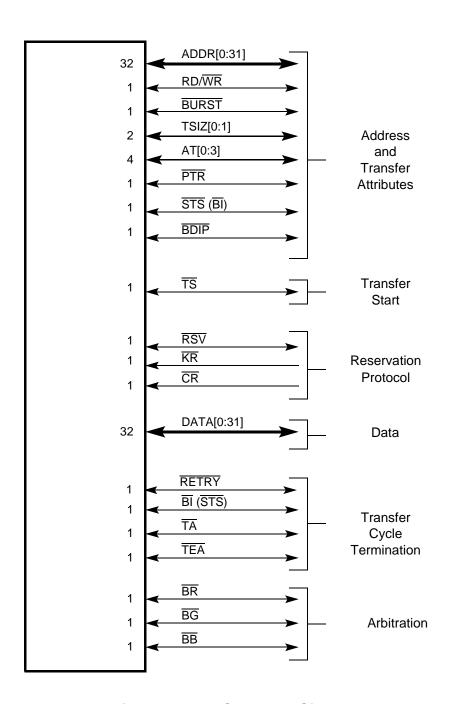

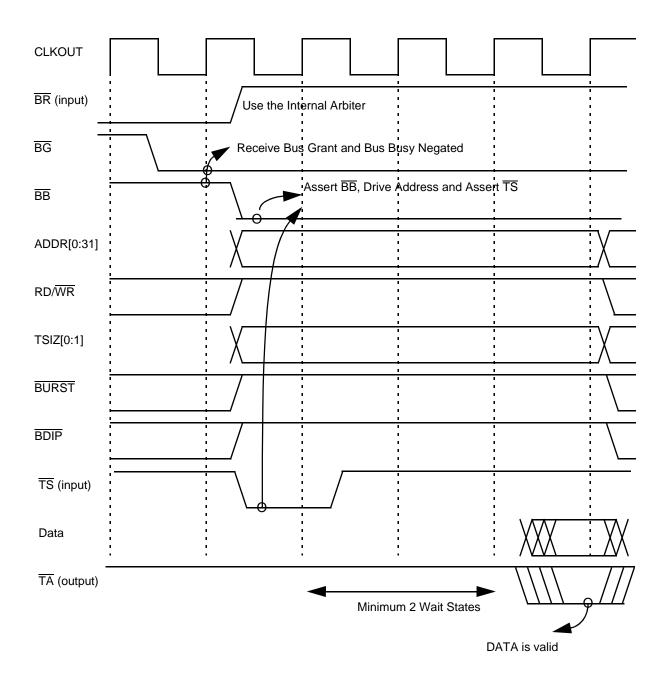

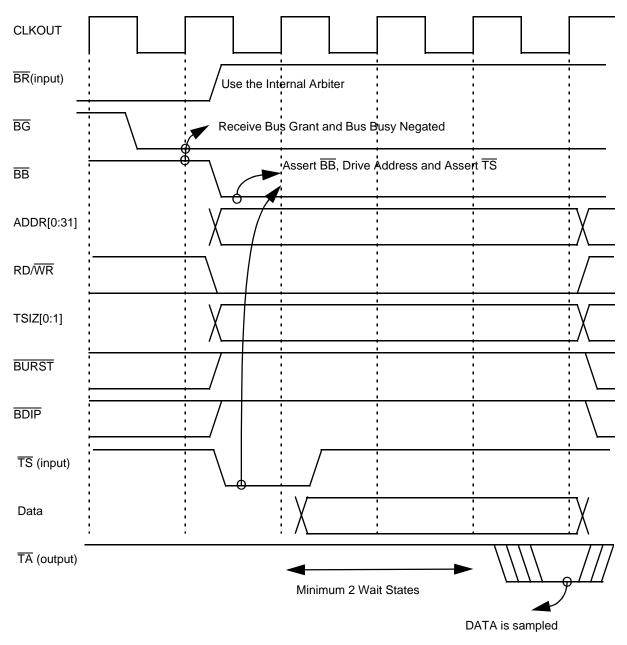

| 9.2 Bus Transfer Signals                                   | 9-1    |

| 9.3 Bus Control Signals                                    | 9-2    |

| 9.4 Bus Interface Signal Descriptions                      |        |

| 9.5 Bus Operations                                         |        |

|   | agrapn                                        | Number |

|---|-----------------------------------------------|--------|

| N | umber                                         | Number |

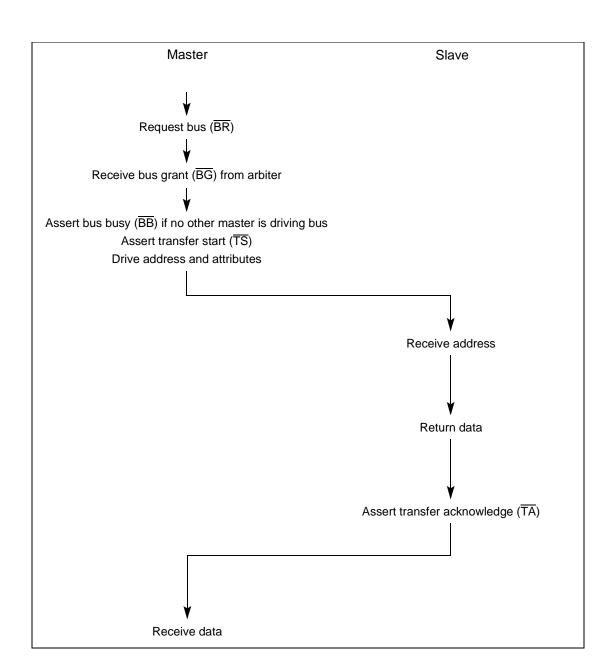

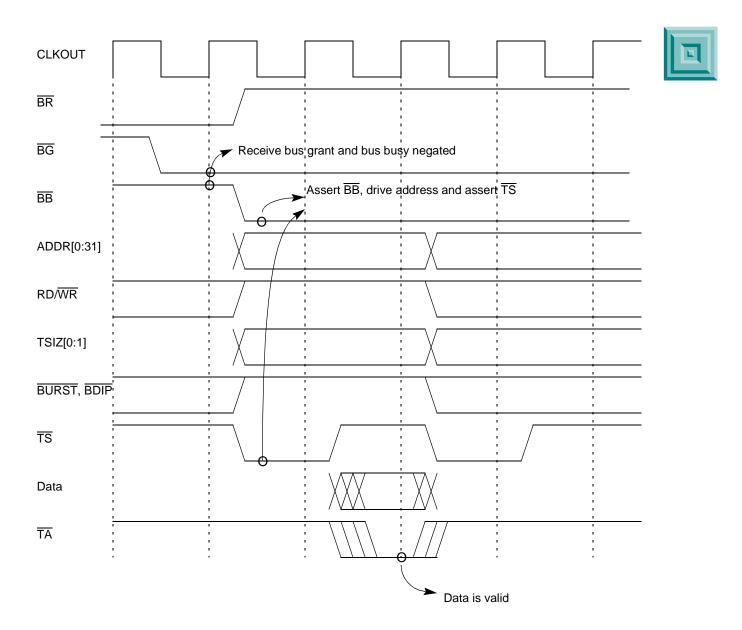

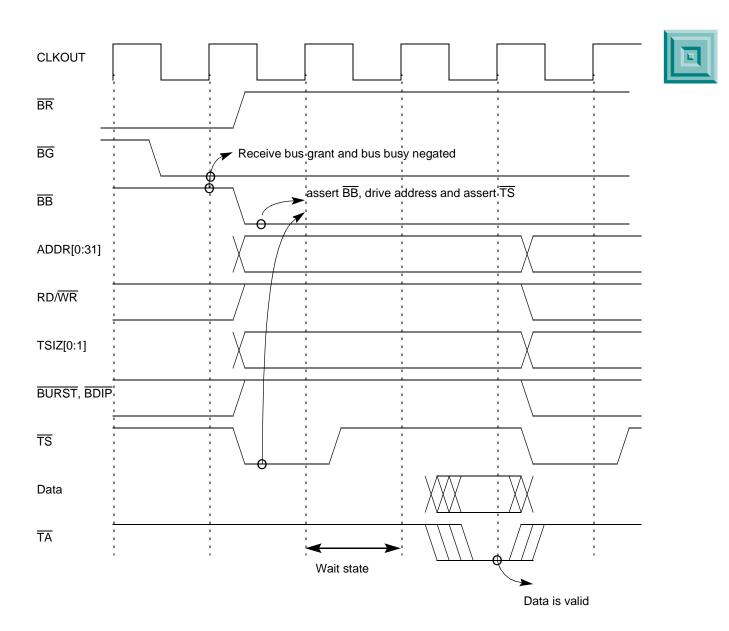

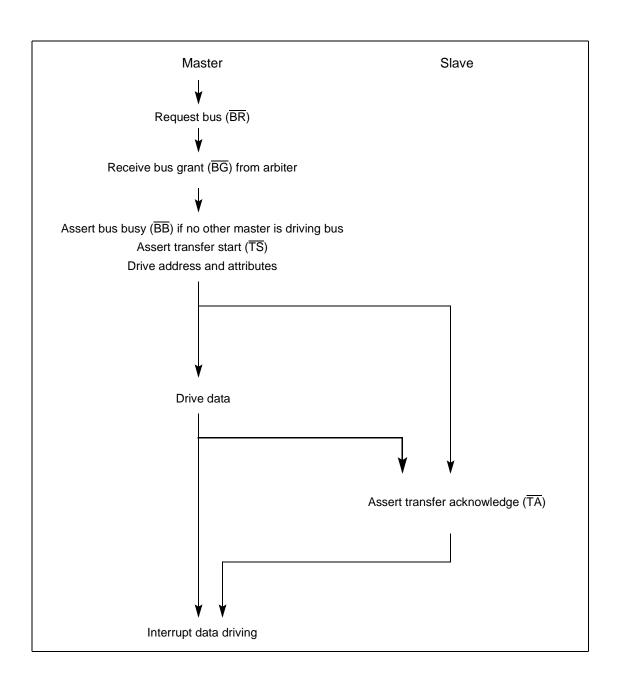

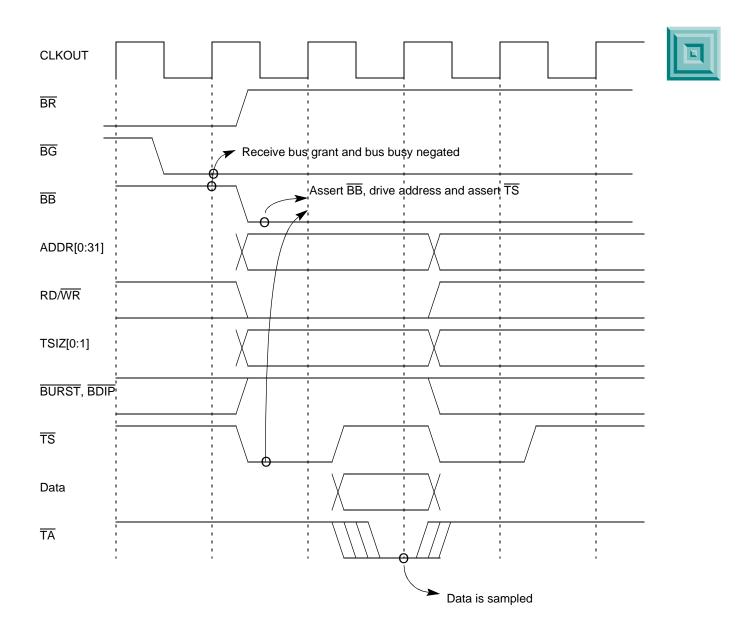

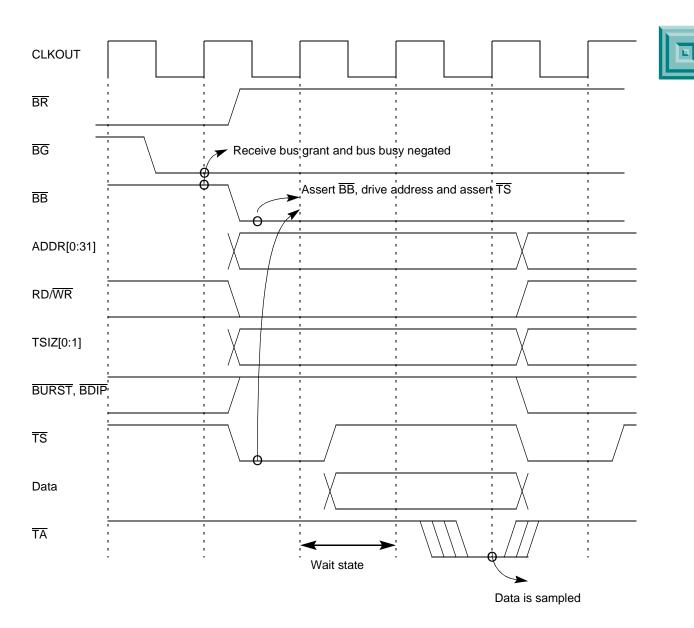

|   | 9.5.1 Basic Transfer Protocol                 |        |

|   | 9.5.2.1 Single Beat Read Flow                 |        |

|   | 9.5.2.2 Single Beat Write Flow                |        |

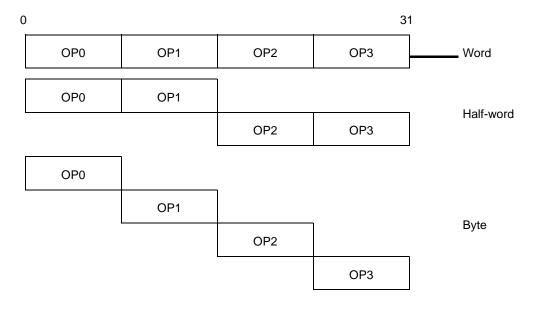

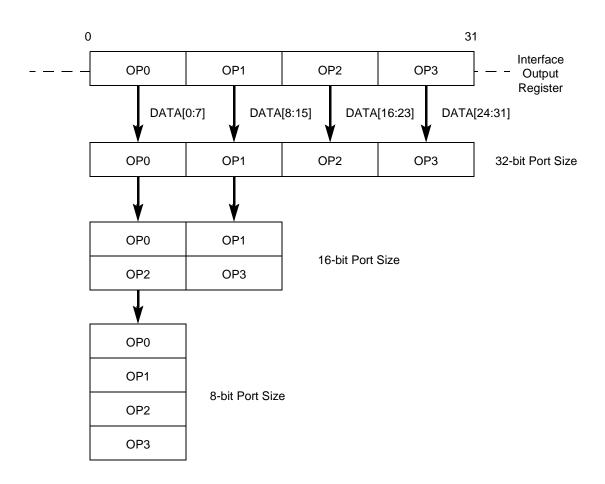

|   | 9.5.2.3 Single Beat Flow with Small Port Size |        |

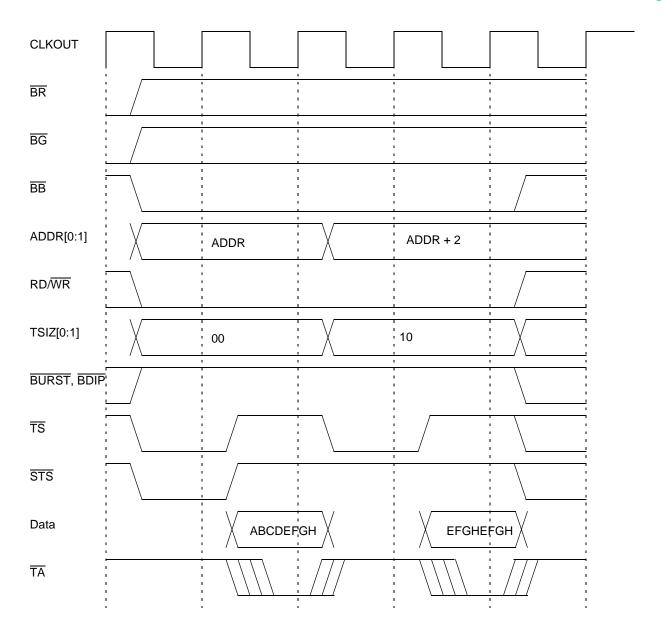

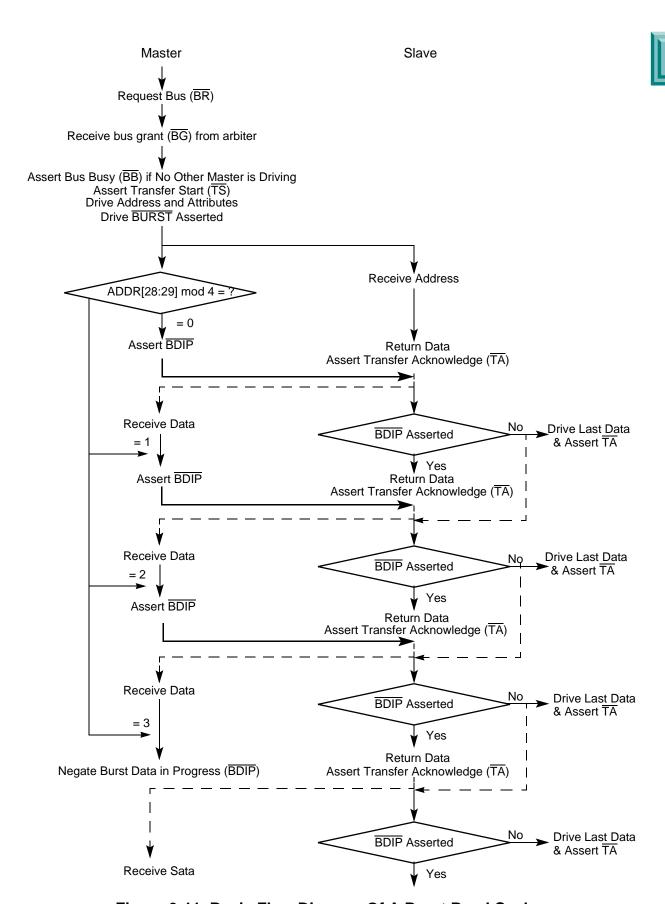

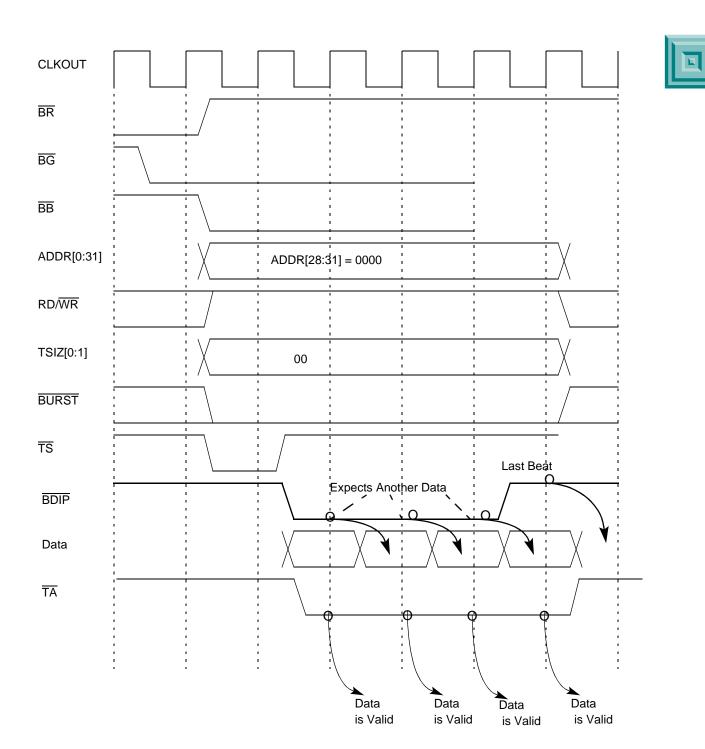

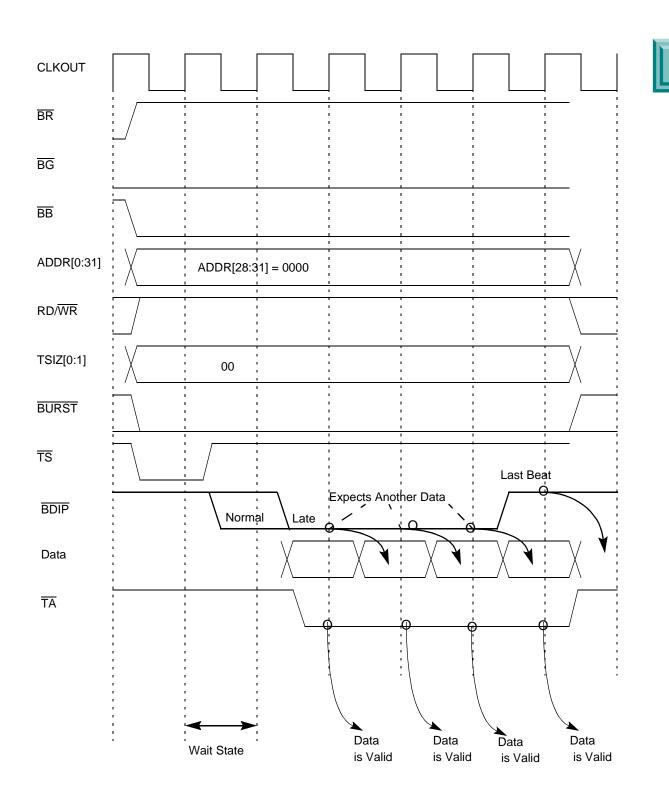

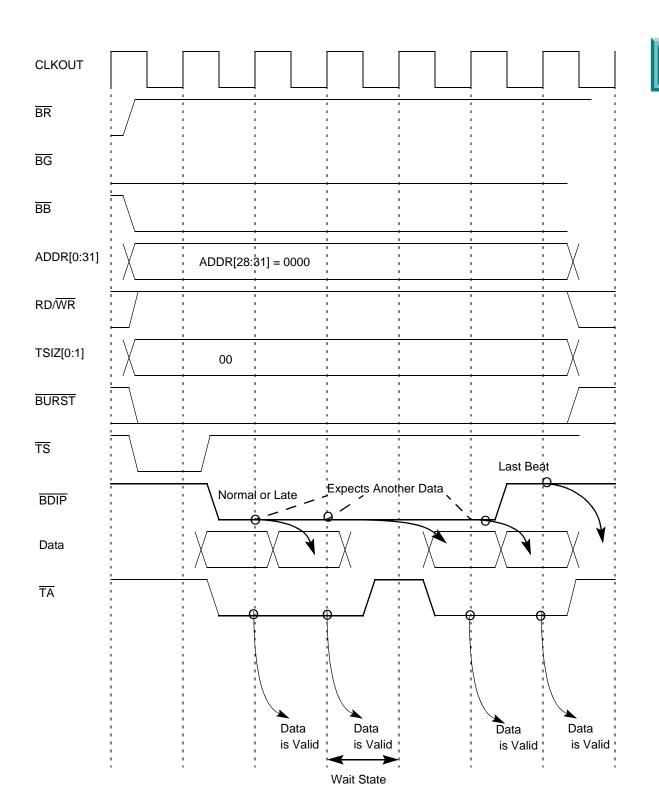

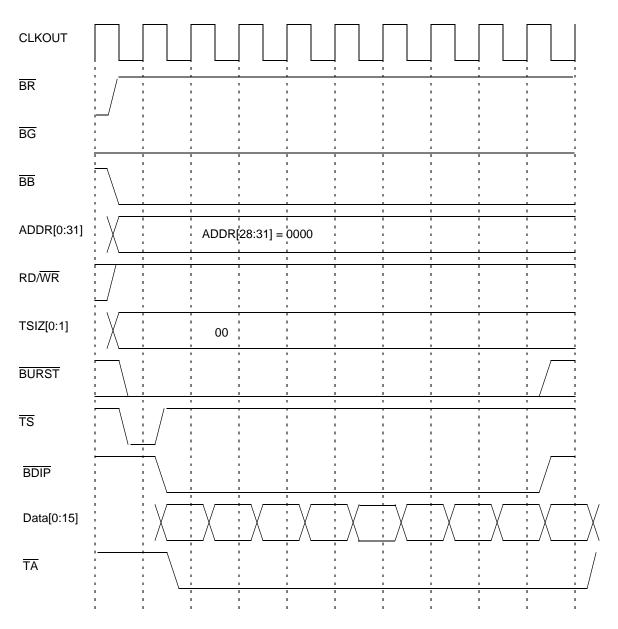

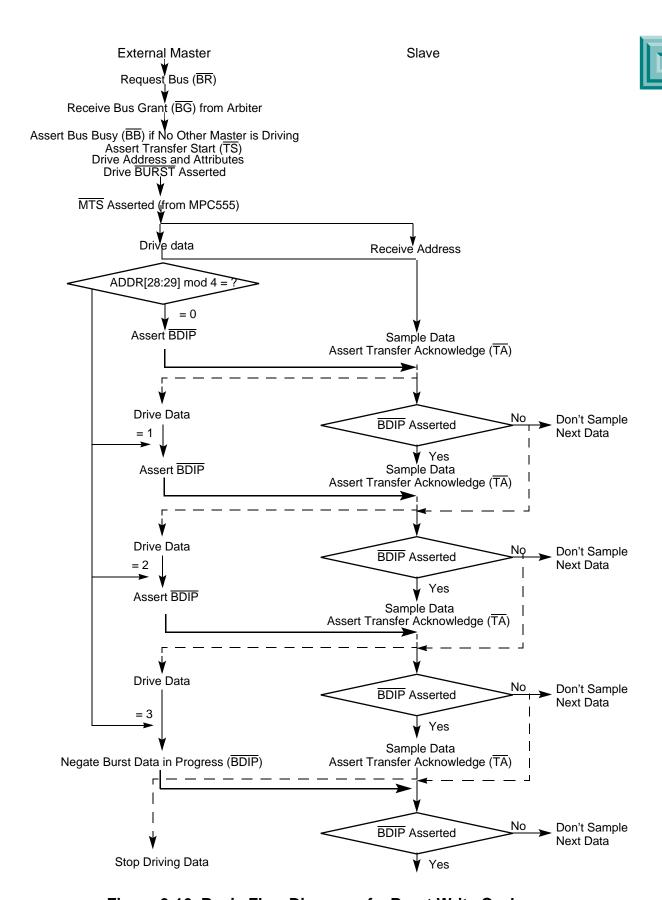

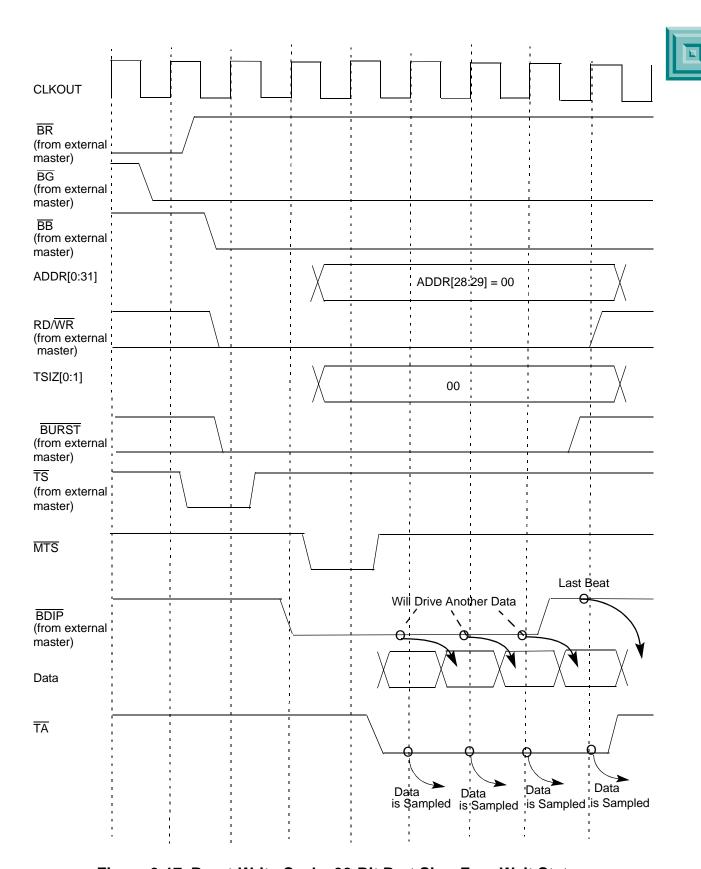

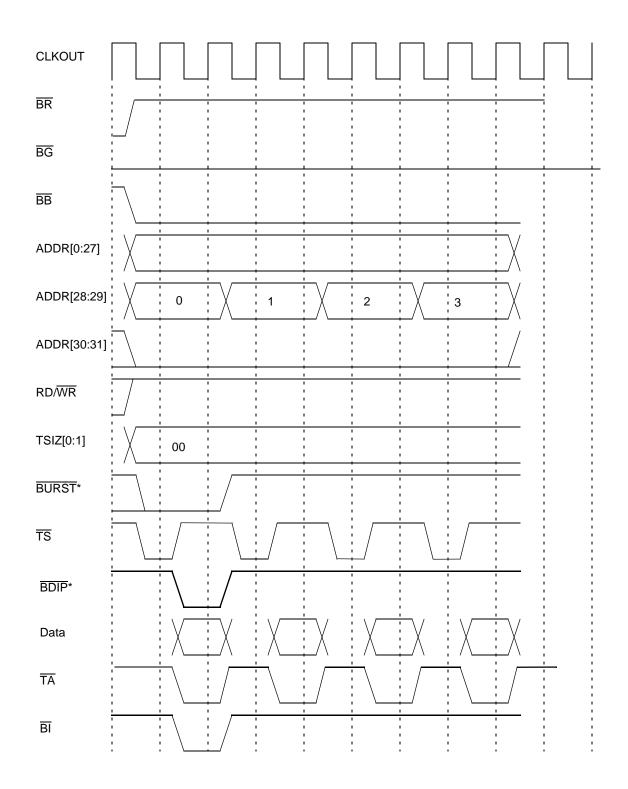

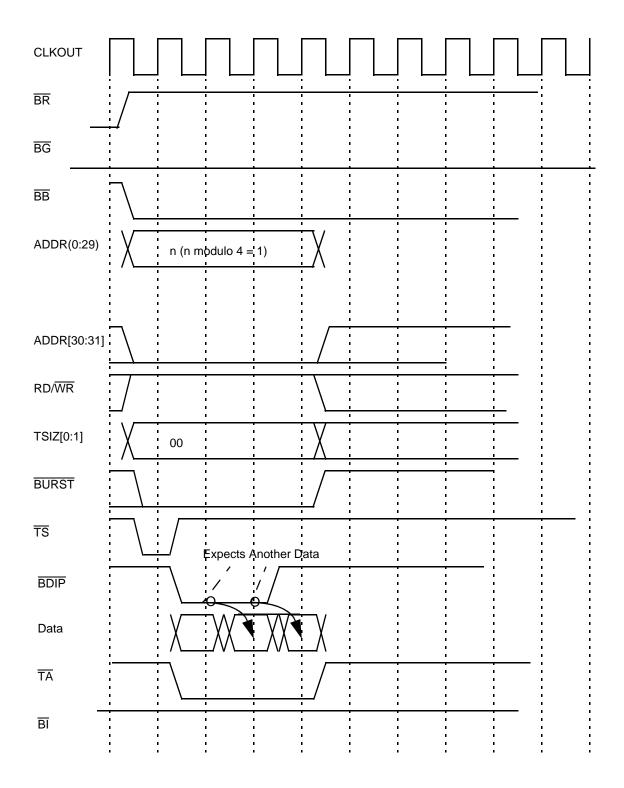

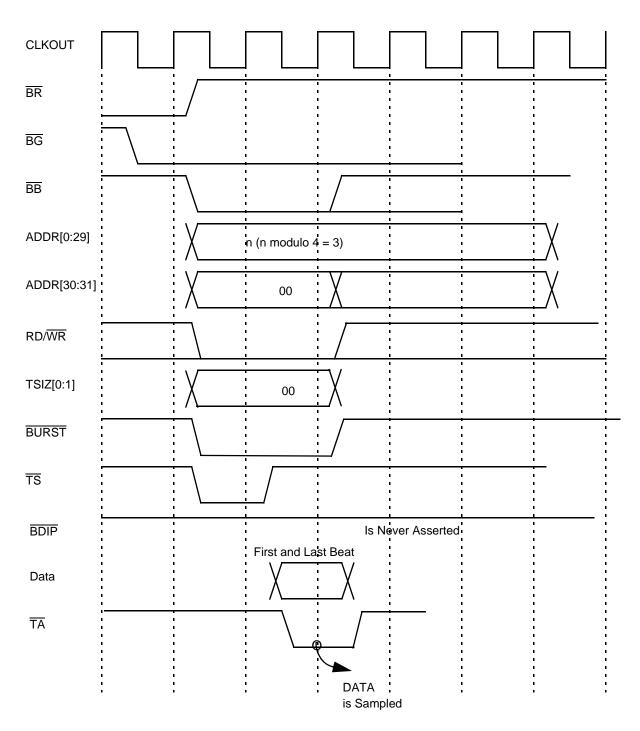

|   | 9.5.3 Burst Transfer                          |        |

|   | 9.5.4 Burst Mechanism                         |        |

|   | 9.5.5 Alignment and Packaging of Transfers    |        |

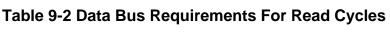

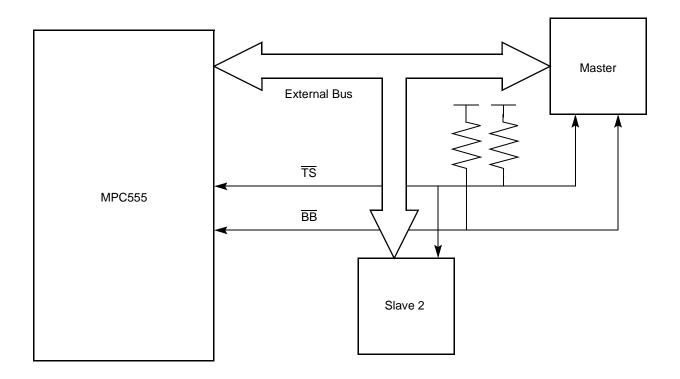

|   | 9.5.6 Arbitration Phase                       |        |

|   | 9.5.6.1 Bus Request                           |        |

|   | 9.5.6.2 Bus Grant                             |        |

|   | 9.5.6.3 Bus Busy                              |        |

|   | 9.5.6.4 Internal Bus Arbiter.                 |        |

|   | 9.5.7 Address Transfer Phase Signals          |        |

|   | 9.5.7.1 Transfer Start                        |        |

|   | 9.5.7.2 Address Bus                           |        |

|   | 9.5.7.3 Read/Write                            |        |

|   | 9.5.7.4 Burst Indicator                       |        |

|   | 9.5.7.5 Transfer Size                         |        |

|   | 9.5.7.6 Address Types                         |        |

|   | 9.5.7.7 Burst Data in Progress                |        |

|   | 9.5.8 Termination Signals                     |        |

|   | 9.5.8.1 Transfer Acknowledge                  |        |

|   | 9.5.8.2 Burst Inhibit.                        |        |

|   | 9.5.8.3 Transfer Error Acknowledge            |        |

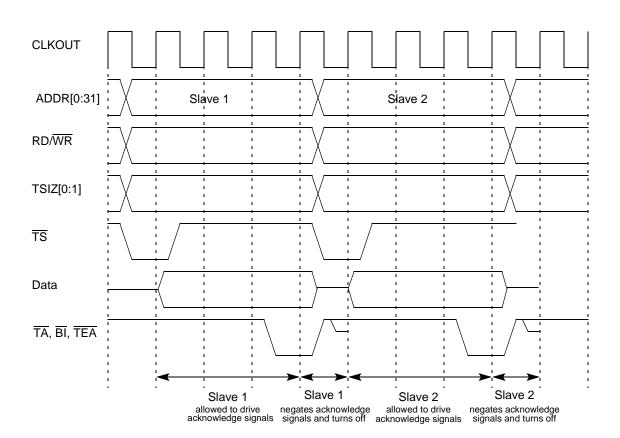

|   | 9.5.8.4 Termination Signals Protocol          |        |

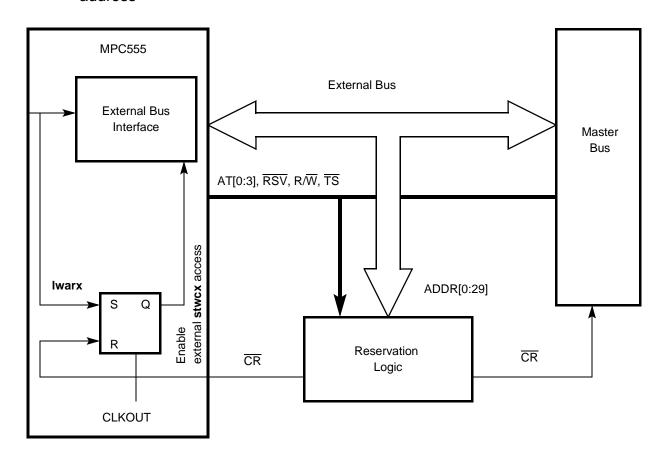

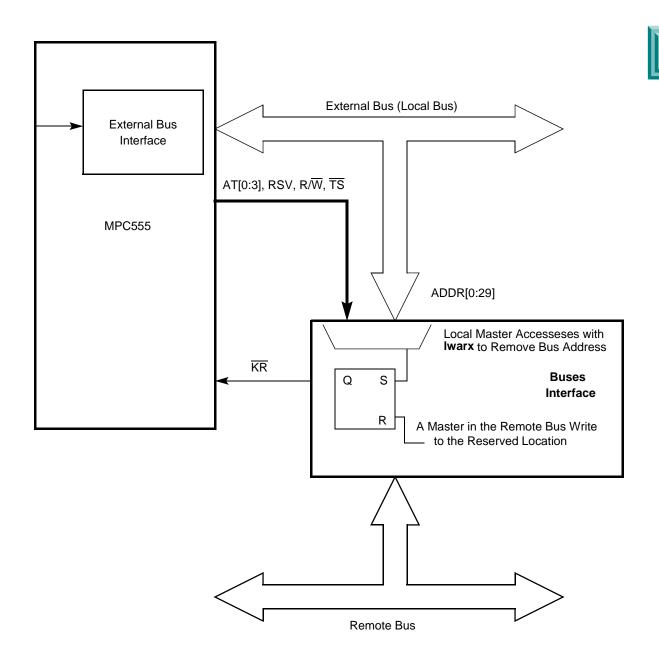

|   | 9.5.9 Storage Reservation                     |        |

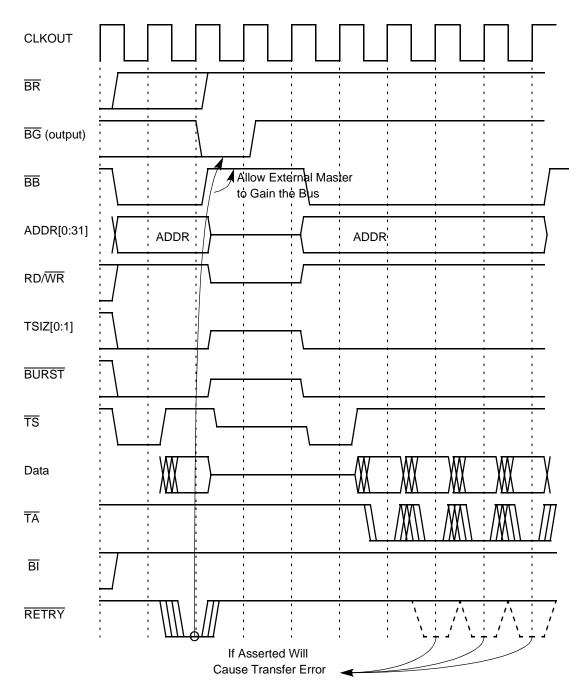

|   | 9.5.10 Bus Exception Control Cycles           |        |

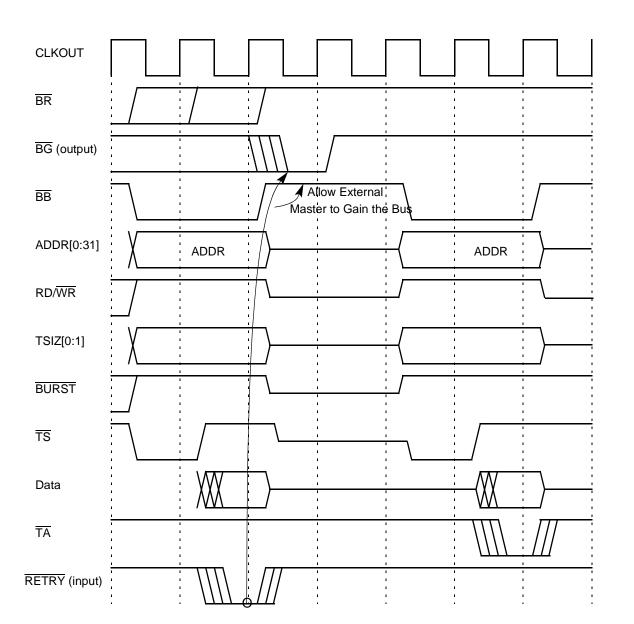

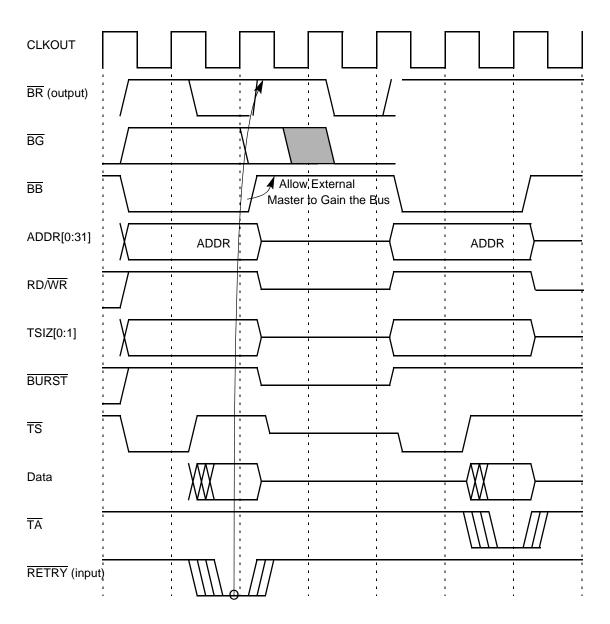

|   | 9.5.10.1 Retrying a Bus Cycle                 |        |

|   | 9.5.10.2 Termination Signals Protocol Summary |        |

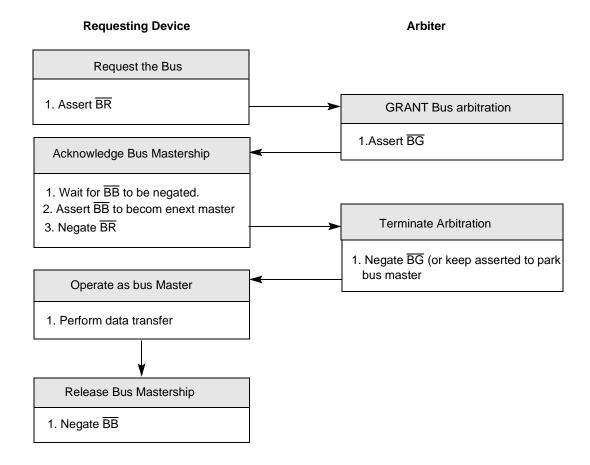

|   | 9.5.11 Bus Operation in External Master Modes |        |

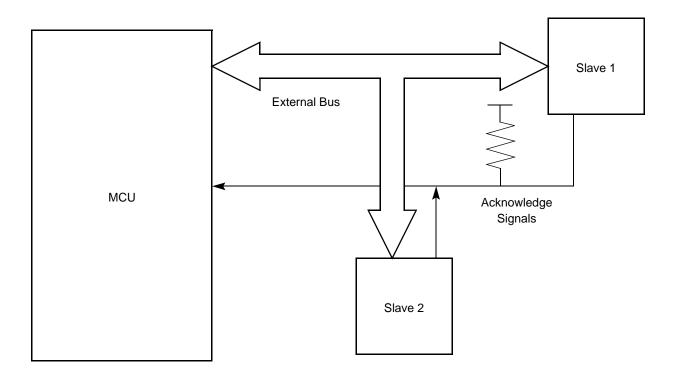

|   | 9.5.12 Contention Resolution on External Bus  |        |

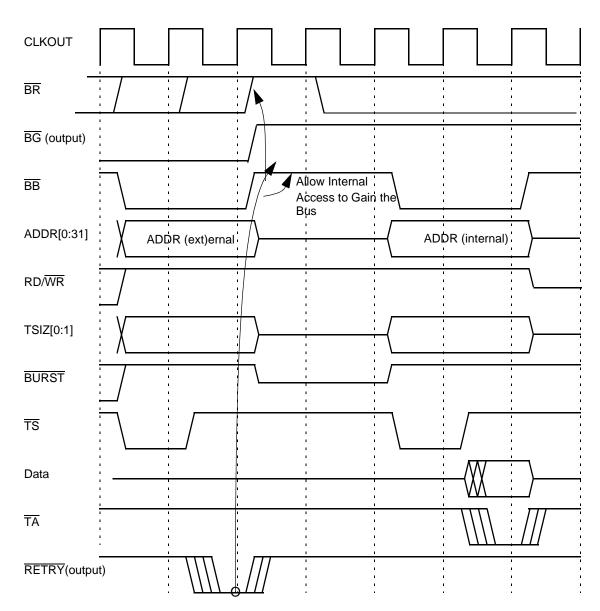

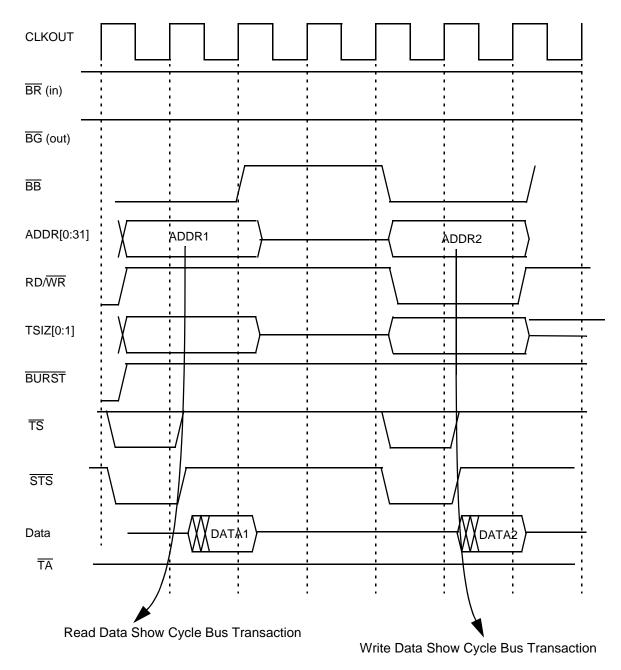

|   | 9.5.13 Show Cycle Transactions                | 9-54   |

|   | Section 10                                    |        |

|   | MEMORY CONTROLLER                             |        |

|   | 10.1 Overview                                 | 10-1   |

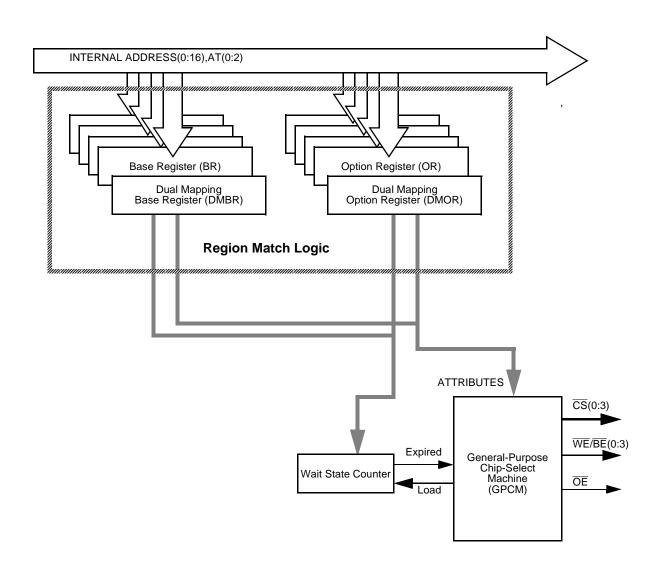

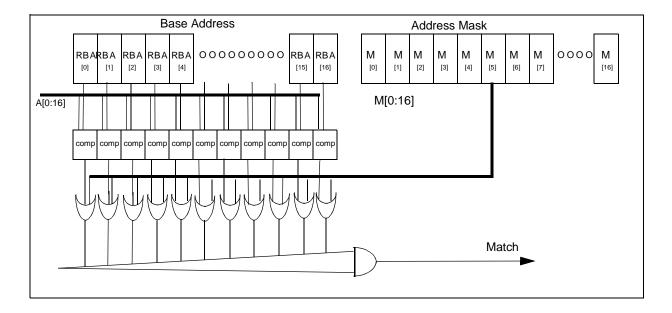

|   | 10.2 Memory Controller Architecture           | 10-3   |

|   | 10.2.1 Associated Registers                   | 10-4   |

|   | 10.2.2 Port Size Configuration                | 10-5   |

|   | 10.2.3 Write-Protect Configuration            |        |

|   | 10.2.4 Address and Address Space Checking     | 10-5   |

|   | 10.2.5. Ruret Support                         | 10-5   |

| aragrapn                                              | Page   |

|-------------------------------------------------------|--------|

| Number                                                | Number |

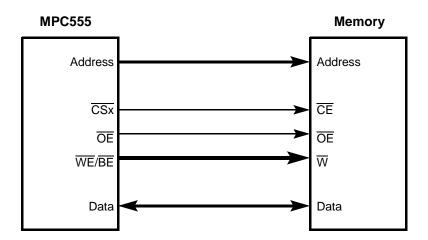

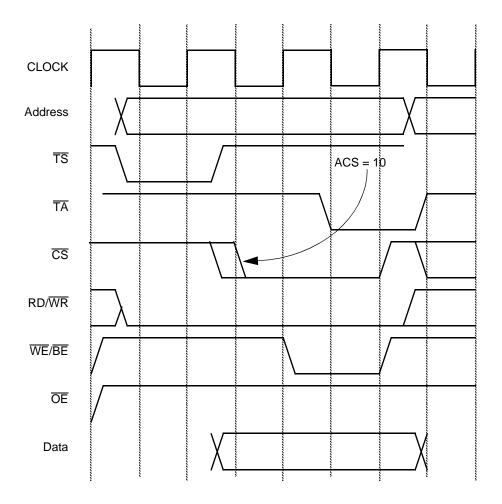

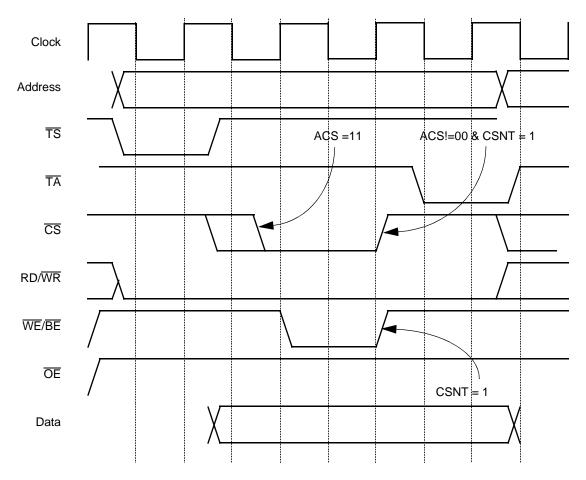

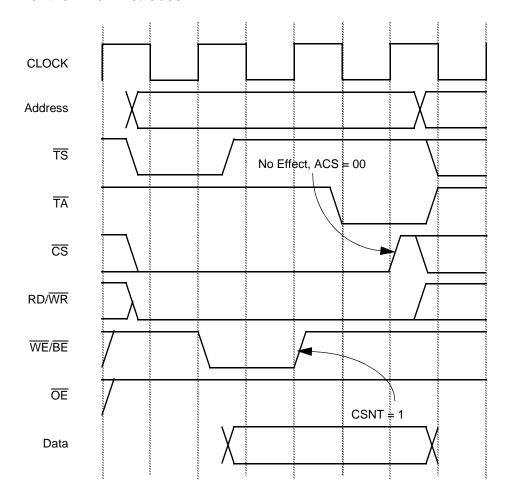

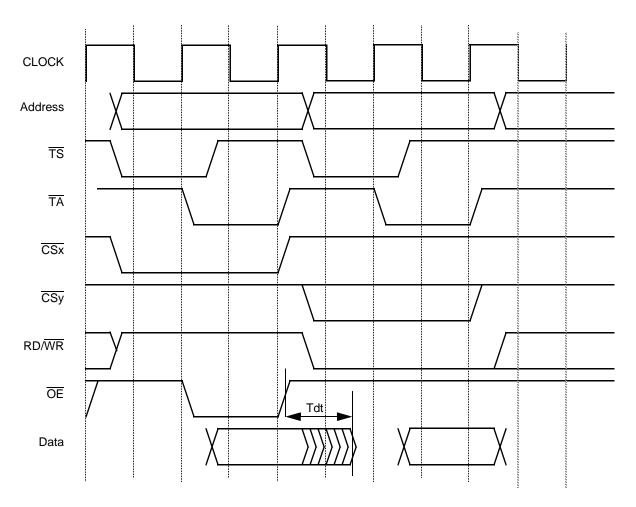

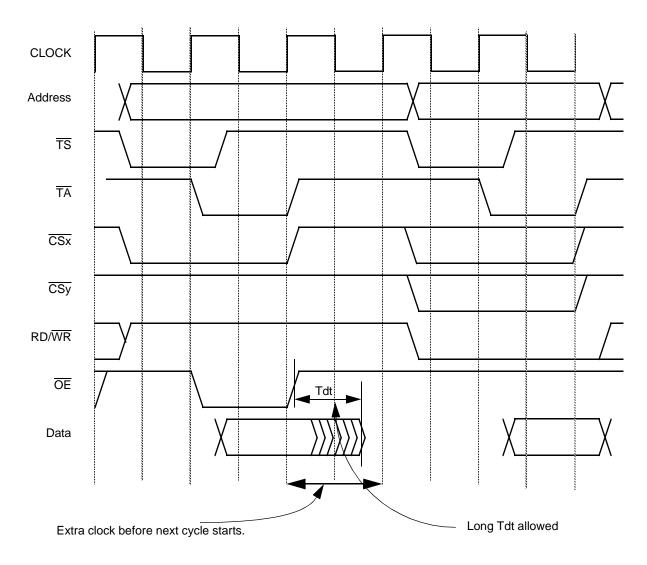

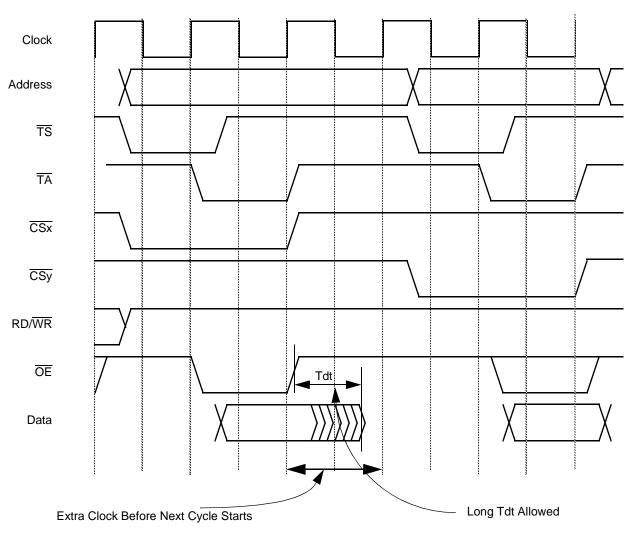

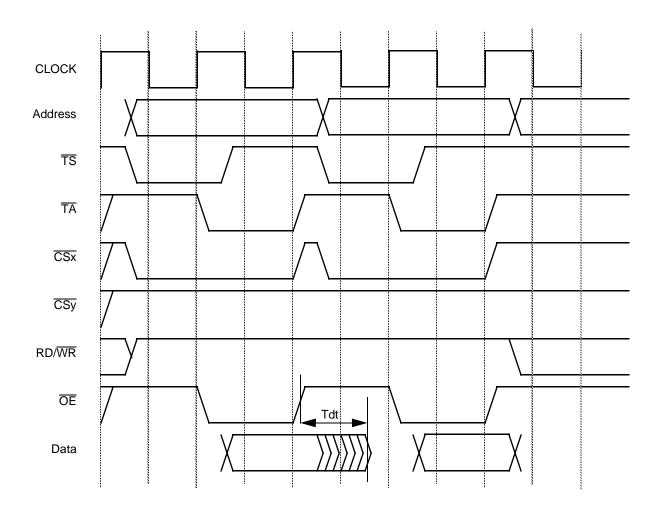

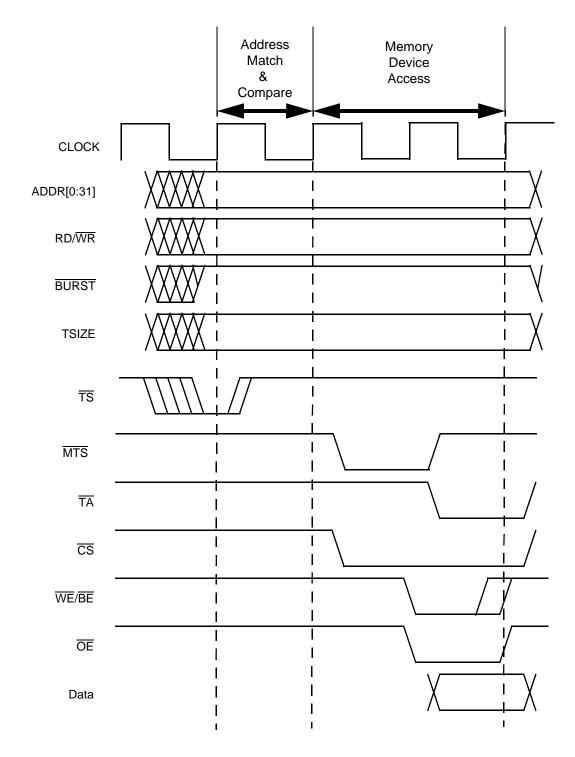

| 10.3 Chip-Select Timing.                              |        |

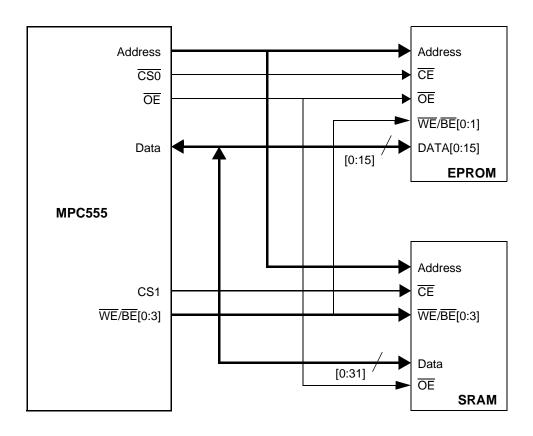

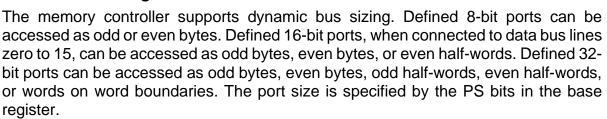

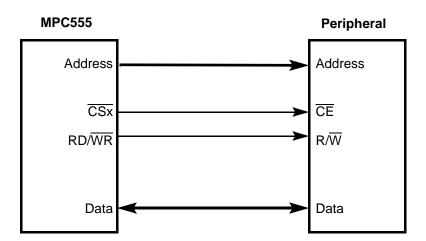

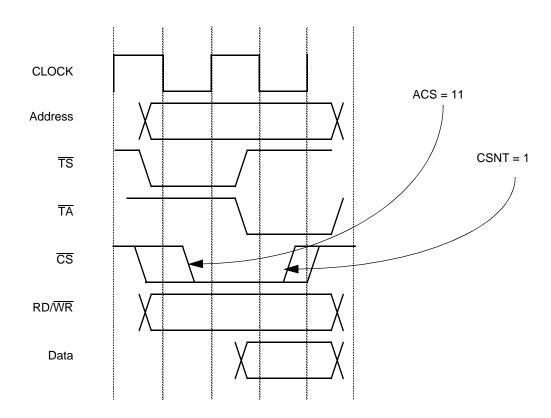

| 10.3.1 Memory Devices Interface Example               |        |

| 10.3.2 Peripheral Devices Interface Example           |        |

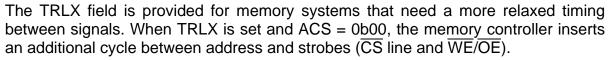

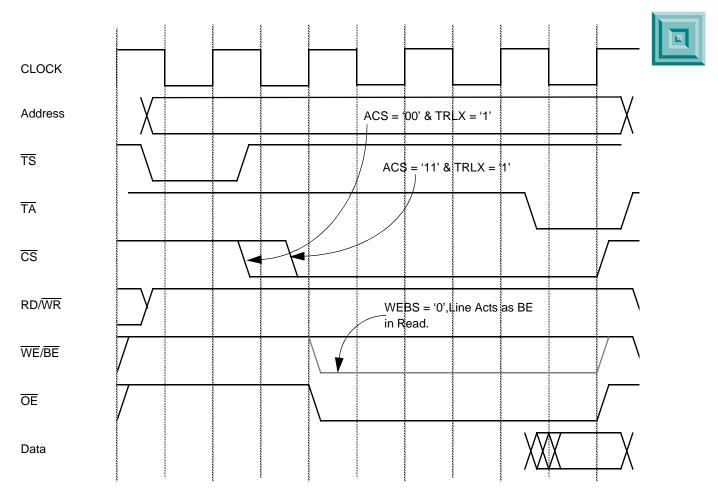

| 10.3.3 Relaxed Timing Examples                        |        |

| 10.3.4 Extended Hold Time on Read Accesses            |        |

| 10.3.5 Summary of GPCM Timing Options                 |        |

| 10.4 Global (Boot) Chip-Select Operation              |        |

| 10.5 Write and Byte Enable Signals                    |        |

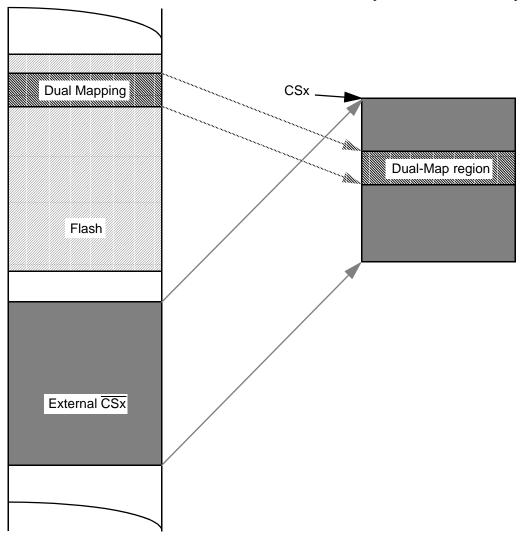

| 10.6 Dual Mapping of the Internal Flash EEPROM Array  |        |

| 10.7 Memory Controller External Master Support        |        |

| 10.8 Programming Model                                |        |

| 10.8.1 General Memory Controller Programming Notes    |        |

| 10.8.2 Memory Controller Status Registers (MSTAT)     |        |

| 10.8.3 Memory Controller Base Registers (BR0 – BR3)   |        |

| 10.8.4 Memory Controller Option Registers (OR0 – OR3) |        |

| 10.8.5 Dual Mapping Base Register (DMBR)              |        |

| 10.8.6 Dual-Mapping Option Register                   | 10-33  |

| Section 11                                            |        |

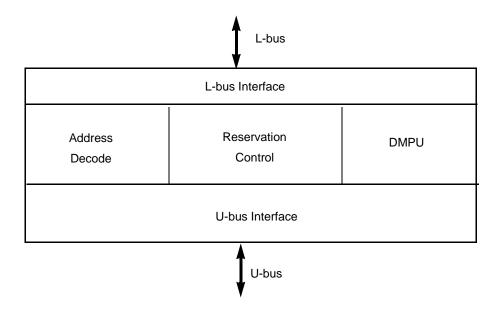

| L-BUS TO U-BUS INTERFACE (L                           | .2U)   |

| 11.1 General Features                                 |        |

| 11.2 DMPU Features                                    |        |

| 11.3 L2U Block Diagram                                |        |

| 11.4 Modes Of Operation                               |        |

| 11.4.1 Normal Mode                                    |        |

| 11.4.2 Reset Operation                                |        |

| 11.4.3 Factory Test Mode                              |        |

| 11.4.4 Peripheral Mode                                |        |

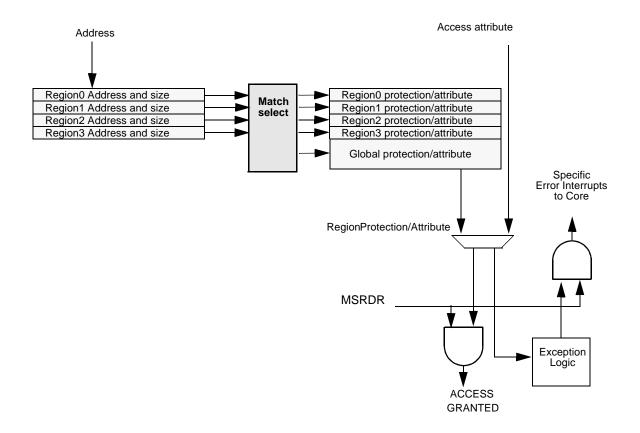

| 11.5 Data Memory Protection                           |        |

| 11.5.1 Functional Description                         |        |

| 11.5.2 Associated Registers                           |        |

| 11.5.3 L-bus Memory Access Violations                 |        |

| 11.6 Reservation Support                              |        |

| 11.6.1 The Reservation Protocol                       |        |

| 11.6.2 L2U Reservation Support                        |        |

| 11.6.3 Reserved Location (Bus) and Possible Actions   |        |

| 11.7 L-Bus Show Cycle Support                         |        |

| 11.7.1 Programming Show Cycles                        |        |

| 11.7.2 Performance Impact                             |        |

| 11.7.3 Show Cycle Protocol                            |        |

| 11.7.4 L-Bus Write Show Cycle Flow                    |        |

| 11.7.5 L-Bus Read Show Cycle Flow                     |        |

| 11.7.6. Show Cycle Support Guidelines                 |        |

| Paragraph                                         | Page                       |

|---------------------------------------------------|----------------------------|

| Number                                            | Number                     |

| 11.8 L2U Programming Model                        |                            |

| 11.8.1 U-bus Access                               |                            |

| 11.8.2 Transaction Size                           |                            |

| 11.8.3 L2U Module Configuration Register (L2U_MC  | CR)                        |

| 11.8.4 Region Base Address Registers (L2U_RBAx)   |                            |

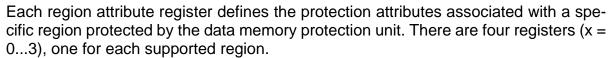

| 11.8.5 Region Attribute Registers (L2U_RAx)       |                            |

| 11.8.6 Global Region Attribute Register           |                            |

| Section                                           | 12                         |

| U-BUS TO IMB3 BUS IN                              |                            |

| 12.1 Features                                     | 12-1                       |

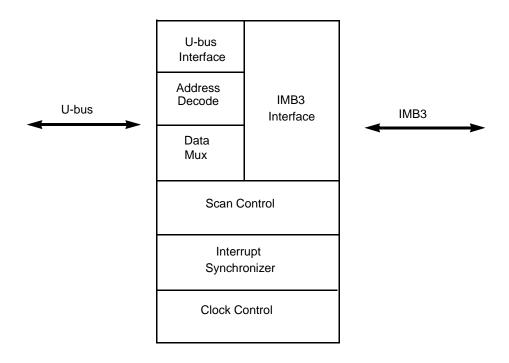

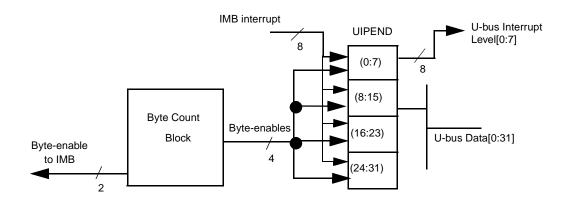

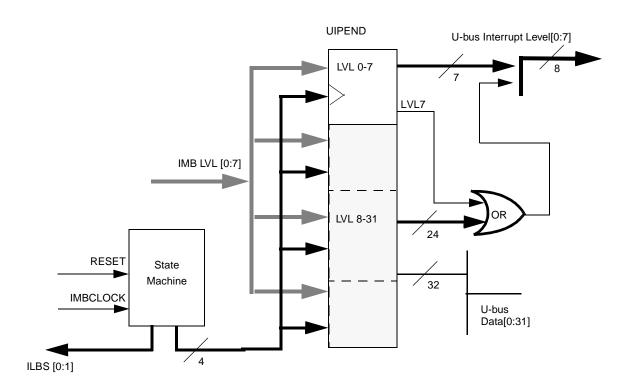

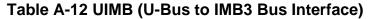

| 12.2 UIMB Block Diagram                           |                            |

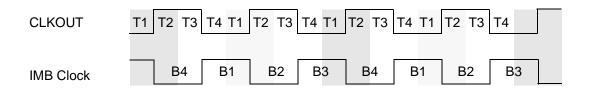

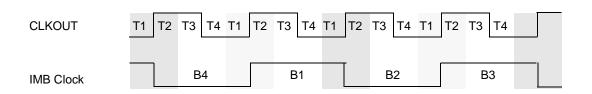

| 12.3 Clock Module                                 |                            |

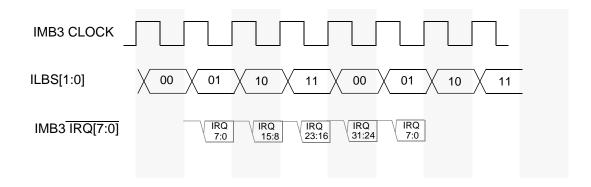

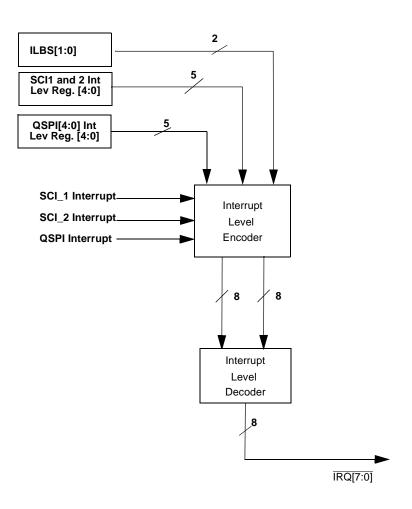

| 12.4 Interrupt Operation                          |                            |

| 12.4.1 Interrupt Sources and Levels on IMB        |                            |

| 12.4.2 IMB Interrupt Multiplexing                 |                            |

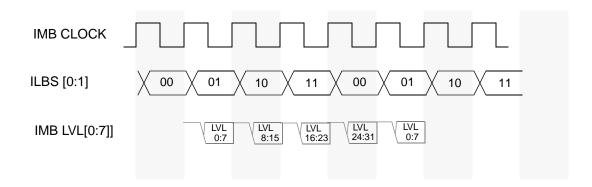

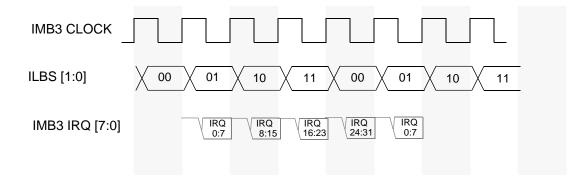

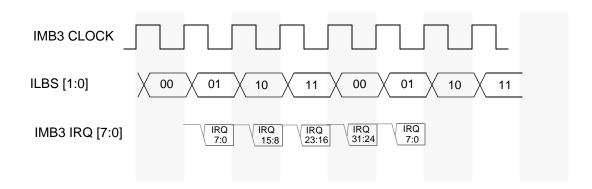

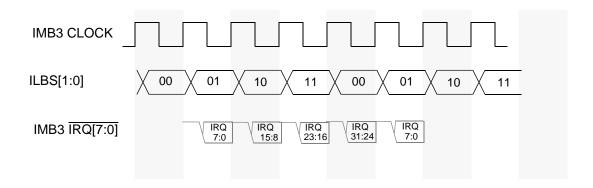

| 12.4.3 ILBS Sequencing                            |                            |

| 12.4.4 Interrupt Synchronizer                     |                            |

| 12.5 Programming Model                            |                            |

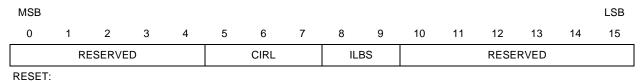

| 12.5.1 UIMB Module Configuration Register (UMCR   | )                          |

| 12.5.2 Test control register (UTSTCREG)           |                            |

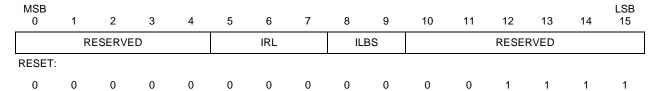

| 12.5.3 Pending Interrupt Request Register (UIPEND | )                          |

| Section                                           | 13                         |

| QUEUED ANALOG-TO-DIGITAL                          | <b>CONVERTER MODULE-64</b> |

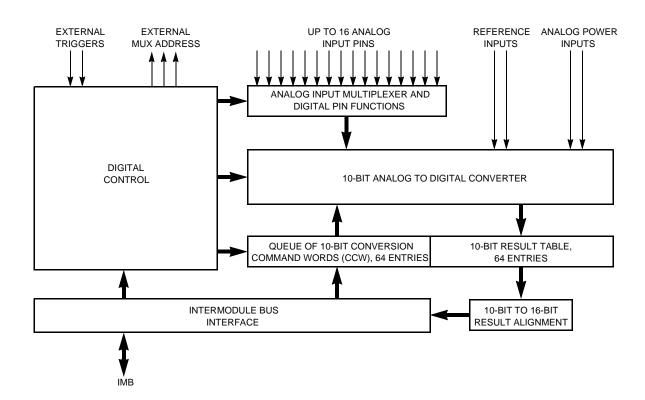

| 13.1 Overview                                     |                            |

| 13.2 Features                                     |                            |

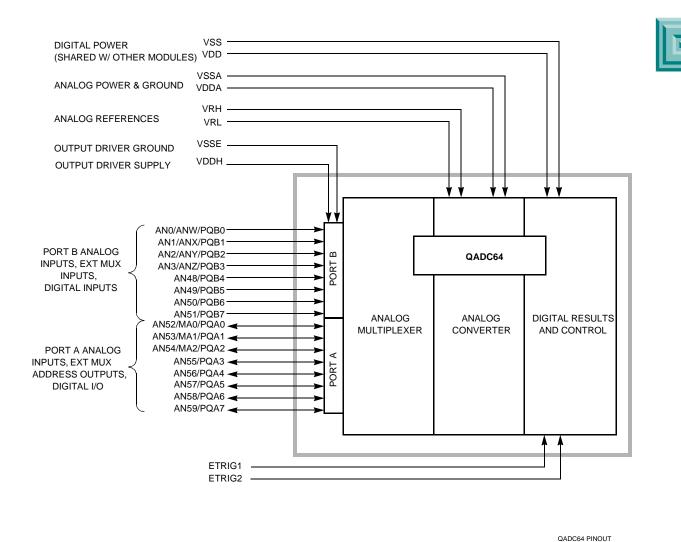

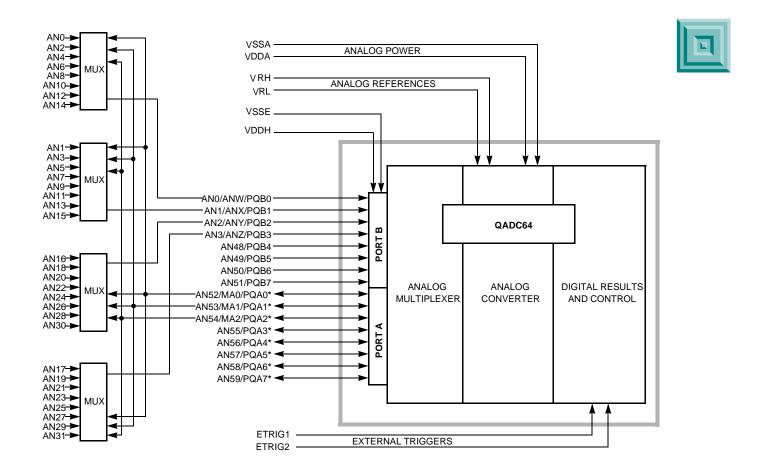

| 13.3 QADC64 Pin Functions                         |                            |

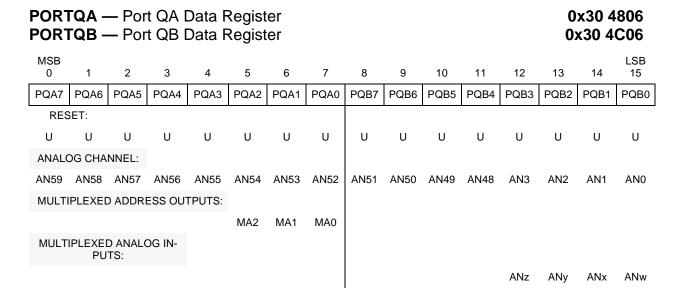

| 13.3.1 Port A Pin Functions                       |                            |

| 13.3.1.1 Port A Analog Input Pins                 |                            |

| 13.3.1.2 Port A Digital Input/Output Pins         |                            |

| 13.3.2 Port B Pin Functions                       |                            |

| 13.3.2.1 Port B Analog Input Pins                 |                            |

| 13.3.2.2 Port B Digital Input Pins                |                            |

| 13.3.3 External Trigger Input Pins                |                            |

| 13.3.4 Multiplexed Address Output Pins            |                            |

| 13.3.5 Multiplexed Analog Input Pins              |                            |

| 13.3.6 Voltage Reference Pins                     |                            |

| 13.3.7 Dedicated Analog Supply Pins               |                            |

| 13.3.8 External Digital Supply Pin                |                            |

| 13.3.9 Digital Supply Pins                        |                            |

| 13.4 QADC64 Bus Interface                         |                            |

| 13.5 Module Configuration                         |                            |

| 13.5.1 Low-Power Stop Mode                        |                            |

| Paragraph                                        | Page   |

|--------------------------------------------------|--------|

| Number                                           | Number |

| 13.5.2 Freeze Mode                               |        |

| 13.5.3 Supervisor/Unrestricted Address Space     | 13-7   |

| 13.6 General-Purpose I/O Port Operation          | 13-7   |

| 13.6.1 Port Data Register                        | 13-8   |

| 13.6.2 Port Data Direction Register              | 13-8   |

| 13.7 External Multiplexing Operation             | 13-9   |

| 13.8 Analog Input Channels                       | 13-10  |

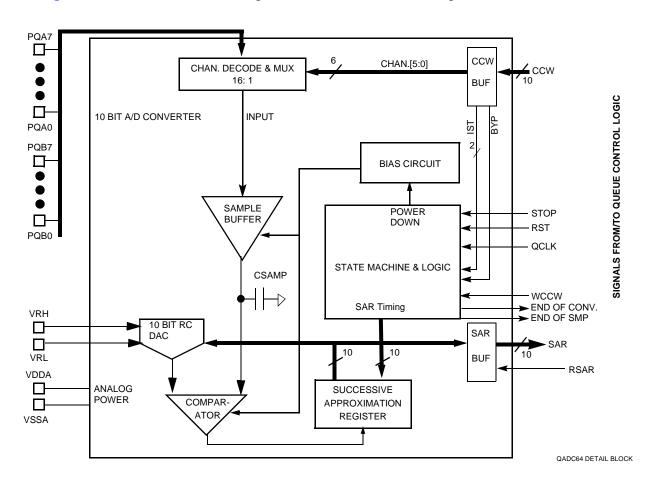

| 13.9 Analog Subsystem                            | 13-11  |

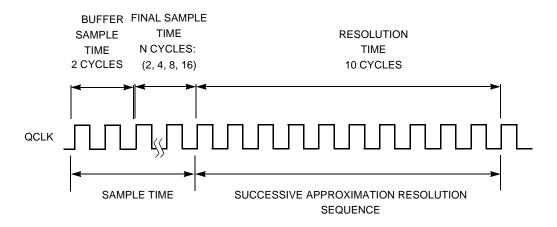

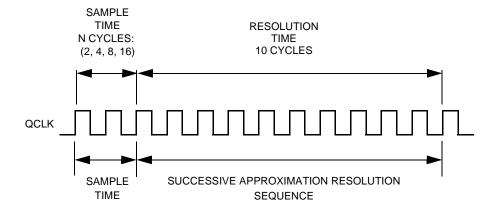

| 13.9.1 Conversion Cycle Times                    | 13-12  |

| 13.9.1.1 Amplifier Bypass Mode Conversion Timing | 13-12  |

| 13.9.2 Front-End Analog Multiplexer              | 13-13  |

| 13.9.3 Digital-to-Analog Converter Array         | 13-13  |

| 13.9.4 Comparator                                | 13-14  |

| 13.9.5 Successive Approximation Register         | 13-14  |

| 13.10 Digital Control Subsystem                  | 13-14  |

| 13.10.1 Queue Priority                           | 13-14  |

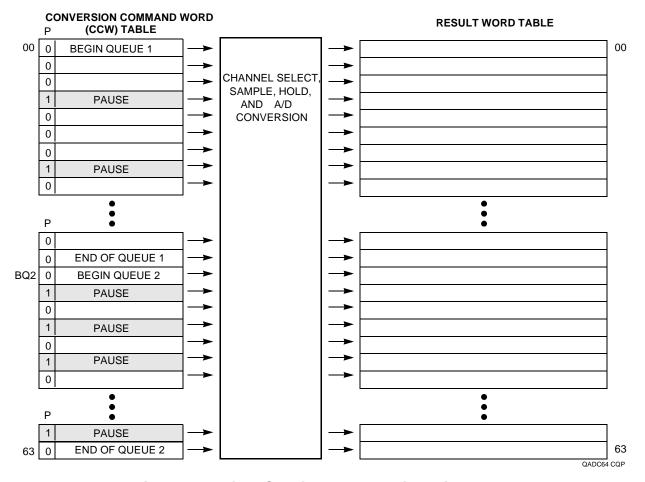

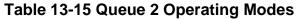

| 13.10.2 Queue Boundary Conditions                |        |

| 13.10.3 Scan Modes                               | 13-17  |

| 13.10.3.1 Disabled Mode                          | 13-18  |

| 13.10.3.2 Reserved Mode                          |        |

| 13.10.3.3 Single-Scan Modes                      | 13-18  |

| 13.10.3.4 Continuous-Scan Modes                  | 13-21  |

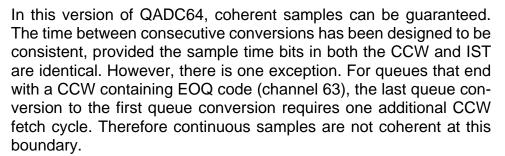

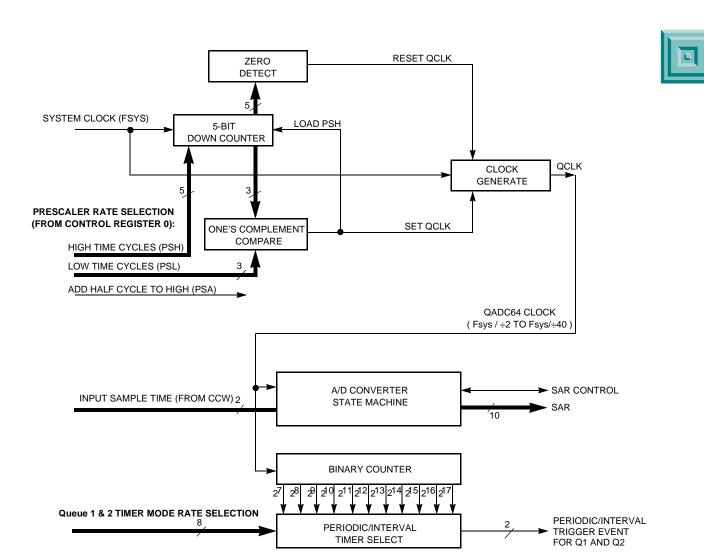

| 13.10.4 QADC64 Clock (QCLK) Generation           | 13-24  |

| 13.10.5 Periodic/Interval Timer                  |        |

| 13.11 Interrupts                                 |        |

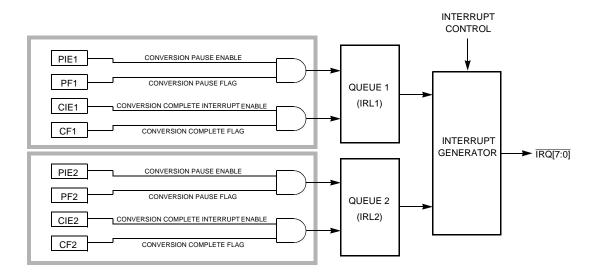

| 13.11.1 Interrupt Sources                        | 13-29  |

| 13.11.2 Interrupt Register                       |        |

| 13.11.3 Interrupt Levels and Time Multiplexing   | 13-30  |

| 13.12 Programming Model                          |        |

| 13.12.1 QADC64 Module Configuration Register     |        |

| 13.12.2 QADC64 Test Register                     |        |

| 13.12.3 QADC64 Interrupt Register                |        |

| 13.12.4 Port A/B Data Register                   |        |

| 13.12.5 Port Data Direction Register             |        |

| 13.12.6 QADC64 Control Register 0 (QACR0)        |        |

| 13.12.7 QADC64 Control Register 1 (QACR1)        |        |

| 13.12.8 QADC64 Control Register 2 (QACR2)        |        |

| 13.12.9 QADC64 Status Register 0 (QASR0)         |        |

| 13.12.10 QADC64 Status Register 1 (QASR1)        |        |

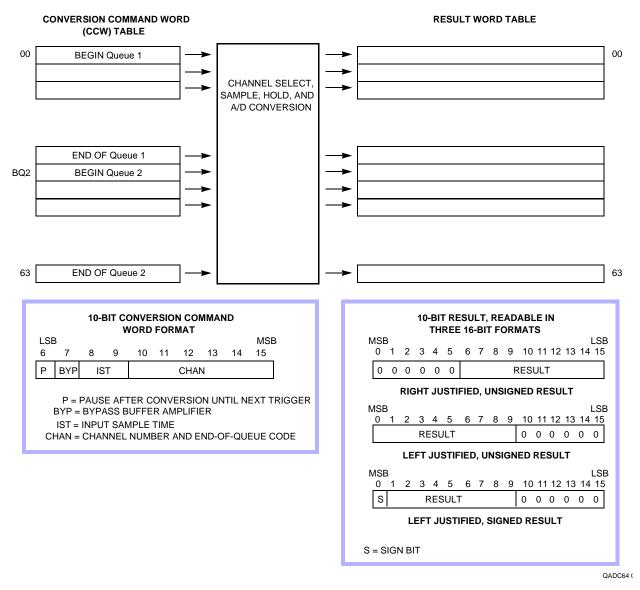

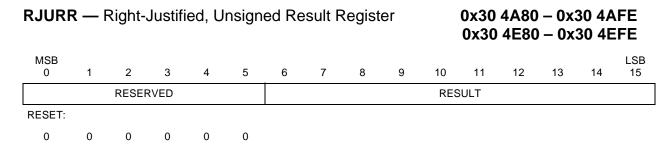

| 13.12.11 Conversion Command Word Table           |        |

| 13.12.12 Result Word Table                       | 13-48  |

xvi

#### Paragraph Number

#### Page Number

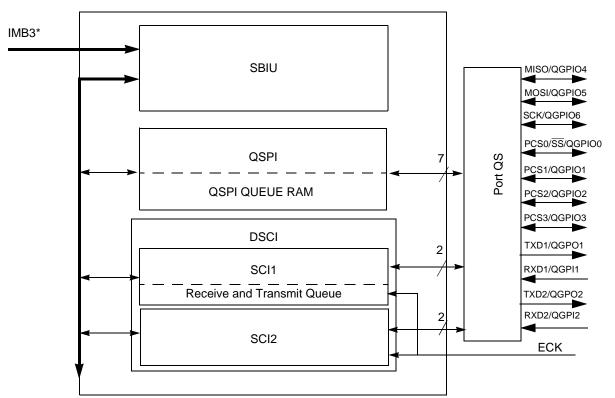

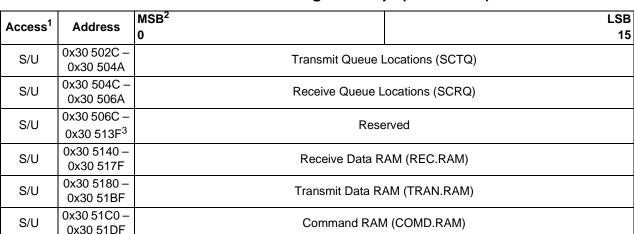

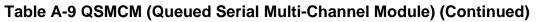

## Section 14 QUEUED SERIAL MULTI-CHANNEL MODULE

| 14.1 Overview                                              | . 14-1 |

|------------------------------------------------------------|--------|

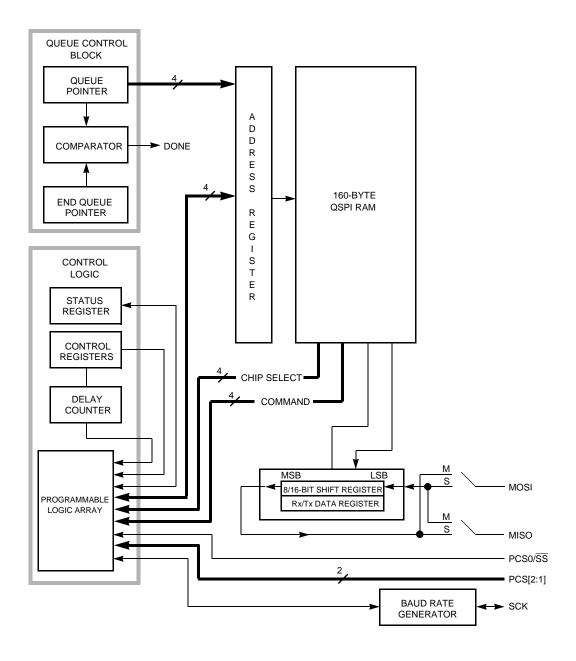

| 14.2 Block Diagram                                         | . 14-1 |

| 14.3 Signal Descriptions                                   | . 14-2 |

| 14.4 Memory Map                                            | . 14-2 |

| 14.5 QSMCM Global Registers                                | . 14-4 |

| 14.5.1 Low-Power Stop Operation                            | . 14-5 |

| 14.5.2 Freeze Operation                                    | . 14-5 |

| 14.5.3 Access Protection                                   | . 14-5 |

| 14.5.4 QSMCM Interrupts                                    | . 14-6 |

| 14.5.5 QSMCM Configuration Register (QSMCMMCR)             | . 14-7 |

| 14.5.6 QSMCM Test Register (QTEST)                         | . 14-8 |

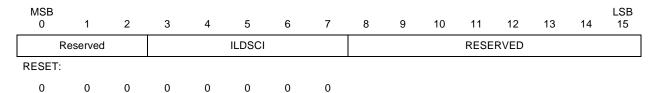

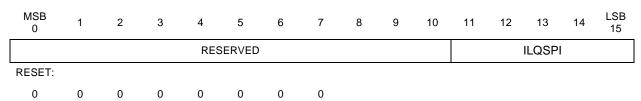

| 14.5.7 QSMCM Interrupt Level Registers (QDSCI_IL, QSPI_IL) | . 14-8 |

| 14.6 QSMCM Pin Control Registers                           | . 14-9 |

| 14.6.1 Port QS Data Register (PORTQS)                      |        |

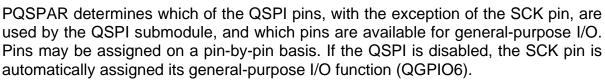

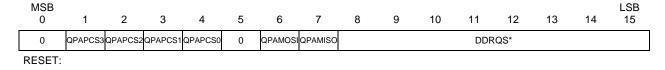

| 14.6.2 PORTQS Pin Assignment Register (PQSPAR)             | 14-11  |

| 14.6.3 PORTQS Data Direction Register (DDRQS)              | 14-12  |

| 14.7 Queued Serial Peripheral Interface                    | 14-13  |

| 14.7.1 QSPI Registers                                      | 14-15  |

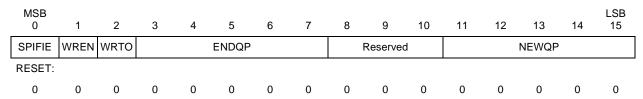

| 14.7.1.1 QSPI Control Register 0                           | 14-16  |

| 14.7.1.2 QSPI Control Register 1                           | 14-17  |

| 14.7.1.3 QSPI Control Register 2                           | 14-18  |

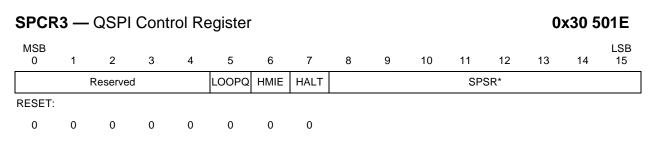

| 14.7.1.4 QSPI Control Register 3                           | 14-19  |

| 14.7.1.5 QSPI Status Register                              | 14-20  |

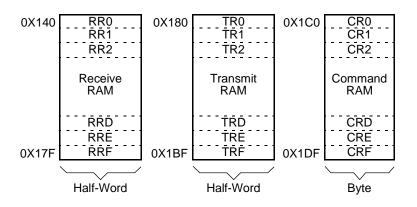

| 14.7.2 QSPI RAM                                            | 14-21  |

| 14.7.2.1 Receive RAM                                       | 14-22  |

| 14.7.2.2 Transmit RAM                                      | 14-22  |

| 14.7.2.3 Command RAM                                       | 14-22  |

| 14.7.3 QSPI Pins                                           | 14-23  |

| 14.7.4 QSPI Operation                                      | 14-24  |

| 14.7.4.1 Enabling, Disabling, and Halting the SPI          | 14-25  |

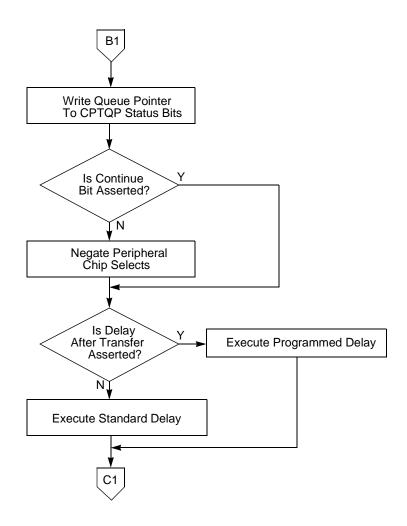

| 14.7.4.2 QSPI Interrupts                                   | 14-26  |

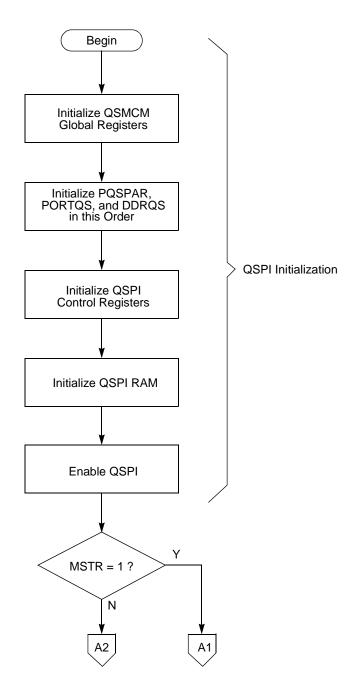

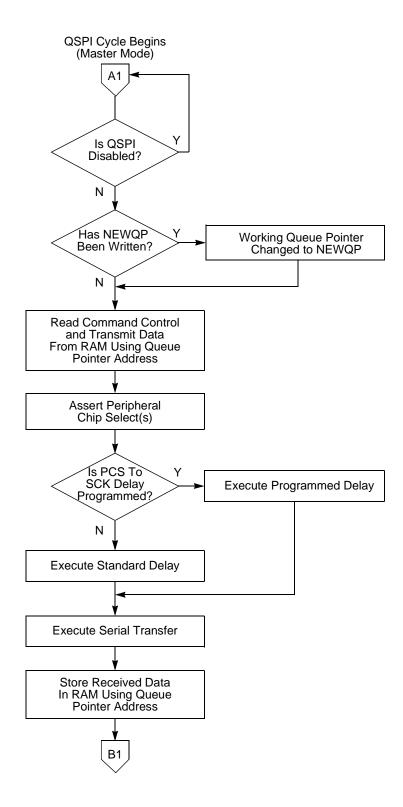

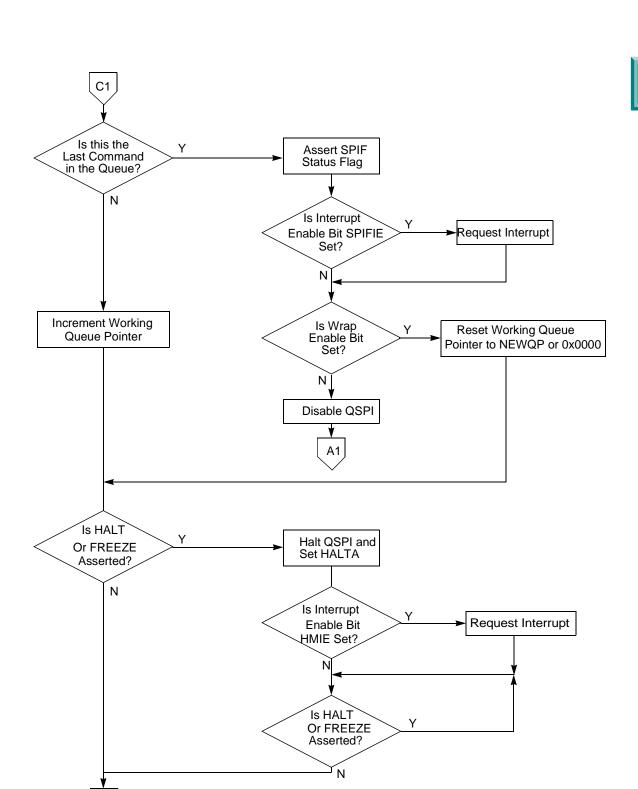

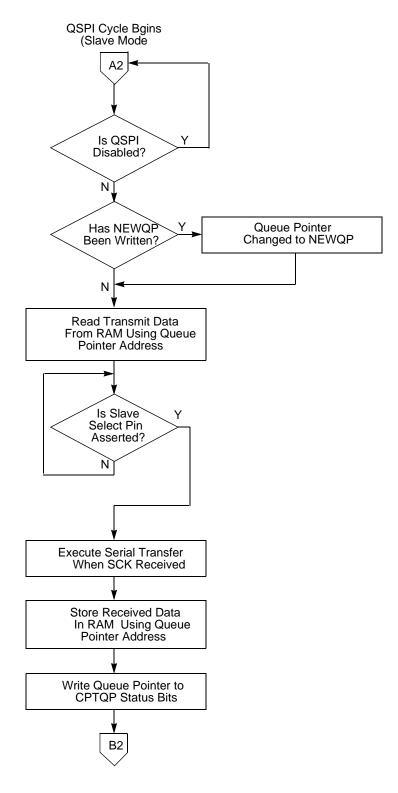

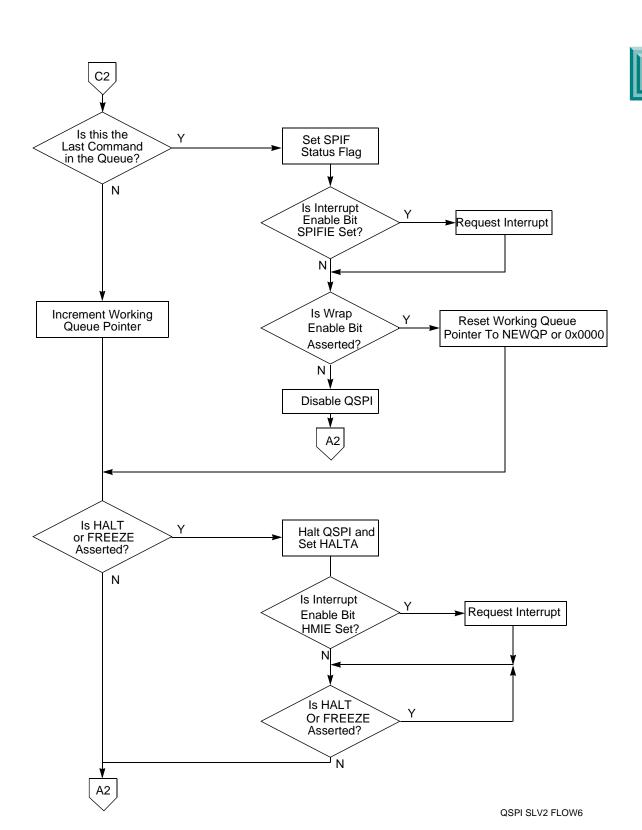

| 14.7.4.3 QSPI Flow                                         | 14-26  |

| 14.7.5 Master Mode Operation                               | 14-33  |

| 14.7.5.1 Clock Phase and Polarity                          | 14-34  |

| 14.7.5.2 Baud Rate Selection                               | 14-34  |

| 14.7.5.3 Delay Before Transfer                             | 14-35  |

| 14.7.5.4 Delay After Transfer                              | 14-35  |

| 14.7.5.5 Transfer Length                                   | 14-36  |

| 14.7.5.6 Peripheral Chip Selects                           | 14-36  |

| 14.7.5.7 Master Wraparound Mode                            | 14-37  |

| 14.7.6 Slave Mode                                          | 14-37  |

|                                                            |        |

| aragrapn                                                  | Page   |

|-----------------------------------------------------------|--------|

| Number                                                    | Number |

| 14.7.6.1 Description of Slave Operation                   |        |

| 14.7.7 Slave Wraparound Mode                              |        |

| 14.7.8 Mode Fault                                         |        |

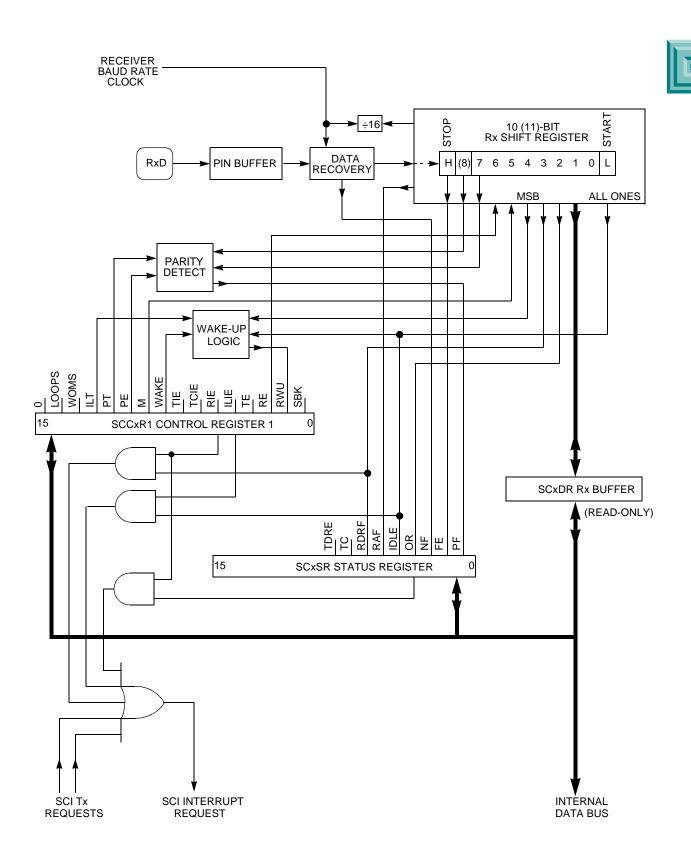

| 14.8 Serial Communication Interface                       |        |

| 14.8.1 SCI Registers                                      |        |

| 14.8.2 SCI Control Register 0                             |        |

| 14.8.3 SCI Control Register 1                             |        |

| 14.8.4 SCI Status Register (SCxSR)                        |        |

| 14.8.5 SCI Data Register (SCxDR)                          |        |

| 14.8.6 SCI Pins                                           |        |

| 14.8.7 SCI Operation                                      |        |

| 14.8.7.1 Definition of Terms                              |        |

| 14.8.7.2 Serial Formats                                   |        |

| 14.8.7.3 Baud Clock                                       |        |

| 14.8.7.4 Parity Checking                                  |        |

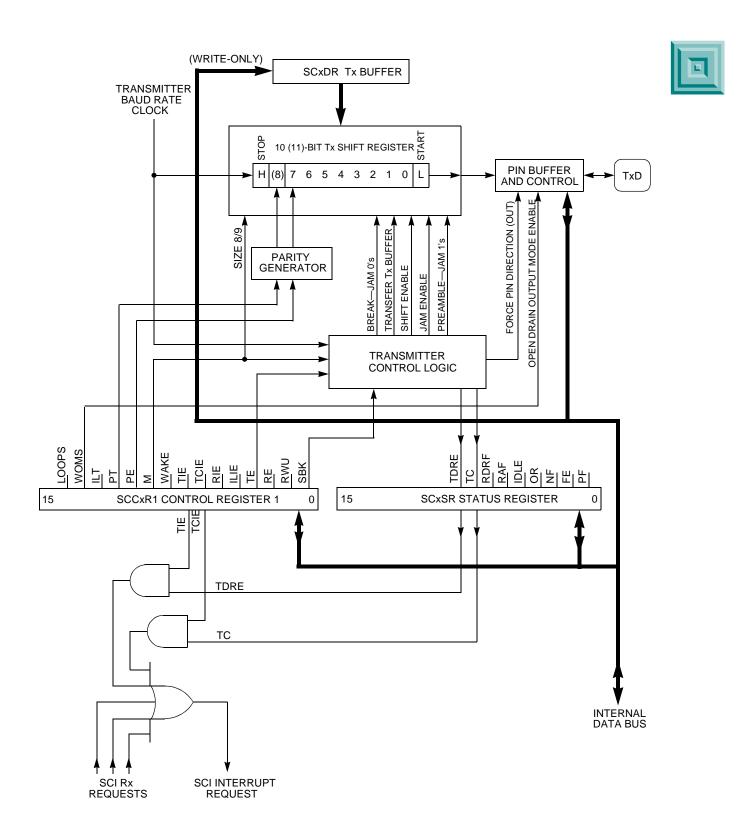

| 14.8.7.5 Transmitter Operation                            |        |

| 14.8.7.6 Receiver Operation                               |        |

| 14.8.7.7 Idle-Line Detection                              |        |

| 14.8.7.8 Receiver Wake-Up                                 |        |

| 14.8.7.9 Internal Loop Mode                               |        |

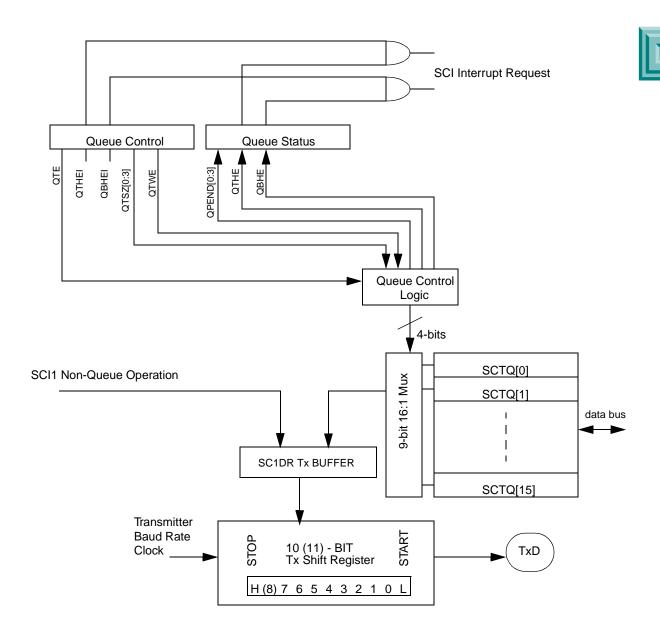

| 14.9 SCI Queue Operation                                  |        |

| 14.9.1 Queue Operation of SCI1 for Transmit and Receive   |        |

| 14.9.2 Queued SCI1 Status and Control Registers           |        |

| 14.9.2.1 QSCI1 Control Register                           |        |

| 14.9.2.2 QSCI1 Status Register                            |        |

| 14.9.3 QSCI1 Transmitter Block Diagram                    |        |

| 14.9.4 QSCI1 Additional Transmit Operation Features       |        |

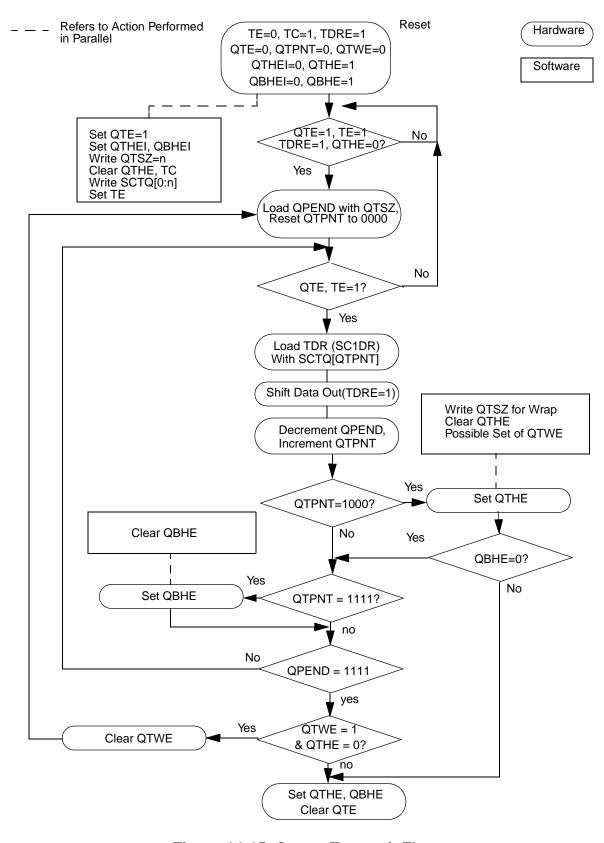

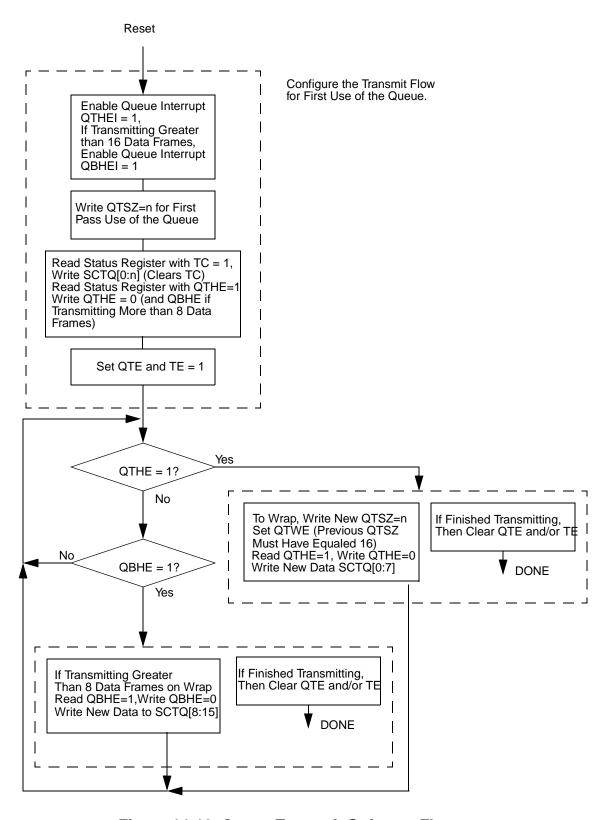

| 14.9.5 QSCI1 Transmit Flow Chart Implementing the Queue   |        |

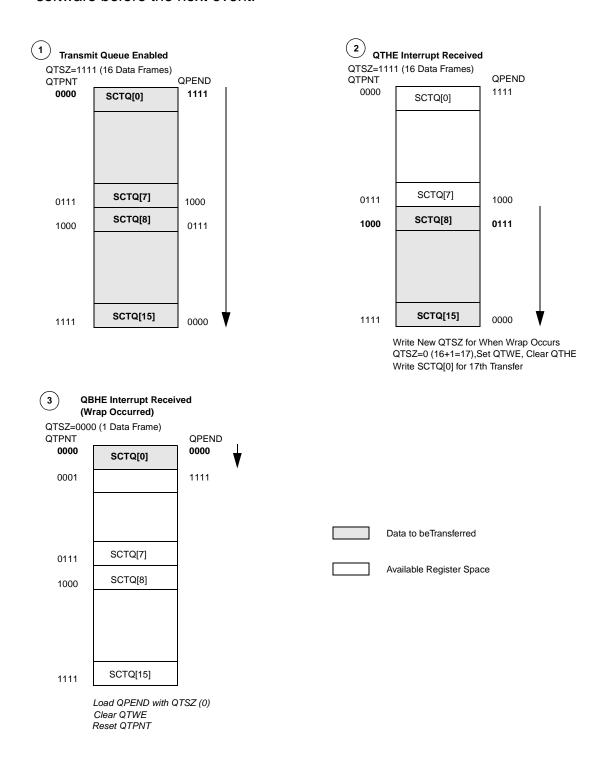

| 14.9.6 Example QSCI1 Transmit for 17 Data Bytes           |        |

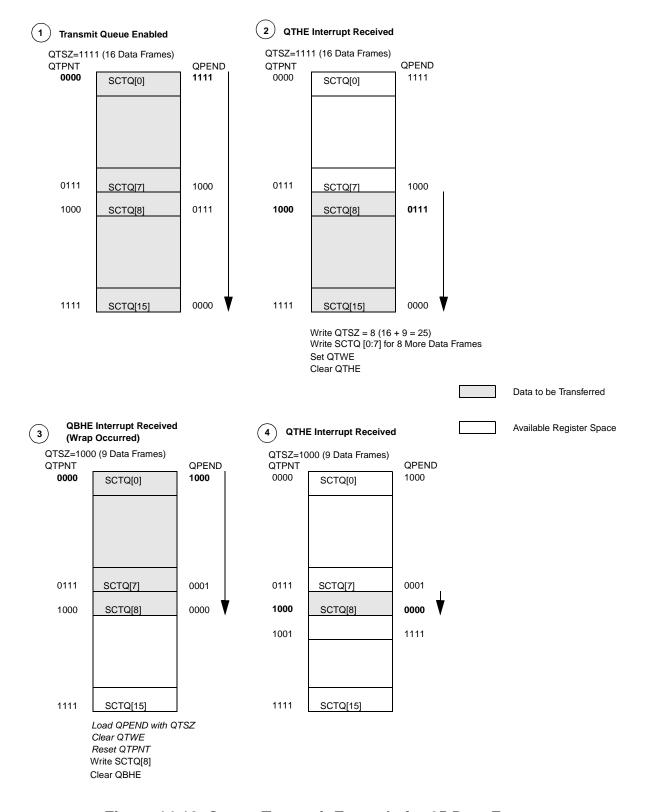

| 14.9.7 Example SCI Transmit for 25 Data Bytes             | 14-66  |

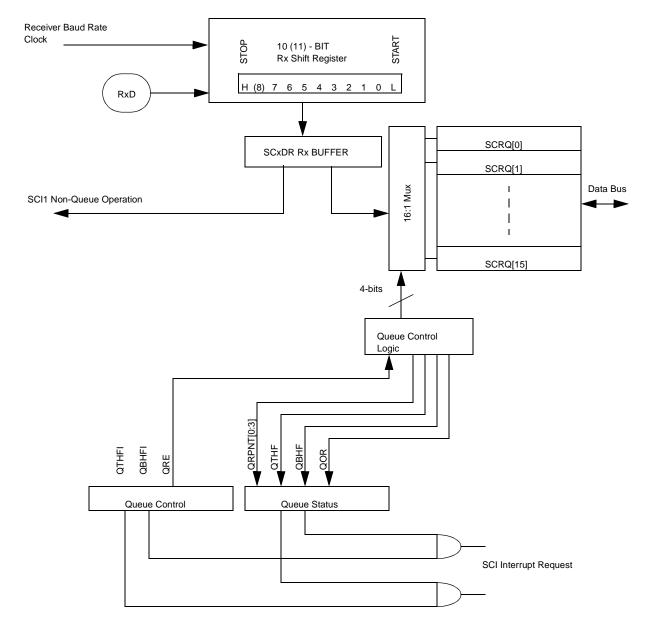

| 14.9.8 QSCI1 Receiver Block Diagram                       | 14-67  |

| 14.9.9 QSCI1 Additional Receive Operation Features        | 14-67  |

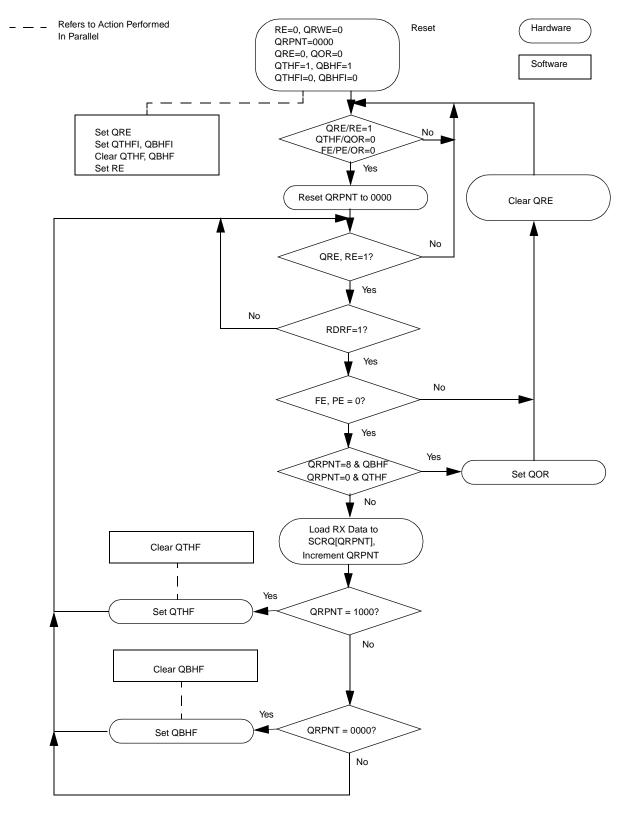

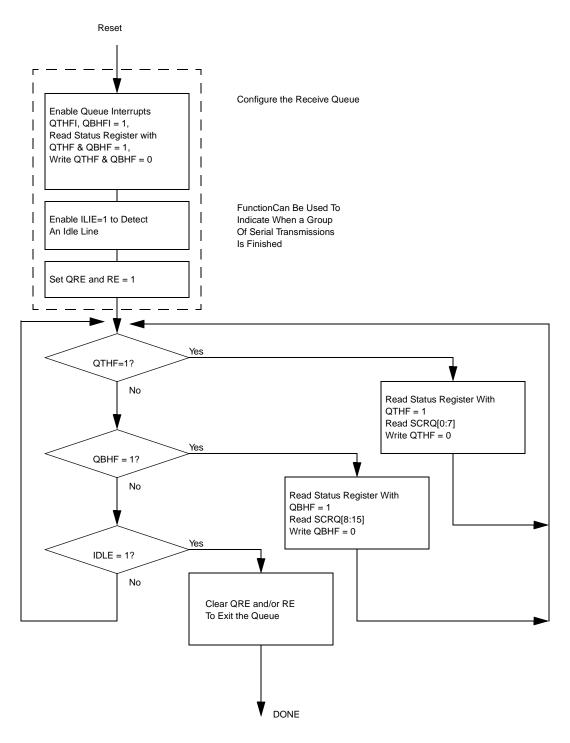

| 14.9.10 QSCI1 Receive Flow Chart Implementing The Queue   | 14-70  |

| 14.9.11 QSCI1 Receive Queue Software Flow Chart           | 14-71  |

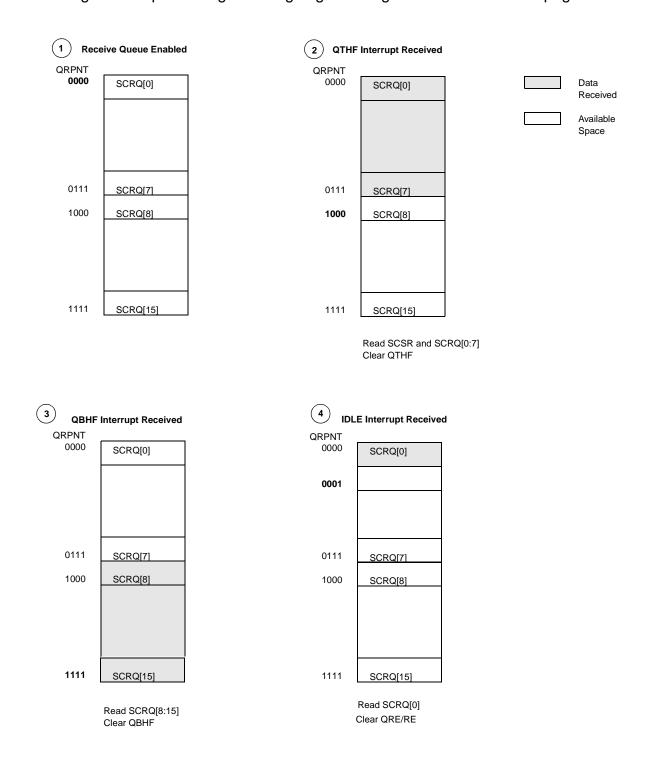

| 14.9.12 Example QSCI1 Receive Operation of 17 Data Frames | 14-72  |

| Section 15                                                |        |

| MODULAR INPUT/OUTPUT SUBSYSTEM (MIC                       | OS1)   |

| 15.1 MIOS1 Features                                       | -      |

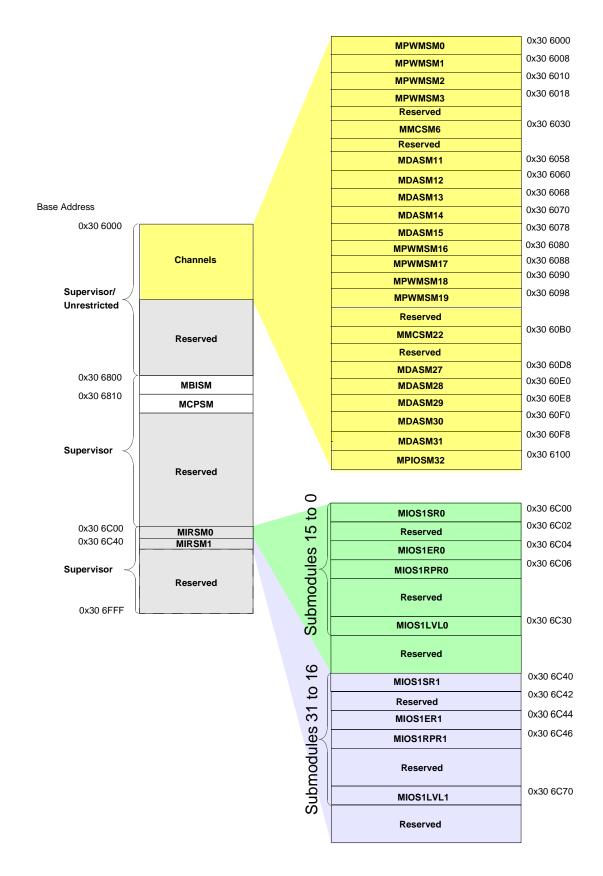

| 15.2 Submodule Numbering, Naming and Addressing           | 15-3   |

| 15.3 MIOS1 Signals                                        |        |

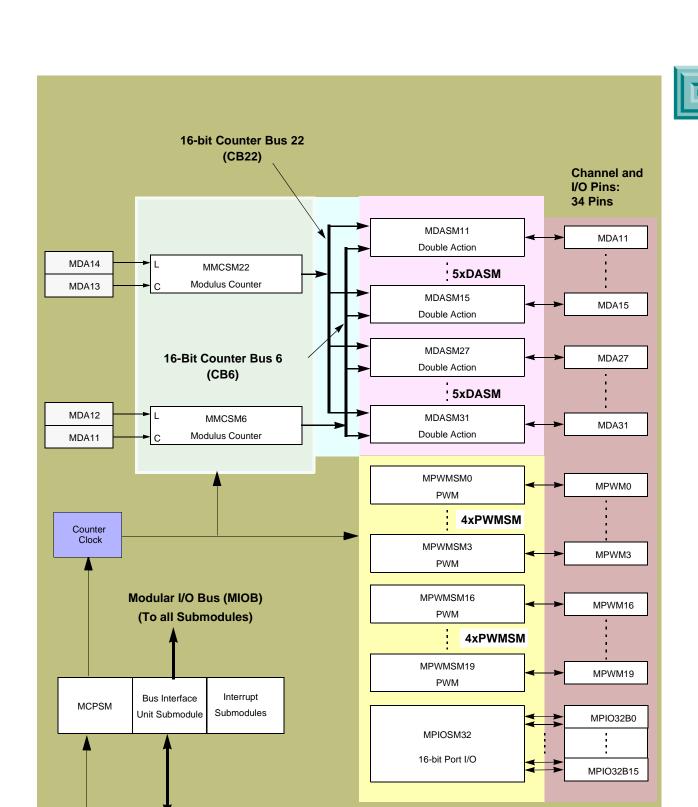

| 15.4 Block Diagram                                        |        |

| 15.5 MIOS1 Pus System                                     |        |

| 15.1 | MIOS1 Features                             | 15- |

|------|--------------------------------------------|-----|

| 15.2 | Submodule Numbering, Naming and Addressing | 15- |

| 15.3 | MIOS1 Signals                              | 15- |

| 15.4 | Block Diagram                              | 15- |

| 15.5 | MIOS1 Bus System                           | 15- |

| Paragraph                                                          | Page   |

|--------------------------------------------------------------------|--------|

| Number                                                             | Number |

| 15.5.1 Read/Write and Control Bus                                  |        |

| 15.5.2 Request Bus                                                 |        |

| 15.5.3 Counter Bus Set                                             |        |

| 15.6 MIOS1 Programmer's Model                                      |        |

| 15.7 MIOS1 I/O Ports                                               |        |

| 15.8 MIOS Bus Interface Submodule (MBISM)                          | 15-8   |

| 15.8.1 MIOS Bus Interface (MBISM) Registers                        | 15-8   |

| 15.8.1.1 MIOS1 Test and Pin Control Register                       |        |

| 15.8.1.2 MIOS1 Vector Register                                     |        |

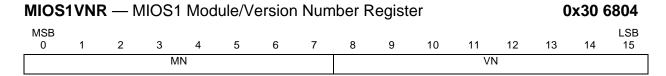

| 15.8.1.3 MIOS1 Module and Version Number Register                  |        |

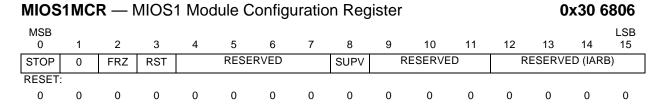

| 15.8.1.4 MIOS1 Module Configuration Register                       |        |

| 15.8.2 MBISM Interrupt Registers                                   |        |

| 15.8.2.1 MIOS1 Interrupt Level Register 0 (MIOS1LVL0)              |        |

| 15.8.2.2 MIOS1 Interrupt Level Register 1 (MIOS1LVL1)              |        |

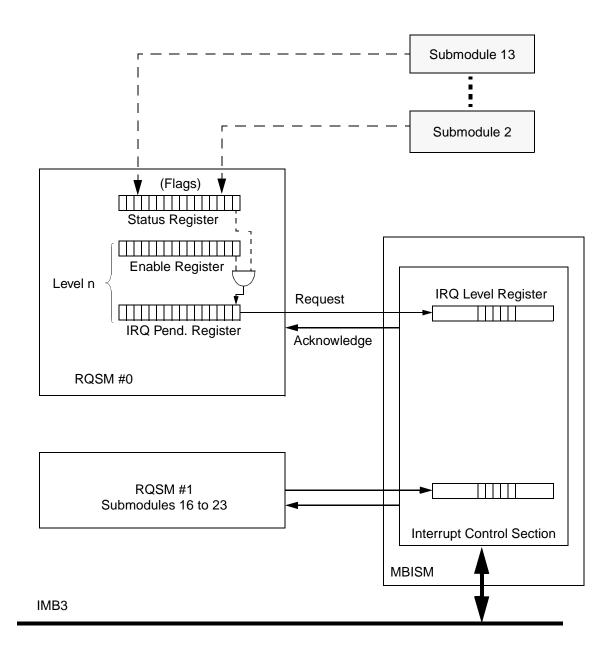

| 15.8.3 Interrupt Control Section (ICS)                             |        |

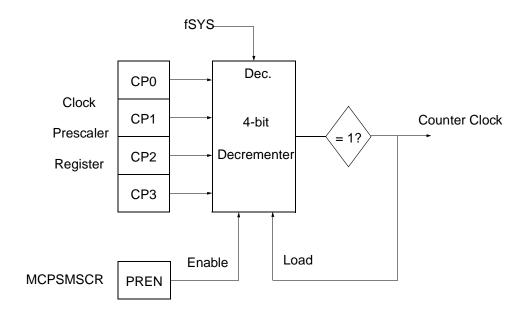

| 15.9 MIOS Counter Prescaler Submodule (MCPSM)                      |        |

| 15.9.1 MIOS Counter Prescaler Submodule (MCPSM) Registers          |        |

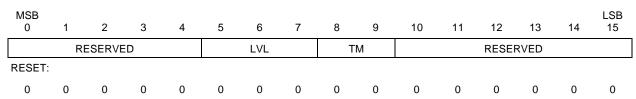

| 15.9.1.1 MCPSM Status/Control Register (MCPSMCSCR)                 |        |

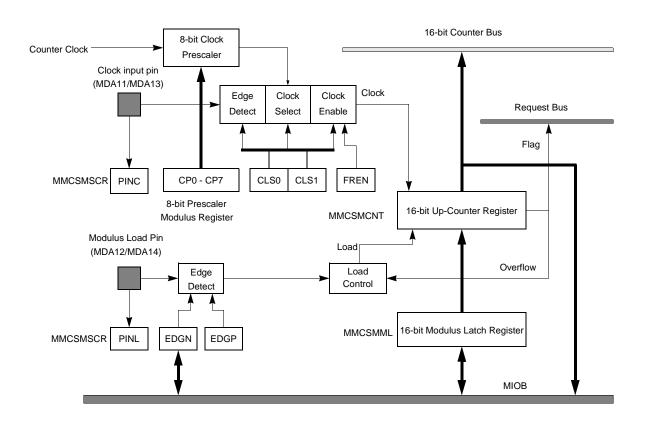

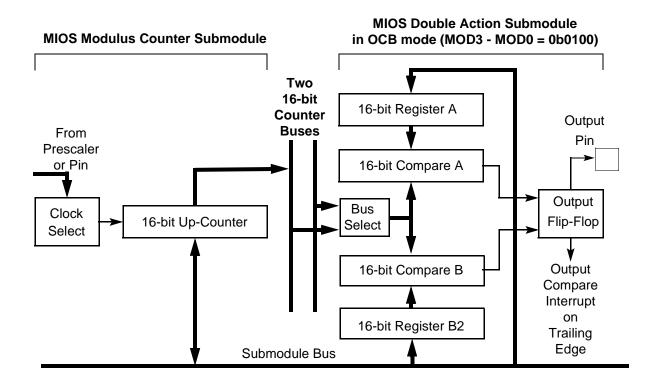

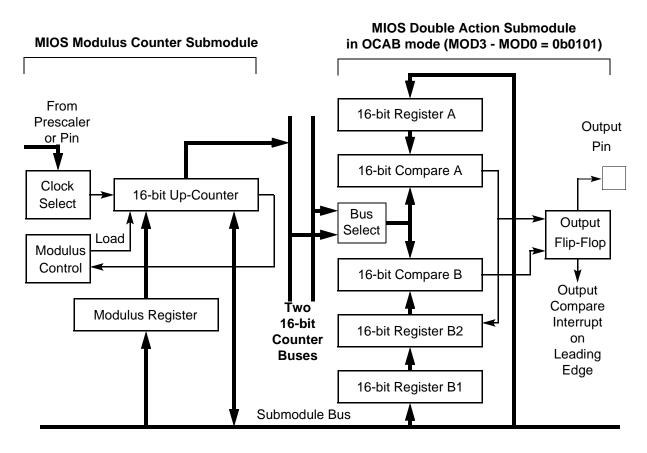

| 15.10 MIOS Modulus Counter Submodule (MMCSM)                       | 15-14  |

| 15.10.1 MIOS Modulus Counter Submodule (MMCSM) Registers           |        |

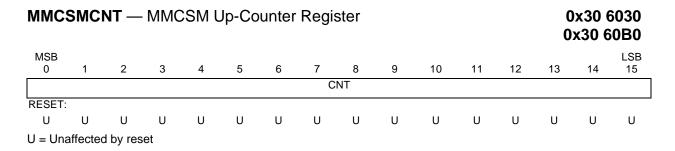

| 15.10.1.1 MMCSM Up-Counter Register (MMCSMCNT)                     |        |

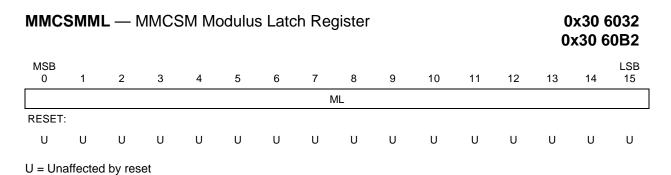

| 15.10.1.2 MMCSM Modulus Latch Register (MMCSMML)                   |        |

| 15.10.1.3 MMCSM Status/Control Register (Duplicated)               |        |

| 15.10.1.4 MMCSM Status/Control Register (MMCSMSCR)                 | 15-17  |

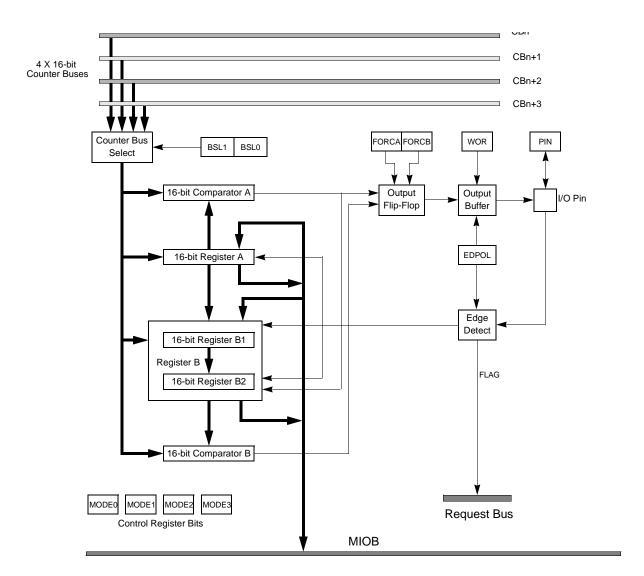

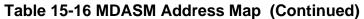

| 15.11 MIOS Double Action Submodule (MDASM)                         |        |

| 15.11.1 MIOS Double Action Submodule (MDASM) Registers             |        |

| 15.11.1.1 MDASM Data A Register                                    |        |

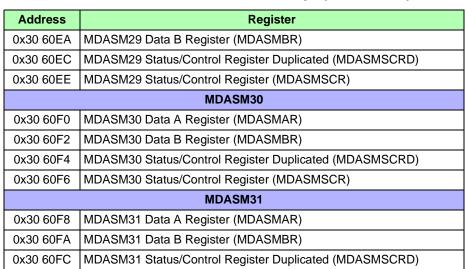

| 15.11.1.2 MDASM Data B Register (MDASMBR)                          |        |

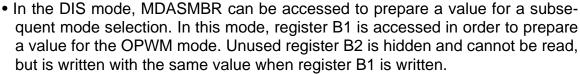

| 15.11.1.3 MDASM Status/Control Register (Duplicated)               |        |

| 15.11.1.4 MDASM Status/Control Register                            |        |

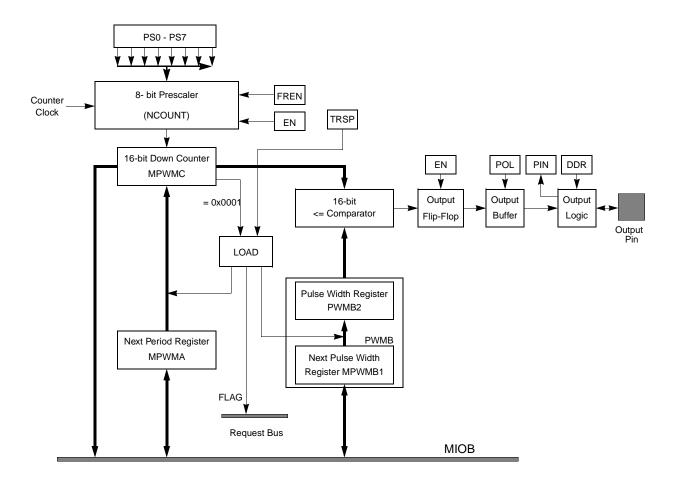

| 15.12 MIOS Pulse Width Modulation Submodule (MPWMSM)               |        |

| 15.12.1 MIOS Pulse Width Modulation Submodule (MPWMSM) Registers . |        |

| 15.12.1.1 MPWMSM Period Register (MPWMSMPERR)                      |        |

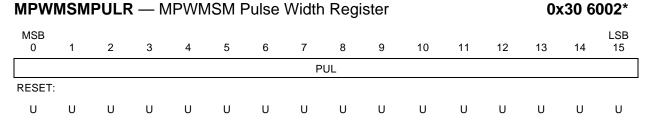

| 15.12.1.2 MPWMSM Pulse Width Register (MPWMSMPULR)                 |        |

| 15.12.1.3 MPWMSM Counter Register (MPWMSMCNTR)                     | 15-30  |

| 15.12.1.4 MPWMSM Status/Control Register(MPWMSMCR)                 | 15-30  |

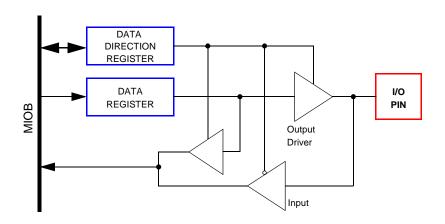

| 15.13 MIOS 16-bit Parallel Port I/O Submodule (MPIOSM)             | 15-32  |

| 15.13.1 MIOS 16-bit Parallel Port I/O Submodule (MPIOSM) Registers | 15-32  |

| 15.13.1.1 MPIOSM Data Register (MPIOSMDR)                          |        |

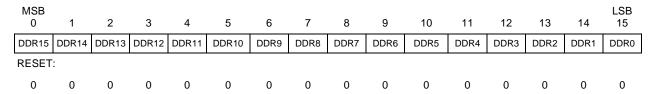

| 15.13.1.2 MPIOSM Data Direction Register (MPIOSMDDR)               | 15-33  |

| 15.14 MIOS1 Interrupts                                             | 15-33  |

| 15.14.1 MIOS Interrupt Request Submodule (MIRSM)                   | 15-34  |

| 15 14 2 MIOS Interrupt Request Submodule 0 (MIRSMO) Registers      | 15-35  |

| Paragraph                                                      | Page   |

|----------------------------------------------------------------|--------|

| Number                                                         | Number |

| 15.14.2.1 MIRSM0 Interrupt Status Register (MIOS1SR0)          | 15-36  |

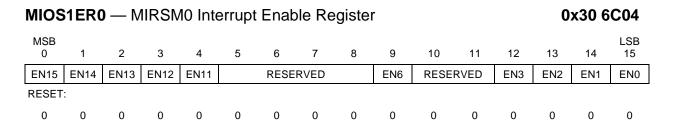

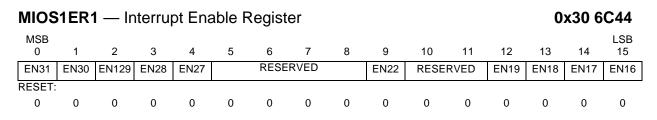

| 15.14.2.2 MIRSM0 Interrupt Enable Register (MIOS1ER0)          | 15-37  |

| 15.14.2.3 MIRSM0 Request Pending Register (MIOS1RPR0)          | 15-37  |

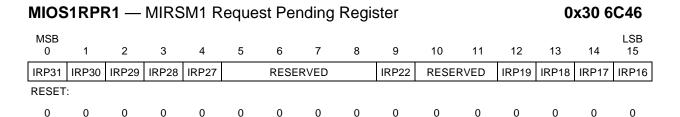

| 15.14.3 MIOS Interrupt Request Submodule 1 (MIRSM1) Registers  | 15-38  |

| 15.14.3.1 MIRSM1 Interrupt Status Register (MIOS1SR1)          | 15-38  |

| 15.14.3.2 MIRSM1 Interrupt Enable Register (MIOS1ER1)          | 15-39  |

| 15.14.3.3 MIRSM1 Request Pending Register (MIOS1RPR1)          | 15-40  |

| 15.15 MIOS1 Function Examples                                  | 15-40  |

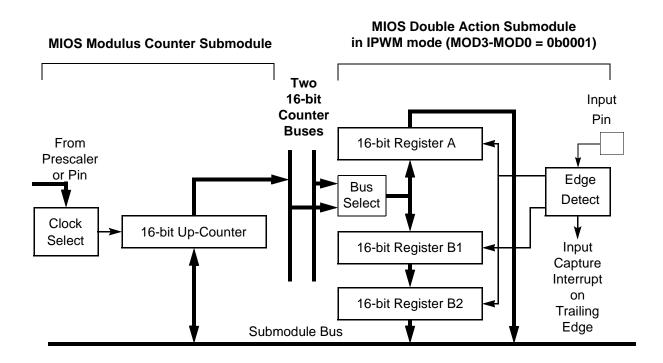

| 15.15.1 MIOS1 Input Double Edge Pulse Width Measurement        | 15-40  |

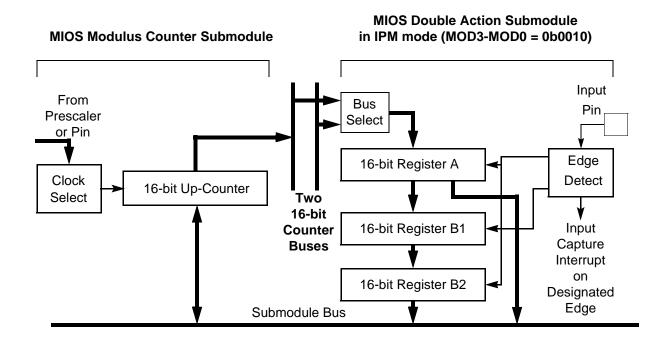

| 15.15.2 MIOS1 Input Double Edge Period Measurement             | 15-42  |

| 15.15.3 MIOS1 Double Edge Single Output Pulse Generation       | 15-43  |

| 15.15.4 MIOS1 Output Pulse Width Modulation With MDASM         | 15-44  |

| 15.15.5 MIOS1 Input Pulse Accumulation                         | 15-45  |

| 15.16 MIOS1 Configuration                                      | 15-45  |

| Section 16                                                     |        |

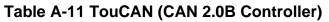

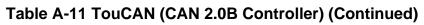

| CAN 2.0B CONTROLLER MODULE                                     |        |

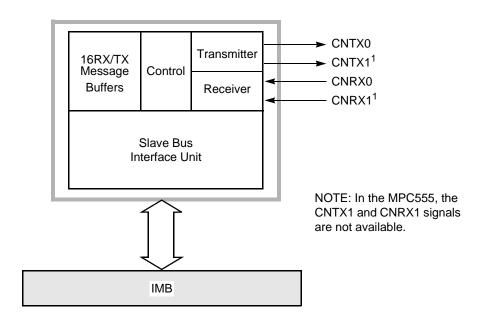

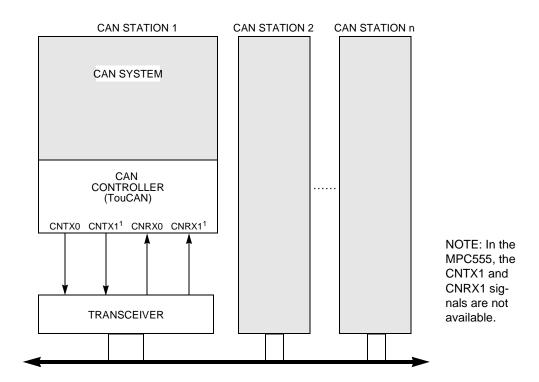

| 16.1 Features                                                  | 16-1   |

| 16.2 External Pins                                             | 16-2   |

| 16.3 TouCAN Architecture                                       | 16-3   |

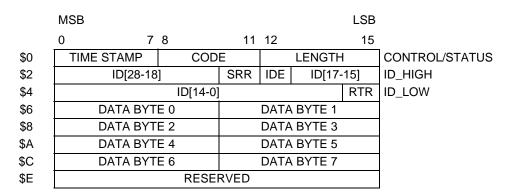

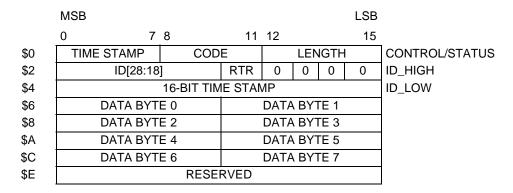

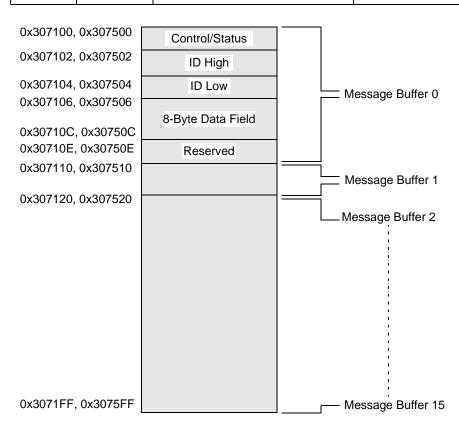

| 16.3.1 TX/RX Message Buffer Structure                          | 16-3   |

| 16.3.1.1 Common Fields for Extended and Standard Format Frames | 16-4   |

| 16.3.1.2 Fields for Extended Format Frames                     | 16-5   |

| 16.3.1.3 Fields for Standard Format Frames                     | 16-6   |

| 16.3.1.4 Serial Message Buffers                                | 16-6   |

| 16.3.1.5 Message Buffer Activation/Deactivation Mechanism      | 16-6   |

| 16.3.1.6 Message Buffer Lock/Release/Busy Mechanism            | 16-6   |

| 16.3.2 Receive Mask Registers                                  | 16-7   |

| 16.3.3 Bit Timing                                              | 16-8   |

| 16.3.3.1 Configuring the TouCAN Bit Timing                     | 16-9   |

| 16.3.4 Error Counters                                          | 16-9   |

| 16.3.5 Time Stamp                                              | 16-10  |

| 16.4 TouCAN Operation                                          | 16-11  |

| 16.4.1 TouCAN Reset                                            | 16-11  |

| 16.4.2 TouCAN Initialization                                   | 16-11  |

| 16.4.3 Transmit Process                                        | 16-12  |

| 16.4.3.1 Transmit Message Buffer Deactivation                  | 16-13  |

| 16.4.3.2 Reception of Transmitted Frames                       | 16-13  |

| 16.4.4 Receive Process                                         | 16-13  |

| 16.4.4.1 Receive Message Buffer Deactivation                   | 16-14  |

| 16.4.4.2 Locking and Releasing Message Buffers                 |        |

| 16.4.5 Remote Frames                                           |        |

| 16.4.6. Overload Frames                                        | 16-16  |

| Paragraph                                      | Page   |

|------------------------------------------------|--------|

| Number                                         | Number |

| 16.5 Special Operating Modes                   |        |

| 16.5.1 Debug Mode                              |        |

| 16.5.2 Low-Power Stop Mode                     |        |

| 16.5.3 Auto Power Save Mode                    |        |

| 16.6 Interrupts                                |        |

| 16.7 Programmer's Model                        |        |

| 16.7.1 TouCAN Module Configuration Register    |        |

| 16.7.2 TouCAN Test Configuration Register      |        |

| 16.7.3 TouCAN Interrupt Configuration Register |        |

| 16.7.4 Control Register 0                      |        |

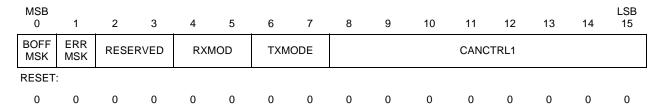

| 16.7.5 Control Register 1                      |        |

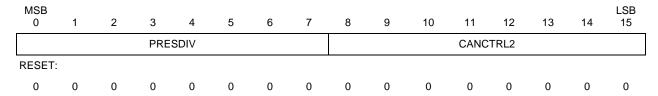

| 16.7.6 Prescaler Divide Register               |        |

| 16.7.7 Control Register 2                      |        |

| 16.7.8 Free Running Timer                      |        |

| 16.7.9 Receive Global Mask Registers           |        |

| 16.7.10 Receive Buffer 14 Mask Registers       |        |

| 16.7.11 Receive Buffer 15 Mask Registers       |        |

| 16.7.12 Error and Status Register              |        |

| 16.7.13 Interrupt Mask Register                |        |

| 16.7.14 Interrupt Flag Register                |        |

| 16.7.15 Error Counters                         |        |

| Sectio                                         | n 17   |

| TIME PROCES                                    |        |

|                                                |        |

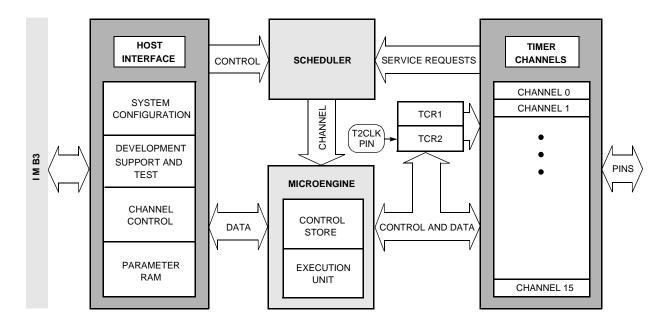

| 17.1 Overview                                  |        |

| 17.2 TPU3 Components                           |        |

| 17.2.1 Time Bases                              |        |

| 17.2.2 Timer Channels                          |        |

| 17.2.3 Scheduler                               |        |

| 17.2.4 Microengine                             |        |

| 17.2.5 Host Interface                          |        |

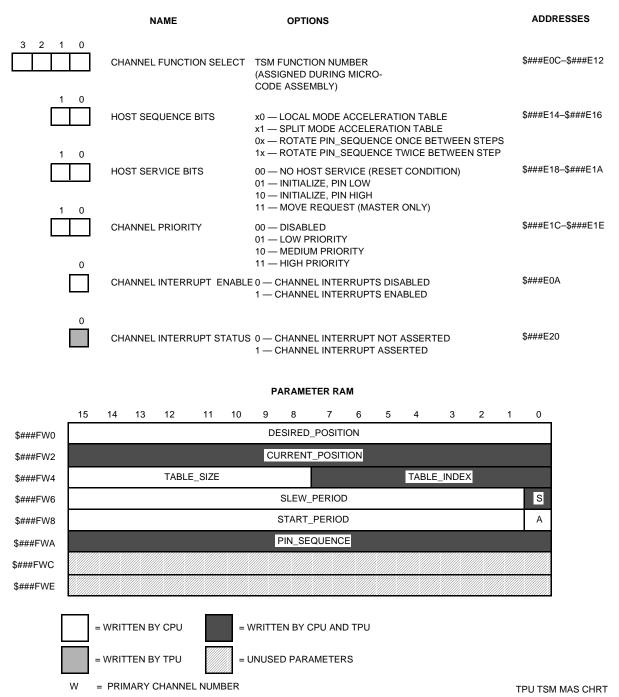

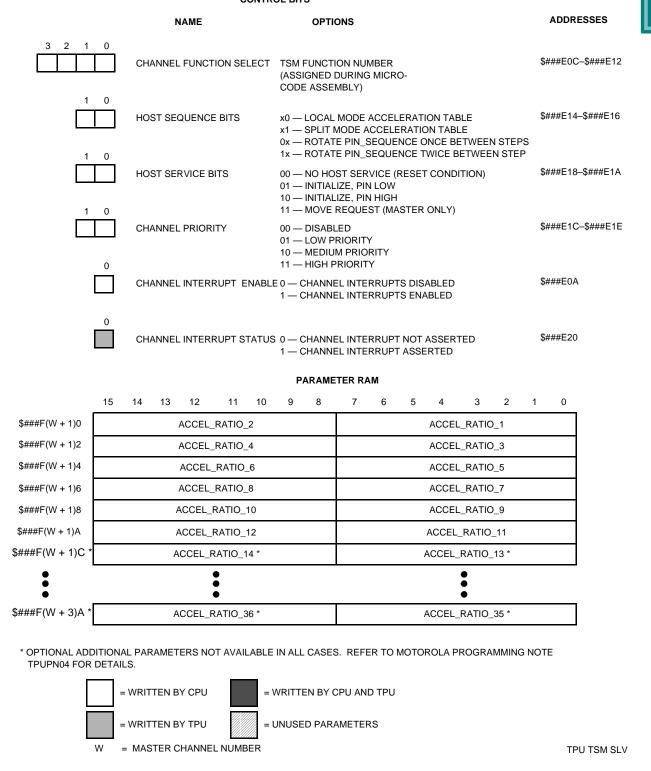

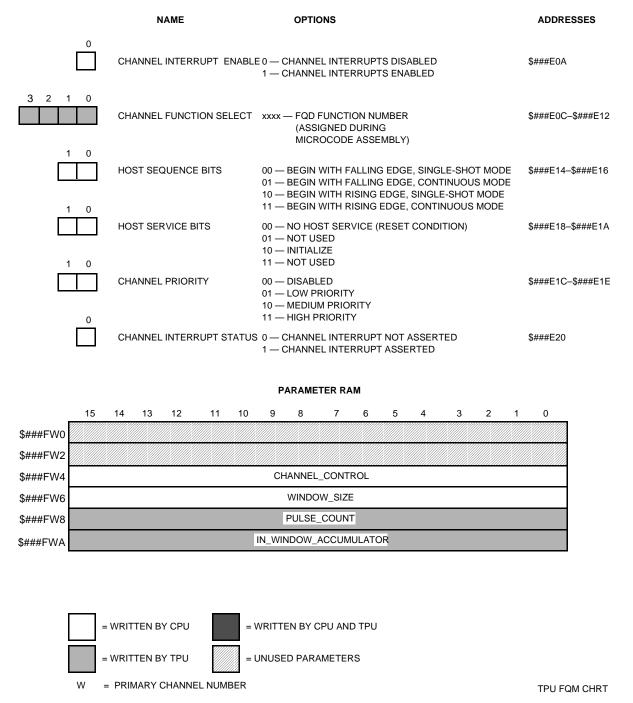

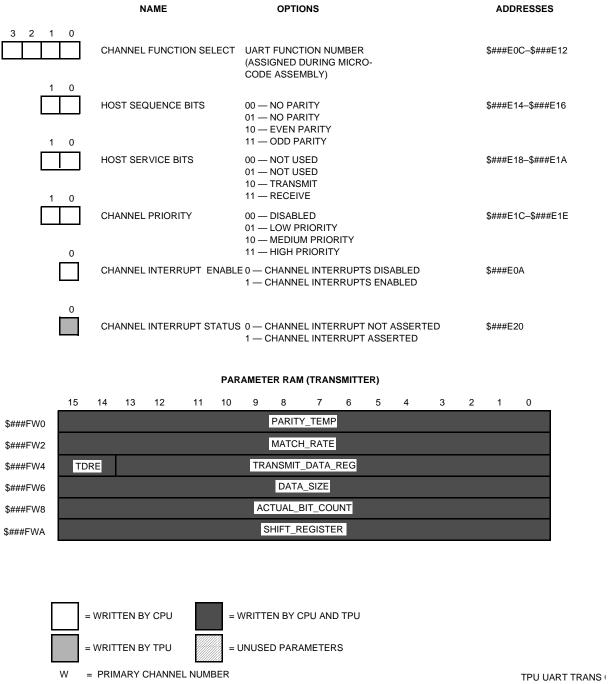

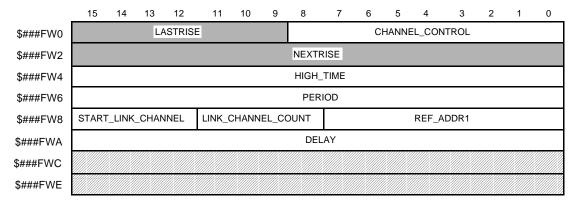

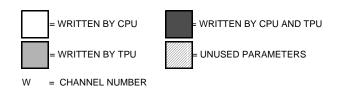

| 17.2.6 Parameter RAM                           |        |

| 17.3 TPU Operation                             |        |

| 17.3.1 Event Timing                            |        |

| 17.3.2 Channel Orthogonality                   |        |

| 17.3.3 Interchannel Communication              |        |

| 17.3.4 Programmable Channel Service Priority   |        |

| 17.3.5 Coherency                               |        |

| 17.3.6 Emulation Support                       |        |

| 17.3.7 TPU3 Interrupts                         |        |

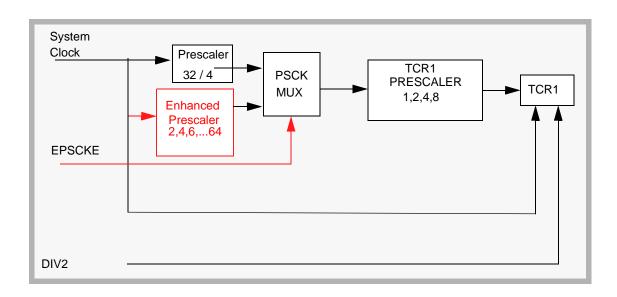

| 17.3.8 Prescaler Control for TCR1              |        |

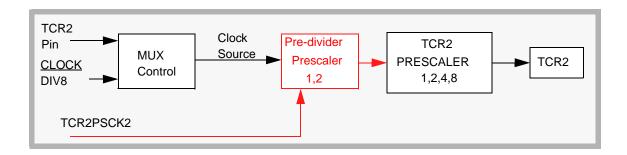

| 17.3.9 Prescaler Control for TCR2              |        |

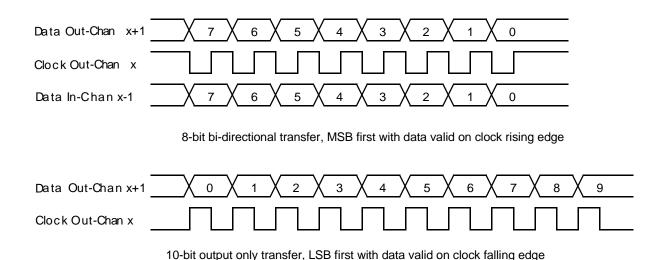

| 17.4 Programming Model                         |        |

| • .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Paragraph                                                    | Page                                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|--|

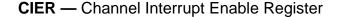

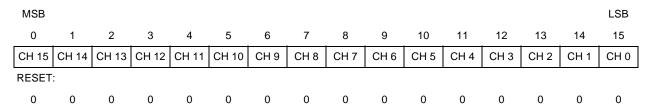

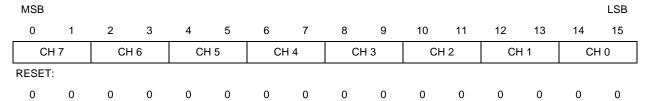

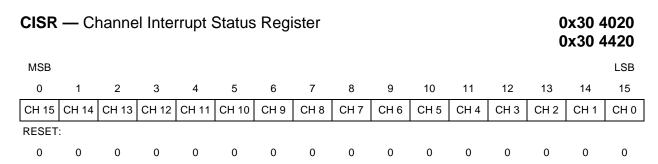

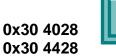

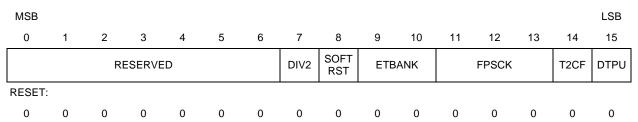

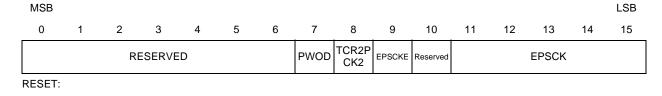

| 17.4.1 TPU Module Configuration Register. 17-41 17.4.2 TPU3 Test Configuration Register 17-41 17.4.3 Development Support Control Register 17-41 17.4.4 Development Support Status Register 17-41 17.4.5 TPU3 Interrupt Configuration Register 17-41 17.4.5 TPU3 Interrupt Configuration Register 17-41 17.4.6 Channel Interrupt Enable Register 17-41 17.4.7 Channel Function Select Registers 17-41 17.4.8 Host Sequence Registers 17-41 17.4.9 Host Service Request Registers 17-41 17.4.10 Channel Priority Registers 17-41 17.4.11 Channel Interrupt Status Register 17-41 17.4.12 Link Register 17-41 17.4.13 Service Grant Latch Register 17-41 17.4.15 TPU3 Module Configuration Register 17-41 17.4.16 TPU3 Module Configuration Register 2 17-2 17.4.17 TPU3 Test Registers 17-2 17.4.18 TPU3 Parameter RAM 17-2 17.5 Time Functions 17-2  Section 18  DUAL-PORT TPU RAM (DPTRAM)  18.1 Features 18- 18.3 DPTRAM Configuration and Block Diagram 18- 18.3.1 DPTRAM Module Configuration Register (DPTMCR) 18- 18.3.3 DPTRAM Test Register 18- 18.3.4 MISR High (MISRH) and MISR Low (MISRL) 18- 18.3.5 MISC Counter (MISCNT) 18- 18.4.0 Peration 18- 18.4.1 Normal Operation 18- 18.4.2 Standby Operation 18- 18.4.3 Reset Operation 18- 18.4.3 Reset Operation 18- 18.4.4 Stop Operation 18- 18.4.5 Freeze Operation 18- 18.4.6 TPU3 Emulation Mode Operation 18- 18.4.7 Freeze Operation 18- 18.4.8 TPU3 Emulation Mode Operation 18- 18.5 Multiple Input Signature Calculator (MISC) 18- 18.5 Multiple Input Signature Calculator (MISC) 18- 18.5 Multiple Input Signature Calculator (MISC) 18- 18.1 Introduction 19- 19.1 Introduction 19- 19.1.1 MPC555 CMF Features 19- |                                                              | Number                                    |  |

| 17.4.3 Development Support Control Register       17-1         17.4.4 Development Support Status Register       17-1         17.4.5 TPU3 Interrupt Configuration Register       17-1         17.4.6 Channel Interrupt Enable Register       17-1         17.4.7 Channel Function Select Registers       17-1         17.4.8 Host Sequence Registers       17-1         17.4.9 Host Service Request Registers       17-1         17.4.10 Channel Priority Registers       17-1         17.4.11 Channel Interrupt Status Register       17-1         17.4.12 Link Register       17-1         17.4.13 Service Grant Latch Register       17-1         17.4.14 Decoded Channel Number Register       17-1         17.4.15 TPU3 Module Configuration Register 2       17-2         17.4.16 TPU Module Configuration Register 3       17-2         17.4.17 TPU3 Test Registers       17-2         17.5 Time Functions       17-2         Section 18         DUAL-PORT TPU RAM (DPTRAM)         18.1 Features       18-1         18.2 DPTRAM Configuration and Block Diagram       18-1         18.3 Programming Model       18-1         18.3.1 DPTRAM Module Configuration Register (DPTMCR)       18-1         18.3.2 DPTRAM Test Register       18-1                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                              |                                           |  |

| 17.4.4 Development Support Status Register       17-4.         17.4.5 TPUS Interrupt Configuration Register       17-4.         17.4.6 Channel Interrupt Enable Registers       17-1.         17.4.7 Channel Function Select Registers       17-1.         17.4.8 Host Sequence Registers       17-1.         17.4.9 Host Service Request Registers       17-1.         17.4.10 Channel Priority Registers       17-1.         17.4.11 Channel Interrupt Status Register       17-1.         17.4.12 Link Register       17-1.         17.4.13 Service Grant Latch Register       17-1.         17.4.14 Decoded Channel Number Register       17-1.         17.4.15 TPU3 Module Configuration Register 2       17-2.         17.4.16 TPU Module Configuration Register 3       17-2.         17.4.17 TPU3 Test Registers       17-2.         17.5 Time Functions       17-2.         Section 18         DUAL-PORT TPU RAM (DPTRAM)         18.1 Features       18-         18.2 DPTRAM Configuration and Block Diagram       18-         18.3 Programming Model       18-         18.3.1 DPTRAM Module Configuration Register (DPTMCR)       18-         18.3.2 DPTRAM Test Register       18-         18.3.3 Ram Base Address Register (RAMBAR)       18-                                                                                                                                                                                                                                                                                                                                                                                                                              | 17.4.2 TPU3 Test Configuration Register                      | 17-12                                     |  |