- Duty Cycle for LCD Driver is Over 1/400

- Recommended V<sub>EE</sub> Voltage Range for LCD Driver: 20 V to 42 V (45 V Max)

- 160 Channel Outputs

- Power Supply Voltage . . . 5 V ± 10%

- High-Voltage CMOS SI Gate Technology

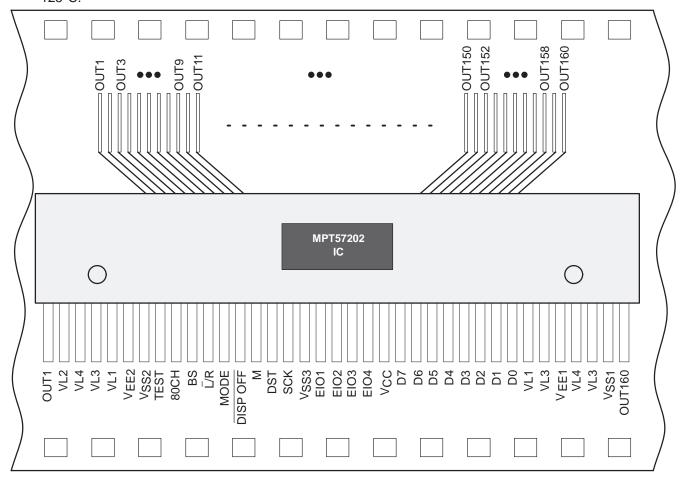

- TAB (Tape Automated Bonding) Packaging

#### description

The MPT57202 is a CMOS integrated circuit designed to drive an LCD (liquid crystal display) for a dot matrix STN (super twisted nematic). The outputs can be configured as one set of 160 output channels or as two sets of 80 output channels. The duty cycle is over 1/400, and the output bias voltage range (V<sub>EE</sub>) is from 20 V to 42 V (45 V maximum).

The outputs can be configured as one set of 160 output channels or as 2 sets of 80 output channels. This high-voltage CMOS SI gate device is available in a custom TAB (tape automated bonding) package.

The MPT57202 is characterized for operation over the full military temperature range of -55°C to 125°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### function table

| SIGNAL    | COMMON (ROW) MODE                                                               |                                                    |  |  |  |  |

|-----------|---------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| BS        | Not Use                                                                         | ed (tie low)                                       |  |  |  |  |

| D7-D0     | Not Use                                                                         | ed (tie low)                                       |  |  |  |  |

| DISP OFF† | TEST VL2 (display off): L                                                       |                                                    |  |  |  |  |

| DST       | Data shift o                                                                    | on falling edge                                    |  |  |  |  |

| 80 CH     | L = 160-channel                                                                 | H=80-channel x 2 (parallel)                        |  |  |  |  |

| EIO1      | Serial I/O                                                                      | 1 CH Serial I/O                                    |  |  |  |  |

| EIO2      | See Note 1                                                                      | 80 CH Serial I/O                                   |  |  |  |  |

| EIO3      | See Note 1                                                                      | 81 CH Serial I/O                                   |  |  |  |  |

| EIO4      | Serial I/O                                                                      | 160 CH Serial I/O                                  |  |  |  |  |

|           | L/R = L (left shift)<br>EIO1 ← <r1> ← <r2> ← <r3>← <r160></r160></r3></r2></r1> |                                                    |  |  |  |  |

| Ī/R       |                                                                                 | (right shift)<br>→ <r3>→ <r160> → EIO4</r160></r3> |  |  |  |  |

|           | M, data combination                                                             | Selects level                                      |  |  |  |  |

| М         | 0,1<br>1,0<br>0,0<br>1,1                                                        | VL1<br>VL3<br>VL4<br>VL2                           |  |  |  |  |

| MODE      |                                                                                 | L                                                  |  |  |  |  |

| SCK       | Not use                                                                         | ed (tie low)                                       |  |  |  |  |

| TEST      | Test pin                                                                        | = L or open                                        |  |  |  |  |

<sup>†</sup> This terminal should be low at power up for logic resetting.

NOTE 1: This terminal is not used in this configuration. Although the pin produces a low output level, it should be left open.

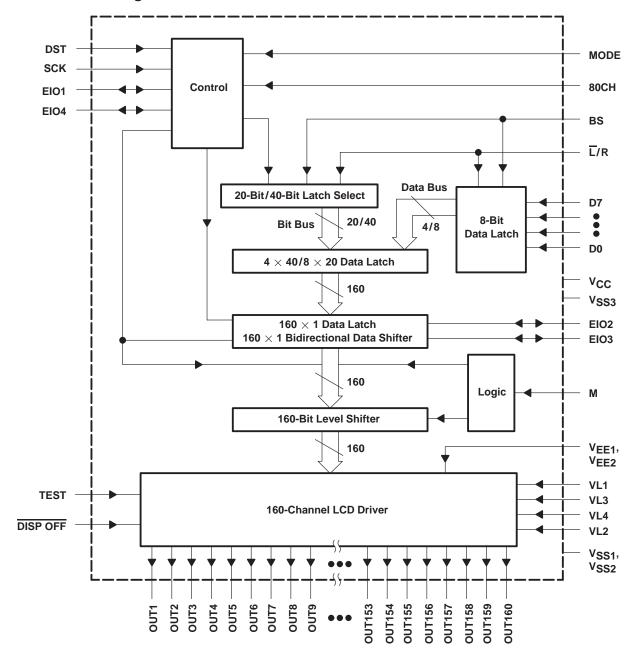

## functional block diagram

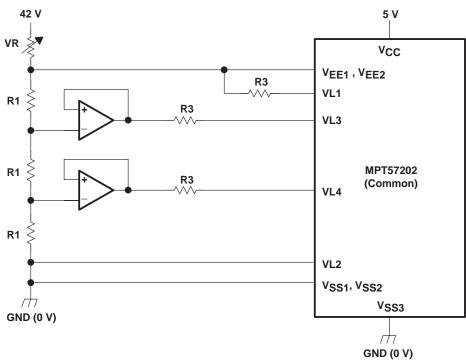

#### power supply circuit

NOTE A. Separation between high voltage GND ( $V_{SS1}$ ,  $V_{SS2}$ ) line and logic GND ( $V_{SS3}$ ) line is recommended to avoid noise problems.

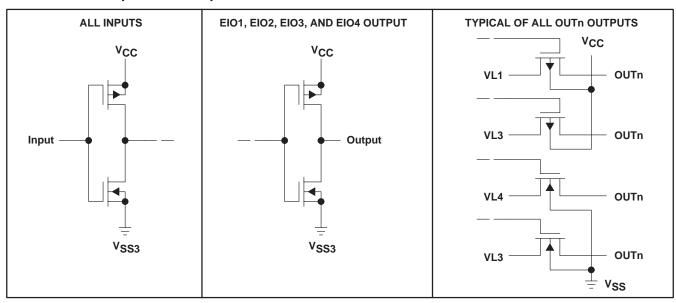

#### schematics of inputs and outputs

#### **Terminal Functions**

#### common (row) driver mode

| TERMINAL<br>NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80CH             | I   | 80CH is the 160-channel/80-channel mode select  L = 160-channel data shift mode; H = 80-channel-x-2 data shift mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BS               | I   | Not used (tie low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D7-D0            | ı   | Not used (tie low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DISP OFF         | I   | Display off. A low level on DISP OFF disables normal operation, turning the display off (0V) and enabling the test mode. DISP OFF must be tied high for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DST              | I   | Data strobe. DST is the data strobed input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EIO1             | I/O | Serial I/O 1. When $\overline{L}/R$ is high, EIO1 is an active-high serial input. When $\overline{L}/R$ is low (left-shift mode), EIO1 is an active-high serial output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EIO2             | I/O | Serial I/O 2:  When the device is configured in 160-channel data shift mode (80CH = L), EIO2 is not used and should be left open.  When the device is configured in 80-channel-x-2 data shift mode (80CH = H) and L/R is low; this EIO2 is an active-high serial input for the first 80-channel output section.  L/R is high; EIO2 is an active-high serial output for the first 80-channel output section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EIO3             | I/O | Serial I/O 3: When MPT57202 is configured in 160-channel data shift mode (80 CH = L), EIO3 is not used and should be left open. When the device is configured in 80-channel-x-2 data shift mode (80CH = H) and  L/R is low; EIO3 is an active-high serial output for the first 80-channel output section.  L/R is high; EIO3 is an active-high serial input for the first 80-channel output section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EIO4             | I/O | Serial I/O 4: When $\overline{L}/R = H$ : EIO4 is an active-high serial output When $\overline{L}/R = L$ : EIO4 is an active-high serial input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ī/R              | 1   | Select left or right shift When the MPT57202 is in 160-channel data shift mode (80CH = L) and $\overline{L}/R$ = H, data is right shifted into EIO1 and out from EIO4 $EIO1 \rightarrow  \rightarrow  \rightarrow \rightarrow  \rightarrow EIO4$ When the MPT57202 is in 160-channel data shift mode (80CH = L) and $\overline{L}/R$ = L, data is left shifted into EIO4 and out from EIO1 $EIO1 \leftarrow  \leftarrow  \leftarrow \leftarrow  \leftarrow EIO4$ When the MPT57202 is in 80-channel-x-2 data shift mode with two parallel 80-channel output sections (80CH = H) and $\overline{L}/R$ = H, data is right shifted into EIO1 and EIO3 and out from EIO2 and EIO4 $EIO1 \rightarrow  \rightarrow  \rightarrow \rightarrow  \rightarrow EIO2$ $EIO3 \rightarrow  \rightarrow  \rightarrow \rightarrow  \rightarrow EIO4$ When the MPT57202 is in 80-channel-x-2 data shift mode with two parallel 80-channel output sections (80CH = H) and $\overline{L}/R$ = L, data is left shifted into EIO2 and EIO4 and out from EIO1 and EIO3 $EIO1 \leftarrow  \leftarrow  \leftarrow \leftarrow  \leftarrow EIO2$ $EIO3 \leftarrow  \leftarrow  \leftarrow \leftarrow  \leftarrow EIO2$ $EIO3 \leftarrow  \leftarrow  \leftarrow \leftarrow  \leftarrow EIO4$ In all cases, R<1> $\rightarrow$ OUT1, e.g., R<1> $\rightarrow$ OUT1, R<76> $\rightarrow$ OUT76, etc. See Table 1 for the cascade configuration. |

| M                | I   | Frame signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MODE             | I   | Common/segment mode select. MODE should be tied low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OUT1-OUT160      | 0   | Common (row) driver output channels (see Table 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SCK              | I   | Not used (tie low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## **Terminal Functions (continued)**

| TERMINAL<br>NAME | I/O | DESCRIPTION                                                                                                                        |

|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------|

| TEST             | I   | TEST is used for factory testing only. For normal operation tie TEST low or leave it open. TEST has an internal pulldown resistor. |

| Vcc              |     | 5-V supply terminal                                                                                                                |

| V <sub>EE1</sub> |     | Output buffer bias                                                                                                                 |

| V <sub>EE2</sub> |     | Output logic bias                                                                                                                  |

| VL1              |     | VL1 is the on-level of the LCD driver output                                                                                       |

| VL2              |     | VL2 is the off-level of the LCD driver output                                                                                      |

| VL3              |     | VL3 is the on-level of the LCD driver output                                                                                       |

| VL4              |     | VL4 is the off-level of the LCD driver output                                                                                      |

| V <sub>SS1</sub> |     | Ground terminal with respect to V <sub>EE1</sub>                                                                                   |

| V <sub>SS2</sub> |     | Ground terminal with respect to V <sub>EE2</sub>                                                                                   |

| V <sub>SS3</sub> |     | Ground terminal with respect to V <sub>CC</sub>                                                                                    |

Table 1. Cascade Configurations - Common-Driver Mode (MODE = L)

| INPUTS |     |        | 1/0    | NUMBER OF CHANNELS/ |        |                 |

|--------|-----|--------|--------|---------------------|--------|-----------------|

| 80 CH  | Ī/R | EIO1   | EIO2   | EIO3                | EIO4   | SHIFT DIRECTION |

| L      | Н   | Input  | -      | -                   | Output | 160/right       |

| L      | L   | Output | -      | -                   | Input  | 160/left        |

| Н      | Н   | Input  | Output | Input               | Output | 80 x 2/right    |

| Н      | L   | Output | Input  | Output              | Input  | 80 x 2/left     |

#### absolute maximum ratings over free-air temperature range†

| Supply voltage range, V <sub>CC</sub> (see Note 2)                                | 0.3 V to 7 V                                                                                                         |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Supply voltage (V <sub>SS1</sub> , V <sub>SS2</sub> , V <sub>SS3</sub> )          | $\dots \dots $ |

| Input voltage range, V <sub>I</sub> (DST, SCK, M, MODE, 80CH, L/R, BS, EIO1-EIO4, |                                                                                                                      |

| D0-D7, DISP OFF, TEST)                                                            | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$                                                                           |

| Output voltage range, VO (EIO1, EIO2, EIO3, EIO4)                                 | $-0.3 \text{ V to V}_{CC} + 0.3 \text{ V}$                                                                           |

| Output bias voltage range for LCD (V <sub>EE1</sub> , V <sub>EE2</sub> )          |                                                                                                                      |

| Supply voltage range for LCD (VL1, VL2, VL3, VL4) (see Note 3)                    | $-0.3 \text{ V to V}_{EE} + 0.3 \text{ V}$                                                                           |

| Input current, I <sub>I</sub>                                                     | ± 10 mA                                                                                                              |

| Output current, I <sub>O:</sub> EIO1 to EIO4                                      | 10 mA                                                                                                                |

| OUT1 to OUT160                                                                    | 5 mA                                                                                                                 |

| Storage temperature range, T <sub>Stg</sub>                                       | $\dots$ -65°C to 150°C                                                                                               |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 2. Voltage values are with respect to VSS1, VSS2, and VSS3.

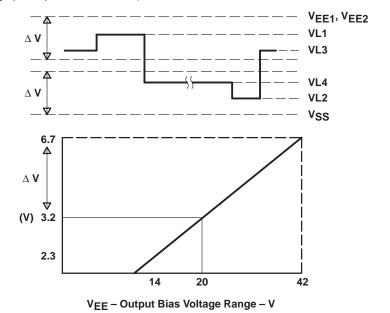

3. The following conditions must be met:  $\begin{array}{lll} \text{VEE1 and VEE2} \geq \text{VL1} \geq \text{VL3} \geq \text{VEE - 7 V, and 7 V} \geq \text{VL4} \geq \text{VL2} \geq \text{VSS1, VSS2, VSS3} \\ \text{VEE1 and VEE2} > \text{VL1} > \text{VL3} > \text{VEE - } \Delta \text{ V, and } \Delta \text{ V} > \text{VL4} > \text{VL2} > \text{VSS1, VSS2, VSS3} \\ \text{(See Figure 1 for a graphic representation of } \Delta \text{ V).} \end{array}$

Figure 1. VLn Voltage Range

#### recommended operating conditions (see Figure 2)

|                                          |                   |                                                                    | MIN                 | NOM | MAX                 | UNIT |

|------------------------------------------|-------------------|--------------------------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>CC</sub>          | See Notes 4 and 5 |                                                                    | 4.5                 | 5   | 5.5                 | V    |

| Supply voltage, VSS                      |                   |                                                                    |                     | 0   |                     | V    |

| Supply voltage for LCD drive             | See Notes 4 and 5 | V <sub>EE1</sub> , V <sub>EE2</sub> , VL1, VL3, VL4, VL2           | 20                  |     | 42                  | V    |

| High-level input voltage, VIH            | •                 | 80CH, BS, D7–D0, DISP OFF, DST, EIO1-EIO4, L/R, M, MODE, SCK, TEST | 0.8 V <sub>CC</sub> |     | VCC                 | V    |

| Low-level input voltage, V <sub>IL</sub> |                   | 80CH, BS, D7–D0, DISP OFF, DST, EIO1-EIO4, L/R, M, MODE, SCK, TEST | VSS                 |     | 0.2 V <sub>CC</sub> | V    |

| Clock frequency, f <sub>CLK</sub>        |                   | DST                                                                |                     |     | 1                   | MHz  |

| Operating free-air temperature, TA       |                   |                                                                    | -55                 |     | 125                 | °C   |

NOTES: 4. VLn voltage range should be under the following conditions:

$\begin{array}{l} \text{V}_{\text{EE1}} \text{ and } \text{V}_{\text{EE2}} \geq \text{VL1} \geq \text{VL3} \geq \text{V}_{\text{EE}} \text{--} 7 \text{ V, and } 7 \text{ V} \geq \text{VL4} \geq \text{VL2} \geq \text{V}_{\text{SS1}}, \text{V}_{\text{SS2}} \text{V}_{\text{SS3}} \\ \text{V}_{\text{EE1}} \text{ and } \text{V}_{\text{EE2}} > \text{VL1} > \text{VL3} > \text{V}_{\text{EE}} \text{--} \Delta \text{ V, and } \Delta \text{ V} > \text{VL4} > \text{VL2} > \text{V}_{\text{SS1}}, \text{V}_{\text{SS2}} \text{V}_{\text{SS3}} \\ \end{array}$

Power-up and power-down sequences are as follows:

Power-up sequence: V<sub>CC</sub> → Input → V<sub>EE1</sub>, V<sub>EE2</sub>, V<sub>EE3</sub>

Power-down sequence: V<sub>EE1</sub>, V<sub>EE2</sub>, V<sub>EE3</sub> → Input → V<sub>CC</sub>

## electrical characteristics over full range of recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                      |                                                                       | TEST CONDITIONS                                                          | MIN                   | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|------|------|------|

| VOH                   | High-level output voltage      | EIO1-EIO4                                                             | $V_{CC} = 5 V \pm 10\%,$<br>$I_{OH} = -0.4 MA$                           | V <sub>CC</sub> - 0.4 |      | VCC  | V    |

| VOL                   | Low-level output voltage       | EIO1-EIO4                                                             | V <sub>CC</sub> = 5 V ± 10%,<br>I <sub>OL</sub> = -0.4 MA                | Vss                   |      | 0.4  | V    |

| ΙΗ                    | High-level input current       | 80CH, BS, D7-D0,<br>DISP OFF, DST,<br>EIO1-EIO4, L/R, M,<br>MODE, SCK |                                                                          | 5                     | μΑ   |      |      |

|                       |                                | TEST                                                                  |                                                                          |                       |      | 500  | μΑ   |

| lı∟                   | Low-level input current        | 80CH, BS, D7-D0,<br>DISP OFF, DST,<br>EIO1-EIO4, L/R, M,<br>MODE, SCK | V <sub>IL</sub> = V <sub>SS</sub>                                        |                       |      | -5   | μΑ   |

|                       |                                | TEST                                                                  | ]                                                                        |                       |      | -5   | μΑ   |

| z <sub>O</sub>        | Output impedance               | OUT1 to OUT160                                                        | $V_{EE} = 14 \text{ V},$<br>$V_{Ln} = \Delta V,$<br>$I_{O} = 150 \mu A,$ |                       |      | 3    | kΩ   |

| ΔZO                   | Output impedance variance      | OUT1 to OUT160                                                        | See Note 6                                                               |                       | ±10% | ±30% |      |

| Ц                     | Input current                  | VL1, VL2, VL3, VL4                                                    | $V_I = V_{EE}, V_{SS}$                                                   |                       |      | ±100 | μΑ   |

| Icc                   | Supply current                 | V <sub>CC</sub>                                                       | 1/480 duty operation,                                                    |                       |      | 1    | mA   |

| IEE                   | Supply current                 | V <sub>EE1</sub> , V <sub>EE2</sub>                                   | See Note 7                                                               |                       |      | 0.5  | mA   |

| ICC                   | Supply current                 | VCC                                                                   | 1/480 duty operation                                                     |                       |      | 5    | mA   |

| IEE                   | Supply current                 | V <sub>EE1</sub> , V <sub>EE2</sub>                                   | 1/400 duty operation                                                     |                       |      | 2    | mA   |

| I <sub>I</sub> (stand | <sub>by)</sub> Standby current | VCC                                                                   | See Note 8                                                               |                       |      | 500  | μΑ   |

NOTES: 6.  $\Delta Z_0 = (1-Xn/Xaverage) \times 100$

Xn = impedance or OUTn, Xaverage = impedance of average OUTn

- 7.  $f_{DST} = 36 \text{ kHz}$ ,  $V_{IH} = V_{CC}$ ,  $V_{IL} = V_{SS}$ , and no output load.

- 8. Voltage level at EIO1 input = VCC

# timing requirements over full range of recommended operating conditions (unless otherwise noted)

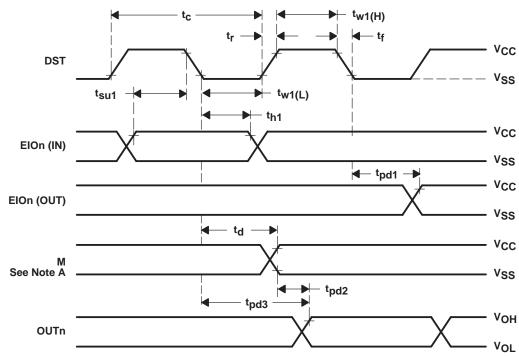

|                    | PARAMETER                        |                            | TEST CONDITIONS | MIN | MAX  | UNIT |

|--------------------|----------------------------------|----------------------------|-----------------|-----|------|------|

| t <sub>C</sub>     | Cycle time                       | DST                        |                 | 1   |      | μs   |

| t <sub>w1(L)</sub> | Pulse duration, low pulse width  | DST                        | Soo Figure 2    | 970 |      | ns   |

| tw1(H)             | Pulse duration, high pulse width | ادما                       | See Figure 2    | 30  |      | ns   |

| t <sub>su1</sub>   | Setup time, EIOn valid to DST↓   |                            | See Figure 2    | 100 |      | ns   |

| t <sub>h1</sub>    | Hold time, EIOn valid to DST↓    |                            | See Figure 2    | 30  |      | ns   |

| t <sub>d</sub>     | Frame delay tolerance time       | Frame delay tolerance time |                 |     | ±300 | ns   |

NOTE 9: This parameter is not production tested.

# switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                   | PARAMETER                                     |                         | TEST CONDITIONS |  |     | UNIT |

|-------------------|-----------------------------------------------|-------------------------|-----------------|--|-----|------|

| t <sub>pd</sub> 1 | Propagation delay time, DST↓ to EIO1 valid    | C <sub>L</sub> = 30 pF, | See Figure 2    |  | 110 | ns   |

| t <sub>pd</sub> 2 | Propagation delay time, M valid to OUTn valid | C <sub>L</sub> = 45 pF, | See Figure 2    |  | 1.5 | μs   |

| t <sub>pd</sub> 3 | Propagation delay time, DST↓ to OUTn valid    |                         |                 |  | 0.7 | μs   |

#### PARAMETER MEASUREMENT INFORMATION

NOTES: A.  $t_{\Gamma}$  and  $t_{f} \le 30$ ns for input pulses

B.  $V_{IH} = 0.8 V_{CC}$ ,  $V_{IL} = 0.2 V_{CC}$

Figure 2. Clock Timing Waveforms for Common-Driver Mode

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated