NOTE A: Pin numbering is for reference only to the function table. The pin numbering in this figure does not correspond to the numbering on the custom tape.

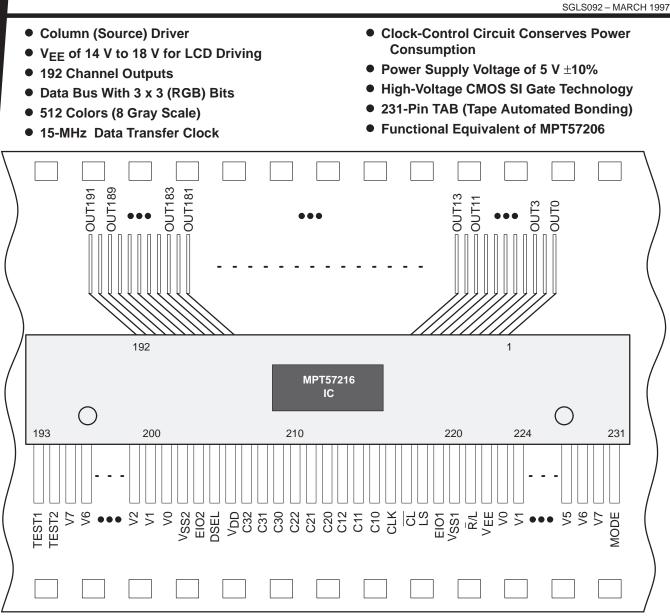

### description

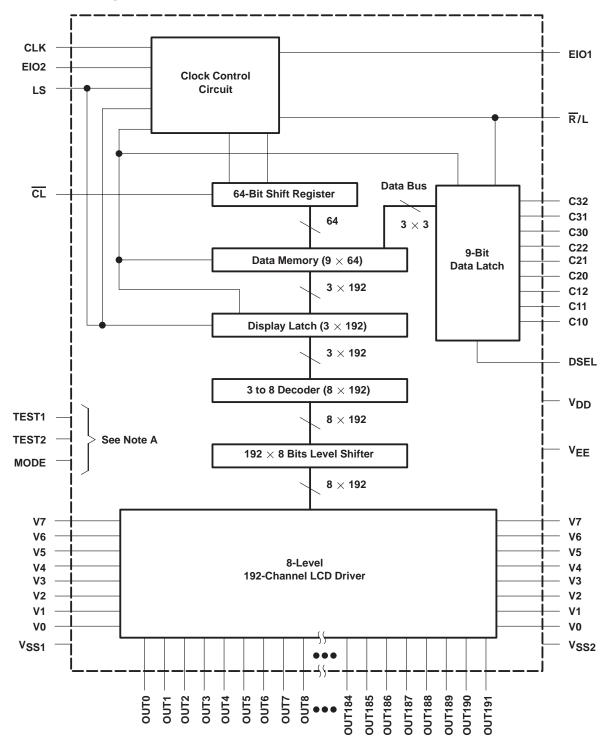

The MPT57216 is a 192-channel color thin-film transistor (TFT) LCD driver based on an active matrix LCD (AMLCD). It has 3 bits for each RGB input. These 3 bits are decoded internally to select one of eight bias-voltage levels, V0 to V7 for output, in order to support 512 colors ( $R = 2^3 = 8$ ;  $G = 2^3 = 8$ ;  $B = 2^3 = 8$ ;  $RGB = 2^9 = 512$ ).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1997, Texas Instruments Incorporated

SGLS092 - MARCH 1997

## functional block diagram

NOTE A: These terminals are for factory testing only and should be left open.

SGLS092 - MARCH 1997

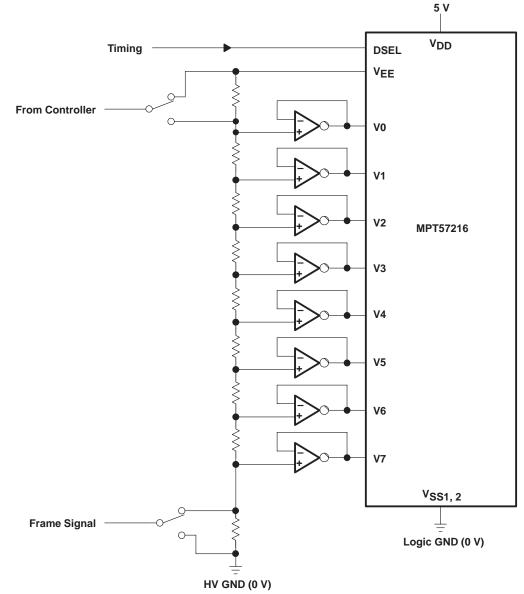

## power supply circuit

NOTE A: Separation between high voltage GND line and logic GND line is recommended to avoid noise problems.

SGLS092 - MARCH 1997

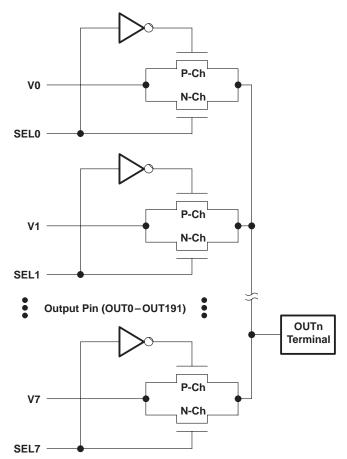

## decoding for OUT0 – OUT191

NOTE A. The C32 – C10 inputs are decoded internally to derive SEL0 – SEL7 from the output of a 3-to-8 decoder. Only one of the decoder outputs, SEL0 – SEL7, puts ≈V<sub>EE</sub> on the P-CH and ≈V<sub>SS</sub> on the N-CH of its corresponding transmission gate. This allows only one of eight bias voltages, V0 – V7, to pass onto OUTn.

SGLS092 - MARCH 1997

## **Terminal Functions**

| NAME                                     | TERMINAL   | I/O    |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 | FUNCT                                  | ION      |                                        |                                                |       |          |           |       |                 |             |  |

|------------------------------------------|------------|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|----------------------------------------|----------|----------------------------------------|------------------------------------------------|-------|----------|-----------|-------|-----------------|-------------|--|

| C32<br>C31                               | 207<br>208 | 8<br>9 |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 |                                        |          | t each of 3 RGB<br>nber and n = weig   | ports selects up to 8-l<br>ght selected.       | ev-   |          |           |       |                 |             |  |

| C30<br>C22                               | 209<br>210 |        |                      | INPUT OUTPUT                                                                                                                                                                                                                                                                                                             |                            |                                 | UT                                     |          |                                        |                                                |       |          |           |       |                 |             |  |

| C21 211<br>C20 212<br>C12 213<br>C11 214 |            |        |                      | C32<br>C22<br>C12                                                                                                                                                                                                                                                                                                        | C31<br>C21<br>C11          | C30<br>C20<br>C10               | DSEL =<br>(Noninver                    |          | DESEL = H<br>(Inverted)                |                                                |       |          |           |       |                 |             |  |

| C10                                      | 214<br>215 |        |                      | 1<br>1<br>1<br>0<br>0<br>0                                                                                                                                                                                                                                                                                               | 1<br>1<br>0<br>1<br>1<br>0 | 1<br>0<br>1<br>0<br>1<br>0<br>1 | V7<br>V6<br>V5<br>V4<br>V3<br>V2<br>V1 |          | V0<br>V1<br>V2<br>V3<br>V4<br>V5<br>V6 |                                                |       |          |           |       |                 |             |  |

|                                          |            |        |                      | 0                                                                                                                                                                                                                                                                                                                        | 0                          | 0                               | VO                                     |          | V0<br>V7                               | ]                                              |       |          |           |       |                 |             |  |

| CL                                       | 217        | 1      |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 |                                        |          |                                        | gister, data memory, a<br>or normal operation. | and   |          |           |       |                 |             |  |

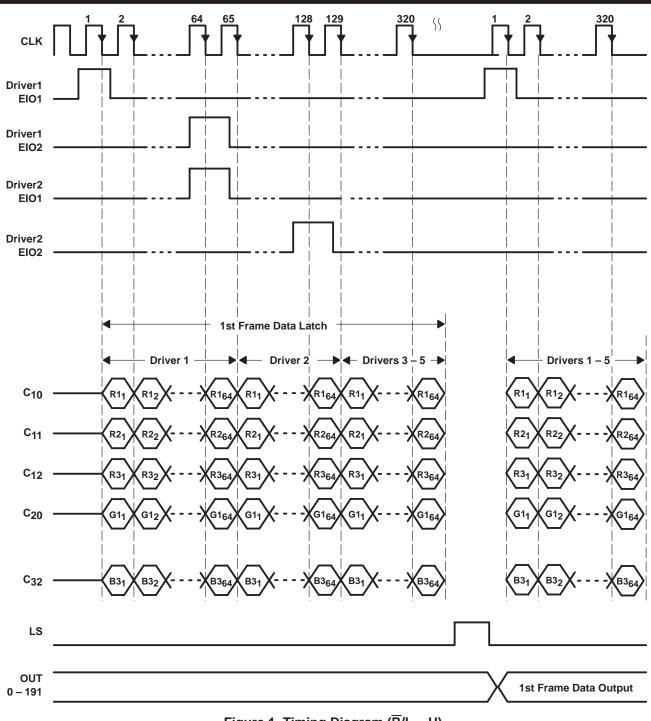

| CLK                                      | 216        | I      | stored in            | Clock input. CLK is the rising edge systems clock for the 64-bit shift register. Also, 9 bits of data are stored in the data memory by the falling edge of CLK. The clock control circuit stops the internal system clock to save power consumption after 64 clocks.                                                     |                            |                                 |                                        |          |                                        |                                                |       |          |           |       |                 |             |  |

| DSEL                                     | 205        | 205 I  | Data sele            | ect input. T                                                                                                                                                                                                                                                                                                             | his input                  | inverts the                     | data on C10 t                          | to C32   | input.                                 |                                                |       |          |           |       |                 |             |  |

|                                          |            |        |                      |                                                                                                                                                                                                                                                                                                                          | INPUT D                    | DATA                            | DAT                                    | A MEMORY |                                        |                                                |       |          |           |       |                 |             |  |

|                                          |            |        |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 |                                        |          |                                        | C10 to                                         | C32 [ | DSEL = L | DSEL =    | н     |                 |             |  |

|                                          |            |        |                      | 0                                                                                                                                                                                                                                                                                                                        |                            | 0                               | 1                                      |          |                                        |                                                |       |          |           |       |                 |             |  |

|                                          |            |        |                      | 1                                                                                                                                                                                                                                                                                                                        |                            | 1                               | 0                                      |          | l                                      |                                                |       |          |           |       |                 |             |  |

| EIO1                                     | 219        | I/O    | Enable I/            | O. EIO1 a                                                                                                                                                                                                                                                                                                                | nd EIO2 a                  | are data en                     | able input/out                         | put for  | cascade interface                      | Э.                                             |       |          |           |       |                 |             |  |

| EIO2                                     | 204        |        |                      |                                                                                                                                                                                                                                                                                                                          | R/L                        |                                 | EIO1                                   |          | EIO2                                   |                                                |       |          |           |       |                 |             |  |

|                                          |            |        |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 |                                        |          |                                        | H (Left S                                      | hift) | Casc     | ade Input | Casca | ade Output (OUT | 0 – OUT191) |  |

|                                          |            |        |                      | L (Right S                                                                                                                                                                                                                                                                                                               | Shift)                     | Casc                            | ade Output                             | Casca    | ade Input (OUT19                       | 91 – OUT0)                                     |       |          |           |       |                 |             |  |

| LS                                       | 218        | I      | 192) and             | Latch Strobe Input. When LS is high, 9 x 64 bits of data memory is latched into the display latch (3 x 192) and passed through a 3-to-8 decoder. The decoder selects one of eight bias voltage $V0 - V7$ to be passed on to OUTn using a transmission gate. LS also clears the shift register and clock control circuit. |                            |                                 |                                        |          |                                        |                                                |       |          |           |       |                 |             |  |

| MODE                                     | 231        | 1      | Mode inp<br>connecte | Mode input. MODE is used for factory testing only and should be left open. The internal pullup resistors connected to V <sub>DD</sub> force the inputs into a high state.                                                                                                                                                |                            |                                 |                                        |          |                                        |                                                |       |          |           |       |                 |             |  |

| OUT0 –<br>OUT191                         | 1 – 192    | 0      |                      |                                                                                                                                                                                                                                                                                                                          |                            |                                 | display. C1x,<br>where n = 0 -         |          |                                        | s voltages, V0 – V7, o                         | on    |          |           |       |                 |             |  |

SGLS092 - MARCH 1997

## **Terminal Functions (continued)**

| NAME                                 | TERMINAL               | I/O |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FUI                                                           | NCTION                                               |                         |  |  |  |  |

|--------------------------------------|------------------------|-----|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|-------------------------|--|--|--|--|

| R/L                                  | 221                    | I   | shift regis<br>three diff<br>three at a | elect right/left shift. $\overline{R}/L$ selects which direction the EIOn enable pulse advances through the 64-bit<br>ift register. It also selects which direction the 3-bit $\times$ 3 RGB data from the data latch is loaded into<br>ree different but adjacent channels of data memory. This data is loaded as the channels are enabled<br>ree at a time by the enable pulse from the shift register. It advances from one output to the next when<br>ifting through the shift register with each clock pulse. |                                                               |                                                      |                         |  |  |  |  |

|                                      |                        |     |                                         | R/L H L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |                                                      |                         |  |  |  |  |

|                                      |                        |     |                                         | Shift Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Left                                                          | Right                                                |                         |  |  |  |  |

|                                      |                        |     |                                         | EIO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Input                                                         | Output                                               |                         |  |  |  |  |

|                                      |                        |     |                                         | EIO2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output                                                        | Input                                                |                         |  |  |  |  |

|                                      |                        |     |                                         | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1, 2, 3, 64                                                   | 1, 2, 3, 64                                          |                         |  |  |  |  |

|                                      |                        |     |                                         | C32 – C30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2, 5, 8, 191                                                  | 191, 188, 185, 2                                     |                         |  |  |  |  |

|                                      |                        |     |                                         | C22 – C20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1, 4, 7, 190                                                  | 190, 187, 184, 1                                     |                         |  |  |  |  |

|                                      |                        |     |                                         | C12 – C10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0, 3, 6, 189                                                  | 189, 186, 183, 0                                     | ļ                       |  |  |  |  |

| TEST1<br>TEST2                       | 193<br>194             | I   |                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ST2 are used for factor<br>to V <sub>DD</sub> force the input | y testing only and should be<br>s into a high state. | left open. The internal |  |  |  |  |

| V0 – V7<br>V0 – V7                   | 202 – 195<br>223 – 230 | I   | device ou<br>the V0 to                  | Eight-level input bias voltage for output buffer. After the three bits for each RGB color are decoded, the evice outputs one voltage level from the eight possible bias voltages ( $V0 - V7$ ). There is no priority on the V0 to V7 terminals. A pair of V0 to V7 bias voltage terminals are provided. Each pair of terminals is equired to be connected together externally.                                                                                                                                     |                                                               |                                                      |                         |  |  |  |  |

| V <sub>DD</sub>                      | 206                    |     | 5-V supp                                | ly input for logic o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | circuits                                                      |                                                      |                         |  |  |  |  |

| VEE                                  | 222                    |     | Supply in                               | Supply input for level shifter and output transmission gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                               |                                                      |                         |  |  |  |  |

| V <sub>SS1</sub><br>V <sub>SS2</sub> | 220<br>203             |     | Ground t                                | Ground terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                               |                                                      |                         |  |  |  |  |

SGLS092 - MARCH 1997

#### SGLS092 - MARCH 1997

### absolute maximum ratings over operating free-air temperature range<sup>†</sup>

| Supply voltage range, V <sub>DD</sub> (see Note 1)                                                                   |

|----------------------------------------------------------------------------------------------------------------------|

| Input voltage range, V <sub>I</sub> (CLK, LS, R/L, CL, C32 to C10, DSEL, EIO1, EIO2)0.3 V to V <sub>DD</sub> + 0.3 V |

| Output voltage range, V <sub>O</sub> (E101, E102) $-0.3$ V to V <sub>DD</sub> + 0.3 V                                |

| Output bias voltage range for LCD, Vx $-0.6$ V to V <sub>DD</sub> + 0.6 V                                            |

| Input current, I <sub>1</sub> ± 10 mA                                                                                |

| Output current, I <sub>O:</sub> E101, E102                                                                           |

| OUT0 to OUT191 5 mA                                                                                                  |

| Power dissipation, P <sub>D</sub> 0.3 W                                                                              |

| Operating free-air temperature range, T <sub>A</sub>                                                                 |

| Storage temperature range, T <sub>stg</sub>                                                                          |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: Voltage values are with respect to V<sub>SS1</sub> and V<sub>SS2</sub>

#### recommended operating conditions

|                                                |                                                | MIN                 | NOM | MAX                 | UNIT |

|------------------------------------------------|------------------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>DD</sub>                | See Note 2                                     | 4.5                 | 5   | 5.5                 | V    |

| Supply voltage, VEE                            | See Note 2                                     | 14                  |     | 18                  | V    |

| Output bias voltage for LCD driver             | V0, V1, V2, V3, V4, V5, V6, V7<br>See Note 2   | 0                   |     | $V_{EE}$            | V    |

| High-level input voltage, VIH                  | CLK, LS, DSEL, R/L, CL, EIO1, EIO2, C32 to C10 | 0.8 V <sub>DD</sub> |     | V <sub>DD</sub>     | V    |

| Low-level input voltage, VIL                   | CLK, LS, DSEL, R/L, CL, EIO1, EIO2, C32 to C10 | VSS                 |     | 0.2 V <sub>DD</sub> | V    |

| Clock frequency at CLK, f(CLK)                 | CLK                                            |                     |     | 15                  | MHZ  |

| Clock frequency at LS, f(LS)                   | LS                                             |                     |     | 100                 | kHz  |

| Operating free-air temperature, T <sub>A</sub> |                                                | -55                 |     | 125                 | °C   |

NOTE 2: Turn-on and -off sequence of power must be as follows: Turn-on sequence:  $V_{DD} \rightarrow Logic Input \rightarrow V_{EE} \rightarrow V7$  to V0 Turn-off sequence: V7 to V0  $\rightarrow V_{EE} \rightarrow Input \rightarrow V_{DD}$

SGLS092 - MARCH 1997

|                    | PARAMETER                                                   |                                                                       | TEST CONDITIONS                                                                                                                                                                 | MIN                  | MAX | UNIT |

|--------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|

| VOH                | High-level output voltage                                   | E101, E102                                                            | I <sub>OH</sub> = -0.3 mA                                                                                                                                                       | V <sub>DD</sub> -0.4 |     | V    |

| VOL                | Low-level output voltage                                    | E101, E102                                                            | I <sub>OH</sub> = 0.3 mA                                                                                                                                                        |                      | 0.4 | V    |

| Ι <sub>ΙΗ</sub>    | High-level input current                                    | <u>C</u> LK <u>, D</u> SEL, LS,<br>R/L, CL, EIO1,<br>EIO2, C32 to C10 | $V_{IH} = V_{DD}$                                                                                                                                                               |                      | 10  | μΑ   |

| Ι <sub>ΙL</sub>    | Low-level input current                                     | <u>C</u> LK <u>, D</u> SEL, LS,<br>R/L, CL, EIO1,<br>EIO2, C32 to C10 | V <sub>IL</sub> = V <sub>SS</sub>                                                                                                                                               |                      | 10  | μΑ   |

| l <sub>lkg</sub>   | Input leakage current                                       | V7 to V0                                                              | V <sub>SS</sub> < Vx < V <sub>EE</sub>                                                                                                                                          | -100                 | 100 | μA   |

| ΔVIO               | Voltage difference between<br>Vx to OUTn (voltage variance) | Vx - OUTn                                                             | $I_{I/O} = \pm 10 \ \mu A$ , $V_{SS} < Vx < V_{EE}$                                                                                                                             |                      | 50  | mV   |

| R <sub>o(on)</sub> | Output resistance                                           | OUT0 – OUT191                                                         | $I_{O} = \pm 100 \ \mu A$                                                                                                                                                       |                      | 5   | kΩ   |

| I <sub>DD</sub>    | Supply current                                              | V <sub>DD</sub>                                                       | $ \begin{array}{ll} f_{(CLK)} = 15 \mbox{ MHZ}, & f_{(ElOxin)} = 30 \mbox{ KHZ}, \\ f_{(LS)} = 30 \mbox{ KHZ}, & V_{DD} = 5.5 \mbox{ V}, \\ V_{EE} = 18 \mbox{ V} \end{array} $ |                      | 4   | mA   |

| IEE                | Supply current                                              | V <sub>EE</sub>                                                       | $ \begin{array}{ll} f_{(CLK)} = 15 \mbox{ MHZ}, & f_{(ElOxin)} = 30 \mbox{ KHZ}, \\ f_{(LS)} = 30 \mbox{ KHZ}, & V_{DD} = 5 \mbox{ V}, \\ V_{EE} = 17 \mbox{ V} \end{array} $   |                      | 1   | mA   |

| h                  | Standby ourrent                                             | V <sub>DD</sub>                                                       | V <sub>DD</sub> = 5 V, V <sub>EE</sub> = 17 V<br>See Note 3                                                                                                                     |                      | 300 | μΑ   |

| I(standby)         | Standby current                                             | V <sub>EE</sub>                                                       | V <sub>DD</sub> = 5 V, V <sub>EE</sub> = 17 V<br>See Note 3                                                                                                                     |                      | 100 | μΑ   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

NOTE 3: Test conditions of standby current are added at  $\overline{R}/L = V_{DD}$ , and EIO1 = V<sub>SS</sub>.

## timing requirements, $V_{DD}$ = 5 V, $T_A$ = –55°C to 125°C

|                        | PARAMETER                           |             | TEST CONDITIONS     | MIN    | MAX                      | UNIT |

|------------------------|-------------------------------------|-------------|---------------------|--------|--------------------------|------|

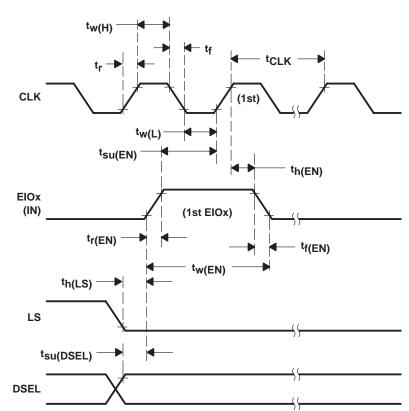

| <sup>t</sup> CLK       | Clock cycle time                    |             | See Figures 2 and 4 | 66     |                          | ns   |

| <sup>t</sup> W(L)      | Low-level pulse width               | CLK         | See Figure 2        | 23     |                          | ns   |

| <sup>t</sup> w(H)      | High-level pulse width              |             | See Figure 2        | 18     |                          | ns   |

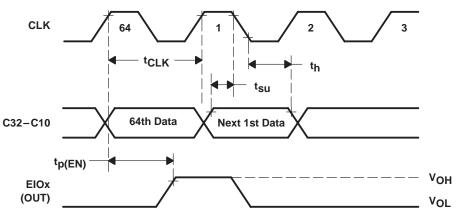

| t <sub>su</sub>        | Data setup time                     | Cxx – CLK   | See Figure 4        | 10     |                          | ns   |

| t <sub>h</sub>         | Data hold time                      | CLK – Cxx   | See Figure 4        | 15     |                          | ns   |

| <sup>t</sup> w(EN)     | Enable high-level pulse width       | EIO1, EIO2  | See Figure 2        | 1/fCLK |                          | ns   |

| <sup>t</sup> su(EN)    | Enable setup time                   | EIOx – CLK  | See Figure 2        | 20     | 30 or<br>1/fCLK          | ns   |

| <sup>t</sup> h(EN)     | Enable hold time                    | CLK – ElOx  | See Figure 2        | 10     | <sup>t</sup> CLK ×<br>62 | ns   |

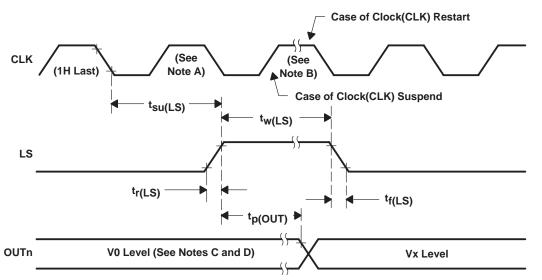

| <sup>t</sup> w(LS)     | Latch strobe high-level pulse width |             | See Figure 3        | 40     |                          | ns   |

| t <sub>su(LS)</sub>    | LS setup time                       | LS          | See Figure 3        | 66     |                          | ns   |

| <sup>t</sup> h(LS)     | LS hold time                        |             | See Figure 2        | 40     |                          | ns   |

| t <sub>su</sub> (DSEL) | DSEL setup time                     | ElOx – DSEL | See Figure 2        | 66     |                          | ns   |

SGLS092 - MARCH 1997

# switching characteristics, $V_{DD}$ = 5 V, $T_A$ = –55°C to 125°C over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                     | TEST CONDITIONS | MIN                                                 | MAX | UNIT |    |

|---------------------|-------------------------------|-----------------|-----------------------------------------------------|-----|------|----|

| <sup>t</sup> p(EN)  | Enable propagation delay time | CLK – EIOx      | C <sub>L</sub> = 35 pF,<br>See Note 4 and Figure 4  |     | 40   | ns |

| <sup>t</sup> p(OUT) | Output propagation delay time | LS – OUTn       | C <sub>L</sub> = 200 pF,<br>See Note 4 and Figure 3 |     | 3.0  | μs |

NOTE 4: CL includes probe and jig capacitance.

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. Input pulse generators have the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%, t<sub>f</sub>  $\leq$  15 ns, t<sub>f</sub>  $\leq$  15 ns, z<sub>0</sub> = 50  $\Omega$ . B. V<sub>IH</sub> and V<sub>IL</sub> for all waveforms are at 0.8 V<sub>DD</sub> and 0.2 V<sub>DD</sub> respectively.

- C. All timing parameters and measurements are referenced at the 0.5 V<sub>DD</sub> point of each waveform.

Figure 2. EIOx (IN), LS, and DSEL Timing Waveforms

SGLS092 - MARCH 1997

## PARAMETER MEASUREMENT INFORMATION

- NOTES: A. Case of data input change: if data has changed after the last clock of 1H, then it is recommended to add a dummy clock of one pulse after the last 1H pulse of the clock.

- B. Case of suspending clock (CLK) after data transfer (1H) completion: it is recommended that the data input not be changed while the clock is suspended.

- C. All timing parameters and measurements are referenced at the 0.5 V<sub>DD</sub> point of each waveform except t<sub>p(OUT)</sub> on the OUTn waveform. The reference point on the OUTn waveform is V0+0.1 Vx for positive-going transitions and V0-0.1 Vx for negative-going transitions.

- D. OUTn waveform transitions are from V0 level to Vx level. Maximum V0 and Vx levels are 8.0 V due to tester limitations.

- E. Input pulse generators have the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%, t<sub>f</sub>  $\leq$  15 ns, t<sub>f</sub>  $\leq$  15 ns, z<sub>O</sub> = 50  $\Omega$ .

- F. VIH and VIL for all waveforms are at 0.8 VDD and 0.2 VDD respectively.

#### Figure 3. LS and OUTn Timing Waveforms

NOTES: A. Input pulse generators have the following characteristics: PRR  $\leq$  1 MHz, duty cycle  $\leq$  50%, t<sub>f</sub>  $\leq$  15 ns, t<sub>f</sub>  $\leq$  15 ns, z<sub>0</sub> = 50  $\Omega$ . B. V<sub>IH</sub> and V<sub>IL</sub> for all waveforms are at 0.8 V<sub>DD</sub> and 0.2 V<sub>DD</sub> respectively.

C. All timing parameters and measurements are referenced at the 0.5 V<sub>DD</sub> point of each waveform.

#### Figure 4. Cxx and EIOx (OUT) Timing Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated