# **MPX2003**

Up to 140kHz All-in-One Flyback Controller with Integrated Primary Control Circuitry and Secondary Synchronous Rectification Driver

#### DESCRIPTION

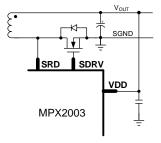

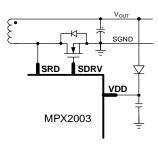

The MPX2003 is an all-in-one flyback controller with an integrated primary driving circuit, secondary controller, synchronous rectification driver, and safety-compliant feedback. It offers the benefits of both primary-side regulation (PSR) and secondary-side regulation (SSR).

A feedback circuit is not required, which reduces system complexity and the total BOM cost. The synchronous rectifier (SR) can match the driving signal of the primary-side MOSFET, meaning the SR can operate safely in continuous conduction mode (CCM). Meanwhile, the integrated SR controller regulates the SR MOSFET at a low threshold, which increases the overall efficiency and design flexibility. An internal linear regulator is integrated for the SR power supply, so the MPX2003 can drive the low-side SR MOSFET without auxiliary winding, even when the output is low.

The MPX2003 can run in CCM under heavy loads, then operate in quasi-resonant (QR) mode when the load decreases. If the load drops further, the MPX2003 works in pulse-frequency modulation (PFM) mode. The switching frequency (fsw) is fixed at 20kHz when the device enters burst mode, which can prevent audible noise. The MPX2003 achieves high efficiency under most load conditions while improving electromagnetic interference (EMI) performance.

The MPX2003 features advanced protections, including  $V_{CC}$  over-voltage protection (OVP), primary over-current protection (POCP), secondary-sense output overload protection (OLP), internal brown-in/brownout (B/I, B/O), short-circuit protection (SCP), current-sense short protection (SSP), current-sense open protection (SOP), SR gate open/short protection (SGOP/SGSP), SRD abnormal protection (SRDP), FB OVP and under-voltage protection (UVP), internal thermal shutdown, under-voltage lockout (UVLO), and an externally triggered protection (Ext.P).

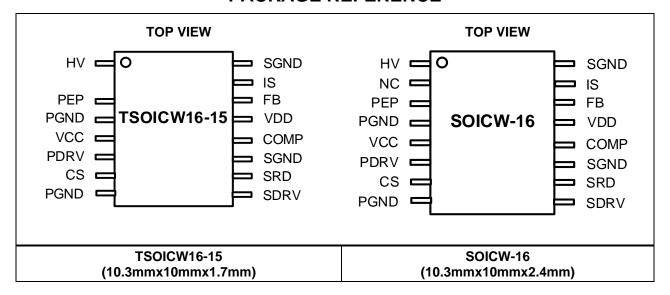

The MPX2003 is available in SOICW-16 and TSOICW16-15 packages.

#### **FEATURES**

- Isolation Voltage >3750V<sub>AC</sub>

- 100% Production HIPOT Compliance Testing

- UL1577 and IEC62368 Safety Approved, DIN VDE V 0884-17 in Process

- Integrated Multi-Mode: Discontinuous Conduction Mode (DCM), Quasi-Resonant (QR) Mode, and Continuous Conduction Mode (CCM)

- Flyback Controller, Secondary-Side Synchronous Rectifier (SR) Sensing/Driving Circuitry, and Safety-Compliant Feedback Link

- Integrated 650V Primary-Side Current Source and 150V Secondary-Side Current Source

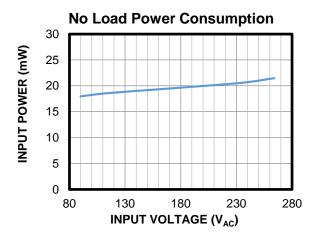

- Less than 30mW in Standby Mode

- Improved SR Control for Reliable Operation and Higher Efficiency

- V<sub>CC</sub> Over-Voltage Protection (OVP), Primary Over-Current Protection (POCP), Secondary-Sense Output Overload Protection (OLP), Internal Brown-In/Brownout (B/O, B/I), Short-Circuit Protection (SCP), Current-Sense Short Protection (SSP), Current-Sense Open Protection (SOP), SR Gate Open/Short Protection (SGOP/SGSP), SRD Abnormal Protection (SRDP), FB OVP and Under-Voltage Protection (UVP), Internal Thermal Shutdown, Under-Voltage Lockout (UVLO), and an Externally Triggered Protection (Ext.P)

- Available in TSOICW16-15 and SOICW-16 Packages

#### **APPLICATIONS**

- High-Performance USB PD Adapters

- Offline Battery Chargers

- High Efficiency, High-Current Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

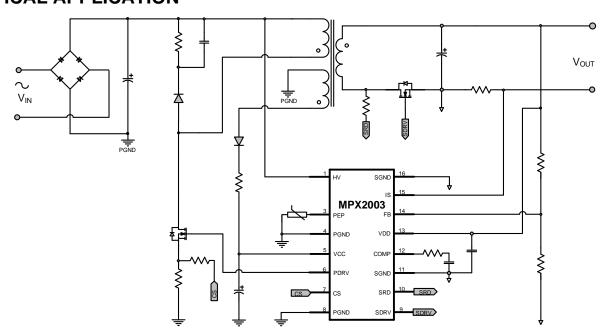

# **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number* | Package     | Top Marking | MSL Rating |

|--------------|-------------|-------------|------------|

| MPX2003GYT   | TSOICW16-15 | Soo Polow   | 2          |

| MPX2003GY    | SOICW-16    | See Below   | S          |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPX2003GYT-Z, MPX2003GY-Z).

# TOP MARKING MPSYYWW MPX2003 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MPX2003: Part num

MPX2003: Part number LLLLLLLL: Lot number

#### **PACKAGE REFERENCE**

# **PIN FUNCTIONS**

| Pin #       |          | Nama | De a suintia n                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TSOICW16-15 | SOICW-16 | Name | Description                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 1           | 1        | HV   | <b>High voltage.</b> The HV pin implements an internal, high-voltage current source for the primary IC's start-up sequence and normal operation. HV samples the input voltage for brown-in/brownout protection and provides line compensation on the primary peak current.                                                                                                  |  |  |

| -           | 2        | NC   | No connection.                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 3           | 3        | PEP  | <b>External protection on the primary IC.</b> The PEP pin provides external protections. Protections include but are not limited to over-temperature protection (OTP) for the primary MOSFET and over-voltage protection (OVP) on the auxiliary winding. An internal current source allows for a direct connection between the external protection circuit and the PEP pin. |  |  |

| 4           | 4        | PGND | Ground of the primary-side IC.                                                                                                                                                                                                                                                                                                                                              |  |  |

| 5           | 5        | VCC  | <b>Power supply for the primary IC operation.</b> The VCC pin senses the output voltage (V <sub>OUT</sub> ) indirectly to provide over-voltage protection (OVP).                                                                                                                                                                                                            |  |  |

| 6           | 6        | PDRV | Output drive for the primary-side external power MOSFET.                                                                                                                                                                                                                                                                                                                    |  |  |

| 7           | 7        | CS   | <b>Primary MOSFET current sense for peak current mode regulation and SCP.</b> The CS pin implements over-power compensation based on the HV voltage.                                                                                                                                                                                                                        |  |  |

| 8           | 8        | PGND | Ground of the primary-side IC.                                                                                                                                                                                                                                                                                                                                              |  |  |

| 9           | 9        | SDRV | Output drive for the secondary-side external power MOSFET.                                                                                                                                                                                                                                                                                                                  |  |  |

| 10          | 10       | SRD  | <b>Voltage-sense drain of the synchronous rectifier MOSFET.</b> The voltage on the SRD pin controls the SR drive and QR operation. This pin can also supply power to VDD.                                                                                                                                                                                                   |  |  |

| 11          | 11       | SGND | Ground of the secondary side IC.                                                                                                                                                                                                                                                                                                                                            |  |  |

| 12          | 12       | COMP | Internal error amplifier for output voltage regulation. Connect the compensation network to the COMP pin to adjust the regulating performance. COMP can be configured as an external compensation network. The COMP voltage can be monitored for secondary overload protection (SOLP).                                                                                      |  |  |

| 13          | 13       | VDD  | Power supply for the secondary IC operation.                                                                                                                                                                                                                                                                                                                                |  |  |

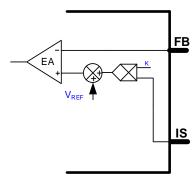

| 14          | 14       | FB   | <b>Feedback for constant voltage regulation.</b> Connect FB to a resistor divider to sense Vout. FB can be reused to achieve output OVP and OLP.                                                                                                                                                                                                                            |  |  |

| 15          | 15       | IS   | <b>Output current sense.</b> IS senses the output current ( $I_{OUT}$ ) when a current-sense resistor is connected to the output loop. This also provides accurate overload protection (OLP). In addition, the IS voltage can be used for cable drop compensation.                                                                                                          |  |  |

| 16          | 16       | SGND | Ground of the secondary side IC.                                                                                                                                                                                                                                                                                                                                            |  |  |

##

# Recommended Operating Conditions (3)

| Operating junction temp (T <sub>J</sub> ) | )40°C to +125°C |

|-------------------------------------------|-----------------|

| VCC to PGND                               | 9.5V to 24V     |

| VDD to SGND                               | 4.8V to 30V     |

| Thermal Resistance (4) | $oldsymbol{	heta}$ JA | $oldsymbol{	heta}$ JC |

|------------------------|-----------------------|-----------------------|

| TSOICW16-15            | 45                    | 18 °C/W               |

| SOICW-16               | 44                    | 24 °C/W               |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J</sub> (MAX), the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX) T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation can produce an excessive die temperature, and the regulator may go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

5

4) Measured on JESD51-7, 4-layer PCB.

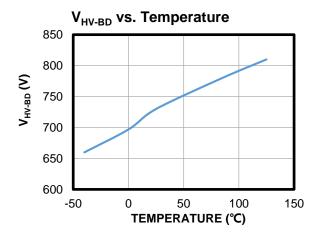

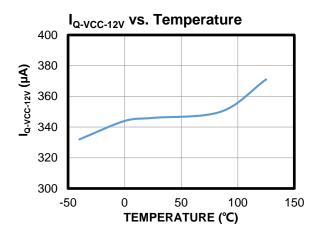

# **ELECTRICAL CHARACTERISTICS**

Typical values tested at  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

| Parameter                           | Symbol                                | Condition                                                                | Min  | Тур  | Max | Units             |

|-------------------------------------|---------------------------------------|--------------------------------------------------------------------------|------|------|-----|-------------------|

| Insulation                          |                                       |                                                                          |      | •    |     | •                 |

| Isolation voltage                   | V <sub>ISO</sub>                      | 50Hz/60Hz                                                                | 3.75 |      |     | kV <sub>RMS</sub> |

| Primary Side (HV)                   | •                                     |                                                                          |      | •    |     |                   |

| Breakdown voltage                   | $V_{HV	ext{-}BD}$                     | T <sub>J</sub> = 25°C                                                    | 650  |      |     | V                 |

| Leakage current from HV             | I <sub>HV-LK</sub>                    | V <sub>HV</sub> = 500V <sub>DC</sub>                                     |      | 7    | 11  | μA                |

| -                                   |                                       | V <sub>CC</sub> = 12V, V <sub>HV</sub> = 80V, T <sub>J</sub> = 25°C      | 4.5  | 5.5  | 6.5 | -                 |

|                                     | HV-SP1                                | V <sub>CC</sub> = 12V, V <sub>HV</sub> = 80V, T <sub>J</sub> = 105°C     | 3.1  | 3.8  | 4.6 |                   |

| Supply current from HV              |                                       | V <sub>CC</sub> = 1.5V, V <sub>HV</sub> = 80V, T <sub>J</sub> = 25°C     |      | 3.7  |     | mA                |

|                                     | I <sub>HV-SP2</sub>                   | V <sub>CC</sub> = 1.5V, V <sub>HV</sub> = 80V,<br>T <sub>J</sub> = 105°C |      | 3.1  |     |                   |

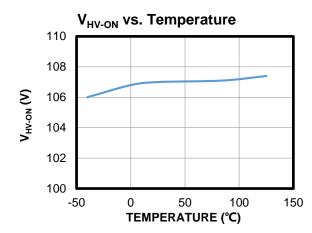

| Brown-in threshold voltage          | V <sub>HV-ON</sub>                    |                                                                          | 95   | 107  | 120 | V                 |

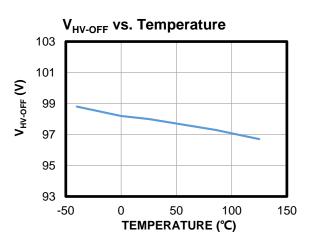

| Brownout threshold voltage          | V <sub>HV-OFF</sub>                   |                                                                          | 85   | 98   | 110 | V                 |

| Brown-in/out hysteresis             | V <sub>HV-Δ</sub>                     |                                                                          |      | 8.5  |     | V                 |

| Delay time for brownout             | t <sub>BO</sub>                       |                                                                          | 45   | 55   | 67  | ms                |

| Primary Side (VCC)                  | •                                     |                                                                          |      | •    |     |                   |

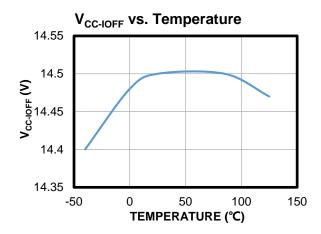

| I <sub>HV-SP</sub> turn-off voltage | V <sub>CC-IOFF</sub>                  |                                                                          | 13   | 14.5 | 16  | V                 |

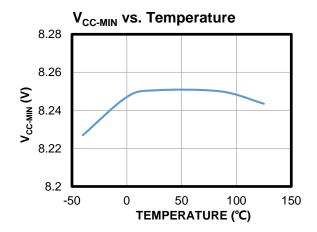

| Minimum operation voltage           | Vcc-min                               |                                                                          | 7.3  | 8.3  | 9.3 | V                 |

| Vcc-IOFF - Vcc-MIN                  | Vcc-stw                               |                                                                          | 5.2  | 6.2  | 7.2 | V                 |

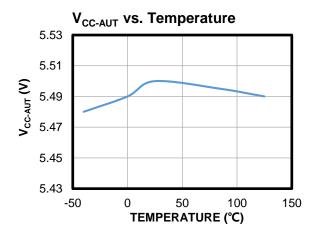

| Auto-recovery protection level      | Vcc-aut                               |                                                                          | 4.9  | 5.5  | 6.1 | V                 |

| Over-voltage protection (OVP) level | Vcc-ovp                               |                                                                          | 24   | 26   | 28  | V                 |

| V <sub>CC</sub> OVP delay time      | t <sub>VCC-OVP</sub>                  |                                                                          |      | 32   |     | μs                |

| Operating current                   | I <sub>OP</sub>                       | $V_{CC} = 15V$ , $f_{SW} = 140kHz$ , $C_L = 1nF$                         |      |      | 5   | mA                |

| Operating current during a          |                                       | V <sub>CC</sub> = 10V, except B/O                                        |      |      | 120 | μA                |

| protection                          | I <sub>OP-PRO</sub>                   | Vcc = 10V, B/O                                                           | 1    |      |     | mA                |

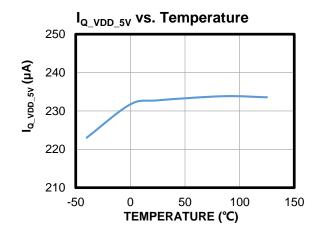

| Quiescent current                   | ΙQ                                    | Vcc = 12V                                                                |      |      | 500 | μA                |

| Primary Side (PDRV)                 | •                                     |                                                                          |      | •    |     | •                 |

| Daharan akana biah lawal            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | $C_L = 1$ nF, $V_{CC} = V_{CC-MIN} + 0.1$ V                              | 5.8  |      |     | V                 |

| Driver voltage high level           | VHIGH                                 | C <sub>L</sub> = 1nF, V <sub>CC</sub> = 12V                              | 9.6  |      |     | V                 |

| Driver voltage clamp level          | VCLAMP                                | C <sub>L</sub> = 1nF, V <sub>CC</sub> = 24V                              | 11.5 | 14.5 | 16  | V                 |

| Driver voltage low level            | $V_{LOW}$                             | C <sub>L</sub> = 1nF                                                     |      |      | 100 | mV                |

| Driver voltage rising time          | t <sub>RISE</sub>                     | C <sub>L</sub> = 1nF                                                     |      | 20   |     | ns                |

| Driver voltage falling time         | t <sub>FALL</sub>                     | C <sub>L</sub> = 1nF                                                     |      | 18   |     | ns                |

© 2022 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued)

Typical values tested at  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

| Parameter                                                                          | Symbol               | Condition                                                             | Min   | Тур   | Max   | Units    |

|------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------|-------|-------|-------|----------|

| Maximum switching frequency                                                        | fsw-max              |                                                                       |       | 110   |       | kHz      |

| Maximum on time                                                                    | ton-max              |                                                                       |       | 6.5   |       | μs       |

| Minimum off time                                                                   | t <sub>OFF-MIN</sub> |                                                                       |       | 1000  |       | ns       |

| Time to trigger primary OCP                                                        | tocp                 |                                                                       | 45    | 55    | 68    | ms       |

| Minimal switching frequency during soft start                                      | f <sub>SW-SOFT</sub> |                                                                       |       | 10    |       | kHz      |

| Primary Side (CS)                                                                  |                      |                                                                       |       |       |       |          |

| Soft-start duration                                                                | tsoft                |                                                                       |       | 9.6   |       | ms       |

| Threshold for SCP                                                                  | V <sub>SCP</sub>     |                                                                       | 0.595 | 0.635 | 0.675 | V        |

| Second SCP blanking time                                                           | t <sub>SCP2</sub>    |                                                                       |       | 90    |       | μs       |

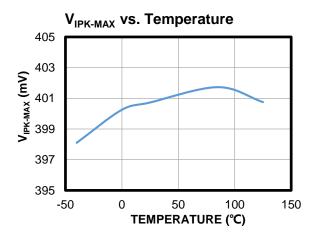

| Maximum peak current limitation                                                    | VIPK-MAX             |                                                                       | 0.384 | 0.4   | 0.416 | V        |

| Minimum peak current limitation                                                    | VIPK-MIN             |                                                                       |       | 0.1   |       | V        |

| Jittering amplitude                                                                | $\Delta V_{IPK}$     | VIPK = VIPK-MAX                                                       |       | ±2.9% |       | VIPK-MAX |

| Jittering period (5)                                                               |                      |                                                                       |       | 256   |       | cycles   |

| f <sub>SW</sub> at which I <sub>PK</sub> foldback begins                           | fsw-н                |                                                                       |       | 60    |       | kHz      |

| Slope of the compensation ramp                                                     | S <sub>RAMP</sub>    |                                                                       |       | 25    |       | mV/µs    |

| LEB for current limitation                                                         | t <sub>LEB-L</sub>   |                                                                       |       | 400   |       | ns       |

| LEB for SCP                                                                        | t <sub>LEB-S</sub>   |                                                                       |       | 250   |       | ns       |

| ΔI <sub>HVCS</sub> / ΔV <sub>HV</sub> Ratio                                        | K <sub>HVCs</sub>    |                                                                       |       | 0.53  |       | μA/V     |

| CS sourcing current                                                                | liusee               | $V_{HV} = 200V, \ V_{IPK} = V_{IPK\text{-MAX}}, \ T_J = 25^{\circ}C$  |       | 36    |       |          |

| C3 Sourcing current                                                                | Invcs                | $V_{HV} = 375V, \ V_{IPK} = V_{IPK\text{-MAX}}, \\ T_J = 25^{\circ}C$ | 100   | 126   | 152   | μA       |

| V <sub>IPK</sub> (below which line compensation completely removed) <sup>(5)</sup> | VLC-END              |                                                                       | 0.15  |       |       | V        |

| Detection time for CS short                                                        | t <sub>SSP</sub>     |                                                                       | 3     | 4.5   | 6     | μs       |

| Threshold for CS short                                                             | Vcss                 | During the soft-start period                                          |       | 50    |       | mV       |

| Primary Side (PEP)                                                                 |                      |                                                                       |       |       |       |          |

| Sourcing current from PEP                                                          | I <sub>PEP</sub>     | V <sub>PEP</sub> = 0.5V                                               |       | 110   |       | μA       |

| Protection trigger threshold                                                       | V <sub>PEP-T</sub>   |                                                                       | 0.425 | 0.5   | 0.575 | V        |

| Protection trigger delay                                                           | t <sub>PEP-T</sub>   |                                                                       |       | 300   |       | μs       |

© 2022 MPS. All Rights Reserved.

# **ELECTRICAL CHARACTERISTICS** (continued)

Typical values tested at  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

| Parameter                              | Symbol              | Condition                                                           | Min   | Тур   | Max   | Units            |

|----------------------------------------|---------------------|---------------------------------------------------------------------|-------|-------|-------|------------------|

| Primary Side – Internal The            | mal Protect         | ion                                                                 |       |       |       |                  |

| OTP threshold (5)                      | T <sub>OTP-P</sub>  |                                                                     |       | 150   |       | °C               |

| Hysteresis to recover from OTP (5)     | T <sub>Δ-P</sub>    |                                                                     |       | 40    |       | °C               |

| Secondary Side (VDD)                   |                     |                                                                     |       |       | 1     | I.               |

|                                        |                     | $V_{DD} = 5V$ , $f_{SW} = 140$ kHz, $C_L = 4.7$ nF                  |       |       | 7.5   |                  |

| Operating current                      | IOPS                | $V_{DD} = 12V$ , $f_{SW} = 140kHz$ , $C_L = 4.7nF$                  |       |       | 10    | mA               |

| Quiescent current                      | IQS                 | $V_{DD} = 5V$                                                       |       |       | 370   | μA               |

| UVLO falling threshold                 | V <sub>DD-OFF</sub> |                                                                     | 4.0   | 4.25  | 4.5   | V                |

| UVLO rising threshold                  | $V_{\text{DD-ON}}$  |                                                                     | 4.3   | 4.5   | 4.7   | V                |

| UVLO hysteresis                        | V <sub>DD-</sub>    |                                                                     |       | 0.3   |       | V                |

| Bleeding current during protection     | I <sub>BLD</sub>    |                                                                     |       | 10    |       | mA               |

| VDD ready threshold                    | V <sub>DD-RDY</sub> |                                                                     | 4.72  | 4.92  | 5.12  | V                |

| VDD clamp level when charged by SRD    | V <sub>DD-C</sub>   |                                                                     | 4.3   | 4.5   | 4.7   | V                |

| Secondary Side (FB)                    |                     |                                                                     |       |       |       |                  |

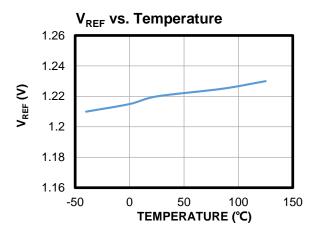

| Feedback reference voltage             | V <sub>REF</sub>    | T <sub>J</sub> = 25°C                                               | 1.21  | 1.22  | 1.23  | V                |

| Feedback current                       | I <sub>FB</sub>     | V <sub>FB</sub> = 1.22V, T <sub>J</sub> = 25°C                      |       |       | 50    | nA               |

| FBOLP threshold                        | V <sub>FBO</sub>    | V <sub>DD</sub> > V <sub>DD-RDY</sub>                               | 0.075 | 0.095 | 0.115 | V                |

| FBOLP delay time                       | t <sub>FBO</sub>    |                                                                     |       | 200   |       | μs               |

| OVP threshold                          | Vovp                |                                                                     | 113%  | 118%  | 123%  | V <sub>REF</sub> |

| OVP delay time                         | tovp-d              |                                                                     |       | 115   |       | μs               |

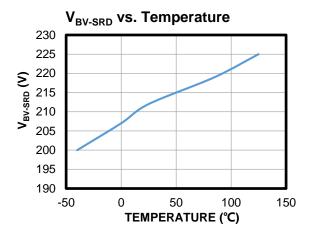

| Secondary Side (SRD)                   |                     |                                                                     | •     |       | •     | •                |

| Turn-on threshold                      | $V_{SR-ON}$         |                                                                     | -105  | -90   | -75   | mV               |

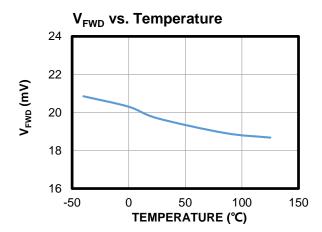

| Regulated forward voltage              | V <sub>FWD</sub>    |                                                                     | 8     | 20    | 32    | mV               |

| Turn-off threshold                     | V <sub>SR-OFF</sub> |                                                                     | -9    | 0     | 9     | mV               |

| Turn-off threshold in ton-min          | Vsr-offm            |                                                                     |       | 1.6   |       | V                |

| Input current at SRD pin               | I <sub>SRD-L</sub>  | V <sub>SRD</sub> = 30V                                              |       |       | 15    | μA               |

| Maximum charging current               |                     | $V_{SRD}=30V$ , $V_{DD}=0V$                                         |       | 50    |       | A                |

| to V <sub>DD</sub>                     | I <sub>SRD-C</sub>  | V <sub>SRD</sub> = 30V, V <sub>DD</sub> = V <sub>DD-ON</sub> - 0.5V |       | 75    |       | mA               |

| Threshold for driver open detection    | Vsgo                | T <sub>J</sub> = 25°C                                               | -0.52 | -0.47 | -0.42 | V                |

| Minimal time for driver open detection | tsgo                | DCM                                                                 |       | 0.5   |       | μs               |

| Secondary Side (SDRV)                  |                     |                                                                     |       |       |       |                  |

| Blanking for turn-on detection         | t <sub>SR-ONB</sub> |                                                                     | 270   | 400   | 570   | ns               |

| Turn-on delay                          | tsr-ond             | C <sub>L</sub> = 4.7nF                                              |       | 150   |       | ns               |

|                                        |                     |                                                                     |       |       |       |                  |

8

# **ELECTRICAL CHARACTERISTICS** (continued)

Typical values tested at  $T_J = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

| Parameter                                  | Symbol                 | Condition                     | Min  | Тур   | Max  | Units |

|--------------------------------------------|------------------------|-------------------------------|------|-------|------|-------|

| Turn-off delay                             | t <sub>SR-OFFD</sub>   | $C_L = 4.7 nF$                |      | 35    | 62   | ns    |

| Minimal on time                            | ton-min                |                               | 0.4  | 0.7   | 1    | μs    |

| Driver veltere levelevel                   |                        | $V_{DD} = V_{DD-OFF} + 0.1V$  |      |       | 0.1  | V     |

| Driver voltage low level                   | V <sub>DRV-L</sub>     | $V_{DD} = 5V$                 |      |       | 0.1  | ] V   |

|                                            |                        | $V_{DD} = V_{DD-OFF} + 0.1V$  | 4.1  | 4.3   | 4.6  |       |

| Driver veltage high level                  | V <sub>DRV-H</sub>     | $V_{DD} = 5V$                 |      | 5     |      | V     |

| Driver voltage high level                  | V DRV-H                | $V_{DD} = 12V$                | 9    |       | 10   | V     |

|                                            |                        | $V_{DD} = 24V$                | 9    |       | 10   |       |

| Max sourcing current (5)                   | Ison                   | $V_{DD} = 12V$                |      | 0.5   |      | Α     |

| Max sinking current (5)                    | Isoff                  | $V_{DD} = 12V$                |      | 3     |      | Α     |

| Driver pull-down resistance                | Rpull-down             | $C_L = 4.7 nF, V_{DD} = 12 V$ |      | 0.65  | 1.05 | Ω     |

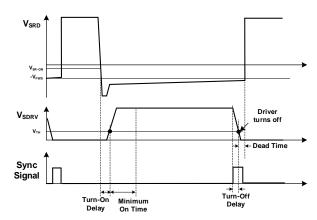

| Dead time under CCM conditions             | t <sub>DT</sub>        |                               |      | 15    |      | ns    |

| Secondary Side (IS)                        | •                      |                               | ·    |       |      |       |

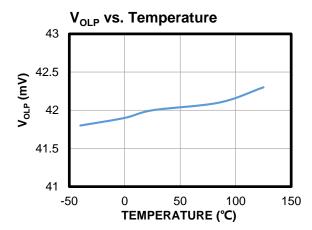

| Overload protection threshold              | V <sub>OLP</sub>       |                               | 37   | 42    | 47   | mV    |

| Overload protection delay                  | tolp                   |                               | 55   | 66    | 77   | ms    |

| Maximum CDC voltage on FB                  | VCDC_MAX               | V <sub>IS</sub> = 40mV        |      | 50    |      | mV    |

| Secondary Side (COMP)                      |                        |                               |      |       |      |       |

| Transconductance                           | GM                     |                               |      | 430   |      | μΑ/V  |

| Maximum sink current                       | Isink                  |                               | 56   | 86    | 120  | μΑ    |

| Maximum source current                     | I <sub>SOURCE</sub>    |                               | -125 | -88   | -60  | μΑ    |

| Maximum COMP voltage                       | V <sub>COMP-S</sub>    | $V_{DD} = 5V$                 | 2.5  | 2.6   | 2.7  | V     |

| Threshold for the max frequency limitation | V <sub>FS-MAX</sub>    |                               | 2.12 | 2.24  | 2.36 | V     |

| Threshold for burst entry                  | VBURST                 |                               | 0.3  | 0.33  | 0.36 | V     |

| Burst exit hysteresis                      | V <sub>BURST-HYS</sub> |                               |      | 0.018 |      | V     |

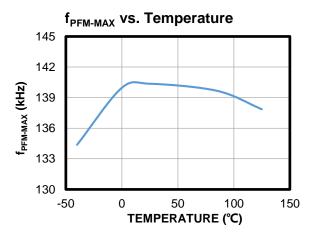

| Maximum PFM frequency                      | f <sub>PFM-MAX</sub>   | $T_J = 25^{\circ}C$           | 135  | 140   | 145  | kHz   |

| Minimal PFM (burst entry) frequency        | fpfm-min               | T <sub>J</sub> = 25°C         | 18   | 20    |      | kHz   |

| Burst exit frequency                       | f <sub>PFM-MIN</sub>   | T <sub>J</sub> = 25°C         | 18   | 20    |      | kHz   |

| Secondary Side - Internal                  | Thermal Prote          | ection                        | •    | •     |      | •     |

| OTP threshold (5)                          | T <sub>OTP-S</sub>     |                               |      | 150   |      | °C    |

| Hysteresis to recover from OTP (5)         | T <sub>Δ-S</sub>       |                               |      | 40    |      | °C    |

#### Note:

5) These parameters are guaranteed by design.

© 2022 MPS. All Rights Reserved.

#### TYPICAL CHARACTERISTICS

© 2022 MPS. All Rights Reserved.

# **TYPICAL CHARACTERISTICS** (continued)

# TYPICAL CHARACTERISTICS (continued)

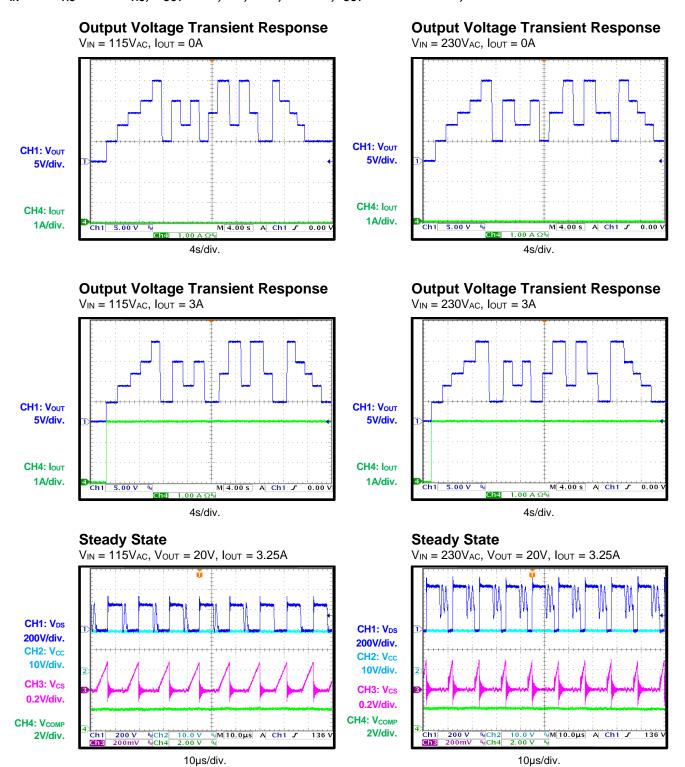

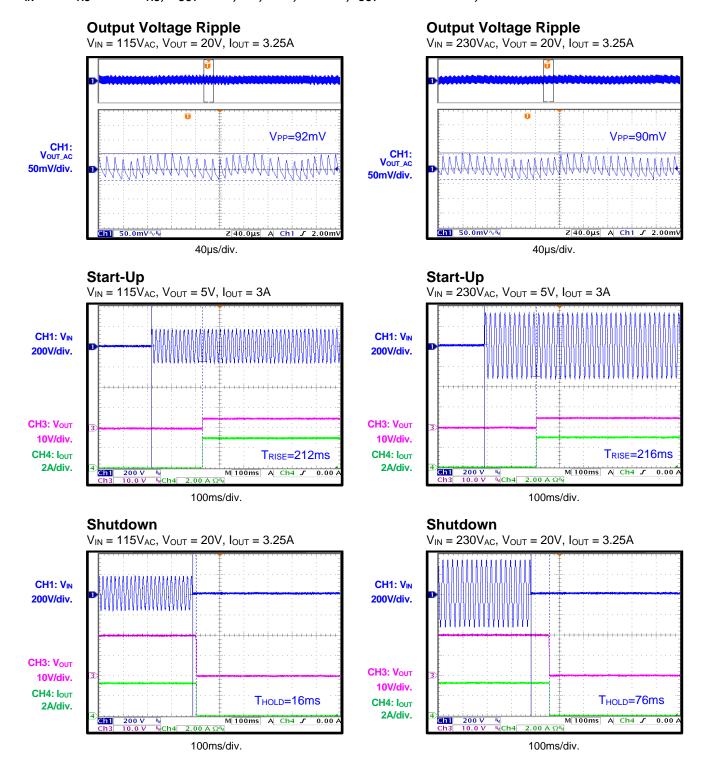

#### TYPICAL PERFORMANCE CHARACTERISTICS.

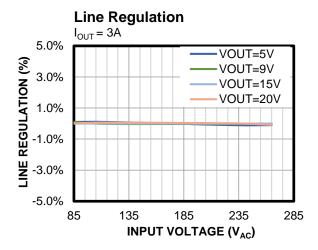

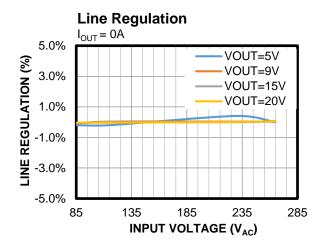

$V_{IN} = 90V_{AC}$  to 265 $V_{AC}$ ,  $V_{OUT} = 5V$ , 9V, 15V, or 20V,  $I_{OUT} = 0A$  to 3.25A, unless otherwise noted.

$V_{IN} = 90V_{AC}$  to 265 $V_{AC}$ ,  $V_{OUT} = 5V$ , 9V, 15V, or 20V,  $I_{OUT} = 0A$  to 3.25A, unless otherwise noted.

$V_{IN} = 90V_{AC}$  to 265 $V_{AC}$ ,  $V_{OUT} = 5V$ , 9V, 15V, or 20V,  $I_{OUT} = 0A$  to 3.25A, tested with a 10cm cable.

$V_{IN} = 90V_{AC}$  to 265 $V_{AC}$ ,  $V_{OUT} = 5V$ , 9V, 15V, or 20V,  $I_{OUT} = 0A$  to 3.25A, test with a 10cm cable.

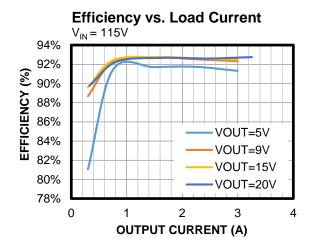

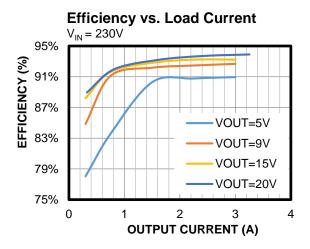

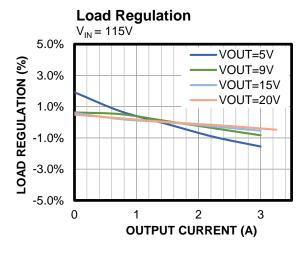

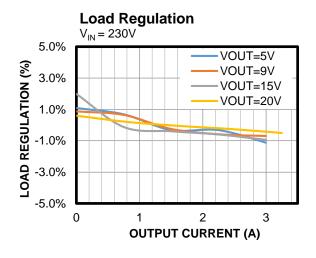

$V_{IN} = 115V_{AC}/230V_{AC}$ ,  $V_{OUT} = 5V$ , 9V, 15V, or 20V,  $I_{OUT} = 0A$  to 3.25A, unless otherwise noted.

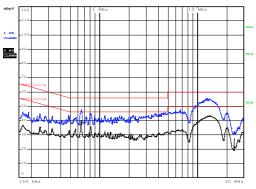

#### **EMI**

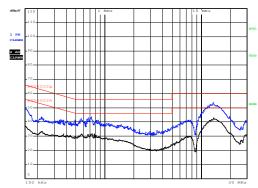

$V_{IN} = 115V_{AC}$ , L line,  $V_{OUT} = 20V$ ,  $I_{OUT} = 3.25A$

# ЕМІ

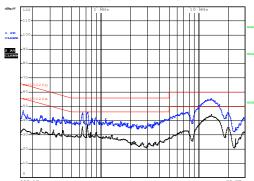

$V_{IN} = 230V_{AC}$ , L line,  $V_{OUT} = 20V$ ,  $I_{OUT} = 3.25A$

#### **EMI**

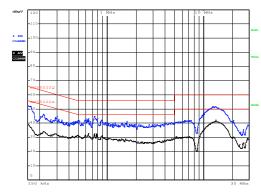

$V_{IN} = 115V_{AC}$ , N line,  $V_{OUT} = 20V$ ,  $I_{OUT} = 3.25A$

#### EMI

$V_{IN} = 230V_{AC}$ , N line,  $V_{OUT} = 20V$ ,  $I_{OUT} = 3.25A$

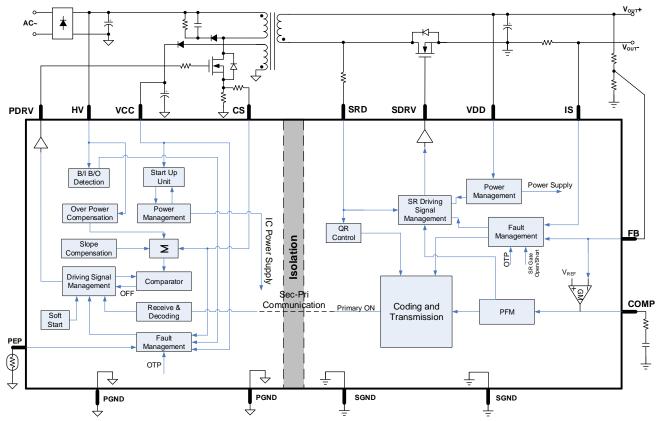

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MPX2003 is an all-in-one flyback controller that provides the benefits of primary-side regulation (PSR) and secondary-side regulation (SSR). The MPX2003 achieves accurate regulation while reducing system complexity and the total solution cost.

The MPX2003 implements a complete SSR scheme. Both the control loop and the modulation block are placed on the secondary IC, so the driving signal of the synchronous rectifier (SR) can match the driving signal of the primary-side MOSFET. This allows the SR to operate safely in continuous conduction mode (CCM), which increases overall efficiency and provides the robust design more flexibility.

#### PRIMARY IC FUNCTIONS

#### Start-Up with Brown-In/Brownout Detection

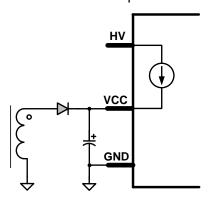

The IC is disabled when there is no power supply. When a voltage is applied to the HV pin, VCC is charged by an internal current source from HV. Once  $V_{CC}$  exceeds the HV current source turn-off voltage ( $V_{CC-IOFF}$ , typically 14.5V), the current source stops charging.

To eliminate voltage drop influence on the external resistor, brown-in/brownout protection is enabled after the HV current source turns off. If the HV voltage exceeds  $V_{\text{HV-ON}}$  (typically 107V), a brown-in condition has occurred. The primary IC turns on the HV current source to charge  $V_{\text{CC}}$  back to  $V_{\text{CC-IOFF}}$  (to guarantee a maximized start-up window) and operates in normal start-up mode. Otherwise, it is treated as a brownout condition. The primary IC's operation remains disabled. Meanwhile,  $V_{\text{CC}}$  is charged and discharged between  $V_{\text{CC-IOFF}}$  and  $V_{\text{CC-MIN}}$ .

Once  $V_{\text{CC}}$  exceeds  $V_{\text{CC-IOFF}}$ , the primary IC begins monitoring the status of the secondary IC before the primary IC runs into normal start-up mode. There are three conditions for primary IC start-up, described below.

If the primary IC starts up normally when a brown-in condition is detected, and the primary IC does not detect any status from the secondary IC, the primary IC starts switching on its own. Once the secondary IC is active, the primary IC stops switching independently, and the secondary IC takes control. There is a time limit on the primary IC's start-up period. Independent primary switching stops when the timer  $(t_{OCP})$  runs out. This means that if there is a fault condition (e.g. an overload), the secondary IC may not start up successfully.  $t_{OCP}$  starts counting from soft start. Then the primary over-current protection (POCP) flag is set, and the primary IC runs in a protection operation.

- 2. If the secondary IC is active before primaryside switching begins, the primary IC does not require independent switching. The secondary IC takes control immediately after the brown-in condition is detected.

- If the protection status is detected before start-up, the IC indicates a fault condition, such as an overload on the secondary side. In this scenario, the primary IC does not switch at all, but sets the protection flag and runs in a protection operation.

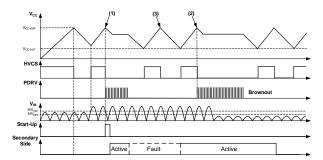

Figure 2 shows the start-up logic for the primary IC.

Figure 2: Start-Up Logic for the Primary IC

# Brownout Protection during Normal Operation

To prevent power supply issues caused by an insufficient input voltage, the primary IC implements brownout protection. If the HV voltage is below  $V_{HV-OFF}$  (typically 98V, which is the internal B/O threshold), the brownout timer starts running. If the HV voltage exceeds  $V_{HV-OFF}$ , the timer is reset. If the brownout timer reaches  $t_{BO}$ , the primary IC triggers brownout protection, and VCC initiates hiccup operation while it is between  $V_{CC-MIN}$  (typically 8.3V) and  $V_{CC-IOFF}$ .

The primary IC does not start up again until there is a valid brown-in detection condition. Brown-in and brownout detection are suspended when the HV current source turns on (to avoid the effect of the HV voltage drop). These protections can be detected after the HV current source turns off.

#### Soft Start (SS)

To reduce stress on the power circuits, a soft-start function is implemented for the primary IC. When the primary IC enters normal start-up mode and starts switching on its own, the internal soft start gradually increases the current limitation from  $V_{IPK-MIN}$  (typically 0.1V) to  $V_{IPK-MAX}$  (typically 0.4V). During this time, the switching frequency ( $f_{SW}$ ) rises from  $f_{SW-SOFT}$  (typically 10kHz) to  $f_{SW-MAX}$  (typically 110kHz). The soft-start period lasts for  $t_{SOFT}$  (typically 9.6ms).

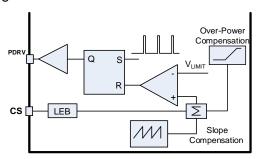

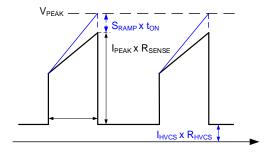

# Peak Current Control with Internal Slope Compensation

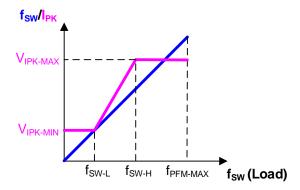

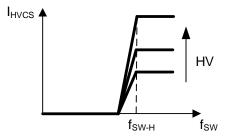

The primary IC employs peak current mode control with a switching on time. This on time is controlled by comparing the voltage across the CS pin's current-sense resistor with the internal reference voltage. The reference voltage is regulated by  $f_{\text{SW}}$  with a maximum value of  $V_{\text{IPK-MAX}}$  and a minimum value of  $V_{\text{IPK-MIN}}$ .

The reference voltage is clamped at  $V_{IPK-MAX}$  when  $f_{SW}$  exceeds  $f_{SW-H}$  (typically 60kHz); the reference voltage is clamped at  $V_{IPK-MIN}$  when  $f_{SW}$  is below  $f_{SW-L}$  (typically 20kHz) (see Figure 3). When  $f_{SW}$  is between  $f_{SW-H}$  and  $f_{SW-L}$ , the reference voltage is adjusted continuously.

Figure 3: Peak Current Reference vs. Switching Frequency

A synchronized positive slope is added to the current-sense signal on CS to prevent subharmonic oscillations and guarantee stable

peak current mode control across a wide range of input voltages.

Due to parasitic capacitance, a spike usually occurs on the current-sense resistor after the MOSFET turns on. To prevent the peak current limitation comparator from being falsely triggered by this turn-on spike, a leading edge blanking (LEB) function is implemented on the comparator. During the blanking time, the peak current limitation comparator is disabled, so the MOSFET cannot turn off. Two-level LEB is adopted in the comparator. Normal operation has t<sub>LEB-L</sub> (typically 400ns), while t<sub>LEB-S</sub> (typically 250ns) is the blanking time during SCP.

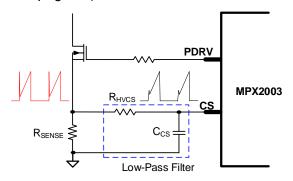

#### **Line Compensation for Peak Current Control**

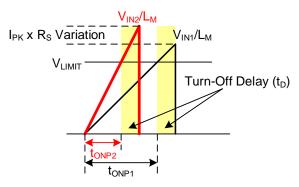

Ideally, the primary peak current should be exactly the same as the reference because of peak current control operation. However, the IC has a logic propagation delay and driver delay, so the actual peak current always exceeds the reference value. The difference between the actual value and reference value varies with the input voltage. A higher input voltage results in a higher peak current overshoot (see Figure 4). This leads to a significant variation in the maximum power limitation.

Figure 4: Peak Current Difference Caused by Turn-Off Delay

The slope compensation voltage is proportional to the primary MOSFET's turn-on time, which is determined by the load and input voltage. This means that the slope compensation value is lower when the input voltage is higher, even if the load is the same.

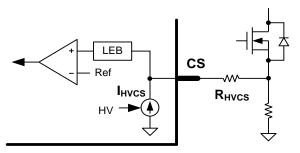

To compensate for this variation and improve overload protection (OLP) accuracy, an offset proportional to the input voltage is added on the

CS signal. The offset is created by an internal sourcing current on CS that flows across an external resistor ( $R_{HVCS}$ ). The current source is proportional to the HV voltage (see Figure 5).

The compensation level can be externally adjusted by  $R_{\text{HVCS}}$ .

Figure 5: Implementation of the Line Compensation Function

The compensation current is at its maximum value (corresponding to the HV voltage) only when the peak current reference is at its maximum limit. The compensation current is removed gradually when  $f_{SW}$  drops below  $f_{SW-H}$ . Compensation is removed once the peak current reference drops below  $V_{LC-END}$ . (see Figure 6).

Figure 6: Current on the CS Pin for Line Compensation

#### **Driver**

The driver capability is specified in the PDRV section of the Electrical Characteristics section on page 6. The voltage is clamped internally at  $V_{\text{CLAMP}}$  (typically 14.5V) to guarantee that the external MOSFET operates safely.

#### **Under-Voltage Lockout (UVLO)**

If  $V_{\text{CC}}$  drops below  $V_{\text{CC-MIN}}$  (typically 8.3V), undervoltage lockout (UVLO) stops primary switching immediately.  $V_{\text{CC}}$  is recharged by the current source from HV.

#### **Primary-Side Protections**

The primary IC provides full protection features and responds to faults on the secondary side.

If a protection is triggered, switching is terminated immediately, and  $V_{\text{CC}}$  drops. If  $V_{\text{CC}}$  drops to  $V_{\text{CC-AUT}}$ , the related protection flag is reset, and the HV current source is enabled to charge the VCC capacitor. Then the primary IC initiates normal start-up logic and operation.

#### Short-Circuit Protection (SCP)

If the CS voltage exceeds  $V_{SCP}$ , the IC triggers short-circuit protection (SCP), which means that the peak current is not effectively regulated by its limit due to a fault condition, such as winding short circuit or output short circuit. During SCP, auto-restart protection mode is triggered. A reduced LEB time ( $t_{LEB-S}$ , typically 250ns) is also adopted by the SCP comparator to prevent a false trigger by the turn-on spike.

For the MPX2003, the behavior during SCP is designed as a surge-proof approach. If SCP is triggered for the first time, the IC does not shut down completely. Instead, primary switching is blanked for  $t_{\text{SCP2}}$ , during which the primary IC does not respond to the secondary IC unless there is a protection signal.

After the blanking time passes, the primary IC resumes switching. If SCP is triggered for a second time within 8 switching cycles, the primary IC stops switching and initiates autorestart recovery. If the short-circuit condition is removed after the first SCP event, the primary IC resets the SCP counter and resumes normal operation.

#### CS Short Protection (SSP)

If the CS voltage does not exceed  $V_{CSS}$  (typically 50mV) within  $t_{SSP}$  (typically 4.5 $\mu$ s) after the primary MOSFET turns on, the primary IC initiates CS short protection (SSP) to prevent the primary current from overstress due to a CS short.

SSP detection is only executed during the first few switching cycles to prevent the CS pin or CS resistor from being directly shorted to GND due to improper soldering.

#### CS Open Protection (SOP)

During the soft-start period, there is an internal leakage current (typically  $0.5\mu A$ ) flowing into the CS pin to guarantee that the CS voltage always exceeds  $V_{SCP}$  when it is open. The MPX2003 implements CS open protection (SOP) to protect the circuitry from being further damaged.

#### Over-Voltage Protection (OVP)

If  $V_{CC}$  exceeds  $V_{CC\text{-}OVP}$  (typically 26V), the primary IC stops switching after a validation time ( $t_{VCC\text{-}OVP}$ ). Over-voltage protection (OVP) triggers auto-restart mode. The primary IC initiates OVP to prevent components from breaking down due to overstress.

#### **Brownout Protection (BOP)**

For more information about brownout protection (BOP), see the Start-Up with Brown-In/Brownout Detection section on page 19 and the Brownout Protection during Normal Operation section on page 19. BOP triggers auto-restart mode.

# Primary Over-Temperature Protection (POTP)

To prevent thermal damage on the chip, primary over-temperature protection (POTP) shuts down switching immediately if the junction temperature exceeds  $T_{\text{OTP-P}}$  (typically 150°C). The protection flag is latched until the junction temperature drops by  $T_{\Delta\text{-P}}$  (typically 40°C).

#### Primary Over-Current Protection (POCP)

For more information about primary over-current protection (POCP), see the Start-Up with Brown-In/Brownout Detection section on page 19. If the primary IC does not receive a start-up signal from the secondary IC for tocp (typically 55ms), POCP is triggered and initiates auto-restart mode.

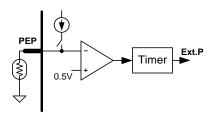

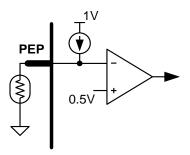

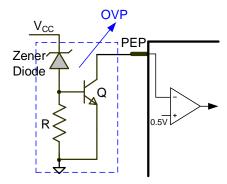

#### Primary External Protection (PEP)

PEP is a general-purpose protection pin. When the IC starts to operate, it begins to monitor the voltage on PEP every 100 $\mu$ s to 200 $\mu$ s. There is an internal current flowing out of PEP with a fixed value of I<sub>PEP</sub> (typically 110 $\mu$ A). A resistor or a bipolar junction transistor (BJT) can be connected to PEP to set the target voltage. If the PEP voltage is below the protection trigger threshold (V<sub>PEP-T</sub>, typically 0.5V) and the condition lasts longer than the trigger delay time (t<sub>PEP-T</sub>, typically 300 $\mu$ s), the PEP flag is set to

high. The PEP flag does not reset until  $V_{CC}$  drops below  $V_{CC-AUT}$ .

PEP detection acts as a switch mode. The current source is only on for several microseconds for every 100µs to 200µs, which can save power loss during steady state.

Typically, PEP can be used to implement an OTP function for external power devices (e.g. the primary MOSFET) by connecting PEP to a negative temperature coefficient (NTC) resistor (see Figure 7). PEP can also configure the OVP threshold.

**Figure 7: Primary External Protection**

#### Response to the Secondary Protections

For more information about responses to secondary protections, see the Start-Up with Brown-In/Brownout Detection section on page 19.

#### **SECONDARY IC FUNCTIONS**

#### **Secondary IC Power Supply Management**

VDD is the general-purpose power supply for the secondary IC. The VDD voltage ( $V_{DD}$ ) can be supplied by itself or the output voltage ( $V_{OUT}$ ). Figure 8 shows the circuit when  $V_{DD}$  is supplied by  $V_{OUT}$ .

Figure 8: V<sub>DD</sub> Supply from the Output

When the voltage supplied from  $V_{\text{OUT}}$  is below  $V_{\text{DD-C}}$ , the current supply to  $V_{\text{DD}}$  comes from SRD to allow the MPX2003 to support low-output applications.

Figure 9: V<sub>DD</sub> Supply from Both the Output and SRD

By allowing  $V_{DD}$  to be powered by  $V_{OUT}$  and SRD, the SR driver has an expedited start-up, which limits the voltage spike caused by the body diode's reverse recovery. Otherwise, the current supply for  $V_{DD}$  comes from  $V_{OUT}$  for optimized efficiency.

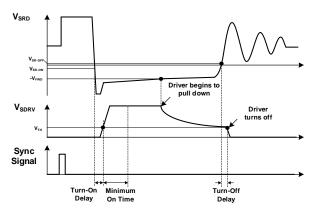

#### Synchronous Rectification Turn On

After the primary-side MOSFET turns off, the inductor current is transferred from the primary side to the secondary side, which makes the SR MOSFET's drain voltage drop. When the voltage on the SRD pin crosses the turn-on threshold ( $V_{SR-ON}$ ), the secondary IC starts to set the SR driver, and the SR MOSFET turns on after the turn-on delay ( $t_{SR-OND}$ ).

When the SR MOSFET is on, there is a minimum on time ( $t_{\text{ON-MIN}}$ ) that prevents the MOSFET from being falsely turned off due to parasitic oscillation. During the minimum on time, the turn-off action is not completely blanked, and the turn-off threshold rises to  $V_{\text{SR-OFFM}}$ . This ensures that the SR MOSFET can always be turned off under severe situations, even during the minimum on time.

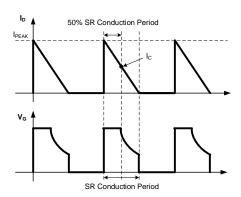

#### **Synchronous Rectification Conduction**

During the SR conduction period, the gate voltage is regulated based on the forward voltage drop across the MOSFET ( $V_{SRD}$ ). When  $V_{SRD}$  is below the internal reference voltage, the gate driver fully turns on to reach the minimum turn-on resistance.  $V_{SRD}$  rises as the current decreases. When  $V_{SRD}$  exceeds the reference voltage, the gate voltage is pulled down to increase the turn-on resistance, and the regulation voltage quickly switches to  $V_{FWD}$ . This means that the rising of  $V_{SRD}$  is regulated to a certain level, which effectively prevents a premature turn-off while maximizing the SR conduction period.

#### **Synchronous Rectification Turn Off**

As the inductor current reaches zero during discontinuous conduction mode (DCM),  $V_{SRD}$  rises to zero. Once  $V_{SRD}$  exceeds  $V_{SR-OFF}$ , the gate immediately pulls down to turn off the SR MOSFET (see Figure 10).

Figure 10: SR Operation during DCM

During continuous conduction mode (CCM), the secondary IC generates a signal based on a dead time to determine when the SR MOSFET turns off and the primary MOSFET turns on. This feature reduces the chances of shoot-through (see Figure 11).

Figure 11: SR Operation during CCM

In burst mode, the SR gate block turns off to reduce power loss. When the IC exits burst mode, the SR gate block turns on after one switching operation.

#### **Output Voltage (Vout) Regulation**

The internal error amplifier regulates  $V_{\text{OUT}}$ .  $V_{\text{OUT}}$  is fed back through the FB pin and external dividing resistors, and is then compared to the internal precise reference voltage ( $V_{\text{REF}}$ ). The

compensation voltage is generated by the transconductance amplifier. In this situation, the external compensation network can be designed by the COMP pin to adjust the regulation performance.

Due to the error amplifier behavior, the COMP voltage can indicate the output load condition, such as when the COMP voltage rises as the load increases.

The COMP voltage is sent to the pulse-frequency modulation (PFM) block to modulate the switching frequency ( $f_{SW}$ ). A lower COMP voltage results in a lower  $f_{SW}$ , and there are also upper and lower limitations on the frequency modulation. When the COMP voltage exceeds  $V_{FS-MAX}$ ,  $f_{SW}$  is clamped at the maximum frequency ( $f_{PFM-MAX}$ ). When the COMP voltage is below  $V_{BURST}$ , the switching pulse stops until the COMP voltage exceeds  $V_{BURST}$  +  $V_{BURST-HYS}$ .  $f_{PFM-MIN}$  is the minimum  $f_{SW}$  corresponding to  $V_{BURST}$ . The first switching pulse is sent without any delay once it exits burst mode. This closed-loop regulation controls  $V_{OUT}$ .

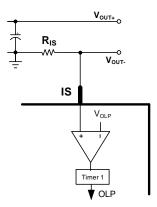

#### **Cable Drop Compensation**

The voltage drop on the cable is proportional to the output current, which is reflected on the voltage of the IS pin (see Figure 12). The maximum CDC voltage on FB is  $V_{\text{CDC\_MAX}}$ . The cable drop compensation voltage can be calculated with Equation (20) on page 29.

Figure 12: Cable Drop Compensation

#### **Quasi-Resonant (QR) Mode Switching**

The secondary-side IC achieves quasi-resonant (QR) mode by comparing the SRD voltage and  $V_{DD}$  when the converter runs in DCM. The primary side switching is always on when the primary side switch is near its minimum voltage. This reduces power loss and minimizes EMI noise.

The primary IC has a variable current limit when  $f_{SW}$  is below  $f_{SW-H}$ , which means that switching is irregular when the IC operates in QR mode. To prevent the IC from entering this mode, the QR is disabled when  $f_{SW}$  is below  $f_{SW-H}$ . At this point, the primary side's on signal does not wait for the QR detection period.

The IC can immediately exit QR mode when certain operations are detected. For example, it exits QR mode under the following conditions:

- If CCM is required (the load becomes heavy)

- More than 6 oscillation valleys are detected

- The oscillation period during DCM lasts longer than 20µs

- SRD has not reached V<sub>DD</sub> within 2.5µs after the SR gate turns off

# Secondary-Side Protections Secondary Under-Voltage Lockout (SUVLO)

The secondary IC does not begin operating until  $V_{DD}$  rises above  $V_{DD-ON}$  (typically 4.5V). If  $V_{DD}$  falls below  $V_{DD-OFF}$  (typically 4.25V), the secondary IC shuts down, and all internal signals are reset. To avoid voltage spike influences (mainly caused by the capacitor's ESR), any valid UVLO detection typically requires a 10 $\mu$ s delay time.

#### Secondary Overload Protection (SOLP)

The IS pin senses the output current with external sensing resistors. When the IS voltage  $(V_{IS})$  exceeds the overload protection threshold  $(V_{IS-OLP})$  and lasts longer than the overload protection delay time  $(t_{OLP})$ , the secondary overload protection (SOLP) flag is set to high and switching stops. The SOLP flag is reset when the secondary IC or primary IC trigger UVLO.

If the IS pin is shorted to SGND, the SOLP function is still available, though the COMP signal is less accurate. SOLP is implemented based on the COMP signal. If the COMP voltage exceeds  $V_{\text{FS-MAX}}$  (higher than the threshold where the switching frequency is set at the maximum limit), the OLP timer begins counting. SOLP is triggered after the timer runs out.

Once SOLP is triggered, COMP is internally shorted to SGND, and it is not released until SOLP is cleared.

8/5/2022

#### Secondary Over-Voltage Protection (SOVP)

If the FB voltage exceeds the OVP threshold  $(V_{OVP})$  and lasts longer than the OVP delay time  $(t_{OVP-D})$ , the secondary over-voltage protection (SOVP) flag is set to high and switching stops.

Switching reverts to normal modulation once the FB voltage returns to  $V_{REF}$ . During SOVP, there is an extra current ( $I_{BLD}$ ) drawn from the VDD pin. This current helps ease the over-voltage condition by discharging the VDD capacitor.

#### FB Open-Loop Protection (FBOLP)

If there are fault conditions (i.e. FB shorted to SGND or an upper FB resistor is open), the MPX2003 loses its feedback loop and  $V_{\text{OUT}}$  goes out of regulation. To protect the circuit from being further damaged, the MPX2003 implements a cross check between  $V_{\text{OUT}}$  and the FB voltage.

If  $V_{DD}$  exceeds  $V_{DD-RDY}$ , this means that  $V_{DD}$  is no longer supplied by SRD. If the FB voltage is still below  $V_{FBO}$ , the secondary IC initiates FB open-loop protection (FBOLP) after a validation time  $(t_{FBO})$ .

The internal leakage current (I<sub>FB</sub>) guarantees that the FB voltage is always pulled to SGND when the FB pin is open.

# SR Gate Open/Short Protection (SGOP/SGSP)

If SDRV is set but the SRD voltage remains low during the conduction period, this indicates that the SR may not be successfully turned on due to an unexpected fault condition, such as an open gate or a broken MOSFET. The MPX2003 implements SR gate open protection (SGOP) to protect the circuitry from being further damaged under these conditions.

The threshold for SR driver open detection is  $V_{\text{SGO}}$ , and the condition must remain for 8 consecutive switching cycles for validation. If SGOP is triggered, the secondary IC does not recover until there is another primary IC self start-up.

If SDRV detects that the connected resistor is below  $1k\Omega$  once  $V_{DD}$  reaches  $V_{DD-ON}$ , this means that SDRV is shorted to SGND. Switching stops until the primary IC starts up again.

#### SRD Abnormal Protection (SRDP)

If the power supply of the secondary IC is successfully set up and there are 17 consecutive primary switching pulses but the SR gate is not triggered by SRD detection, SRD abnormal protection (SRDP) is triggered. Switching stays off and COMP is pulled to ground. The secondary IC does not recover until the secondary IC or primary IC trigger UVLO. Then the secondary IC starts switching once a valid signal is detected on SRD.

# Secondary Over-Temperature Protection (SOTP)

To prevent any thermal damage on the chip, secondary over-temperature protection (SOTP) sets the SOTP flag high if the junction temperature exceeds  $T_{\text{OTP-S}}$ . The protection flag is latched until the junction temperature drops by  $T_{\Delta\text{-S}}$ .

#### APPLICATION INFORMATION

#### Selecting the VCC Capacitor

Figure 13 shows the start-up circuit.

Figure 13: Start-Up Circuit

$V_{\text{CC}}$  is initially charged by HV. When  $V_{\text{CC}}$  reaches  $V_{\text{CC-IOFF}}$ , HV stops charging  $V_{\text{CC}}$  and the IC starts to operate. To guarantee a successful start-up,  $V_{\text{OUT}}$  should be set up before  $V_{\text{CC}}$  drops to  $V_{\text{CC\_MIN}}$ . For most applications, choose a VCC capacitor value that is about 22 $\mu$ F. To ensure safe operation across the entire input and output range (especially under no load conditions),  $V_{\text{CC}}$  should have some margin. Usually, the minimum  $V_{\text{CC}}$  is recommended to be about 1V greater than the minimum operating voltage ( $V_{\text{CC-MIN}}$ ). The recommended VCC capacitor ( $C_{\text{VCC}}$ ) value can be calculated with Equation (1):

$$C_{\text{VCC}} > \frac{I_{\text{OP}} \times t_{\text{START-UP}}}{V_{\text{CC-IOFF}} - V_{\text{CC-MIN}}} \tag{1}$$

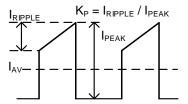

# **Designing the Transformer's Magnetizing Inductance**

The MPX2003's maximum switching frequency ( $f_{SW}$ ) is recommended to be 130kHz at maximum. With internal slope compensation, the MPX2003 supports CCM when the duty cycle exceeds 50%. Set a ratio ( $K_P$ ) for the primary inductor's ripple current amplitude vs. the peak current value to  $0 < K_P \le 1$ , where  $K_P = 1$  for DCM.

Figure 14 shows the relevant waveforms. A larger inductor leads to a smaller  $K_P$ , which can reduce the RMS current but increase transformer size. An optimal  $K_P$  value is between 0.6 and 0.8 for the universal input range, or 0.8 to 1 for the 230V<sub>AC</sub> input range.

**Figure 14: Typical Primary Current Waveform**

The input power  $(P_{IN})$  at the minimum input can be estimated with Equation (2):

$$P_{IN} = \frac{V_{OUT} \times I_{OUT}}{\eta}$$

(2)

Where  $V_{\text{OUT}}$  is the output voltage,  $I_{\text{OUT}}$  is the rated output current, and  $\eta$  is the estimated efficiency (typically between 0.85 and 0.9 depending on the input range and output application).

During CCM at the minimum input, the converter's maximum duty cycle can be calculated with Equation (3):

$$D_{MAX} = \frac{(V_{OUT} + V_{FWD}) \times N_{PS}}{(V_{OUT} + V_{FWD}) \times N_{PS} + V_{IN(MIN)}}$$

(3)

Where  $V_{\text{FWD}}$  is the secondary SR MOSFET regulated forward voltage,  $N_{\text{PS}}$  is the transformer's primary-secondary turn ratio, and  $V_{\text{IN(MIN)}}$  is the minimum voltage on the bulk capacitor.

The MOSFET turn-on time can be estimated with Equation (4):

$$t_{ON} = D \times t_{S} \tag{4}$$

Where  $t_S$  is the frequency jitter's dominant switching period. The relationship between  $t_{SMIN}$  and  $f_{SW-MAX}$  can be calculated with Equation (5):

$$\frac{1}{t_{SMIN}} = f_{SW-MAX} = 130kHz$$

(5)

The average value for the primary current can be estimated with Equation (6):

$$I_{AV} = \frac{P_{IN}}{V_{IN(MIN)}} \tag{6}$$

The peak value for the primary current can be calculated with Equation (7):

$$I_{PEAK} = \frac{I_{AV}}{(1 - \frac{K_{P}}{2}) \times D}$$

(7)

The ripple value for the primary current can be estimated with Equation (8):

$$I_{RIPPLE} = K_{P} \times I_{PEAK}$$

(8)

The valley value for the primary current can be calculated with Equation (9):

$$I_{VALLEY} = (1 - K_{P}) \times I_{PEAK}$$

(9)

The magnetizing inductance can be estimated with Equation (10):

$$L_{M} = \frac{V_{IN(MIN)} \times t_{ON}}{I_{RIPPLE}}$$

(10)

#### **Selecting the Current-Sense Resistor**

Figure 15 shows the peak current comparator logic.

Figure 15: Peak Current Comparator Circuit Logic

Figure 16 shows the peak current comparator waveform.

Figure 16: Peak Current Comparator Waveform

When the sum of the voltage on the currentsense resistor, the voltage on the over-power compensation resistor. and the generated by the slope compensation block reach V<sub>PEAK</sub>, the comparator goes high to reset the RS flip-flop, and DRV is pulled down to turn off the MOSFET (see Figure 15). The maximum current limit is V<sub>IPK-MAX</sub>. The slope compensator is S<sub>RAMP</sub>, and at low line the over-power compensation is zero. Given a certain margin, V<sub>PEAK</sub> is equal to 0.95 x V<sub>IPK-MAX</sub> under full loads. The voltage on the current-sense resistor can be calculated with Equation (11):

$$V_{SENSE} = 95\% \times V_{IPK-MAX} - S_{RAMP} \times t_{ON} \quad (11)$$

The current-sense resistor can be estimated with Equation (12):

$$R_{SENSE} = \frac{V_{SENSE}}{I_{PEAK}}$$

(12)

Select a current-sense resistor with an appropriate power rating. The current-sense resistor's power loss can be calculated with Equation (13):

$$P_{\text{SENSE}} = \left[ \left( \frac{I_{\text{PEAK}} + I_{\text{VALLEY}}}{2} \right)^2 + \frac{1}{12} \left( I_{\text{PEAK}} - I_{\text{VALLEY}} \right)^2 \right] \times D \times R_{\text{SENSE}}$$

(13)

# Over-Power Compensation and Selecting the Low-Pass Filter on CS

The MPX2003 has an over-power compensation (OPC) function that draws current from CS. The purpose of OPC is to minimize the OLP difference caused by different input voltages. The offset current is proportional to the input peak voltage sensed by HV.

Assume the resistor in the current-sense loop is  $R_{HVCS}$  and the bus voltage is  $V_{HV}$ . The compensation voltage on the CS pin can be estimated with Equation (14):

$$V_{OPC} = R_{HVCS} \times I_{HVCS}$$

(14)

The compensation criteria makes the COMP pin voltage under high-line, full-load conditions similar to its voltage under low-line, full-load conditions. Generally, R<sub>HVCS</sub> is recommended to be between hundreds of Ohms to one thousand Ohms.

A small capacitor is connected to the CS pin and R<sub>HVCS</sub> to form a low-pass filter for noise filtering when the MOSFET turns on and off (see Figure 17 on page 28).

Figure 17: Low-Pass Filter on CS

The low-pass filter's R x C constant should not exceed 1/3 of the leading-edge blanking period for SCP ( $t_{\text{LEB-S}}$ , typically 250ns). Otherwise, the filtered sensed voltage cannot reach the SCP point to trigger SCP if an output short circuit occurs.

#### **Ramp Compensation**

When adopting peak current control, subharmonic oscillations occur when the duty cycle exceeds 50% (D > 0.5) in CCM. The MPX2003 provides internal ramp compensation to solve this issue. Use the coefficient  $\alpha$  to determine whether the ramp compensation is appropriate.  $\alpha$  can be calculated with Equation (15):

$$\alpha = \frac{\frac{D_{MAX} \times V_{IN(MIN)}}{(1 - D_{MAX}) \times L_{M}} \times R_{SENSE} - S_{RAMP}}{\frac{V_{IN(MIN)}}{L_{M}} \times R_{SENSE} + S_{RAMP}}$$

(15)

Where  $S_{\text{RAMP}}$  is the minimum internal slope value of the compensation ramp. For stable operation,  $\alpha$  must be less than 1. The primary-side slew rate can be estimated with Equation (16):

$$\frac{V_{IN(MIN)}}{L_{M}} \times R_{SENSE}$$

(16)

The equivalent secondary-side voltage sensed by the CS resistor can be calculated with Equation (17):

$$\frac{D_{MAX} \times V_{IN(MIN)}}{(1 - D_{MAX}) \times L_{M}} \times R_{SENSE}$$

(17)

#### **External Protection through the PEP Pin**

The PEP pin can be used to implement an overtemperature protection (OTP) function for external power devices (e.g. the primary MOSFET) by connecting a negative temperature coefficient (NTC) resistor to this pin (see the Primary External Protection (PEP) section on page 22). Figure 18 shows OTP through the PEP pin.

Figure 18: OTP through PEP

The sourcing current for PEP is I<sub>PEP</sub>. At working temperatures, the NTC resistor should satisfy a particular relationship, estimated with Equation (18):

$$I_{PEP} \times R_{PEP} > V_{PEP-T} \tag{18}$$

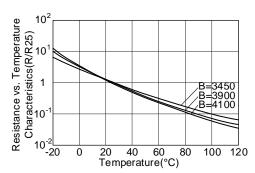

When the temperature increases, the NTC resistance decreases. Figure 19 shows the typical waveform for NTC resistance vs. temperature.

Figure 19: NTC Resistance vs. Temperature

I<sub>PEP</sub> can also meet the condition at the protected temperature value, calculated with Equation (19):

$$I_{PEP} \times R_{PEP} < V_{PEP-T} \tag{19}$$

The PEP pin can also provide over-voltage protection (OVP) using several passive components. The breakdown voltage (BV) of the Zener diode should be equal to the over-voltage threshold when an over-voltage condition occurs. For example, the BV of the Zener diode is equal to the  $V_{\rm CC}$  over-voltage threshold when a secondary over-voltage condition occurs.

Figure 20 shows OVP through the PEP pin.

Figure 20: OVP through PEP

#### **Cable Drop Compensation**

The CP voltage is proportional to the IS voltage  $(V_{IS})$ . The default ratio between  $V_{IS}$  and the compensation voltage on FB is 3:3.7, which means that when the IS voltage reaches its maximum value (40mV), the compensation voltage on the FB reference is about 50mV. The cable drop's compensation voltage on the output can be calculated with Equation (20):

$$V_{CP} = R_{IS} \times I_{OUT} \times \frac{3.7}{3} \times \frac{(R_H + R_L)}{R_I}$$

(20)

Cable drop compensation is disabled when the IS pin is shorted to GND on the secondary side.

#### Overload Protection through the IS Pin

Overload protection can be achieved through the IS pin. Place one high-precision current-sense resistor in the output power loop and measure the voltage drop on this resistor through the IS pin. When  $V_{\rm IS}$  exceeds  $V_{\rm OLP}$ , the MPX2003 enters secondary OLP (SOLP) after a certain time ( $t_{\rm OLP}$ ). This sensing resistor follows the relationship estimated with Equation (21):

$$R_{IS} = (0.8 \sim 0.9) \times \frac{V_{OLP}}{I_{OUT}}$$

(21)

Figure 21 shows OLP through the IS pin.

Figure 21: OLP through the IS Pin

If R<sub>IS</sub> can be shorted, OLP through the IS pin is disabled.

#### Selecting the SR MOSFET

Power MOSFET selection is a tradeoff between  $R_{DS(ON)}$  and  $Q_G$ . To improve efficiency, use a MOSFET with a lower  $R_{DS(ON)}$ . Generally, a MOSFET with a lower  $R_{DS(ON)}$  has a higher  $Q_G$ , which reduces the turn-on/off speed and increases switching loss.

If  $Q_G$  is not optimized, the gate driving signal may turn off prematurely. A MOSFET with an  $R_{DS(ON)}$  that is too low is not recommended because the gate driver is pulled low when the MOSFET's drain-source voltage ( $V_{DS}$ , calculated by - $I_{SD}$  x  $R_{DS(ON)}$ ) exceeds - $V_{FWD}$ .

The MOSFET's  $R_{DS(ON)}$  does not contribute to conduction loss, because  $V_{DS}$  is adjusted at  $-V_{FWD}$  during the driving period (when the switching current is fairly small). The conduction loss can be calculated with Equation (22):

$$P_{CON} = -V_{DS} \times I_{SD} \approx I_{SD} \times V_{FWD}$$

(22)

Figure 22 on page 30 shows the typical waveform when a flyback application works in DCM. Assume a 50% duty cycle, and the output current is  $I_{\text{OUT}}$ .

8/5/2022

Figure 22: SR Waveforms in QR Mode

To effectively utilize the MOSFET's  $R_{DS(ON)}$ , the MOSFET should be completely turned on for at least 50% of the SR conduction period.  $V_{DS}$  can be estimated with Equation (23):

$$V_{DS} = -I_{C} \times R_{ON} = -2 \times I_{OUT} \times R_{ON} \le -V_{FWD} \qquad (23)$$

Where V<sub>FWD</sub> is the forward voltage threshold.

The MOSFET's  $R_{DS(ON)}$  should not be lower than 12 /  $I_{OUT}$  (in  $m\Omega$ ). For example, for a 5A application,  $R_{DS(ON)}$  should not be below 2.4m $\Omega$ .

#### **Design Example**

Table 1 shows a design example when using the MPX2003 for a 65W PD charger application.

**Table 1: Design Specifications**

| Parameter      | Symbol           | Value                                     |

|----------------|------------------|-------------------------------------------|

| Input          | Vin              | 90V <sub>AC</sub> to 265V <sub>AC</sub> , |

| specifications | V 111 V          | 47Hz to 63Hz                              |

| Output         |                  | $5V_{DC}$ / 0A to 3A,                     |

|                | Vout /           | $9V_{DC}$ / 0A to 3A,                     |

| specifications | I <sub>OUT</sub> | $12V_{DC}$ / 0A to 3A,                    |

| specifications | IOUT             | $15V_{DC}$ / 0A to 3A,                    |

|                |                  | 20V <sub>DC</sub> / 0A to 3.25A           |

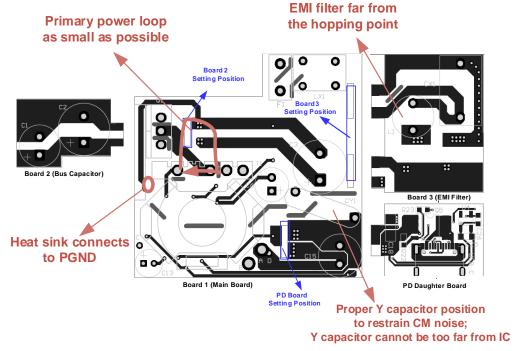

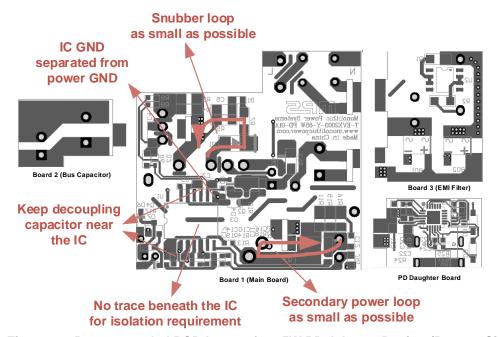

#### **PCB Layout Guidelines**

PCB layout is vital to achieve reliable operation, as well as excellent EMI performance and efficient thermal performance. For the best results, follow the guidelines below and refer to Figure 23 and Figure 24 on page 32:

- Minimize the power stage loop area, including the primary power loop (C1, C2, C3 T1- Q1 R3, R4 C1), the snubber loop (T1 D1 R7 B1 R5, C5 T1), and the secondary power loop (T1 C15 Q3 T1).

- 2. Separate the IC GND and power GND.

- 3. Connect the heat sink to the primary GND plane to improve EMI and thermal dissipation.

- Place the decoupling capacitors (for VCC, PEP, CS, COMP, VDD, and FB) close to the IC.

- Route the EMI filter far from the hopping point.

- 6. Ensure that there is no trace beneath the IC for isolation requirements.

- 7. Keep the Y-capacitor as close as possible to the IC to reduce CM noise.

Figure 23: Recommended PCB Layout for 65W PD Adapter Design (Top Side)

Figure 24: Recommended PCB Layout for 65W PD Adapter Design (Bottom Side)

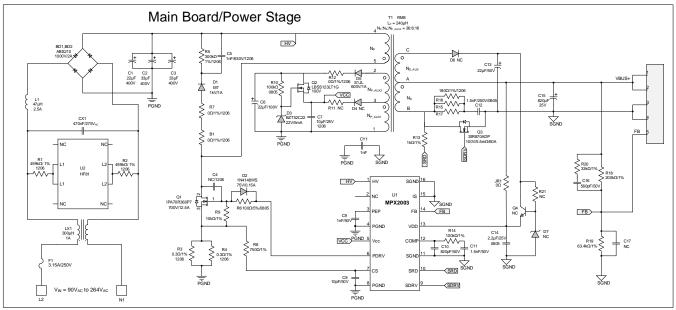

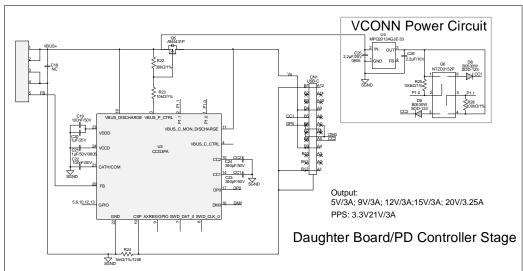

#### TYPICAL APPLICATION CIRCUIT

Figure 25 shows the MPX2003's typical application circuit with a universal input and 65W output specification.

Figure 25: Example of the 65W PD Typical Application

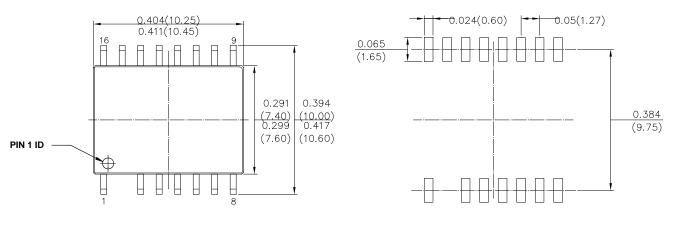

#### **PACKAGE INFORMATION**

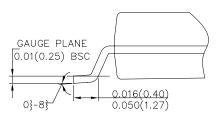

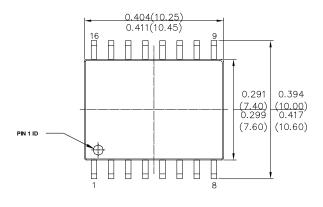

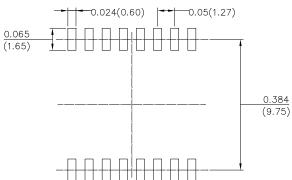

#### **TSOICW16-15**

**TOP VIEW**

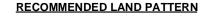

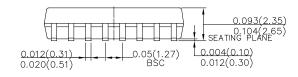

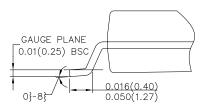

RECOMMENDED LAND PATTERN

**DETAIL "A"**

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING REFERENCE TO JEDEC MS-013, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

# PACKAGE INFORMATION (continued)

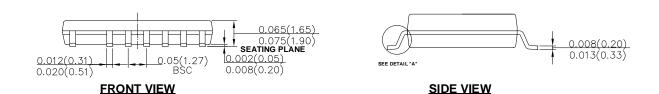

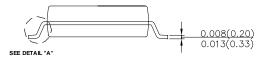

#### SOICW-16

#### **TOP VIEW**

#### **FRONT VIEW**

**SIDE VIEW**

DETAIL "A"

#### NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-013, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

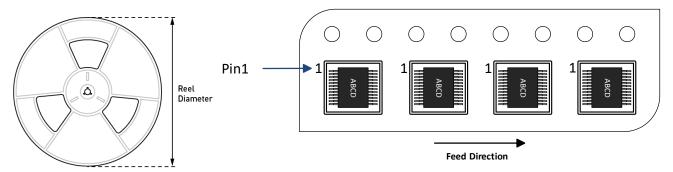

# **CARRIER INFORMATION**

| Part Number  | Package<br>Description | Quantity/<br>Reel | Quantity/<br>Tube | Reel<br>Diameter | Carrier<br>Tape<br>Width | Carrier<br>Tape<br>Pitch |

|--------------|------------------------|-------------------|-------------------|------------------|--------------------------|--------------------------|

| MPX2003GYT-Z | TSOICW16-15            | 1000              | 4.4               | 13in             | 24mm                     | 12mm                     |

| MPX2003GY-Z  | SOICW-16               | 1000              | 44                | 13111            | 24mm                     | 1211111                  |