## MiniRISC<sup>™</sup> MR4010 Superscalar Microprocessor

**Reference Device**

| Contents | 1             | MR4     | 010 Features                                    | 7  |

|----------|---------------|---------|-------------------------------------------------|----|

|          | 2             | MR4     | 010 Functional Blocks                           | 9  |

|          |               | 2.1     | CW4010 Shell                                    | 10 |

|          |               | 2.2     | Synchronous DRAM Controller (DRAMC)             | 12 |

|          |               | 2.3     | SCbus to Local I/O Bus (Lbus) Controller (SCLC) | 12 |

|          |               | 2.4     | PLL Clock Circuit                               | 12 |

|          | 3             | MR4     | 010 Programming Model                           | 13 |

|          | 4             | Sign    | al Descriptions                                 | 13 |

|          |               | 4.1     | SCbus Interface                                 | 14 |

|          |               | 4.2     | External Buffering for SCbus Signals            | 21 |

|          |               | 4.3     | CW4010 Shell Interface                          | 24 |

|          |               | 4.4     | Mbus Interface                                  | 26 |

|          |               | 4.5     | Lbus Interface                                  | 28 |

|          |               | 4.6     | Phase-Locked Loop (PLL) Clock Signals           | 31 |

|          |               | 4.6     | Test Signals                                    | 32 |

|          |               | 4.7     | CW4010 Core Monitor Signals                     | 33 |

|          | 5 PLL Circuit | Circuit | 36                                              |    |

|          | 6 5           | Syst    | em Configuration                                | 37 |

|          |               | 6.1     | CW4010 CCC Register                             | 37 |

|          |               | 6.2     | Lbus Controller Registers                       | 41 |

|          | 7             | MR4     | 010 Memory Map                                  | 42 |

|          | 8             | CW4     | 1010 Instruction Set Summary                    | 43 |

|          | 9             | DRA     | M Controller and Memory Bus                     | 55 |

|          |               | 9.1     | DRAM Types and Available DRAM Address Area      | 55 |

|          |               | 9.2     | Memory Interface                                | 56 |

|          |               | 9.3     | Address Bit Assignment                          | 58 |

|          |               | 9.4     | DRAM Modes and Programmable Configurations      | 59 |

|          |               | 9.5     | DRAM Refresh                                    | 67 |

|          |               | 9.6     | DRAM Commands                                   | 69 |

|          |               | 9.7     | Initializing the DRAM and Programming the Mode  |    |

|    |       | Register                                    | 71 |

|----|-------|---------------------------------------------|----|

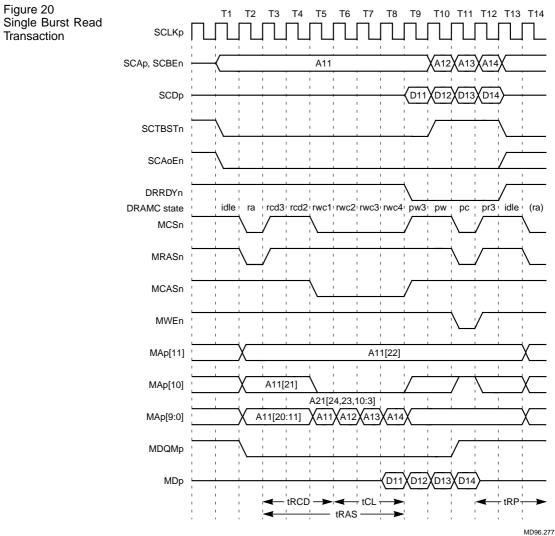

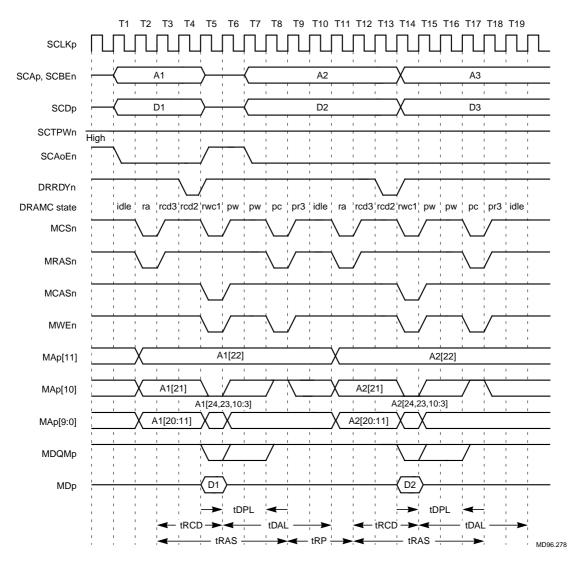

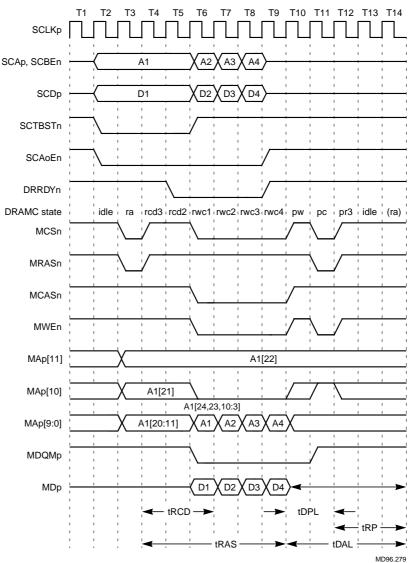

|    | 9.8   | DRAM Transactions                           | 76 |

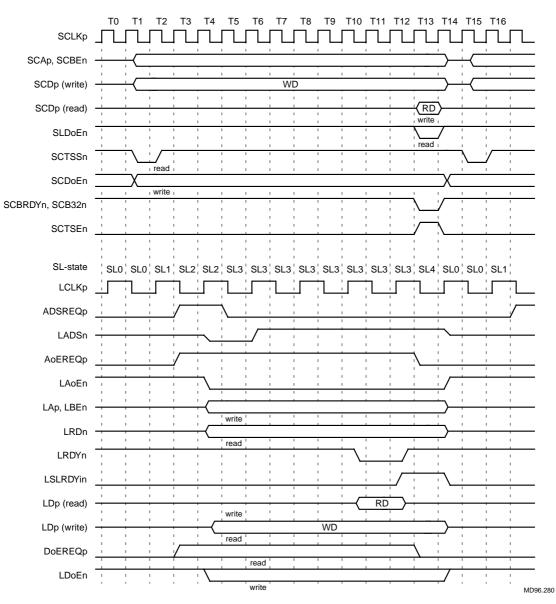

| 10 | Loca  | I I/O bus and SCbus/Lbus Converter Module   | 80 |

|    | 10.1  | Lbus Features                               | 80 |

|    | 10.2  | MR4010 as Master on the Lbus                | 81 |

|    | 10.3  | MR4010 as Slave on the Lbus                 | 83 |

|    | 10.4  | SCbus Timeout Watchdog Timer                | 85 |

|    | 10.5  | External Vectored Interrupt (EVInt) Support | 86 |

| 11 | Cach  | e Configuration and Maintenance             | 87 |

|    | 11.1  | Cache Configuration                         | 87 |

|    | 11.2  | Cache Maintenance                           | 89 |

| 12 | Orga  | nization of Specific Internal Signals       | 89 |

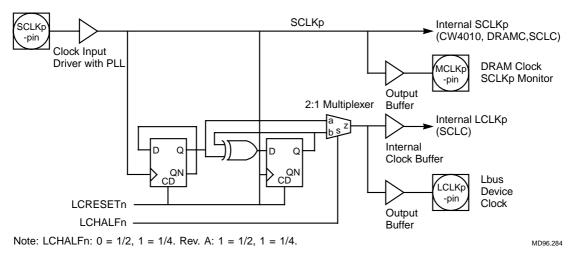

|    | 12.1  | Clock Circuitry                             | 89 |

|    | 12.2  | Exception Inputs                            | 91 |

| 13 | Elect | rical Characteristics                       | 93 |

| 14 | Pack  | age Information                             | 96 |

| Figures |  |

|---------|--|

|---------|--|

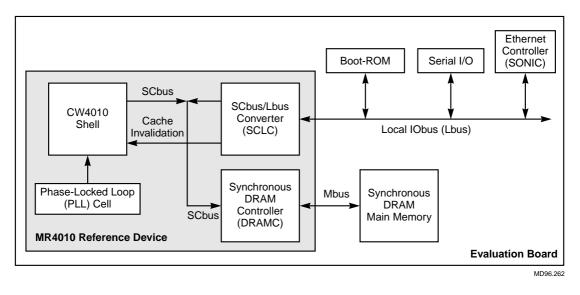

| 1  | Block Diagram of MR4010 and Evaluation Board Circuitry    | - 7             |

|----|-----------------------------------------------------------|-----------------|

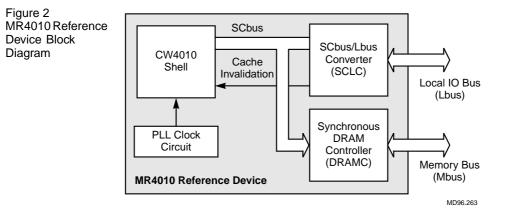

| 2  | MR4010 Reference Device Block Diagram                     | 9               |

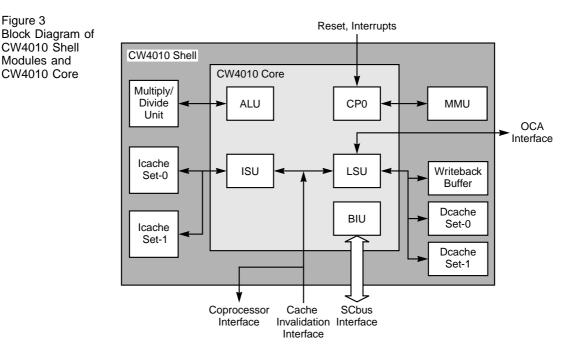

| 3  | Block Diagram of CW4010 Shell Modules and CW4010 Core     | 10              |

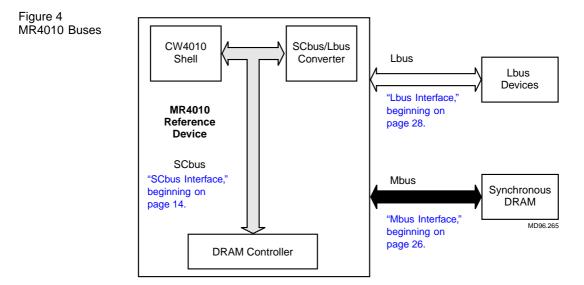

| 4  | MR4010 Buses                                              | 14              |

| 5  | SCbus Interface                                           | 15              |

| 6  | Buffering for SCAp[31:0] Address Bus                      | 21              |

| 7  | Buffering for SCDp[63:0] Data Bus                         | 22              |

| 8  | Buffering for SCBEn[7:0] Byte Enable                      | 23              |

| 9  | Shell Interface Overview                                  | 24              |

| 10 | Mbus and Lbus Interface                                   | 27              |

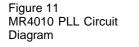

| 11 | MR4010 PLL Circuit Diagram                                | 36              |

| 12 | CW4010 CCC Register                                       | 37              |

| 13 | MR4010 Master/Slave Memory Map                            | 43              |

| 14 | MR4010 Interface with DRAM                                | 57              |

| 15 | SCbus DRAM Address Bit Assignment                         | 58              |

| 16 | DRAM Mode Register Format                                 | 60              |

| 17 | DRAM Controller Configuration Register Format             | 62              |

| 18 | DRAM Refresh Interval Timer                               | <mark>68</mark> |

| 19 | Timing Requirements for the DRAM Initialization Sequence  | 75              |

| 20 | Single Burst Read Transaction                             | 77              |

| 21 | Two Continuous Single Write Transactions                  | 78              |

| 22 | Burst Write Transaction                                   | 79              |

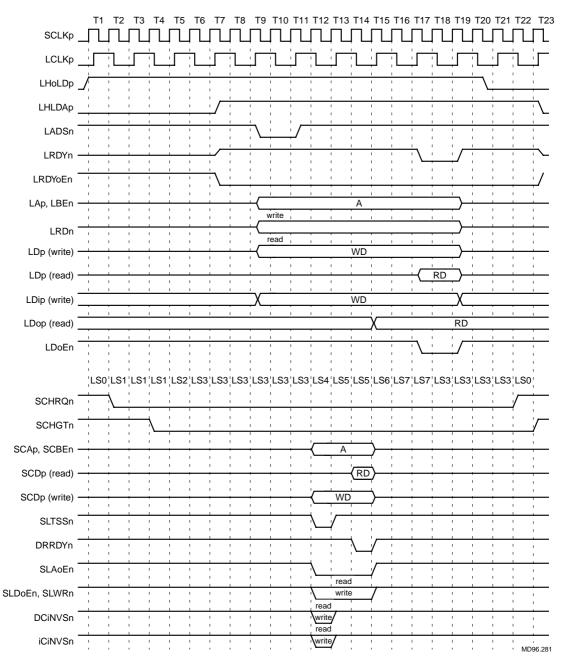

|    | Timing Requirements for an SCbus-to-Lbus Transaction      | 82              |

| 24 | Timing Requirements for Lbus-to-SCbus Transaction         | 84              |

|    | SCbus Error Address and Status Register Bit Format        | 85              |

|    | External Vectored Interrupt Register Bit Format           | 86              |

| 27 | MR4010 PLL Clock Circuitry                                | 90              |

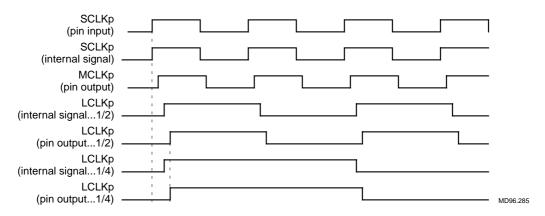

| 28 | Timing Requirements for the CW4010 and Lbus Clocks        | 91              |

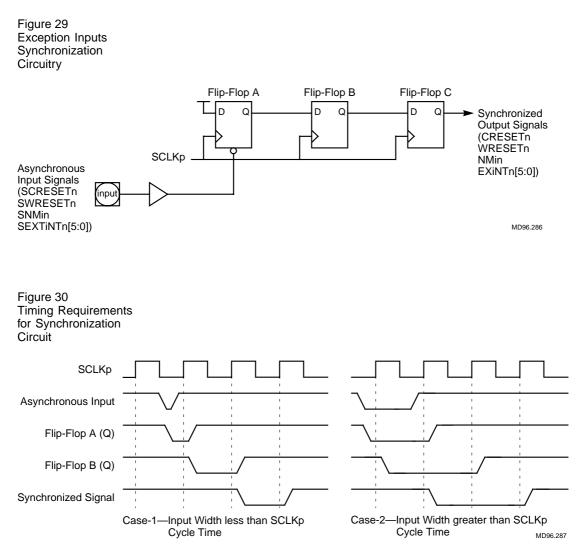

|    | Exception Inputs Synchronization Circuitry                | 92              |

|    | Timing Requirements for Synchronization Circuit           | 92              |

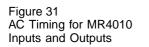

| 31 | AC Timing for MR4010 Inputs and Outputs                   | 96              |

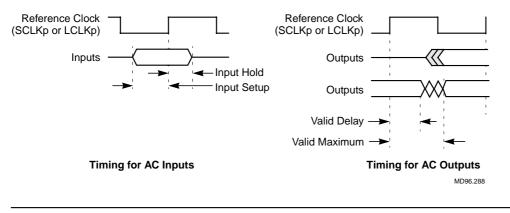

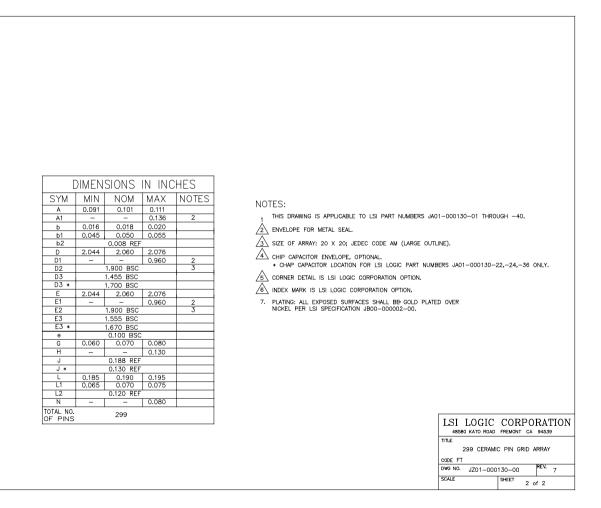

| 32 | Mechanical Drawing of the 299-Pin CPGA (FT) MR4010 Device | 97              |

## Tables

| 1  | Bus Error Internal Registers                      | 42 |

|----|---------------------------------------------------|----|

| 2  | MR4010 (CW4010) Instruction Set Summary           | 44 |

| 3  | DRAM Configurations                               | 56 |

| 4  | SCbus Address and Mbus Address Bit Assignment     | 59 |

| 5  | Relationship Between Frequency and Latency        | 67 |

| 6  | Refresh Register Programming Values               | 69 |

| 7  | Summary of DRAM Commands and Mbus Control Signals | 70 |

| 8  | Timing Signals                                    | 73 |

| 9  | Timing Diagram Abbreviations                      | 74 |

| 10 | Cache Size and Accessing                          | 88 |

| 11 | Dcache Scratchpad RAM Configuration               | 88 |

| 12 | Icache Scratchpad RAM Configuration               | 89 |

| 13 | Summary of MR4010 Clocks                          | 91 |

| 14 | Absolute Maximum Ratings                          | 93 |

| 15 | Recommended Operating Conditions                  | 93 |

| 16 | Input/Output Capacitance                          | 93 |

| 17 | DC Characteristics                                | 94 |

| 18 | MR4010 AC Timing Specifications                   | 95 |

| 19 | MR4010 Pin Assignments                            | 99 |

|    |                                                   |    |

Overview The MiniRISC MR4010 Microprocessor Reference Device is a chip implementation of the MiniRISC CW4010 Microprocessor core and shell. The MR4010 contains the following circuitry:

- The CW4010 shell, which is an unencrypted Verilog model containing the CW4010 core, the Multiply/Divide unit, Instruction cache (Icache), Data cache (Dcache), Memory Management Unit (MMU), and a Writeback Buffer

- A DRAM Controller (DRAMC) that controls the memory bus and an external synchronous DRAM array

- An SCbus/Lbus Converter (SCLC) that controls the Local I/O bus and external Lbus devices

- A Phase-Locked Loop (PLL) circuit that supplies clock inputs to the other modules in the MR4010

The MR4010 uses the maximum configuration CW4010 shell. You can disable optional modules by programming the Configuration Register in the CW4010 core's Coprocessor 0 (CP0). "MR4010 Functional Blocks," starting on page 9, provides further information about the different elements of the MR4010.

The MR4010 is housed on an evaluation board that allows you to use and test the microprocessor. In addition to the MR4010 Reference Device, the board also contains the DRAM array and Lbus facilities for plugging in devices such as a Boot-ROM, serial I/O devices, and an external Ethernet Controller. Figure 1 provides a block diagram of the MR4010 evaluation board circuitry. Figure 1 Block Diagram of MR4010 and Evaluation Board Circuitry

1 MR4010 Features The MR4010 Reference Device has the following features:

- Superscalar microprocessor supports the MIPS-II 32-bit instruction set:

- Executes up to two instructions per clock cycle

- Four-deep write buffer

- Load scheduling

- R3000/R4000 compatible mode for Exception Return and Status Register

- 32-bit timer (R4000 compatible)

- SCbus watchdog timer with error reporting features

- Full internal scan testing

- ♦ Local IObus (Lbus) interface

- Subset of the VLbus (486 bus); does not have I/O space, data/code, INTA, support for burst transactions

- Demultiplexed 32-bit address bus and 32-bit data bus

- ◆ Direct interface to the SONIC<sup>™</sup> Ethernet Controller

- Synchronous DRAM Controller, with 64-bit wide data transfer, interfaces to the following 16-Mbit DRAMs:

- 1-Mword x 16-bit DRAM devices in an 8-Mbyte or 16-Mbyte configuration

- 2-Mword x 8-bit DRAM devices in a 16-Mbyte or 32-Mbyte configuration

- 4-Mword x 4-bit DRAM devices in an 32-Mbyte or 64-Mbyte configuration

- PLL circuit for system clock

- 3.3 V operation

- Up to 66 MHz microprocessor clock

- Packaged in a 299-pin CPGA (ceramic pin-grid array package)

- Maximum CW4010 configuration:

- Direct-mapped or two-way set-associative Icache and Dcache

- 1-Kbyte, 2-Kbyte, 4-Kbyte, or 8-Kbyte cache sets; organized as either direct-mapped (single set) cache with maximum cache size of 8 Kbytes, or as two-way set-associative cache with a maximum cache size of 16 Kbytes.

- Memory management unit with 32-entry fully associative TLB (translation lookaside buffer)

- Fast multiplier supporting multiply-accumulate operations

2 This section describes the functional blocks that make up the MR4010

MR4010 Reference Device:

Functional

## " ◆ (

Blocks

- CW4010 shell

- SCbus/Lbus Converter

- DRAM Controller

- PLL clock circuit

Figure 2 shows the relationship between these blocks.

## 2.1 CW4010 Shell

Figure 3

CW4010 Shell

Modules and CW4010 Core The CW4010 shell consists of the CW4010 core and a number of optional modules, including Icache, Dcache, the Multiply/Divide unit, the MMU (Memory Management Unit), and the Writeback Buffer. You can modify the modules in the shell to fit your own ASIC design. Figure 3 shows a block diagram of the shell modules.

## 2.1.1 CW4010 Core

The CW4010 core is part of LSI Logic's CoreWare® Library. It is an encrypted synthesizable Verilog model. As shown in Figure 3, it contains the basic microprocessor elements:

- Arithmetic Logic Unit (ALU)

- Instruction Scheduling Unit (ISU)

- Load/Store Unit (LSU) ٠

- Bus Interface Unit (BIU)

- Coprocessor 0 (CP0)

The core is a hardmacro. It remains the same for each ASIC design, and can easily be reused.

The CW4010 core executes all MIPS-II 32-bit based instructions except for multiply/divide instructions, which are handled by the Multiply/Divide unit. The microprocessor is implemented as efficient dual six-stage pipelines. The pipelines have the traditional instruction fetch and execution stages. An additional queuing (Q) stage (one of the instruction fetch stages) removes the penalty cycle when a branch instruction is executed. Standard MIPS compiled code for R3000 and R4000 processors runs on the CW4010 core.

The CW4010 has an extended instruction set and implements ADDCIU (Add with Circular Mask Immediate Unsigned), MADD/MADDU (Multiply Accumulate (Unsigned)), MSUB/MSUBU (Multiply Subtract (Unsigned)), FFS/FFC (Find First Set/Clear Bit), SELSR/SELSL (Select and Shift Right/Left), WAITI (Wait Interrupt) and FLUSHID (Flush Instruction/Data Cache) instructions.

## 2.1.2 Multiply/Divide

The multiply/divide module supports Multiply-Add/Subtract operations as well as Multiply and Divide. The Multiply instruction executes in three cycles. The Multiply-Add/Subtract instruction is optimized to two cycles.

## 2.1.3 Memory Management Unit (MMU)

The MMU has 32 single-page entries, which are a subset of the R4000 32-bit addressing mode. Each page is individually specified to be 4 Kbyte or 16 Mbyte and may be cached or uncached.

## 2.1.4 Writeback Buffer

The CW4010 uses this buffer when the Dcache operates in Writeback mode. When a cache miss occurs at a dirty line, the dirty data is written into the Writeback Buffer instead of the main memory. This reduces the latency of the cache refill for missed addresses. Data in the Writeback Buffer is written into the main memory after the refill is completed.

## 2.1.5 Caches

The MR4010 has separate instruction and data caches—Icache and Dcache—that are part of the CW4010 shell. Both caches can be organized as direct-mapped or two-way set-associative caches. The cache controllers support configurations of 1, 2, 4, or 8 Kbytes for each set.

Thus, the smallest supported configuration is a 1 Kbyte direct-mapped cache, and the largest is a 16 Kbyte two-way set-associative cache, with 8 Kbytes per set. You can select between Writeback and Writethrough modes. You can also configure the Dcache for scratch pad RAM mode.

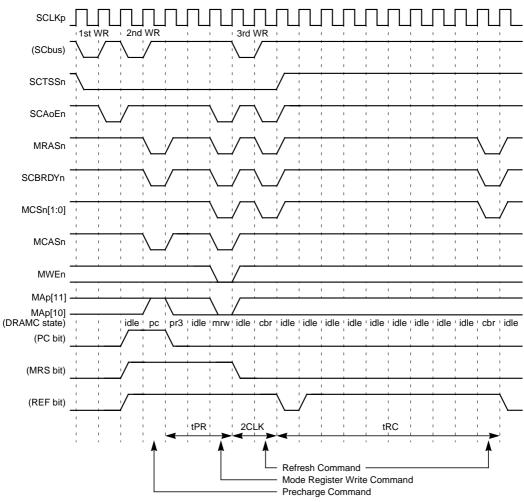

2.2The DRAM Controller is part of the MR4010 Reference Device externalSynchronousto the CW4010 shell. It generates DRAM transactions according toDRAMrequests from the CW4010 core or from the SCLC module. The DRAMControllerController also generates initialization cycles and refresh cycles for(DRAMC)DRAM.

2.3The SCLC module is part of the MR4010 Reference Device external toSCbus to Localthe CW4010 shell. It provides an interface between the internal CW4010I/O Bus (Lbus)microprocessor bus, (SCbus), and the external Local I/O bus (Lbus). TheControllerLbus connects boot-ROM, serial I/O devices, and the Ethernet Controller(SCLC)to the MR4010.

The CW4010 SCbus is a 32-bit address, 64-bit data bus. The Lbus, which is a subset of the industrial standard VLbus, is a 32-bit address, 32-bit data bus. The CW4010 uses the SCLC module to access devices on the Lbus. Devices on the Lbus access the DRAM main memory through the SCLC module and the DRAM Controller.

The CW4010 microprocessor generally has ownership of the SCbus and the Lbus. When a device on the Lbus wants to access the DRAM, it asserts the bus hold request signal on the Lbus. The SCLC module detects the asserted signal and then asserts the bus hold request to the CW4010. The CW4010 asserts the grant signal to the SCLC module, and the SCLC module then asserts the hold acknowledge signal to the Lbus device.

2.4The PLL circuit is part of the MR4010 Reference Device external to thePLL ClockCW4010 shell. It drives the clock signals to the CW4010 shell and the<br/>other modules that are part of the MR4010.

| 3<br>MR4010<br>Programming<br>Model | <ul> <li>The term 'programming model' refers to the way data is arranged in registers and in memory. You will find information on these subjects in the following areas of this technical summary:</li> <li>"System Configuration" on page 37</li> <li>"DRAM Modes and Programmable Configurations" on page 59</li> <li>"SCbus Timeout Watchdog Timer" on page 85</li> <li>"Cache Configuration and Maintenance" on page 87</li> <li>In addition, <i>MiniRISC CW4010 Superscalar Microprocessor Core Technical Manual</i> provides information about the Memory Management Unit and Coprocessor 0 (CP0).</li> </ul>                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>Signal<br>Descriptions         | <ul> <li>This section describes the MR4010 signals in the following groupings:</li> <li>SCbus Interface <ul> <li>The interface between the CW4010 shell and the DRAMC and the SCLC module implemented by means of the SCbus.</li> <li>External buffering required for certain SCbus signals.</li> </ul> </li> <li>CW4010 Shell Interface <ul> <li>Other signals that interface between the CW4010 shell and the DRAMC and SCLC.</li> </ul> </li> <li>Mbus Interface <ul> <li>The interface between the DRAM Controller and the DRAM array, with inputs and outputs referenced to the MR4010 Reference Device.</li> </ul> </li> <li>Lbus Interface <ul> <li>The interface between the SCLC and devices on the Lbus, with inputs and outputs referenced to the MR4010 Reference Device.</li> </ul> </li> <li>Phase-Locked Loop (PLL) Interface <ul> <li>The interface between the PLL clock generator and the CW4010 shell.</li> </ul> </li> </ul> |

Test Signals

Input pins that allow LSI Logic to test the MR4010.

• Core Monitor Signals

Output signals that allow you to monitor the behavior of the CW4010 core.

Figure 4 shows the three major buses.

Each signal definition contains the mnemonic and the full signal name. Active LOW signals have an 'n' suffix, for example, SCRESETn. Active HIGH signals have a 'p' suffix, for example, MDQMp. 'Assert' means to drive the signal TRUE or active. 'Deassert' means to drive the signal FALSE or inactive.

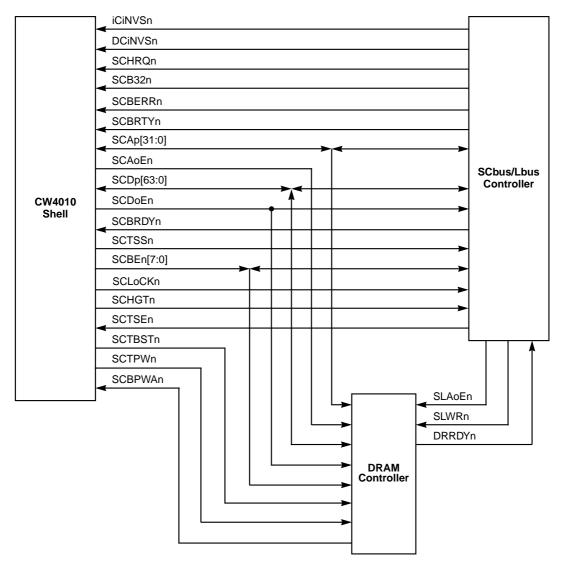

## 4.1 SCbus Interface

Figure 5 shows how the CW4010 shell uses the SCbus to interface with the MR4010 Reference Device's SCLC module and DRAM Controller. In the interface between the CW4010 and the SCLC, either module can function as the bus master or slave. In the interface between the CW4010 and the DRAM Controller, the CW4010 is always the master.

Figure 5 also shows the cache invalidation signals input to the CW4010 shell from the SCLC, and the address and write enable signal interface and the bus ready signal interface between the DRAMC and the SCLC.

You will need to provide external buffering for certain SCbus signals. "External Buffering for SCbus Signals" on page 21 provides information on this subject.

## Figure 5 SCbus Interface

- SCHRQn Bus Hold Request Input to Shell from SCLC SCHRQn indicates that a device on the Lbus is requesting ownership of the SCbus. Bus hold request has the highest priority during bus arbitration. However, it cannot break continuous transactions of in-page writes and burst read/write transactions if those transactions are supported by an asserted SCTSEn, and SCHRQn must wait until SCTSEn is deasserted.

- SCB32n 32-Bit Bus Width Sizing Input to Shell from SCLC SCB32n indicates that the external bus slave on the SC bus needs 32-bit bus sizing. The CW4010 core samples this signal on the rising edge of the clock that synchronizes the SCbus ready signal, SCBRDYn. If SCB32n is asserted for a 64-bit transaction, which is a doubleword or part of a burst transaction, the bus interface unit in the CW4010 core generates a subsequent 32-bit word transaction and packs data to 64 bits for a read transaction or unpacks data to 32 bits for a write transaction.

## SCBERRnBus ErrorInput to Shell from SCLCThe Lbus master device asserts SCBERRn to terminate<br/>the current transaction when a bus error occurs. If<br/>SCBRDYn, or the bus retry signal, SCBRTYn, is asserted<br/>at the same time as SCBERRn, SCBERRn has higher<br/>priority. SCBERRn is reported to the CP0 and the CP0<br/>generates an exception.

# SCBRTYnBus RetryInput to Shell from SCLCThe Lbus master device asserts SCBRTYn when the<br/>current transaction has been terminated unsuccessfully<br/>and must be retried later. The control state goes back<br/>once to the idle state, then all bus requests are arbitrated<br/>again. If there are no higher priority requests and the<br/>Lbus master has asserted SCTSEn, there is one idle<br/>state between the first transaction and a retry transaction.<br/>If SCBRDYn and SCBRTYn are asserted at the same<br/>time, SCBRTYn has the higher priority.

## SCAp[31:0] Address Bus Bidirectional between Shell and SCLC Input to DRAMC

SCAp[31:0] is the 32-bit address bus for instruction fetch and data read/write operations. The bus signals are valid only when the address output enable signal, SCAoEn, is asserted. The enable signal remains valid throughout the

operation until SCBRDYn, SCBRTYn, or SCBERRn is asserted. The CW4010 asserts the signals on this bus and outputs them to the SCLC or the DRAMC. The Lbus master can also assert SCAp[31:0] and output them to the CW4010 shell through the SCLC.

SCAoEn Address Output Enable Output from Shell to DRAMC When the CW4010 asserts this signal, it indicates that the address bus lines, SCAp[31:0], are valid. The signal remains active throughout the bus transaction. SCAoEn also enables SCTBSTn, SCTBEn, and SCTPWn. This signal is not valid at the same time as SLAoEn, which is the Address Output Enable signal output from the SCLC shell to the DRAMC described on page 20.

## SCDp[63:0] Data Bus Bidirectional between Shell, SCLC, and DRAMC

SCDp[63:0] are the data bus signals. They are output from the shell for data read/write operations and for data Writeback to the Dcache. They are input to the shell for data read and instruction fetch transactions. The CW4010 shell samples the signals on the rising edge of the clock when SCBRDYn is asserted. The signals are valid throughout a write transaction where the CW4010 is writing to DRAM through the DRAMC, or the Lbus device is writing to the CW4010 or DRAMC through the SCLC. Byte ordering is little endian.

## SCDoEn Data Output Enable Output from Shell to SCLC and DRAMC

The CW4010 asserts SCDoEn throughout a write transaction and outputs it to the SCLC or the DRAMC. The signal indicates that the current transaction is a write transaction, and it also enables data output. It performs the same function for a CW4010 write transaction to DRAM that SLWRn (page 20) performs for an SCLC write transaction to DRAM.

SCTSSn Transaction Start Strobe Output from Shell to SCLC The CW4010 asserts SCTSSn for one clock cycle at the beginning of a transaction to indicate that a transaction has started. If the next transaction begins immediately, the CW4010 asserts SCTSSn continuously.

## SCBEn[7:0] Byte Enable Bidirectional between Shell and SCLC and input to DRAMC

SCBEn[7:0] indicate which byte positions are valid for a read or write transaction. The CW4010 asserts the signals and outputs them to the SCLC or the DRAMC. The Lbus device can also assert the signals and input them to the CW4010 through the SCLC. Only one of the signals is asserted during a byte read or byte write transaction. All signals are asserted for a doubleword or burst transaction.

SCTBSTn Burst Transaction Output from Shell to DRAMC The CW4010 asserts SCTBSTn and outputs it to the DRAMC to indicate that a transaction is taking place during which four doublewords will be moved, and that the first doubleword is currently being moved. It deasserts the signal after the first word has been transferred and during singleword transactions.

## SCI oCKn Bus Lock Output from Shell to SCLC The CW4010 asserts SCLoCKn to indicate that it wishes to lock the SCbus and restrict ownership. The CW4010 asserts the signal when a read transaction is started by executing a LoadLink instruction in an uncached area or a Writethrough cached area. It deasserts the signal just before a write transaction is started by executing a Store-Conditional instruction. During read and write transactions, the CW4010 asserts the signal continuously, preventing ownership from changing during one of these transactions. If a StoreConditional transaction hits the Dcache in a Writeback cached read while SCLoCKn is asserted, an incorrect condition exists, and the CW4010 deasserts SCLoCKn without completing any bus transactions.

## SCTPWn Next Transaction is In-Page Write Output from Shell to DRAMC

When asserted, this signal indicates that the next transaction is in the same DRAM page as defined in the Configuration Register. When the CW4010 asserts SCTPWn, a maximum of four write transactions take place one after the other, even if there is an instruction fetch request or data read request. If there are four continuous write transactions, the CW4010 asserts SCTPWn from the first through the last (fourth)

transaction. The CW4010 asserts SCTPWn from the beginning of one in-page write transaction to the end of that transaction. The write buffer in the CW4010's LSU checks to see if the subsequent write request is in the same page.

- SCHGTnBus Hold GrantOutput from Shell to SCLCThe CW4010's bus interface unit enters the hold state<br/>and asserts SCHGTn to indicate that it is releasing<br/>SCbus ownership in response to a bus hold request<br/>(SCHRQn) from one of the devices on the Lbus.

- SCTSEN Transaction Start Enable Input to Shell from SCLC SCTSEn enables or disables a new SCbus transaction. Transaction requests are arbitrated only when SCTSEn is asserted. The Lbus device must deassert then assert the signal when SCBRDYn is asserted to allow an idle cycle between the two transactions. During the time SCTSEn is deasserted, the CW4010's bus interface unit repeats the idle state.

- SCBRDYnBus ReadyInput to Shell from SCLCThe SCLC asserts SCBRDYn when the current transaction is terminated, indicating that the SCbus is available.The signal remains active (LOW) until the nextThe signal remains active (LOW) until the nexttransaction starts. The SCLC deasserts the signal toindicate that the SCbus is not available.The SCLCreceives a bus-ready signal, DRRDYn from the DRAMC(see page 20), merges DRRDYn with its own bus readysignal, and drives SCBRDYn, which is output to theCW4010 shell.

## SCBPWAn Bus In-Page Write Accept Input to Shell from DRAMC

The DRAMC asserts SCBPWAn to indicate that it accepts in-page write transactions. The CW4010 samples the signal on the rising edge of the clock that synchronizes SCBRDYn. If the CW4010 has not asserted SCTPWn, asserting or deasserting SCBPWAn has no significance.

## iCiNVSn Icache Invalidation Strobe

www.DataSheet4U.com

## Input to Shell from SCLC

The SCLC asserts this signal to indicate that the Icache invalidation address bus is valid and there is no need for a snooping sequence. If the cache tag is not coincident with higher address bits, the line is not invalidated.

## DCiNVSn Dcache Invalidation Strobe Inpu

## Input to Shell from SCLC

The SCLC asserts this signal to indicate that the Dcache invalidation address bus is valid and there is no need for a snooping sequence. If the cache tag is not coincident with higher address bits, the line is not invalidated.

## SLAoEn Address Output Enable Output from SCLC to DRAMC

When the SCLC asserts this signal, it indicates that the address bus lines, SCAp[31:0], are valid. The signal remains active throughout the bus transaction. SCAoEn also enables SCTBSTn, SCTBEn, and SCTPWn. This signal is not valid at the same time as SCAoEn, which is the Address Output Enable signal output from the CW4010 shell to the SCLC described on page 17.

- SLWRN SCLC Write Enable Output from SCLC to DRAMC The SCLC asserts this signal throughout a DRAM write operation and outputs it to the DRAMC. It performs the same function for a CW4010 write transaction to DRAM that SLWRn (page 17) performs for an SCLC write transaction to DRAM.

- DRRDYn DRAM Ready Output from DRAMC to SCLC The DRAMC asserts DRRDYn when the current DRAM transaction is terminated, indicating that the bus is available. The signal remains active (LOW) until the next transaction starts. The DRAMC outputs the signal to the SCLC, which merges DRRDYn with its own bus ready signal (see page 19), and drives SCBRDYn, which is output to the CW4010 shell.

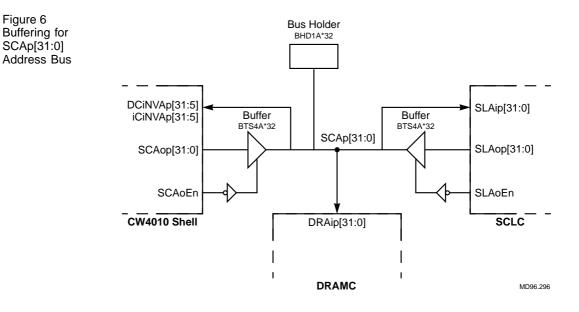

You must provide external buffering for certain SCbus signals, including

## 4.2 External Buffering for SCbus Signals

- Address bus SCAp[31:0]

- Address output enable signal SCAoEn and SLAoEN

- SC data bus SCDp[63:0]

- Data output enable SCDoEn

- SCbus byte enable SCBEn[7:0]

Figure 6 shows an example of a buffer configuration in which the bidirectional address bus is buffered at the SCLC and CW4010 ends by BTS4A\*32 3-state buffers. When the CW4010 asserts SCAoEn, the signal enables the buffer at the CW4010 end. When the SCLC asserts SLAoEn, the signal enables the buffer at the SCLC end.

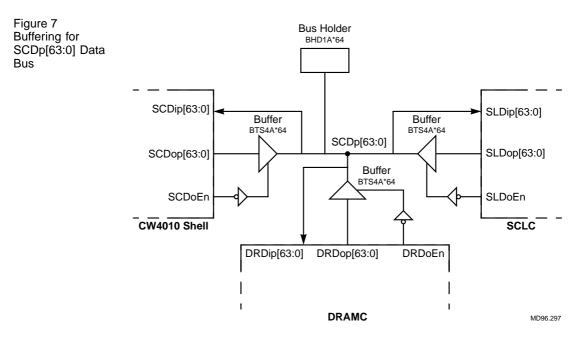

Figure 7 shows an example of a buffer configuration in which the SC data bus is buffered at the SCLC and CW4010 ends by BTS4A\*64 3-state buffers. When the CW4010 asserts SCDoEn, the signal enables the buffer at the CW4010 end. When the SCLC asserts SLDoEn, the signal enables the buffer at the SCLC end. A BTS4A\*64 buffer also buffers the data output from the DRAMC. This buffer is enabled when the DRAMC asserts DRDoEn.

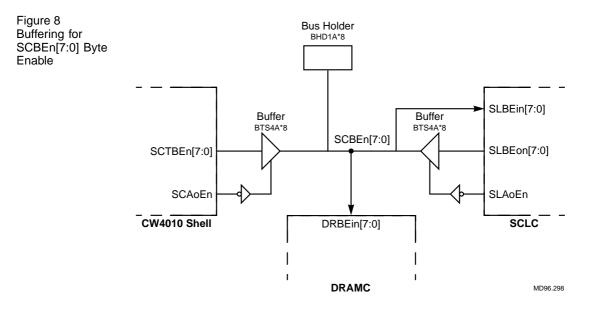

Figure 8 shows an example of a buffer configuration in which the SC byte enable signals, SCTBEn[7:0], are buffered at the SCLC and CW4010 ends by BTS4A\*8 3-state buffers. When the CW4010 asserts SCAoEn, the signal enables the buffer at the CW4010 end. When the SCLC asserts SLAoEn, the signal enables the buffer at the SCLC end.

## 4.3 CW4010 Shell Interface

Figure 9

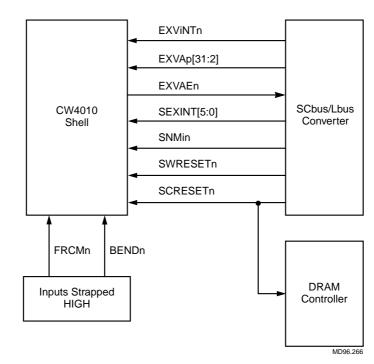

Shell Interface Overview Figure 9 shows the internal interface that links the CW4010 shell, the SCLC, and the DRAMC. "SCbus Interface" beginning on page 14 describes the SCbus interface between these modules.

**EXVINTn** External Vectored Input Input to Shell from SCLC The SCLC drives this signal. When the CW4010 shell receives the signal, it generates an external interrupt exception.

## EXVAp[31:2]

**External Vectored Interrupt Address** Input to Shell The CW4010 shell accepts the external vectored interrupt address when the SCLC asserts EXVApEn. The CW4010 writes the address directly into the program counter. The address bus must remain stable until EXVApEn is asserted.

EXVAEn EXVAp Enable Output from Shell to SCLC This is the enable signal for the vectored interrupt address. The CW4010 asserts this signal to acknowledge the address.

## SEXiNTn[5:0]

## External Interrupt Input [5:0]

## Input to Shell

The DRAMC or SCLC asserts one of the SEXiNTn signals to cause the CP0 in the CW4010 core to generate an interrupt exception. The assertion is registered in the IP field of the CW4010 Cause Register. The SCLC should continue to assert the signals until the exception routine has serviced the interrupt.

The CW4010 does not recognize interrupts if the interrupt enable bit in the Status Register is not set. The CW4010 can therefore disable individual interrupt inputs by clearing the related bits. However, the interrupt inputs are still registered in the IP field of the Cause Register.

External Interrupt Input [5:0] are synchronized to the system clock, SCLKp, internally in the CW4010 shell.

SNMinNonmaskable InterruptInput to ShellThis input is synchronized internally to the system clock,<br/>SCLKp. When the SCLC asserts this signal, the CW4010<br/>recognizes a nonmaskable interrupt. The CP0 then<br/>generates a nonmaskable interrupt exception<br/>(0xBFC0 0000).

## SWRESETN Warm Reset Input to Shell This input initiates a warm reset for the MR4010. Inside the MR4010, this signal is synchronized to the system clock, SCLKp. The MR4010 enters the warm reset condition when the SCLC asserts SWRESETn and immediately exits from the warm reset when the SCLC deasserts SWRESETn.

## SCRESETCold ResetInput to ShellThis input initiates a cold reset for the MR4010. Inside the<br/>MR4010, this signal is synchronized to the system clock,<br/>SCLKp. The MR4010 enters the cold reset condition<br/>when the SCLC asserts SCRESETn and immediately<br/>exits from the cold reset when the SCLC deasserts<br/>SCRESETn.

FRCMn Force Cache Miss (Strap Input) Input to Shell This input is used for system debug. Under normal operating conditions, you should strap it HIGH. To use it for debug, you should assert it by tying it LOW. When LOW, it forces a cache miss for the Icache and the

Dcache in the CW4010 shell. The CW4010 treats this event as an access to an uncached area. The CW4010 can then read and write all instructions and data as uncached, regardless of the memory segment and the MMU.

BENDnBig Endian (Strap Input)Input to ShellThis input affects the byte positions for sizing and<br/>load/store data alignment. When the input is LOW<br/>(asserted), the CW4010 uses big-endian addressing. The<br/>MR4010 uses only little-endian addressing, so you tie this<br/>input HIGH.

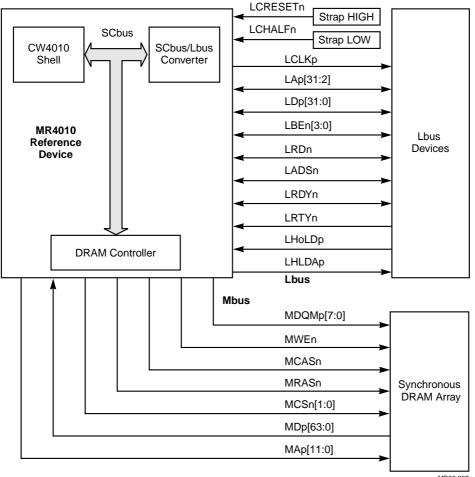

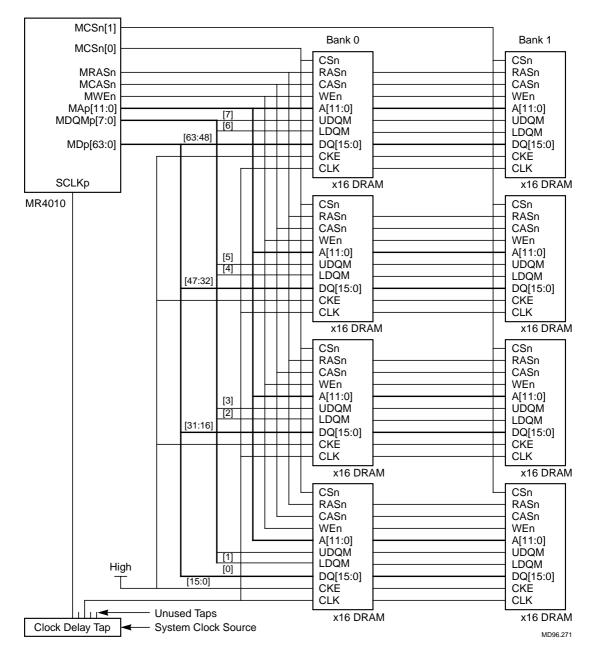

Figure 10 shows the 89 Mbus signals that the MR4010 uses to connect the MR4010 DRAM Controller to the synchronous DRAMs in the main memory array. Inputs and outputs are referenced to the DRAM Controller.

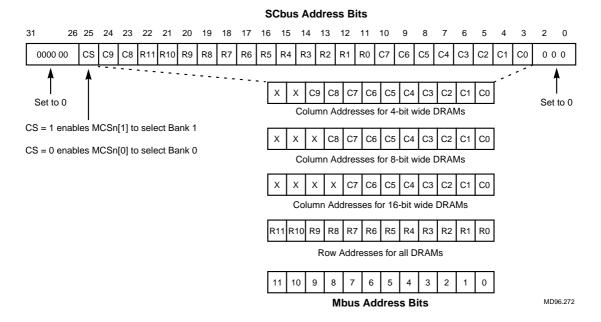

MAp[11:0]Multiplexed Memory Address BusOutputThese multiplexed signals carry row and column<br/>addresses. MRASn strobes the row addresses into the<br/>DRAMs, and MCASn strobes the column addresses.<br/>"Address Bit Assignment" on page 58 provides detailed<br/>information about the address bus.Output

During memory initialization, the DRAM Controller uses MAp[11:0] to write the 12-bit Mode Register in each DRAM.

- MDp[63:0]Memory Data BusBidirectionalThis 64-bit bidirectional data bus carries data between<br/>the MR4010 and the memory array. The direction of data<br/>flow is controlled by MWEn.

- MCSn[1:0] Memory Chip Select Output MCSn[1:0] select between Banks 0 and 1 in the DRAM array. The DRAM Controller asserts MSCn0 to select the DRAMs that make up Bank 0, and asserts MSCn1 to select the DRAMs in Bank 1. If only one bank of DRAMs is installed, the DRAM Controller asserts MCSn0.

- MRASnMemory Row Address StrobeOutputThe MR4010 asserts MRASn to strobe memory row<br/>addresses into the memory devices.Output

MCASn Memory Column Address Strobe Output The MR4010 asserts MCASn to strobe memory column addresses into the memory devices.

## MWEnMemory Write EnableOutputThe MR4010 asserts MWEn to enable a write operation<br/>and deasserts MWEn to enable a read operation.

Figure 10 Mbus and Lbus Interface

MD96.267

## MDQMp[7:0] Memory Data Enable/Mask

## Output

This is an 8-bit data mask used only during write operations. When asserted, each bit of the mask selects one byte of data, as shown in the examples below, to enable write operations in individual bytes of the data word. During read operations, the DRAM Controller asserts all the mask bits to select all data bytes.

| Mask                                                | Byte Selected                                                                              | DRAM Byte/Number                                                                       |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| 8-Bit Wide DRAM                                     |                                                                                            |                                                                                        |  |

| MDQMp 7                                             | MDp[63:56]                                                                                 | 7                                                                                      |  |

| MDQMp 6                                             | MDp[55:48]                                                                                 | 6                                                                                      |  |

| MDQMp 5                                             | MDp[47:40]                                                                                 | 5                                                                                      |  |

| MDQMp 4                                             | MDp[39:32]                                                                                 | 4                                                                                      |  |

| MDQMp 3                                             | MDp[31:24]                                                                                 | 3                                                                                      |  |

| MDQMp 2                                             | MDp[23:16]                                                                                 | 2                                                                                      |  |

| MDQMp 1                                             | MDp[15:8]                                                                                  | 1                                                                                      |  |

| MDQMp 0                                             | MDp[7:0]                                                                                   | 0                                                                                      |  |

|                                                     |                                                                                            |                                                                                        |  |

| Mask                                                | Byte Selected                                                                              | DRAM Byte/Number                                                                       |  |

| Mask                                                | Byte Selected<br>16-Bit Wide I                                                             | •                                                                                      |  |

| Mask<br>MDQMp 7                                     | -                                                                                          | •                                                                                      |  |

|                                                     | 16-Bit Wide                                                                                | DRAM                                                                                   |  |

| MDQMp 7                                             | <b>16-Bit Wide</b> MDp[63:56]                                                              | DRAM<br>3 (Upper Byte)                                                                 |  |

| MDQMp 7<br>MDQMp 6                                  | <b>16-Bit Wide</b> I<br>MDp[63:56]<br>MDp[55:48]                                           | 3 (Upper Byte)<br>3 (Lower Byte)                                                       |  |

| MDQMp 7<br>MDQMp 6<br>MDQMp 5                       | <b>16-Bit Wide</b> MDp[63:56]<br>MDp[55:48]<br>MDp[47:40]                                  | 3 (Upper Byte)<br>3 (Lower Byte)<br>2 (Upper Byte)                                     |  |

| MDQMp 7<br>MDQMp 6<br>MDQMp 5<br>MDQMp 4            | <b>16-Bit Wide</b> MDp[63:56]<br>MDp[55:48]<br>MDp[47:40]<br>MDp[39:32]                    | 3 (Upper Byte)<br>3 (Lower Byte)<br>2 (Upper Byte)<br>2 (Lower Byte)                   |  |

| MDQMp 7<br>MDQMp 6<br>MDQMp 5<br>MDQMp 4<br>MDQMp 3 | <b>16-Bit Wide</b> I<br>MDp[63:56]<br>MDp[55:48]<br>MDp[47:40]<br>MDp[39:32]<br>MDp[31:24] | 3 (Upper Byte)<br>3 (Lower Byte)<br>2 (Upper Byte)<br>2 (Lower Byte)<br>1 (Upper Byte) |  |

## 4.5 Lbus Interface

Figure 10 shows the 75 Lbus signals that connect the SCLC in the MR4010 with external Lbus devices. The MR4010 functions as the bus master to access external devices on the Lbus, such as boot-ROM, serial devices, and the Ethernet Controller. These Lbus devices can also function as bus master to access the DRAM through the SCLC and the DRAMC.

This section describes the signals on the Lbus. Inputs and outputs are referenced to the MR4010. Since the MR4010 or an Lbus device can be bus master, some signals that are typically unidirectional, such as the read signal LRDn, are bidirectional. When the MR4010 is bus master and asserts LRDn, it enables a read operation in one of the Lbus devices. When an Lbus device is bus master, it can assert LRDn to read data from the DRAM.

## LCRESETn LCLK Divider Reset Input You can use this input for testing. Normally you should strap it HIGH (deasserted) on the system board, which means the signal is deasserted.

### LCHALFn Lbus Clock Speed

This signal sets the clock speed for the Lbus. When a device on the Lbus drives this signal LOW, it divides the SCbus clock (SCLKp) by two and the MR4010 outputs a clock signal (LCLKp) that is half the frequency of SCLKp. When the signal is HIGH, it divides the clock by four, and the MR4010 outputs a clock signal (LCLKp) that is one quarter the frequency of SCLKp.

## LCLKp Lbus Clock Output This output is derived from the SCbus clock, SCLKp. The Lbus clock rate is either half or quarter the clock rate of SCLKp, depending on the state of the LCHALFn input to the MR4010.

### Lbus Address Bus Bidirectional LAp[31:2]

When the MR4010 is master of the Lbus, it outputs the address that is used to access one of the devices on the Lbus. If one of the devices on the Lbus is bus master, it inputs the address that the MR4010 uses to access the DRAM.

### LDp[31:0] Lbus Data Bus Bidirectional This 32-bit bidirectional data bus transfers data between the devices on the Lbus and the MR4010. The read/write

signal, LRDn, controls the direction of data flow on the Lbus.

## LBEn[3:0] Lbus Byte Enables When the master device drives these signals active

(LOW), they enable data on the Lbus, as shown below. The read/write signal, LRDn, controls the direction of data flow.

| Byte Enable Signal | Byte Bits  | Byte Number |

|--------------------|------------|-------------|

| LBEn 3             | LDp[31:24] | Byte 3      |

| LBEn 2             | LDp[23:16] | Byte 2      |

| LBEn 1             | LDp[15:8]  | Byte 1      |

| LBEn 0             | LDp[7:0]   | Byte 0      |

## Input

## Bidirectional

www.DataSheet4U.com LRDn Lbus Read Bidirectional The master device asserts this signal to enable a read operation and deasserts it to enable a write operation. When the MR4010 asserts LHLDAp and grants bus ownership to an Lbus master device, the master device inputs this signal to the MR4010. When the MR4010 is the bus master, it inputs this signal to the Lbus device. The initiating device must synchronize this signal to the Lbus clock, LCLKp. LADSn Lbus Address Strobe **Bidirectional** This signal strobes the Lbus addresses. The bus master asserts it at the first LCLKp cycle of a transaction. When the MR4010 asserts LHLDAp and grants bus ownership to an Lbus master device, the master device inputs this signal to the MR4010. When the MR4010 is the bus master, it inputs this signal to the Lbus device. The initiating device must synchronize this signal to the Lbus clock, LCLKp. LRDYn Lbus Data Readv Bidirectional When it is asserted, this signal terminates a transaction. When the MR4010 asserts LHLDAp and grants bus ownership to an Lbus master device, the master device inputs this signal to the MR4010. When the MR4010 is the bus master, it inputs this signal to the Lbus device. The initiating device must synchronize this signal to the Lbus clock, LCLKp

LRTYnLbus RetryInputWhen an Lbus master device asserts this signal and<br/>inputs it to the MR4010, the MR4010 temporarily aborts<br/>any transaction in progress and initiates the transaction<br/>again later. The initiating Lbus device must synchronize<br/>the signal to the rising edge of LCLKp.LHoLDpLbus Hold RequestInput<br/>An Lbus device asserts LHoLDp to request ownership of<br/>the Lbus. The initiating device must synchronize the

signal to the rising edge of LCLKp.

LHLDAp Lbus Hold Acknowledge Output The MR4010 asserts this signal in response to an LHoLDp input from an Lbus device. When asserted, the signal grants a bus hold and allows the Lbus device to take bus ownership.

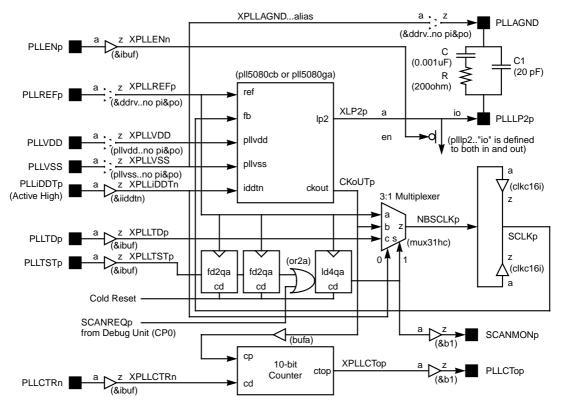

## 4.6 Phase-Locked Loop (PLL) Clock Signals

The PLL circuit generates the clock inputs for the CW4010 shell and for the other modules that are part of the MR4010. The PLL is part of the MR4010 Reference Device, as shown in Figure 1 on page 7. This section describes the PLL signals. "PLL Circuit," on page 36 provides further information. The test signals associated with the PLL circuit are not for general use and are therefore deasserted by strapping them LOW if they are active-high signals, and strapping them HIGH if they are active-low signals.

- PLLREFp

System Clock Reference

Input

This is the system reference clock, input to the CW4010

by the PLL circuit.

- PLLENP VCO Enable(1)/Disable(0) Strapped Input This signal is input to the PLL circuit and enables the PLL circuit when it is active (HIGH). It is strapped HIGH on the main circuit board so that the PLL circuit is always enabled.

- PLLLP2pVCO Input and Loop FilterFilter PinYou must connect an RC (resistor/capacitor) circuit for the<br/>PLL filter between pins PLLLP2p and PLLAGND on the<br/>PLL circuit, as shown in Figure 11, on page 36.

- PLLiDDTpTest Enable InputInput to PLL CircuitThis signal enables test inputs when it is active (HIGH).<br/>It is strapped LOW on the main circuit board.

PLLCTopTest CounterOpen Output from PLL CircuitThis signal is an open pin on the board.

- PLLCTRnTest Counter ResetInput to PLL CircuitThis signal is strapped LOW on the board.

- PLLTSTp

Test Enable

Input to PLL Circuit

This signal is strapped LOW on the board, which means that testing is generally disabled.

Input to PLL Circuit

- PLLTDpTest Data (Clock)<br/>This signal is strapped LOW on the board.Input to PLL CircuitPLLVDDPLL Power<br/>This signal provides VDD power.Input to PLL CircuitPLLVSSPLL Ground<br/>This is the ground for the PLL circuit.Ground

- PLLAGNDPLL Analog GroundGroundThis is the analog ground for the PLL circuit. You must<br/>connect an RC (resistor/capacitor) circuit for the PLL filter<br/>between pins PLLLP2p and PLLAGND on the PLL circuit,<br/>as shown in Figure 11 on page 36.

## **Test Signals**

There are nine pins on the MR4010 chip that allow designers at LSI Logic to test devices on the board using an LSI tester. When the pins are not being used for testing, you must deassert all inputs by strapping active-high signals LOW and active-low signals HIGH. You must leave all outputs open. Inputs and outputs are referenced to and from the MR4010.

SCANCRipCW4010 Core ScanInputThis input allows you to initiate a scan of the CW4010<br/>core. Strap it LOW on the board.CW4010

## SCANCRopCW4010 Core ScanOutputThis output allows you to read the results of the CW4010<br/>core scan. Leave it open on the board.Output

SCANKZipMR4010 Peripherals ScanInputThis input allows you to initiate a scan of the peripheral<br/>circuitry that is part of the MR4010 Reference Device.<br/>Strap it LOW on the board.Strap it LOW

## SCANKZopMR4010 Peripherals ScanOutputThis output allows you to read the results of the MR4010<br/>peripherals scan. Leave it open on the board.Output

SCANENBp Global MR4010 Scan Enable Input This input allows you to initiate a global scan of the MR4010. Strap it LOW on the board.

- SCANMONP Scan Mode Monitor Output This output allows you to monitor the scan mode. Leave it open on the board.

- ZSTATEN Global 3-State Control Input This input is reserved for factory use during testing. Strap it HIGH on the board.

- PARAMOUTp

Parametric Nand Tree

Output

This output allows you to check the parametric NAND tree. It is reserved for factory use during testing. Leave it open on the board.

Output

## TESTMpTest Mode for ScanInputThis input is reserved for factory use during testing. Strap<br/>it LOW on the board through a 10 K resistor.

4.7 There are 11 pins that enable you to monitor the behavior of the CW4010CW4010 Core Monitor SignalsThere are 11 pins that enable you to monitor the behavior of the CW4010the you are not using the outputs to monitor the core, make sure they are open.

- BRLiKFn CW4010 Branchlikely of Even Slot is False Output The CW4010 asserts BRLiKFn when the Branch Likely instruction is in an even slot and it is false. If, at this time, a coprocessor has a valid instruction in the EX stage, the instruction must be cancelled. It is not necessary to check whether the instruction in the EX stage is in an even or odd slot, since the CW4010 asserts BRLiKFn only when the Branch Likely instruction is in the even slot. If the Branch Likely instruction in the even slot is not taken, the instruction in the odd slot must be nullified although it has already been started.

- MCLKp Internal Clock Monitor Output This output from the internal clock allows you to check the clock phase. When you are not using the pin to check the clock, the output should be open.

- PCANCRnCW4010 Pipeline Cancel at CR StageOutputWhen one or more exceptions occur, the pipeline is<br/>cancelled at the CR stage and the CW4010 asserts<br/>PCANCRn. Coprocessor pipelines must be cancelled to<br/>prevent a second execution of the coprocessor instruction<br/>under either of the following conditions: when the copro-<br/>cessor returns from an exception handler; or when the

coprocessor has finished executing an LWCz instruction that caused a TLB (translation lookaside buffer) miss. The WB stage is not cancelled when PCANCRn is asserted.

## PCANoDDn CW4010 Pipeline Cancel to Odd Output

PCANoDDn is valid only when PCANCRn is asserted. The signal informs coprocessors whether the cancellation is for an odd or even slot. When the CW4010 asserts the signal, cancellation applies to the odd slot. When it deasserts the signal, cancellation applies to both even and odd slots.

The coprocessor must track which slot it is executing in based on the CPXoDDn signal. When the CW4010 asserts both PCANCRn and PCANoDDn and the coprocessor instruction is in the odd slot, the instruction must be cancelled. When the CW4010 asserts PCANCRn and deasserts PCANoDDn, the coprocessor instruction must be cancelled regardless of the slot in which it is operating. This signal is valid at the CR stage of the pipeline.

## **PSTALLn CW4010 Pipeline Stall Monitor Output** The CW4010 asserts this signal to indicate that all stages of the CW4010 pipelines are stalled. Pipelines must be stalled when they are executing instructions. This signal is valid at any stage of the pipelines.

SCAoEnSCbus Address Output EnableOutputThe CW4010 asserts SCA0En to indicate that the<br/>address output bus SCAop[31:0] lines are valid. The<br/>CW4010 asserts the signal when the BIU is performing<br/>an SCbus transaction, and the signal remains active<br/>throughout the operation.

## SCBRDYnSCbus Bus ReadyOutputThe SCLC asserts SCBRDYn when the current transac-<br/>tion is terminated. When asserted, it indicates that the<br/>SCbus is available. The signal remains active (LOW) until<br/>the next transaction starts. The SCLC then deasserts the<br/>signal to indicate that the SCbus is not available.

## SCDoEnSCbus Data Output Enable<br/>The CW4010 asserts SCDoEN to indicate that the data<br/>output signals SCDop[63:0] are valid. The CW4010<br/>asserts the signal throughout the write transaction to<br/>indicate that the current transaction is a write transaction<br/>and to enable data output.

## SCiFETn SCbus Instruction Fetch Output SSCiFETn indicates that the BIU is fetching an instruction for monitoring purposes. The CW4010 drives the signal low at this time and outputs it to external logic.

## SCTBSTn SCbus Burst Transaction Output The CW4010 uses burst transactions to the DRAM Controller. When the CW4010 asserts SCTBSTn, it indicates that a DRAM transaction is taking place during which four doublewords will be moved, and that currently the first doubleword is being moved. The CW4010 deasserts the signal after the first word has been transferred and during singleword transactions.

SCTSSn SCbus Transaction Start Strobe Output When the CW4010 asserts SCTSSn, it indicates that a transaction has started. The CW4010 asserts the signal for one clock cycle at the beginning of a transaction. If the transaction lasts through one cycle and the next transaction begins immediately, the CW4010 asserts SCTSSn continuously.

## SUSPEXnCW4010 Suspend EX StageOutputThe CW4010 Instruction Scheduler Unit (ISU) asserts<br/>SUSPEXn to request coprocessors to suspend the<br/>instruction in the EX stage. The instruction in the EX<br/>stage must be held until the ISU deasserts SUSPEXn.<br/>Instructions in the CR and WB stages must be<br/>completed. This signal is valid at the EX stage of the<br/>pipeline.

Figure 11 shows the layout of the MR4010 PLL circuit. This circuit is an

PLL Circuit

LSI Logic PLL cell (pll5080cb) used for cell-based design. The system clock drives the PLLREFp input. You need to provide capacitance devices and a resistor between PLLLP2p and PLLAGND. You must connect other PLL circuit inputs to VDD or GND. SCANMONp and PLLCTop outputs must be open.

For more information about the PLL circuit, refer to the LSI Logic *LCB500K Preliminary Design Manual*.

6 MR4010 has a number of features that allow you to modify the system configuration. This section describes the Configuration and Cache Configuration

Configuration

Control (CCC) Register, which is part of the CW4010 core, and several Lbus registers, which are part of the SCLC module. You can also configure the DRAM, as described in "DRAM Modes and Programmable Configurations" on page 59.

6.1The Configuration and Cache Control (CCC) Register is part of theCW4010 CCCCW4010 coprocessor, CP0. It allows you to use software to configure<br/>various pieces of the core design, such as the BIU, the TLB, and the con-<br/>trollers for the Icache and Dcache.

You can read from the CCC Register or write to it using the MFC0 and MTC0 instructions described in Table 2, which starts on page 44. The register's address in CP0 is '16.' Figure 12 shows the bit configuration of the CCC Register. All bits are initialized to 0 at reset, so that the caches are not available until the register is programmed.

Figure 12 CW4010 CCC Register

| 31 |         |     | 28  | 27  | 26   | 25   | 24                  | 23     | 22     | 21    | 20      | 19     | 18     | 17  | 16       |

|----|---------|-----|-----|-----|------|------|---------------------|--------|--------|-------|---------|--------|--------|-----|----------|

|    | F       | र   |     | SDB | IR1  | EVI  | CMP                 | IIE    | DIE    | MUL   | MAD     | TMR    | BGE    | IE0 | IE1      |

|    |         |     |     |     |      |      |                     |        |        |       |         |        |        |     |          |

| 15 | 14      | 13  | 12  | 11  | 10   | 9    | 8                   | 7      | 6      | 5     | 4       | 3      | 2      | 1   | 0        |

|    | IS[1:0] | DE0 | DE1 | DS[ | 1:0] | IPWE | IPWS                | S[1:0] | TE     | WB    | SR0     | SR1    | ISC    | TAG | INV      |

|    |         |     |     |     |      |      |                     |        |        |       |         |        |        |     | MD96.269 |

|    |         |     | R   |     |      |      | erved<br>field is   | s rese | erved. | The b | oits ar | e clea | red to | -   | 31:28]   |

|    |         |     | SD  | В   |      | This | <b>Deb</b> ibit ena | ables  |        |       | •       |        |        | •   |          |

mode.

www.DataSheet4U.com

Register to 1 and clearing the Error Level and Exception Level bits in the Mode Register to 0.

- BGEBIU Bus Enable Grant18This bit enables and disables the BIU bus grant. Setting<br/>this bit to 1 enables the external bus master. Clearing it<br/>to 0 allows the CW4010 core to ignore the external bus<br/>master.17IE0Icache Set-0 Enable17

- Icache Set-0 Enable 17 This bit enables and disables Set-0 of the Icache. Setting the bit to 1 enables Set-0 and clearing it to 0 disables Set-0.

- IE1Icache Set-1 Enable16This bit enables and disables Set-1 of the Icache. Setting<br/>the bit to 1 enables Set-1 and clearing it to 0 disables<br/>Set-1.

### IS[1:0] Icache Size [15:14] The IS[1:0] field determines the size of each Icache set. The field settings are defined as follows:

|     |     | -              |

|-----|-----|----------------|

| IS1 | IS0 | Cache Set Size |

| 0   | 0   | 1 Kbyte        |

| 0   | 1   | 2 Kbyte        |

| 1   | 0   | 4 Kbyte        |

| 1   | 1   | 8 Kbyte        |

## DE0Dcache Set-0 Enable13This bit enables and disables Set-0 of the Dcache.<br/>Setting the bit to 1 enables Set-0 and clearing it to 0<br/>disables Set-0.13DE1Dcache Set-1 Enable<br/>This bit enables and disables Set-1 of the Dcache12

This bit enables and disables Set-1 of the Dcache. Setting the bit to 1 enables Set-1 and clearing it to 0 disables Set-1.

### DS[1:0] **Dcache Size**

IPWE

TE

[15:14]

| The DS[1:0] field determines the size of each Dcache |

|------------------------------------------------------|

| set. The field settings are defined as follows:      |

| DS1 | DS0 | Cache Set Size |

|-----|-----|----------------|

| 0   | 0   | 1 Kbyte        |

| 0   | 1   | 2 Kbyte        |

| 1   | 0   | 4 Kbyte        |

| 1   | 1   | 8 Kbyte        |

|     |     |                |

In-Page Write Enable 9 This bit enables and disables in-page write operations. Setting the bit to 1 enables in-page write and clearing it to 0 disables in-page write. **IPWS[1:0] In-Page Write Size** [8:7]

### The IPWS[1:0] field determines the size of the Icache set. The field settings are defined as follows:

| IPWS1 | IPWS0 | In-Page Write Size |

|-------|-------|--------------------|

| 0     | 0     | 1 Kbyte            |

| 0     | 1     | 2 Kbyte            |

| 1     | 0     | 4 Kbyte            |

| 1     | 1     | 8 Kbyte            |

| <b>TLB Enable</b><br>This bit enables and disables the TLB. Setting the bit to<br>enables the TLB and clearing the bit to 0 disables the<br>TLB. | <b>6</b><br>1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Writeback                                                                                                                                        | 5             |

### WB writeback This bit defines operation for addresses not mapped by the TLB. Setting the bit to 1 enables a Writeback operation and clearing it to 0 enables a Writethrough operation.

SR0 Scratchpad RAM Mode Set-0 4 This bit enables and disables scratchpad RAM mode for Set-0 of the Dcache. Setting the bit to 1 enables scratchpad mode and clearing it to 0 disables scratchpad mode.

| SR1 | Scratchpad RAM Mode Set-1 3<br>This bit enables and disables scratchpad RAM mode for<br>Set-1 of the Dcache. Setting the bit to 1 enables scratch-<br>pad mode and clearing it to 0 disables scratchpad mode.                                                                                                                                                                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IsC | <b>Isolate Cache</b> 2<br>This bit enables isolate cache mode. This means that<br>stores to the cache are not propagated to external<br>memory. Setting the bit to 1 enables the mode and<br>clearing it to 0 disables the mode.                                                                                                                                                                                   |

| TAG | Tag Test Mode1This bit enables and disables Tag Test Mode, which is<br>used for cache maintenance. Setting the bit to 1 enables<br>the mode, which means that load and store operations<br>access the Tag RAMs, and sample the tag bits Tag Data,<br>Hit, Writeback (Dcache only), and Valid. Clearing the bit<br>to 0 disables Tag Test Mode.                                                                     |

| INV | Invalidate Cache Mode 0<br>This bit enables and disables Cache Invalidate Mode,<br>which is used for cache maintenance. Setting the bit to 1<br>enables the mode, which means that the software must<br>invalidate all lines in the Icache and the Dcache. After<br>reset, zeros must be written into all Tags for both sets of<br>the Icache and Dcache. Clearing the bit to 0 disables<br>Invalidate Cache Mode. |

6.2 The Lbus controller has three 32-bit registers that store information about Lbus Controller Registers The SCbus errors and interrupts. They are the SCbus Error Address Register, the SCbus Error Status Register, and the External Vectored Interrupt Register: You must access these registers through *kseg1*. Access to an unused address causes an SCbus timeout error. Table 1 shows the physical and virtual addresses of these registers. "SCbus Timeout Watchdog Timer" on page 85 provides further information on this subject.

Table 1 Bus Error Internal Registers

| Name                                    | Virtual Address | Physical Address | Function                                            |

|-----------------------------------------|-----------------|------------------|-----------------------------------------------------|

| SCbus Error Address<br>Register         | 0x B010 0000    | 0x 1010 0000     | Contains the SCbus error address                    |

| SCbus Error Status<br>Register          | 0x B010 0004    | 0x 1010 0004     | Contains the error status information for the SCbus |

| External Vectored<br>Interrupt Register | 0x B010 0008    | 0x 1010 0008     | Contains the vectored interrupt for the SCbus       |

### 7

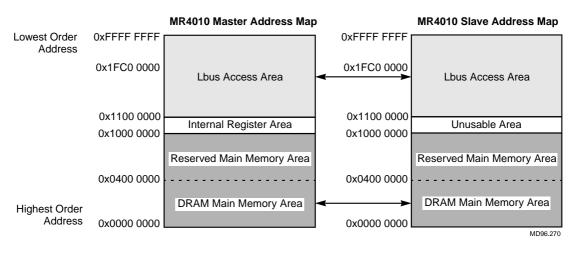

MR4010 Memory Map Figure 13 shows the memory map of the MR4010 where the MR4010 is bus master, and where an Lbus device is bus master and the MR4010 is a slave. In both cases, address spaces are linear 4-Gbyte spaces. Lbus master devices cannot access MR4010 internal memory mapped registers.

Synchronous DRAM main memory that is interfaced to the MR4010 is located at address space 0x0000 0000 through 0x03FF FFFF. The MR4010 works as an Lbus slave device for this 64-Mbyte memory space. There is no guarantee that memory devices exist in the entire 64-Mbyte area. Software, in the form of a setup/bootstrap utility or equivalent, must check installed memory size when the system is initialized. The upper 192-Mbyte space is reserved as an extended main memory area.

MR4010 internal registers for DRAM Controller and error reporting are located in the Internal Registers area between addresses 0x1000 0000 and 0x10FF FFFF. These registers must be accessed through *kseg1*, the uncached-unmapped area. The virtual address for these registers is 0xB000 0000 through 0xB0FF FFFF.

### Figure 13 MR4010 Master/Slave Memory Map

### 8 CW4010 Instruction Set Summary

Table 2 describes the instructions that make up the MR4010 instruction set. The chip supports 32-bit MIPS-II instructions and also implements additional extended instructions. The instructions are arranged alphabet-ically within the following functional groups:

- Load and store, on page 44

- Load linked, on page 45

- ALU immediate, on page 45

- ALU three-operand register type, on page 46

- Shift, on page 47

- Multiply/divide, on page 48

- CW4010 extended computational, on page 48

- Jump, on page 50

- Branch, on page 50

- Trap, on page 52

- Special, on page 52

- Coprocessor, on page 52

- CP0, on page 53

- Cache maintenance, on page 54

Table 2 MR4010 (CW4010) Instruction Set Summary Format and Description Instruction Load and Store Instructions Load Byte LB rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Sign-extend the contents of addressed byte and load into rt. Load Byte Unsigned LBU rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Zero-extend the contents of addressed byte and load into rt. Load Halfword LH rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Sign-extend the contents of addressed halfword and load into rt. Load Halfword Unsigned LHU rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Zero-extend contents of addressed halfword and load into rt. Load Word LW rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address, and load the addressed word into rt. Load Word Left LWL rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift addressed word left so that addressed byte is leftmost byte of a word. Merge bytes from memory with contents of register rt and load result into register rt. Load Word Right LWR rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Shift addressed word right so that addressed byte is rightmost byte of a word. Merge bytes from memory with contents of register rt and load result into register rt. Store Byte SB rt, offset(base) Sign extend the 16-bit offset and add to the contents of register base to form address. Store least-significant byte of register rt at addressed location. (Sheet 1 of 11)

| Instruction                | Format and Description                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Load and Store Instructi   | ons (continued)                                                                                                                                                                                                                                                                                                |  |  |  |

| Store Halfword             | SH rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of register base to<br>form address. Store least-significant halfword of register rt at addressed<br>location.                                                                                                                    |  |  |  |

| Store Word                 | SW rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of register base to<br>form address. Store contents of register rt at addressed location.                                                                                                                                         |  |  |  |

| Store Word Left            | SWL rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of register base to<br>form address. Shift contents of register rt left so that the leftmost byte of<br>the word is in the position of the addressed byte. Store word containing<br>shifted bytes into word at addressed byte.   |  |  |  |

| Store Word Right           | SWR rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of register base to<br>form address. Shift contents of register rt right so that the rightmost byte<br>of the word is in the position of the addressed byte. Store word containing<br>shifted bytes into word at addressed byte. |  |  |  |

| Load Linked Instruction    | 5                                                                                                                                                                                                                                                                                                              |  |  |  |

| Load Linked                | LL rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of the register base<br>to form the address. Load the addressed word into register rt.                                                                                                                                            |  |  |  |

| Store Conditional          | SC rt, offset(base)<br>Sign extend the 16-bit offset and add to the contents of the register base<br>to form the address. Conditionally store register rt at the address, based<br>on whether the load-link has been "broken."                                                                                 |  |  |  |

| Synchronize                | SYNC<br>Complete all outstanding load and store instructions before allowing any<br>new load or store instruction to start.                                                                                                                                                                                    |  |  |  |

| ALU Immediate Instructions |                                                                                                                                                                                                                                                                                                                |  |  |  |

| Add Immediate              | ADDI rt, rs, immediate<br>Add 16-bit, sign-extended immediate to register rs and place 32-bit result<br>in register rt. Trap on two's complement overflow.                                                                                                                                                     |  |  |  |

| Add Immediate Unsigned     | ADDIU rt, rs, immediate<br>Add 16-bit, sign-extended immediate to register rs and place 32-bit result<br>in register rt. Do not trap on overflow.                                                                                                                                                              |  |  |  |

| (Sheet 2 of 11)            |                                                                                                                                                                                                                                                                                                                |  |  |  |

| Instruction                            | Format and Description                                                                                                                                                                                             |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ALU Immediate Instruct                 | ions (continued)                                                                                                                                                                                                   |  |  |  |  |

| Set on Less than<br>Immediate          | SLTI rt, rs, immediate<br>Compare 16-bit, sign-extended immediate with register rs as signed<br>32-bit integers. Result = 1 if rs is less than immediate; otherwise<br>result = 0. Place result in register rt.    |  |  |  |  |

| Set on Less than<br>Immediate Unsigned | SLTIU rt, rs, immediate<br>Compare 16-bit, sign-extended immediate with register rs as unsigned<br>32-bit integers. Result = 1 if rs is less than immediate; otherwise result = 0.<br>Place result in register rt. |  |  |  |  |

| AND Immediate                          | ANDI rt, rs, immediate<br>Zero-extend 16-bit immediate, AND with contents of register rs, and place<br>result in register rt.                                                                                      |  |  |  |  |

| OR Immediate                           | ORI rt, rs, immediate<br>Zero-extend 16-bit immediate, OR with contents of register rs, and place<br>result in register rt.                                                                                        |  |  |  |  |

| Exclusive OR Immediate                 | XORI rt, rs, immediate<br>Zero-extend 16-bit immediate, exclusive OR with contents of register rs,<br>and place result in register rt.                                                                             |  |  |  |  |

| Load Upper Immediate                   | LUI rt, immediate<br>Shift 16-bit immediate left 16 bits. Set least-significant 16 bits of word to<br>zeros. Store result in register rt.                                                                          |  |  |  |  |

| ALU Three-Operand Reg                  | gister Type Instructions                                                                                                                                                                                           |  |  |  |  |

| Add                                    | ADD rd, rs, rt<br>Add contents of registers rs and rt and place 32-bit result in register rd.<br>Trap on two's complement overflow.                                                                                |  |  |  |  |

| Add Unsigned                           | ADDU rd, rs, rt<br>Add contents of registers rs and rt and place 32-bit result in register rd.<br>Do not trap on overflow.                                                                                         |  |  |  |  |

| Subtract                               | SUB rd, rs, rt<br>Subtract contents of registers rt from rs and place 32-bit result in<br>register rd. Trap on two's complement overflow.                                                                          |  |  |  |  |

| Subtract Unsigned                      | SUBU rd, rs, rt<br>Subtract contents of register rt from rs and place 32-bit result in<br>register rd. Do not trap on overflow.                                                                                    |  |  |  |  |

| Set on Less than                       | SLT rd, rs, rt<br>Compare contents of registers rt and rs (as signed, 32-bit integers). If<br>register rs is less than rt, rd = 1; otherwise, rd = 0.                                                              |  |  |  |  |