# **WIDE BANDWIDTH VIDEO AMPLIFIER SYSTEM**

M.S.KENNEDY CORP.

4707 Dey Road Liverpool, N.Y. 13088

(315) 701-6751

#### **FEATURES:**

- 230 MHz Video Bandwidth With Vout = 4Vpp

- Transition Times Less Than 2.0nS With Vout = 4Vpp

- 0 To 4 Volt High Input Impedance DC Drive Control With ±3dB Range

- O To 4 Volt High Input Impedance DC Contrast Control With 40dB Range

- Externally Gated Comparator for Brightness Control

- Simple To Parallel For RGB Color Tracking

- 0.5V to 9.0V Output Voltage Swing Capability

- On Board Accurate Reference Voltage Generator

- · Available Fully Qualified to MIL-PRF-38534

The MSK 620(B) is a very high frequency video amplifier system capable of driving displays with resolutions up to 1664 x 1200. Brightness is controlled with a gated differential input black level clamp comparator. There are also DC inputs available for contrast control and drive control. All DC control inputs operate over a OV to 4V input range and feature high impedance inputs. The MSK 620(B) is packaged in a space efficient hermetically sealed 18 pin dip package.

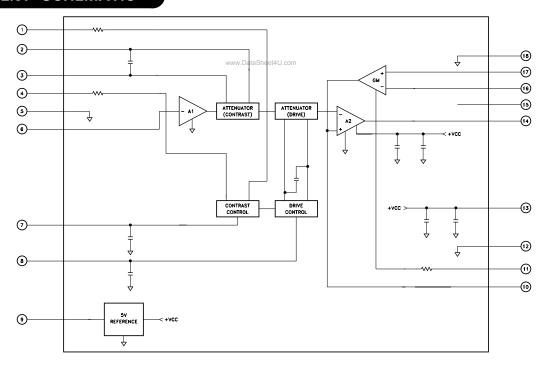

## **EQUIVALENT SCHEMATIC**

# TYPICAL APPLICATIONS

- Wideband Amplifier With Gain and DC Offset Control

- · High Resolution CRT Monitor

- · Ultra High Performance Video Processing

### PIN-OUT INFORMATION

- Control Output (+)

- 2 Attn. Input (+)

- 3 Attn. Input (-)

- 4 Control Output (-)

- 5 Ground

- 6 Video Input

- 7 Contrast Control Input

- 8 **Drive Control Input**

- 9 Vref Output

- 10 Clamp Cap

- Clamp Gate Input 11

- 12 Ground

- 13 +Vcc

- 14 Video Output

- 15 N/C

- 16 Clamp Input (-)

- 17 Clamp Input (+)

- 18 Ground

# **ABSOLUTE MAXIMUM RATINGS**

| +Vcc            | Supply Voltage + 13.5V               | $T_{ST}$ | Storage Temperature Range  | -65°C to +150°C     |

|-----------------|--------------------------------------|----------|----------------------------|---------------------|

| hetaJC          | Thermal Resistance                   | $T_LD$   | Lead Temperature Range     | 300°C               |

|                 | (Junction to Case)                   |          | (10 Seconds)               |                     |

| VIN             | Voltage At Any Input Pin Vcc≥Vin≥GND | Tc       | Case Operating Temperature |                     |

| Іоит            | Video Output Current 28.0mA          |          | MSK620                     | 40°C to +85°C       |

| <b>I</b> OUTREF | Reference Output Current 20mA        |          | MSK620B                    | -55 °C to $+125$ °C |

|                 |                                      | ΤJ       | Junction Temperature       | 150°C               |

# **ELECTRICAL SPECIFICATIONS**

+Vcc = +12.0V Unless Otherwise Specified

| Parameter                          | Test Conditions ①      | Group A MSK 620B |      | В     | MSK 620 |      |       |      |       |

|------------------------------------|------------------------|------------------|------|-------|---------|------|-------|------|-------|

| raiailletei                        |                        | Subgroup         | Min. | Тур.  | Max.    | Min. | Тур.  | Max. | Units |

| STATIC                             |                        |                  |      |       |         |      |       |      |       |

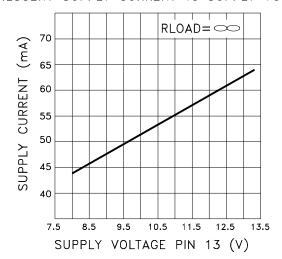

| Power Supply Current               | RLOAD = ∞              | 1,2,3            | -    | 60    | 68      | -    | 60    | 72   | mA    |

| Video Input Bias Voltage           | VIN = N/C              | 1,2,3            | 2.0  | 2.65  | 2.9     | 2.0  | 2.65  | 2.9  | V     |

| Clamp Gate High Input Voltage      | Comparator Off         | 1,2,3            | 2.0  | -     | -       | 1.8  | -     | -    | V     |

| Clamp Gate Low Input Voltage       | Comparator On          | 1,2,3            | -    | -     | 0.8     | -    | -     | 1.0  | ٧     |

| DYNAMIC CHARACTERISTICS            |                        |                  |      |       |         |      |       |      |       |

| Video Amplifier Gain ⑤             |                        | 4                | 16   | 20    | 24      | 16   | 20    | 24   | V/V   |

| Video Output Low Voltage ⑤         | Clamp Cap Voltage = 0V | 4                | -    | 0.2   | 0.65    | -    | 0.2   | 0.65 | V     |

| Video Output High Voltage ⑤        | Clamp Cap Voltage = 6V | 4                | 9.0  | 10    | -       | 9.0  | 10    | -    | V     |

| Attenuation ②                      | VCONTRAST = 0.5V       | -                | -    | -23   | -       | -    | -23   | -    | dB    |

| Video Amplifier Input Resistance ② | fin = 12KHz            | -                | -    | 20    | -       | -    | 20    | -    | ΚΩ    |

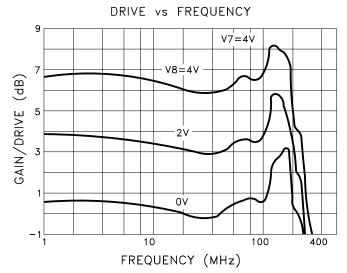

| Gain Range ⑤                       | VDRIVE = 0V to 4V      | 4                | 5    | 6     | -       | 5    | 6     | -    | dB    |

| -3dB Video Amplifier Bandwidth 5   | Vo = 4VPP              | 4                | 200  | 230   | -       | 190  | 200   | -    | MHz   |

| Output Rise Time (5)               | Vo = 4VPP              | 4                | -    | 1.5   | 2.0     | -    | 2.0   | 3.0  | nS    |

| Output Fall Time ⑤                 | Vo = 4VPP              | 4                | -    | 1.5   | 2.0     | -    | 2.0   | 3.0  | nS    |

| VOLTAGE REFERENCE                  |                        |                  |      |       |         |      |       |      |       |

| Output Voltage                     | IL=0mA Ext             | 1                | 4.95 | 5.00  | 5.05    | 4.9  | 5.0   | 5.1  | V     |

| Line Regulation ②                  | Vcc = 11V to 13V       | -                | -    | 0.006 | 0.01    | -    | 0.006 | 0.01 | %/V   |

| Load Regulation ②                  | IL=0 to 10mA           | -                | -    | 0.005 | 0.01    | -    | 0.005 | 0.01 | %/mA  |

| Output Voltage Change w/Temp.②     | -55°C≤Tc≤125°C         | -                | -    | 0.18  | 0.45    | -    | 0.18  | 0.45 | %     |

## **NOTES:**

RIN = 30Ω, CIN = 10μF, RL = 499Ω, unless otherwise specified. Clamp Gate Input = 0V, VCONTRAST = VDRIVE = VBRIGHTNESS = 4V.

Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

Industrial grade devices shall be tested to subgroups 1 and 4 unless otherwise specified.

Military grade devices ('B' suffix) shall be 100% tested to subgroups 1,2,3 and 4.

Subgroup 5 and 6 testing available upon request.

Subgroup 2,5  $T_A = T_C = +125 \, ^{\circ}C$

Subgroup 3,6  $T_A = T_C = -55$  °C

### **APPLICATION NOTES**

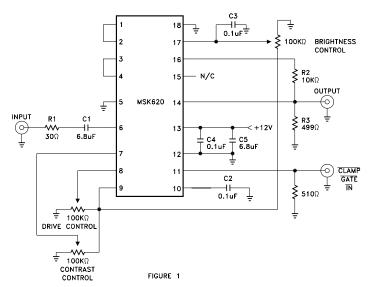

#### VIDEO INPUT

Pin 6 is the video input pin. The video input signal is coupled to this point through a  $30\Omega$ ,  $10\mu\text{F}$  'RC' filter as shown in figure two. The MSK 620 is designed to receive input voltages as high as  $\pm 13.5\text{V}$ .

#### **OUTPUT**

Pin 14 is the video output pin. Since the output of the MSK 620 is a push pull design, there is no need for an external pullup resistor. A 499 $\Omega$  load resistor to analog ground will optimize the output stage current level and bandwidth and is highly recommended.

#### POWER SUPPLY CONNECTIONS

Pin 13 is the positive power supply pin. Convenient internal power supply decoupling consists of a parallel combination of three capacitors ranging from  $0.01\mu\text{F}$  to  $0.47\mu\text{F}$ . The user is advised to connect at least a  $4.7\mu\text{F}$  tantalum decoupling capacitor as close to the power supply pin as possible.

#### Vref OUTPUT

Pin 9 is the Vref output pin. This pin connects to the output of an ultra stable 5.0VDC reference voltage generator internal to the MSK 620. This reference is used as a voltage source for the contrast, drive and clamp inputs.

#### CONTRAST CONTROL

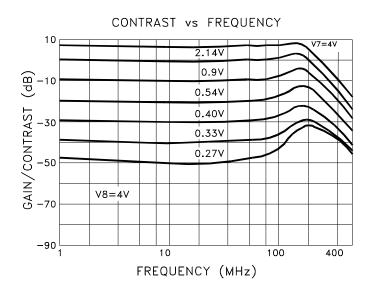

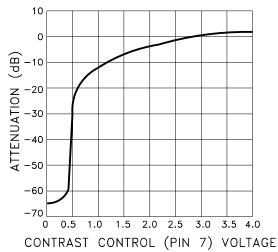

To achieve contrast control, pin 1 is shorted to pin 2 and pin 3 is shorted to pin 4. The voltages at pins 1 and 4 are controlled by the input voltage at pin seven. As the voltage at pin 7 increases, the voltages at pins 1 and 4 become offset. With pin 7 at zero volts, pins 1 and 4 are at minimum offset and the contrast is set to the minimum value of -38dB typical. With pin 7 at 4V, pins 1 and 4 are at maximum offset and contrast is maximized to  $+26 \mathrm{dB}$ . Pin 7 is internally decoupled to ground with a 0.1uF capacitor.

### **DRIVE CONTROL**

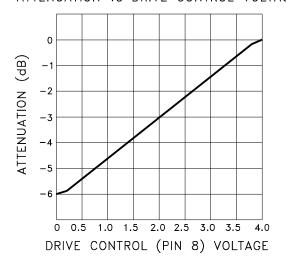

Pin 8 is the drive control input. This pin accepts a DC voltage to control overall gain. Pin 8 is internally decoupled to ground with a 0.1uF capacitor. With OV at pin 8, the gain is minimum (-6dB). With 4V at pin 8, the gain is maximum (OdB). Drive control is approximated by the following formula:

ATTENUATION (dB) =  $(1.5) \times (DRIVE\ VOLTAGE) - (6dB)$

See graph of Attenuation vs. Drive Control Voltage.

### CLAMP CAP

Pin 10 is the clamp comparator output pin. A capacitance of approximately  $0.1\mu F$  is connected from this pin to ground. During the "back porch" portion of the clamp signal, the clamp capacitor is either charged or discharged to match the voltage set on the non-inverting input of the clamp comparator (pin 16). During the video portion of the input signal, the clamp comparator is disabled and the clamp cap holds the proper DC bias in the video amplifier.

#### CLAMP CONNECTIONS

Pin 16 is the (-) clamp input pin. This pin is the inverting input to the clamp comparator. A  $10 \mathrm{K}\Omega$  feedback resistor is connected from this pin to the output pin of the amplifier (pin 14). When the clamp comparator is enabled, the voltage at pin 16 is compared to the voltage at pin 17, which is the non-inverting input of the clamp comparator. A source or sink current is generated at pin 10 to charge or discharge the clamp cap and supply DC bias to the video amplifier. The DC voltage at pin 17 is user adjustable through a  $100 \mathrm{K}\Omega$  potentiometer voltage divider to Vref (see Figure 2). In DC coupled cathode drive applications, brightness can be varied by varying the DC voltage at pin 17.

#### NO CONNECT PINS

Pins 15 is a no connect pin and should be tied to the nearest available video ground plane.

### DC RESTORATION

Pin 11 is the clamp gate input pin and is driven by a TTL back porch clamp signal. A voltage level of +1.3V or less is a "low level" and a voltage level of +1.5V or greater is a "high level". An active low level at this pin enables the clamp comparator section so that DC restoration can be accomplished. This pin should be held at a "high" logic level when a back porch clamp signal is not used.

A typical single video channel connection diagram for the MSK 620 is shown in Figure 1 above. The DC voltage at pin 6 is internally fixed at +2.6V and the video signal is AC coupled to the input. An internal reference voltage generator supplies a +5.0VDC level at pin 9 for use with the contrast, drive and brightness control potentiometers. With pin 7 at 0V, minimum gain is realized. With pin 7 at 4V, maximum gain is realized. The clamp gate input at pin 11 accepts a TTL level clamp signal for DC restoration during the back porch segment of the video signal. Pin 17 is the brightness control input pin and accepts a zero to four volt DC level. This level sets the black level of the signal. If pin 17 = +1VDC the signal black level will be +1VDC. The  $499\Omega$  load resistor biases the class A output stage and should be included during the power dissipation calculation stage.  $499\Omega$  is the minimum recommended value of load resistance for the MSK 620.

Rev. A 8/00

3

# **TYPICAL PERFORMANCE CURVES**

QUIESCENT SUPPLY CURRENT vs SUPPLY VOLTAGE

ATTENUATION vs DRIVE CONTROL VOLTAGE

ATTENUATION vs CONTRAST CONTROL VOLTAGE

4

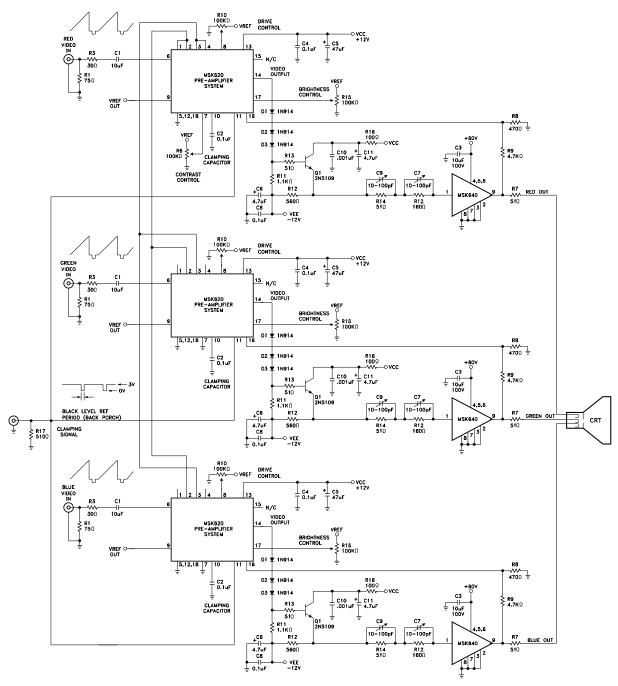

### **COMPLETE RGB VIDEO SYSTEM**

FIGURE 2

A typical connection diagram for a red, green, blue video amplifier system is shown in Figure 2. To achieve optimum contrast tracking, a master slave contrast connection is utilized. This is accomplished by connecting pins 1 and 2 of all three preamplifiers together and using the contrast control of one channel to vary the contrast of all three channels simultaneously. White balance is achieved through individual drive controls. Black level can also be adjusted for each channel by adjusting the voltage at pin 17. If the cathode is AC coupled, the video signal is DC restored at the cathode. In that case black level clamping can be accomplished by biasing pin 17 to the desired black level. The video output pins of the MSK 620 rests at approximately +3.9VDC and the input of the MSK 640 must be biased at approximately +1.55VDC. D1, D2, D3 and Q1 act as a level shifting stage to match the DC level requirements of the preamplifier and the driver. Black level control is accomplished with R8 and R9 sampling the output and feeding it back to the clamping section of the MSK 620. This scheme provides black level control superior to locally sampling the MSK 620 output and feeding that back to the clamping section.

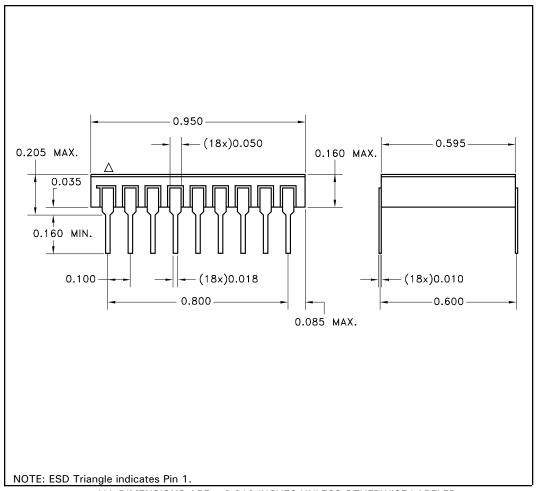

ALL DIMENSIONS ARE ±0.010 INCHES UNLESS OTHERWISE LABELED

# ORDERING INFORMATION

| Part<br>Number | Screening Level        |  |  |  |  |

|----------------|------------------------|--|--|--|--|

| MSK620         | Industrial             |  |  |  |  |

| MSK620B        | Military-Mil-PRF-38534 |  |  |  |  |

M.S. Kennedy Corp.

4707 Dey Road, Liverpool, New York 13088

Phone (315) 701-6751

FAX (315) 701-6752

www.mskennedy.com

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make changes to its products or specifications without notice, however, and assumes no liability for the use of its products.

# This datasheet has been downloaded from:

www. Data sheet Catalog.com

Datasheets for electronic components.