## **DATA SHEET**

OKI

# MSM60804

## **PCMCIA Host Adapter**

FIRST EDITION

**ISSUE DATE: JAN. 1999**

#### **NOTICE**

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.

## **Table of Contents**

| GENERAL DESCRIPTION              | 1  |

|----------------------------------|----|

| FEATURES                         | 1  |

| BLOCK DIAGRAM                    | 2  |

| PIN CONFIGURATION (TOP VIEW)     | 3  |

| PIN DESCRIPTION                  | 6  |

| ABSOLUTE MAXIMUM RATINGS         | 11 |

| RECOMMENDED OPERATING CONDITIONS | 11 |

| ELECTRICAL CHARACTERISTICS       | 12 |

| TIMING DIAGRAM                   | 14 |

| FUNCTIONAL DESCRIPTION           | 18 |

| REGISTERS                        | 23 |

## **OKI** Semiconductor

This version: Jan. 1999

## MSM60804

**PCMCIA Host Adapter**

#### **GENERAL DESCRIPTION**

The MSM60804 PCMCIA Host Adapter is a PCMCIA host interface chip capable of controlling two PCMCIA sockets. The MSM60804 is compatible with indutry standard 82365SL functions.

#### **FEATURES**

- Functionally compatible with 82365SL

- ISA bus interface

- Compliance with PCMCIA 2.1/JEIDA 4.2

- Mixed-voltage (3.3 V or 5.5 V) operation

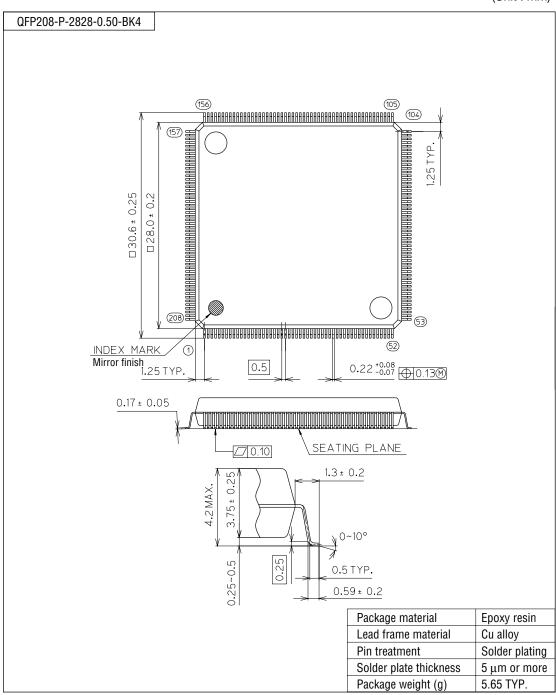

- Dual PCMCIA socket interface:208-pin QFP

- 8-bit or 16-bit access supported

- Complies with both MEMORY CARD and I/O CARD

- Range of window setting:

64KB I/O access space (0-FFFFH)

64MB memory access space (0-3FFFFFFH) (common, attribute)

- One of IRQ3, IRQ4, IRQ5, IRQ7, IRQ9, IRQ10, IRQ11, IRQ12, IRQ14, IRQ15, and IOCHCK can be allocated to each slot

- Power supply control to each slot is available (5 V card and 3 V card are supported)

- Card power down control

- 4 slots are available by cascade connection

- Package:

208-pin plastic QFP (QFP208-P-2828-0.50-K4) (Product name:MSM60804GS-K4)

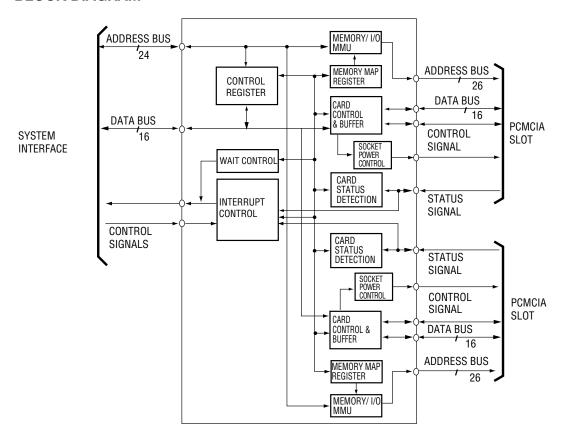

#### **BLOCK DIAGRAM**

Figure 1 MSM60804 Block Diagram

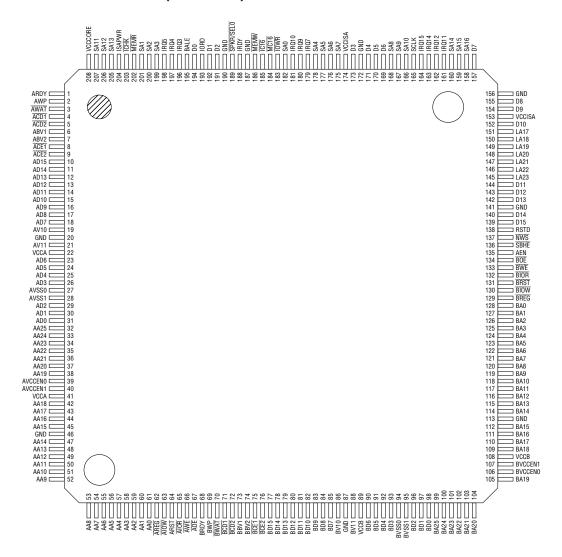

## PIN CONFIGURATION (TOP VIEW)

208-Pin Plastic QFP

## **Pin List**

| Pin Number | Signal Name |

|------------|-------------|------------|-------------|------------|-------------|------------|-------------|

| 1          | ĀRDY        | 31         | AD0         | 61         | AA0         | 91         | BD5         |

| 2          | AWP         | 32         | AA25        | 62         | ĀRĒG        | 92         | BD4         |

| 3          | AWAT        | 33         | AA24        | 63         | AIOW        | 93         | BD3         |

| 4          | ACD1        | 34         | AA23        | 64         | ARST        | 94         | BVSS0       |

| 5          | ACD2        | 35         | AA22        | 65         | AIOR        | 95         | BVSS1       |

| 6          | ABV1        | 36         | AA21        | 66         | ĀWĒ         | 96         | BD2         |

| 7          | ABV2        | 37         | AA20        | 67         | ĀŌĒ         | 97         | BD1         |

| 8          | ACE1        | 38         | AA19        | 68         | BRDY        | 98         | BD0         |

| 9          | ACE2        | 39         | AVCCEN0     | 69         | BWP         | 99         | BA25        |

| 10         | AD15        | 40         | AVCCEN1     | 70         | BWAT        | 100        | BA24        |

| 11         | AD14        | 41         | VCCA        | 71         | BCD1        | 101        | BA23        |

| 12         | AD13        | 42         | AA18        | 72         | BCD2        | 102        | BA22        |

| 13         | AD12        | 43         | AA17        | 73         | BBV1        | 103        | BA21        |

| 14         | AD11        | 44         | AA16        | 74         | BBV2        | 104        | BA20        |

| 15         | AD10        | 45         | AA15        | 75         | BCE1        | 105        | BA19        |

| 16         | AD9         | 46         | GND         | 76         | BCE2        | 106        | BVCCEN0     |

| 17         | AD8         | 47         | AA14        | 77         | BD15        | 107        | BVCCEN1     |

| 18         | AD7         | 48         | AA13        | 78         | BD14        | 108        | VCCB        |

| 19         | AV10        | 49         | AA12        | 79         | BD13        | 109        | BA18        |

| 20         | GND         | 50         | AA11        | 80         | BD12        | 110        | VA17        |

| 21         | AV11        | 51         | AA10        | 81         | BD11        | 111        | BA16        |

| 22         | VCCA        | 52         | AA9         | 82         | BD10        | 112        | BA15        |

| 23         | AD6         | 53         | AA8         | 83         | BD9         | 113        | GND         |

| 24         | AD5         | 54         | AA7         | 84         | BD8         | 114        | BA14        |

| 25         | AD4         | 55         | AA6         | 85         | BD7         | 115        | BA13        |

| 26         | AD3         | 56         | AA5         | 86         | BV10        | 116        | BA12        |

| 27         | AVSS0       | 57         | AA4         | 87         | GND         | 117        | BA11        |

| 28         | AVSS1       | 58         | AA3         | 88         | BV11        | 118        | BA10        |

| 29         | AD2         | 59         | AA2         | 89         | VCCB        | 119        | BA9         |

| 30         | AD1         | 60         | AA1         | 90         | BD6         | 120        | BA8         |

MSM60804

## Pin List (continued)

| Pin Number | Signal Name |

|------------|-------------|------------|-------------|------------|-------------|------------|-------------|

| 121        | BA7         | 143        | D12         | 165        | SCLK        | 187        | GND         |

| 122        | BA6         | 144        | D11         | 166        | SA10        | 188        | IRDY        |

| 123        | BA5         | 145        | LA23        | 167        | SA9         | 189        | SPKR/SEL0   |

| 124        | BA4         | 146        | LA22        | 168        | SA8         | 190        | GND         |

| 125        | BA3         | 147        | LA21        | 169        | D6          | 191        | D2          |

| 126        | BA2         | 148        | LA20        | 170        | D5          | 192        | D1          |

| 127        | BA1         | 149        | LA19        | 171        | D4          | 193        | TORD        |

| 128        | BA0         | 150        | LA18        | 172        | GND         | 194        | D0          |

| 129        | BREG        | 151        | LA17        | 173        | D3          | 195        | BALE        |

| 130        | BIOW        | 152        | D10         | 174        | VCCISA      | 196        | IRQ3        |

| 131        | BRST        | 153        | VCCISA      | 175        | SA7         | 197        | IRQ4        |

| 132        | BIOR        | 154        | D9          | 176        | SA6         | 198        | IRQ5        |

| 133        | BWE         | 155        | D8          | 177        | SA5         | 199        | SA3         |

| 134        | BOE         | 156        | GND         | 178        | SA4         | 200        | SA2         |

| 135        | AEN         | 157        | D7          | 179        | IRQ7        | 201        | SA1         |

| 136        | SBHE        | 158        | SA16        | 180        | IRQ9        | 202        | MEMR        |

| 137        | NWS         | 159        | SA15        | 181        | IRQ10       | 203        | TCHK        |

| 138        | RSTD        | 160        | SA14        | 182        | SA0         | 204        | ISAPWR      |

| 139        | D15         | 161        | IRQ11       | 183        | TOWR        | 205        | SA13        |

| 140        | D14         | 162        | IRQ12       | 184        | MC16        | 206        | SA12        |

| 141        | GND         | 163        | IRQ14       | 185        | ĪC16        | 207        | SA11        |

| 142        | D13         | 164        | IRQ15       | 186        | MEMW        | 208        | VCCCORE     |

## **PIN DESCRIPTION**

| Symbol           | I/O  | Pin<br>Count | Drive<br>Current<br>(mA) | Description                                                                                                                          |

|------------------|------|--------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| System Interface | Pins |              | ( 4                      |                                                                                                                                      |

| LA [23 : 17]     | I    | 24           | _                        | System Address Bus                                                                                                                   |

| SA [16:0]        |      |              |                          | The address bus lines of host system interface.                                                                                      |

|                  |      |              |                          | These lines enable direct addressing of the 16MB memory space                                                                        |

|                  |      |              |                          | on the card. In the Word Access mode, SAO is not used.                                                                               |

|                  |      |              |                          | These lines are connected to LA[23:17] and SA[16:0] of the 16-bit                                                                    |

|                  |      |              |                          | ISA system.                                                                                                                          |

| D [15:0]         | 1/0  | 16           | 16                       | System Data bus                                                                                                                      |

|                  |      |              |                          | The bidirectional 16-bit data bus lines of host system interface.                                                                    |

|                  |      |              |                          | The lower byte D[7:0] is also used to access a register in the PCIC.                                                                 |

|                  |      |              |                          | When the MSM60804 is connected to an 8-bit system, pins of the                                                                       |

|                  |      |              |                          | higher byte are pulled up.                                                                                                           |

| RSTD             | I    | 1            | _                        | System Reset Drive                                                                                                                   |

|                  |      |              |                          | An active-high System Reset signal                                                                                                   |

|                  |      |              |                          | This signal is used to reset the PCIC and also drive the Base Address                                                                |

| IOADWD           | + .  |              |                          | Select signal of a register in the PCIC.                                                                                             |

| ISAPWR           | I    | 1            | _                        | ISA Power Supply                                                                                                                     |

|                  |      |              |                          | This pin selects an interface type of pins connected to the system:                                                                  |

|                  |      |              |                          | high for 5 V TTL interface or low for the other interface type (3 V TTL interface or 5 V/3 V CMOS interface). This pin is internally |

|                  |      |              |                          | pulled up.                                                                                                                           |

| BALE             | 1    | 1            |                          | Bus Address Latch Enable                                                                                                             |

| DALL             | '    | '            |                          | This pin is active high and used to latch LA[23:17] at the start of                                                                  |

|                  |      |              |                          | bus cycle timing.                                                                                                                    |

| SCLK             |      | 1            | _                        | System Clock                                                                                                                         |

|                  |      |              |                          | A system clock input of the ISA                                                                                                      |

|                  |      |              |                          | This pin determines ICHK timing and MEMR and MEMW delays                                                                             |

|                  |      |              |                          | in 16-bit accessing. The pulse width of $\overline{\text{ICHK}}$ is three times as                                                   |

|                  |      |              |                          | wide as the clock cycle. When a bus cycle wait is set by a register,                                                                 |

|                  |      |              |                          | the pulse width of IRDY is equal to one SCLK (1 wait).                                                                               |

| TOWR             | I    | 1            | _                        | I/O Port Write                                                                                                                       |

|                  |      |              |                          | An active-low I/O Write signal                                                                                                       |

|                  |      |              |                          | This pin drives data output to an I/O port pointed to by a system                                                                    |

|                  |      |              |                          | address.                                                                                                                             |

| ĪORD             | I    | 1            | _                        | I/O Port Read                                                                                                                        |

|                  |      |              |                          | An active-low I/O Read signal                                                                                                        |

|                  |      |              |                          | This pin drives data input from an I/O port pointed to by a system                                                                   |

|                  |      |              |                          | address.                                                                                                                             |

| Symbol           | I/O    | Pin<br>Count | Drive<br>Current<br>(mA) | Description                                                               |  |  |  |

|------------------|--------|--------------|--------------------------|---------------------------------------------------------------------------|--|--|--|

| System Interface | Pins   |              |                          |                                                                           |  |  |  |

| IC16             | OD     | 1            | 16                       | 16bit I/O Select                                                          |  |  |  |

|                  |        |              |                          | An active-low signal, indicating the host system that the PC card         |  |  |  |

|                  |        |              |                          | is in the 16-bit I/O Access mode.                                         |  |  |  |

| IRDY             | OD     | 1            | 16                       | I/O Channel Ready                                                         |  |  |  |

|                  |        |              |                          | An active high signal, indicating the host system that the memory         |  |  |  |

|                  |        |              |                          | or I/O bus cycle has completed. While this signal is low, the host        |  |  |  |

|                  |        |              |                          | system is requested to wait.                                              |  |  |  |

| MEMW             | I      | 1            | _                        | System Memory Write                                                       |  |  |  |

|                  |        |              |                          | An active-low memory write signal                                         |  |  |  |

|                  |        |              |                          | This pin drives data output to a PC card pointed to by a system address.  |  |  |  |

| MEMR             | I      | 1            | _                        | System Memory Read                                                        |  |  |  |

|                  |        |              |                          | An active-low memory read signal                                          |  |  |  |

|                  |        |              |                          | This pin drives data input from a PC card pointed to by a system address. |  |  |  |

| MC16             | OD     | 1            | 16                       | 16-bit Memory Select                                                      |  |  |  |

|                  |        |              |                          | An active high signal, indicating to the host system that the PC          |  |  |  |

|                  |        |              |                          | card is in the 16-bit memory access mode.                                 |  |  |  |

| AEN              | 1      | 1            | _                        | System Address Enable                                                     |  |  |  |

| SBHE             | I      | 1            | _                        | System Bus High Enable                                                    |  |  |  |

|                  |        |              |                          | An active-low signal, indicating the high byte of the 16-bit system       |  |  |  |

|                  |        |              |                          | data bus                                                                  |  |  |  |

| SPKR/SEL0        | I/O-pu | 1            | 16                       | Register Base Address Select                                              |  |  |  |

|                  |        |              |                          | This pin selects the base address of a register. This pin is driven       |  |  |  |

|                  |        |              |                          | by a system reset signal (RSTD) and determines the address decode         |  |  |  |

|                  |        |              |                          | value of a register according to this input when PCICs are connected      |  |  |  |

|                  |        |              |                          | in a cascade fashion. While resetting is not executed, this pin works     |  |  |  |

|                  |        |              |                          | as a speaker-out output. (This pin is a bi-directional pin.)              |  |  |  |

|                  |        |              |                          | The digital audio signal from the card is output through this pin.        |  |  |  |

| NWS              | OD     | 1            | 16                       | No-Wait State                                                             |  |  |  |

|                  |        |              |                          | An active-low signal, indicates that the PC card executes no-wait         |  |  |  |

|                  |        |              |                          | accessing                                                                 |  |  |  |

|                  |        |              |                          | This pin is disabled during a 16-bit I/O cycle, and in the other          |  |  |  |

|                  |        |              |                          | cycle, is enabled by register setting.                                    |  |  |  |

| IRQ (3-5, 7, 9-  | 0      | 10           | 2                        | Interrupt Request                                                         |  |  |  |

| 12, 14-15)       |        |              |                          | An active-high signal, outputting an interrupt request to the host        |  |  |  |

|                  |        |              |                          | system. Each slot assigns one of the IRQ pins as an interrupt             |  |  |  |

|                  |        |              |                          | signal.                                                                   |  |  |  |

| TCHK             | 0      | 1            | 2                        | I/O Channel Interrupt                                                     |  |  |  |

|                  |        |              |                          | An active-low signal, outputting a non-maskable interrupt request         |  |  |  |

|                  |        |              |                          | (NMI) to the CPU (maskable by system hardware DatigStaciet) U.c           |  |  |  |

| Symbol                   | I/O         | Pin<br>Count | Drive<br>Current<br>(mA) | Description                                                                                                                             |

|--------------------------|-------------|--------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| PCMCIA Card Soc          | ket Interfa | ace Pins     | 11                       |                                                                                                                                         |

| ACD1, ACD2<br>BCD1, BCD2 | I-pu        | 4            | _                        | Card Detect An active-low signal detecting proper card insertion.                                                                       |

| ·                        |             |              |                          | The status of this pin is reflected on the contents of registers.                                                                       |

|                          |             |              |                          | The status transition of this pin can be used as an interrupt request                                                                   |

|                          |             |              |                          | by register setting.                                                                                                                    |

| ABV1, BBV1               | I-pu        | 4            | _                        | Battery Voltage Detect                                                                                                                  |

| ABV2, BBV2               |             |              |                          | These signals are generated by the memory card as an indication of its                                                                  |

|                          |             |              |                          | battery condition. The status of these pins is reflected in the card status                                                             |

|                          |             |              |                          | register. The status change of these pins is available for an interrupt                                                                 |

|                          |             |              |                          | request using the register.                                                                                                             |

|                          |             |              |                          | Status Change                                                                                                                           |

|                          |             |              |                          | When I/O interface is selected, BV1 signal is replaced by an active-low card                                                            |

|                          |             |              |                          | status change (STSCHG). The status of this pin is reflected in the                                                                      |

|                          |             |              |                          | interface status register. The status change of this pin is available as                                                                |

|                          |             |              |                          | an interrupt request by the register.                                                                                                   |

|                          |             |              |                          | Speaker                                                                                                                                 |

|                          |             |              |                          | In the I/O PC card, BV2 is replaced as an active-low audio digital                                                                      |

|                          |             |              |                          | wavefrom 1 (SPKR). It is connected to the speaker out pin                                                                               |

|                          |             |              |                          | (SPKR or SEL0) to drive a host speaker.                                                                                                 |

| AWAT, BWAT               | l-pu        | 2            | _                        | Bus Cycle Wait                                                                                                                          |

|                          |             |              |                          | An active-low Wait Request signal, requesting a bus cycle wait                                                                          |

|                          |             |              |                          | signal from a PC card to the host system.                                                                                               |

| ARDY, BRDY               | I-pu        | 2            | _                        | Ready/Busy/Interrupt Request                                                                                                            |

|                          |             |              |                          | In memory Card mode, this signal is set active high to tell the host                                                                    |

|                          |             |              |                          | system that the memory PC card is ready to accept a next bus cycle.                                                                     |

|                          |             |              |                          | While low, this signal indicates that the memory PC card is busy                                                                        |

|                          |             |              |                          | processing previous bus cycle and not available to execute a next                                                                       |

|                          |             |              |                          | bus cycle. The status of this pin is reflected in the register.                                                                         |

|                          |             |              |                          | The status change of this pin can be used as an interrupt request                                                                       |

| AMAD DWD                 | Lnu         | 2            |                          | by reading the interface status register.                                                                                               |

| AWP, BWP                 | l-pu        | 2            | _                        | Write-protect/16-bit I/O-Access                                                                                                         |

|                          |             |              |                          | In memory Card mode, these pins detect the state of the Write Protect switch of a PC card. This signal, when active high, indicates the |

|                          |             |              |                          | memory PC card is write-protected. To make a memory PC card                                                                             |

|                          |             |              |                          | without a Write Protect switch writable, these pins are grounded.                                                                       |

|                          |             |              |                          | To make a memory PC card read-only, these pins are connected to                                                                         |

|                          |             |              |                          | VCC. In I/O Card mode, these pins are active low to indicate 16-bit                                                                     |

|                          |             |              |                          | 1/0 accessing. (IOIS16)                                                                                                                 |

|                          |             |              |                          | 1/O accessing. (IOIO10)                                                                                                                 |

| Symbol          | I/O        | Pin<br>Count | Drive<br>Current<br>(mA) | Description                                                                               |

|-----------------|------------|--------------|--------------------------|-------------------------------------------------------------------------------------------|

| PCMCIA Card Soc | ket Interf | ace Pins     | . ,                      |                                                                                           |

| AA [25 : 0]     | T0         | 52           | 2                        | Card Address Bus                                                                          |

| BA [25:0]       |            |              |                          | This bus enables the PCIC to directly access the 64M-byte memory                          |

|                 |            |              |                          | address space on the card.                                                                |

| AD [15:0]       | 1/0        | 32           | 2                        | Card Data Bus                                                                             |

| BD [15:0]       |            |              |                          | A bus for transferring 16-bit data to and from the PC card.                               |

| ACE1, ACE2      | T0         | 4            | 2                        | Card Enable                                                                               |

| BCE1, BCE2      |            |              |                          | These signals enable setting of 8-bit or 16-bit accessing to the PC                       |

|                 |            |              |                          | card and enable odd-numbered or even-numbered-address bytes.                              |

|                 |            |              |                          | These signals are combined with A0 to determine a method to access                        |

|                 |            |              |                          | the PC card. The CE1 or CE2 output is enabled according to the                            |

|                 |            |              |                          | register setting or TOIS16 setting.                                                       |

| AREG, BREG      | T0         | 2            | 2                        | Attribute Memory Select                                                                   |

|                 |            |              |                          | When this signal is active low, access is limited to Attribute Memory.                    |

|                 |            |              |                          | When this signal is high, Common Memory Access mode is set.                               |

|                 |            |              |                          | In Common Memory Access mode, accessing to the I/O PC card is                             |

|                 |            |              |                          | disabled.                                                                                 |

| AIOW, BIOW      | TO         | 2            | 2                        | I/O Write                                                                                 |

|                 |            |              |                          | An active-low signal to enable writing data to the PC card's I/O space.                   |

|                 |            |              |                          | This signal is not available when the REG signal is inactive high.                        |

| AIOR, BIOR      | T0         | 2            | 2                        | I/O Read                                                                                  |

|                 |            |              |                          | An active-low signal to enable reading data from the PC card's I/O space.                 |

|                 |            |              |                          | This signal is not available when the REG signal is inactive high.                        |

| AWE, BWE        | TO         | 2            | 2                        | Write Enable                                                                              |

|                 |            |              |                          | An active-low signal to enable writing data in the PC card. This                          |

|                 |            |              |                          | signal enables writing data in common memory of the memory PC                             |

|                 |            |              |                          | card when the $\overline{\text{REG}}$ signal is high or in attribute memory of the I/O    |

|                 |            |              |                          | PC card or memory PC card when the REG signal is low.                                     |

| AOE, BOE        | TO         | 2            | 2                        | Output Enable                                                                             |

|                 |            |              |                          | An active-low signal is used to gate control memory read data from                        |

|                 |            |              |                          | the PC card. When the $\overline{\text{REG}}$ signal is high, this signal enables reading |

|                 |            |              |                          | data from memory of the memory PC card and when the REG signal                            |

|                 |            |              |                          | is low from attribute memory of the I/O PC card memory PC card.                           |

| ARST, BRST      | T0         | 2            | 2                        | Card Reset                                                                                |

|                 |            |              |                          | Active high signals reset the PC cards.                                                   |

|                 |            |              |                          | These signals are set by PC IC's register.                                                |

| AVSS1, AVSS0    | I-pu       | 4            | _                        | Voltage Sense Pins                                                                        |

| BVSS1, BVSS0    |            |              |                          | These signals indicate the voltages required for the PC card.                             |

|                 |            |              |                          | The values of these signals are reflected to the PCIC register.                           |

| Symbol            | I/O                                             | Pin<br>Count | Drive<br>Current<br>(mA) | Description                                                          |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------------|--------------|--------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|

| Card Power Supply | Card Power Supply Control and Power Supply Pins |              |                          |                                                                      |  |  |  |  |  |  |  |

| AVCCEN0           | 0                                               | 8            | 16                       | Power Supply Control                                                 |  |  |  |  |  |  |  |

| AVCCEN1           |                                                 |              |                          | These pins control power supplied to the PC cards and power to       |  |  |  |  |  |  |  |

| BVCCEN0           |                                                 |              |                          | the buffer in the card interface of the PCIC. Their values are set   |  |  |  |  |  |  |  |

| BVCCEN1           |                                                 |              |                          | by registers.                                                        |  |  |  |  |  |  |  |

| AV10, AV11        |                                                 |              |                          |                                                                      |  |  |  |  |  |  |  |

| VB10, VB11        |                                                 |              |                          |                                                                      |  |  |  |  |  |  |  |

| VCCISA            | PW                                              | 3            | _                        | System Interface Buffer / Core Power Supply                          |  |  |  |  |  |  |  |

| VCCCORE           |                                                 |              |                          | These pins supply power to the buffer and the core on the system     |  |  |  |  |  |  |  |

|                   |                                                 |              |                          | interface side. VCCISA and VCCCORE voltages must be equal.           |  |  |  |  |  |  |  |

| VCCA, VCCB        | PW                                              | 4            | _                        | Card Interface Buffer Power Supply                                   |  |  |  |  |  |  |  |

|                   |                                                 |              |                          | These pins supply power (of the same voltage as that of power        |  |  |  |  |  |  |  |

|                   |                                                 |              |                          | supplied to the card slot) to the buffer on the card interface side. |  |  |  |  |  |  |  |

| GND               | PW                                              | 9            | _                        | Ground                                                               |  |  |  |  |  |  |  |

System interface pins: 66

Card interface pins (per slot): 59 Card power supply pins (per slot): 4

Power supply pins: 16 Total number of pins: 208

> TO: Tristate OD: Open Drain PU: Pull Up

PW: Power Supply or GRD Pins.

Note: The above drive current values are for 5 V interface. The drive current values for 3 V interface are half of the above values.

The MSM60804 does not support the INPAK signal of the PCMCIA.

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition      | Rating                        | Unit |

|---------------------|------------------|----------------|-------------------------------|------|

| Supply Voltage      | V <sub>DD</sub>  |                | -0.5 to +6.5                  |      |

| Input Voltage       | VI               | Ta = 25°C      | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output Voltage      | V <sub>0</sub>   | $V_{SS} = 0 V$ | -0.5 to V <sub>DD</sub> + 0.5 |      |

| Input Current       | II               |                | -10 to +10                    |      |

| Outrant Ourse       |                  | 2 mA buffer    | -25 to +25                    | mA   |

| Output Current      | 10               | 16 mA buffer   | -50 to +50                    |      |

| Storage Temperature | T <sub>STG</sub> | <u> </u>       | -65 to +150                   | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                 | Symbol          |     | Min. | Тур. | Max. | Unit |  |

|---------------------------|-----------------|-----|------|------|------|------|--|

| Supply Voltage            | V               | 3 V | 2.7  | 3.3  | 3.6  | V    |  |

|                           | V <sub>DD</sub> | 5 V | 4.5  | 5    | 5.5  | V    |  |

| Operating Temperature     | Top             |     | -40  | +25  | +85  | °C   |  |

| Input Rise and Fall Times | tr, tf          |     | _    | 2    | 20   | ns   |  |

#### **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

#### 3.3 V Interface

$(V_{DD} = 2.7 \text{ V to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_{j} = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                  | Symbol           | Condition                                                                                | Min. | Тур.  | Max.                                                         | Unit |

|----------------------------|------------------|------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------------------|------|

| "H" Level Input Voltage    | V <sub>IH</sub>  | TTL Level Input (Note 2)                                                                 | 1.8  | _     | $V_{DD} + 0.5$                                               | V    |

| "L" Level Input Voltage    | V <sub>IL</sub>  | TTL Level Input (Note 2)                                                                 | -0.5 | _     | +0.8                                                         | V    |

| "H" Level Output Voltage   | V <sub>OH</sub>  | $I_{OH} = -1, -8 \text{ mA}$                                                             | 2.2  | _     | _                                                            | V    |

| "L" Level Output Voltage   | V <sub>OL</sub>  | $I_{0L} = 1.8 \text{ mA}$                                                                | _    | _     | 0.4                                                          | V    |

| "H" Level Input Current    | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                                                        | _    | 0.01  | 1                                                            | μΑ   |

| "I " Lovel Input Current   | _                | $V_{IL} = V_{SS}$                                                                        | -1   | -0.01 | _                                                            | μΑ   |

| "L" Level Input Current    | I <sub>IL</sub>  | $V_{IL} = V_{SS}$ (with 100 k $\Omega$ Pull-up)                                          | -120 | -35   | V <sub>DD</sub> + 0.5<br>+0.8<br><br>0.4<br>1<br><br>-5<br>1 | μΑ   |

| Three state                | I <sub>OZH</sub> | $V_{OH} = V_{DD}$                                                                        | _    | 0.01  | 1                                                            | μΑ   |

| Three-state                |                  | $V_{OL} = V_{SS}$                                                                        | -1   | -0.01 | _                                                            | μΑ   |

| Output Leakage Current     | I <sub>OZL</sub> | $V_{OL} = V_{SS}$ (with 100 k $\Omega$ Pull-up)                                          | -120 | -35   | -5                                                           | μΑ   |

| Supply Current (Stand by)  | I <sub>DDS</sub> | Output non-load (V <sub>IH</sub> = V <sub>DD</sub> , V <sub>IL</sub> = V <sub>SS</sub> ) | _    | 0.1   | 10                                                           | μΑ   |

| Supply Current (Operating) | I <sub>DDO</sub> | Output non-load ( $V_{IH} = V_{DD}$ , $V_{IL} = V_{SS}$ )<br>f = 10  MHz                 | _    | _     | 20                                                           | mA   |

Note 1 : Typical conditions are  $V_{DD} = 3.3 \text{ V}$ ,  $T_j = 25^{\circ}\text{C}$

Note 2: 1 SA PWR pin should be held "low".

Voltage control register bit 2 should be set to "0".

#### 5.0 V Interface

$(V_{DD} = 4.5 \text{ V to } 5.5 \text{ V}, V_{SS} = 0 \text{ V}, Tj = -40^{\circ}\text{C to } +85^{\circ}\text{C})$

| Parameter                     | Symbol           | Condition                                                                | Min. | Тур.  | Max.                  | Unit |

|-------------------------------|------------------|--------------------------------------------------------------------------|------|-------|-----------------------|------|

| "H" Level Input Voltage       | V <sub>IH</sub>  | TTL Level Input (Note 2)                                                 | 2.2  | _     | V <sub>DD</sub> + 0.5 | V    |

| "L" Level Input Voltage       | V <sub>IL</sub>  | TTL Level Input (Note 2)                                                 | -0.5 | _     | +0.8                  | V    |

| "H" Level Output Voltage      | V <sub>OH</sub>  | $I_{OH} = -2, -16 \text{ mA}$                                            | 3.7  | _     | _                     | V    |

| "L" Level Output Voltage      | V <sub>OL</sub>  | I <sub>OL</sub> = 2, 16 mA                                               | _    |       | 0.4                   | V    |

| "H" Level Input Current       | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                                        | _    | 0.01  | 10                    | μΑ   |

| III II I accel lancot Commant |                  | V <sub>IL</sub> = V <sub>SS</sub>                                        | -1   | -0.01 | _                     | μΑ   |

| "L" Level Input Current       | I <sub>IL</sub>  | $V_{IL} = V_{SS}$ (with 50 k $\Omega$ Pull-up)                           | -250 | -100  | -20                   | μΑ   |

| Three state                   | I <sub>OZH</sub> | $V_{OH} = V_{DD}$                                                        | _    | 0.01  | 10                    | μΑ   |

| Three-state                   |                  | V <sub>OL</sub> = V <sub>SS</sub>                                        | -10  | -0.01 | _                     | μΑ   |

| Output Leakage Current        | I <sub>OZL</sub> | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                     | -100 | -20   | μΑ                    |      |

| Supply Current (Stand by)     | I <sub>DDS</sub> | Output non-load $(V_{IH} = V_{DD}, V_{IL} = V_{SS})$                     | _    | 0.1   | 100                   | μΑ   |

| Supply Current (Operating)    | I <sub>DDO</sub> | Output non-load ( $V_{IH} = V_{DD}$ , $V_{IL} = V_{SS}$ )<br>f = 10  MHz | _    | _     | 40                    | mA   |

Note 1 : Typical conditions are :  $V_{DD} = 3.3 \text{ V}$ ,  $T_j = 25^{\circ}\text{C}$

Note 2: 1 SA PWR pin should be held "High".

Voltage Control register bit 2 should be set to "1".

## **AC Characteristics**

## **AC Timing Conditions**

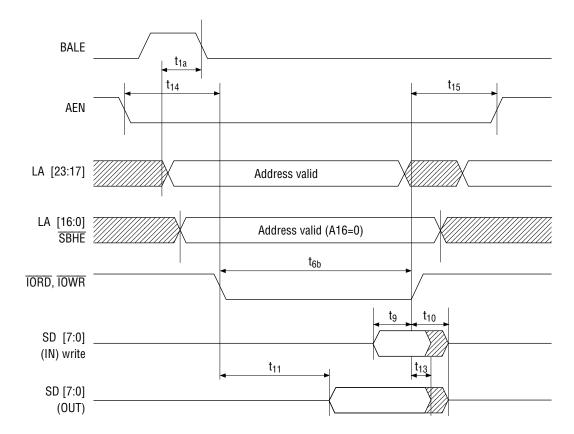

| Symbol             | Parameter                                                                                    | Min. | Max. | Unit |

|--------------------|----------------------------------------------------------------------------------------------|------|------|------|

| t <sub>1a</sub>    | LA <23:17> Setup Time to BALE Inactive                                                       | 20   | _    |      |

| t <sub>1b</sub>    | LA <23:17> Hold Time from BALE Inactive                                                      | 0    | _    |      |

| t <sub>1</sub>     | MC16 Delay Time from LA <23:17> Valid                                                        | 30   | _    |      |

| t <sub>5</sub>     | MC16 Delay Time from LA <23:17> Invalid                                                      | 30   | _    |      |

| t <sub>3</sub>     | SA [16:0] Setup Time to Command Active                                                       | 20   | _    |      |

| t <sub>6a</sub>    | MEMR, MEMW Pulse Width                                                                       | 100  | _    |      |

| t <sub>6b</sub>    | TORD, TOWR Pulse Width                                                                       | 100  | _    |      |

| t <sub>18</sub>    | MC16 Delay Time from SA [16:0] Active                                                        | _    | 35   |      |

| t <sub>2a</sub>    | IC16 Delay Time from SA [16:0] Active                                                        | _    | 40   |      |

| t <sub>2b</sub>    | IC16 Delay Time from Command Inactive                                                        | _    | 30   |      |

| t <sub>19</sub>    | NWS Delay Time from Command Active                                                           | _    | 25   |      |

| t <sub>20</sub>    | NWS Delay Time from Command Inactive                                                         | _    | 25   |      |

| t <sub>4</sub>     | Delay Time from Command Active to IRDY Inactive                                              | _    | 20   |      |

| t <sub>5a</sub>    | Delay Time from AWAY, BWAT Active to IRDY Inactive                                           | _    | 12   | ns   |

| t <sub>5b</sub>    | Delay Time from AWAY, BWAT Inactive to IRDY Active                                           | _    | 20   |      |

| t <sub>p1a</sub>   | AA [25:0], BA [25:0] Delay Time from SA [16:0] Valid                                         | _    | 55   |      |

| t <sub>p1b</sub>   | AA [25:0], BA [25:0] Delay Time from SA [16:0] Invalid                                       | _    | 55   |      |

| t <sub>p2a</sub>   | Delay Time from Command Active to $\overline{\text{OE}}, \overline{\text{WE}}$ Valid         | _    | 55   |      |

| t <sub>p2b</sub>   | Hold Time from Command Inactive to $\overline{\text{OE}}$ , $\overline{\text{WE}}$ Valid     | _    | 55   |      |

| t <sub>p3a</sub>   | Delay Time from SA [16:0] Valid to $\overline{\text{CE}}$ , $\overline{\text{REG}}$ Valid    | _    | 55   |      |

| t <sub>p3b</sub>   | Hold Time from SA [16:0] Invalid to $\overline{\text{CE}}$ , $\overline{\text{REG}}$ Invalid | _    | 85   |      |

| t <sub>14</sub>    | AEN Inactive Setup Time to Command Active                                                    | 15   | _    |      |

| t <sub>15</sub>    | AEN Hold Time from Command Inactive                                                          | 10   | _    |      |

| t <sub>9</sub>     | Data Valid Setup Time to TOWR Inactive                                                       | 10   | _    |      |

| t <sub>10</sub>    | Data Valid Setup Hold Time from TOWR Inactive                                                | 5    | _    |      |

| t <sub>11</sub>    | SD [7:0] Data Delay Time from TORD Active                                                    | _    | 55   |      |

| t <sub>13</sub>    | SD [7:0] Data Hold Time from TORD Inactive                                                   | _    | 50   |      |

| t <sub>piola</sub> | IOR, IOW Delay Time from Command                                                             | _    | 45   |      |

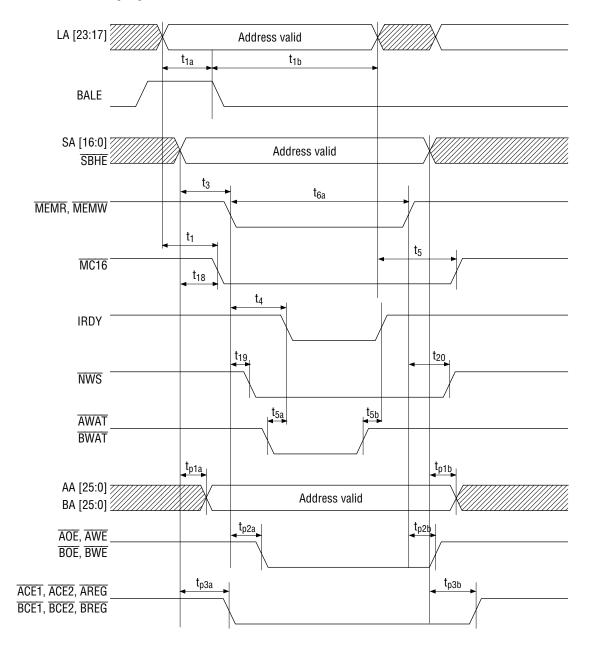

#### **TIMING DIAGRAM**

#### 8/16-Bit Memory Cycle

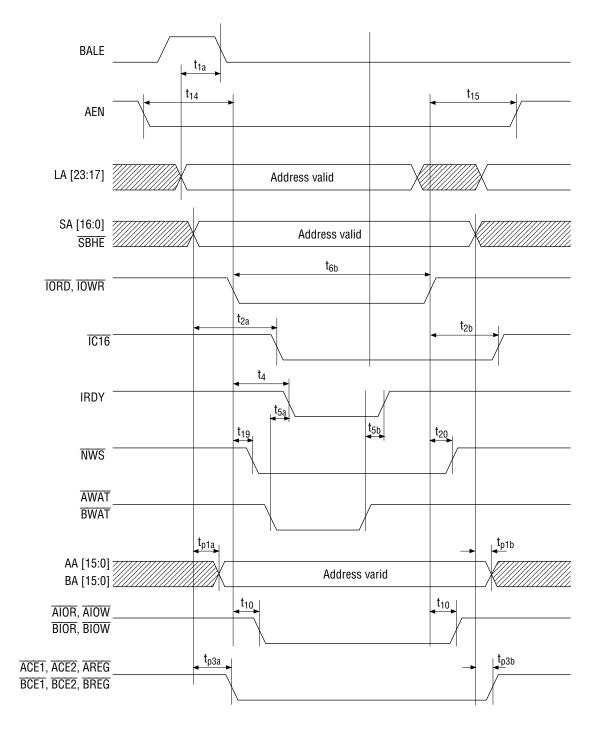

## 8/16-Bit I/O Cycle

## **Register Access**

**Level Mode**

#### **FUNCTIONAL DESCRIPTION**

The MSM60804 offers PC card interface which is functionally compatible to the Intel SE82365SL. The MSM60804 supports the ISA on its system interface side and function to control 2 slots of the PCMCIA2.1 or JEIDA.2 on its card interface side. For details of pins and registers, see "Pin Description" and "Register Description".

#### **Power Control**

- The MSM60804 supplies 5 V or 3 V power to the PCIC core and to the interface buffer on the system side.

- This power is supplied through the VCCISA and VCCCORE pins.

- The VCCISA voltage must be equal to the VCCCORE voltage.

- The interface buffer on the system side supports 5 V or 3 V CMOS and 5 V or 3 V TTL interface levels.

- The levels are selected by the ISAPWR signal.

- Power supply voltage to the interface buffer on the card side is selected to each slot from either 5 V or 3 V according to the rated voltage of the PC card inserted into each slot.

- Power is supplied to the interface buffer on the card side through the VCCA and VCCB pins.

- Voltages supplied to VCCA and VCCB and voltages supplied to slots are determined by controlling the external power supply circuit by VCCEN0 and VCCEN1.

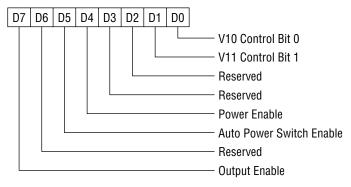

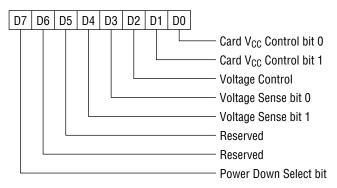

- The VCCEV0 and VCCEN1 outputs are determined by the voltage control registers (+17h and +57h).

- The voltage of VPP power supplied to card slots are determined by controlling the external supply by the V10 and V11 pins.

- The V10 and V11 outputs are determined by the power control registers (+02h and +42h).

#### **Memory Access**

- The memory address space of the PC card supports both attribute memory and common memory (maximum 64M bytes each).

- Attribute memory or common memory is selected by the  $\overline{\text{REG}}$  signal.

- The REG signal output is determined by the following two registers: Interrupt and General-Purpose Register (+03h or +43h) Card Memory Offset Address # High Byte Register

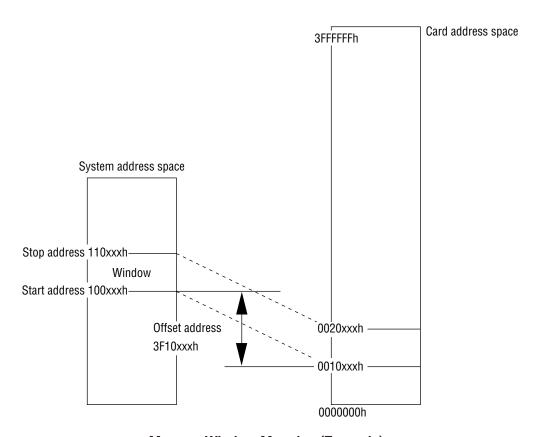

- Accessing to the memory space of the PC card is made through the Memory Address Mapping window.

- The Memory Address Mapping window allocates the following three addresses as shown below:

- System memory mapping start address System memory mapping offset address Card memory offset address

MSM60804

#### Memory Window Mapping (Example)

- The above addresses (to each window) are set by the following registers:

System Memory Address # Mapping Start Low Byte register

System Memory Address # Mapping Start High Byte register

System Memory Address # Mapping Stop Low Byte register

System Memory Address # Mapping Stop High Byte register

Card Memory Offset Address # Low Byte register

Card Memory Offset Address # High Byte register

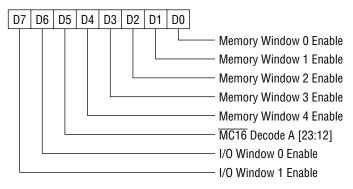

- Up to 16MB can be allocated to a signal Memory Address Mapping window.

- The window size is assigned by 4KB units.

- Five windows can be allocated to each slot.

- Each window is enabled by setting the following register: Address Window Enable register (+06h or +46h)

- The MSM60804 supports both 8-bit and 16-bit accessing modes on both systems interface and card interface sides.

- On the system interface side, the 8-bit and 16-bit accessing modes are switched by the SBHE signal.

- On the card interface side, the accessing method is determined by combinations of  $\overline{\text{CE1}}$  and  $\overline{\text{CE2}}$  signals.

- The values of CE1 and CE2 signals are set by A0 and the System Memory Address #Mapping Start High Byte register.

OKI Semiconductor MSM60804

- A wait can be set for a memory access cycle of the PC card.

- A wait can be set for IRDY by a WAIT signal from the card.

- A wait can be set for each system clock cycle by the following register: System Memory Address # Mapping Start High Byte register

- The 0-wait state is reported to the NWS pin by the following register: System Memory Address # Mapping Start High Byte register

#### I/O Access

- The I/O address space of the PC card is 0 to FFFFh.

- Accessing to an I/O card is enabled by  $\overline{REG}$ ,  $\overline{OE}$ , and  $\overline{WE}$  signals.

- Accessing to the I/O address space of the PC card is made through the I/O Address Mapping window.

- The I/O Address Mapping window allocates the following two addresses:

- I/O address mapping start address

- I/O address mapping stop address

- The above address (for each window) is set by the following registers:

- I/O Address # Mapping Start Low Byte register

- I/O Address # Mapping Start High Byte register

- I/O Address # Mapping Stop Low Byte register

- I/O Address # Mapping Stop High Byte register

- An I/O address space of 0 to FFFh can be allocated to each single I/O address Mapping window.

- The window size is a multiple of 1 byte.

- Two windows can be allocated to each slot.

- Each window is enabled by setting the following register: Address Window Enable register (+06h and +46h)

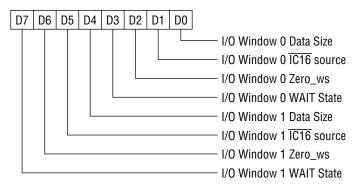

- The MSM60804 supports both 8- bit and 16-bit accessing modes on both system interface and card interface sides.

- On the system interface side, the 8-bit and 16-bit accessing modes are switched by the SBHE signal.

- On the card interface side, the accessing method is determined by combinations of  $\overline{\text{CE1}}$  and  $\overline{\text{CE2}}$  signals.

- <u>CE1</u> and <u>CE2</u> signals are set by A0, IOIS16 and the I/O Control register (+07 and 47h).

- A wait can be set for an I/O access cycle of the PC card.

- A wait can be set for IRDY by a WAIT signal from the card.

- A wait can be set for each system clock cycle by the following register:

- I/O Control register (+07 and +47h)

- The 0-wait state is transferred to the  $\overline{\text{NWS}}$  pin by the following register:

- I/O Control register (+07 and +47h)

#### **PCIC Register Access**

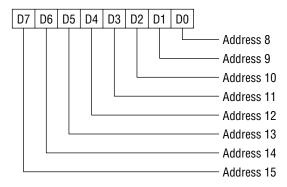

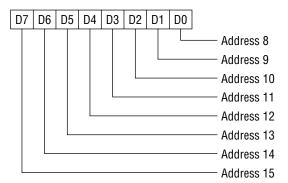

- The MSM60804 provides a 40h register space for each slot.

- The register address of slot A is 3Fh and the register address of slot B is 40h to 7Fh.

- When two MSM60804 chips are cascaded, register addresses are decoded according to the status of the SEL0 signal. Register addresses of slot C and slot D are respectively 80h to BFh and C0h to FFh.

| SEL 0 | Base Address | Index   | Slot  |

|-------|--------------|---------|-------|

| 0     | 0h           | 0h-3Fh  | 0 (A) |

| 0     | 0h           | 40h-7Fh | 1 (B) |

| 1     | 80h          | 80h-BFh | 2 (A) |

| 1     | 80h          | C0h-FFh | 3 (B) |

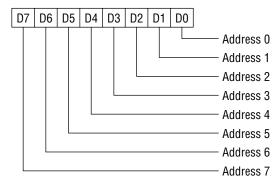

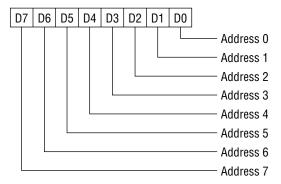

- Accessing to the register address space is indirect addressing through I/O addresses of 3E0h and 3E1h.

- The I/O address 3E0h specifies the register address to be accessed.

- The I/O address 3E1h accesses a register specified by 3E0h.

#### Selection of Memory Mode or I/O Mode

- The Memory PC Card Access Mode and the I/O PC Card Access mode are switched by register setting.

- A PC card access mode is selected by the following register: Interrupt & General Control Register (+03h and +43h)

- Functions of a specific pin of the PCMCIA are switched by mode switching.

#### **Detection of Card Interface Status**

- The MSM60804 detects the following seven PC card statuses and reflects them upon register values:

- The seven states are as follows:

Card detection ( $\overline{\text{CD1}}$  or  $\overline{\text{CD2}}$ )

Card Power Supply Active (V10 or V11)

Voltage Sense (VSS0 or VSS1)

Ready/Busy (RDY) (for memory cards only)

Write Protect (WP) (for memory cards only)

Battery Voltage Detect (BV1 or BV2) (for memory cards only)

Status Change (BV1) (for I/O mode only)

• The detected state is reflected upon the following two registers:

Interface Status register (+02h and +42h)

Voltage Control register (+17h and +57h)

#### **Reset Control**

- The MSM60804 is reset by the RSTD signal from the system.

- It is possible to read only the Configuration register when the PC card is removed by setting it on the register.

- Resetting of the Configuration register is enabled by the following register:

- Card Detection & General Control Register (+16h and +56h)

- For configuration registers, see the configuration register list.

- The PC card in each slot can be reset individually by register setting.

- Set the following register to reset the PC card:

Interrupt & General Control Register (+03h and +43h)

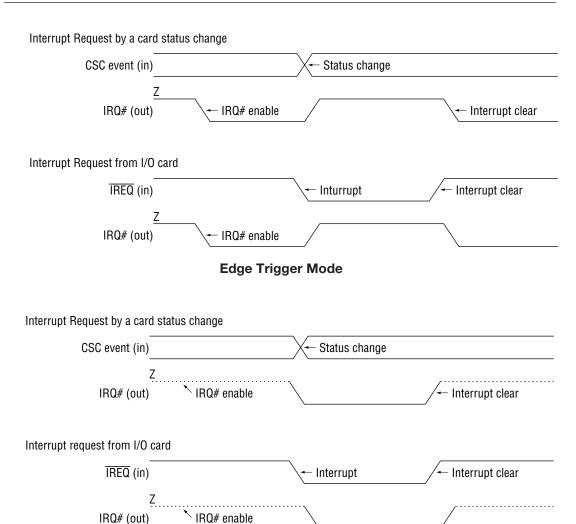

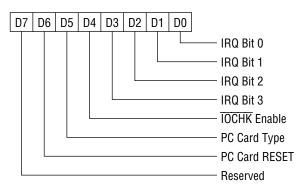

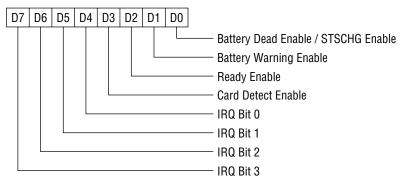

#### **Interrupt Control**

- The MSM60804 supports interrupts by the  $\overline{\text{IREQ}}$  signals from PC cards and interrupts due to card status changed.

- These interrupts can be assigned to each slot.

- The interrupt by the IREQ signal can be assigned to one of the IRQ pins.

- This assignment is set by the following register: Interrupt & General Control Register (+03 and +43h)

- The interrupt due to card status changed can be assigned to one of the IRQ numbers or to ICHK.

- This assignment is set by the following registers:

- Interrupt & General Control Register (+03h and +43h)

- Card status Change Interrupt Configuration Register (+05h and +45h)

- Edge triggering or level triggering can be selected.

- This selection is set by the following register: General Control register (+1Eh ad +5Eh)

#### **Power-Down Control**

- The MSM60804 supports the Power-Down mode. This mode can be set for each slot.

- The Power-Down mode can be set by the following register: Voltage Control register (+17h and +57h)

#### **Cascade Connection**

- By internal decoding of register address, it is possible to connect two MSM60804 chips in a cascade manner and to support four slots simultaneously.

- When the base address is set by the SPKR or SEL0 input, the register address of the second MSM60804 is assigned to 80h to FFh.

## **REGISTERS**

## MSM60804 Register Table

| Slot A Offset | Slot B Offset | Register Name                                   |  |  |

|---------------|---------------|-------------------------------------------------|--|--|

| +00h          | +40h          | Identification and Revision                     |  |  |

| +01h          | +41h          | Interface Status                                |  |  |

| +02h          | +42h          | Power Control                                   |  |  |

| +03h          | +43h          | Interrupt and General Control                   |  |  |

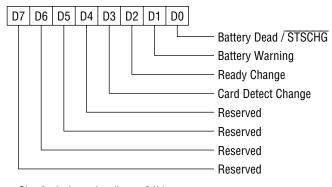

| +04h          | +44h          | Card Status Change                              |  |  |

| +05h          | +45h          | Card Status Change Interrupt Configuration      |  |  |

| +06h          | +46h          | Address Window Enable                           |  |  |

| +07h          | +47h          | I/O Control                                     |  |  |

| +08h          | +48h          | I/O Address 0 Start Low Byte                    |  |  |

| +09h          | +49h          | I/O Address 0 Start High Byte                   |  |  |

| +0Ah          | +4Ah          | I/O Address O Stop Low Byte                     |  |  |

| +0Bh          | +4Bh          | I/O Address 0 Stop High Byte                    |  |  |

| +0Ch          | +4Ch          | I/O Address 1 Start Low Byte                    |  |  |

| +0Dh          | +4Dh          | I/O Address 1 Start High Byte                   |  |  |

| +0Eh          | +4Eh          | I/O Address 1 Stop Low Byte                     |  |  |

| +0Fh          | +4Fh          | I/O Address 1 Stop High Byte                    |  |  |

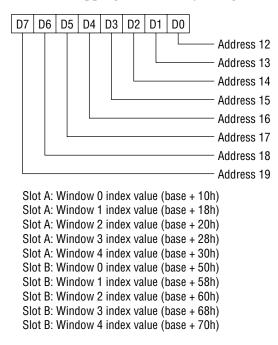

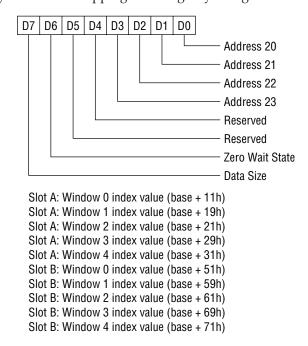

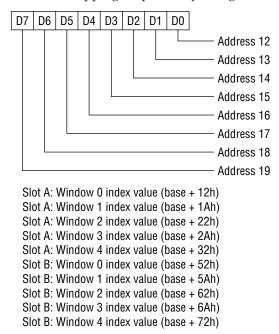

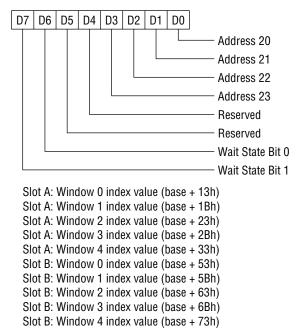

| +10h          | +50h          | System Memory Address 0 Mapping Start Low Byte  |  |  |

| +11h          | +51h          | System Memory Address 0 Mapping Start High Byte |  |  |

| +12h          | +52h          | System Memory Address 0 Mapping Stop Low Byte   |  |  |

| +13h          | +53h          | System Memory Address 0 Mapping Stop High Byte  |  |  |

| +14h          | +54h          | Card Memory Offset Address 0 Low Byte           |  |  |

| +15h          | +55h          | Card Memory Offset Address 0 High Byte          |  |  |

| +16h          | +56h          | Card Detect and General Control                 |  |  |

| +17h          | +57h          | Voltage Control Register                        |  |  |

| +18h          | +58h          | System Memory Address 1 Mapping Start Low Byte  |  |  |

| +19h          | +59h          | System Memory Address 1 Mapping Start High Byte |  |  |

| +1Ah          | +5Ah          | System Memory Address 1 Mapping Stop Low Byte   |  |  |

| +1Bh          | +5Bh          | System Memory Address 1 Mapping Stop High Byte  |  |  |

| +1Ch          | +5Ch          | Card Memory Offset Address 1 Low Byte           |  |  |

| +1Dh          | +5Dh          | Card Memory Offset Address 1 High Byte          |  |  |

| +1Eh          | +5Eh          | Global Control                                  |  |  |

| +1Fh          | +5Fh          | Reserved                                        |  |  |

| +20h          | +60h          | System Memory Address 2 Mapping Start Low Byte  |  |  |

| +20h          | +61h          | System Memory Address 2 Mapping Start High Byte |  |  |

| +22h          | +62h          | System Memory Address 2 Mapping Stop Low Byte   |  |  |

| +23h          | +63h          | System Memory Address 2 Mapping Stop Low Byte   |  |  |

| +24h          | +64h          | Card Memory Offset Address 2 Low Byte           |  |  |

| +25h          | +65h          | Card Memory Offset Address 2 High Byte          |  |  |

## MSM60804 Register Table (continued)

| Slot A Offset | Slot B Offset | Register Name                                   |  |

|---------------|---------------|-------------------------------------------------|--|

| +26h          | +66h          | Reserved                                        |  |

| +27h          | +67h          | Reserved                                        |  |

| +28h          | +68h          | System Memory Address 3 Mapping Start Low Byte  |  |

| +29h          | +69h          | System Memory Address 3 Mapping Start High Byte |  |

| +2Ah          | +6Ah          | System Memory Address 3 Mapping Stop Low Byte   |  |

| +2Bh          | +6Bh          | System Memory Address 3 Mapping Stop High Byte  |  |

| +2Ch          | +6Ch          | Card Memory Offset Address 3 Low Byte           |  |

| +2Dh          | +6Dh          | Card Memory Offset Address 3 High Byte          |  |

| +2Eh          | +6Eh          | Reserved                                        |  |

| +2Fh          | +6Fh          | Reserved                                        |  |

| +30h          | +70h          | System Memory Address 4 Mapping Start Low Byte  |  |

| +31h          | +71h          | System Memory Address 4 Mapping Start High Byte |  |

| +32h          | +72h          | System Memory Address 4 Mapping Stop Low Byte   |  |

| +33h          | +73h          | System Memory Address 4 Mapping Stop High Byte  |  |

| +34h          | +74h          | Card Memory Offset Address 4 Low Byte           |  |

| +35h          | +75h          | Card Memory Offset Address 4 High Byte          |  |

| +36h          | +76h          | OKI Revision                                    |  |

| +37h          | +77h          | Reserved                                        |  |

| +38h          | +78h          | Reserved                                        |  |

| +39h          | +79h          | Reserved                                        |  |

| +3Ah          | +7Ah          | Reserved                                        |  |

| +3Bh          | +7Bh          | Reserved                                        |  |

| +3Ch          | +7Ch          | Reserved                                        |  |

| +3Dh          | +7Dh          | Reserved                                        |  |

| +3Eh          | +7Eh          | Reserved                                        |  |

| +3Fh          | +7Fh          | Reserved                                        |  |

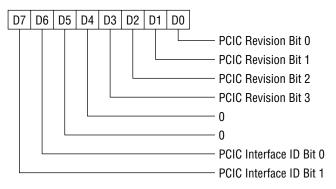

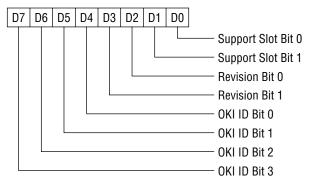

#### **PCIC Revision Register**

The Identification and Revision Register, as shown below is for read purposes only. 83h can be read from the Identification and Revision Register, similar to the 82365SL (Step B).

Slot A: Index value (Base +00h) Slot B: Index value (Base +40h)

#### **Identification and Revision Register (Read Only)**

#### **OKI Revision Register**

The OKI revision register, as shown below, is for read purposes only.

Slot A: Index value (Base +36h) Slot B: Index value (Base +76h)

#### **OKI Revision Register (Read Only)**

The OKI Revision Register shows the ID number of an OKI chip (B2h), as shown below.

#### **OKI Revision Register**

| Bits         | Values |

|--------------|--------|

| ID           | 1011   |

| Revision     | 00     |

| Support Slot | 10     |

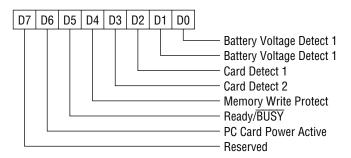

#### **Interface Status Register**

The Interface Status Register is shown below. The bits are defined below.

Slot A : Index value (base + 01h) Slot B : Index value (base + 41h)

## **Interface Status Register (Read Only)**

#### **Interface Status Register Description**

| D Bits | Description                                                                                                                                 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 6  | PC Card Power Active. When set to "1", this bit indicates that V <sub>PP1</sub> and V <sub>PP2</sub> are active. When set to                |

| DIL U  | "0", this bit indicates that V <sub>PP1</sub> and V <sub>PP2</sub> are inactive.                                                            |

| Bit 5  | Ready/ $\overline{BUSY}$ . When set to "1", this bit indicates that RDY/ $\overline{BSY}$ is active (RDY/ $\overline{BSY}$ = "1"). When set |

| טונ ט  | to "0", this bit indicates that RDY/ $\overline{BSY}$ is inactive (RDY/ $\overline{BSY}$ = "0").                                            |

| D:+ 1  | Memory Write Protect. When set to "1", this bit indicates that WP is active (WP = "1"). When set to                                         |

| Bit 4  | "0", this bit indicates that WP is inactive (WP = "0").                                                                                     |

| Bit 3  | Card Detect 2. When set to "1", this bit indicates that $\overline{CD2}$ is active ( $\overline{CD2}$ = "0"). When set to "0", this         |

| DIL 3  | bit indicates that $\overline{CD2}$ is inactive ( $\overline{CD2}$ = "1").                                                                  |

| Bit 2  | Card Detect 1. When set to "1", this bit indicates that $\overline{CD1}$ is active ( $\overline{CD1}$ = "0"). When set to "0", this         |

| DIL Z  | bit indicates that $\overline{CD1}$ is inactive ( $\overline{CD1}$ = "1").                                                                  |

|        | Battery Voltage Detect 2. When set to "1", this bit indicates that BVD2 is active (BVD2 = "1"). When                                        |

| Bit 1  | set to "0", this bit indicates that BVD2 is inactive (BVD2 = "0"). In the case of ID Card Mode, this bit                                    |

|        | indicates the SKPR status.                                                                                                                  |

|        | Battery Voltage Detect 1. When set to "1", this bit indicates that BVD1 is active (BVD1 = "1"). When                                        |

| Bit 0  | set to "0", this bit indicates that BVD1 is inactive (BVD1 = "0"). In the case of ID Card Mode, this bit                                    |

|        | indicates the STSCHG status.                                                                                                                |

The output statuses of CD1 and CD2 signals are shown below

## **Output Status of CD1 and CD2 Signals**

| CD1 | CD2 | Status                                                    |  |