ww.DataSheet4U.com PRELIMINARY<sup>‡</sup>

#### 4 MEG x 16, 2 MEG x 16 ASYNC/PAGE CellularRAM MEMORY

### ASYNCHRONOUS CellularRAM™

MT45W4MW16PFA MT45W4MV16PFA MT45W4ML16PFA MT45W2MW16PFA MT45W2MV16PFA MT45W2ML16PFA

For the latest data sheet, please refer to Micron's Web site: www.micron.com/datasheets

#### **Features**

**Options**

Package 48-ball FBGA

**Operating Temperature Range**

Wireless (-25°C to +85°C)

Industrial (-40°C to +85°C)

- Asynchronous and Page Mode interface

- Random Access Time: 70ns, 85ns

- Page Mode Read Access

Sixteen-word page size

Interpage read access: 70ns, 85ns

Intrapage read access: 20ns, 25ns

- Vcc, VccQ Voltages

1.70V-1.95V Vcc

1.70V-2.25V VccQ (Option W)

2.30V-2.70V VccQ (Option V)

2.70V-3.30V VccQ (Option L)

- Low Power Consumption

Asynchronous READ < 25mA

Intrapage READ < 15mA

Standby: 90μA (32Mb), 100μA (64Mb)

Deep Power-Down < 10μA</li>

- Low-Power Features

Temperature Compensated Refresh (TCR)

Partial Array Refresh (PAR)

Deep Power-Down (DPD) Mode

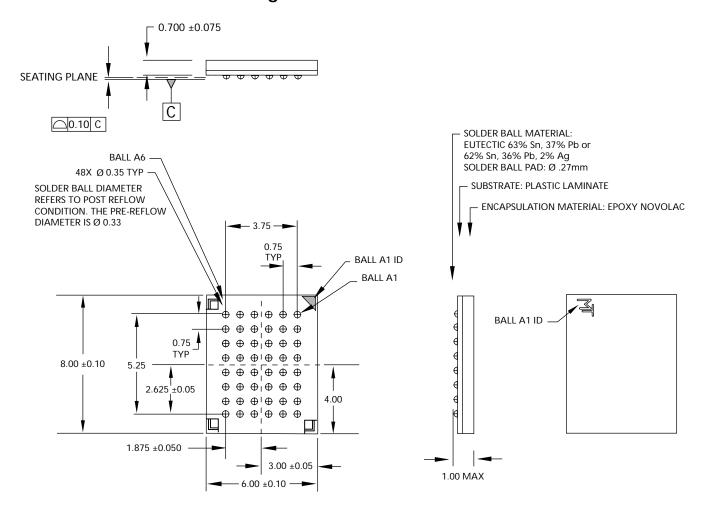

#### Figure 1: 48-Ball FBGA

| Options                                     | wanking           |

|---------------------------------------------|-------------------|

| <ul> <li>VCC Core Voltage Supply</li> </ul> |                   |

| 1.8V – MT45WxMx16PFA                        | W                 |

| <ul> <li>VccQ I/O Voltage</li> </ul>        |                   |

| 3.0V - MT45WxML16PFA                        | L                 |

| 2.5V – MT45WxMV16PFA                        | V                 |

| 1.8V – MT45WxMW16PFA                        | W                 |

| <ul> <li>Access Time</li> </ul>             |                   |

| 60ns                                        | (contact factory) |

| 70ns                                        | -70               |

| 85ns                                        | -85               |

| <ul> <li>Configuration</li> </ul>           |                   |

| 4 Meg x 16                                  | MT45W4Mx16PFA     |

| 2 Meg x 16                                  | MT45W2Mx16PFA     |

NOTE:

Marking

FA

WT

IT (contact factory)

See Table 1 on page 3 for Ball Descriptions. See Figure 18 on page 22 for the 48-ball mechanical drawing.

NOTE: A part marking guide for the FBGA devices can be found on Micron's Web site: <a href="https://www.micron.com/numberguide">www.micron.com/numberguide</a>.

Part Number Example: MT45W2ML16PFA-70WT

09005aef80be1f7f

AsyncCellularRAM.fm - Rev. A 7/03 EN

© 2003 Micron Technology, Inc. All Rights Reserved.

#### **General Description**

Micron<sup>®</sup> CellularRAM™ products are high-speed, CMOS dynamic random access memories that have been developed for low-power portable applications. The MT45W4Mx16PFA is a 64Mb device organized as 4 Meg x 16 bits, and the MT45W2Mx16PFA is a 32Mb device organized as 2 Meg x 16 bits. These devices include the industry-standard, asynchronous memory interface found on other low-power SRAM or Pseudo SRAM offerings.

Operating voltages have been reduced in an effort to minimize power consumption. The core voltage has been reduced to a 1.80V operating level. To maintain compatibility with different memory bus interfaces, CellularRAM devices are available with I/O voltages of 3.00V. 2.50V or 1.80V.

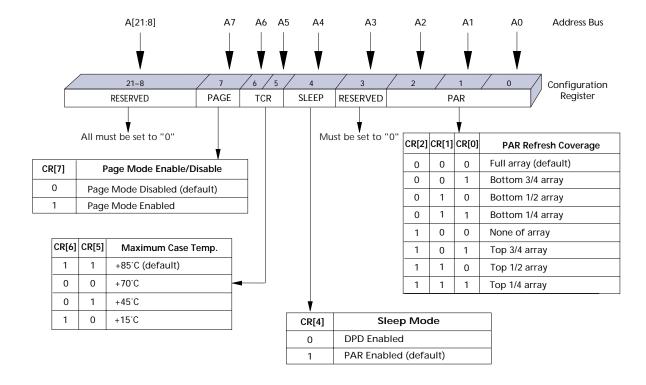

A user-accessible configuration register (CR) has been included to define device operation. The CR defines how the CellularRAM device performs on-chip refresh and whether page mode read accesses are permitted. This register is automatically loaded with a default setting during power-up and can be updated at any time during normal operation.

To operate seamlessly on an asynchronous memory bus, CellularRAM products have incorporated a transparent self refresh mechanism. The hidden refresh requires no additional support from the system memory controller and has no significant impact on device read/write performance.

Special attention has been focused on current consumption during self refresh. CellularRAM products include three system-accessible mechanisms used to minimize refresh current. Temperature compensated refresh (TCR) is used to adjust the refresh rate according to the case temperature. The refresh rate can be decreased at lower temperatures to minimize current consumption during standby. Setting the sleep enable pin ZZ# to LOW enables one of two low-power modes: partial array refresh (PAR); or deep power-down (DPD). PAR limits refresh to only that part of the DRAM array that contains essential data. DPD halts refresh operation altogether and is used when no vital information is stored in the device. These three refresh mechanisms are accessed through the CR.

A[20:0] (for 32Mb) Address Decode Input/ A[21:0] 2,048K x 16 DQ[7:0] Logic (for 64Mb) (4,096K x 16) Output MUX DRAM **MEMORY** and DQ[15:8] **Buffers** ARRAY Configuration Register (CR) CE# WE# OE# Control UB# Logic LB# ZZ#

Figure 2: Functional Block Diagram 4 Meg x 16 and 2 Meg x 16

#### NOTE:

Functional block diagrams illustrate simplified device operation. See truth table, pin descriptions, and timing diagrams for detailed information.

#### Table 1: FBGA Ball Descriptions

| FBGA BALL<br>ASSIGNMENT                                                                               | SYMBOL   | ТҮРЕ             | DESCRIPTION                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3, A4, A5, B3,<br>B4, C3, C4, D4,<br>H2, H3, H4, H5,<br>G3, G4, F3, F4,<br>E4, D3, H1, G2,<br>H6, E3 | A[21:0]  | Input            | Address Inputs: Inputs for the address accessed during READ or WRITE operations. The address lines are also used to define the value to be loaded into the configuration register. On the 32Mb device, A21 (ball E3) is not internally connected. |

| A6                                                                                                    | ZZ#      | Input            | Sleep Enable: When ZZ# is LOW, the configuration register can be loaded or the device can enter one of two low-power modes (DPD or PAR).                                                                                                          |

| B5                                                                                                    | CE#      | Input            | Chip Enable: Activates the device when LOW. When CE# is HIGH, the device is disabled and goes into standby power mode.                                                                                                                            |

| A2                                                                                                    | OE#      | Input            | Output Enable: Enables the output buffers when LOW. When OE# is HIGH, the output buffers are disabled.                                                                                                                                            |

| G5                                                                                                    | WE#      | Input            | Write Enable: Enables WRITE operations when LOW.                                                                                                                                                                                                  |

| A1                                                                                                    | LB#      | Input            | Lower Byte Enable. DQ[7:0]                                                                                                                                                                                                                        |

| B2                                                                                                    | UB#      | Input            | Upper Byte Enable. DQ[15:8]                                                                                                                                                                                                                       |

| B6, C5, C6, D5,<br>E5, F5, F6, G6,<br>B1, C1, C2, D2,<br>E2, F2, F1, G1                               | DQ[15:0] | Input/<br>Output | Data Inputs/Outputs.                                                                                                                                                                                                                              |

| D6                                                                                                    | Vcc      | Supply           | Device Power Supply: (1.7V–1.95V) Power supply for device core operation.                                                                                                                                                                         |

| E1                                                                                                    | VccQ     | Supply           | I/O Power Supply: (1.8V, 2.5V, 3.0V) Power supply for input/output buffers.                                                                                                                                                                       |

| E6                                                                                                    | Vss      | Supply           | Vss must be connected to ground.                                                                                                                                                                                                                  |

| D1                                                                                                    | VssQ     | Supply           | VssQ must be connected to ground.                                                                                                                                                                                                                 |

### **Table 2: Bus Operations**

| MODE                              | POWER                 | CE# | WE# | OE# | LB#/UB# | ZZ# | DQ[15:0] <sup>1</sup> | NOTES   |

|-----------------------------------|-----------------------|-----|-----|-----|---------|-----|-----------------------|---------|

| Standby                           | Standby               | Н   | Х   | Χ   | Х       | Н   | High-Z                | 2, 5    |

| Read                              | Active > Standby      | L   | Н   | L   | L       | Н   | Data-Out              | 1, 4    |

| Write                             | Active > Standby      | L   | L   | Х   | L       | Н   | Data-In               | 1, 3, 4 |

| Active                            | Standby               | L   | Н   | Н   | L       | Н   | High-Z                | 4, 5    |

| PAR                               | Partial Array Refresh | Н   | Х   | Х   | Х       | L   | High-Z                | 6       |

| DPD                               | Deep Power-Down       | Н   | Х   | Х   | Х       | L   | High-Z                | 6       |

| Load<br>Configuration<br>Register | Active                | L   | L   | Х   | Х       | L   | High-Z                |         |

#### NOTE

- 1. When LB# and UB# are in select mode (LOW), DQ[15:0] are affected. When LB# only is in select mode, only DQ[7:0] are affected. When UB# only is in the select mode, DQ[15:8] are affected.

- 2. When the device is in standby mode, control inputs (WE#, OE#), address inputs, and data inputs/outputs are internally isolated from any external influence.

- 3. When WE# is invoked, the OE# input is internally disabled and has no effect on the I/Os.

- 4. The device will consume active power in this mode whenever addresses are changed.

- 5. VIN = Vcc or 0V; all device balls must be static (unswitched) in order to achieve minimum standby current.

- 6. DPD is enabled when configuration register bit CR[4] is "0"; otherwise, PAR is enabled.

Table 3: Abbreviated Component Marks—

CellularRAM FBGA-Packaged Components

| PART NUMBER         | ENGINEERING<br>SAMPLE | QUALIFIED<br>SAMPLE |

|---------------------|-----------------------|---------------------|

| MT45W4MW16PFA-85 WT | PX300                 | PW300               |

| MT45W4MW16PFA-70 WT | PX306                 | PW306               |

| MT45W4ML16PFA-85 WT | PX303                 | PW303               |

| MT45W4ML16PFA-70 WT | PX304                 | PW304               |

| MT45W2MW16PFA-85 WT | PX200                 | PW200               |

| MT45W2MW16PFA-70 WT | PX206                 | PW206               |

| MT45W2ML16PFA-85 WT | PX203                 | PW203               |

| MT45W2ML16PFA-70 WT | PX204                 | PW204               |

| MT45W4MW16PFA-85 IT | PX348 <sup>1</sup>    | PW348 <sup>1</sup>  |

| MT45W4MW16PFA-70 IT | PX349 <sup>1</sup>    | PW349 <sup>1</sup>  |

| MT45W4ML16PFA-85 IT | PX350 <sup>1</sup>    | PW350 <sup>1</sup>  |

| MT45W4ML16PFA-70 IT | PX351 <sup>1</sup>    | PW351 <sup>1</sup>  |

| MT45W2MW16PFA-85 IT | PX207 <sup>1</sup>    | PW207 <sup>1</sup>  |

| MT45W2MW16PFA-70 IT | PX208 <sup>1</sup>    | PW208 <sup>1</sup>  |

| MT45W2ML16PFA-85 IT | PX209 <sup>1</sup>    | PW209 <sup>1</sup>  |

| MT45W2ML16PFA-70 IT | PX210 <sup>1</sup>    | PW210 <sup>1</sup>  |

#### NOTE:

1. Contact factory for availability.

#### **Functional Description**

In general, the MT45W4Mx16PFA device and the MT45W2Mx16PFA device are high-density alternatives to SRAM and Pseudo SRAM products, popular in low-power, portable applications. The MT45W4Mx16PFA contains 67,108,864 bits organized as 4,194,304 addresses by 16 bits. The MT45W2Mx16PFA contains 33,554,432 bits organized as 2,097,152 addresses by 16 bits. These devices include the industry-standard, asynchronous memory interface found on other low-power SRAM or Pseudo SRAM offerings. Page mode accesses are also included as a bandwidth-enhancing extension to the asynchronous read protocol.

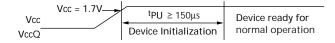

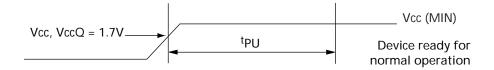

#### **Power-Up Initialization**

Cellular RAM products include an on-chip voltage sensor that is used to launch the power-up initialization process. Initialization will load the CR with its default settings. VCC and VCCQ must be applied simultaneously, and when they reach a stable level above 1.70V, the device will require 150µs to complete its self-initialization process (see Figure 3 below). During the initialization period, CE# should remain HIGH. When initialization is complete, the device is ready for normal operation. At power-up, the CR is set to 0070h.

Figure 3: Power-Up Initialization Timing

#### **Bus Operating Modes**

The MT45W4Mx16PFA and the MT45W2Mx16PFA CellularRAM products incorporate the industry-standard, asynchronous interface found on other low-power SRAM or Pseudo SRAM offerings. This bus interface supports asynchronous READ and WRITE operations as well as the bandwidth-enhancing page mode READ operation. The specific interface that is supported is defined by the value loaded into the CR.

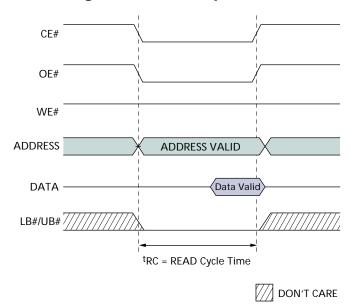

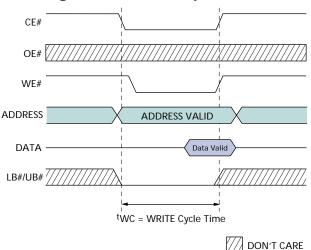

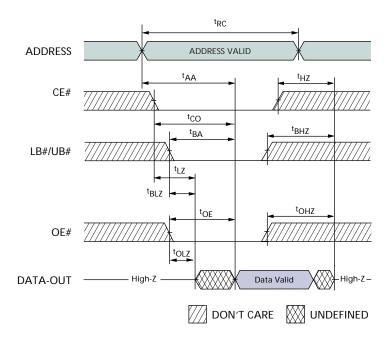

#### Asynchronous Mode

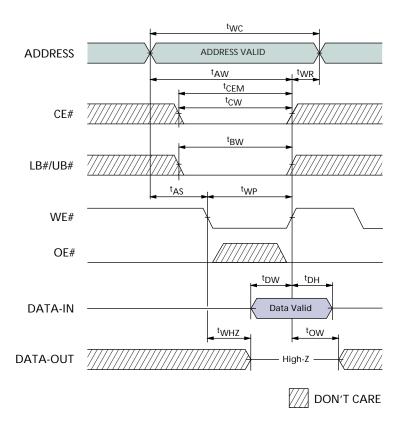

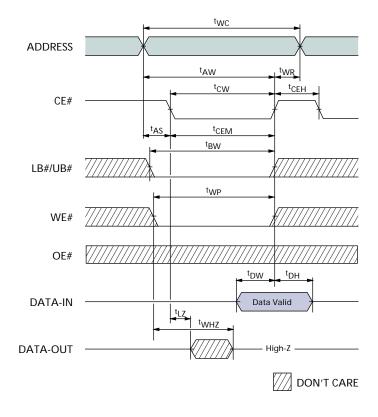

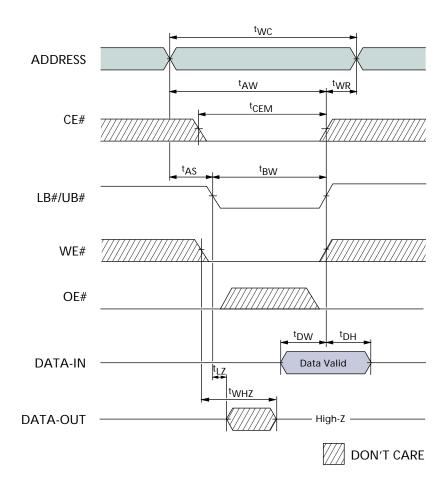

CellularRAM products power up in the asynchronous operating mode. This mode uses the industry-standard SRAM control interface (CE#, OE#, WE#, LB#/UB#). READ operations (Figure 4) are initiated by bringing CE#, OE#, and LB#/UB# LOW while keeping WE# HIGH. Valid data will be driven out of the I/Os after the specified access time has elapsed. WRITE operations (Figure 5) occur when CE#, WE#, and LB#/UB# are driven LOW. During WRITE operations, the level of OE# is a "Don't Care"; WE# will override OE#. The data to be written will be latched on the rising edge of CE#, WE#, or LB#/UB# (whichever occurs first).

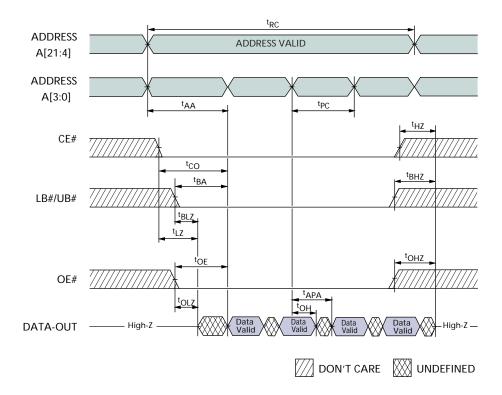

Figure 4: READ Operation

Figure 5: WRITE Operation

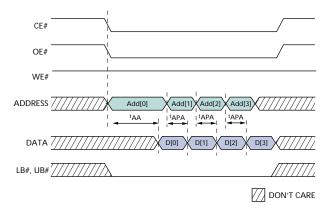

#### Page Mode READ Operation

Page mode is a performance-enhancing extension to the legacy asynchronous READ operation. In page-mode-capable products, an initial asynchronous read access is performed, then adjacent addresses can be quickly read by simply changing the low-order address. Addresses A[3:0] are used to determine the members of the 16-address CellularRAM page. Addresses A[4] and higher must remain fixed during the entire page mode access. Figure 6 shows the timing diagram for a page mode access.

Page mode takes advantage of the fact that adjacent addresses can be read in a shorter period of time than random addresses. WRITE operations do not include comparable page mode functionality.

Figure 6: Page READ Operation

#### LB#/UB# Operation

The lower byte (LB#) enable and upper byte (UB#) enable signals allow for byte-wide data transfers. During READ operations, enabled bytes are driven onto the DQs. The DQs associated with a disabled byte are put into a High-Z state during a READ operation. During WRITE operations, any disabled bytes will not be transferred to the memory array and the internal value will remain unchanged. During a WRITE cycle, the data to be written is latched on the rising edge of CE#, WE#, LB#, or UB#, whichever occurs first.

When both the LB# and UB# are disabled (HIGH) during an operation, the device will disable the data bus from receiving or transmitting data. Although the device will seem to be deselected, the device remains in an active mode as long as CE# remains LOW.

#### **Low Power Operation**

#### Standby Mode Operation

During standby, the device current consumption is reduced to the level necessary to perform the DRAM refresh operation on the full array. Standby operation occurs when CE# and ZZ# are HIGH and there are no transactions in progress.

The device will enter standby operation during READ and WRITE operations where the address and control inputs remain static for an extended period of time. This "active" standby mode will continue until a change occurs to the address or control inputs.

#### Temperature Compensated Refresh

Temperature compensated refresh (TCR) is used to adjust the refresh rate depending on the device operating temperature. DRAM technology requires more frequent refresh operations to maintain data integrity as temperatures increase. More frequent refresh is required due to the increased leakage of the DRAM's capacitive storage elements as temperatures rise. A decreased refresh rate at lower temperatures will facilitate a savings in standby current.

TCR allows for adequate refresh at four different temperature thresholds: +15°C, +45°C, +70°C, and +85°C. The setting selected must be for a temperature higher than the case temperature of the CellularRAM device. If the case temperature is +50°C, the system can minimize self refresh current consumption by selecting the +70°C setting. The +15°C and +45°C settings would result in inadequate refreshing and cause data corruption.

#### Partial Array Refresh

Partial array refresh (PAR) restricts refresh operation to a portion of the total memory array. This feature enables the system to reduce refresh current by only refreshing that part of the memory array that is absolutely necessary. The refresh options are full array, three-quarters array, one-half array, one-quarter array, or none of the array. Data stored in addresses not receiving refresh will become corrupted. The mapping of these partitions can start at either the beginning or the end of the address map (Tables 5 and 6). READ and WRITE operations are ignored during PAR operation.

The device can only enter PAR mode if the SLEEP bit in the configuration register has been set HIGH (CR[4] = 1). PAR is initiated by bring the ZZ# pin to the LOW state for longer than  $10\mu s$ . Returning ZZ# to HIGH will

www.DataSheet4U.com

## 4 MEG x 16, 2 MEG x 16 ASYNC/PAGE CellularRAM MEMORY

cause an exit from PAR and the entire array will be immediately available for READ and WRITE operations.

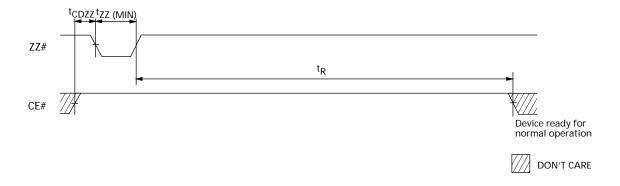

#### **Deep Power-Down Operation**

Deep power-down (DPD) operation disables all refresh-related activity. This mode is used when the system does not require the storage provided by the CellularRAM device. Any stored data will become corrupted when DPD is entered. When refresh activity has been re-enabled, the CellularRAM device will require 150µs to perform an initialization procedure before normal operations can resume. READ and WRITE operations are ignored during DPD operation.

The device can only enter DPD if the SLEEP bit in the CR has been set LOW (CR[4] = 0). DPD is initiated by bringing the ZZ# pin to the LOW state for longer than 10 $\mu$ s. Returning ZZ# to HIGH will cause the device to exit DPD and begin a 150 $\mu$ s initialization process. During this 150 $\mu$ s period, the current consumption will be higher than the specified standby levels but considerably lower than the active current specification.

Driving the ZZ# pin LOW will place the device in the PAR mode if the SLEEP bit in the CR has been set HIGH(CR[4] = 1).

#### **Configuration Register Operation**

The configuration register (CR) defines how the CellularRAM device performs its transparent self refresh. This register is automatically loaded with default settings during power-up and can be updated anytime while the device is operating in a standby state.

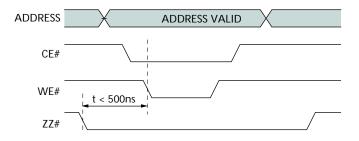

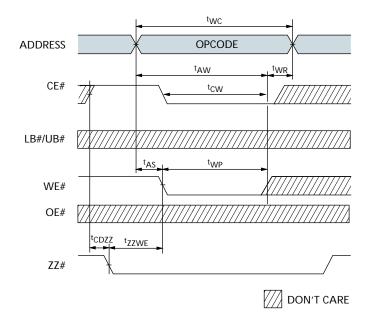

The CR is loaded using a WRITE operation immediately after ZZ# makes a HIGH-to-LOW transition (Figure 7). The values placed on addresses A[21:0] are latched into the CR on the rising edge of CE# or WE#, whichever occurs first. Altering the refresh parameters can dramatically reduce current consumption during standby mode. Page mode control is also embedded into the configuration register. Table 4 on page 9 describes the control bits used in the CR. At power up, the CR is set to 0070h.

Figure 7: Load Configuration Register Operation

#### Partial Array Refresh (CR[2:0]) Default = Full Array Refresh

The PAR bits restrict refresh operation to a portion of the total memory array. This feature allows the system to reduce current by only refreshing that part of the memory array required by the host system. The refresh options are full array, three-quarters array, onehalf array, one-quarter array, or none of the array. The mapping of these partitions can start at either the beginning or the end of the address map (see Tables 5 and 6 on page 9).

### Sleep Mode (CR[4]) Default = PAR Enabled, DPD Disabled

The sleep mode bit determines which low-power mode is to be entered when ZZ# is driven LOW. If CR[4] = 1, PAR operation is enabled. If CR[4] = 0, DPD operation is enabled.

DPD operation disables all refresh-related activity. This mode will be used when the system does not require the storage provided by the CellularRAM device. Any stored data will become corrupted when DPD is enabled. When refresh activity has been reenabled, the CellularRAM device will require 150µs to perform an initialization procedure before normal operation can resume.

### Temperature Compensated Refresh (CR[6:5]) Default = +85°C Operation

The TCR bits allow for adequate refresh at four different temperature thresholds:  $+15^{\circ}$ C,  $+45^{\circ}$ C,  $+70^{\circ}$ C, and  $+85^{\circ}$ C. The setting selected must be for a temperature higher than the case temperature of the CellularRAM device. If the case temperature is  $+50^{\circ}$ C, the system can minimize self refresh current consumption by selecting the  $+70^{\circ}$ C setting. The  $+15^{\circ}$ C and  $+45^{\circ}$ C settings would result in inadequate refreshing and cause data corruption.

### Page Mode READ Operation (CR[7]) Default = Disabled

The page mode operation bit determines whether page mode READ operations are enabled. In the power-up default state, page mode is disabled.

### **Table 4: Configuration Register Bit Mapping**

Table 5: 32Mb Address Patterns for PAR (CR[4] = 1)

| CR[2] | CR[1] | CR[0] | ACTIVE SECTION        | ADDRESS SPACE   | SIZE         | DENSITY |

|-------|-------|-------|-----------------------|-----------------|--------------|---------|

| 0     | 0     | 0     | Full die              | 000000h-1FFFFFh | 2 Meg x 16   | 32Mb    |

| 0     | 0     | 1     | Three-quarters of die | 000000h-17FFFh  | 1.5 Meg x 16 | 24Mb    |

| 0     | 1     | 0     | One-half of die       | 000000h-0FFFFh  | 1 Meg x 16   | 16Mb    |

| 0     | 1     | 1     | One-quarter of die    | 000000h-07FFFh  | 512K x 16    | 8Mb     |

| 1     | 0     | 0     | None of die           | 0               | 0 Meg x 16   | 0Mb     |

| 1     | 0     | 1     | Three-quarters of die | 080000h-1FFFFFh | 1.5 Meg x 16 | 24Mb    |

| 1     | 1     | 0     | One-half of die       | 100000h-1FFFFFh | 1 Meg x 16   | 16Mb    |

| 1     | 1     | 1     | One-quarter of die    | 180000h–1FFFFFh | 512K x 16    | 8Mb     |

Table 6: 64Mb Address Patterns for PAR (CR[4] = 1)

| CR[2] | CR[1] | CR[0] | ACTIVE SECTION        | ADDRESS SPACE   | SIZE       | DENSITY |

|-------|-------|-------|-----------------------|-----------------|------------|---------|

| 0     | 0     | 0     | Full die              | 000000h-3FFFFFh | 4 Meg x 16 | 64Mb    |

| 0     | 0     | 1     | Three-quarters of die | 000000h-2FFFFFh | 3 Meg x 16 | 48Mb    |

| 0     | 1     | 0     | One-half of die       | 000000h-1FFFFFh | 2 Meg x 16 | 32Mb    |

| 0     | 1     | 1     | One-quarter of die    | 000000h-0FFFFFh | 1 Meg x 16 | 16Mb    |

| 1     | 0     | 0     | None of die           | 0               | 0 Meg x 16 | 0Mb     |

| 1     | 0     | 1     | Three-quarters of die | 100000h-3FFFFFh | 3 Meg x 16 | 48Mb    |

| 1     | 1     | 0     | One-half of die       | 200000h-3FFFFFh | 2 Meg x 16 | 32Mb    |

| 1     | 1     | 1     | One-quarter of die    | 300000h-3FFFFFh | 1 Meg x 16 | 16Mb    |

#### Absolute Maximum Ratings\*

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Table 7: Electrical Characteristics and Operating Conditions**

Wireless Temperature (-25°C  $\leq$  T<sub>C</sub>  $\leq$  +85 °C) Industrial Temperature (-40°C < T<sub>C</sub> < +85°C)

| DESCRIPTION             | CONDITIC                                             | NS       | SYN  | /IBOL       | MIN       | MAX        | UNITS | NOTES |

|-------------------------|------------------------------------------------------|----------|------|-------------|-----------|------------|-------|-------|

| Supply Voltage          |                                                      |          | V    | 'cc         | 1.70      | 1.95       | V     |       |

| I/O Supply Voltage      |                                                      | L: 3.00V | Vo   | cQ          | 2.70      | 3.30       | V     |       |

|                         |                                                      | V: 2.50V | Vo   | cQ          | 2.30      | 2.70       | V     |       |

|                         |                                                      | W:1.80V  | Vo   | cQ          | 1.70      | 2.25       | V     |       |

| Input High Voltage      |                                                      |          | V    | <b>/</b> IH | 1.4       | VccQ + 0.2 | V     |       |

| Input Low Voltage       |                                                      |          | V    | /IL         | -0.2      | +0.4       | V     |       |

| Output High Voltage     | IOH = -0.2mA                                         |          | V    | ОН          | 0.80 VccQ |            | V     |       |

| Output Low Voltage      | IOL = 0.2n                                           | nA       | V    | OL          |           | 0.20 VccQ  | V     |       |

| Input Leakage Current   | VIN = 0 to V                                         | /ccQ     | I    | LI          |           | 1          | μΑ    |       |

| Output Leakage Current  | OE# = VIH or Chip                                    | Disabled | lı   | _0          |           | 1          | μΑ    | 2     |

| Read Operating Current  | VIN = VCCQ                                           | or 0V    | Icc1 | -70         |           | 25         | mA    | 1, 2  |

|                         | Chip Enabled,                                        | IOUT = 0 |      | -85         |           | 20         | mA    | 1, 2  |

| Write Operating Current | VIN = VCCQ                                           |          | Icc2 | -70         |           | 25         | mA    | 1, 2  |

|                         | Chip Enabled                                         |          |      | -85         |           | 20         | mA    | 1, 2  |

| MAX Standby Current     | MAX Standby Current  VIN = VccQ or 0V  Chip Disabled |          | Isb  | 32Mb        |           | 90         | μΑ    | 2, 3  |

|                         |                                                      |          |      | 64Mb        |           | 100        | μΑ    | 2, 3  |

#### NOTE:

- 1. This parameter is specified with the outputs disabled to avoid external loading effects. The user must add current required to drive output capacitance expected in the actual system.

- 2. This device assumes a standby mode if the chip is disabled (CE# HIGH). It will also automatically go into a standby mode whenever all input signals are quiescent (not toggling), regardless of the state of CE#, LB#, and UB#. In order to achieve low standby current, all inputs must be either VccQ or Vss.

- 3. ISB (MAX) values measured with PAR set to FULL ARRAY and TCR set to +85°C.

#### Table 8: Temperature Compensated Refresh Specifications and Conditions

| DESCRIPTION                | CONDITIONS        | SYMBOL | DENSITY | MAX CASE<br>TEMPERATURES | TYP | MAX | UNITS |

|----------------------------|-------------------|--------|---------|--------------------------|-----|-----|-------|

| Temperature                | VIN = VCCQ or 0V, | ITCR   | 64Mb    | +85°C                    |     | 100 | μA    |

| Compensated                | Chip Disabled     |        |         | +70°C                    |     | TBD | μΑ    |

| Refresh Standby<br>Current |                   |        |         | +45°C                    |     | TBD | μA    |

| Current                    |                   |        |         | +15°C                    |     | 50  | μΑ    |

|                            |                   |        | 32Mb    | +85°C                    |     | 90  | μΑ    |

|                            |                   |        |         | +70°C                    |     | TBD | μA    |

|                            |                   |        |         | +45°C                    |     | TBD | μΑ    |

|                            |                   |        |         | +15°C                    |     | 50  | μA    |

#### NOTE:

- 1. ITCR (MAX) values measured with FULL ARRAY refresh.

- 2. This device assumes a standby mode if the chip is disabled (CE# HIGH). It will also automatically go into a standby mode whenever all input signals are quiescent (not toggling), regardless of the state of CE#, LB#, and UB#. In order to achieve low standby current, all inputs must be either VccQ or Vss.

**Table 9: Partial Array Refresh Specifications and Conditions**

| DESCRIPTION           | CONDITIONS             | SYMBOL    | DENSITY | ARRAY<br>PARTITION | TYP | MAX | UNITS |  |

|-----------------------|------------------------|-----------|---------|--------------------|-----|-----|-------|--|

| Partial Array Refresh | VIN = VccQ or 0V       | IPAR      | 64Mb    | Full               |     | 100 | μΑ    |  |

| Current               | ZZ# = LOW<br>CR[4] = 1 |           |         | 3/4                |     | TBD | μΑ    |  |

|                       |                        | CR[4] = 1 |         | 1/2                |     | TBD | μΑ    |  |

|                       |                        |           |         |                    |     |     | 1/4   |  |

|                       |                        |           |         | 0                  |     | 50  | μΑ    |  |

|                       |                        |           | 32Mb    | Full               |     | 90  | μΑ    |  |

|                       |                        |           |         | 3/4                |     | TBD | μΑ    |  |

|                       |                        |           |         | 1/2                |     | TBD | μΑ    |  |

|                       |                        |           |         | 1/4                |     | TBD | μΑ    |  |

|                       |                        |           |         | 0                  |     | 50  | μΑ    |  |

NOTE:

IPAR (MAX) values measured with TCR set to 85°C.

**Table 10: Deep Power-Down Specifications and Conditions**

| DESCRIPTION     | CONDITIONS                                        | SYMBOL | TYP | MAX | UNITS |

|-----------------|---------------------------------------------------|--------|-----|-----|-------|

| Deep Power-Down | VIN = VCCQ or 0V; +25°C<br>ZZ# = LOW<br>CR[4] = 0 | Izz    |     | 10  | μΑ    |

**Table 11: Capacitance Specifications and Conditions**

| DESCRIPTION                   | CONDITIONS                               | SYMBOL | MIN | MAX | UNITS | NOTES |

|-------------------------------|------------------------------------------|--------|-----|-----|-------|-------|

| Input Capacitance             | $T_C = +25^{\circ}C; f = 1 \text{ MHz};$ | CIN    | -   | 6   | pF    | 1     |

| Input/Output Capacitance (DQ) | VIN = 0V                                 | Cio    | -   | 6   | pF    | 1     |

#### NOTE:

1. These parameters are verified in device characterization and are not 100% tested.

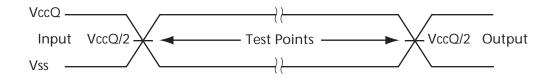

Figure 8: AC Input/Output Reference Waveform

#### NOTE:

AC test inputs are driven at VccQ for a logic 1 and Vss for a logic 0. Input timing begins at VccQ/2, and output timing ends at VccQ/2. Input rise and fall times (10% to 90%) < 1.6ns.

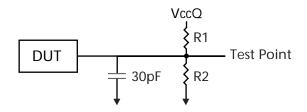

Figure 9: Output Load Circuit

**Table 12: Output Load Circuit**

| VccQ | R1/R2 |

|------|-------|

| 1.8V | 2.7ΚΩ |

| 2.5V | 3.7ΚΩ |

| 3.0V | 4.5ΚΩ |

#### **Table 13: READ Cycle Timing Requirements**

|                                  |                  | -7  | 70  | -8  | 35  |       |       |

|----------------------------------|------------------|-----|-----|-----|-----|-------|-------|

| PARAMETER                        | SYMBOL           | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Address Access Time              | <sup>t</sup> AA  |     | 70  |     | 85  | ns    |       |

| Page Access Time                 | <sup>t</sup> APA |     | 20  |     | 25  | ns    |       |

| LB#/UB# Access Time              | <sup>t</sup> BA  |     | 70  |     | 85  | ns    |       |

| LB#/UB# Disable to High-Z Output | <sup>t</sup> BHZ | 0   | 8   | 0   | 8   | ns    | 2     |

| LB#/UB# Enable to Low-Z Output   | <sup>t</sup> BLZ | 10  |     | 10  |     | ns    | 1     |

| Chip Select Access Time          | <sup>t</sup> CO  |     | 70  |     | 85  | ns    |       |

| Chip Disable to High-Z Output    | <sup>t</sup> HZ  | 0   | 8   | 0   | 8   | ns    | 2     |

| Chip Enable to Low-Z Output      | <sup>t</sup> LZ  | 10  |     | 10  |     | ns    | 1     |

| Output Enable to Valid Output    | <sup>t</sup> OE  |     | 20  |     | 20  | ns    |       |

| Output Hold from Address Change  | <sup>t</sup> OH  | 5   |     | 5   |     | ns    |       |

| Output Disable to High-Z Output  | <sup>t</sup> OHZ | 0   | 8   | 0   | 8   | ns    | 2     |

| Output Enable to Low-Z Output    | <sup>t</sup> OLZ | 5   |     | 5   |     | ns    | 1     |

| Page Cycle Time                  | <sup>t</sup> PC  | 20  |     | 25  |     | ns    |       |

| Read Cycle Time                  | <sup>t</sup> RC  | 70  |     | 85  |     | ns    |       |

**Table 14: WRITE Cycle Timing Requirements**

|                               |                  | -70 |     | -8  | 35  |       |       |

|-------------------------------|------------------|-----|-----|-----|-----|-------|-------|

| PARAMETER                     | SYMBOL           | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Address Setup Time            | <sup>t</sup> AS  | 0   |     | 0   |     | ns    |       |

| Address Valid to End of Write | <sup>t</sup> AW  | 70  |     | 85  |     | ns    |       |

| Byte Select to End of Write   | <sup>t</sup> BW  | 70  |     | 85  |     | ns    |       |

| CE# HIGH Time During Write    | <sup>t</sup> CEH | 5   |     | 5   |     | ns    |       |

| Maximum CE# Pulse Width       | <sup>t</sup> CEM |     | 10  |     | 10  | μs    |       |

| Chip Enable to End of Write   | <sup>t</sup> CW  | 70  |     | 85  |     | ns    |       |

| Data Hold from Write Time     | <sup>t</sup> DH  | 0   |     | 0   |     | ns    |       |

| Data Write Setup Time         | <sup>t</sup> DW  | 23  |     | 25  |     | ns    |       |

| Chip Enable to Low-Z Output   | <sup>t</sup> LZ  | 10  |     | 10  |     | ns    | 1     |

| End Write to Low-Z Output     | <sup>t</sup> OW  | 5   |     | 5   |     | ns    |       |

| Write Cycle Time              | <sup>t</sup> WC  | 70  |     | 85  |     | ns    |       |

| Write to High-Z Output        | <sup>t</sup> WHZ | 0   | 8   | 0   | 8   | ns    | 2     |

| Write Pulse Width             | <sup>t</sup> WP  | 46  |     | 50  |     | ns    |       |

| Write Recovery Time           | <sup>t</sup> WR  | 0   |     | 0   |     | ns    |       |

#### NOTE:

- 1. High-Z to Low-Z timings are tested with the circuit shown in Figure 9 on page 12. The Low-Z timings measure a 100mV transition away from the High-Z (VccQ/2) level toward either VoH or VoL.

- 2. Low-Z to High-Z timings are tested with the circuit shown in Figure 9 on page 12. The High-Z timings measure a 100mV transition from either VoH or VoL toward VccQ/2.

#### **Table 15: Load Configuration Register Timing Requirements**

|                               |                   | -70 |     | -85 |     |       |       |

|-------------------------------|-------------------|-----|-----|-----|-----|-------|-------|

| DESCRIPTION                   | SYMBOL            | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Address Setup Time            | <sup>t</sup> AS   | 0   |     | 0   |     | ns    |       |

| Address Valid to End of Write | <sup>t</sup> AW   | 70  |     | 85  |     | ns    |       |

| Chip Deselect to ZZ# LOW      | <sup>t</sup> CDZZ | 5   |     | 5   |     | ns    |       |

| Chip Enable to End of Write   | <sup>t</sup> CW   | 70  |     | 85  |     | ns    |       |

| Write Cycle Time              | <sup>t</sup> WC   | 70  |     | 85  |     | ns    |       |

| Write Pulse Width             | <sup>t</sup> WP   | 40  |     | 40  |     | ns    |       |

| Write Recovery Time           | <sup>t</sup> WR   | 0   |     | 0   |     | ns    |       |

| ZZ# LOW to WE# LOW            | <sup>t</sup> ZZWE | 10  | 500 | 10  | 500 | ns    |       |

#### **Table 16: Deep Power-Down Timing Requirements**

|                          |                    | -70 |     | -85 |     |       |       |

|--------------------------|--------------------|-----|-----|-----|-----|-------|-------|

| DESCRIPTION              | SYMBOL             | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Chip Deselect to ZZ# LOW | <sup>t</sup> CDZZ  | 5   |     | 5   |     | ns    |       |

| Deep Power-Down Recovery | <sup>t</sup> R     | 150 |     | 150 |     | μs    |       |

| Minimum ZZ# Pulse Width  | <sup>t</sup> ZZMIN | 10  |     | 10  |     | μs    |       |

#### **Table 17: Power-Up Initialization Timing Requirements**

|                                |                 | -70 |     | -85 |     |       |       |

|--------------------------------|-----------------|-----|-----|-----|-----|-------|-------|

| PARAMETER                      | SYMBOL          | MIN | MAX | MIN | MAX | UNITS | NOTES |

| Power-Up Initialization Period | <sup>t</sup> PU | 150 |     | 150 |     | μs    |       |

Figure 10: Power-Up Initialization Period

**Table 18: Initialization Timing Parameters**

|                 | -70 |     | -8  |     |       |

|-----------------|-----|-----|-----|-----|-------|

| SYMBOL          | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> PU | 150 |     | 150 |     | μs    |

Figure 11: Load Configuration Register

**Table 19: Load Configuration Register Timing Requirements**

|                   | -70 |     | -8  |     |       |

|-------------------|-----|-----|-----|-----|-------|

| SYMBOL            | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> AS   | 0   |     | 0   |     | ns    |

| <sup>t</sup> AW   | 70  |     | 85  |     | ns    |

| <sup>t</sup> CDZZ | 5   |     | 5   |     | ns    |

| <sup>t</sup> CW   | 70  |     | 85  |     | ns    |

|                   | -70 |     | -8  |     |       |

|-------------------|-----|-----|-----|-----|-------|

| SYMBOL            | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> WC   | 70  |     | 85  |     | ns    |

| <sup>t</sup> WP   | 40  |     | 40  |     | ns    |

| <sup>t</sup> WR   | 0   |     | 0   |     | ns    |

| <sup>t</sup> ZZWE | 10  | 500 | 10  | 500 | ns    |

Figure 12: Deep Power-Down — Entry/Exit

**Table 20: Deep Power-Down Timing Parameters**

|                       | -70 |     | -8  |     |       |

|-----------------------|-----|-----|-----|-----|-------|

| SYMBOL                | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> CDZZ     | 5   |     | 5   |     | ns    |

| <sup>t</sup> R        | 150 |     | 150 |     | μs    |

| <sup>t</sup> ZZ (MIN) | 10  |     | 10  |     | μs    |

Figure 13: Single READ Operation (WE# = VIH)

**Table 21: READ Timing Parameters**

|                  | -70 |     | -8  | <b>15</b> |       |

|------------------|-----|-----|-----|-----------|-------|

| SYMBOL           | MIN | MAX | MIN | MAX       | UNITS |

| <sup>t</sup> AA  |     | 70  |     | 85        | ns    |

| <sup>t</sup> BA  |     | 70  |     | 85        | ns    |

| <sup>t</sup> BHZ | 0   | 8   | 0   | 8         | ns    |

| <sup>t</sup> BLZ | 10  |     | 10  |           | ns    |

| <sup>t</sup> CO  |     | 70  |     | 85        | ns    |

| <sup>t</sup> HZ  | 0   | 8   | 0   | 8         | ns    |

|                  | -70 |     | -8  |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> LZ  | 10  |     | 10  |     | ns    |

| <sup>t</sup> OE  |     | 20  |     | 20  | ns    |

| <sup>t</sup> OHZ | 0   | 8   | 0   | 8   | ns    |

| <sup>t</sup> OLZ | 5   |     | 5   |     | ns    |

| <sup>t</sup> RC  | 70  |     | 85  |     | ns    |

Figure 14: Page Mode READ Operation (WE# = VIH)

**Table 22: Page Mode READ Timing Parameters**

|                  | -70 |     | -8  | 15  |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> AA  |     | 70  |     | 85  | ns    |

| <sup>t</sup> APA |     | 20  |     | 25  | ns    |

| <sup>t</sup> BA  |     | 70  |     | 85  | ns    |

| <sup>t</sup> BHZ | 0   | 8   | 0   | 8   | ns    |

| <sup>t</sup> BLZ | 10  |     | 10  |     | ns    |

| <sup>t</sup> CO  |     | 70  |     | 85  | ns    |

| <sup>t</sup> HZ  | 0   | 8   | 0   | 8   | ns    |

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> LZ  | 10  |     | 10  |     | ns    |

| <sup>t</sup> OE  |     | 20  |     | 20  | ns    |

| <sup>t</sup> OH  | 5   |     | 5   |     | ns    |

| <sup>t</sup> OHZ | 0   | 8   | 0   | 8   | ns    |

| <sup>t</sup> OLZ | 5   |     | 5   |     | ns    |

| <sup>t</sup> PC  | 20  |     | 25  |     | ns    |

| <sup>t</sup> RC  | 70  |     | 85  |     | ns    |

Figure 15: WRITE Cycle (WE# Control)

**Table 23: WRITE Timing Parameters**

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> AS  | 0   |     | 0   |     | ns    |

| <sup>t</sup> AW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> BW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> CEM |     | 10  |     | 10  | μs    |

| <sup>t</sup> CW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> DH  | 0   |     | 0   |     | ns    |

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> DW  | 23  |     | 25  |     | ns    |

| <sup>t</sup> OW  | 5   |     | 5   |     | ns    |

| tWC              | 70  |     | 85  |     | ns    |

| <sup>t</sup> WHZ | 0   | 8   | 0   | 8   | ns    |

| <sup>t</sup> WP  | 46  |     | 50  |     | ns    |

| <sup>t</sup> WR  | 0   |     | 0   |     | ns    |

Figure 16: WRITE Cycle (CE# Control)

**Table 24: WRITE Timing Parameters**

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> AS  | 0   |     | 0   |     | ns    |

| <sup>t</sup> AW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> BW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> CEH | 5   |     | 5   |     | ns    |

| <sup>t</sup> CEM |     | 10  |     | 10  | μs    |

| <sup>t</sup> CW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> DH  | 0   |     | 0   |     | ns    |

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> DW  | 23  |     | 25  |     | ns    |

| <sup>t</sup> LZ  | 10  |     | 10  |     | ns    |

| <sup>t</sup> WC  | 70  |     | 85  |     | ns    |

| <sup>t</sup> WHZ | 0   | 8   | 0   |     | ns    |

| <sup>t</sup> WP  | 46  |     | 50  |     | ns    |

| <sup>t</sup> WR  | 0   |     | 0   |     | ns    |

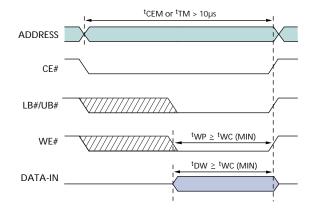

Figure 17: WRITE Cycle (LB#/UB# Control)

**Table 25: WRITE Timing Parameters**

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> AS  | 0   |     | 0   |     | ns    |

| <sup>t</sup> AW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> BW  | 70  |     | 85  |     | ns    |

| <sup>t</sup> CEM |     | 10  |     | 10  | μs    |

| <sup>t</sup> DH  | 0   |     | 0   |     | ns    |

|                  | -70 |     | -85 |     |       |

|------------------|-----|-----|-----|-----|-------|

| SYMBOL           | MIN | MAX | MIN | MAX | UNITS |

| <sup>t</sup> DW  | 23  |     | 25  |     | ns    |

| <sup>t</sup> LZ  | 10  |     | 10  |     | ns    |

| tWC              | 70  |     | 85  |     | ns    |

| <sup>t</sup> WHZ | 0   | 8   | 0   | 8   | ns    |

| tWR              | 0   |     | 0   |     | ns    |

Figure 18: 48-Ball FBGA

#### NOTE:

- 1. All dimensions in millimeters, MAX/MIN or typical where noted.

- 2. Package width and length do not include mold protrusion; allowable mold protrusion is 0.25mm per side.

#### **Data Sheet Designation: PRELIMINARY**

This data sheet contains initial characterization limits, subject to change upon full characterization of production devices.

8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900

E-mail: prodmktg@micron.com, Internet: http://www.micron.com, Customer Comment Line: 800-932-4992

Micron, and the Micron Technology, Inc.

CellularRAM is a trademark of Micron Technology, Inc., inside the U.S. and a trademark of Infineon Technologies outside the U.S.

All other trademarks are the property of their respective owners.

### **APPENDIX A**

## How Extended Timings Impact CellularRAM<sup>™</sup> Operation

#### Introduction

CellularRAM<sup>TM</sup> products use a DRAM technology that periodically requires refresh to ensure against data corruption. CellularRAM devices include on-chip circuitry that performs the required refresh in a manner that is completely transparent in systems with normal bus timings. The refresh circuitry does impose constraints on timings in systems that take longer than  $10\mu$ s to complete WRITE operations. This appendix describes CellularRAM timing requirements in systems that perform extended operations.

#### **Operation When Page Mode is Disabled**

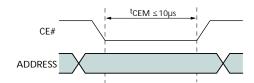

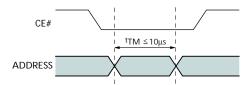

CellularRAM products require that all WRITE operations must be completed within  $10\mu s$ . After completing an operation, the device must either enter standby (by transitioning CE# HIGH), or else perform a second operation using a new address. Figures 19 and 20 demonstrate these constraints as they apply during an asynchronous (page-mode-disabled) operation. Either the CE# active period ( $^t$ CEM in Figure 19) or the address valid period ( $^t$ TM in Figure 20) must be less than  $10\mu s$  during any operation to accommodate orderly scheduling of refresh.

Figure 19: Extended Timing for <sup>t</sup>CEM

NOTE:

Timing constraints when page mode is disabled.

Figure 20: Extended Timing for <sup>t</sup>TM

NOTE:

Timing constraints when page mode is disabled.

#### **Operation When Page Mode is Enabled**

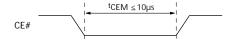

When a CellularRAM device is configured for page mode operation, the address inputs are used to accelerate read accesses and cannot be used by the on-chip circuitry to schedule refresh. CE# must return HIGH upon completion of all WRITE operations when page mode is enabled (Figure 21). The total time taken for a WRITE operation should not exceed 10µs to accommodate orderly scheduling of refresh.

Figure 21: Extended Timing for <sup>t</sup>CEM

NOTE:

Timing constraints when page mode is enabled.

#### **Impact on Extended WRITE Operations**

Modified timings are only required during extended WRITE operations (see Figure 22 below). An extended WRITE operation requires that both the write pulse width (<sup>t</sup>WP) and the data valid period (<sup>t</sup>DW) will need to be lengthened to at least the minimum WRITE cycle time (<sup>t</sup>WC [MIN]). These increased timings ensure that time is available for both a refresh operation and successful completion of the WRITE operation.

Figure 22: Extended WRITE Operation

#### Summary

CellularRAM products are designed to ensure that any possible bus timings do not cause corruption of array data due to lack of refresh. The on-chip refresh circuitry will only affect the required timings for WRITE operations (READs are unaffected) performed in a system with

a slow memory interface. The impact for WRITE operations is that some of the timing parameters (<sup>t</sup>WP, <sup>t</sup>DW) are lengthened. The modified timings are likely to have little or no impact when interfacing a Cellular-RAM device with a low-speed memory bus.

### **Table 26: Revision History**

| CHANGE | DATE     | CHANGED<br>BY | DESCRIPTION                                                                                                                                                                                                                            |

|--------|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | 07/10/03 | ddb           | Input/Output leakage to 1µA.                                                                                                                                                                                                           |

| 6      | 6/23/03  | ddb           | Incorporated Industrial Temperature data where applicable.                                                                                                                                                                             |

| 5      | 6/20/03  | ddb           | Added condition ZZ# LOW to PAR and DPD tables.                                                                                                                                                                                         |

| 4      | 6/19/03  | ddb           | Changed standby power to 90µA and 100µA respectively; changed specified values to "TBD."  Moved LB#/UB# rising edge back in WRITE Operation diagram.                                                                                   |

| 3      | 06/09/03 | ddb           | Absolute Maximum Signal Input value changed.                                                                                                                                                                                           |

| 2      | 06/06/03 | ddb           | Edits suggested 6/6:<br>Electrical Characteristics and Operating Conditions (Table 7 on page 10), changed<br>Input High Voltage MAX to VccQ + 0.2, Output HIGH Voltage and Output LOW<br>Voltage presentation changed for consistency. |

| 1      | 06/05/03 | ddb           | Initial release.                                                                                                                                                                                                                       |