DataShe

### MICRON

## **DRAM**

## 1MEG x 1 DRAM

NIBBLE MODE

#### **FEATURES**

- Industry standard x1 pin-out, timing, functions and packages

- High performance, CMOS silicon gate process

- Single +5V±10% power supply

- Low power, 5mW standby; 175mW active, typical

- All inputs, outputs and clocks are fully TTL and CMOS compatible

- 512 cycle refresh distributed across 8ms

- Refresh modes: RAS ONLY, CAS-BEFORE-RAS, and HIDDEN

- Optional Nibble Mode access cycle

| MARKING |                                     | Vcc                                             |

|---------|-------------------------------------|-------------------------------------------------|

| 2       |                                     |                                                 |

| - 8     |                                     |                                                 |

| -10     |                                     |                                                 |

| -12     |                                     |                                                 |

|         |                                     |                                                 |

| None    | DataSheet41                         | J.com                                           |

| C       |                                     |                                                 |

| Z       |                                     |                                                 |

| DJ      |                                     |                                                 |

|         | - 8<br>-10<br>-12<br>None<br>C<br>Z | - 8<br>-10<br>-12<br>None DataSheet40<br>C<br>Z |

#### GENERAL DESCRIPTION

The MT4C1025 is a randomly accessed solid-state memory containing 1,048,576 bits organized in a x1 configuration. During READ or WRITE cycles each bit is uniquely addressed through the 20 address bits which are entered 10 bits (A0-A9) at a time. RAS is used to latch the first 10 bits and CAS the latter 10 bits. A READ or WRITE cycle is selected with the WE input. A logic HIGH on WE dictates READ mode while a logic LOW on WE dictates WRITE mode. During a WRITE cycle, data in (D) is latched by the falling edge of WE or CAS, whichever occurs last. If WE goes LOW prior to CAS going LOW, the output pin(s) remain open (high Z) until the next CAS cycle. If WE goes LOW after data reaches the output pin(s), Q is activated and retains the selected cell data as long as CAS remains LOW (regardless of WE or RAS). This late WE pulse results in a READ-WRITE cycle.

Returning RAS and CAS HIGH terminates a memory cycle and decreases chip current to a reduced standby level. Also, the chip is preconditioned for the next cycle during

| <b>20 Pin DIP</b> (PD, CD)                                                                                                          | <b>20 Pin ZIP</b> (ZB) |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| D 1 • 18 Vss  WE 2 17 Q  RAS 3 16 CAS  ••TF 4 15 A9•  A0 5 14 A8  A1 6 13 A7  A2 7 12 A6  A3 8 11 A5  Vcc 9 10 A4  20 Pin Se  (DJA) | A9* 1                  |

PIN ASSIGNMENT (Top View)

| DQ                                    | 1 •      | 26                         | □ Vss                                |

|---------------------------------------|----------|----------------------------|--------------------------------------|

| WE [                                  | 2        | 25                         | þQ                                   |

| RAS [                                 | 3        | 24                         | CAS                                  |

| **TF 🛚                                | 4        | 23                         | D NC                                 |

| NC [                                  | 5        | 22                         | D A9*                                |

| A0 [<br>A1 [<br>A2 [<br>A3 [<br>Vcc [ | 10<br>11 | 18<br>17<br>16<br>15<br>14 | □ A8<br>□ A7<br>□ A6<br>□ A5<br>□ A4 |

\*Address not used for RAS ONLY refresh

\*\*TF = Test Function, Viv must be disconnected or between Vss and Vcc for normal operation.

the RAS high time. Memory cell data is retained in its correct state by maintaining power and executing any RAS cycle (READ, WRITE, RAS ONLY, CAS-BEFORE-RAS, or HIDDEN refresh) so that all 512 combinations of RAS addresses (A0-A8) are executed at least every 8ms, regardless of sequence.

NIBBLE MODE operation allows faster sequential serial data operations (READ, WRITE or READ-MODIFY-WRITE) up to 4 bits. The first of 4 bits is accessed in the usual manner with  $\overline{CAS}$  address A9 (nibble MSB) and  $\overline{RAS}$  address A9 (nibble LSB) selecting one of 4 bits within a nibble for initial access. By holding  $\overline{RAS}$  LOW,  $\overline{CAS}$  can be toggled incrementing the nibble address field in modulo 4 fashion with wrap around (see below).

MT4C1025

1-63

Micron Technology, Inc. reserves the right to change products or specifications without notice.

# MICRON

#### **FUNCTIONAL BLOCK DIAGRAM NIBBLE MODE** WE o DATA IN -o D BUFFER CAS . NO. 2 CLOCK GENERATOR **-o** () DATA OUT BUFFER NIBBLE SELECTOR COLUMN ADDRESS BUFFER (10) COLUMN DELODER 2048 ----REFRESH SENSE AMPLIFIERS CONTROLLER A 3 0-I/O GATING A 5 0 REFRESH --- 2048 --COUNTER A 7 0-ROW DECODER ROW 512 MEMORY ADDRESS ARRAY BUFFERS (10) NO. 1 CLOCK GENERATOR RAS . • V<sub>CC</sub>

**TRUTH TABLE**

**HIDDEN** REFRESH

**CAS-BEFORE-**

**RAS REFRESH**

L→H→L

H→L

L

DataSheet4U.com

| Function               | RAS | CAS   | WE    | TF | tR  | tC  |                                   |

|------------------------|-----|-------|-------|----|-----|-----|-----------------------------------|

| Standby                | Н   | Н     | Н     | Х  | Х   | Х   | High Impedance                    |

| READ                   | L   | L     | Τ     | Х  | ROW | COL | Data Out                          |

| WRITE<br>(EARLY-WRITE) | L   | L     |       | Х  | ROW | COL | Data In                           |

| READ-WRITE             | L   | L     | H→L→H | Х  | ROW | COL | Valid Data Out,<br>Valid Data In  |

| NIBBLE<br>READ         | L   | H→L→H | Н     | Х  | ROW | COL | Valid Data Out,<br>Valid Data Out |

| NIBBLE<br>WRITE        | L   | H→L→H | L     | х  | ROW | COL | Valid Data In,<br>Valid Data In   |

| NIBBLE<br>READ-WRITE   | L   | H→L→H | H→L→H | Х  | ROW | COL | Valid Data Out,<br>Valid Data In  |

| RAS ONLY<br>REFRESH    | L   | Н     | н     | Х  | ROW | n/a | High Impedance                    |

ROW

Χ

COL

Χ

Valid Data Out

High Impedance

**Addresses**

1-64

Χ

χ

Н

Н

DataSheet4U.com

www.DataSheet4U.com

⊸∨<sub>SS</sub>

DataShe

## MICHON

MT4C1025

#### **ABSOLUTE MAXIMUM RATINGS\***

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

....

## ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS (0°C $\leq$ T $_{A}$ $\leq$ 70°C)

| PARAMETER/CONDITION                                                                                          |                        | SYMBOL     | MIN  | MAX   | UNITS      | NOTES |

|--------------------------------------------------------------------------------------------------------------|------------------------|------------|------|-------|------------|-------|

| Supply Voltage                                                                                               |                        | Vcc        | 4.5  | 5.5   | V          | 1     |

| Input High (Logic 1) Voltage, All Inputs                                                                     |                        | ViH        | 2.4  | Vcc+1 | ٧          | 1     |

| Input Low (Logic 0) Voltage, All Inputs                                                                      |                        | VIL        | -1.0 | 0.8   | ٧          | 1     |

| INPUT LEAKAGE CURRENT<br>any input (0V ≤ V <sub>IN</sub> ≤ Vcc),<br>all other pins not under test = 0 volts) |                        | lı         | -10  | 10    | μА         |       |

| OUTPUT LEAKAGE CURRENT (Q is disa                                                                            | bled, 0V ≤ Voυτ ≤ Vcc) | loz        | -10  | 10    | μ <b>A</b> |       |

| OUTPUT LEVELS Output High voltage (lout = -5mA) Output Low voltage (lout = 4.2mA)                            | DataSheet4U.com        | Vон<br>Vol | 2.4  | 0.4   | V          |       |

et4U.con

Dataon

| lotes : 1, 3, 4, 6, | 7) (0°C ≤ T | <sub>∧</sub> ≤ 70°C; ' | $Vcc = 5.0V \pm 10\%$ |

|---------------------|-------------|------------------------|-----------------------|

|---------------------|-------------|------------------------|-----------------------|

| A = 10 0, 10 = 10 10, 10 0 = 10 10, 10 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                         |                  | MAX |     |     |       |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|-------|-------|

| PARAMETER/CONDITION                                                                                                                                          | SYMBOL           | -8  | -10 | -12 | UNITS | NOTES |

| OPERATING CURRENT (RAS and CAS = Cycling: tnc = tnc(MIN))                                                                                                    | lcc <sub>1</sub> | 70  | 60  | 50  | mA    | 3, 4  |

| OPERATING CURRENT: NIBBLE MODE (RAS = VIL, CAS = Cycling: tpc = tpc(MIN))                                                                                    | lcc2             | 70  | 60  | 50  | mA    | 3, 4  |

| STANDBY CURRENT: TTL INPUT LEVELS  Power supply standby current (RAS = CAS = ViH after 8 RAS cycles min.)                                                    | lcc3             | 3   | 2   | 2   | mA    |       |

| STANDBY CURRENT: CMOS INPUT LEVELS  Power supply standby current (RAS = CAS = Vcc -0.2V  after 8 RAS cycles min. All other inputs at Vcc-0.2V or Vss + 0.2V) | Icc4             | 1   | 1   | 1   | mA    |       |

| REFRESH CURRENT: RAS ONLY (RAS = Cycling: CAS = VIH)                                                                                                         | lcc5             | 70  | 60  | 50  | mA    | 3     |

| REFRESH CURRENT: CAS-BEFORE-RAS (RAS and CAS = Cycling)                                                                                                      | Icc6             | 70  | 60  | 50  | mA    | 3, 5  |

1-65

#### **CAPACITANCE**

| PARAMETER                       | SYMBOL | MIN | MAX | UNITS | NOTES |

|---------------------------------|--------|-----|-----|-------|-------|

| Input Capacitance: Ao-A9, D     | CI1    |     | 5   | pF    | 2     |

| Input Capacitance: RAS, CAS, WE | Cl2    | -   | 7   | рF    | 2     |

| Output Capacitance: Q           | Cô     | ·   | 7   | pF    | 2     |

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 6, 7, 8, 9, 10, 11, 12, 13) ( $0^{\circ}C \le T_{A} \le +70^{\circ}C$ ,  $Vcc = 5.0V \pm 10\%$ )

| A.C. CHARACTERISTICS                         |                  |                 | -8         |        | -10      | <u> </u> | -12    |       | <u> </u>          | _    |

|----------------------------------------------|------------------|-----------------|------------|--------|----------|----------|--------|-------|-------------------|------|

| PARAMETER                                    | SYM              | MIN             | MAX        | MIN    | MAX      | MIN      | MAX    | UNITS | NOTES             | _    |

| Random READ or WRITE cycle time              | t <sub>RC</sub>  | 150             |            | 180    |          | 220      |        | ns    | <u> </u>          | 1    |

| READ-MODIFY-WRITE cycle time                 | tRWC             | 175             |            | 210    | <u> </u> | 255      |        | ns    | <u> </u>          | _    |

| Access time from RAS                         | t <sub>RAC</sub> |                 | 80         |        | 100      |          | 120    | ns    | 14                | 1    |

| Access time from CAS                         | tCAC             |                 | 20         |        | 25       |          | 30     | ns    | 15                | ↓    |

| Access time from column address              | <sup>t</sup> AA  |                 | 40         |        | 50       |          | 60     | ns    | <u> </u>          | ↓    |

| Access time from CAS precharge               | t <sub>CPA</sub> |                 | 45         |        | 55       |          | 65     | ns    | <b></b>           | -    |

| RAS pulse width                              | t <sub>RAS</sub> | 80              | 10,000     | 100    | 10,000   | 120      | 10,000 | ns    | <u> </u>          | -    |

| RAS hold time                                | <sup>t</sup> RSH | 20              |            | 25     |          | 30       |        | ns    | <u> </u>          | -    |

| RAS precharge time                           | t <sub>RP</sub>  | 60              |            | 80     |          | 90       |        | ns    | <u> </u>          | ]    |

| CAS pulse width                              | t <sub>CAS</sub> | 20              | 10,000     | 25     | 10,000   | 30       | 10,000 | ns    | <u> </u>          | 4    |

| CAS hold time                                | t <sub>CSH</sub> | 1 <b>80</b> ta9 | Sheet4U.co | om 100 |          | 120      |        | ns    | D.                | - Sh |

| CAS precharge time                           | t <sub>CPN</sub> | 10              |            | 10     |          | 20       |        | ns    | 16 <sup>Dat</sup> | .801 |

| RAS to CAS delay time                        | <sup>t</sup> RCD | 20              | 60         | 10     | 75       | 15       | 90     | ns    | 17                | _    |

| CAS to RAS precharge time                    | t <sub>CRP</sub> | 5               |            | 10     |          | 15       |        | ns    |                   | _    |

| Row address set-up time                      | tASR             | 0               |            | 0      | <u> </u> | 0        |        | ns    | <u> </u>          | ╛    |

| Row address hold time                        | <sup>t</sup> RAH | 10              | T          | 15     | <u> </u> | 20       |        | ns    |                   | ╛    |

| RAS to column                                | t <sub>RAD</sub> | 15              | 40         | 20     | 50       | 15       | 60     | ns    | 18                | }    |

| address delay time                           | l'               |                 | <u> </u>   |        | !        | <u> </u> |        |       |                   | ]    |

| Column address set-up time                   | tASC             | 0               |            | 0      |          | 0        |        | ns    |                   | _    |

| Column address hold time                     | <sup>t</sup> CAH | 15              |            | 20     |          | 25       |        | ns    |                   | _    |

| Column address hold time (referenced to RAS) | <sup>t</sup> AR  | 60              |            | 75     |          | 110      |        | ns    |                   |      |

| Column address to RAS lead time              | <sup>t</sup> RAL | 40              |            | 50     |          | 60       |        | ns    |                   |      |

| Read command set-up time                     | t <sub>RCS</sub> | 0               |            | 0      |          | 0        |        | ns    |                   | _    |

| Read command hold time (referenced to CAS)   | <sup>t</sup> RCH | 0               |            | 0      |          | 0        |        | ns    | 19                |      |

| Read command hold time (referenced to RAS)   | <sup>t</sup> RRH | 0               |            | 0      |          | 0        |        | ns    | 19                |      |

| CAS to output in low-Z                       | t <sub>CLZ</sub> | 0               |            | 0      |          | 0        |        | ns    |                   | ]    |

| Output buffer turn-off delay                 | tOFF             | 0               | 20         | 0      | 20       | 0        | 25     | ns    | 20                | ]    |

| WE command set-up time                       | twcs             | 0               |            | 0      |          | 0        |        | ns    | 21                | ]    |

| Write command hold time                      | tWCH             | 15              |            | 20     |          | 25       | T      | ns    |                   |      |

| Write command hold time (referenced to RAS)  | tWCR             | 60              |            | 75     |          | 80       |        | ns    |                   |      |

| Write command pulse width                    | <sup>t</sup> WP  | 15              |            | 20     | 1        | 25       |        | ns    |                   | ]    |

1-66

\_\_\_\_\_

www.DataSheet4U.com

DataSheet4U.com

# MICRON

MT4C1025

## **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Notes: 6, 7, 8, 9, 10, 11, 12, 13) ( $0^{\circ}C \le T_{A} \le +70^{\circ}C$ ,  $Vcc = 5.0V \pm 10\%$ )

| A.C. CHARACTERISTICS                        | -8                |     |          | -10   | -12     |     |          |       |       |

|---------------------------------------------|-------------------|-----|----------|-------|---------|-----|----------|-------|-------|

| PARAMETER                                   | SYM               | MIN | MAX      | MIN   | MAX     | MIN | MAX      | UNITS | NOTES |

| Write command to RAS lead time              | <sup>t</sup> RWL  | 20  |          | 25    |         | 30  |          | ns    |       |

| Write command to CAS lead time              | tCWL              | 20  |          | 25    |         | 30  |          | ns    |       |

| Data-in set-up time                         | <sup>t</sup> DS   | 0   |          | 0     |         | 0   | <u> </u> | ns    | 22    |

| Data-in hold time                           | t <sub>DH</sub>   | 15  |          | 20    |         | 20  |          | ns    | 22_   |

| Data-in hold time<br>(referenced to RAS)    | <sup>t</sup> DHR  | 60  |          | 75    |         | 110 |          | ns    |       |

| RAS to WE delay time                        | tRWD              | 80  |          | 100   |         | 120 |          | ns    | 21    |

| Column address to WE delay time             | <sup>t</sup> AWD  | 40  |          | 50    |         | 60  |          | ns    | 21    |

| CAS to WE delay time                        | tCWD              | 20  |          | 25    |         | 35  |          | ns    | 21    |

| Transition time (rise or fall)              | t <sub>T</sub>    | 3   | 50       | 3     | 50      | 3   | 50       | ns    | 9, 10 |

| Refresh Period (512 cycles)                 | <sup>t</sup> REF  |     | 8        |       | 8       |     | 8        | ms    |       |

| RAS to CAS Precharge time                   | tRPC              | 0   |          | 0     |         | 0   |          | ns    |       |

| CAS set-up time<br>(CAS-BEFORE-RAS refresh) | <sup>†</sup> CSR  | 10  |          | 10    |         | 10  |          | ns    | 5     |

| CAS hold time<br>(CAS-BEFORE-RAS refresh)   | <sup>t</sup> CHR  | 30  |          | 30    |         | 30  |          | ns    | 5     |

| RAS pulse width (NIBBLE MODE)               | <sup>t</sup> RASN | 80  | 100,000  | 100   | 100,000 | 120 | 100,000  | ns    |       |

| CAS precharge time (NIBBLE MODE)            |                   | 10  |          | 10    |         | 15  |          | ns    |       |

| NIBBLE MODE cycle time                      | ¹NC               | 40  |          | 45    |         | 55  |          | ns    |       |

| NIBBLE MODE READ-MODIFY-                    | <sup>t</sup> NRWC | 65  |          | 75    |         | 85  |          | ns    |       |

| WRITE cycle time                            |                   | Da  | aSheet4L | l.com |         |     |          |       |       |

| NIBBLE MODE access time                     | <sup>t</sup> NCAC |     | 20       |       | 20      |     | 35       | ns    | 15    |

| NIBBLE MODE pulse width                     | <sup>t</sup> NCAS | 20  |          | 25    |         | 35  |          | ns    |       |

| NIBBLE MODE CAS precharge time              | t <sub>NCP</sub>  | 10  |          | 10    |         | 10  |          | ns    |       |

| NIBBLE MODE RAS hold time                   | tNRSH_            | 20  |          | 25    |         | 30  |          | ns    |       |

| NIBBLE MODE CAS to WE delay time            | tNCWD             | 20  |          | 25    |         | 35  |          | ns    |       |

| NIBBLE MODE WE command to RAS lead time     | <sup>t</sup> NRWL | 20  |          | 25    |         | 30  |          | ns    |       |

| NIBBLE MODE WE command to CAS lead time     | <sup>t</sup> NCWL | 20  |          | 25    |         | 30  |          | ns    |       |

et4U.com

ataShe

### MICHON

### MT4C1025

#### **NOTES**

- 1. All voltages referenced to Vss.

- 2. This parameter is sampled. Capacitance is calculated from the equation  $C = \underline{I\Delta t}$  with  $\Delta V = 3V$  and Vcc = 5V.

- 3. Icc is dependent on cycle rates.

- Icc is dependent on output loading and cycle rates.

Specified values are obtained with minimum cycle time and the output open.

- 5. Enables on-chip refresh and address counters.

- The minimum specifications are used only to indicate cycle time at which proper operation over the full temperature range (0°C ≤ T<sub>A</sub> ≤ 70°C) is assured.

- 7. An initial pause of 100µs is required after power-up followed by any 8 RAS cycles before proper device operation is assured. The 8 RAS cycle wake-up should be repeated any time the 8ms refresh requirement is exceeded.

- 8. AC characteristics assume  ${}^{t}T = 5$ ns.

- 9. Vih min and Vil max are reference levels for measuring timing of input signals. Transition times are measured between Vih and Vil (or between Vil and Vih).

- 10. In addition to meeting the transition rate specification, all input signals must transit between Vih and Vil. (or between Vil and Vih) in a monotonic manner.

- 11. If  $\overline{CAS}$  = ViH, data output is high impedance.

- 12. If  $\overline{CAS} = V_{IL}$ , data output may contain data from the last valid READ cycle.

- 13. Measured with a load equivalent to 2 TTL gates and 100pF.

- 14. Assumes that <sup>t</sup>RCD < <sup>t</sup>RCD (max). If <sup>t</sup>RCD is greater than the maximum recommended value shown in this table, <sup>t</sup>RAC will increase by the amount that <sup>t</sup>RCD exceeds the value shown.

- 15. Assumes that  ${}^{t}RCD \ge {}^{t}RCD$  (max).

- 16. If  $\overline{\text{CAS}}$  is LOW at the falling edge of  $\overline{\text{RAS}}$ , Q will be maintained from the previous cycle. To initiate a new cycle and clear the data out buffer,  $\overline{\text{CAS}}$  must be pulsed HIGH for <sup>t</sup>CPN.

- 17. Operation within the <sup>t</sup>RCD (max) limit ensures that <sup>t</sup>RAC (max) can be met. <sup>t</sup>RCD (max) is specified as a reference point only; if <sup>t</sup>RCD is greater than the specified <sup>t</sup>RCD (max) limit, then access time is controlled exclusively by <sup>t</sup>CAC.

- 18. Operation within the <sup>t</sup>RAD (max) limit ensures that <sup>t</sup>RCD (max) can be met. <sup>t</sup>RAD (max) is specified as a reference point only; if <sup>t</sup>RAD is greater than the specified <sup>t</sup>RAD (max) limit, then access time is controlled exclusively by <sup>t</sup>AA.

- 19. Either <sup>t</sup>RCH or <sup>t</sup>RRH must be satisfied for a READ cycle.

- 20. <sup>t</sup>OFF (max) defines the time at which the output achieves the open circuit condition and is not referenced to Voh or Vol.

- 21. ¹WCS, ¹RWD, ¹AWD and ¹CWD are restrictive operating parameters in late WRITE, READ-WRITE and READ-MODIFY-WRITE cycles only. If ¹WCS ≥ ¹WCS (min), the cycle is an early WRITE cycle and the data output will remain an open circuit throughout the entire cycle. If ¹RWD ≥ ¹RWD (min), ¹AWD ≥ ¹AWD (min) and ¹CWD ≥ ¹CWD (min), the cycle is a Pata She READ-WRITE and the data output will contain data read from the selected cell. If neither of the above conditions are met, the state of data out (at access time and until CAS goes back to Vih) is indeterminate

- 22. These parameters are referenced to  $\overline{\text{CAS}}$  leading edge in early WRITE cycles and  $\overline{\text{WE}}$  leading edge in late WRITE or READ-WRITE cycles.

- 23. A HIDDEN REFRESH may also be performed after a WRITE cycle. In this case WE = LOW.

1-68

## MICRON

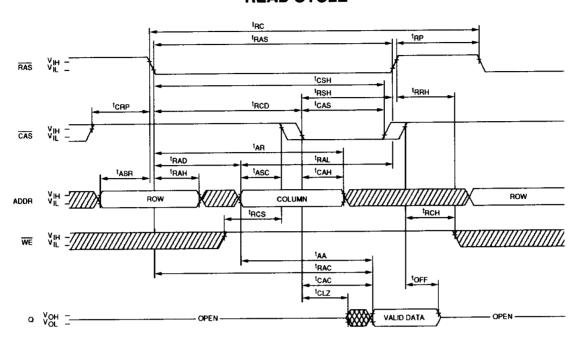

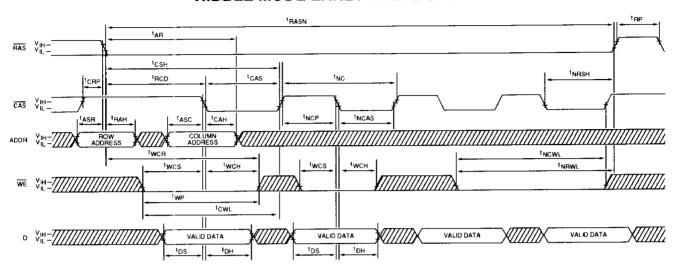

### **READ CYCLE**

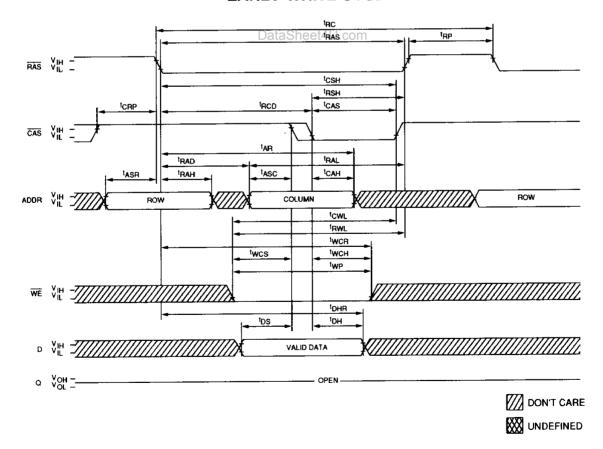

### **EARLY-WRITE CYCLE**

1-69

DataShe

DataSheet4U.com

et4U.com

# MICRON

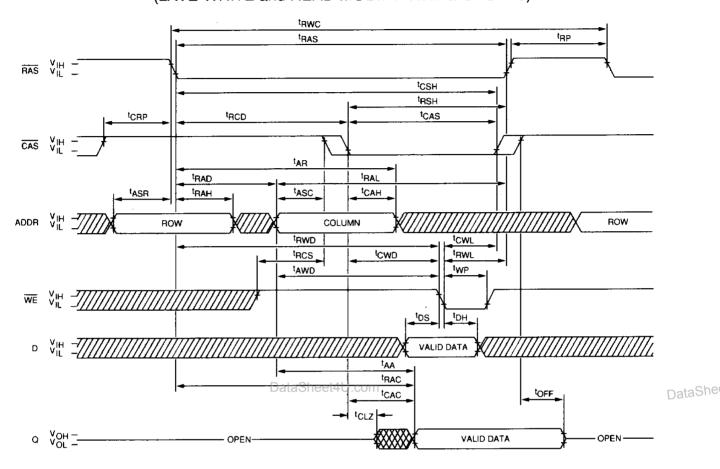

# **READ-WRITE CYCLE**(LATE-WRITE and READ-MODIFY-WRITE CYCLES)

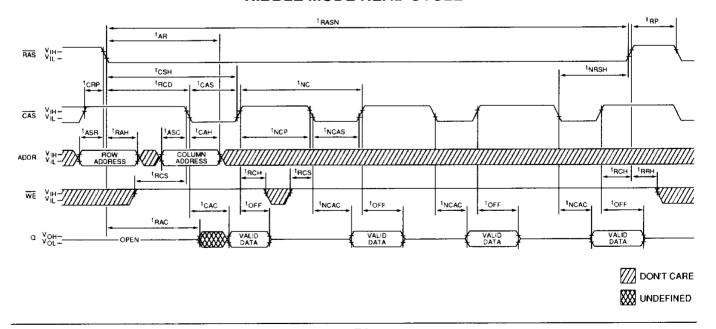

#### **NIBBLE MODE READ CYCLE**

1-70

DataSheet4U.com

# MICHON

MT4C1025

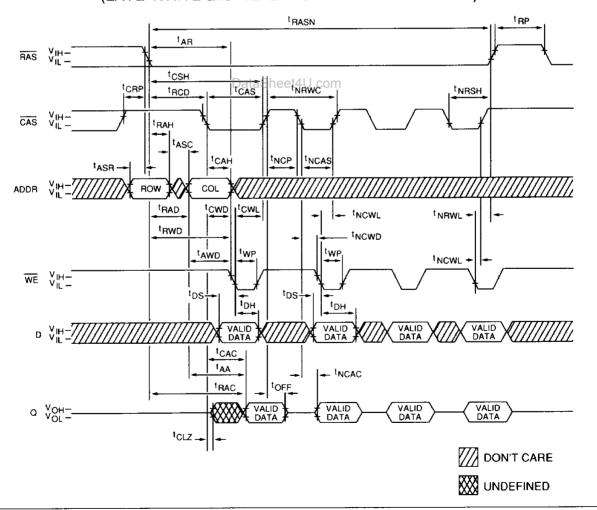

#### NIBBLE MODE EARLY-WRITE CYCLE

# NIBBLE MODE READ-WRITE CYCLE (LATE-WRITE and READ-MODIFY-WRITE CYCLES)

et4U.com

DataShe

1-71

MICRON

MT4C1025

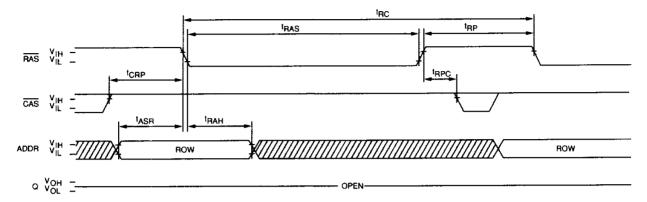

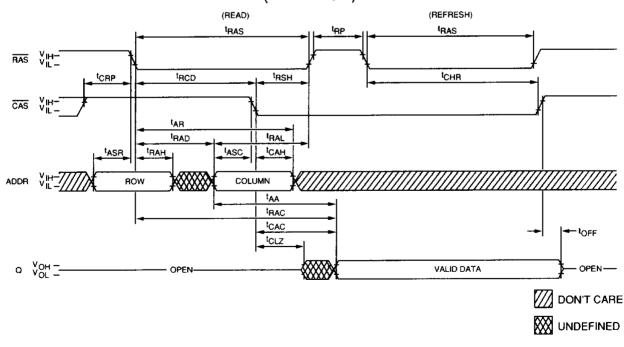

### **RAS ONLY REFRESH CYCLE**

(ADDR =  $A_0 - A_8$ ;  $A_9$  and  $\overline{WE}$  = DON'T CARE.)

### **CAS-BEFORE-RAS REFRESH CYCLE**

$(A_0 - A_9 \text{ and } \overline{WE} = DON'T CARE)$

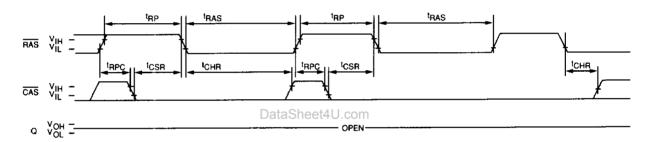

### **HIDDEN REFRESH CYCLE**

$(\overline{WE} = HIGH)^{23}$

1-72

DataSheet4U.com