## **SRAM**

## 4K x 4 SRAM

WITH OUTPUT ENABLE

#### **FEATURES**

- High speed: 9, 10, 12, 15, 20 and 25ns

- High-performance, low-power, CMOS double-metal process

- Single +5V ±10% power supply

- Easy memory expansion with CE and OE options

- All inputs and outputs are TTL-compatible

| OPTIONS               | MARKING |

|-----------------------|---------|

| Timing                |         |

| 9ns access            | - 9     |

| 10ns access           | -10     |

| 12ns access           | -12     |

| 15ns access           | -15     |

| 20ns access           | -20     |

| 25ns access           | -25     |

| • Packages            |         |

| Plastic DIP (300 mil) | None    |

| Plastic SOJ (300 mil) | DJ      |

|                       |         |

Temperature

· 2V data retention

| Commercial | (0°C to +70°C)    | None |

|------------|-------------------|------|

| Industrial | (-40°C to +85°C)  | IT   |

| Automotive | (-40°C to +125°C) | AT   |

| Extended   | (-55°C to +125°C) | XT   |

Part Number Example: MT5C1605DJ-15 IT

NOTE: Not all combinations of operating temperature, speed, data retention and low power are necessarily available. Please contact the factory for availability of specific part number combinations.

L

#### **GENERAL DESCRIPTION**

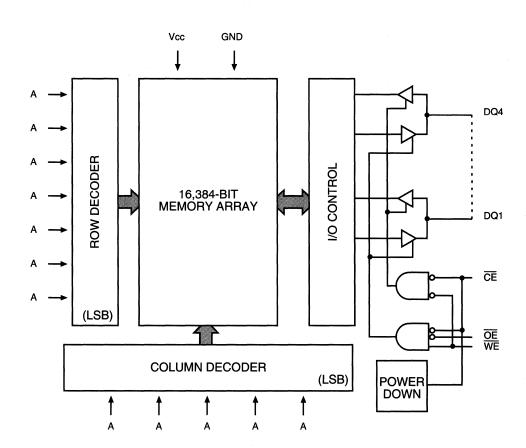

The MT5C1605 is organized as a 4,096 x 4 SRAM using a four-transistor memory cell with a high-speed, low-power CMOS process. Micron SRAMs are fabricated using double-layer metal, double-layer polysilicon technology.

For flexibility in high-speed memory applications, Micron offers chip enable  $(\overline{CE})$  and output enable  $(\overline{OE})$  with this organization. This enhancement can place the outputs in High-Z for additional flexibility in system design.

#### **PIN ASSIGNMENT (Top View)**

**22-Pin DIP** (SA-2)

| <b>A</b> 4 | þ | 1  | 0 | 22 | Vcc |

|------------|---|----|---|----|-----|

| <b>A</b> 5 | þ | 2  |   | 21 | АЗ  |

| A6         | þ | 3  |   | 20 | A2  |

| A7         | þ | 4  |   | 19 | A1  |

| A8         | þ | 5  |   | 18 | A0  |

| Α9         | þ | 6  |   | 17 | ИС  |

| A10        | þ | 7  |   | 16 | DQ4 |

| A11        | þ | 8  |   | 15 | DQ3 |

| CE         | þ | 9  |   | 14 | DQ2 |

| ŌĒ         | þ | 10 |   | 13 | DQ1 |

| Vss        | Ь | 11 |   | 12 | WE  |

## **24-Pin SOJ** (SD-1)

| A4  | þ | 1  | 24   | Ъ | Vcc |

|-----|---|----|------|---|-----|

| A5  | d | 2  | 23   | þ | АЗ  |

| A6  | Ц | 3  | 22   | þ | A2  |

| A7  | d | 4  | 21   | 6 | Α1  |

| A8  | q | 5  | 20   | þ | Α0  |

| A9  | d | 6  | 19   | 5 | NC  |

| NC  | þ | 7  | 18   | þ | NC  |

| A10 | d | 8  | 17   | Þ | DQ  |

| A11 | þ | 9  | 16   | Þ | DQ: |

| CE  |   | 10 | 15   | Þ | DQ  |

| ŌĒ  | þ | 11 | 14   |   | DQ  |

| Vss | þ | 12 | 13   | þ | WE  |

|     | Ų |    | <br> | , |     |

Writing to these devices is accomplished when write enable  $(\overline{WE})$  and  $\overline{CE}$  inputs are both LOW. Reading is accomplished when  $\overline{WE}$  remains HIGH and  $\overline{OE}$  and  $\overline{CE}$  go LOW. The device offers a reduced power standby mode when disabled. This allows system designers to meet low standby power requirements.

All devices operate from a single +5V power supply and all inputs and outputs are fully TTL-compatible.

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **TRUTH TABLE**

| MODE         | ŌĒ | CE | WE | DQ     | POWER   |

|--------------|----|----|----|--------|---------|

| STANDBY      | Х  | Н  | Х  | HIGH-Z | STANDBY |

| READ         | L  | L  | Н  | Q      | ACTIVE  |

| NOT SELECTED | Н  | L  | Н  | HIGH-Z | ACTIVE  |

| WRITE        | X  | L  | L  | D      | ACTIVE  |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Supply Relative to Vss | 1V to +7V      |

|---------------------------------------|----------------|

| Storage Temperature (plastic)         | 55°C to +150°C |

| Power Dissipation                     | 1W             |

| Short Circuit Output Current          |                |

| Voltage on Any Pin Relative to Vss    | 1V to Vcc +1V  |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \le T_A \le 70^{\circ}C; Vcc = 5V \pm 10\%)$

| DESCRIPTION                                               | CONDITIONS              | SYMBOL | MIN  | MAX    | UNITS | NOTES                    |  |

|-----------------------------------------------------------|-------------------------|--------|------|--------|-------|--------------------------|--|

| Input High (Logic 1) Voltage                              |                         | ViH    | 2.2  | Vcc +1 | V     | 1                        |  |

| Input Low (Logic 0) Voltage                               |                         | VIL    | -0.5 | 0.8    | V     | 1, 2                     |  |

| Input Leakage Current                                     | 0V ≤ VIN ≤ VCC          | ILı    | -5   | 5      | μΑ    |                          |  |

| Output Leakage Current Output(s) disabled 0V ≤ VouT ≤ Vcc |                         | ILo    | -5   | 5      | μА    | = 1<br>- 1<br>- 1<br>- 1 |  |

| Output High Voltage                                       | Iон = -4.0mA            | Vон    | 2.4  |        | V     | 1                        |  |

| Output Low Voltage                                        | lo <sub>L</sub> = 8.0mA | Vol    |      | 0.4    | ٧     | 1                        |  |

| Supply Voltage                                            |                         | Vcc    | 4.5  | 5.5    | ٧     | 1                        |  |

|                                    |                                                                                                                                                                                |        |     |     |     | MAX |     |     |     |       |       |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-----|-----|-----|-------|-------|--|

| DESCRIPTION                        | CONDITIONS                                                                                                                                                                     | SYMBOL | TYP | -9  | -10 | -12 | -15 | -20 | -25 | UNITS | NOTES |  |

| Power Supply<br>Current: Operating | CE ≤ VIL; Vcc = MAX<br>f = MAX = 1/ ¹RC<br>outputs open                                                                                                                        | lcc    | 125 | 190 | 185 | 175 | 165 | 140 | 130 | mA    | 3, 13 |  |

| Power Supply<br>Current: Standby   | СЕ ≥ Viн; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>outputs open                                                                                                            | ISB1   | 22  | 60  | 50  | 45  | 40  | 35  | 35  | mA    | 13    |  |

|                                    | $\overline{\text{CE}} \ge \text{Vcc} -0.2\text{V}; \text{Vcc} = \text{MAX}$ $\text{Vin} \le \text{Vss} +0.2\text{V or}$ $\text{Vin} \ge \text{Vcc} -0.2\text{V}; \text{f} = 0$ | ISB2   | 0.5 | 3   | 3   | 3   | 3   | 3   | 5   | mA    | 13    |  |

#### **CAPACITANCE**

| DESCRIPTION        | CONDITIONS                       | SYMBOL | MAX | UNITS | NOTES |

|--------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C; f = 1 MHz | Cı     | 5   | pF    | 4     |

| Output Capacitance | Vcc = 5V                         | Со     | 7   | pF    | 4     |

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

(Note 5) (0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C; Vcc = 5V  $\pm$ 10%)

| DECODIDEION                        | .                 |     | 9        | -10 -12 |     | -15 |     | -20 |     | -25 |     |     | T           |       |       |

|------------------------------------|-------------------|-----|----------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-------------|-------|-------|

| DESCRIPTION                        |                   | MIN | MAX      | MIN     | MAX | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX         | UNITS | NOTES |

| READ Cycle                         |                   |     |          |         |     |     |     |     |     |     |     |     | <del></del> |       | -     |

| READ cycle time                    | tRC               | 9   | 7        | 10      |     | 12  |     | 15  |     | 20  |     | 25  |             | ns    |       |

| Address access time                | <sup>t</sup> AA   |     | 9        |         | 10  |     | 12  |     | 15  |     | 20  |     | 25          | ns    |       |

| Chip Enable access time            | †ACE              |     | 9        |         | 9   |     | 10  |     | 12  |     | 15  |     | 20          | ns    |       |

| Output hold from address change    | tOH               | 3   |          | 3       |     | 3   |     | 3   |     | 3   |     | 3   |             | ns    |       |

| Chip Enable to output in Low-Z     | †LZCE             | 2   |          | 2       |     | 2   |     | 2   |     | 2   |     | 2   |             | ns    | 7, 14 |

| Chip disable to output in High-Z   | tHZCE             |     | 5        |         | 5   |     | 6   |     | 7   |     | 8   |     | 8           | ns    | 6, 7  |

| Chip Enable to power-up time       | <sup>t</sup> PU   | 0   |          | 0       |     | 0   |     | 0   |     | 0   |     | 0   |             | ns    |       |

| Chip disable to power-down time    | <sup>t</sup> PD   |     | 9        |         | 10  |     | 12  |     | 15  |     | 20  |     | 25          | ns    |       |

| Output Enable access time          | †AOE              |     | 4.5      |         | 5   |     | 6   |     | 7   |     | 8   |     | 8           | ns    |       |

| Output Enable to output in Low-Z   | †LZ0E             | 0   |          | 0       |     | 0   |     | 0   |     | 0   |     | 0   |             | ns    |       |

| Output disable to output in High-Z | tHZOE             |     | 4.5      |         | 5   |     | 5   |     | 6   |     | 7   |     | 8           | ns    | 6     |

| WRITE Cycle                        |                   |     | <b>.</b> | -       | -   |     |     |     |     |     |     |     |             |       | -     |

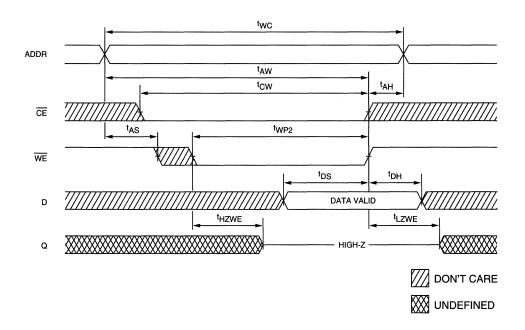

| WRITE cycle time                   | tWC               | 9   |          | 10      |     | 12  |     | 15  |     | 20  |     | 25  |             | ns    |       |

| Chip Enable to end of write        | tCW               | 7   |          | 8       |     | 10  |     | 12  |     | 15  |     | 20  |             | ns    |       |

| Address valid to end of write      | tAW               | 7   |          | 8       |     | 10  |     | 12  |     | 15  |     | 20  |             | ns    |       |

| Address setup time                 | <sup>t</sup> AS   | 0   |          | 0       |     | 0   |     | 0   |     | 0   |     | 0   |             | ns    |       |

| Address hold from end of write     | <sup>t</sup> AH   | 0   |          | 0       |     | 0   |     | 0   |     | 0   |     | 0   |             | ns    |       |

| WRITE pulse width                  | tWP1              | 6   |          | 7       |     | 8   |     | 10  |     | 12  |     | 15  |             | ns    |       |

| WRITE pulse width                  | tWP2              | 8   |          | 9       |     | 10  |     | 14  |     | 18  |     | 20  |             | ns    |       |

| Data setup time                    | t <sub>DS</sub>   | 5   |          | 6       |     | 7   |     | 8   |     | 9   |     | 10  |             | ns    |       |

| Data hold time                     | <sup>t</sup> DH   | 1   |          | 1       |     | 1   |     | 1   |     | 1   |     | 1   |             | ns    |       |

| Write disable to output in Low-Z   | tLZWE             | 2   |          | 2       |     | 2   |     | 2   |     | 2   |     | 2   |             | ns    | 7     |

| Write Enable to output in High-Z   | <sup>t</sup> HZWE |     | 4        |         | 5   |     | 5   |     | 6   |     | 8   |     | 8           | ns    | 6, 7  |

#### **INDUSTRIAL TEMPERATURE SPECIFICATIONS (IT)**

The following specifications are to be used for Industrial Temperature (IT) MT5C1605 SRAMs. (-40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C)

| DESCRIPTION                        | CONDITIONS                                                                          | SYMBOL            | -10 | -12 | -15 | -20 | -25 | UNITS | NOTES |

|------------------------------------|-------------------------------------------------------------------------------------|-------------------|-----|-----|-----|-----|-----|-------|-------|

| Power Supply<br>Current: Operating | CE ≤ VIL; Vcc = MAX<br>f = MAX = 1/ tRC<br>outputs open                             | Icc               | 195 | 185 | 175 | 150 | 140 | mA    | 3, 13 |

| Power Supply<br>Current: Standby   | CE ≥ ViH; Vcc = MAX<br>f = MAX = 1/ <sup>t</sup> RC<br>outputs open                 | Is <sub>B</sub> 1 | 60  | 50  | 45  | 40  | 40  | mA    | 13    |

|                                    | CE ≥ Vcc -0.2V; Vcc = MAX         VIN ≤ Vss +0.2V or         VIN ≥ Vcc -0.2V; f = 0 | IsB2              | 5   | 5   | 5   | 5   | 5   | mA    | 13    |

### DATA RETENTION ELECTRICAL CHARACTERISTICS (L version only)

| DESCRIPTION            | COND                           | SYMBOL   | TYP   | MAX | UNITS | NOTES |    |

|------------------------|--------------------------------|----------|-------|-----|-------|-------|----|

|                        | <u>CE</u> ≥ (Vcc -0.2V)        | Vcc = 2V | ICCDR | 130 | 300   | μΑ    | 14 |

| Data Retention Current | Vin ≥ (Vcc -0.2V)<br>or ≤ 0.2V | Vcc = 3V | ICCDR | 210 | 550   | μА    | 14 |

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

Refer to commercial temperature timing parameters for specifications not listed here. (Notes 5, 14) (-40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C)

| DESCRIPTION                      |       | -12 |     | -15 |     | -20 |     | -25 |     |       |       |

|----------------------------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|

|                                  |       | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| READ Cycle                       |       |     |     |     |     |     |     |     |     |       | 1000  |

| Output hold from address change  | tOH.  | 2   |     | 2   |     | 2   |     | 2   |     | ns    |       |

| Chip Enable to output in Low-Z   | tLZCE | 1   |     | 1   |     | 1   |     | 1   |     | ns    | 7     |

| WRITE Cycle                      |       |     |     |     |     |     |     |     |     |       |       |

| Write disable to output in Low-Z | tLZWE | 1   | 100 | 1   |     | 1   |     | 1   |     | ns    | 7     |

#### **AUTOMOTIVE AND EXTENDED TEMPERATURE SPECIFICATIONS (AT AND XT)**

The following specifications are to be used for Automotive Temperature (AT) and Extended Temperature (XT) MT5C1605 SRAMs. (-40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C - AT) (-55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C - XT)

|                                    |                                                                                                                                                                                    |        |     | MAX |     |     |       |       |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|-----|-------|-------|

| DESCRIPTION                        | CONDITIONS                                                                                                                                                                         | SYMBOL | -12 | -15 | -20 | -25 | UNITS | NOTES |

| Power Supply<br>Current: Operating | CE ≤ VIL; Vcc = MAX<br>f = MAX = 1/ ¹RC<br>outputs open                                                                                                                            | lcc    | 185 | 175 | 150 | 140 | mA    | 3, 13 |

| Power Supply<br>Current: Standby   | CE ≥ V <sub>IH</sub> ; V <sub>CC</sub> = MAX<br>f = MAX = 1/ <sup>1</sup> RC<br>outputs open                                                                                       | ISB1   | 50  | 45  | 40  | 40  | mA    | 13    |

|                                    | $\overline{\text{CE}} \ge \text{Vcc} - 0.2\text{V}; \text{Vcc} = \text{MAX}$ $\text{Vin} \le \text{Vss} + 0.2\text{V} \text{ or}$ $\text{Vin} \ge \text{Vcc} - 0.2\text{V}; f = 0$ | Isb2   | 5   | 5   | 5   | 5   | mA    | 13    |

#### DATA RETENTION ELECTRICAL CHARACTERISTICS (L version only)

| DESCRIPTION            | CONDITIONS                                             |          | SYMBOL | TYP | MAX | UNITS | NOTES |

|------------------------|--------------------------------------------------------|----------|--------|-----|-----|-------|-------|

| Data Batantian Current | <u>CE</u> ≥ (Vcc -0.2V)                                | Vcc = 2V | ICCDR  | 130 | 300 | μΑ    | 14    |

| Data Retention Current | V <sub>IN</sub> ≥ (V <sub>CC</sub> -0.2V)<br>or ≤ 0.2V | Vcc = 3V | ICCDR  | 210 | 550 | μА    | 14    |

#### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS**

Refer to commercial temperature timing parameters for specifications not listed here. (Notes 5, 14) (-40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C; -55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C; Vcc = 5V  $\pm$ 10%)

| DESCRIPTION                      |       |     | 12  | -1  | 5   | -2  | 20  | -2  | 5   |       |       |

|----------------------------------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-------|-------|

|                                  |       | MIN | MAX | MIN | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| READ Cycle                       |       |     |     |     |     |     |     |     |     |       |       |

| Output hold from address change  | tOH   | 2   |     | 2   |     | 2   |     | 2   |     | ns    |       |

| Chip Enable to output in Low-Z   | tLZCE | 1   |     | 1   |     | 1   |     | 1   |     | ns    | . 7   |

| WRITE Cycle                      |       |     |     |     |     |     |     |     |     |       |       |

| Write disable to output in Low-Z | tLZWE | 1   |     | 1.  |     | 1   |     | 1   |     | ns    | 7     |

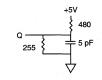

#### **AC TEST CONDITIONS**

| Input pulse levels            | Vss to 3.0V         |

|-------------------------------|---------------------|

| Input rise and fall times     | 3ns                 |

| Input timing reference levels | 1.5V                |

| Output reference levels       | 1.5V                |

| Output load                   | See Figures 1 and 2 |

Fig. 1 OUTPUT LOAD EQUIVALENT

Fig. 2 OUTPUT LOAD EQUIVALENT

#### **NOTES**

- 1. All voltages referenced to Vss (GND).

- 2. -3V for pulse width < tRC/2.

- 3. Icc is dependent on output loading and cycle rates.

- 4. This parameter is sampled.

- Test conditions as specified with the output loading as shown in Fig. 1 unless otherwise noted.

\*HZCE\_HZWE and HZOE are specified with CL.

- tHZCE, tHZWE and tHZOE are specified with CL = 5pF as in Fig. 2. Transition is measured ±500mV from steady state voltage.

- At any given temperature and voltage condition, <sup>t</sup>HZCE is less than <sup>t</sup>LZCE and <sup>t</sup>HZWE is less than <sup>t</sup>LZWE.

- 8. WE is HIGH for READ cycle.

- 9. Device is continuously selected. All chip enables are held in their active state.

- 10. Address valid prior to, or coincident with, latest occurring chip enable.

- 11. tRC = Read Cycle Time.

- 12. Chip enable and write enable can initiate and terminate a WRITE cycle.

- 13. Typical values are measured at 5V,  $25^{\circ}$ C and 15ns cycle time.

- 14. Typical currents are measured at 25°C.

- 15. Output enable  $(\overline{OE})$  is inactive (HIGH).

- 16. Output enable  $(\overline{OE})$  is active (LOW).

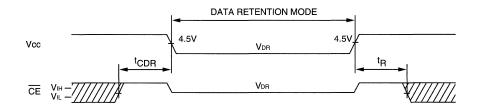

### DATA RETENTION ELECTRICAL CHARACTERISTICS (L version only)

| DESCRIPTION                             | CONDITIONS                                   |          | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|-----------------------------------------|----------------------------------------------|----------|------------------|-----|-----|-----|-------|-------|

| Vcc for Retention Data                  |                                              | VDR      | 2                |     |     | ٧   |       |       |

| Data Retention Current                  | <u>CE</u> ≥ (Vcc -0.2V)<br>Vin ≥ (Vcc -0.2V) | Vcc = 2V | ICCDR            |     | 130 | 300 | μА    | 14    |

| Data Noterition Guirent                 | or ≤ 0.2V                                    | Vcc = 3V | ICCDR            |     | 210 | 400 | μΑ    | 14    |

| Chip Deselect to Data<br>Retention Time |                                              |          | <sup>t</sup> CDR | 0   |     |     | ns    | 4     |

| Operation Recovery Time                 |                                              |          | <sup>t</sup> R   | †RC |     |     | ns    | 4, 11 |

#### **LOW Vcc DATA RETENTION WAVEFORM**

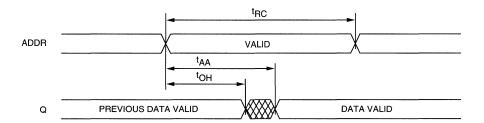

#### **READ CYCLE NO. 18,9**

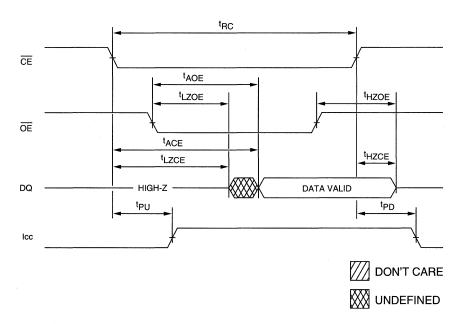

### READ CYCLE NO. 27,8,10

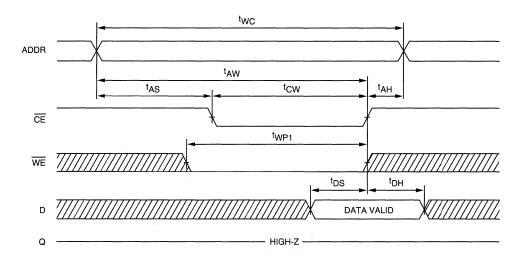

## WRITE CYCLE NO. 1 12 (Chip Enable Controlled)

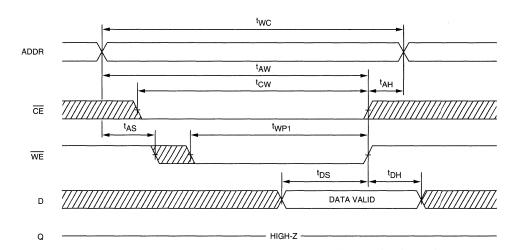

# WRITE CYCLE NO. 2 12, 15 (Write Enable Controlled)

# WRITE CYCLE NO. 3<sup>7, 12, 16</sup> (Write Enable Controlled)