# **ΜΕΟΙΛΤΕΚ**

# **RF and Wireless Systems** Konka WCX

## Data Sheet

## MT6162 (Othello H)

Version: 1.5 Release date/Status: not released July 23, 2010 Date created:

© 2011 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc. Unauthorized use, reproduction or disclosure of this information in whole or in part is strictly prohibited.

WCY

Specifications are subject to change without notice.

## Multi-band Multi-mode Single Chip HEDGE Transceiver

MT6162

© 2011 MediaTek Inc.

This document contains information that is confidential and proprietary to MediaTek Inc. and applies to a product under development. Its characteristics and specifications are subject to change without notice. MediaTek assumes no obligation regarding future manufacture unless otherwise agreed in writing. The information is provided AS IS; MediaTek assumes no responsibility for its use, including claims of infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any intellectual property rights, including patent rights, of MediaTek. Unauthorized use, reproduction, or disclosure of this information in whole or in part is strictly prohibited.

Konka WCX

## Multi-band Multi-mode Single Chip HEDGE Transceiver

## **MEDI/ITEK** Preliminary Datasheet

## MT6162

#### INTRODUCTION

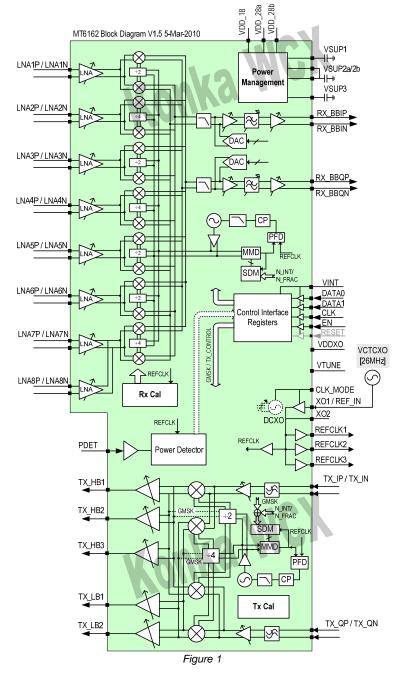

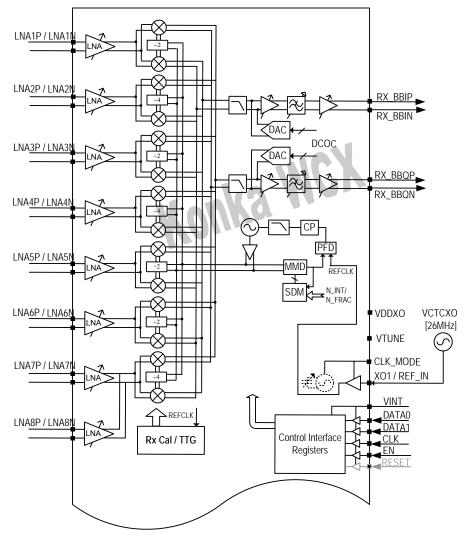

The MT6162 is a single-chip multi-mode multi-band transceiver offering unparalleled integration and feature set resulting in industry's lowest eBoM. It is fully compliant with 3G mode (3GPP Rel. 6), as well as supporting GSM/GPRS/EDGE modes (GGE). It constitutes with MediaTek's baseband modem ICs a complete chipset solution for 3G and GGE cellular user equipment. Quad-band GGE and a wide range of 3G bands support (I - VI, VIII - X) is provided in terms of both frequency ranges and the flexibility of band allocation.

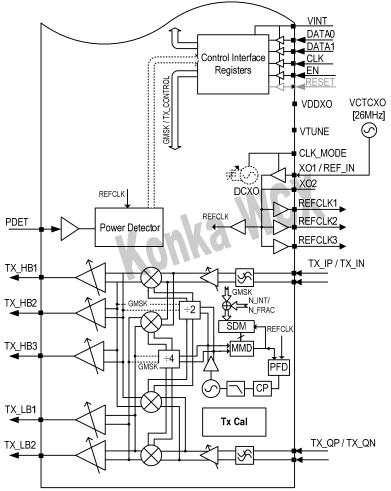

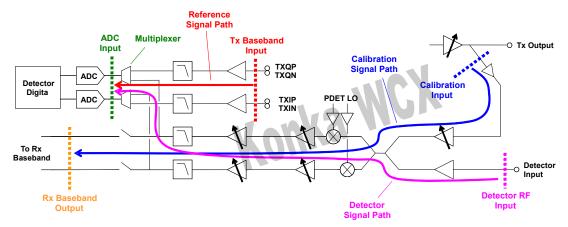

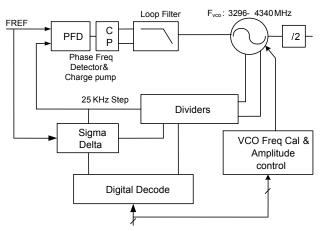

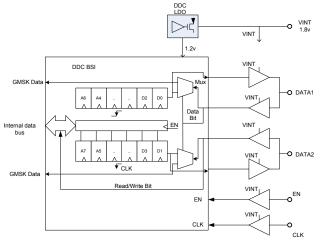

The direct conversion receiver is part of an over-sampled sigma-delta architecture, which shifts more signal conditioning to digital baseband (DBB) and results in optimum HSDPA throughput. The direct modulation transmitter (8PSK/3G), combined with a low noise GMSK constant envelope modulator or DFM (Direct-Frequency Modulation), delivers high modulation accuracy with exceptionally low noise and eliminates the need for transmit SAW filters in any of the supported GGE and 3G modes. On-chip impairments compensation is used to guarantee optimum 3G Rx and Tx performance. The 3G receiver operation is SAW-less and does not require any Rx SAW filters post LNAs. Two on-chip VCOs at 2xLO/4xLO frequencies provide the two local oscillators required for RX and TX sections; they are followed by frequency dividers and are locked to the system reference via two fast-settling RF Fractional-N PLLs.

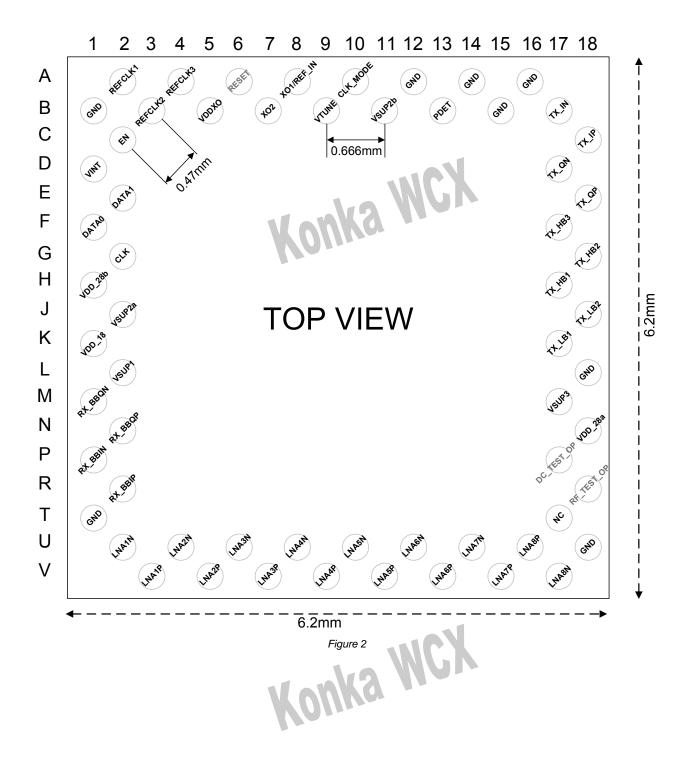

All functional and PLL programming is done via a 3-wire serial bus. The chip operates from 2.8V and 1.8V regulated supplies from a PMT sub-system in the baseband section, and is housed in a 6.2x6.2mm<sup>2</sup> 62-pin aQFN package with an offset array 0.666mm pin spacing (minimum pin to pin distance 0.47mm).

#### **FEATURES**

#### General

Fully integrated single chip RF Transceiver

Quad-band GSM/EDGE operation

Multi-band (I - VI, and VIII - X) 3G FDD operation

Part of MTK's turnkey platform solutions with best-in-class performance and industry's lowest eBoM due to smart architecture choice

Compliant with 3GPP HSDPA/HSUPA Release 6

On-chip correction for RF impairments, with digital baseband support for optimum TRx performance and reduced chip calibration test time

Lead free 62-pin aQFN package (6.2x6.2mm<sup>2</sup>)

#### Transmitter

Low noise GMSK/ 8PSK/ 3G TX modulator eliminating external SAW filters, with Direct-Frequency Modulation TX for GSM mode

Dedicated Tx drivers that can support radio configuration with multi-mode multi-Band PAs Excellent 3G EVM performance over the full Tx dynamic range

High dynamic range integrated synchronous power detector, with ultra-fast TX power control support Low Tx supply current from Vbat: Typical 48mA (3G avg. DG09, Band I); 36mA (GMSK DFM)

Receiver

High performance SAW-less (3G only) direct conversion receiver, with differential input LNAs Receiver with superior sensitivity and blocking margins

Low Rx supply current from Vbat: Typical 37mA (3G avg. DG09, Band I); 40mA (GSM/EDGE)

#### **Frequency Synthesizers**

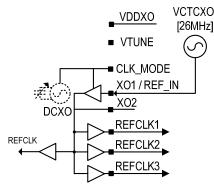

Fast settling synthesizers, with 26MHz internal DCXO or external VCTCXO reference

## MEDI/TEK

## Multi-band Multi-mode Single Chip HEDGE Transceiver

## **Preliminary Datasheet**

## MT6162

#### APPLICATIONS

Single and multi band / mode 3G handsets 3G/HSDPA/HSUPA Wireless data modems (3GPP Release 6) WEDGE / HEDGE solutions

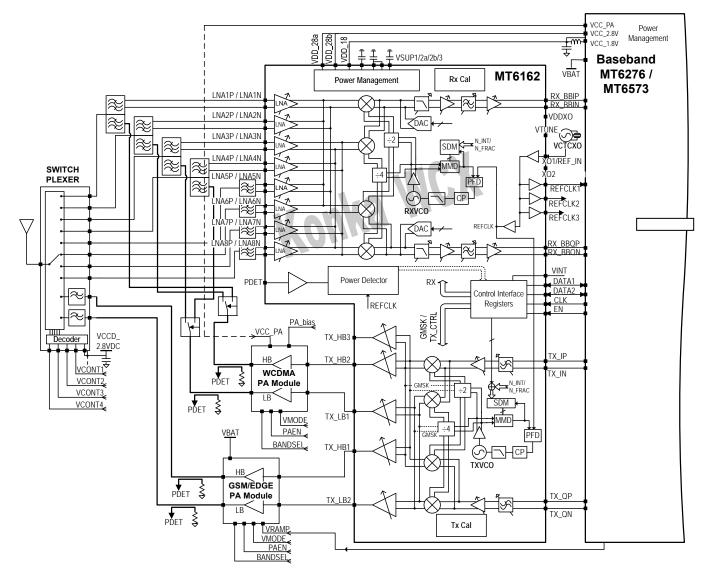

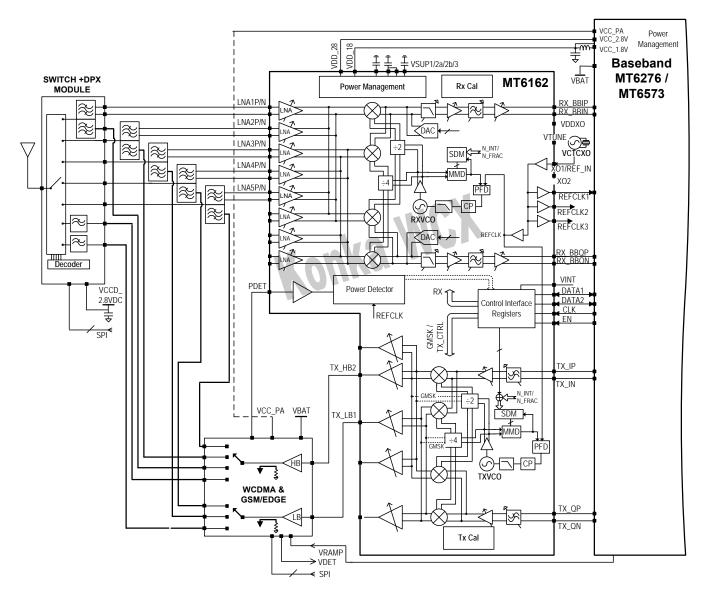

#### FUNCTIONAL BLOCK DIAGRAM

REV. (1.5) Mar 20<sup>th</sup> 2011

#### TABLE OF CONTENTS

| Introduction                                 |   |

|----------------------------------------------|---|

| Features                                     |   |

| Applications4                                |   |

| Functional block diagram4                    |   |

| Operating conditions                         |   |

| Absolute Maximum Ratings7                    |   |

| Thermal Resistance7                          |   |

| ESD Caution7                                 |   |

| Pin Configuration and Function Descriptions8 |   |

| Transceiver Pin configuration10              |   |

| Receiver Front-End mapping10                 |   |

| Transmitter Front-End mapping10              |   |

| Electrical Characteristics                   |   |

| DC & Voltage Regulators11                    | P |

| Receiver System12                            |   |

| Transmitter System15                         |   |

| Transmit Power Control18                     |   |

| Synthesizers and References18                | А |

| Serial Port19                                | 0 |

| Typical Performance Characteristics21        | 0 |

| Theory of Operation                          | R |

| 22           |

|--------------|

| 22           |

| 23           |

| 23           |

| 23           |

| erator<br>23 |

| 24           |

| 24           |

| 25           |

| 25           |

| 25           |

| 26           |

| 26           |

| 26           |

| 27           |

| 28           |

| 30           |

| 31           |

| 32           |

|              |

Konka WCX

#### OPERATING CONDITIONS

#### Table 1

| Parameter                                        | Symbol             | Min   | Тур   | Max   | Unit   | Comments                                                                                                 |

|--------------------------------------------------|--------------------|-------|-------|-------|--------|----------------------------------------------------------------------------------------------------------|

| Reference Supply                                 | V <sub>DD_28</sub> | 2.75  | 2.85  | 2.95  | V      | Linear regulated supply                                                                                  |

|                                                  | V <sub>DD_18</sub> | 1.75  | 1.825 | 1.9   | V      | Switching regulated supply                                                                               |

|                                                  | V <sub>INT</sub>   | 1.675 | 1.8   | 1.925 | V      | Serial interface control logic                                                                           |

| VCXO/DCXO Supply                                 | V <sub>DDXO</sub>  | 2.7   | 2.8   | 2.9   | V      | Linear regulated supply                                                                                  |

| Ambient Temperature                              | T <sub>amb</sub>   | -30   | 25    | 85    | °C     |                                                                                                          |

| Rx baseband load capacitance                     | C <sub>LD</sub>    |       |       | 10    | pF     | Equivalent Differential <sup>1)</sup>                                                                    |

| Rx baseband load resistance                      | R <sub>Ld</sub>    | 20    | 32    | 45    | kΩ     | Differential                                                                                             |

| Rx required amplitude balance                    | DA <sub>diff</sub> | -1    |       | 1     | dB     | All Rx input pairs                                                                                       |

| Rx required phase balance                        | Df <sub>diff</sub> | -10   |       | 10    | deg    | All Rx input pairs                                                                                       |

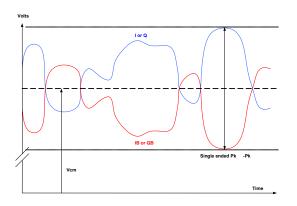

| Tx baseband I/Q common                           | V                  | 1.05  | 1.1   | 1.15  | V      |                                                                                                          |

| mode                                             | V <sub>CM</sub>    | 1.05  |       | 1.25  | V      | Acceptable range with slight degradation <sup>2)</sup>                                                   |

| Tx baseband I/Q differential<br>Full-Scale input |                    | 940   | 990   | 1040  | mVppd  | 2.4dB allocated for Tx RF impairments<br>compensation; 750mVppd effectively used<br>for I/Q Tx BB signal |

| Tx baseband I/Q Input<br>Resistance              |                    | 200   |       |       | kΩ     | Differential                                                                                             |

| Tx baseband I/Q Input                            |                    |       |       | 2.5   | pF     | Differential                                                                                             |

| Capacitance                                      |                    |       |       | 4.0   | pF     | Single-Ended                                                                                             |

| High Band (HB) Transmitter                       |                    | 1920  |       | 1980  |        | 3G Band I                                                                                                |

| Frequency                                        |                    | 1850  |       | 1910  | MHz    | 3G Band II / GSM1900                                                                                     |

|                                                  | F <sub>Tx</sub>    | 1710  |       | 1785  |        | 3G Band III/IV/IX/X / GSM1800                                                                            |

| Low Band (LB) Transmitter                        |                    | 824   |       | 849   | MHz    | 3G Band V/VI / GSM850                                                                                    |

| Frequency                                        |                    | 880   |       | 915   |        | 3G Band VIII / GSM900                                                                                    |

| High Band (HB) Receiver                          |                    | 2110  |       | 2170  |        | 3G Band I/IV/X                                                                                           |

| Frequency                                        |                    | 1930  |       | 1990  | MHz    | 3G Band II / GSM1900                                                                                     |

|                                                  | F <sub>Rx</sub>    | 1805  |       | 1880  |        | 3G Band III/IX / GSM1800                                                                                 |

| Low Band (LB) Receiver                           |                    | 869   |       | 894   | MHz    | 3G Band V/VI / GSM850                                                                                    |

| Frequency                                        |                    | 925   |       | 960   |        | 3G Band VIII / GSM900                                                                                    |

| Reference Input Clock<br>(VCTCXO) Frequency      | F <sub>ref</sub>   |       | 26    |       | MHz    |                                                                                                          |

| Voltage Swing                                    |                    | 700   |       | 1500  | mVpp   |                                                                                                          |

| Duty Cycle                                       |                    | 40    |       | 60    | %      |                                                                                                          |

| Reference Input Clock                            |                    |       |       | -106  | dBc/Hz | @ F <sub>offset</sub> = 100Hz                                                                            |

| (VCTCXO) Phase Noise                             |                    |       |       | -134  | dBc/Hz | @ F <sub>offset</sub> = 1KHz                                                                             |

|                                                  |                    |       |       | -144  | dBc/Hz | @ F <sub>offset</sub> = 10KHz                                                                            |

|                                                  |                    |       |       | -148  | dBc/Hz | @ F <sub>offset</sub> = 100KHz                                                                           |

| Harmonic Content                                 |                    |       |       | -8    | dBc    | HD2 @ 52MHz                                                                                              |

|                                                  |                    |       |       | -10   | dBc    | HD3 @ 78MHz                                                                                              |

|                                                  |                    |       |       | -20   | dBc    | HD4 @ 104MHz                                                                                             |

<sup>1)</sup>V<sub>CM</sub> up to 1.25V causes no performance degradation for nominal silicon over ETC. For worst-case silicon, a ~1dB degradation in full chain ACLR can be expected.

<sup>2)</sup> The load capacitance can be either common mode (to AC ground) or differential. The specification is written in terms of an equivalent differential load capacitance. In reality, the split can be arbitrary between common mode and differential mode, and both scenarios must be considered. The maximum difference between  $C_{RX-GND}$  and  $C_{RXB-GND}$  is 1pF.

#### ABSOLUTE MAXIMUM RATINGS

Table 2

| Parameter                      | Rating                             |

|--------------------------------|------------------------------------|

| VSUP3, VDD_28a/b, VDDXO        | -0.3 V to 3.6 V                    |

| VSUP1, VSUP2, VDD_18           | -0.3 V to 2.0 V                    |

| Serial Interface supply VINT   | -0.3 V to 2.0 V                    |

| Digital Input Voltage          | -0.3 to VINT+0.3V                  |

| Analog Input Voltage           | -0.3 to VDD28+0.3V                 |

| Storage Temperature            | -55 °C to 150 °C                   |

| Operating Junction Temperature | +125 °C                            |

| LNA Input Level                | +3dBm RF differential input (100Ω) |

| Power Detector Input Level     | +7dBm RF input (50Ω)               |

| Maximum power dissipation      | 750mW                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Notes Notes

- 1. No DC input should be directly applied to the Rx inputs. Matching network should either be a series capacitor/inductor or shunt inductor (RXn/RXnB)

- 2. Tx Output is DC shorted to ground internally no DC should be applied under any circumstances (AC coupling required for those PA's with DC at the input)

- 3. VSUP1-VSUP3: No short circuit protect is implemented; no DC should be applied under any circumstances

#### THERMAL RESISTANCE

Thermal resistance data is with a JEDEC standard PCB board.

#### **Table 3 Thermal Resistance**

| Package Type | Θ <sub>ja</sub> (to ambient) | $\Psi_{jb}$ (to board) | Unit |

|--------------|------------------------------|------------------------|------|

| aQFN         | 26                           | 5                      | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Konka WCX

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

| Pin | Name      | Description                                            | Pin | Name    | Description                            |

|-----|-----------|--------------------------------------------------------|-----|---------|----------------------------------------|

| A2  | REFCLK1   | Reference Clock Buffer #1 main for<br>digital baseband | K1  | VDD_18  | Regulated supply for IC                |

| A4  | REFCLK3   | Reference Clock Buffer #3                              | K17 | TX_LB1  | Tx Low band Driver #1                  |

| A6  | NC        | No connect                                             | L2  | VSUP1   | Internal Supply (ext. cap)             |

| A8  | XO1/REFIN | Crystal Pin #1 or Ref Clock Input                      | L18 | GND     | Ground; connect to GND plane or<br>PCB |

| A10 | CLK_MODE  | Select DCXO or VCTCXO                                  | M1  | RX_BBQN | Rx Baseband Output – Q Channe          |

| A12 | GND       | Ground; connect to GND plane on PCB                    | M17 | VSUP3   | Internal Supply (ext. cap)             |

| A14 | GND       | Ground; connect to GND plane on PCB                    | N2  | RX_BBQP | Rx Baseband Output – Q Channe          |

| A16 | GND       | Ground; connect to GND plane on PCB                    | N18 | VDD_28a | Regulated supply for IC                |

| B1  | GND       | Ground; connect to GND plane on PCB                    | P1  | RX_BBIN | Rx Baseband Output – I Channel         |

| B3  | REFCLK2   | Reference Clock Buffer #2                              | P17 | NC      | No connect                             |

| B5  | VDDXO     | Regulated supply for VCXO/DCXO                         | R2  | RX_BBIP | Rx Baseband Output – I Channel         |

| B7  | XO2       | Crystal Pin #2                                         | R18 | NC      | No connect                             |

| B9  | VTUNE     | AFCDAC Output                                          | T1  | GND     | Ground; connect to GND plane or<br>PCB |

| B11 | VSUP2b    | Internal Supply (ext. cap)                             | T17 | NC      | No Connect                             |

| B13 | PDET      | Power Detector Input                                   | U2  | LNA1N   | Rx Path #1 Input                       |

| B15 | GND       | Ground; connect to GND plane on<br>PCB                 | U4  | LNA2N   | Rx Path #2 Input                       |

| B17 | TX_IN     | Tx Baseband Input – I Channel                          | U6  | LNA3N   | Rx Path #3 Input                       |

| C2  | EN        | Serial Interface Enable (BSI)                          | U8  | LNA4N   | Rx Path #4 Input                       |

| C18 | TX_IP     | Tx Baseband Input – I Channel                          | U10 | LNA5N   | Rx Path #5 Input                       |

| D1  | VINT      | Serial interface control logic                         | U12 | LNA6N   | Rx Path #6 Input                       |

| D17 | TX_QN     | Tx Baseband Input – Q Channel                          | U14 | LNA7N   | Rx Path #7 Input                       |

| E2  | DATA1     | Serial Data I/O (BSI)                                  | U16 | LNA8P   | Rx Path #8 Input                       |

| E18 | TX_QP     | Tx Baseband Input –Q Channel                           | U18 | GND     | Ground; connect to GND plane or<br>PCB |

| F11 | DATA0     | Serial Data I/O (BSI)                                  | V3  | LNA1P   | Rx Path #1 Input                       |

| F17 | TX_HB3    | Tx High band Driver #3                                 | V5  | LNA2P   | Rx Path #2 Input                       |

| G2  | CLK       | Serial Interface Clock (BSI)                           | V7  | LNA3P   | Rx Path #3 Input                       |

| G18 | TX_HB2    | Tx High band Driver #2                                 | V9  | LNA4P   | Rx Path #4 Input                       |

| H1  | VDD_28b   | Regulated supply for IC                                | V11 | LNA5P   | Rx Path #5 Input                       |

| H17 | TX_HB1    | Tx High band Driver #1 (2G only)                       | V13 | LNA6P   | Rx Path #6 Input                       |

| J2  | VSUP2a    | Internal Supply (ext. cap)                             | V15 | LNA7P   | Rx Path #7 Input                       |

| J18 | TX_LB2    | Tx Low band Driver #2 (2G only)                        | V17 | LNA8N   | Rx Path #8 Input                       |

#### Table 4 Pin Allocation / Function Description

notes

1. VSUP2a and VSUP2b should be shorted on the PCB

2. VDD\_28a and VDD\_28b should be shorted on the PCB

3. Pin T17 is recommended a 'No Connect' pin to balance parasitics on the RF Input pins

4. CLK\_MODE:

GND = Internal DCXO (Crystal mode) Floating or connect to VDDXO = External Clock (VCTCXO)

- 9 - MediaTek Proprietary & Confidential Information

#### TRANSCEIVER PIN CONFIGURATION

#### **RECEIVER FRONT-END MAPPING**

Each of the eight independent LNA/mixer/divider are dedicated to either high (VCO divide-by-2) or low (VCO divide-by-4) band. Furthermore, even though the LNA's are identical, some recommended configurations are required since performance may be limited by board/package isolation.

| LNA # | High / Low | Configuration#1 | Configuration#2 | Configuration#3          |

|-------|------------|-----------------|-----------------|--------------------------|

| 1     | HB         | Band 2          | Band2/GSM1900   | Band 2                   |

| 2     | LB         | Band 8          | Band8/GSM900    | Band 8                   |

| 3     | HB         | Band 1          | Band 1          | Band 1                   |

| 4     | LB         | Band 5          | Band5/GSM850    | Band 5                   |

| 5     | HB         | GSM1900         | N/C             | Band 4                   |

| 6     | НВ         | GSM1800         | GSM1800         | GSM1800/1900<br>(Diplex) |

| 7     | LB         | GSM900          | N/C             | GSM900                   |

| 8     | LB         | GSM850          | N/C             | GSM850                   |

#### Table 5Rx configuration

#### TRANSMITTER FRONT-END MAPPING

Each of the five independent Tx output drivers are dedicated to either high (VCO divide-by-2) or low (VCO divide-by-4) band. Furthermore, two outputs (TX\_LB2/TX\_HB1) are dedicated to GSM/EDGE mode only, and the remaining three outputs are multimode (MM  $\equiv$  '3G and GSM/EDGE').

#### Table 6Tx Configuration#1

| Tx Output | GSM850/900   | GSM1800/1900 | B5/B8        | B1/B2/B3/B4 | Notes                                |

|-----------|--------------|--------------|--------------|-------------|--------------------------------------|

| TX_LB1    |              |              | $\checkmark$ |             | Single Mode WCDMA or<br>Multimode PA |

| TX_LB2    | $\checkmark$ |              |              |             | Single Mode GSM/EDGE PA              |

| TX_HB1    |              | ✓            |              |             | Single Mode GSM/EDGE PA              |

| TX_HB2    |              |              |              | ~           | Single Mode WCDMA or<br>Multimode PA |

| TX_HB3    |              |              |              | ✓           | Single Mode WCDMA or<br>Multimode PA |

#### Table 7Tx Configuration#2

| Tx Output | GSM850/900   | GSM1800/1900 | B5/B8 | B1/B2/B3/B4 | Notes                                |

|-----------|--------------|--------------|-------|-------------|--------------------------------------|

| TX_LB1    | $\checkmark$ |              | ~     |             | Single Mode WCDMA or<br>Multimode PA |

| TX_LB2    |              |              |       |             | Single Mode GSM/EDGE PA              |

| TX_HB1    |              |              |       |             | Single Mode GSM/EDGE PA              |

| TX_HB2    |              | 1            | 6Xno  | 1           | Single Mode WCDMA or<br>Multimode PA |

| TX_HB3    |              |              |       |             | Single Mode WCDMA or<br>Multimode PA |

#### ELECTRICAL CHARACTERISTICS

The Electrical Characteristics defined are valid for the Operating Conditions specified in Table 1, receiver pin configuration#1, and transmitter pin configuration#1, unless otherwise described. For ABB gain blocks settings based on a specific ABB gain. The dc-dc converter supplying  $V_{DD_{-18}}$  is assumed to have 90% efficiency and operates from a nominal battery voltage,  $V_{bat} \sim 3.6V$ .

Typical specifications are for register settings are mid-band channel frequencies, and recommended operating conditions. Min/Max specifications are for Extreme operating voltage and temperature conditions, unless otherwise stated.

#### **DC & VOLTAGE REGULATORS**

Table 8 Parameter Min Тур Max Unit **Test Conditions / Comments** VINT on: All else off Idle mode 11 μA Equivalent Battery Supply Current <sup>3)</sup> VDD 18 & VDD 28 **Rx** Alert 3.3 4 mΑ All Rx power domain LDOs enabled Rx On RX signal path fully enabled; Tx off 38 48 LNA HI gain/ ABB gain: 32dB 3G mode, max gain mA 31 40 3G mode, med gain mΑ LNA MED gain/ ABB gain: 14dB 3G mode, low gain 28 35 mΑ LNA LOW gain/ ABB gain: -7dB 50 GGE mode, max gain 40 LNA HI gain/ ABB gain: 32dB mΑ GGE mode, med gain 33 41 mΑ LNA MED gain/ ABB gain: 14dB 30 37.5 GGE mode, low gain mΑ LNA LOW gain/ ABB gain: -7dB 2 Tx Alert 3 All Tx power domain LDOs enabled mΑ Tx (HB) On Tx high-band signal path on; Rx off WCDMA mode @ Pout = +4.5dBm 92 112 mΑ 12.2k UL ref ch. (187mVd rms I/Q) 91 WCDMA mode @ Pout = +2.5dBm 110 mΑ 12.2k UL ref ch. (187mVd rms I/Q) WCDMA mode @ Pout = -10dBm 51 62 mΑ 12.2k UL ref ch. (187mVd rms I/Q) WCDMA mode @ Pout ≤ -58dBm 34 43 mΑ 12.2k UL ref ch. (187mVd rms I/Q) 35 GMSK mode 44 mΑ TX HB1 output 8PSK mode @ Pout = -2.5dBm 64 80 mΑ TX HB1 output; (180mVd rms I/Q) MMMB GMSK mode 94 mΑ TYP output power; RF gain = 1 MMMB 8PSK mode @ Pout = +3.5dBm 83 104 mΑ Tx (LB) On Tx low-band signal path on; Rx off 12.2k UL ref ch. (187mVd rms I/Q) WCDMA mode @ Pout = +2.5dBm 75 94 mΑ WCDMA mode @ Pout = -10dBm 40 50 12.2k UL ref ch. (187mVd rms I/Q) mΑ WCDMA mode @ Pout ≤ -58dBm 34 43 mΑ 12.2k UL ref ch. (187mVd rms I/Q) GMSK mode 36 45 mΑ TX LB2 output 8PSK mode @ Pout = +0.5dBm 71 89 mΑ TX LB2 output; (180mVd rms I/Q) MMMB GMSK mode 87 TYP output power; RF gain = 1 mΑ MMMB 8PSK mode @ Pout = +4.5dBm 90 110 mΑ

1.8V 1

| 5) | eauivalent | batterv | current = Idd(VDD) | (28) + Idd(VL) | DD 18) | $\times \frac{1.0}{} \times$ | < <u> </u> |

|----|------------|---------|--------------------|----------------|--------|------------------------------|------------|

|    | - 1        |         |                    | /(             | /      | 3.6V                         | 0.9        |

Table 9 Parameter Min Тур Max Unit **Test Conditions / Comments VDDXO Supply Current** External clock mode 2.2 mΑ REFCLK1 output enabled with DS load condition; AFC DAC turned off DCXO mode 3.5 REFCLK1 output enabled with DS load mΑ condition; AFC DAC turned off

2)

#### **RECEIVER SYSTEM**

All receiver characteristics are applicable for all RX frequency bands when operated under the recommended operating conditions and receiver pin configuration#1, unless stated otherwise. Receiver's differential input ports are matched to  $100\Omega$  (3G) /  $100\Omega$  (GGE) characteristic impedance (Z<sub>0</sub>), with all power levels (in dBm) referenced to Z<sub>0</sub>. The BB I/Q output ports are presented each with a differential load equivalent to  $32k\Omega$ ||5pF. The reference oscillator's frequency used for the on-chip PLL is 26MHz. For ABB gain blocks settings based on a specific ABB gain.

Typical specifications are for register settings mid-band channel frequency, and recommended operating conditions. Min/Max specifications are for Extreme operating voltage and temperature conditions, unless otherwise stated.

| Table 10                          | 1                      | 1   | 1   |     |      |                                                                                         |

|-----------------------------------|------------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------|

| Parameter                         | Symbol                 | Min | Тур | Max | Unit | Test Conditions / Comments                                                              |

| 3G Receiver                       |                        |     |     |     |      |                                                                                         |

| Input Return Loss                 | S <sub>11</sub>        |     | -10 |     | dB   | Ref. plane ( $Z_0$ ) at matching components                                             |

| Voltage gain: Max. (HB)           | G <sub>V,max</sub>     | 67  | 70  | 72  | dB   | LNA HI gain; G <sub>ABB</sub> = 32dB                                                    |

| Max (LB)                          |                        | 66  | 69  | 71  | dB   |                                                                                         |

| Voltage gain: Mid. (HB)           | G <sub>V,mid</sub>     | 38  | 41  | 43  | dB   | LNA MED gain; G <sub>ABB</sub> = 14dB                                                   |

| Voltage gain: Min. (HB)           | G <sub>V,min</sub>     | 3   | 6   | 8   | dB   | LNA LOW gain; G <sub>ABB</sub> = -7dB                                                   |

| Min. (LB)                         |                        | 5   | 8   | 10  | dB   |                                                                                         |

| DSB Noise Figure (HB)             | NF <sub>HI</sub>       |     | 2.5 | 3.9 | dB   | All frequency channels; LNA HI gain;                                                    |

| (LB)                              |                        |     | 2.6 | 4.0 | dB   | G <sub>ABB</sub> = 29dB                                                                 |

| DSB Noise Figure, Mid. gain       | NF <sub>MID</sub>      |     | 13  | 16  | dB   | LNA MED gain; G <sub>ABB</sub> = 14dB                                                   |

| Rx Composite EVM*                 | EVM <sub>Rx</sub>      |     |     |     |      | -63dBm desired signal; Rx gain = G <sub>V,mid</sub> ;                                   |

| (* not including digital baseband |                        |     | 5   | 8   | %    | // (HSDPA Hset-2 QPSK)                                                                  |

| phase compensation)               |                        |     | 6   | 9   | %    | // (HSDPA Hset-2 16QAM)                                                                 |

| Input IP3 (ACS1)                  | iIP <sub>3,ACS1</sub>  | -3  | 2   |     | dBm  | df1= $\pm$ 3.5M, df2= $\pm$ 6.5M; -35dBm/tone;<br>LNA MED gain; G <sub>ABB</sub> = 23dB |

| Input IP3 (ACS2)                  | iIP <sub>3,ACS2</sub>  | 0   | 5   |     | dBm  | df1= ±3.5M, df2= ±6.5M; –20dBm/tone;<br>LNA LOW gain; G <sub>ABB</sub> = 20dB           |

| Input IP3 (10/20M) (HB)           | ilP <sub>3,IM</sub>    | -7  | -2  |     | dBm  | df1= ±10.1MHz, df2= ±20MHz //                                                           |

| (LB)                              | -,                     | -5  | 0   |     |      | –38dBm/tone; LNA HI gain; G <sub>ABB</sub> = 29dB                                       |

| Input IP3 (NB_IM)                 | iIP <sub>3,NBIM</sub>  |     |     |     |      | –35dBm/tone; LNA HI gain; G <sub>ABB</sub> = 17dB                                       |

| (HB)                              | 0,112.111              | -7  | -2  |     | dBm  | df1/2= ±3.5MHz/ ±5.9MHz (band II/V/X);                                                  |

| (LB)                              |                        | -4  | 1   |     | dBm  | df1/2= ±3.6MHz/±6.0MHz (band III/ VIII)                                                 |

| Input IP3 (GMSK w Tx Blocker)     | iIP <sub>3,NBwTx</sub> |     |     |     |      | –35dBm/tone; LNA MED gain; G <sub>ABB</sub> =<br>29dB                                   |

| Band II/V/X                       |                        | -2  | 3   |     | dBm  | df1= ±2.7MHz, f2/f3=f <sub>Tx</sub> -1.1/+1.1MHz                                        |

| Band III/VIII                     |                        | -2  | 3   |     | dBm  | df1= ±2.8MHz, f2/f3=f <sub>Tx</sub> -1.1/+1.1MHz                                        |

| Input IP3 (Out of Band blocker)   | ilP <sub>3,OBwTx</sub> |     | _   |     |      | LNA HI gain; G <sub>ABB</sub> = 29dB                                                    |

| Band I                            |                        | -7  | -3  |     | dBm  | 2024.9M/ –38dBm, 1930M/ –28dBm                                                          |

| Band II                           |                        | -7  | -3  |     | dBm  | 1830.2M/ –38dBm, 1910M/ –28dBm                                                          |

| Band V                            |                        | -4  | 0   |     | dBm  | 784.2M/ –41dBm, 829M/ –31dBm                                                            |

| Band VIII                         |                        | -4  | 0   |     | dBm  | 840.2M/ –41dBm, 885M/ –31dBm                                                            |

|                                   | iD                     | 50  | >60 |     |      |                                                                                         |

| Input IP2 (ACS2)                  | iIP <sub>2,ACS2</sub>  | 50  | -00 | 2   | dBm  | df1= $\pm$ 4.5M, df2= $\pm$ 5.5M; –20dBm/tone;<br>LNA LOW gain; G <sub>ABB</sub> = 20dB |

| Input IP2 (@15M inband            | iIP <sub>2,IB15</sub>  | 40  | 50  |     | dBm  | df1= ±14.5M, df2= ±15.5M;                                                               |

| blocker offset)                   |                        |     |     |     |      | –27dBm/tone; LNA HI gain; G <sub>ABB</sub> = 26dB                                       |

| Input IP2 (@ Tx blocker offset)   | ilP <sub>2,Tx</sub>    |     |     |     |      |                                                                                         |

| (HB)                              |                        | 45  | 55  |     | dBm  | $f1=\pm(f_{Tx}-0.5M); f2=\pm(f_{Tx}+0.5M);$                                             |

| (LB)                              |                        | 45  | 55  |     | dBm  | –27dBm/tone; LNA HI gain; G <sub>ABB</sub> = 29dB                                       |

| Input-1dB compression             | IP-1dB                 | -9  | -5  |     | dBm  | LNA LOW gain; G <sub>ABB</sub> = -7dB                                                   |

REV. (1.5) Mar 20<sup>th</sup> 2011

| Parameter                                                                           | Symbol                      | Min  | Тур  | Max  | Unit | Test Conditions / Comments                                                                                      |

|-------------------------------------------------------------------------------------|-----------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------------------|

| Input-1dB gain compression (ACS2)                                                   | IP-1dB,ACS2                 | -12  | -8   |      | dBm  | Blocker level that results in 1dB gain<br>reduction at desired signal; LNA LOW<br>gain; G <sub>ABB</sub> = 20dB |

| Input-1dB gain compression<br>(Inband Blocker @ 15M offset)                         | IP <sub>-1dB,IB15</sub>     | -19  | -15  |      | dBm  | Blocker level that results in 1dB gain<br>reduction at desired signal; LNA HI<br>gain; G <sub>ABB</sub> = 26dB  |

| Input-1dB gain compression<br>(GMSK blocker @ 2.7M offset;<br>band II/III/V/VIII/X) | IP <sub>-1dB,</sub><br>GMSK | -38  | -34  |      | dBm  | Blocker level that results in 1dB gain reduction at desired signal; LNA MED gain; G <sub>ABB</sub> = 29dB       |

| Input-1dB gain compression<br>(Tx blocker)                                          | IP-1dB, TX                  | -19  | -15  |      | dBm  | Blocker level that results in 1dB gain reduction at desired signal; LNA HI gain; G <sub>ABB</sub> = 29dB        |

| Uncal. I/Q phase mismatch                                                           | $\Delta \Phi_{IQ_{RX}}$     |      |      | ±2   | deg  | Un-calibrated spec.; LNA MED gain //                                                                            |

| Uncal. I/Q amplitude mismatch                                                       | $\Delta A_{IQ_{RX}}$        |      |      | ±0.5 | dB   | G <sub>ABB</sub> = 17dB; BB tone freq. = 200kHz                                                                 |

| Quadrature phase mismatch                                                           | $\Delta \Phi_{IQ_{RX}}$     |      |      | ±0.5 | deg  | Calibrated spec. using TTG RF tone //                                                                           |

| Quadrature amplitude mismatch                                                       | $\Delta A_{IQ_{RX}}$        | N C  |      | ±0.1 | dB   | LNA MED gain; G <sub>ABB</sub> = 17dB; BB tone<br>freq. = 200kHz                                                |

| <b>3G Receiver Analog Basebanc</b>                                                  | l section                   |      |      |      |      |                                                                                                                 |

| DC Common Mode Level                                                                | V <sub>RX_DCCM</sub>        | 1.08 | 1.2  | 1.32 | V    |                                                                                                                 |

| Output-1dB Compression                                                              | OP <sub>-1dB</sub>          | 1.7  | 1.9  | 2.1  | Vpd  | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                            |

| Gain step variation                                                                 | $\Delta G_{RX}$ 3dB         | -0.2 |      | 0.2  | dB   | 3dB gain step from any gain setting                                                                             |

|                                                                                     | $\Delta G_{RX_XdB}$         | -0.5 |      | 0.5  | dB   | Any gain change                                                                                                 |

| Baseband filter                                                                     |                             |      |      |      |      |                                                                                                                 |

| 3dB corner frequency                                                                | A <sub>-3dB</sub>           | 2.11 | 2.23 |      | MHz  | After corner frequency calibration                                                                              |

| Stopband attenuation                                                                |                             |      | _    |      |      |                                                                                                                 |

| 2.7/2.8M offset (GMSK)                                                              | A <sub>GSM2.7M</sub>        | 6    | 8    |      | dB   | Integrated over 200kHz BW at 2.7/2.8M                                                                           |

| 3.5/3.6M offset (CW)                                                                | A <sub>3.5M</sub>           | 14   | 17   |      | dB   | At 3.5/3.6M                                                                                                     |

| 5.9/6.0M offset (GMSK)                                                              | A <sub>GSM5.9M</sub>        | 30   | 33   |      | dB   | Integrated over 200kHz BW at 5.9/6.0M                                                                           |

| 5M offset (WCDMA)                                                                   | A <sub>W5M</sub>            | 18   | 22   |      | dB   | Integrated over 3.84M BW at 5M                                                                                  |

| 10M offset (WCDMA)                                                                  | A <sub>W10M</sub>           | 45   | 49   |      | dB   | Integrated over 3.84M BW at 10M                                                                                 |

| 15M offset (WCDMA)                                                                  | A <sub>W15M</sub>           | 65   | 69   |      | dB   | Integrated over 3.84M BW at 15M                                                                                 |

| Parameter                         | Symbol              | Min | Тур | Max | Unit | Test Conditions / Comments                                                                                     |

|-----------------------------------|---------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------|

| GGE Receiver                      |                     |     |     |     |      |                                                                                                                |

| Input Return Loss                 | S <sub>11</sub>     |     | -10 |     | dB   | Ref. plane (Z <sub>0</sub> ) at matching components                                                            |

| Voltage gain: Max. (HB)           | G <sub>V,max</sub>  | 67  | 70  | 72  | dB   | LNA HI gain/ G <sub>ABB</sub> = 32dB                                                                           |

| Max (LB)                          |                     | 66  | 69  | 71  | dB   |                                                                                                                |

| Voltage gain: Mid.                | G <sub>V,mid</sub>  | 38  | 41  | 43  | dB   | LNA MED gain/ G <sub>ABB</sub> = 14dB                                                                          |

| Voltage gain: Min.                | G <sub>V,min</sub>  | 3   | 6   | 9   | dB   | LNA LOW gain/ G <sub>ABB</sub> = -7dB                                                                          |

| DSB Noise Figure (HB)             | NFHI                |     | 2.3 | 3.4 | dB   | All frequency channels; LNA HI gain;                                                                           |

| (LB)                              |                     |     | 2.5 | 3.6 | dB   | G <sub>ABB</sub> = 29dB                                                                                        |

| Input IP3 (HB)                    | iIP <sub>3,IM</sub> | -5  | -1  |     | dBm  | df1= ±0.81MHz, df2= ±1.6MHz;                                                                                   |

| (LB)                              |                     | -3  | 1   |     |      | –41dBm/tone; LNA HI gain; G <sub>ABB</sub> = 29dB                                                              |

| Input IP2 (AM detection) (HB)     | ilP <sub>2,AM</sub> | 45  | 55  |     | dBm  | df1= ±5.98MHz, df2= ±6.02MHz;                                                                                  |

| (LB)                              |                     | 50  | 60  |     | dBm  | –27dBm/tone; LNA HI gain; G <sub>ABB</sub> = 29dB                                                              |

| Input-1dB compression             | IP <sub>-1dB</sub>  | -9  | -5  |     | dBm  | LNA LOW gain; G <sub>ABB</sub> = -7dB                                                                          |

| Input-1dB gain compression (ACI1) | IP-1dB,ACI1         | -31 | -27 |     | dBm  | Blocker level that results in 1dB gain<br>reduction at desired signal; LNA HI<br>gain; G <sub>ABB</sub> = 14dB |

| Parameter                                              | Symbol                             | Min  | Тур | Max  | Unit | <b>Test Conditions / Comments</b>                                                                        |

|--------------------------------------------------------|------------------------------------|------|-----|------|------|----------------------------------------------------------------------------------------------------------|

| Input-1dB gain compression<br>(ACI2)                   | IP <sub>-1dB,ACI2</sub>            | -32  | -28 |      | dBm  | Blocker level that results in 1dB gain reduction at desired signal; LNA HI gain; G <sub>ABB</sub> = 20dB |

| Input-1dB gain compression<br>(CW Blocker 0.8M offset) | IP <sub>-1dB,0.8M</sub>            | -30  | -26 |      | dBm  | Blocker level that results in 1dB gain reduction at desired signal; LNA HI gain; G <sub>ABB</sub> = 29dB |

| Input-1dB gain compression<br>(CW Blocker 3M offset)   | IP <sub>-1dB,3M</sub>              | -21  | -17 |      | dBm  | Blocker level that results in 1dB gain reduction at desired signal; LNA HI gain; G <sub>ABB</sub> = 29dB |

| 2.Rx Suppression                                       | H <sub>OOB_2RX</sub>               | 37   | 55  |      | dB   | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                     |

| 3-Rx Suppression (HB)                                  | H <sub>OOB_3RX</sub>               | 20   | 25  |      | dB   | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                     |

| (LB)                                                   |                                    | 18   | 23  |      | dB   | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                     |

| 5.Rx Suppression (LB)                                  | H <sub>OOB_5RX</sub>               | 26   | 35  |      | dB   | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                     |

| Uncal. I/Q phase mismatch                              | $\Delta \Phi_{IQ RX}$              |      |     | ±2   | deg  | Un-calibrated spec.; LNA MED gain//                                                                      |

| Uncal. I/Q amplitude mismatch                          | $\Delta A_{IQ_{RX}}$               |      |     | ±0.5 | dB   | G <sub>ABB</sub> = 17dB; BB tone freq. = 200kHz                                                          |

| Quadrature phase mismatch                              | $\Delta \Phi_{IQ RX}$              |      |     | ±0.5 | deg  | Calibrated spec. using TTG RF tone //                                                                    |

| Quadrature amplitude mismatch                          | $\Delta A_{IQ_{RX}}$               |      |     | ±0.1 | dB   | LNA MED gain; G <sub>ABB</sub> = 17dB; BB tone freq. = 200kHz                                            |

| GGE Receiver Analog Baseba                             | nd section                         |      |     |      |      |                                                                                                          |

| DC Common Mode Level                                   | V <sub>RX_DCCM</sub>               | 1.08 | 1.2 | 1.32 | V    |                                                                                                          |

| Output-1dB Compression                                 | OP-1dB                             | 1.7  | 1.9 | 2.1  | Vpd  | LNA HI gain; G <sub>ABB</sub> = 29dB                                                                     |

| Gain step variation                                    | $\Delta G_{RX 3dB}$                | -0.2 |     | 0.2  | dB   | 3dB gain step from any gain setting                                                                      |

|                                                        | $\Delta G_{\text{RX}\_\text{XdB}}$ | -0.5 |     | 0.5  | dB   | Any gain change                                                                                          |

| Baseband filter                                        |                                    |      |     |      |      |                                                                                                          |

| 3dB corner frequency                                   | A-3dB                              | 148  | 156 |      | kHz  | After calibration                                                                                        |

| Stopband attenuation                                   |                                    |      |     |      |      |                                                                                                          |

| ACI2                                                   | A <sub>ACI1</sub>                  | 22   | 26  |      | dB   | 400kHz offset (BW=200kHz)                                                                                |

| ACI3                                                   | A <sub>ACI2</sub>                  | 35   | 39  |      | dB   | 600kHz offset (BW=200kHz)                                                                                |

| 800kHz offset (CW)                                     | A <sub>0.8M</sub>                  | 44   | 49  |      | dB   | At 800kHz                                                                                                |

| 1.6MHz offset (CW)                                     | A <sub>1.6M</sub>                  | 65   | 75  |      | dB   | At 1.6M                                                                                                  |

| 3.0MHz offset (CW)                                     | А <sub>3.0М</sub>                  |      | >90 |      | dB   | At 3.0M                                                                                                  |

Konka WCX

#### TRANSMITTER SYSTEM

All transmitter characteristics are applicable for all TX frequency bands when operated under the recommended operating conditions and transmitter pin configuration#1, unless stated otherwise. Measured with 50ohm load at driver output; Input at BB is DC coupled (High Zin). In 3G and GGE modes, I/Q inputs are driven each with 185mVrms DIFF signal (WCDMA UL 12.2kbps reference channel) and 180mVrms (8PSK), respectively. The reference oscillator used with the on-chip PLL is 26MHz.

Typical specifications are for mid-band channel frequency, and recommended operating conditions. Min/Max specifications are for Extreme operating voltage and temperature conditions, unless otherwise stated.

| Parameter                    | Symbol           | Min | Тур  | Max  | Unit | Test Conditions / Comments                                 |

|------------------------------|------------------|-----|------|------|------|------------------------------------------------------------|

| BG Transmitter Output        |                  |     |      |      |      |                                                            |

| Output Return Loss           | S <sub>22</sub>  |     | -12  | -10  | dB   | 50Ω load                                                   |

| Max Output Power             |                  |     |      | 1    |      |                                                            |

| All bands, except Band II    | P <sub>max</sub> | 2.5 |      |      | dBm  | Worst case ACLR, EVM, noise emissions                      |

| Band II only                 | P <sub>max</sub> | 4.5 |      | 12   | dBm  | and spurious emissions specs. are met                      |

| Min Output Power             |                  |     |      |      |      |                                                            |

| (HB)                         | P <sub>min</sub> |     |      | -82  | dBm  |                                                            |

| (LB)                         | P <sub>min</sub> |     |      | -81  | dBm  |                                                            |

| RF output Frequency response | ΔP               |     | ±0.2 | ±0.7 | dB   | Pout = min.P <sub>max</sub>                                |

| ACLR1                        |                  |     |      |      |      | ±5MHz offset;                                              |

| (HB)                         | ACLR1            |     | -48  | -43  | dBc  | Pout = min.P <sub>max</sub>                                |

| (LB)                         | ACLR1            |     | -50  | -41  | dBc  | Pout = min.P <sub>max</sub>                                |

| All bands                    | ACLR1            |     | -52  | -48  | dBc  | Pout = min.P <sub>max</sub> – 11dB                         |

| ACLR2                        | ACLR2            |     | -71  | -65  | dBc  | ±10MHz offset; Pout = = min.P <sub>max</sub>               |

| EVM                          |                  |     |      |      |      | Measured over 1 slot/2560chips, after Tx                   |

|                              |                  |     |      |      |      | I/Q imbalance and LO leakage calibration                   |

| (HB)                         | EVM              |     | 2.0  | 3.0  | %    | Pout= min.P <sub>max</sub>                                 |

|                              |                  |     | 2.0  | 3.0  | %    | Pout= min.P <sub>max</sub> -11dB                           |

| (LB)                         | EVM              |     | 1.5  | 2.3  | %    | Pout= min.P <sub>max</sub>                                 |

|                              |                  |     | 1.5  | 2.3  | %    | Pout= min.P <sub>max</sub> -11dB                           |

| Spectrum Emission Mask       | SEM              |     |      |      |      | Pout= min.P <sub>max</sub> ; 3.5M offset in 30kHz BW       |

| (HB)                         |                  |     | -60  | -56  | dBc  | Note A                                                     |

| (LB)                         |                  |     | -65  | -61  | dBc  | Note A                                                     |

| Carrier Suppression          |                  |     |      | -20  | dBc  | Pout $\geq$ min.P <sub>max</sub> -44dB; before calibration |

|                              |                  |     | -48  | -35  | dBc  | Pout= min.P <sub>max</sub> ; after calibration             |

|                              |                  |     | -39  | -31  | dBc  | Pout= min.P <sub>max</sub> -44dB; after calibration        |

| Sideband Suppression         |                  |     | -45  | -38  | dBc  | Pout $\geq$ min.P <sub>max</sub> -44dB; after calibration  |

| Harmonic Emissions in 1 MHz  |                  |     |      |      |      |                                                            |

| 2 <sup>nd</sup> harmonic     |                  |     |      | -25  | dBc  | Pout= min.P <sub>max</sub>                                 |

| 3 <sup>rd</sup> harmonic     |                  |     |      | -15  | dBc  | Pout= min.P <sub>max</sub>                                 |

| 4 <sup>th</sup> harmonic     |                  |     |      | -25  | dBc  | Pout= min.P <sub>max</sub>                                 |

| Ref. clock harmonics         |                  |     | -90  | -70  | dBc  | 52MHz; 104MHz; 208MHz                                      |

Note A: NTC1: Nominal Test Conditions (Low, Mid, High frequency channels; +15C ... +35C ambient temperature; Vbat = 3.6 - 4.0V)

| Parameter                  | Symbol | Min | Тур    | Max    | Unit   | Test Conditions / Comments                                              |

|----------------------------|--------|-----|--------|--------|--------|-------------------------------------------------------------------------|

| Noise Emissions            |        |     |        |        |        |                                                                         |

| Band I, 12.5MHz offset     |        |     | -145   | -140   | dBc/Hz | Pout= min.P <sub>max</sub> ; Note A                                     |

| Band I, 40MHz offset       |        |     | -159   | -157   | dBc/Hz | Pout= min.P <sub>max</sub> ; measured at 1880M with fTx = 1920M; Note A |

| Band I, noise in Rx        |        |     | -162.5 | -159.5 | dBc/Hz | Pout= min.P <sub>max</sub> ; measured at 135M offset                    |

|                            |        |     |        | -153.5 | dBc/Hz | Pout = -9dBm; measured at 135M offset                                   |

| Band II, noise in Rx       |        |     | -162   | -160   | dBc/Hz | Pout= min.P <sub>max</sub> ; measured at 80M offset                     |

|                            |        |     |        | -156   | dBc/Hz | Pout = -6dBm; measured at 80M offset                                    |

| Band V/VI, noise in Rx     |        |     | -162   | -160   | dBc/Hz | Pout= min.P <sub>max</sub> ; measured at 45M offset                     |

|                            |        |     |        | -156   | dBc/Hz | Pout = -8.0dBm; measured at 45M offset                                  |

| Band VIII, noise in Rx     |        |     | -162   | -160   | dBc/Hz | Pout= min.P <sub>max</sub> ; measured at 45M offset                     |

|                            |        |     |        | -156   | dBc/Hz | Pout = -6.5dBm; measured at 45M offset                                  |

| 3G Tx baseband section     |        |     |        |        |        |                                                                         |

| Baseband Filter            |        |     |        |        |        |                                                                         |

| Selectivity, 10MHz offset  |        | 10  | 20     |        | dB     | After frequency corner calibration                                      |

| Selectivity, 40MHz offset  |        |     | 55     |        | dB     | After frequency corner calibration                                      |

| 3G TX Gain Control         |        |     |        |        |        |                                                                         |

| Gain control resolution    |        |     | 1/32   |        | dB     | Average of LSB steps                                                    |

| Gain Control Step Accuracy |        | 0.7 | 1.0    | 1.3    | dB     | Any 1dB step                                                            |

|                            |        | 8.5 | 10     | 11.5   | dB     | Any 10dB step                                                           |

| Table 13                    |                      |      |     |     |      |                                   |

|-----------------------------|----------------------|------|-----|-----|------|-----------------------------------|

| Parameter                   | Symbol               | Min  | Тур | Max | Unit | Test Conditions / Comments        |

| GGE Transmitter Output      |                      |      |     |     |      |                                   |

| Output Return Loss          | S <sub>22</sub>      |      | -12 | -10 | dB   | 50 $\Omega$ load                  |

| Max Output Power (GMSK)     |                      |      |     |     |      |                                   |

| 2G output, Mode1            | P <sub>max</sub>     | 1    | 3   | 5   | dBm  | GMSK Modulation, using DFM        |

| 2G output, Mode2, LB only   | P <sub>max</sub>     | 4    | 6   | 8   | dBm  | GMSK Modulation, using DFM        |

| MM output                   | P <sub>max</sub>     | 8    | 10  | 12  | dBm  | GMSK Modulation, using DFM        |

| Max Output Power (8PSK)     |                      |      |     |     |      |                                   |

| 2G output, LB               | P <sub>max</sub>     | 0.5  |     |     | dBm  | Worst case ORFS, EVM, noise and   |

| 2G output, HB               | P <sub>max</sub>     | -2.5 |     |     | dBm  | spurious emissions specs. are met |

| MM output, LB               | P <sub>max</sub>     | 4.5  |     |     | dBm  |                                   |

| MM output, HB               | P <sub>max</sub>     | 3.5  |     |     | dBm  |                                   |

| Minimum Output Power (8PSK) |                      |      |     |     |      |                                   |

| 2G output, LB               | P <sub>min</sub>     |      |     | -33 | dBm  |                                   |

| 2G output, HB               | P <sub>min</sub>     |      |     | -38 | dBm  |                                   |

| MM output, LB               | P <sub>min</sub>     |      |     | -27 | dBm  |                                   |

| MM output, HB               | P <sub>min</sub>     |      |     | -32 | dBm  |                                   |

| ORFS (GMSK)                 |                      |      |     |     |      |                                   |

| 200kHz                      | ORFS <sub>200k</sub> |      | -36 | -33 | dB   | Pout= min.Pmax; BW=30kHz          |

| 400kHz                      | ORFS <sub>400k</sub> |      | -66 | -63 | dB   | Pout= min.Pmax; BW=30kHz          |

| ORFS (8PSK)                 |                      |      |     |     |      |                                   |

| 200kHz                      | ORFS <sub>200k</sub> |      | -40 | -36 | dB   | Pout= min.Pmax; BW=30kHz          |

| 400kHz                      | ORFS <sub>400k</sub> |      | -65 | -62 | dB   | Pout= min.Pmax; BW=30kHz          |

|                                                          | 0. mah al          |     | <b>T</b> |        | 11      |                                            |

|----------------------------------------------------------|--------------------|-----|----------|--------|---------|--------------------------------------------|

| Parameter                                                | Symbol             | Min | Тур      | Max    | Unit    | Test Conditions / Comments                 |

| Modulation accuracy (GMSK)                               |                    |     |          |        |         |                                            |

| RMS phase error, LB                                      | $\Phi_{RMS}$       |     | 1.2      | 3.0    | deg     | Pout= min.Pmax                             |

| RMS phase error, HB                                      |                    |     | 1.3      | 3.0    | deg     | Pout= min.Pmax                             |

| PEAK phase error, LB                                     | $\Phi_{Peak}$      |     | 3.0      | 6.0    | deg     | Pout= min.Pmax                             |

| PEAK phase error, HB                                     |                    |     | 4.0      | 8.0    | deg     | Pout= min.Pmax                             |

| Modulation accuracy (8PSK)                               |                    |     |          |        |         |                                            |

| RMS EVM, LB                                              | EVM <sub>RMS</sub> |     | 2.0      | 3.0    | %       | Pout= min.Pmax                             |

| RMS EVM, HB                                              |                    |     | 2.5      | 3.8    | %       | Pout= min.Pmax                             |

| Peak EVM, LB                                             | $EVM_{Pk}$         |     | 6        | 10     | %       | Pout= min.Pmax                             |

| Peak EVM, HB                                             |                    |     | 8        | 12     | %       | Pout= min.Pmax                             |

| Origin offset suppression                                | OOS                |     |          | -20    | dB      | 8PSK; Pout $\geq$ Pmin; before calibration |

|                                                          | OOS                |     | -40      | -35    | dB      | 8PSK; Pout = min.Pmax; after calibration   |

|                                                          | OOS                |     | -39      | -31    | dB      | 8PSK; Pout = Pmin; after calibration       |

| Sideband Suppression                                     |                    |     | -45      | -38    | dBc     | Pout $\geq$ Pmin; after calibration        |

| Tx Noise Emissions (GMSK)                                |                    |     |          | N O    |         |                                            |

| 20MHz offset, LB                                         |                    |     | -165.8   | -163   | dBc/Hz  | Pout= min.Pmax; Note A                     |

| 20MHz offset, HB                                         |                    |     | -159     | -156   |         | Pout= min.Pmax; Note A                     |

| 32MHz offset, LB                                         |                    |     | -166.5   | -165   |         | Pout= min.Pmax; Note R                     |

| 32MHz offset, HB                                         |                    |     | -162     | -159   |         | Pout= min.Pmax; Note B                     |

| Tx Noise Emissions <sup>1</sup> (8PSK)                   |                    |     | 102      | 100    | 000/112 | 2G Output                                  |

| 20MHz offset, LB, Pout <sup>1</sup>                      |                    |     | -159     | -157   | dBc/Uz  | Pout = -4dBm; Note A                       |

| Pout <sup>2</sup>                                        |                    |     | -159     |        |         | Pout $\leq -6.5$ dBm                       |

| 20MHz offset, HB, Pout <sup>1</sup>                      |                    |     | -154     | -105.5 |         | Pout = -7dBm; Note A                       |

| 2010112 Olisel, HB, Poul<br>Pout <sup>2</sup>            |                    |     | -154     |        |         | Pout $\leq$ -9.5dBm                        |

|                                                          |                    |     | 160 E    |        |         |                                            |

| 32MHz offset, LB, Pout <sup>1</sup><br>Pout <sup>2</sup> |                    |     | -160.5   | -158   |         | Pout = -4dBm; Note B                       |

|                                                          |                    |     | 155 5    |        |         | Pout ≤ -6.5dBm                             |

| 32MHz offset, HB, Pout <sup>1</sup><br>Pout <sup>2</sup> |                    |     | -155.5   | -153   |         | Pout = -7dBm; Note B<br>Pout ≤ -9.5dBm     |

|                                                          |                    |     |          | -102.5 | иыш/п/  |                                            |

| Tx Noise Emissions <sup>2</sup> (8PSK)                   |                    |     | 100      | 450 5  |         | MM Output                                  |

| 20MHz offset, LB, Pout <sup>1</sup>                      |                    |     | -162     |        |         | Pout = 0dBm; Note A                        |

| Pout <sup>2</sup>                                        |                    |     |          |        |         | Pout ≤ -2.5dBm                             |

| 20MHz offset, HB, Pout <sup>1</sup>                      |                    |     | -157     |        |         | Pout = -1dBm; Note A                       |

| Pout <sup>2</sup>                                        |                    |     |          |        |         | Pout ≤ -3.5dBm                             |

| 32MHz offset, LB, Pout <sup>1</sup>                      |                    |     | -162     |        |         | Pout = 0dBm; Note B                        |

| Pout <sup>2</sup>                                        |                    |     |          |        |         | Pout ≤ -2.5dBm                             |

| 32MHz offset, HB, Pout <sup>1</sup>                      |                    |     | -159     |        |         | Pout = -1dBm; Note B                       |

| Pout <sup>2</sup>                                        |                    |     |          | -159   | dBm/Hz  | Pout ≤ -3.5dBm                             |

| Tx Spurious Emissions                                    |                    |     |          |        |         |                                            |

| 2 <sup>nd</sup> harmonic                                 |                    |     |          | -25    | dBc     | Pout= min.Pmax                             |

| 3 <sup>rd</sup> harmonic                                 |                    |     |          | -13    | dBc     | Pout= min.Pmax                             |

| 4 <sup>th</sup> harmonic                                 |                    |     |          | -25    | dBc     | Pout= min.Pmax                             |

| 8PSK Tx baseband section                                 |                    |     |          |        |         |                                            |

| Baseband Filter                                          |                    |     |          | Vor    |         |                                            |

| Selectivity, 20MHz offset                                |                    |     | 26       |        | dB      |                                            |

| -,,                                                      | I                  |     | 1        | I      | 1       | I I                                        |

<u>Note A</u>: NTC1: Nominal Test Conditions (Low, Mid, High frequency channels;  $+15C \dots +35C$  ambient temperature; Vbat = 3.6 - 4.0V) <u>Note B</u>: TTC: Typical Test Conditions (Mid frequency channel; +25C ambient temperature; Vbat = 3.7V)

#### TRANSMIT POWER CONTROL

| Table 14 |  |

|----------|--|

|----------|--|

| Parameter             | Symbol               | Min  | Тур | Max  | Unit              | Test Conditions / Comments       |

|-----------------------|----------------------|------|-----|------|-------------------|----------------------------------|

| Power Detector        |                      |      |     |      |                   |                                  |

| RF Input Frequency    | F <sub>det</sub>     | 824  |     | 1980 | MHz               |                                  |

| Input Return Loss     | S <sub>11</sub>      |      | -12 | -10  | dB                | Ref. impedance 50 $\Omega$       |

| Maximum Input Signal  | P <sub>det,max</sub> |      |     | 0    | dBm               | 1dB excursion from nominal slope |

| Minimum Input Signal  | P <sub>det,min</sub> | -50  |     |      | dBm               | 1dB excursion from nominal slope |

| Measurement Accuracy  |                      | -0.3 |     | 0.3  | dB                | 3 –sigma; WCDMA/ 8PSK only       |

| Temperature Stability |                      | -15  | 2   | 15   | mdB/              | Averaged over -40 to 100°C range |

| Frequency response    |                      |      |     | ±10  | °C<br>mdB/<br>MHz | Averaged over any supported band |

| Measurement time      |                      |      | 14  | 0    | μS                | With above Specifications        |

## SYNTHESIZERS AND REFERENCES

| Parameter                          | Symbol | Min | Тур   | Max  | Unit   | Test Conditions / Comments                                                                            |

|------------------------------------|--------|-----|-------|------|--------|-------------------------------------------------------------------------------------------------------|

| Receiver Synthesizer               |        |     |       |      |        |                                                                                                       |

| Channel resolution                 |        |     | 25    |      | kHz    |                                                                                                       |

| Lock Time                          |        |     | 120   | 150  | μS     | Phase within 10° of final lock                                                                        |

|                                    |        |     |       |      | •      | conditions; frequency error removed                                                                   |

| Transmitter Synthesizer            |        |     |       |      |        |                                                                                                       |

| Channel resolution                 |        |     | 3     |      | Hz     | 3G / GGE mode                                                                                         |

| Lock Time                          |        |     | 120   | 150  | μS     | Phase within 10°. of final lock conditions; frequency error removed                                   |

| GMSK Lock Time                     |        |     |       | 200  | μS     | In DFM mode (inc. loop gain<br>calibration) after register CW1 is<br>written; frequency error removed |

| Reference Input (XO1)              |        |     |       |      |        |                                                                                                       |

| Frequency                          |        |     | 26    |      | MHz    |                                                                                                       |

| Reference Outputs<br>(REFCLK1,2,3) |        |     |       |      |        |                                                                                                       |

| Frequency                          |        |     | 26    |      | MHz    | REFCLK pin                                                                                            |

| Output Swing                       |        | 0.7 |       | 1.2  | Vpp    | Square wave (3kΩ    20 pF Load)                                                                       |

| Rise / Fall Time                   |        | 2.5 |       | 9    | ns     | 10% - 90% of signal swing ( $3k\Omega \parallel 20$ pF Load)                                          |

| Duty Cycle                         |        | 40  |       | 60   | %      | 50% Input duty cycle                                                                                  |

| Harmonic rejection                 |        |     | <-25  | -22  | dBc    | 2 <sup>nd</sup> harmonic                                                                              |

| -                                  |        |     |       | -10  | dBc    | 3 <sup>rd</sup> harmonic                                                                              |

|                                    |        |     |       | -30  | dBc    | 4 <sup>th</sup> harmonic                                                                              |

| SSB phase noise                    |        |     | <-138 | -131 | dBc/Hz | 1kHz offset                                                                                           |

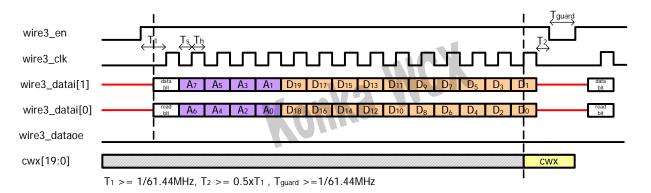

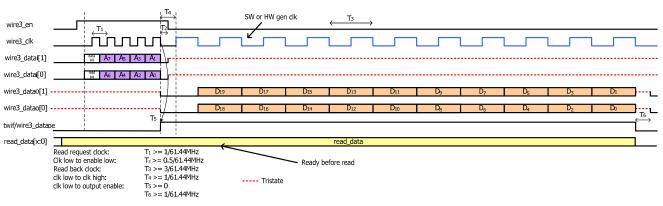

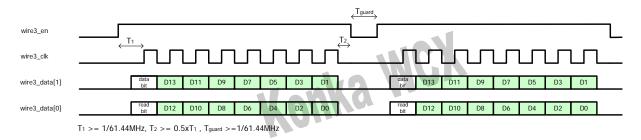

|                                    |        |     | <-147 | -141 | dBc/Hz | 10kHz offset                                                                                          |