# MT6253 GSM/GPRS Baseband Process Data Sheet

Version: 0.99 SP1

Release date: 2009-07-30

### © 2009 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Specifications are subject to change without notice.

# **Revision History**

| Revision | Date         | Comments              |

|----------|--------------|-----------------------|

| 0.99     | May 22, 2009 | Initial draft version |

| 0.99 SP1 | Jul 30, 2009 | Special patch version |

# **TABLE OF CONTENTS**

| Rev      | vision History                     | 2   |

|----------|------------------------------------|-----|

| Pre      | eface                              | 5   |

| 1        | System Overview                    | 7   |

|          | .1 Platform Features               |     |

|          | 1.2 MODEM Features                 |     |

|          | 1.3 Multi-Media Features           |     |

|          | 1.4 General Description            |     |

|          | •                                  |     |

|          | Product Description                |     |

|          | 2.1 Pin Outs                       |     |

|          | 2.2 Top Marking Definition         |     |

|          | 2.3 DC Characteristics             |     |

| 2.       | 2.4 Pin Description                | 20  |

| <b>3</b> | Micro-Controller Unit Subsystem    |     |

| 3.       | 3.1 Processor Core                 |     |

| 3.       | 3.2 Memory Management              |     |

| 3.       | 3.3 Bus System                     |     |

| 3.       | 3.4 Direct Memory Access           |     |

| 3.       | 3.5 Code Cache controller          | 58  |

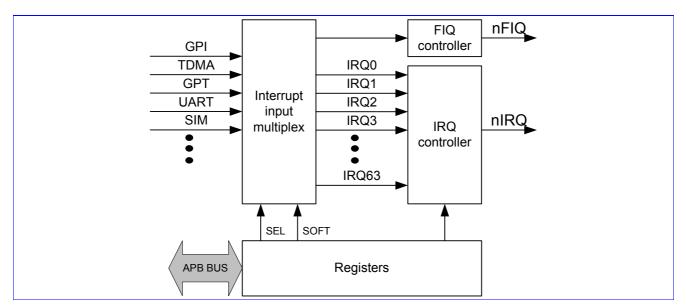

| 3.       | 3.6 Interrupt Controller           | 67  |

| 3.       | 3.7 MPU                            | 85  |

| 3.       | 3.8 Internal Memory Interface      | 94  |

| 3.       | 3.9 External Memory Interface      | 95  |

| 4        | Microcontroller Peripherals        | 111 |

|          | 4.1 Pulse-Width Modulation Outputs |     |

| 4.       | 4.2 Alerter                        | 115 |

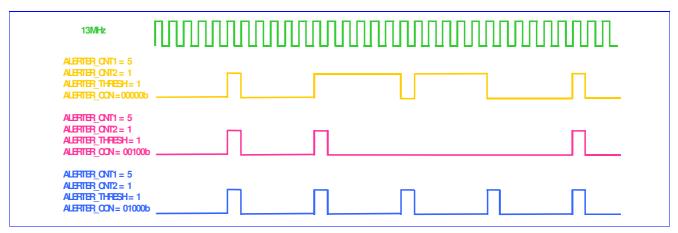

| 4.       | 4.3 SIM Interface                  | 118 |

| 4.       | 4.4 Keypad Scanner                 |     |

| 4.       | 4.5 General Purpose Inputs/Outputs |     |

| 4.       | 4.6 General Purpose Timer          |     |

| 4.       | 4.7 UART                           |     |

| 4.       | 4.8 IrDA Framer                    |     |

| 4.       | 4.9 Real Time Clock                |     |

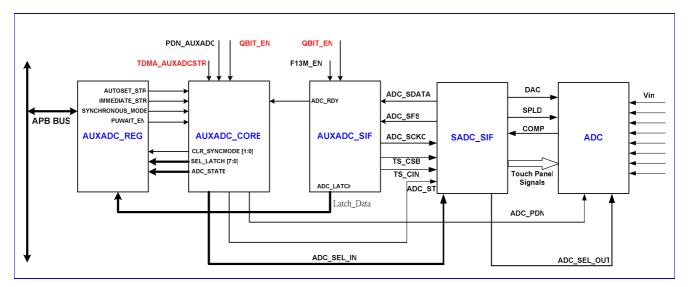

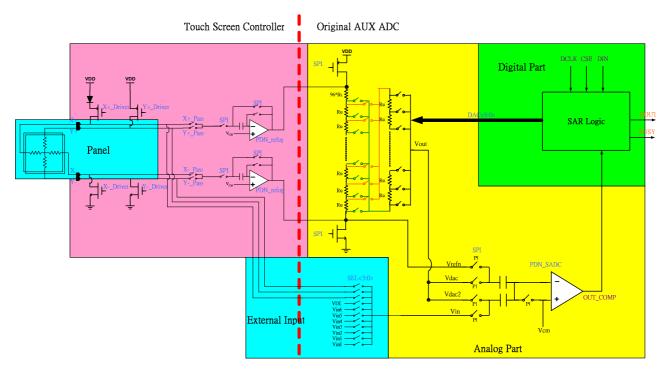

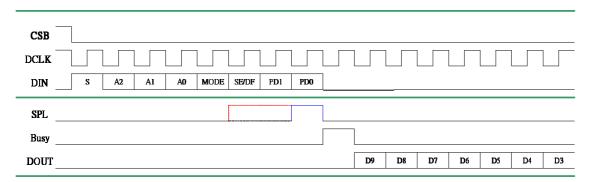

| 4.       | 4.10 Auxiliary ADC Unit            |     |

|          | 4.11 I2C / SCCB Controller         |     |

| <b>5</b> | Microcontroller Coprocessors       | 227 |

|          | 5.1 Divider                        |     |

|          | 5.2 CSD Accelerator                |     |

|          | 5.3 FCS Codec                      |     |

|          | 5.4 GPRS Cipher Unit               |     |

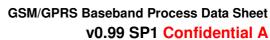

| 6        | Multi-Media Subsystem              | 240 |

| _        | 5.1 LCD Interface                  |     |

|          | 5.2 Image Resizer                  | 293 |

MediaTek Confidential

# GSM/GPRS Baseband Process Data Sheet v0.99 SP1 Confidential A

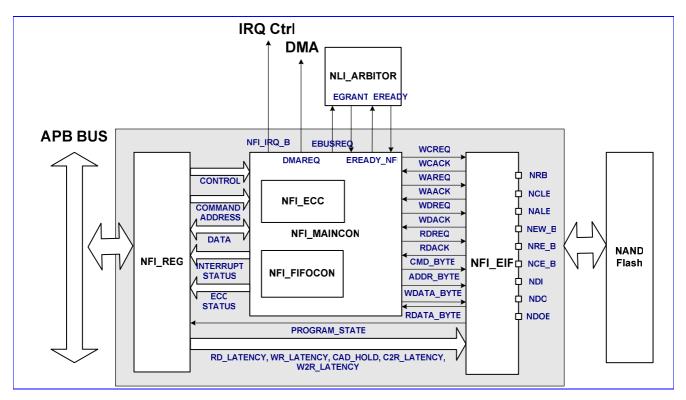

| 6.          | NAND FLASH interface                           |     |

|-------------|------------------------------------------------|-----|

| 6.          | .4 USB 2.0 High-Speed Dual-Role Controller     |     |

| 6.:         | 5.5 Memory Stick and SD Memory Card Controller | 381 |

| 6.          |                                                |     |

| <b>7</b>    | Audio Front-End                                | 422 |

| 7.          |                                                |     |

| 7.          | .2 Register Definitions                        | 425 |

| 7.          | .3 DSP Register Definitions                    | 441 |

| 7.          | .4 Programming Guide                           | 446 |

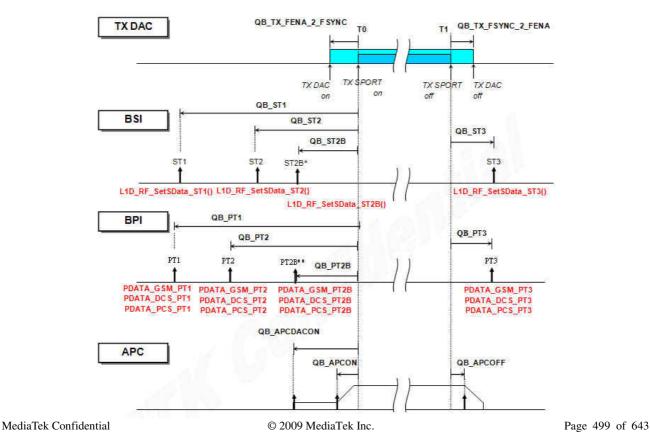

| 8 1         | Radio Interface Control                        | 448 |

| 8.          |                                                |     |

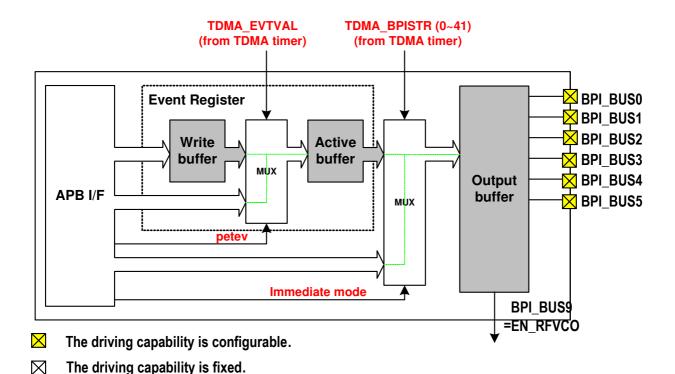

| 8.          | .2 Baseband Parallel Interface                 | 456 |

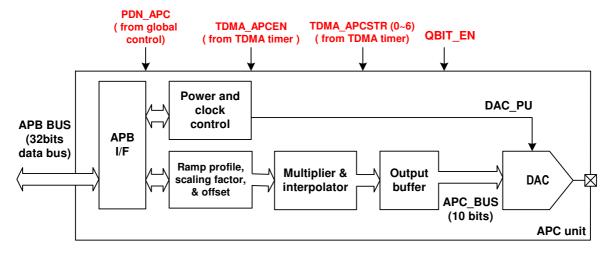

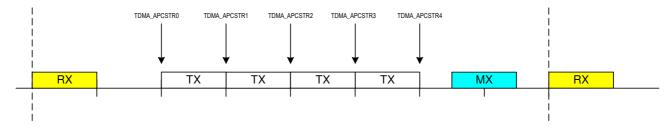

| 8.          | .3 Automatic Power Control (APC) Unit          | 461 |

| 9 ]         | Baseband Front End                             | 468 |

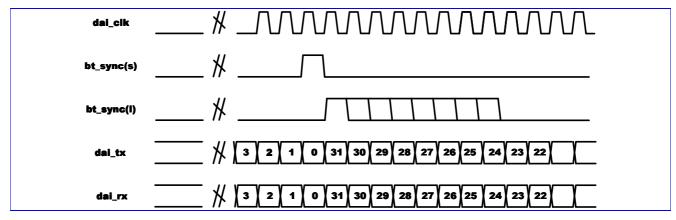

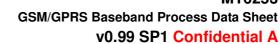

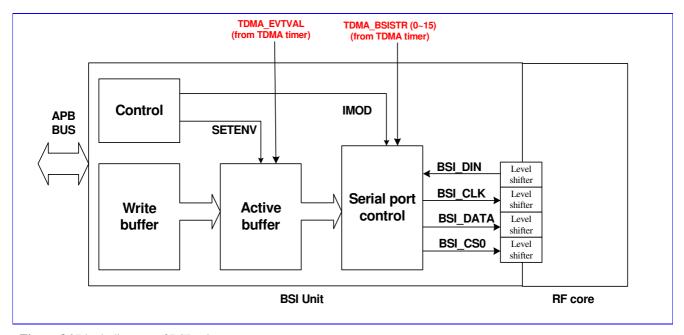

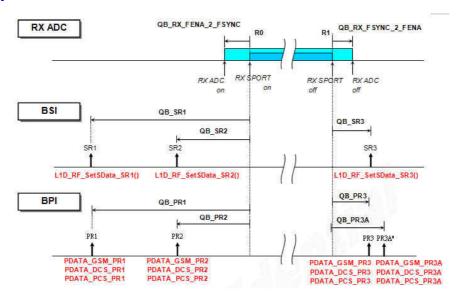

| 9.          | .1 Baseband Serial Ports                       | 469 |

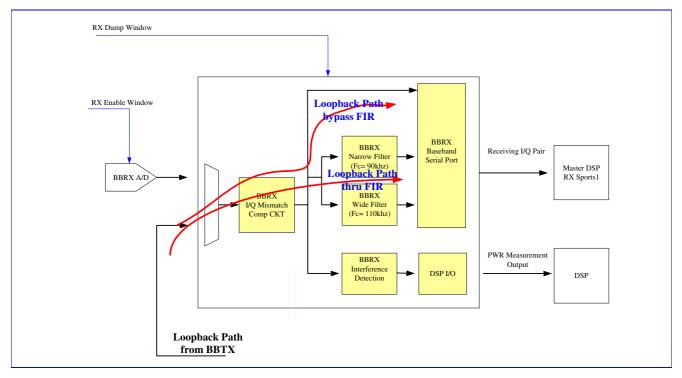

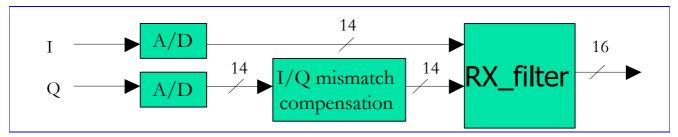

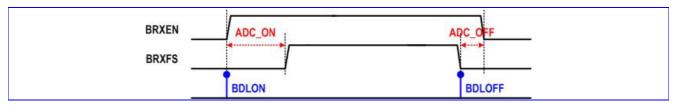

| 9.          | .2 Downlink Path (RX Path)                     | 472 |

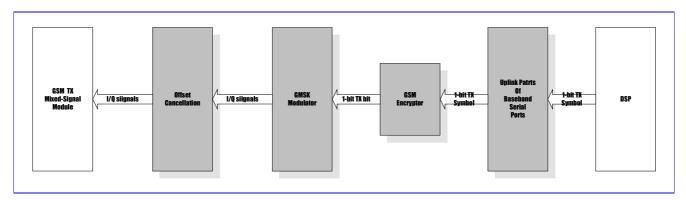

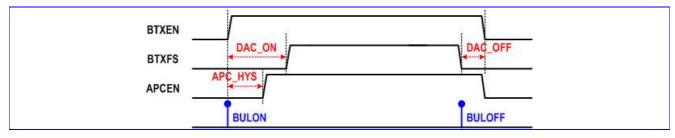

| 9.          | .3 Uplink Path (TX Path)                       |     |

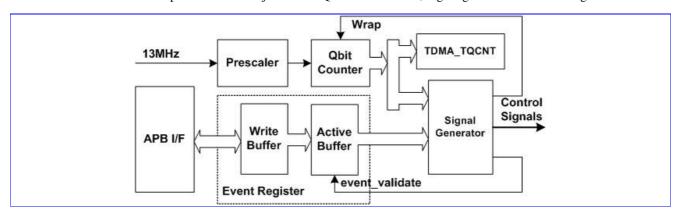

| 10          | Timing Generator                               | 487 |

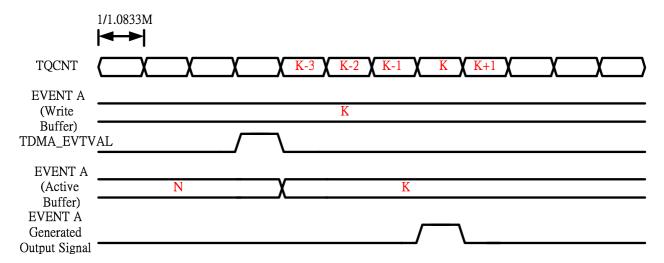

|             | 0.1 TDMA timer                                 |     |

| 11 I        | Power, Clocks and Reset                        | 501 |

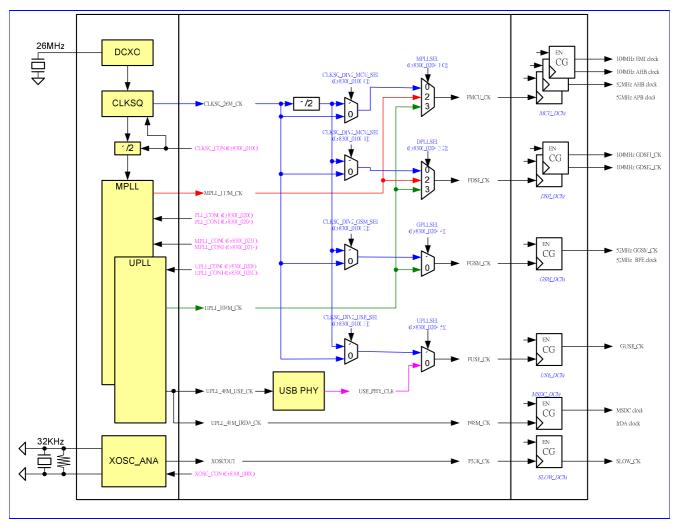

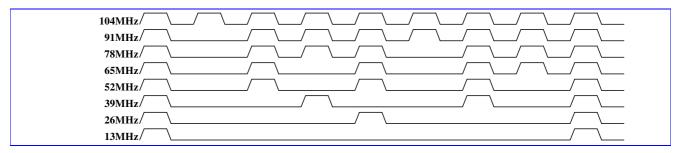

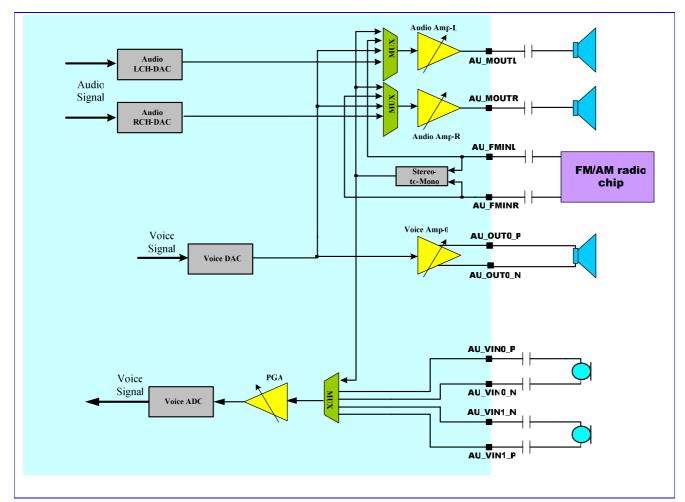

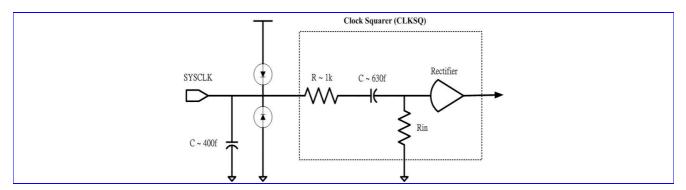

|             | 1.1 Clocks                                     |     |

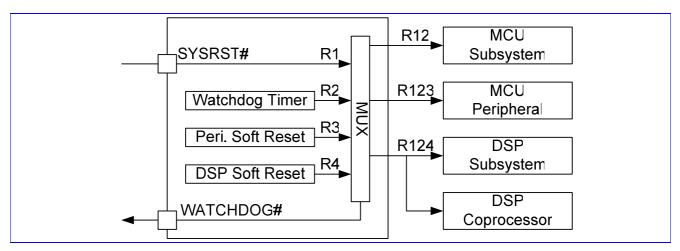

| 11          | 1.2 Reset Generation Unit (RGU)                | 514 |

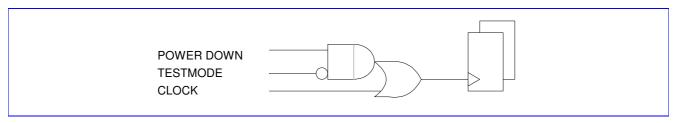

| 11          | 1.3 Software Power Down Control                | 518 |

| <b>12</b> A | Analog Front-end & Analog Blocks               | 526 |

|             | 2.1 General Description                        |     |

| 12          | 2.2 ABB Register Definitions                   | 537 |

| 12          | 2.3 PMU Registers Definition                   | 571 |

|             | 2.4. Programming Guide                         |     |

# **Preface**

## **Acronym for Register Type**

| R/W | Capable of both read and write access                                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RO  | Read only                                                                                                                                                                                              |

| RC  | Read only. After reading the register bank, each bit which is $HIGH(1)$ will be cleared to $LOW(0)$ automatically.                                                                                     |

| wo  | Write only                                                                                                                                                                                             |

| W1S | Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the corresponding bit to be set to 1. Data bits which are LOW(0) has no effect on the corresponding bit.     |

| W1C | Write only. When writing data bits to register bank, each bit which is HIGH(1) will cause the corresponding bit to be cleared to 0. Data bits which are LOW(0) has no effect on the corresponding bit. |

GSM/GPRS Baseband Process Data Sheet v0.99 SP1 Confidential A

MediaTek Confidential © 2009 MediaTek Inc. Page 6 of 643

# 1 System Overview

MT6253 is Mediatek's first monolithic GSM/GPRS handset chip solution which integrates RF, analog baseband, digital baseband as well as Power Management Unit (PMU) and can greatly reduce the component count and make smaller PCB size. Besides, MT6253 is capable of SAIC (Single Antenna Interference Cancellation) and AMR speech. Based on 32 bit ARM7EJ-S<sup>TM</sup> RISC processor, MT6253 provides an unprecedented platform for high quality modem performance.

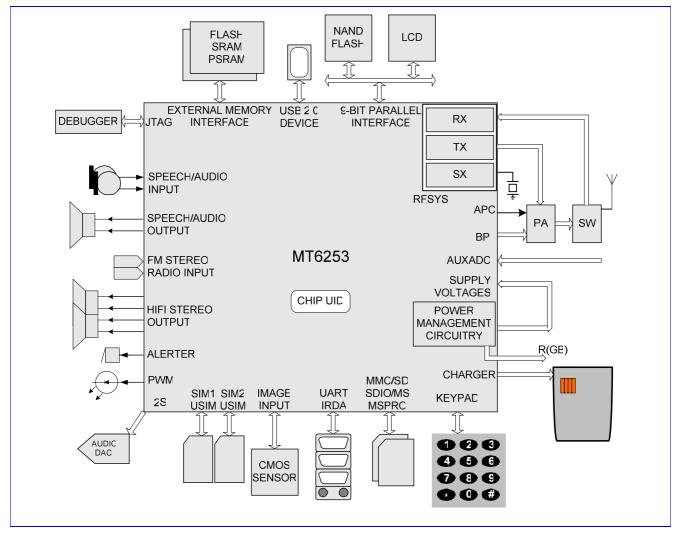

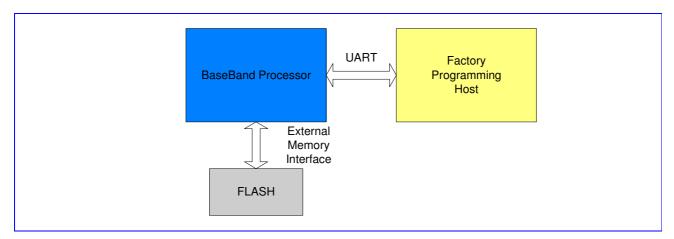

The typical application diagram is shown as **Figure 1**.

#### Platform

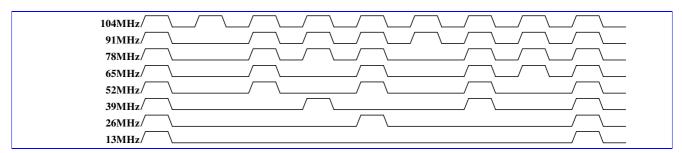

MT6253 has the ARM7EJ-S<sup>TM</sup> RISC processor running up to 104 MHz, thus providing best trade-off between system performance and power consumption.

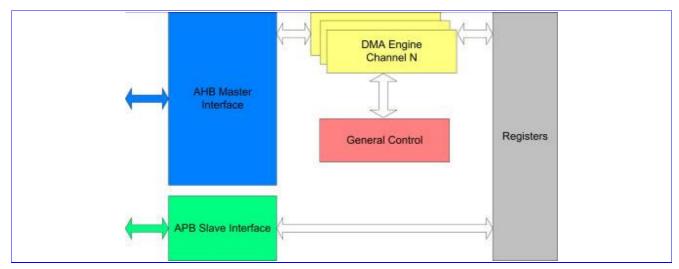

For large amount of data transfer, high performance DMA (Direct Memory Access) with hardware flow control is implemented, that which greatly enhances the data movement speed while reducing MCU processing load.

Targeted as a modem-centric platform for mobile applications, MT6253 also provides hardware security digital rights management for copyright protection. For further safeguarding, and to protect manufacturer's development investment, hardware flash content protection is also provided to prevent unauthorized porting of software load.

#### Memory

MT6253 supports up to 3 external state-of-the-art devices through its 16-bit host interface. Devices such as burst mode Flash, SRAM, and Pseudo SRAM are supported. To minimize power consumption and ensure low noise, this interface is designed for flexible I/O voltage and allows lowering of supply voltage down to

1.8V. The driving strength is configurable for signal integrity adjustment. The data bus also employs retention technology to prevent the bus from floating during turn over.

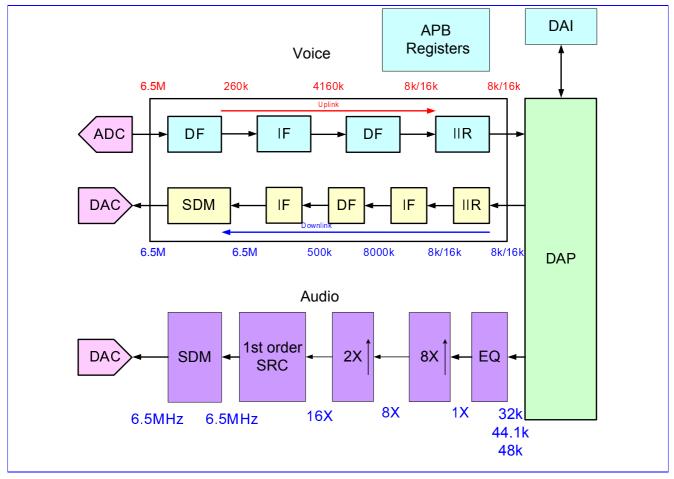

#### Multi-media

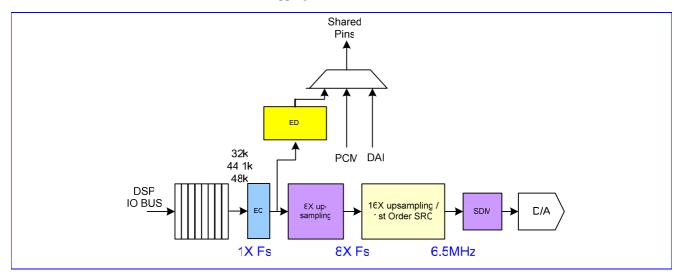

MT6253 utilize high resolution audio DAC, digital audio, and audio synthesis technology to provide superior audio features, e.g. MP3 ring tone.

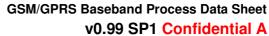

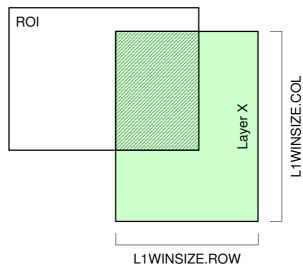

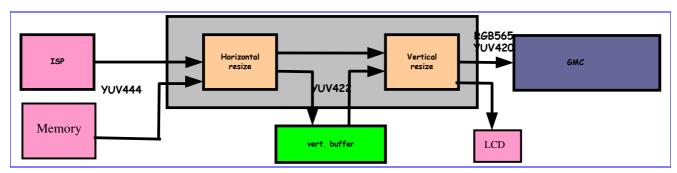

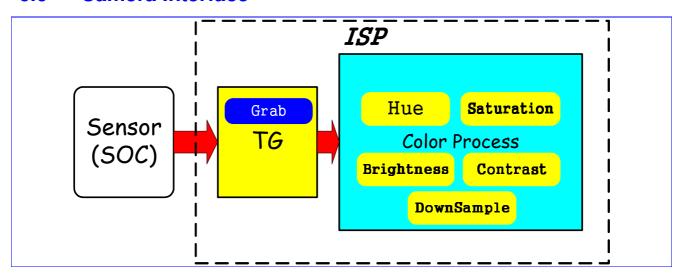

In order to provide more flexibility and bandwidth for multimedia products, an additional 8/9 bit parallel interface is incorporated. This interface is designed specially for support with Camera companion chip as well as LCD panel. In addition, MT6253 has camera YUV interface that can connect to CMOS sensor of resolution up to VGA. Moreover, it can connect NAND flash device to provide a solution for multimedia data storage. For running multimedia application faster, MT6253 integrates also several hardware-based engines. With hardware based Resizer and advanced display engine, it can display and combine arbitrary size of images with up to 4 blending layers.

### Connectivity and Storage

MT6253 supports UART as well as Bluetooth interface. Also, necessary peripheral blocks are embedded for a voice centric phone: Keypad Scanner with the capability to detect multiple key presses, dual SIM Controller, Alerter, Real Time Clock, PWM, Serial LCD Controller, USB 2.0 HS/FS/LS, MMC/SD/MS/MS Pro/SDIO, IrDA and general purpose programmable I/Os.

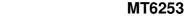

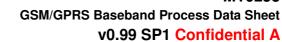

#### <u>Audio</u>

Using a highly integrated mixed-signal Audio Front-End architecture of MT6253 allows for easy audio interfacing with direct connection to the audio transducers. The audio interface integrates D/A and A/D Converters for Voice band, as well as high resolution Stereo D/A Converters for Audio band. In addition, MT6253 also

MediaTek Confidential © 2009 MediaTek Inc. Page 7 of 643

provides Stereo Input and Analog Mux. MT6253 also supports AMR codec to adaptively optimize speech and audio quality. Moreover, HE-AAC codec is implemented to deliver CD-quality audio at low bit rates.

Also, the 800mW class-D amplifier is also embedded to save the BOM cost of adopting external amplifier.

#### Radio

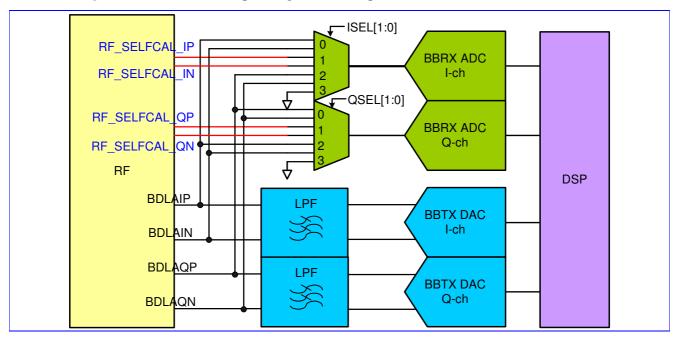

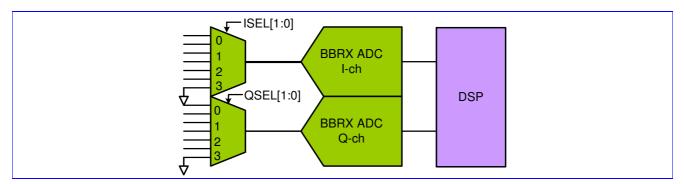

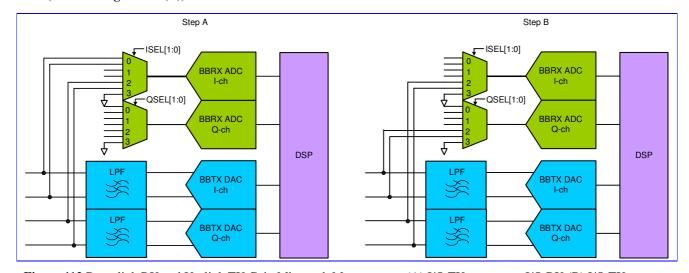

MT6253 integrates a mixed-signal Baseband front-end in order to provide a well-organized radio interface with flexibility for efficient customization. It contains gain and offset calibration mechanisms, and filters with programmable coefficients for comprehensive compatibility control on RF modules. MT6253 achieves great MODEM performance by utilizing 14-bit high resolution A/D Converter in the RF downlink path. Furthermore, to reduce the need for extra external current-driving component, the driving strength of some BPI outputs is designed to be configurable.

MT6253 also integrates the RF transceiver for multi-band GSM and GPRS cellular system. In the RF modules in SOC, a high performance quad band differential input LNAs/fully integrated channel filter with  $f_{\rm 3dB}{=}150 \rm kHz$  receiver is integrated. Also, the transmitter performs integrated TXVCO and loop filter. Furthermore, the frequency synthesizer and Digitally-Controlled Crystal Oscillator (DCXO) are build-in.

#### **Debug Function**

The JTAG interface enables in-circuit debugging of software program with the ARM7EJ-S<sup>TM</sup> core. With this standardized debugging interface, MT6253 provides developers with a wide set of options in choosing ARM development kits from different third party vendors. For security reason, JTAG interface can be disabled by programming internal OTP (one-time programmable) fuse.

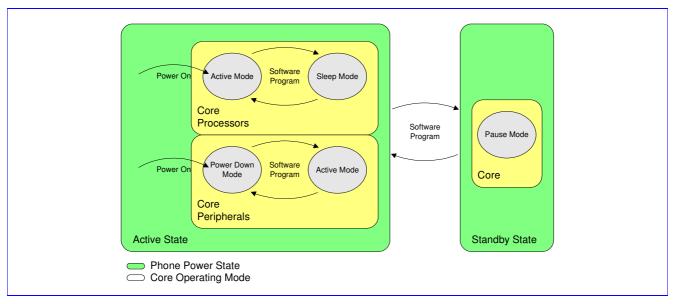

#### Low Power Features

MT6253 offers various low-power features to help reduce system power consumption. These features include Pause Mode of 32KHz clocking at Standby State, Power Down Mode for individual peripherals, and Processor Sleep Mode. In addition, MT6253 are also fabricated in advanced low leakage CMOS process, hence providing an overall ultra low leakage solution.

### Power Management

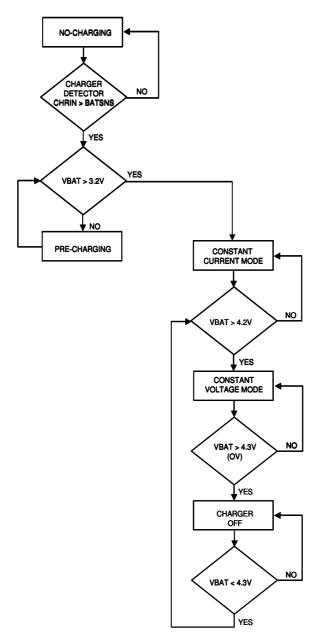

MT6253 integrates all regulators that a voice-centric phone needs. 11 LDOs optimized for Specific GSM/GPRS baseband sub-systems are included. Besides Li-Ion battery charge function, SIM card level shifter interface, two open-drain output switches to control the LED and vibrator are equipped. Other power management schemes such as thermal overload protection, Under Voltage Lock-out Protection (UVLO), over voltage protection and power-on reset and start-up timer are also MT6253 features. Besides, 3 NMOS switches controlling the RGB LEDs are also embedded to reduce BOM count.

### **Package**

The MT6253 device is offered in 11.5mm×11.5mm, 260-ball, 0.47 mm staggered pin pitch, aQFN package

MediaTek Confidential © 2009 MediaTek Inc. Page 8 of 643

Figure 1 Typical application of MT6253

MediaTek Confidential © 2009 MediaTek Inc. Page 9 of 643

# **MEDIATEK**

#### MT6253

# GSM/GPRS Baseband Process Data Sheet v0.99 SP1 Confidential A

## 1.1 Platform Features

#### General

- Integrated voice-band, audio-band and base-band analog front ends

- aQFN 11.5mm×11.5mm, 260-ball, 0.47 mm pitch package

#### MCU Subsystem

- ARM7EJ-S 32-bit RISC processor

- High performance multi-layer AMBA bus

- Java hardware acceleration for fast Java-based games and applets

- Operating frequency: 52/104 MHz

- Dedicated DMA bus

- 7 DMA channels

- 144KB on-chip SRAM

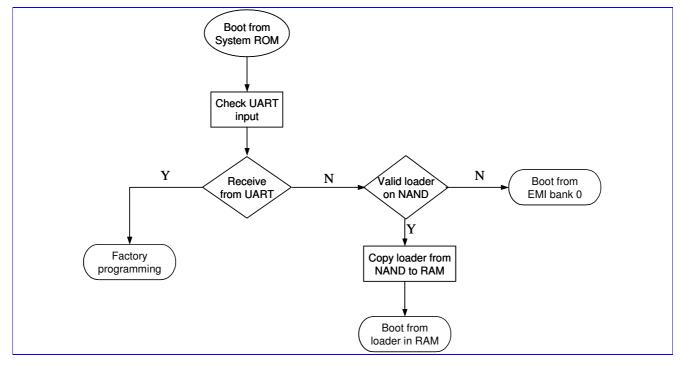

- On-chip boot ROM for Factory Flash Programming

- Watchdog timer for system crash recovery

- 3 sets of General Purpose Timer

- Circuit Switch Data coprocessor

- Division coprocessor

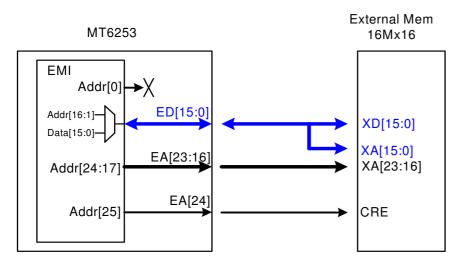

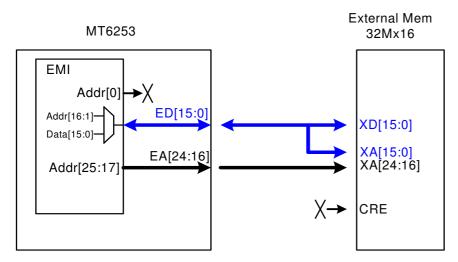

## **External Memory Interface**

- Supports up to 3 external devices

- Supports 16-bit memory components with maximum size of up to 64M Bytes for each bank

- Supports Flash and SRAM/PSRAM with Burst Mode

- Support legacy industry standard parallel LCD Interface

- Supports multi-media companion chips with 8/16 bits data width

- Configurable driving strength for memory interface

#### User Interfaces

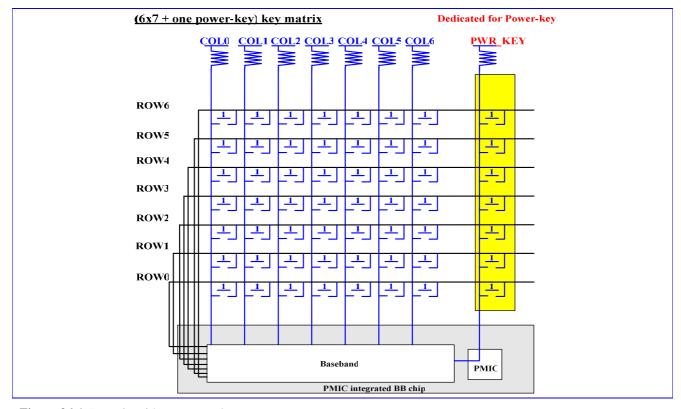

- 6-row x 7-column keypad controller with hardware scanner

- Supports multiple key presses for gaming

- SIM/USIM Controller with hardware T=0/T=1 protocol control

- Real Time Clock (RTC) operating with a separate power supply

- General Purpose I/Os (GPIOs)

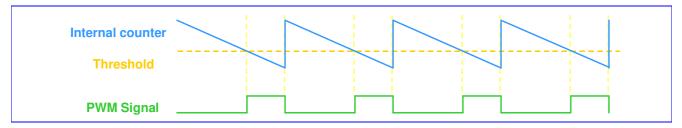

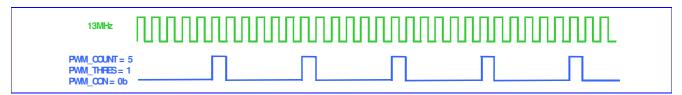

- 1 set of Pulse Width Modulation (PWM) Output

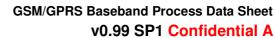

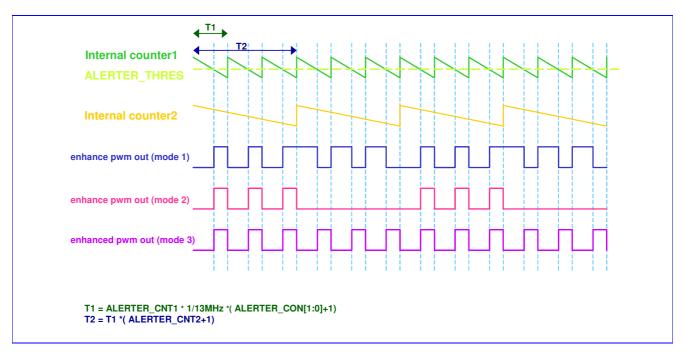

- Alerter Output with Enhanced PWM or PDM

- Maximum 7 external interrupt lines

### Security

• Supports security key and 128 bit chip unique ID

### Connectivity

- 3 sets of UART with hardware flow control and speed up to 921600 bps

- IrDA modulator/demodulator with hardware framer supports SIR mode of operation

- HS/FS/LS USB 2.0 Device controller

- Multi Media Card/Secure Digital Memory Card/Memory Stick/Memory Stick Pro/SDIO host controller

MediaTek Confidential © 2009 MediaTek Inc. Page 10 of 643

- Supports SDIO interface for SDIO peripherals as well as WIFI connectivity

- DAI/PCM and I2S interface for Audio application

### Low Power Schemes

- Power Down Mode for analog and digital circuits

- Processor Sleep Mode

- Pause Mode of 32KHz clocking at Standby State

- 3-channel Auxiliary 10-bit A/D Converter for application usage other than battery monitoring

#### Power and Supply Management

- 2.8V to 4.7V Input Range

- Charger Input up to 8V

- 11 sets of LDO Optimized for Specific GSM Sub-systems

- One LDO for RF transceiver

- High Operation Efficiency and Low Stand-by Current

- Li-Ion Battery Charge function

- Dual SIM Card Interface

- One boost regulator and Four Open-Drain

Output Current Regulators to Supply/Control the

LED

- LDO type Vibrator

- One NMOS switch to control R(GB) LED

- Thermal Overload Protection

- Under Voltage Lock-out Protection

#### Test and Debug

Over Voltage Protection

- Built-in digital and analog loop back modes for both Audio and Baseband Front-End

- DAI port complying with GSM Rec.11.10

- JTAG port for debugging embedded MCU

## 1.2 MODEM Features

#### Integrated RF Receiver

- Direct conversion architecture

- Quad band differential input LNAs

- Quadrature RF mixers

- Fully integrated channel filter with f<sub>3dB</sub>=150kHz

- 95 dB gain with 60 dB gain control range

- No IIP2 calibration

### Integrated RF Transmitter

- Offset phase lock loop

- IQ modulator DC offset calibration by BB ADC/DAC.

- Precise quadrature by IF divide-by-4.

- Integrated TX VCO

- Integrated loop filter

### Integrated RF Frequency Synthesizer

- Programmable fractional-N synthesizer

- Integrated wide range RFVCO

- Integrated loop filter

MediaTek Confidential © 2009 MediaTek Inc. Page 11 of 643

# **MEDIATEK**

#### MT6253

# GSM/GPRS Baseband Process Data Sheet v0.99 SP1 Confidential A

Fast settling time suitable for multi-slot GPRS/EDGE applications

# Integrated RF Digitally-Controlled Crystal Oscillator (DCXO)

- One-pin 26 MHz crystal oscillator

- On-chip programmable capacitor array for cross tune

- On-chip programmable capacitor array for fine tune

#### Radio Interface and Baseband Front End

- GMSK modulator with analog I and Q channel outputs

- 10-bit D/A Converter for uplink baseband I and Q signals

- 14-bit high resolution A/D Converter for downlink baseband I and Q signals

- Calibration mechanism of offset and gain mismatch for baseband A/D Converter and D/A Converter

- 10-bit D/A Converter for Automatic Power Control

- Programmable Radio RX filter with adaptive bandwidth control

- Dedicated Rx filter for FB acquisition

- 6-Pin Baseband Parallel Interface (BPI) with programmable driving strength

- Multi-band support

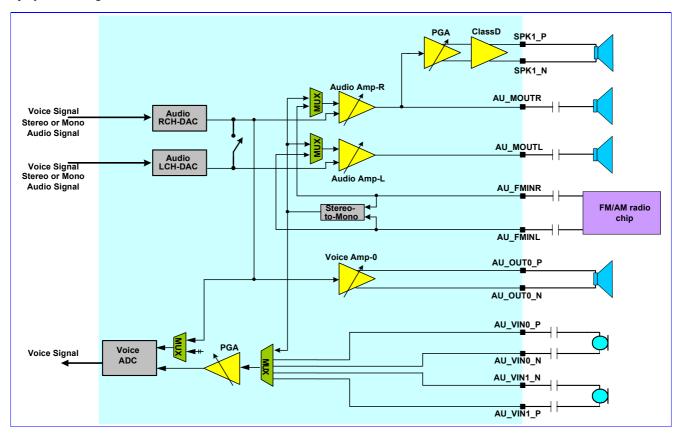

### **■ Voice and Modem CODEC**

- Dial tone generation

- Voice Memo

- Noise Reduction

- Echo Suppression

- Advanced Sidetone Oscillation Reduction

- Digital sidetone generator with programmable gain

- Two programmable acoustic compensation filters

- GSM/GPRS quad vocoders for adaptive multirate (AMR), enhanced full rate (EFR), full rate (FR) and half rate (HR)

- GSM channel coding, equalization and A5/1, A5/2 and A5/3 ciphering

- GPRS GEA1, GEA2 and GEA3 ciphering

- Programmable GSM/GPRS Modem

- GSM Circuit Switch Data

- GPRS Class 12

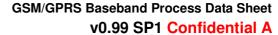

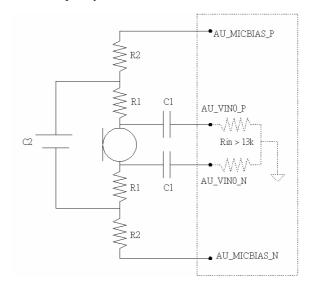

#### **Voice Interface and Voice Front End**

- Two microphone inputs sharing one low noise amplifier with programmable gain and automatic gain control (AGC) mechanism

- Voice power amplifier with programmable gain

- 2<sup>nd</sup> order Sigma-Delta A/D Converter for voice uplink path

- D/A Converter for voice downlink path

- Supports half-duplex hands-free operation

- Compliant with GSM 03.50

## 1.3 Multi-Media Features

LCD Interface

Page 12 of 643

MediaTek Confidential

© 2009 MediaTek Inc.

# **МЕДІЛІЕК**

#### MT6253

# GSM/GPRS Baseband Process Data Sheet v0.99 SP1 Confidential A

Dedicated Parallel Interface supports 2 external 8/9 bit Parallel Interface, and Serial interface for LCM

- Stereo to Mono Conversion

- HE-AAC decode support

### **LCD Controller**

- Supports LCM format: RGB332, RGB444, RGB565, RGB666, RGB888

- Supports LCD module with maximum resolution up to 240x320 at 16bpp

- Capable of combining display memories with up to 4 blending layers

- Accelerated Gamma correction with programmable gamma table.

- Supports hardware display rotation for each layer

### Audio CODEC

- Wavetable synthesis with up to 64 tones

- Advanced wavetable synthesizer capable of generating simulated stereo

- Wavetable including GM full set of 128 instruments and 47 sets of percussions

- PCM Playback and Record

- Digital Audio Playback

### Audio Interface and Audio Front End

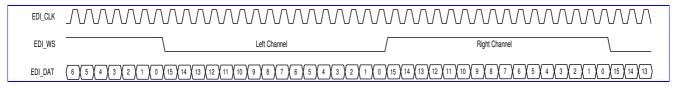

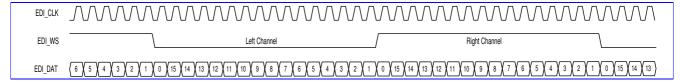

- Supports I2S interface

- High resolution D/A Converters for Stereo Audio playback

- Stereo analog input for stereo audio source

- Analog multiplexer for Stereo Audio

- FM Radio Recording

© 2009 MediaTek Inc.

Page 13 of 643

# 1.4 General Description

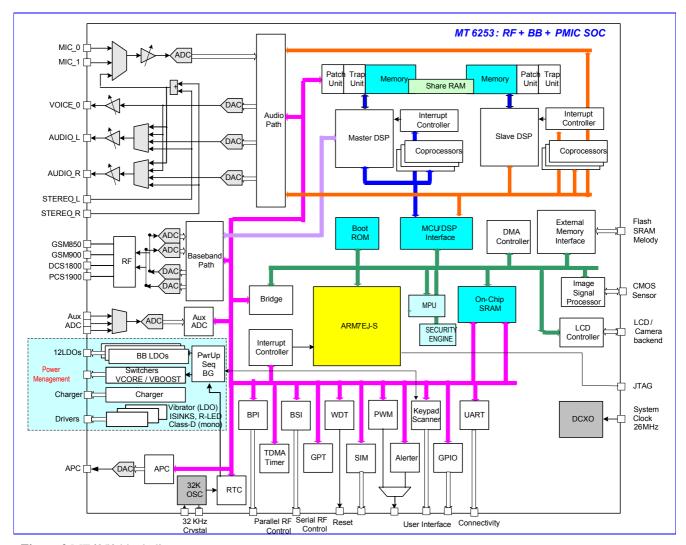

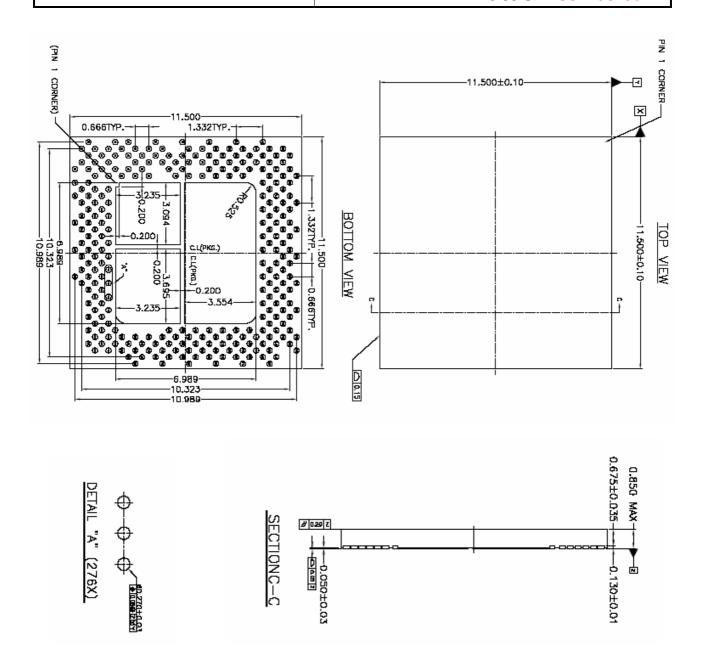

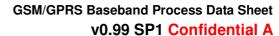

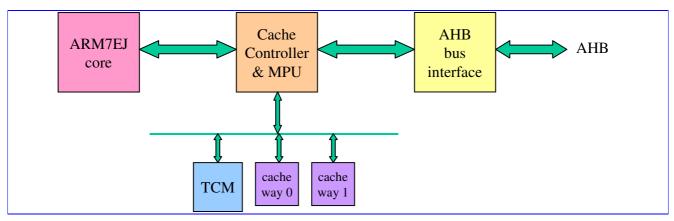

**Figure 2** details the block diagram of MT6253. Based on a dual-processor architecture, MT6253 integrates both an ARM7EJ-S core and 2 digital signal processor cores. ARM7EJ-S is the main processor that is responsible for running 2G and 2.5G protocol software. Digital signal processors handle the MODEM algorithms as well as advanced audio functions. Except for some mixed-signal circuitries, the other building blocks in MT6253 are connected to either the microcontroller or one of the digital signal processors.

Specifically, MT6253 consist of the following subsystems:

- Highly integrated RF transceiver for multi-band GMS and GPRS cellular systems.

- Microcontroller Unit (MCU) Subsystem includes an ARM7EJ-S RISC processor and its accompanying memory management and interrupt handling logics.

- Digital Signal Processor (DSP) Subsystem includes 2 DSP cores and their accompanying memory, memory controller, and interrupt controller.

- MCU/DSP Interface where the MCU and the DSPs exchange hardware and software information.

- Microcontroller Peripherals includes all user interface modules and RF control interface modules.

- Microcontroller Coprocessors runs computing-intensive processes in place of Microcontroller.

- DSP Peripherals hardware accelerators for GSM/GPRS channel codec.

- Voice Front End the data path for converting analog speech from and to digital speech.

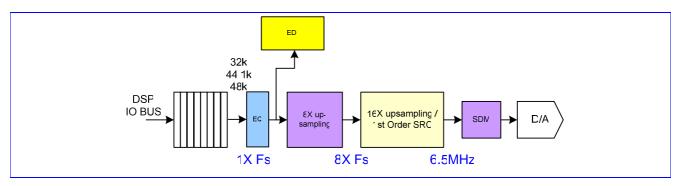

- Audio Front End the data path for converting stereo audio from stereo audio source

- Baseband Front End the data path for converting digital signal from and to analog signal of RF modules.

- Timing Generator generates the control signals related to the TDMA frame timing.

- Power, Reset and Clock subsystem manages the power, reset, and clock distribution inside MT6253

- LDOs, Power-on sequences, switches and SIM level shifters.

- Details of the individual subsystems and blocks are described in following Chapters.

MediaTek Confidential © 2009 MediaTek Inc. Page 14 of 643

Figure 2 MT6253 block diagram

MediaTek Confidential © 2009 MediaTek Inc. Page 15 of 643

# **2 Product Description**

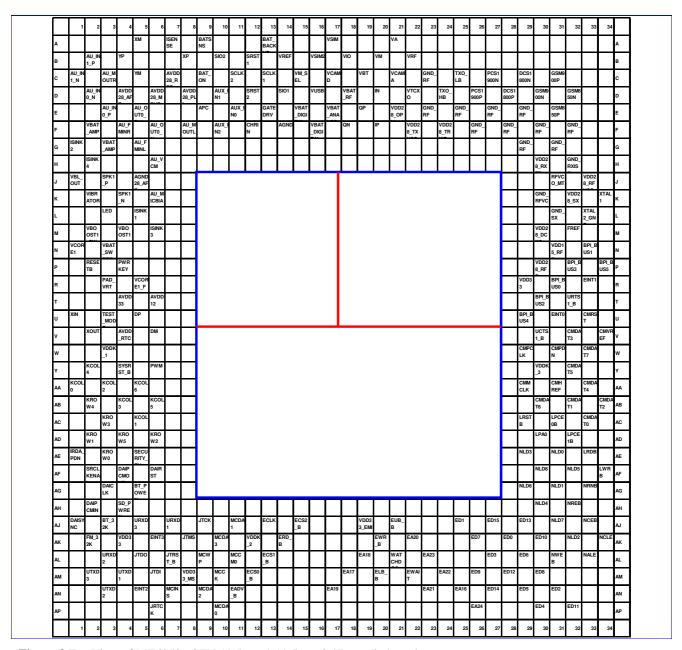

## 2.1 Pin Outs

One type of package for this product, aQFN 11.5mm \* 11.5mm, 260-ball, 0.47mm pitch Package is offered.

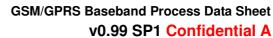

Pin-outs and the top view are illustrated in **Figure 3** for this package. Outline and dimension of package is illustrated in **Figure 4**, while the definition of package is shown in **Table 1**.

Figure 3 Top View of MT6253 aQFN 11.5mm \* 11.5mm 0.47mm pitch package

MediaTek Confidential © 2009 MediaTek Inc. Page 17 of 643

Figure 4 Outlines and Dimension of MT6253 aQFN 11.5mm \* 11.5mm 0.47mm pitch package

| Body | Size | <b>Ball Count</b> | Ball Pitch | Ball Dia. | Package Thk. |

|------|------|-------------------|------------|-----------|--------------|

| 11.5 | 11.5 | 260               | 0.47       | 0.270     | 0.850        |

**Table 1** Definition of aQFN 11.5mm \* 11.5mm 0.47mm pitch package (Unit: mm)

MediaTek Confidential

© 2009 MediaTek Inc.

Page 18 of 643

This document contains information that is proprietary to MediaTek Inc.

# 2.2 Top Marking Definition

<u>ARM</u>

MT6253N DDDD-### LLLLL

S

MT6253N: Part No. DDDD: Date Code

###: Subcontractor Code

LLLLL: Die Lot No. S: Special Code

Figure 5 Top Mark of MT6253

# 2.3 DC Characteristics

# 2.3.1 Absolute Maximum Ratings

Prolonged exposure to absolute maximum ratings may reduce device reliability. Functional operation at these maximum ratings is not implied.

| Item                  | Symbol | Min  | Max       | Unit    |

|-----------------------|--------|------|-----------|---------|

| IO power supply       | VDD33  | -0.3 | VDD33+0.3 | V       |

| I/O input voltage     | VDD33I | -0.3 | VDD33+0.3 | V       |

| Operating temperature | Topr   | -20  | 80        | Celsius |

| Storage temperature   | Tstg   | -55  | 125       | Celsius |

# 2.4 Pin Description

Below pin description is identical for both MT6253, total 260 pins.

| aQFN       | NAME       | Dir | PIN DESCRIPTION  Analog Baseband Interface (20 pins) | Aux Func.0 | Aux Func.1 | Aux Func.2 | Aux Func.3   | PU/PD | Reset |

|------------|------------|-----|------------------------------------------------------|------------|------------|------------|--------------|-------|-------|

|            |            |     | Analog Baseband Interface (Eo pins)                  |            | ı          |            | I            | I     |       |

| F8         | AU_MOUTL   |     | Audio analog output left channel                     |            |            |            |              |       |       |

| C3         | AU_MOUTR   |     | Audio analog output right channel                    |            |            |            |              |       |       |

| F4         | AU_FMINR   |     | FM radio analog input right channel                  |            |            |            |              |       |       |

| G5         | AU_FMINL   |     | FM radio analog input left channel                   |            |            |            |              |       |       |

| F6         | AU_OUT0_N  |     | Earphone 0 amplifier output (-)                      |            |            |            |              |       |       |

| E5         | AU_OUT0_P  |     | Earphone 0 amplifier output (+)                      |            |            |            |              |       |       |

| B2         | AU_IN1_P   |     | Microphone 1 amplifier input (+)                     |            |            |            |              |       |       |

| C1         | AU_IN1_N   |     | Microphone 1 amplifier input (-)                     |            |            |            |              |       |       |

| D2         | AU_INO_N   |     | Microphone 0 amplifier input (+)                     |            |            |            |              |       |       |

| E3         | AU_IN0_P   |     | Microphone 0 amplifier input (-)                     |            |            |            |              |       |       |

| E11        | AUX_IN0    |     | Auxiliary ADC input 0                                |            |            |            |              |       |       |

| D10        | AUX_IN1    |     | Auxiliary ADC input 1                                |            |            |            |              |       |       |

| F10        | AUX_IN2    |     | Auxiliary ADC input 2                                |            |            |            |              |       |       |

| <b>E</b> 9 | APC        |     | Automatic power control DAC output                   |            |            |            |              |       |       |

| B8         | XP         |     | Touch panel X-axis positive input                    |            |            |            |              |       |       |

| A5         | хм         |     | Touch panel X-axis negative input                    |            |            |            |              |       |       |

| B4         | YP         |     | Touch panel Y-axis positive input                    |            |            |            |              |       |       |

| C5         | YM         |     | Touch panel Y-axis negative input                    |            |            |            |              |       |       |

| Н6         | AU_VCM     |     | Clean VCM for reference buffer                       |            |            |            |              |       |       |

| K6         | AU MICBIAS |     | Microphone bias source P                             |            |            |            |              |       |       |

|            | _          |     | RF Interface (17 pins)                               |            | ,          |            | ,            |       |       |

| E21        | GSM850P    |     | Differential DE input and for DV CCM050 hand         |            |            |            |              |       |       |

| E31        |            |     | Differential RF input pad for RX GSM850 band         |            |            |            |              |       |       |

| D32        | GSM850N    |     | Differential RF input pad for RX GSM850 band         |            |            |            |              |       |       |

| D30        | GSM900N    |     | Differential RF input pad for RX GSM900 band         |            |            |            |              |       |       |

| C31        | GSM900P    |     | Differential RF input pad for RX GSM900 band         |            |            |            | <del> </del> |       |       |

| D28        | DCS1800P   |     | Differential RF input pad for RX DCS1800 band        |            |            |            | 1            |       |       |

| C29        | DCS1800N   |     | Differential RF input pad for RX DCS1800 band        |            | -          |            | -            |       |       |

| C27        | PCS1900N   |     | Differential RF input pad for RX PCS1900 band        |            |            |            | -            |       |       |

| D26        | PCS1900P   |     | Differential RF input pad for RX PCS1900 band        |            |            |            |              |       |       |

| C25        | TXO_LB     |     | RF output pad for TX LB (GSM900/GSM850)              |            | -          |            |              |       | -     |

| D24        | TXO_HB     |     | RF output pad for TX HB (DCS/PCS)                    |            |            |            |              |       |       |

| F20        | IP         |     | I/O pad for BB analog IQ                             |            |            |            |              |       |       |

| D20        | IN         |     | I/O pad for BB analog IQ                             |            |            |            |              |       |       |

MediaTek Confidential © 2009 MediaTek Inc. Page 20 of 643

| E19 QP I/O pad for BB analog IQ  F18 QN I/O pad for BB analog IQ  J31 RFVCO_MT Monitor pad for RFVCO output  M32 FREF Monitor pad for DCXO output  K34 XTAL1 Input pad for DCXO crystal  RF Control Circuitry (6 pins)  P34 BPI_BUS5 IO RF hard-wire control bus bit 5 GPIO82 BPI_BUS5  U29 BPI_BUS4 IO RF hard-wire control bus bit 4 GPIO81 BPI_BUS4  P32 BPI_BUS3 IO RF hard-wire control bus bit 3  T30 BPI_BUS2 IO RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |         | Output |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|--------|

| J31 RFVCO_MT Monitor pad for RFVCO output  M32 FREF Monitor pad for DCXO output  K34 XTAL1 Input pad for DCXO crystal  RF Control Circuitry (6 pins)  P34 BPI_BUS5 IO RF hard-wire control bus bit 5 GPIO82 BPI_BUS5  U29 BPI_BUS4 IO RF hard-wire control bus bit 4 GPIO81 BPI_BUS4  P32 BPI_BUS3 IO RF hard-wire control bus bit 3  T30 BPI_BUS2 IO RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |         |        |

| M32   FREF   Monitor pad for DCXO output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |         |        |

| RF Control Circuitry (6 pins)   RF hard-wire control bus bit 5   GPIO82   BPI_BUS5   BPI_BUS4   IO   RF hard-wire control bus bit 4   GPIO81   BPI_BUS4   BPI_BUS3   IO   RF hard-wire control bus bit 3   RF hard-wire control bus bit 2   RF hard-wire control bus bit 3   RF hard-wire control bus bit 4   RF hard-wire control bus bit 4   RF hard-wire control bus bit 5   RF hard-wire control bus bit 6   RF hard-wire control bus bit 6   RF hard-wire control bus bit 7   RF hard-wire control bus bit 9   RF hard-wire control bus b |            |         |        |

| RF Control Circuitry (6 pins)     P34   BPI_BUS5   IO   RF hard-wire control bus bit 5   GPIO82   BPI_BUS5     U29   BPI_BUS4   IO   RF hard-wire control bus bit 4   GPIO81   BPI_BUS4     P32   BPI_BUS3   IO   RF hard-wire control bus bit 3     T30   BPI_BUS2   IO   RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |         |        |

| P34         BPI_BUS5         IO         RF hard-wire control bus bit 5         GPI082         BPI_BUS5           U29         BPI_BUS4         IO         RF hard-wire control bus bit 4         GPI081         BPI_BUS4           P32         BPI_BUS3         IO         RF hard-wire control bus bit 3         IO         RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |         |        |

| U29         BPI_BUS4         IO         RF hard-wire control bus bit 4         GPIO81         BPI_BUS4           P32         BPI_BUS3         IO         RF hard-wire control bus bit 3           T30         BPI_BUS2         IO         RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |         |        |

| P32 BPI_BUS3 IO RF hard-wire control bus bit 3  T30 BPI_BUS2 IO RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |         | Output |

| T30 BPI_BUS2 IO RF hard-wire control bus bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |         | Juipui |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |         | Output |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |         | Output |

| N33 BPI_BUS1 IO RF hard-wire control bus bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |         | Output |

| R31 BPI_BUS0 IO RF hard-wire control bus bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |         | Output |

| Digital Audio Interface (5 pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |         |        |

| AG3 DAICLK IO DAI interface clock output GPIO15 DAICLK clko5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |            | PU/PD   | Output |

| AF4 DAIPCMOUT IO DAI PCM data output GPIO16 DAIPCMOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | PU/PD   | Output |

| AH2 DAIPCMIN IO DAI PCM data input GPIO17 DAIPCMIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IRDA_PDN   | PU/PD   | Input  |

| AF6 DAIRST IO DAI reset signal input GPIO18 DAIRST clko0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IRDA_TX    | PU/PD   | Input  |

| AJ1 DAISYNC IO DAI frame synchronization input GPIO19 DAISYNC XADMUX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | PU/PD   | Input  |

| PWM Interface (1 pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |         |        |

| Y6 PWM IO Pulse-width modulated signal GPIO0 PWM CLKSQ_SE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | L Alerter  | PU/PD   | Input  |

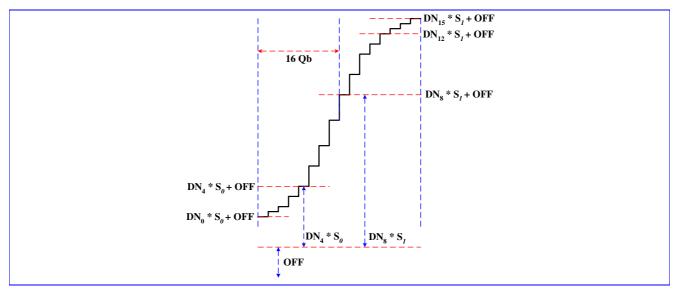

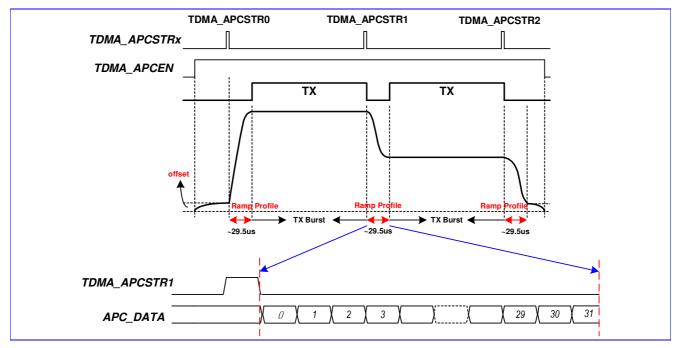

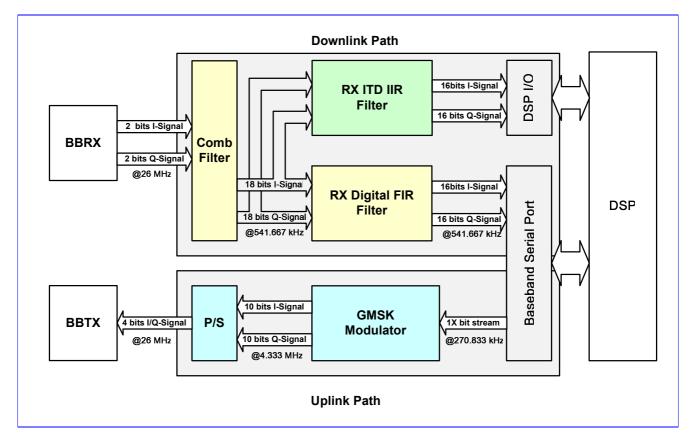

| JTAG Interface (6 pins)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LI Aleitei | F 0/F D | mput   |