MEDIATEK

Confidential B

## MT6616 Application Note EX Confidential Newsconding

Copyright © MediaTek Inc. All rights reserved.

## Revise history

| Revision | Date       | Comments                            | Pages |

|----------|------------|-------------------------------------|-------|

| V0.1     | 2010/01/XX | Initial release                     |       |

| V0.2     | 2010/3/XX  | Modify FM design guide for de-sense |       |

|          |            |                                     |       |

|          |            |                                     |       |

|          |            | Sat                                 |       |

|          |            | 2-10366 In.                         |       |

|          |            | L'al Relegio                        |       |

|          |            | e dontial                           |       |

|          | -V C.01    | Miner                               |       |

| -1011    | I FV a.    |                                     |       |

|          |            | - MANA                              |       |

|          |            |                                     |       |

|          | Dati       | CGIII                               |       |

Confidential B

#### louceut MCX **Outline**

#### FM receiver

- ✓ Reference Schematic and Layout

- ✓ PCB Design Example for MT6616

- ✓ Audio Interface Design

- ✓ FM Earphone Antenna Illustrations

#### 2. Bluetooth

- Release for ✓ Reference Schematic and Layout

- ✓ MT6616 Power Protection

- ✓ Interfacing

- ✓ BT Antenna Placement Guideline

#### 3. External 26MHz Sharing with RF

- MT6253

- ✓ AD6548

- ✓ MT6160 (3G VCTC)

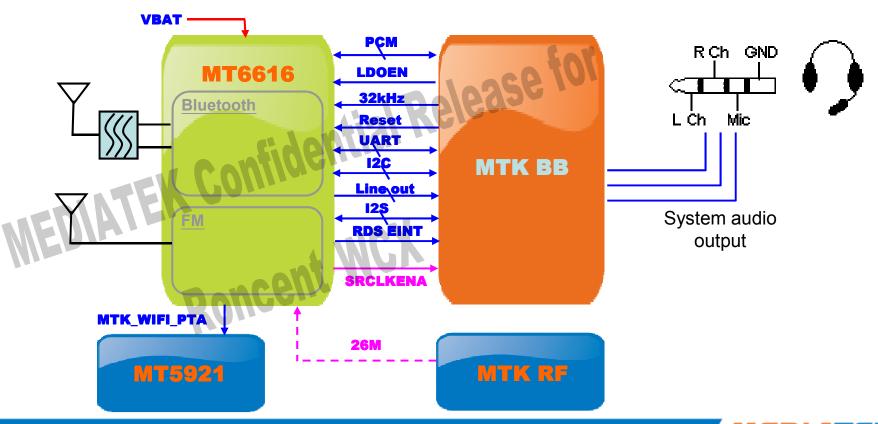

#### **MT6616 System Interface**

Supports QFN & CSP Package

MATER JOIN

- ✓ QFN package for low-cost layout design

- ✓ CSP package for compact layout design (2010 Q1)

- Built-in LDO, LDO cost saved (US\$ 0.05)

- Support external 32kHz and 26MHz clock, no Crystal needed.

Confidential B

## MEDIATEK MEDIATEK

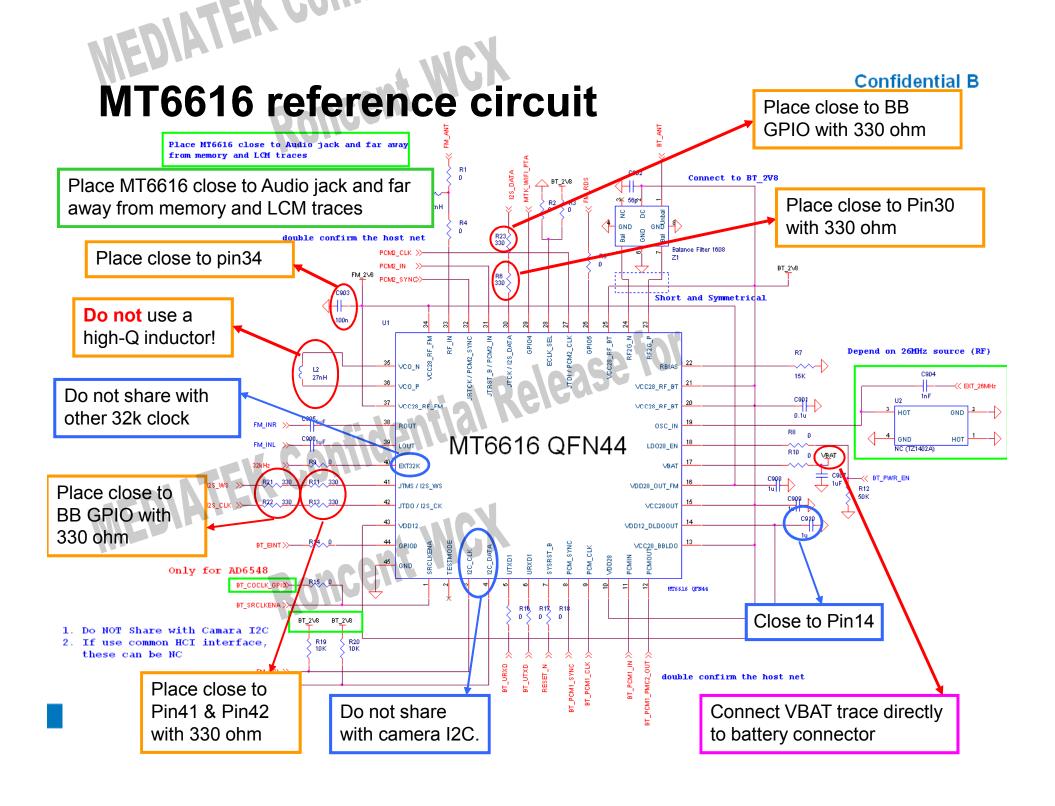

#### MT6616 Design Guide - FM Receiver

Copyright © MediaTek Inc. All rights reserved.

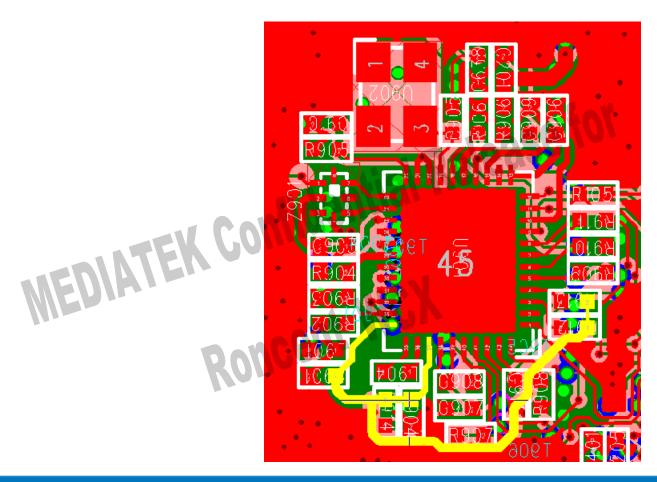

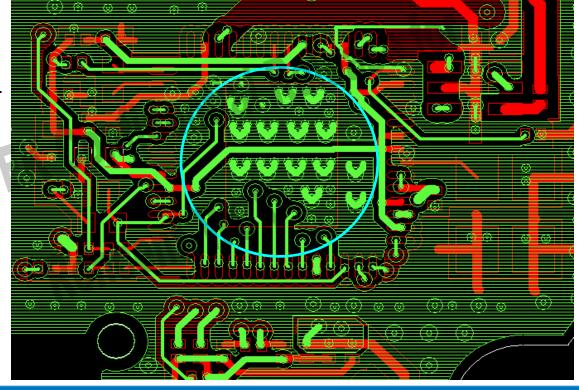

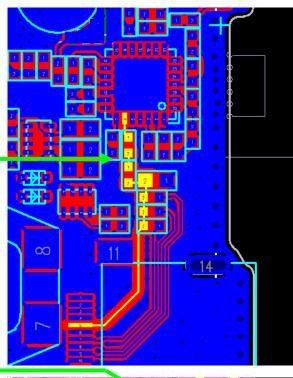

## Reference Layout – MT6616 FM

#### Placement

- Place the FM near the earphone jack. Avoid high-speed digital devices, such as memory and LCM devices, near the RF signal area.

- Bypass cap for power should be placed beside the VCC and VCO pin (MT6616 pin 13,14,15,16,34,35,36,37).

- Place VCO inductor close to pin 35 and 36. Do not let any noisy trace near or cross VCO inductor path

#### Routing

- FM antenna trace should have a  $50\Omega$  impedance.

- Power should be routed to the bypass cap and the VCCVCO pin first, then to all other power pins on the FM chip. See the following pages for example.

- Keep layer2 GND plane under MT6616 chip as complete as possible. See the following pages for example.

- Add series 330 ohm for I2S\_data , I2S\_WS , I2S\_CLK trace to prevent noise coupling

- Use inner layer for I2S\_data , I2S\_WS , I2S\_CLK trace routing.

- Protect the following areas with GND vias and GND planes:

- RF signal from the earphone jack all the way to the FM chip;

- 32.768 kHz and 26 MHz signal;

- VCO inductor (MT6616 pins 13,14,15,16,34,35,36,37);

#### Power Feeding Network Layout Guidelines Confidential B

The FM power should be monopolized: do not connect other blocks to VCC\_FM.

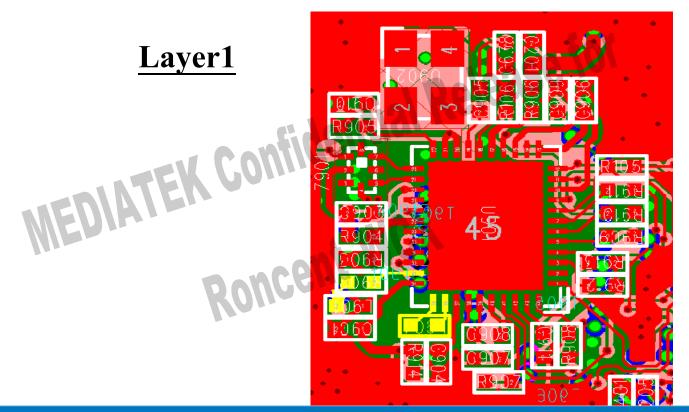

#### **Ground Layout (layer1)**

Assure all bypass caps grounding or front-end matching grounding is solid grounding

#### Layer1

#### **Ground Layout (layer2)**

Keep layer2 GND plane under MT6616 chip as complete as possible to minimize AC return current loop. Broken GND plane will result in large AC return current loop and increase EMI on FM

#### Layer2

Confidential B

#### Other System Consideration for FM (1/2)

- Rule 1: Protect the BB 32.768kHz crystal layout

- If the 32.768kHz signal is corrupted by digital signals, FM channel locking may be unstable.

- BB 32.768kHz crystal layout rules:

VILEY AM

- Place the 32.768kHz crystal unit close to the BB, and L2 beneath crystal needs to be complete ground. The crystal and its traces must be protected by ground vias and ground planes.

- Do not route power, MCP, FM I2C traces near 32.768kHz crystal circuit.

- The 32.768kHz traces between crystal unit and BB should be on top layer.

- Rule 2: Backlight driver adoption

- USE a charge pump backlight driver.

- Using a DC-DC backlight driver may cause increased noise levels when the backlight is on. Need to take good care of DC-DC traces.

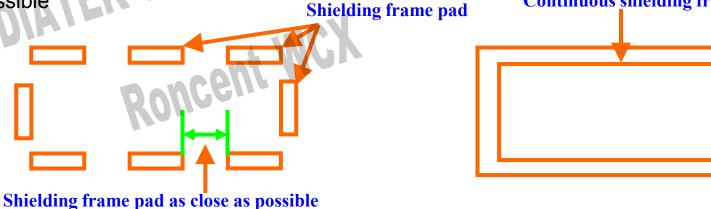

Don't dig hole in shielding cover and keep shielding frame pad as close or continuous as possible

Shielding frame pad

Continuous shielding frame pad

Confidential B

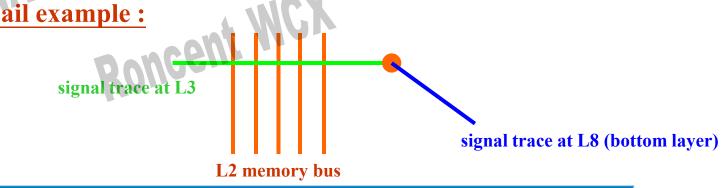

#### Other System Consideration for FM (2/2)

MAJEN AAN

- Since FPC/connectors/LCM screen might result in FM wireless de-sense issue, to keep earphone jack away from the above EMI source is recommended

- USB bus/LCM bus/memory bus traces have to route in inner PCB GND layers with solid GND shielding or route in shielding cover to avoid EMI on FM de-sense

- Since EMI filter is generally applied in LCM traces, to select EMI filter with FM band attenuation is recommended

- Don't let other signal traces crossed or paralleled with memory bus/LCM bus/USB bus, especially the signal traces finally will route in PCB top/bottom layer without shielding

# PCB Design example for MT6616 MEDIATEK Confidential Release MEDIATEK Confidential Release for MT6616

Roncent WCX

#### MEDIAIEN Son Roncent WCX **Outline**

- FM design notes

- Earphone pin definition

- PMU VBAT, VCORE, Boost1 & Class D

- LCM

- Memory interface

#### FM De-sense Design Note

- Noise source

- Low chip level EMI

- Low slew rate

- Low switching frequency

- Low output swing

- Clock frequency hopping

- Path

- Power trace star connection

- Inner layer covered with ground for noise trace routing

- Adding bead for noise suppression

- Solid ground for bypass cap

- FM IC

- Place FM chip near earphone jack

- Short and well-shielded antenna trace

- Solid ground and bypass cap close to FM chip

- Protected 32.768KHz clock trace

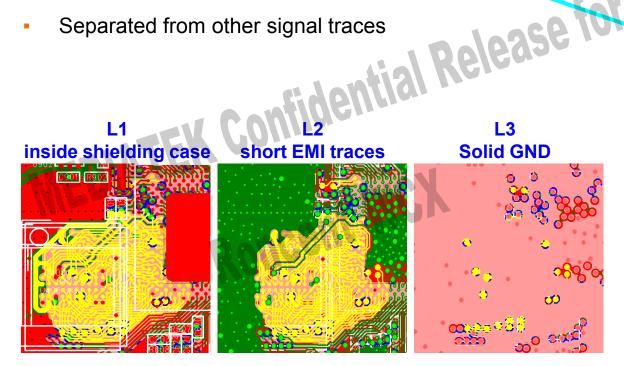

#### EDIAIEN John FM Design Note

#### Confidential B

- FM

- Place FM chip near earphone jack

- Short and well-shielded antenna trace

- Solid ground and bypass cap close to FM chip

- Protected 32.768KHz clock trace

- Other noisy trace

- Inner layer with ground trace around

Adding series head for a

Roncent WCX

Solid ground for bypass cap

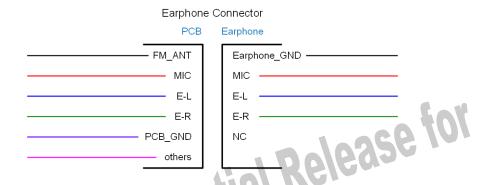

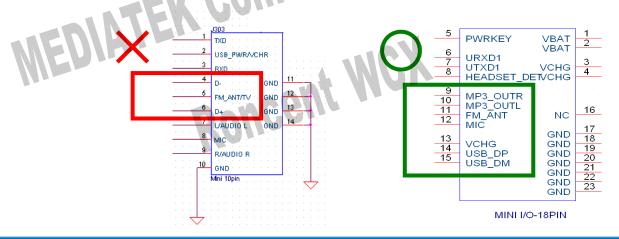

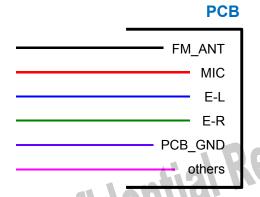

#### **Earphone PIN Definition**

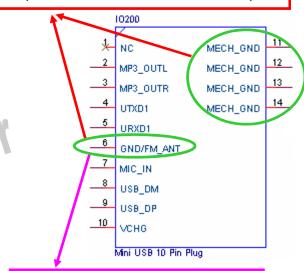

- Connect earphone ground to FM\_ANT

- Separate FM\_ANT pin from USB data pins to avoid noise coupling

Not recommend: USB data pins next to FM\_ANT pin (x)

#### **Audio Interface Design Concept**

MATEN DOWN

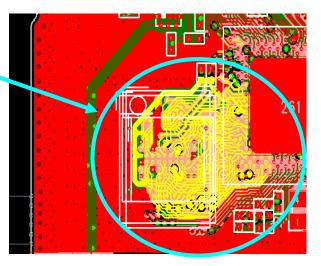

#### PMU DC/DC switching design notes

- PMU VBAT, VCORE, Boost1 and Class D

- Input power trace star connection

- Input & output **bead** close to IC in shielding case

- Input bypass capacitor close to IC in shielding case Input & output trace width

- Input & output solid ground and short return ground path

Roncent WCX

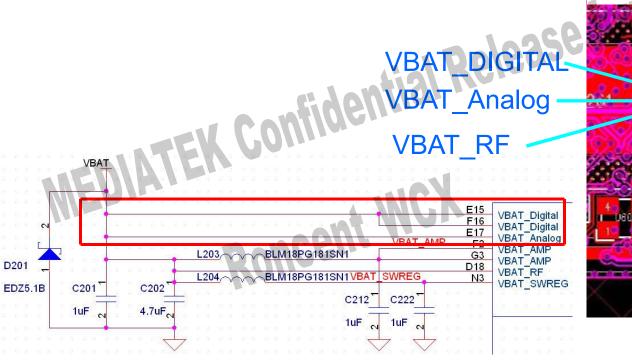

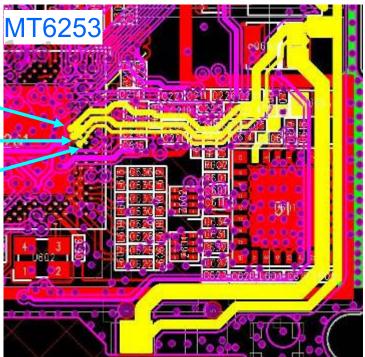

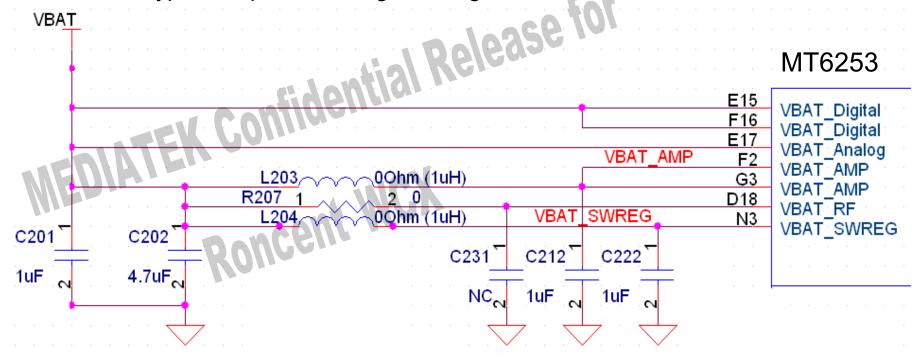

#### PMU - VBAT Traces (1/2)

VBAT\_Analog and VBAT\_RF should separate the VBAT\_DIGITAL trace and star-connect to the bulk capacitor near battery connector.

**BAT** connector

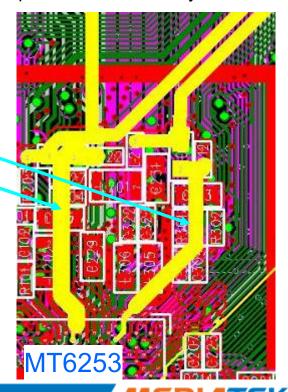

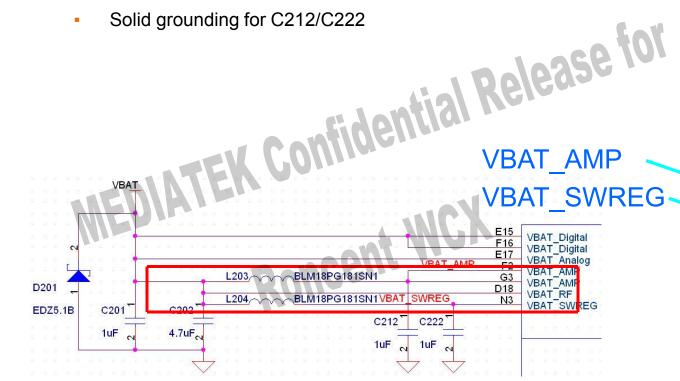

#### PMU - VBAT Traces (2/2)

- (VBAT\_AMP/VBAT\_SWREG) should separate the VBAT\_DIGITAL trace. Start connection from battery connector and all traces should be in inner layer or under shielding case.

- L203/L204/C212/C222 should put close to pin-out and be in shielding case.

- Enhance the VIA connection (at least >2)

MAJEN Jan

Solid grounding for C212/C222

plane via hole directly.

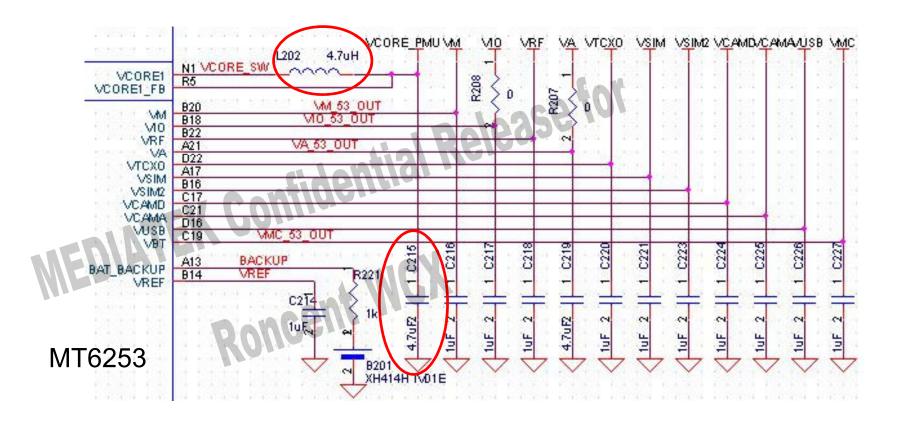

#### **PMU – VCORE (1/2)**

LFV Agin.

- Inner layer routing with GND shielding

- Star connection to CON directly

- VBAT branch line width 28mil at least

- Reserve one bead (BLM15AX102SN1) for L204 and close to IC to avoid switching noise influencing FM de-sense

- Place bypass cap with solid grounding and close to IC

## PMU – VCORE (2/2)

As for VCORE, please keep L202 and C215 close to MT6253 and in shielding cover.

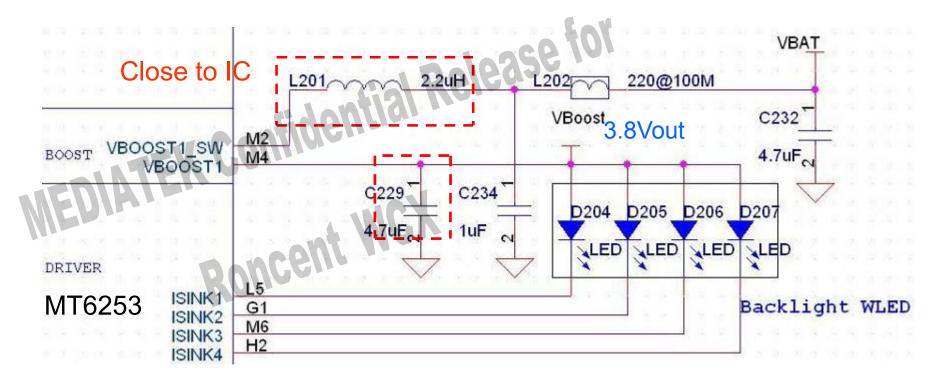

#### PMU – Boost1 For Parallel LCM

MATEN OUT

- Set BOOST Vout=3.8V and apply ISINK (constant current ) for backlight WLED

- Reserve one bead (BLM15AX102SN1) for L202 and close to IC to avoid switching noise influencing FM de-sense

- Keep L201 and C229 close to MT6253 and put in shield case.

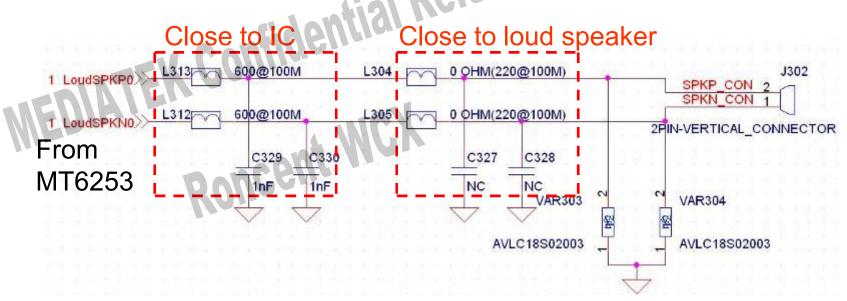

## PMU - Class-D Audio Amplifier Output Filter

Use Class AB as back-up

MEDIAIEN voi.

- Reserve 2 stage filter at output stage of Class-D to prevent interference to RF performance.

- 1<sup>st</sup> stage filter should be close to IC as possible, 2<sup>nd</sup> stage filter should be close to loud speaker.

- All the traces from IC to 2<sup>nd</sup> stage filter should not exposed to prevent interference I Release 10 to RF performance

## LCM FPC ancent WCX

- Use copper and short FPC to avoid noise radiation

- Shield LCM with ground well

- Reserve EMI filter in LCM data bus and close to LCM FPC connector.

- EMI filter includes FM band attenuation

- Suppress LCM screen and FPC radiation on FM wireless de-sense

#### XLong and no shielding

#### Short and shielded well

#### EMI filter near FPC connector

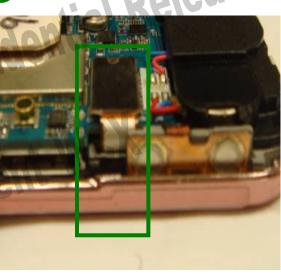

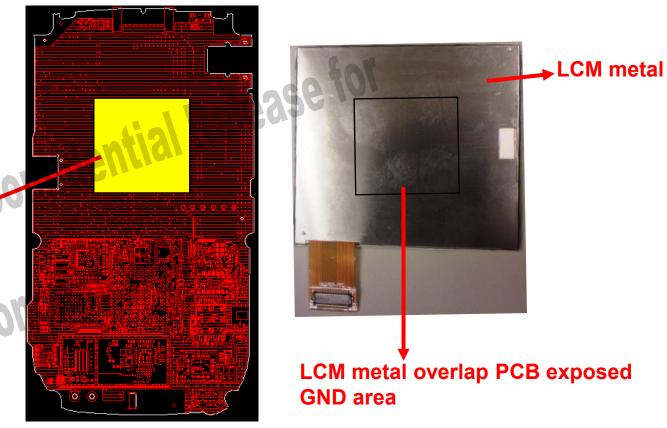

#### LCM Metal NCX

- In order to suppress LCM screen radiation, proper PCB exposed GND area(1/4 LCM metal area at least is recommended) reserving for LCM metal solid grounding is necessary

- if necessary, to insert conductive cloth between LCM metal and PCB exposed GND area can assure solid grounding

PCB exposed GND area reserving for LCM metal solid grounding

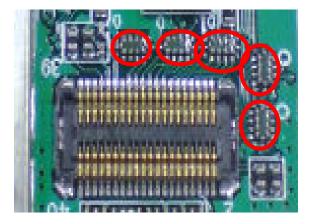

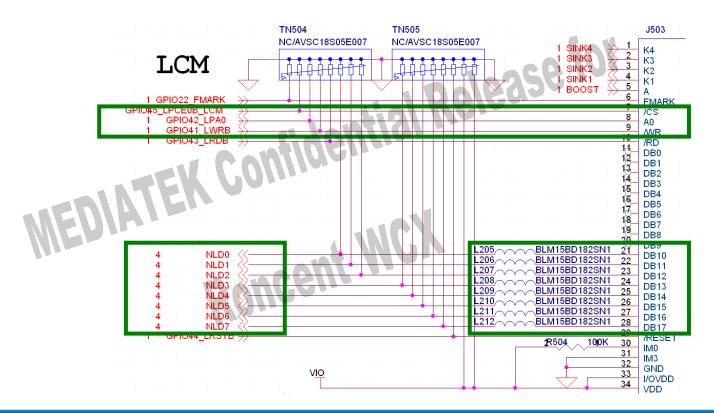

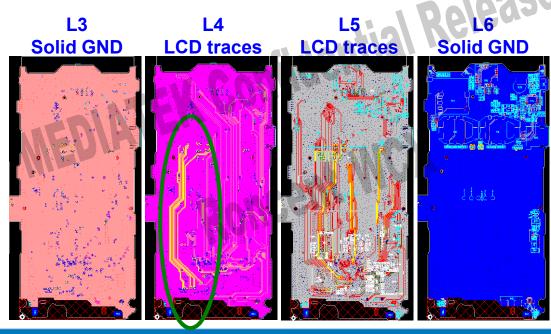

## LCM interface (1/2)

- Suggest adding series beads or EMI filter on LCD data pins (NLD0-NLD7)

- Use inner layer for LCD trace routing with GND shielding

#### LCM interface (2/2)

- Short and inner layer trace routing

- Solid ground around signal traces

- Avoid parallel with other traces

- Short and copper FPC or add series beads or EMI filter

### Tearing-solving & Performance-guaranteed nfidential B Settings in 6253

LCD\_write\_cycles should be small than or equal to 9/7 when QVGA/WQVGA display under 52MHz LCD clock settings.

| LCD resolution           |        |         |         |         |        |        |        |          |      |

|--------------------------|--------|---------|---------|---------|--------|--------|--------|----------|------|

| width                    | 240    |         |         |         |        |        |        |          |      |

| height                   | 320    |         |         |         | f _ 10 |        |        |          |      |

| pixel per frame          | 76800  |         |         |         | . 301  |        |        |          |      |

|                          | tearin | g-free( | 75Hz) . | Safe zo | ne wh  | en QVO | A in a | ll scena | ario |

| LCD write cycles (cycles | 3      | 4       | 5       | 6       | 7      | 8      | 9      | 10       |      |

| AHB_freq (MHz)           | 52     | 52      | 52      | 52      | 52     | 52     | 52     | 52       |      |

| LCD write time (ns)      | 57.69  | 76.92   | 96.15   | 115.38  | 134.62 | 153.85 | 173.08 | 192.31   |      |

| frame update time (ms)   | 8.86   | 11.82   | 14.77   | 17.72   | 20.68  | 23.63  | 26.58  | 29.54    |      |

|                          |        |         |        |         |        |        |        |        | _      |

|--------------------------|--------|---------|--------|---------|--------|--------|--------|--------|--------|

| LCD resolution           |        |         |        |         |        |        |        |        |        |

| width                    | 240    | 1110    | N      |         |        |        |        |        | ]      |

| height                   | 400    |         |        |         |        |        |        |        | ]      |

| pixel per frame          | 96000  |         |        |         |        |        |        |        | 1      |

|                          | tearir | ng-free | (75Hz) | Safe zo | one wh | en WQ  | VGA in | all sc | enario |

| LCD write cycles (cycles | 3      | 4       | 5      | 6       | 7      | 8      | 9      | 10     |        |

| AHB_freq (MHz)           | 52     | 52      | 52     | 52      | 52     | 52     | 52     | 52     |        |

| LCD write time (ns)      | 57.69  | 76.92   | 96.15  | 115.38  | 134.62 | 153.85 | 173.08 | 192.31 |        |

| frame update time (ms)   | 11.08  | 14.77   | 18.46  | 22.15   | 25.85  | 29.54  | 33.23  | 36.92  |        |

#### Memory interface (EMI)

- Place memory close to MT6253 memory pins

- Short ,inner layer and shielded trace routing

- Solid ground around signal traces

- Avoid parallel with other traces

- Separated from other signal traces

#### FM de-sense debug check list (1/2)

- Check if above rules are followed

- Check original performance

MEDIAIEN Jan

- Check conductive performance

- Remove FM ANT series cap and inductor

- Use external 2.8V supply

- Use external 32KHz

- Remove external R/L series cap

- Use external I2C

- Check earphone jack

- tial Release for Modify EINT (earphone detection) to turn on FM w/o earphone

- Remove series components on FM\_ANT neighbor pins

- Remove FM ANT neighbor pins Roncent WCX

#### FM de-sense debug check list (2/2)

- Check LCM

- Shield LCM FPC

MEDIAIEN Jon

- Shield LCM frame

- Remove LCM

- Shield LCM connector pins

- Add extra series bead on LCM connector pins

Roncent WCX

- Check memory shielding case

- Improve grounding

- Check keypad

- Improve grounding

- dential Release for Add extra series bead or bypass cap

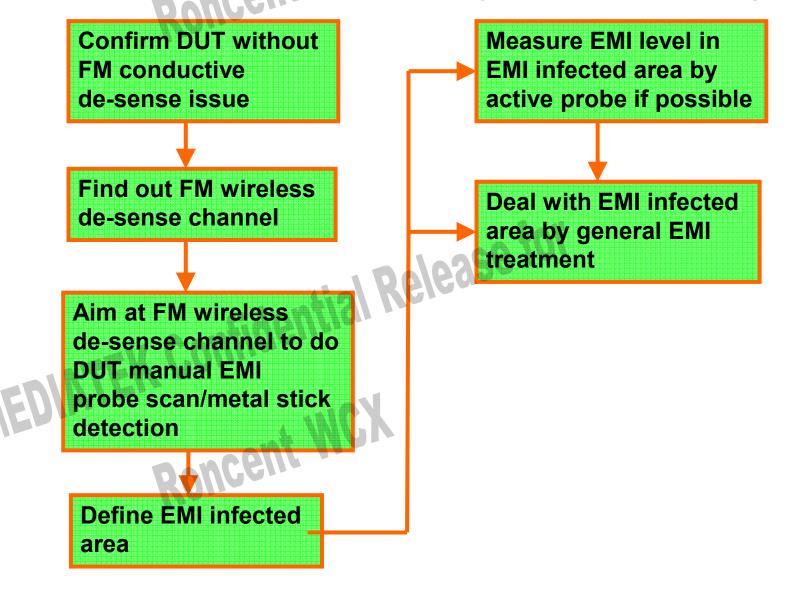

## FM wireless de-sense debug trick and flow (1/3) B

#### Traditional method

- Human ear test to find out FM de-sense channel

- Use EMI probe to search possible interference source located in de-sense channel

- Try to deal with possible interference source by shielding, attenuation, bypass, rework, etc. to confirm interference source

#### New method

- Human ear test to find out FM de-sense channel

- Use a metal stick to touch component and check if any human ear performance degradation in de-sense channel at the same time. If degradation is existent, it is a possible interference source

- Try to deal with possible interference source by shielding, attenuation, bypass, rework, etc. to confirm interference source

## FM wireless de-sense debug trick and flow(2/3)<sup>tial B</sup>

|                                                    | Traditional method | New method |

|----------------------------------------------------|--------------------|------------|

| Min. detection area                                | Large              | Small      |

| Confirmation way                                   | Indirect           | Direct Win |

| Rework effort for confirmation (period voice case) | Large              | No Win     |

| Manual scan time                                   | Short Wil          | Long W     |

| Instrument requirement                             | Yes                | No Win     |

| EMI source level/signal type indentify             | Medium Wil         | Z Low      |

| EMI source location accuracy and speed             | Low V              | High Win   |

| Dougelle                                           |                    | W          |

#### FM wireless de-sense debug trick and flow(3/3) | | | |

# MEDIAIEN Roncent WCX

# Audio Interface Design 2.5mm/3.5mm Earphone • Mini USB Earphone

Roncent MC

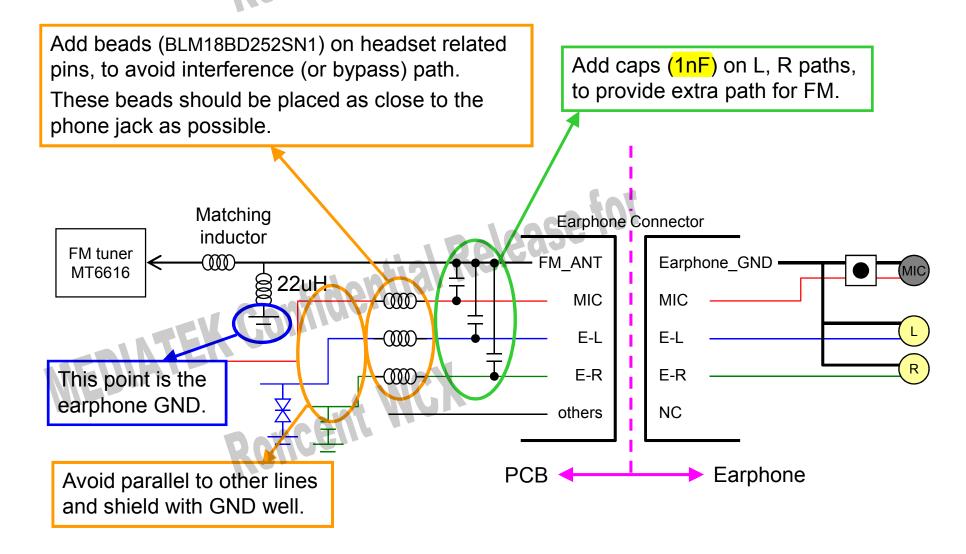

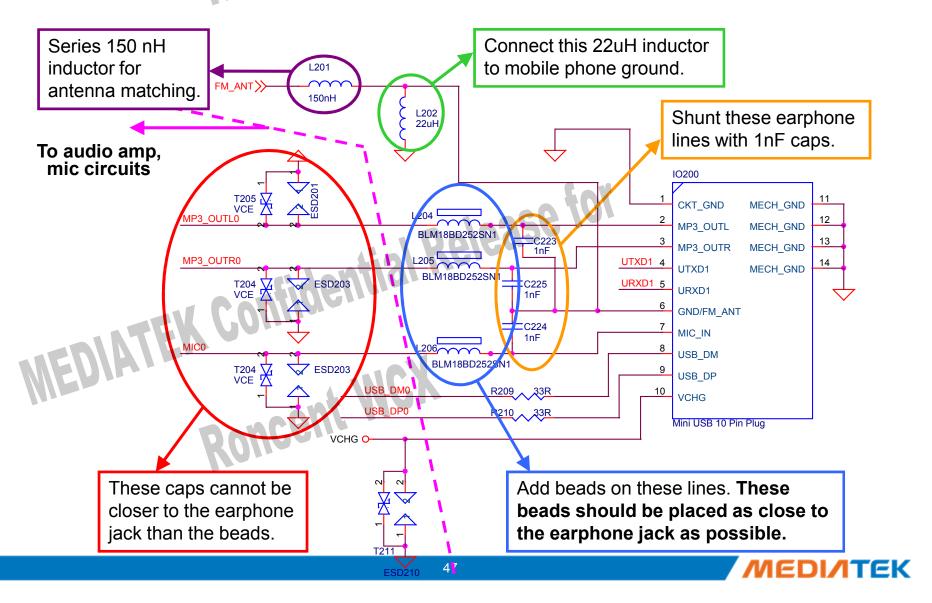

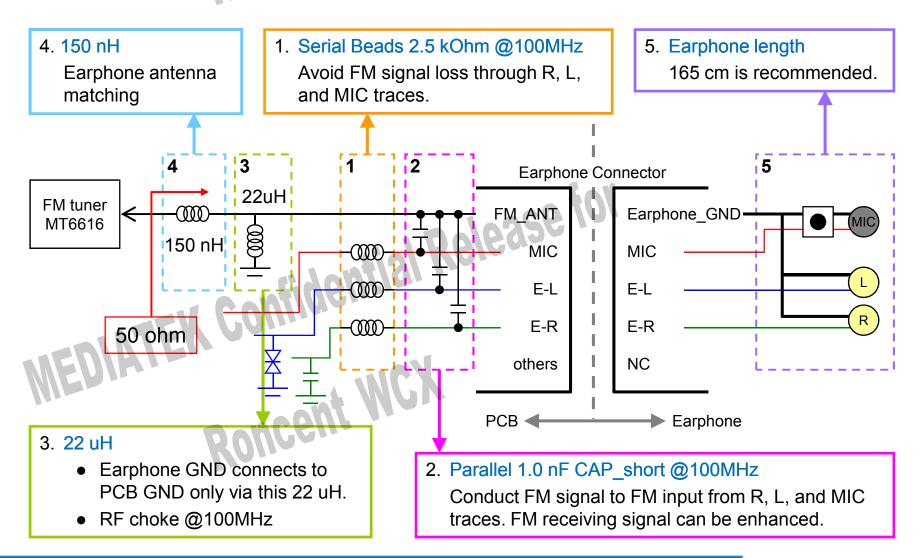

# Audio Interface Design Guidelines

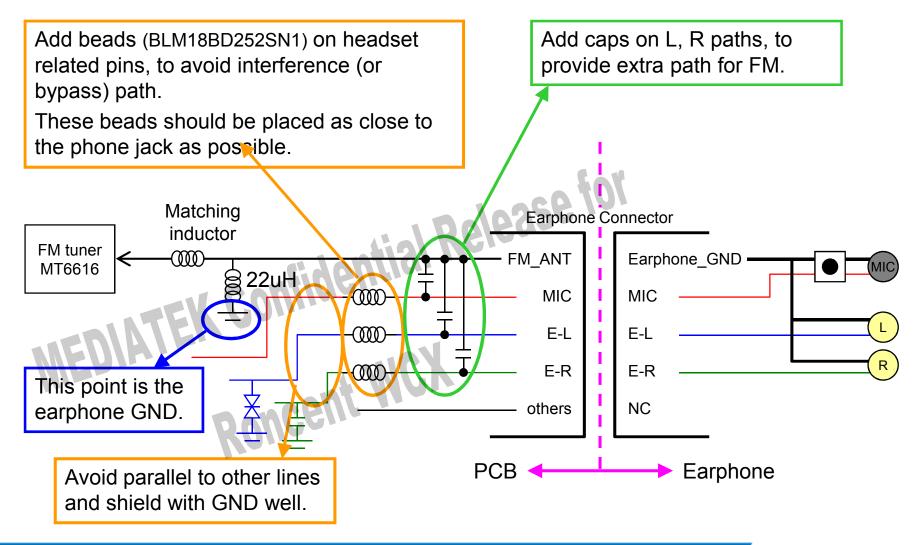

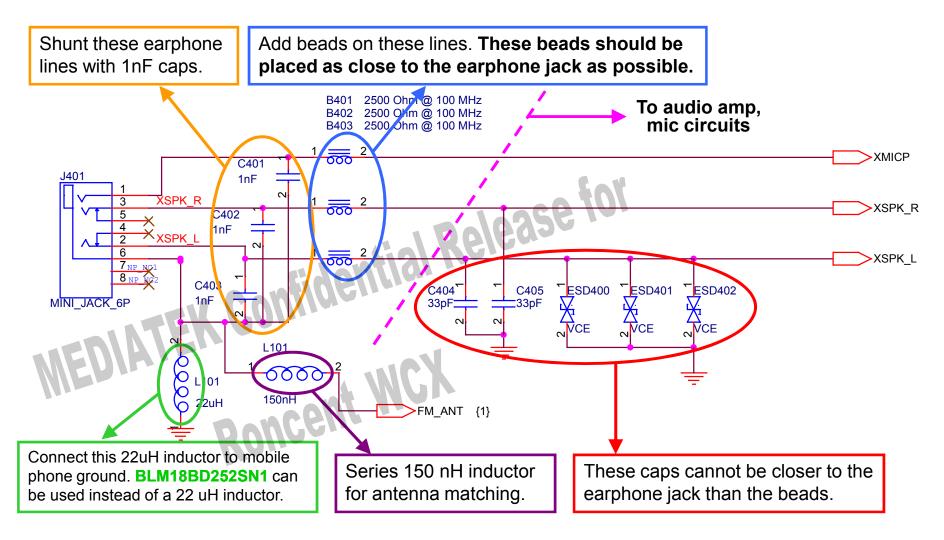

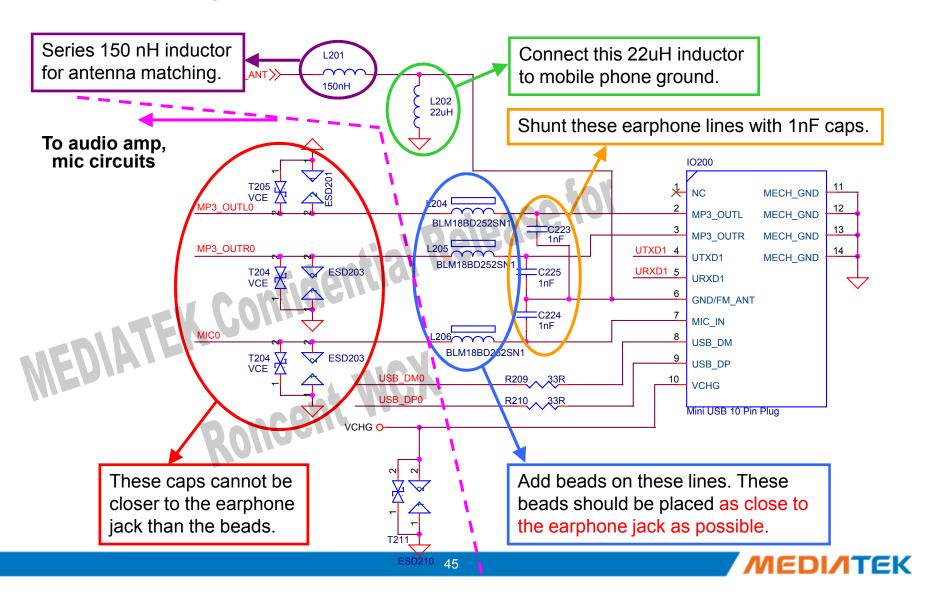

- On earphone pins AFL, AFR, and MIC:

- Place 1 nF shunt capacitors (shunt to earphone GND pin) closest to the earphone jack.

To improve earphone echo performance, connect the 3 capacitors from each pin to the earphone GND pin separately. (See next page.)

- Place the BLM18BD252SN1 series bead second closest to the earphone jack.

- No other components can be closer to the earphone jack.

Roncent WCX

- Earphone GND wire (FM\_ANT) should not be connected to the earphone connector shell.

- An earphone longer than 150 cm is recommended for better performance.

#### **Audio Interface Design Concept**

Confidential B

### Wireless Sensitivity Enhancement

Each earphone suggestions improves wireless sensitivity significantly. The following table shows the improvement amount based on MTK's experiments.

| tial Release                                                | Improvement amount |

|-------------------------------------------------------------|--------------------|

| Series beads on earphone AFL, AFR, and MIC pins             | 14.5 dB            |

| 1 nF shunt cap between earphone AFL, AFR, MIC, and GND pins | 2~3 dB             |

| Earphone length > 150 cm                                    | 1~2 dB             |

# MEDIAIEN Son Roncent WCX

2.5mm/3.5mm Earphone Design

MEDIATEK Confidential Release Roncent WCX

### Audio Interface Reference Circuit (2.5mm or 3.5mm Earphone Jack)

# Mini USB Earphone Design With only 1 GND pin on IO connector With 2 GND pins on IO connector

- Roncent WCX

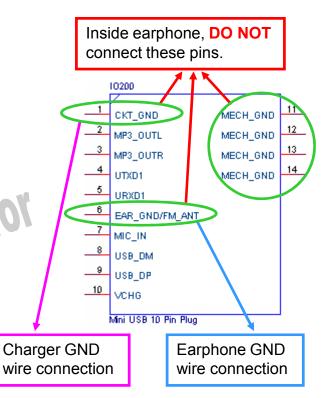

# Mini USB IO Connector Design Recommendation: Confidential B Only 1 GND Pin on IO Connector

#### **Accessory interior design suggestion**

EDIAIEN OO!

- The earphone GND wire MUST be used for the FM antenna. Inside the earphone, the GND wire CANNOT be connected to any other wire or to the outer shell in any way. Other wires inside the earphone CANNOT be connected to PCB GND.

- The 22uH inductor cannot tolerate high current. For high current application, such as a charger, connect the charger GND wire inside the charger to both the GND/FM\_ANT pin and the charger outer shell.

- In this example, the earphone GND wire is connected to IO connector pin6, and the charger GND wire is connected to pin6 and the charger outer shell.

Charger: Connect these pins.

Earphone: **DO NOT** connect these pins.

Earphone GND wire connection. Charger GND wire connection.

#### IO connector pin description

| IO pin name | Function                                                                                                          | Notes for PCB design                                                                                 |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| GND/FM ANT  | GND for all Mini USB accessories and FM antenna.                                                                  | CANNOT be directly connected to PCB ground. MUST be connected to PCB ground through a 22uH inductor. |  |  |  |  |

| MECH_GND    | 4 outer shell pins of the IO connector. Mainly used for better connector strength. Can also serve as charger GND. | These 4 pins are directly connected to PCB ground.  DO NOT connect these pins to the GND/FM_ANT pin. |  |  |  |  |

### **Audio Interface Reference Circuit: Only 1 GND Pin on IO Connector**

IEDIAIEN SSI

#### Mini USB IO Connector Design Recommendation: Confidential B 2 GND Pins on IO Connector

#### **Accessory interior design suggestion**

DIVIEW AND

- The earphone GND wire MUST be used for the FM antenna. Inside the earphone, the GND wire CANNOT be connected to any other wire or to the outer shell in any way. Other wires inside the earphone CANNOT be connected to PCB GND.

- The 22uH inductor cannot tolerate high current. For high current applications, such as a charger, use another IO connector pin if available. The charger GND wire inside the charger can also be connected to the charger outer shell.

- In this example, the earphone GND wire is connected to IO connector pin6, and the charger GND wire is connected to pin1 and possibly the charger outer shell as well.

#### IO connector pin description

| IO connector pin d | escription                                                                                                            | wire connection wire connection                                                                      |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| IO pin name        | Function                                                                                                              | Note for PCB design                                                                                  |  |  |  |  |  |

| EAR_GND/FM_ANT     | Earphone GND, also FM antenna.                                                                                        | CANNOT be directly connected to PCB ground. MUST be connected to PCB ground through a 22uH inductor. |  |  |  |  |  |

| CKT_GND            | GND for Mini USB accessory, with large GND current.                                                                   | This pin is directly connected to PCB ground.  DO NOT connect this pin to the EAR_GND/FM_ANT pin.    |  |  |  |  |  |

| MECH_GND           | 4 outer shell pins of the IO connector. Mainly used for better connector strength. Can also be served as charger GND. | These 4 pins are directly connected to PCB ground.  DO NOT connect these pins to EAR_GND/FM_ANT.     |  |  |  |  |  |

### **Audio Interface Reference Circuit: 2 GND Pins on IO Connector**

#### **Component Replacement Suggestions**

Series beads on earphone pins AFL, AFR, and MIC

VEDIAIEN VVII

- Suggested: 0603-size BLM18BD252SN1 bead

However, if board space is limited, 0402-size bead BLM15BD182SN1 or BLM15HD182SN1 can be used instead.

- Inductor connecting earphone GND wire to board GND

- Suggested: 22 uH inductor or BLM18BD252SN1 bead

However, if the earphone GND pin serves as the only GND path for the charger, then

this component must be able to tolerate high current. The components in the table below

can be used instead.

| Murata<br>part number | Inductor value | Size | Self-resonant frequency | Rated current | Notes                                                                                                                      |

|-----------------------|----------------|------|-------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------|

| LQH2MCN1R0M02         | 1.0 uH         | 0603 | 100 MHz                 | 485 mA        |                                                                                                                            |

| LQM21PN1R0MC0D        | 1.0 uH         | 0805 | 90 MHz                  | 800 mA        |                                                                                                                            |

| LQM21PNR47MC0D        | 0.47 uH        | 0805 | 100 MHz                 | 1100 mA       | Usable, but its wireless performance is the worst among the three. Not recommended unless such a high current is required. |

# FM Design Checklist

| Item      | Done! | Checkpoint                                                                                                                                                              |

|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         |       | Series beads are placed on the AFL, AFR, and MIC pins of the earphone jack.                                                                                             |

| 2         |       | 1 nF shunt caps are placed between the AFL, AFR, MIC, and GND pins of the earphone jack.                                                                                |

| 3         |       | The earphone is longer than 150 cm.                                                                                                                                     |

| 4         |       | The FM_2V8 bypass cap is placed beside pin34, and the FM_2V8 feeding network routed is properly.                                                                        |

| 5         |       | Place 3300hm close to Pin30,41,42                                                                                                                                       |

| <b>E6</b> | 10    | The FM antenna path is routed using a $50\Omega$ RF trace.                                                                                                              |

| 7         |       | Follow the FM system layout guide as previous slides . Especially , place MT6616 far away from LCM traces and memory. Connect VBAT trace directly to battery connector. |

| 8         |       | Earphones: Follow MTK's suggestion for GND connection and pin assignment on PCB and inside earphone.                                                                    |

If you require MTK's assistance in FM design, please prepare this checklist and submit it along with schematics, layout files and earphone schematics/data sheet.

### **More Detailed FM Earphone Antenna Illustrations** tial Release

- י ation of FM earphone antenna FM earphone antenna pin definition FM earphone antenna troubleshooting

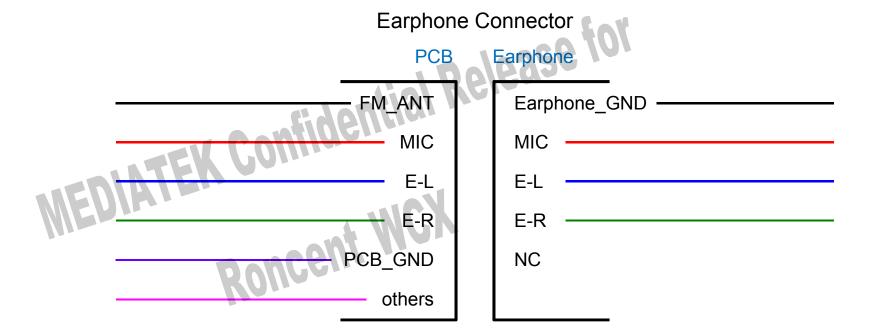

# Illustration of FM Earphone Antenna (1/2)

Confidential B

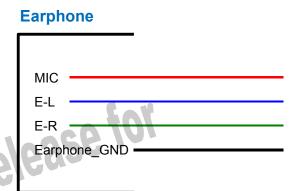

- On next page, there is an illustration to explain the respective purposes of each components. It can help customers to know how to enhance FM wireless performance.

- Besides FM schematics, wrong earphone pin definition also destroys FM wireless performance.

- Notice that the only one path from Earphone\_GND to PCB\_GND is via FM\_ANT Pin and 22uH. If there are another paths existing, FM receiving signal would degrade seriously. This issues frequently happens on customers' projects.

- Four pins are enough on earphone including R, L, MIC, and Earphone\_GND.

- Only Earphone\_GND can be used as FM Antenna.

Roncent WCX

Place all FM related components near earphone jack in PCB layout.

#### Illustration of FM Earphone Antenna (2/2)

:DIATEN Jan

Confidential B

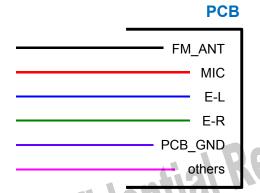

#### FM Earphone Antenna Pin Definition (1/3) Confidential B

The following illustrates the correct pin definition for the FM earphone antenna:

#### FM Earphone Antenna Pin Definition (2/3)

Confidential B

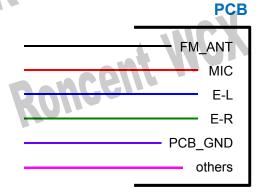

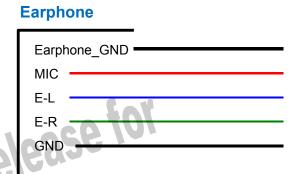

- Some incorrect pin definitions

- Case 1: Floating FM\_ANT pin

Case 2: Earphone\_GND connects to both FM\_ANT pin and PCB\_GND

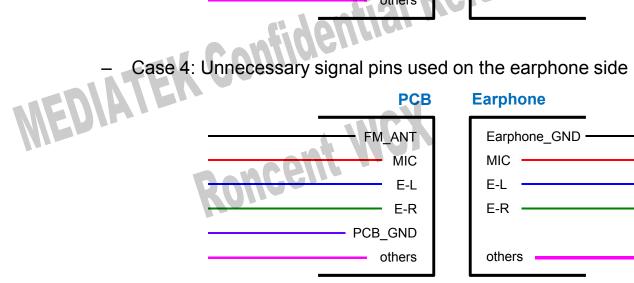

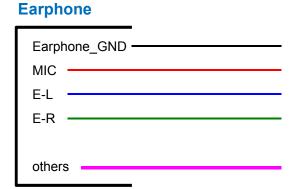

#### FM Earphone Antenna Pin Definition (3/3)

Confidential B

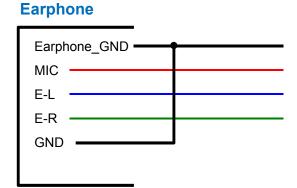

- Some incorrect pin definitions

- Case 3: Unnecessary GND pin used on the earphone side

Confidential B

#### FM Earphone Antenna Troubleshooting

- Simple troubleshooting techniques:

- a. Check that only four earphone pins are used. (Case 3, Case 4)

- b. Remove the 22 uH inductor.

- c. Plug in the earphone.

- d. Use a digital multimeter to check whether the connections between PCB\_GND, FM\_ANT pin, and Earphone\_GND pin are OPEN or SHORT.

|                              | sidential Rel           | ease for                      |         |

|------------------------------|-------------------------|-------------------------------|---------|

| FM_ANT<br>to<br>Earphone_GND | FM_ANT<br>to<br>PCB_GND | PCB_GND<br>to<br>Earphone_GND | Issue   |

| SHORT                        | OPEN                    | OPEN                          | Correct |

| OPEN ROM                     | OPEN                    | SHORT                         | Case 1  |

| SHORT                        | SHORT                   | SHORT                         | Case 2  |

MEDIATER MCX

AREDIATEK

Confidential B

# MT6616 Design Guide - Bluetooth

Copyright © MediaTek Inc. All rights reserved.

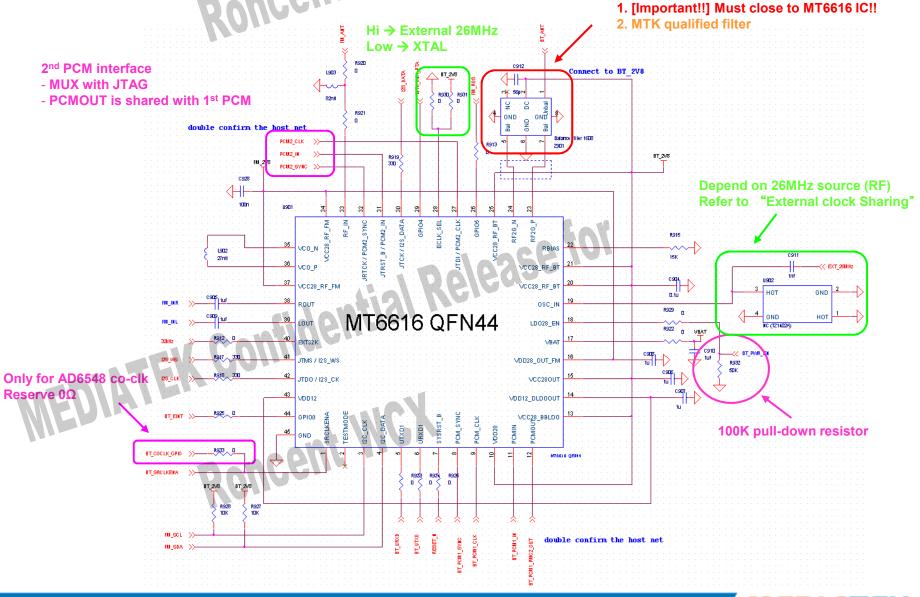

# Reference Circuit – MT6616 BT

#### Confidential B

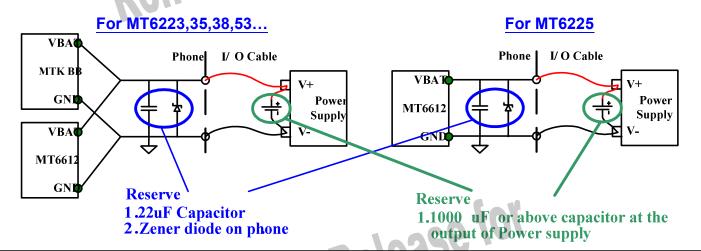

### MT6616 Reference Design – Power Protection

Because VBAT is directly applied, battery voltage protection should be applied:

Design notice in Phone side:

1. Add 22uF capacitor.

EDIAIEN aan

2. Add Zener diode (5.6V) to protect the IC against low frequency voltage surge. Put it between battery connector and MT6612.

Notice: If using IO connector or test point to supply VBAT for download, manufacture, or repair, should let VBAT trace passing zener diode and 22uF capacitor before entering IC. Notice: Using 5.6V zener will introduce some leakage when VBAT = 4.2V.

ex. 5.6V zener CZRU52C5V6, will have extra 5uA leakage.

Design notice in Power Supply side:

Add 1000uF (or above) capacitor at the output of the power supply to reduce the voltage bounce caused by long power cable. And the power cable should be as short as possible. Also add 1000uF (or above) capacitor at the end of power cable (near phone side).

### Baseband GPIO Assignment for MT6616 (1/2)

#### BT/Baseband Interface assignment

- In the BT/BB interface assign phase, the GPIO should be arranged carefully. Do not use GPIO with conflict power domain (for example, camera power domain).

- Example:

| AD17 | URXD2    | VDD33_NOR<br>M2 | VSS33_NO<br>RM2 | VDDK C | VSSK |

|------|----------|-----------------|-----------------|--------|------|

| U16  | SYSRST_B | VDD33_NOR<br>M2 |                 | VDDK   | VSSK |

| AD18 | URTS1    | VDD33_NOR<br>M2 | VSS33_NO<br>RM2 | VDDK   | VSSK |

| T16  | EINT0    | VDD33_NOR<br>M2 | VSS33_NO<br>RM2 | VDDK   | VSSK |

| AD19 | UCTS1    | VDD33_NOR<br>M2 | VSS33_NO<br>RM2 | VDDK   | VSSK |

|      | Roncer   | t MC            |                 |        |      |

Confidential B

### Baseband GPIO Assignment for MT6616 (2/2)

Reserve the default (hardware) pull-down GPIO to LDO28EN pin to avoid unwanted leakage.

| <b>GPIO</b> | GPIO +0400h GPIO pull-up/pull-down select register 1 |        |        |        |        |        |       |       |       |       |       |       |       |       |       |       |

|-------------|------------------------------------------------------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit         | 15                                                   | 14     | 13     | 12     | 11     | 10     | 9     | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| Name        | GPIO15                                               | GPIO14 | GPIO13 | GPIO12 | GPIO11 | GPIO10 | GPIO9 | GPIO8 | GPIO7 | GPIO6 | GPIO5 | GPIO4 | GPIO3 | GPIO2 | GPIO1 | GPIO0 |

| Туре        | RW                                                   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset       | $\times$                                             | 0      | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

0: Default (after reset state) is pulled-down

| <b>GPIO</b> | PIO +0440h GPIO pull-up/pull-down select register 2 |        |        |          |        |        |        |        |        |        |        |        |        |        |        |          |

|-------------|-----------------------------------------------------|--------|--------|----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------|

| Bit         | 15                                                  | 14     | 13     | 12       | 11     | 10     | 9      | 8      | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0        |

| Name        | GPIO31                                              | GPIO30 | GPIO29 | GPIO28   | GPIO27 | GPIO26 | GPIO25 | GPIO24 | GPIO23 | GPIO22 | GPIO21 | PGIO20 | GPIO19 | GPIO18 | GPIO17 | GPIO16   |

| Туре        | R/W                                                 | R/W    | RW     | R/W      | RM     | R/W      |

| Reset       | 0                                                   | 0      | 1      | $\times$ | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      | $\times$ |

Do not use → 1: Default (after reset state) is pulled-high

#### Reference assignment

| MT6616  | MT6238 | MT6235 | MT6223 | MT6229 | Notes                      |

|---------|--------|--------|--------|--------|----------------------------|

| LDO28EN | GPIO29 | GPIO39 | GPIO30 | GPIO9  | Do not use pulled-up GPIO! |

| EXT32K  | GPIO77 | GPIO27 | GPIO21 | GPIO36 |                            |

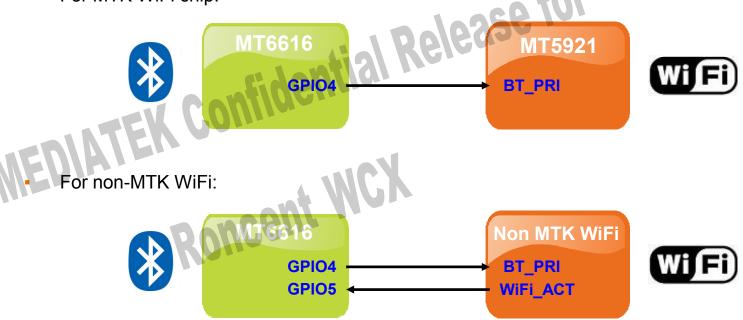

#### **MT6616 PTA Interface**

MT6616 can support 1-wire PTA interconnection for MTK WiFi co-existence.

| MT6616's GPIO for PTA | GPIO4 | GPIO5 (FM_RDS) |

|-----------------------|-------|----------------|

| MTK 1-Wire            | V     |                |

| Standard 2-Wire       | V     | V              |

For MTK WiFi chip:

# Dual-PCM for G+C Application

|      | MT6616 Pin number (QFN-44) |    |  |  |  |  |  |

|------|----------------------------|----|--|--|--|--|--|

|      | 1st PCM 2nd PCM            |    |  |  |  |  |  |

| CLK  | 9                          | 27 |  |  |  |  |  |

| SYNC | 8                          | 32 |  |  |  |  |  |

| IN   | 11                         | 31 |  |  |  |  |  |

| OUT  | 12                         | 12 |  |  |  |  |  |

- PCMOUT is shared for 1<sup>st</sup> and 2<sup>nd</sup> PCM interface.

- To prevent from leakage, VIO of PCM for G- and C- modem should be the same.

- Reserve series-0Ω resistor on PCMOUT to C-network path.

- PCM format (CLK=128K, Short/Long sync, MSB/LSB, etc) setting should be same for G and C modem.

- GPIO configure should also be careful to prevent unwanted leakage.

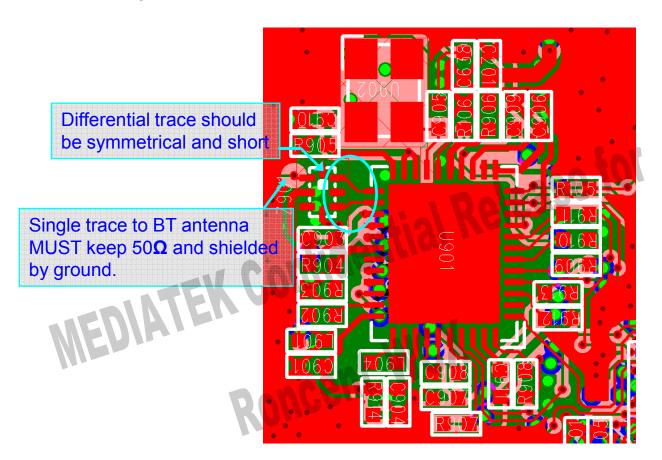

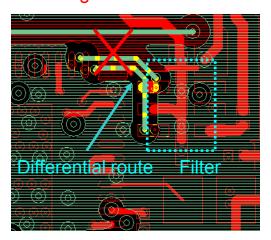

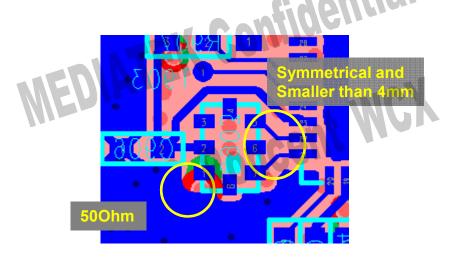

#### BT Part Layout Guideline (1/2)

Layout criterion:

BAD design example:

→Differential trace not symmetrical and long.

#### BT Part Layout Guideline (2/2)

#### **RF/Analog part:**

- Using qualified balance filter, need no external matching network.

- Balance port routing should be symmetrical and shorter than 4mm, while the single-end trace route should  $\overline{\text{keep }} 50\Omega$ .

#### **Power rail part:**

- Make star-connection at C905 (pin-15) for 2.8V power trace.

- Provide complete ground for power traces, do not route power traces in parallel with or crossing to digital or strong disturbance signals.

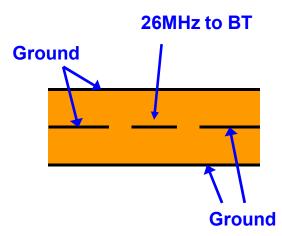

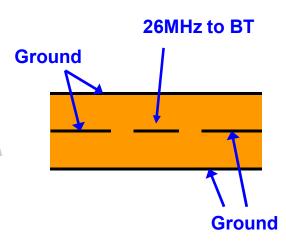

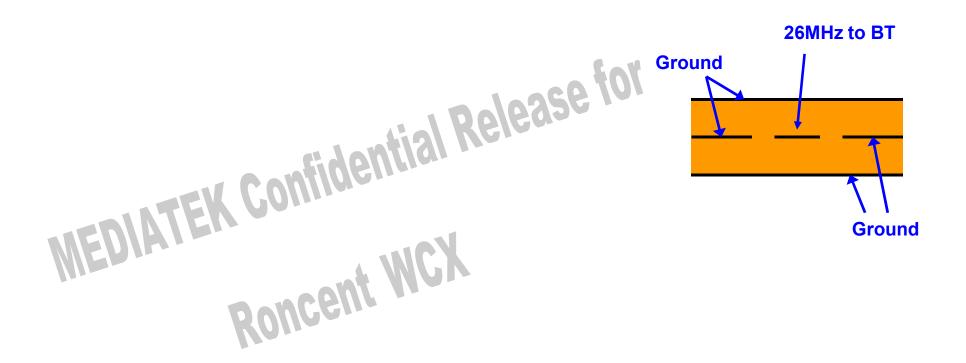

#### 26MHz from RF:

MUST be well shielded by ground.

No separate ground plane but add more ground via.

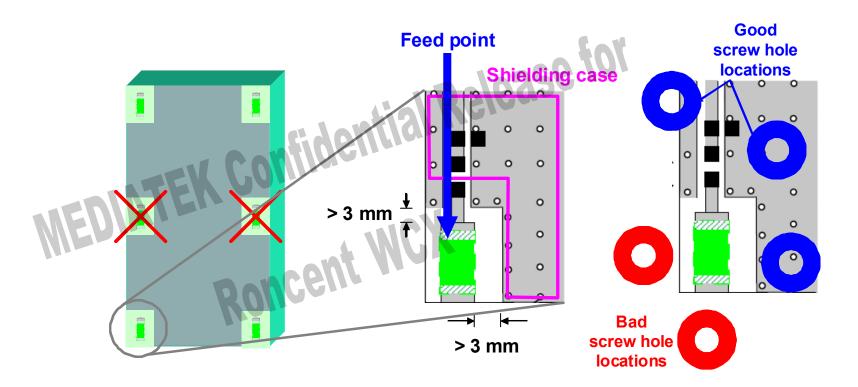

#### **BT Antenna Placement Guideline**

- Place the BT antenna at the corner of the PCB.

- The feed point is directly connected to the antenna.

- Reserve enough distance between the antenna, ground and the shielding case.

- Ground blue screw holes, and don't ground red screw holes.

MEDIATER

Confidential B

# **External Clock Sharing**

Copyright © MediaTek Inc. All rights reserved.

# External Clock Sharing

- MT6253

- AD6548

- MT6268+MT6160 (Othello-3)

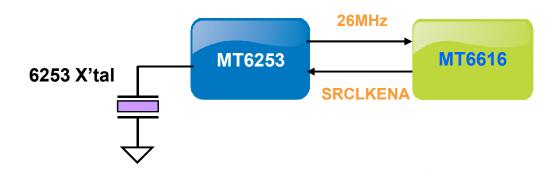

#### Shared External Clock – MT6253 (1/2)

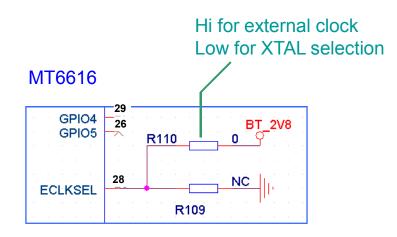

- 1. Reserve Xtal footprint for backup.

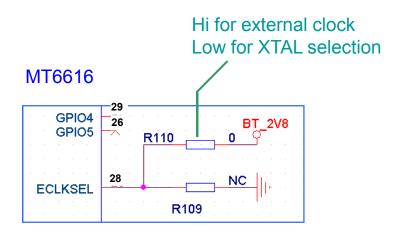

- 2. Reserve pull-up and pull-down resistor on ECLKSEL pin to select external or X'tal clock.

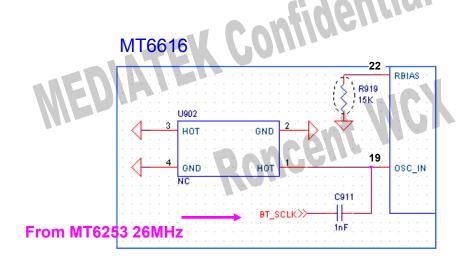

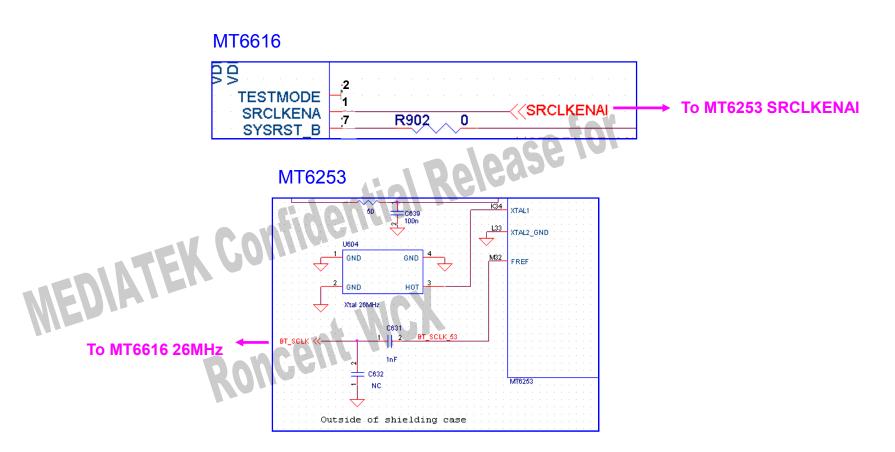

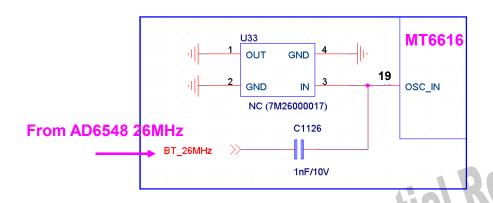

#### Shared External Clock – MT6253 (2/2)

- 3. Connect SRCLKENA (clock request) to MT6253's SRCLKENAI

- 4. Connect 26MHz output from MT6253 to 6616 via 1nF AC couple capacitor.

#### Special Notes for MT6253 Co-clock Layout

- Follow original design rule for MT6253 and BT if not mentioned.

- BT close to RF transceiver! (Highly recommended)

- 26MHz trace routing rule

- As short as possible

- Good shielding with ground to avoid noise & coupling

- MEDIATEK Confidential Release for Using MTK recommended MT6253 Xtal.

for MT6253+6616 co-clock

Reduce BT Xtal cost (0.13USD) without any effort!

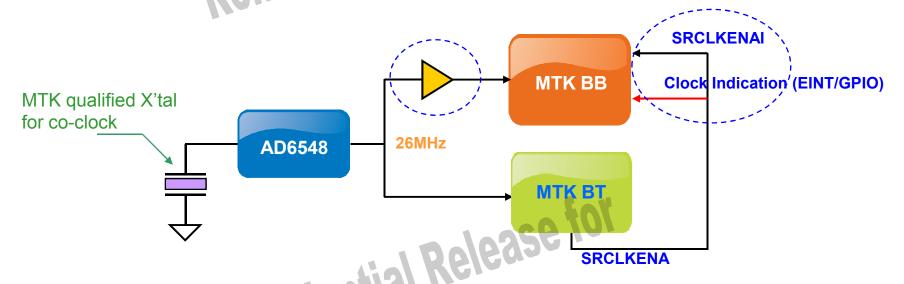

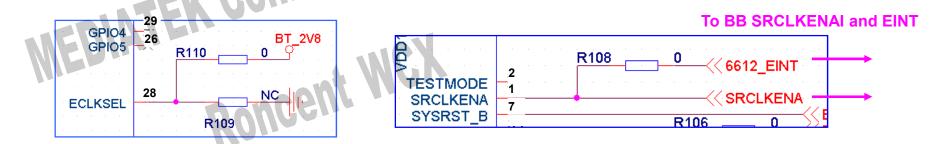

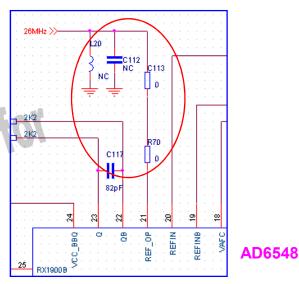

#### Shared External Clock – AD6548 (1/3)

#### Confidential B

1. Reserve pull-up and pull-down resistor on ECLKSEL pin to select external or X'tal clock.

2. Connect SRCLKENA to BB's SRCLKENAI and EINT/GPIO (please follow the table for reference assignment)

### Shared External Clock – AD6548 (2/3)

#### Assignment for Clock Indication (EINT/GPIO):

|        | EINT # | BB Pin | Pin Name | IO Power    | GPIO<br>MODE 0 | GPIO<br>MODE 1 | GPIO<br>MODE 2 | GPIO<br>MODE 3 | Edge/Level<br>Trigger | HW<br>Debounce |

|--------|--------|--------|----------|-------------|----------------|----------------|----------------|----------------|-----------------------|----------------|

| MT6225 | EINT4  | T3     | GPIO0    | VDD33       | GPIO0          |                |                | EINT4          | Edge/Level            | Yes            |

|        | EINT5  | U4     | GPIO1    | VDD33       | GPIO1          |                |                | EINT5          | Edge/Level            | Yes            |

|        | EINT6  | T4     | GPIO2    | VDD33       | GPIO2          |                | UCTS1          | EINT6          | Edge/Level            | Yes            |

|        | EINT7  | U5     | GPIO3    | VDD33       | GPIO3          | BSI_RFIN       | URTS1          | EINT7          | Edge/Level            | Yes            |

| MT6223 | EINT2  | C11    | EINT2    | VDD33       | GPIO42         | EINT2          | MIRQ           |                | Edge/Level            | Yes            |

|        | EINT3  | D11    | EINT3    | VDD33       | GPIO43         | EINT3          | 11.4           |                | Edge/Level            | Yes            |

|        | EINT4  | R8     | JTRST_B  | VDD33       | GPIO26         | JTRST_B        | EINT4          |                | Edge/Level            | Yes            |

|        | EINT5  | P8     | JTDI     | VDD33       | GPIO27         | JTDI           | EINT5          |                | Edge/Level            | Yes            |

|        | EINT6  | T9     | JTMS     | VDD33       | GPIO28         | JTMS           | EINT6          |                | Edge/Level            | Yes            |

| MT6235 | EINT3  | E24    | EINT3    | VDD33       | GPIO44         | EINT3          | DRF_DATA       | IRQ2           | Edge/Level            | Yes            |

|        | EINT4  | E23    | EINT4    | VDD33       | GPIO45         | EINT4          | DRF_EN         | CLKM3          | Edge/Level            | Yes            |

|        | EINT5  | D23    | EINT5    | VDD33       | GPIO46         | EINT5          | EDICK          |                | Edge/Level            | Yes            |

|        | EINT6  | D25    | EINT6    | VDD33       | GPIO47         | EINT6          | EDIWS          |                | Edge/Level            | Yes            |

|        | EINT7  | D24    | EINT7    | VDD33       | GPIO48         | EINT7          | EDIDAT         |                | Edge/Level            | Yes            |

| WIL    | EINT0  | T16    | EINT0    | VDD33_NORM2 | GPIO77         | EINT0          | CLKM4          |                | Edge/Level            | Yes            |

| MT6238 | EINT1  | AB17   | EINT1    | VDD33_NORM2 | GPIO78         | EINT1          | CLKM5          |                | Edge/Level            | Yes            |

|        | EINT2  | AC19   | EINT2    | VDD33_NORM2 | GPIO79         | EINT2          | DSP_GPO3       | TBTXEN         | Edge/Level            | Yes            |

|        | EINT3  | AC25   | EINT3    | VDD33_NORM2 | GPIO33         | EINT3          | DSP_GPO2       | TBTXFS         | Edge/Level            | Yes            |

|        | EINT4  | AD24   | EINT4    | VDD33_NORM2 | GPIO34         | EINT4          | DSP_GPO1       | TBRXEN         | Edge/Level            | Yes            |

|        | EINT5  | T17    | EINT5    | VDD33_NORM2 | GPIO35         | EINT5          | DSP_GP00       | TBRXFS         | Edge/Level            | Yes            |

|        | EINT6  | AE18   | EINT6    | VDD33_NORM2 | GPIO36         | EINT6          | EDIWS          |                | Edge/Level            | Yes            |

|        | EINT7  | AC20   | EINT7    | VDD33_NORM2 | GPIO37         | EINT7          | EDIDAT         |                | Edge/Level            | Yes            |

# Shared External Clock – AD6548 (3/3)

3. Please also reserve X'tal footprint for back-up. 4.

In AD6548 26MHz output, reserve LPF footprint and default use 0**Ω** connection.

5. Place clock buffer on 26MHz to BB path and connect buffer power to VTCXO.

VBT

BACKUP

MT6235B

—<⟨Keypad\_LED1

#### Special Notes for AD6548 Co-clock Layout Confidential B

- Follow original design rule for OG and BT if not mentioned.

- BT close to RF transceiver! (Highly recommended)

- 26MHz trace routing rule

- As short as possible

- Good shielding with ground to avoid noise & coupling

- Transceiver trace routing rule

- Have VCXO power good decouple and clean ground.

- Confidential Release Using MTK recommended OG Xtal and clock buffer

for AD6548+MT6612 co-clock only

BB cause additional 1mA idle current

Cost down 0.13USD

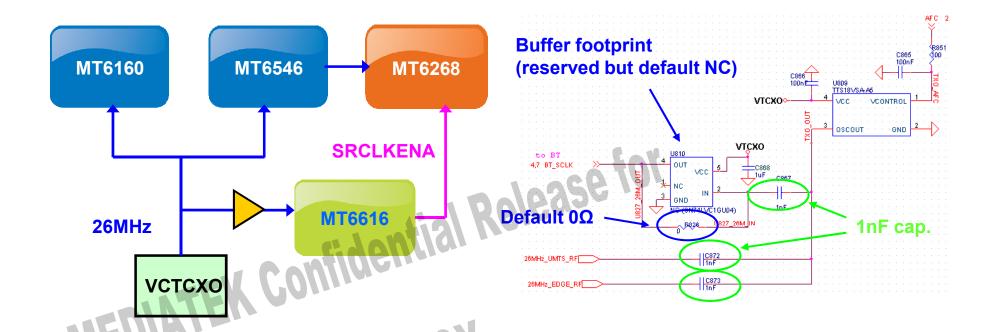

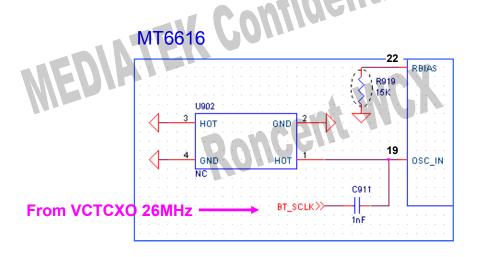

# Shared External Clock – MT6268 (1/2)

- Direct share VTCXO 26MHz output through 1nF AC couple cap.

- Reserve clock buffer footprint on BT path and default is  $0\Omega$ -through.

#### Shared External Clock - MT6268 (2/2)

- 1. Connect SRCLKENA (clock request) to MT6268's SRCLKENAI

- 2. Connect 26MHz output from VCTCXO to 6612 via 1nF AC couple capacitor.

# MT6616 TESTMODE SRCLKENAL SYSRST\_B TO MT6268 SRCLKENAL

- 3. Reserve Xtal footprint for backup.

- 4. Reserve pull-up and pull-down resistor on ECLKSEL pin to select external or X'tal clock.

### Special Notes for MT6268 Co-clock Layout

- Follow original design rule for MT6268 and BT if not mentioned.

- 26MHz trace routing to BT must be surrounded by ground to have good shielding.

- Reserve BT Xtal footprint.

# Shared External Clock – SW Configuration (1/4)

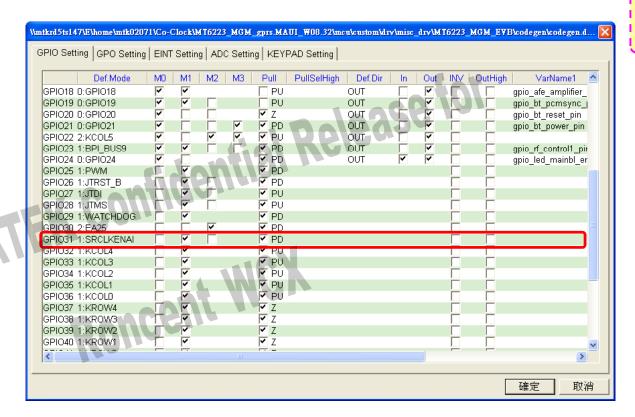

Step 1 (for MT6253 AND AD6548). Use Drv tool in Custom folder to configure clock request input should be configured as SRCLKENAI mode.

**MT6253 AND**

# Shared External Clock – SW Configuration (2/4)

For AD6548 clock sharing, need more steps to configure:

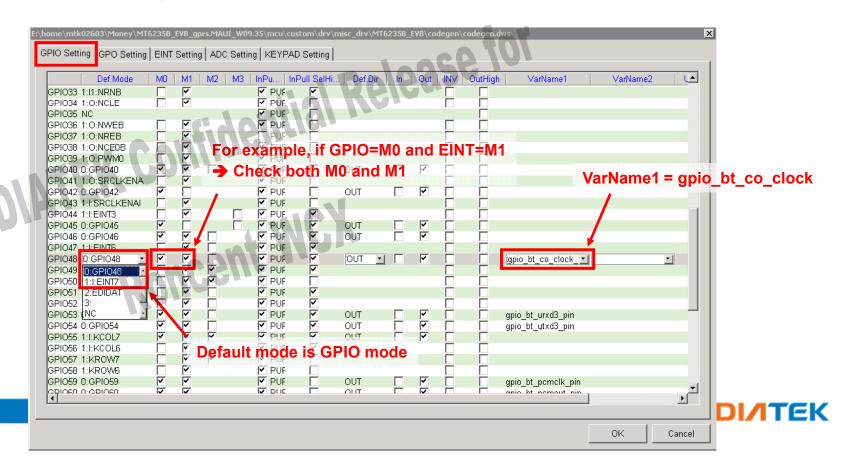

Step 2 (for AD6548). In GPIO setting page, set clock indication signal

AD6548 only

- → Def mode = GPIO

- → Check both GPIO and EINT mode (for example, if GPIO=M0 and EINT=M1 → then check M0 and M1)

- → VarName1 = gpio\_bt\_co\_clock

### Shared External Clock – SW Configuration (3/4)

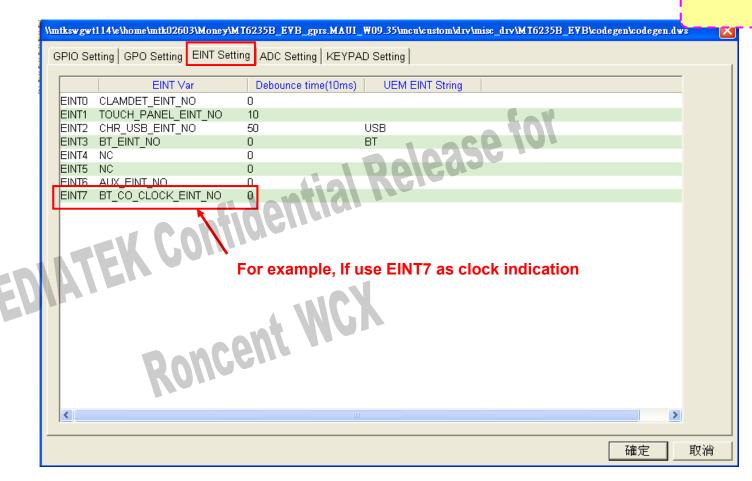

Step 3 (for AD6548). In EINT setting page, set the corresponding EINT Var as BT\_CO\_CLOCK\_EINT\_NO.

**AD6548** only

### Shared External Clock – SW Configuration (4/4)

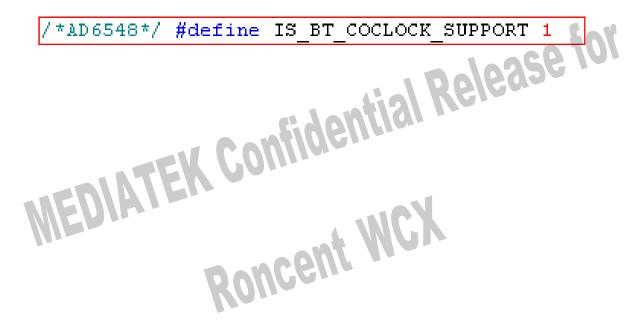

Step 4 (for AD6548).

Modified IS\_BT\_COCLOCK\_SUPPORT in the following .h file:

\mcu\custom\l1 rf\AD6548 CUSTOM\ l1d custom rf.h

as:

MEDIATEK

Confidential B

www.mediatek.com

Copyright © MediaTek Inc. All rights reserved.