# MT7981B

## Wi-Fi 6 Generation Router Platform: Datasheet

### Open Version

Version: 1.0

Release Date: 2024-03-25

Use of this document and any information contained therein is subject to the terms and conditions set forth in Exhibit 1.

This document is subject to change without notice.

## 1 Introduction

### 1.1 General Description

MT7981B is a highly integrated wireless network router SoC (System-on-Chip) used for high wireless performance, home entertainment, and home automation and so on.

MT7981B is fabricated with advanced silicon process and integrates a dual-core Arm® Cortex-A53 MPCore™ operating up to 1.3 GHz and more DRAM bandwidth. This SoC also includes a variety of peripherals, including SGMII, and USB3.0 (host) ports. To support popular network applications, MT7981B also implements two 2.5Gbps HSGMII Ethernet interface. MT7981B combines with a RF chip, they can provide dual-band concurrent chipset solution for Wi-Fi 6 AX3000 wireless router platforms.

Besides the connectivity features, the hardware-based NAT engine with QoS embedded in MT7981B transporting the audio/video streams in higher priority than other non-timely services also enriches the home entertainment application. The SFQ separating P2P sessions from audio/video ones so that MT7981B guarantees the streaming service.

With the advanced technology and abundant features, MT7981B is well positioned to be the core of next-generation smart Wi-Fi AP router and home gateway systems.

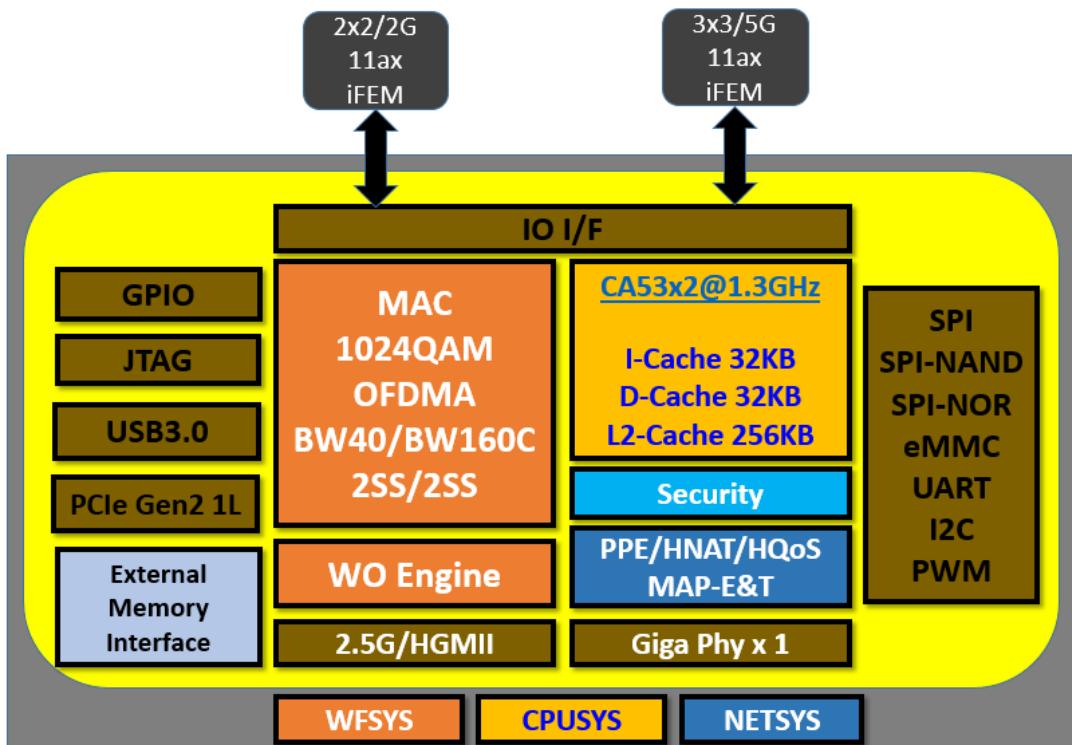

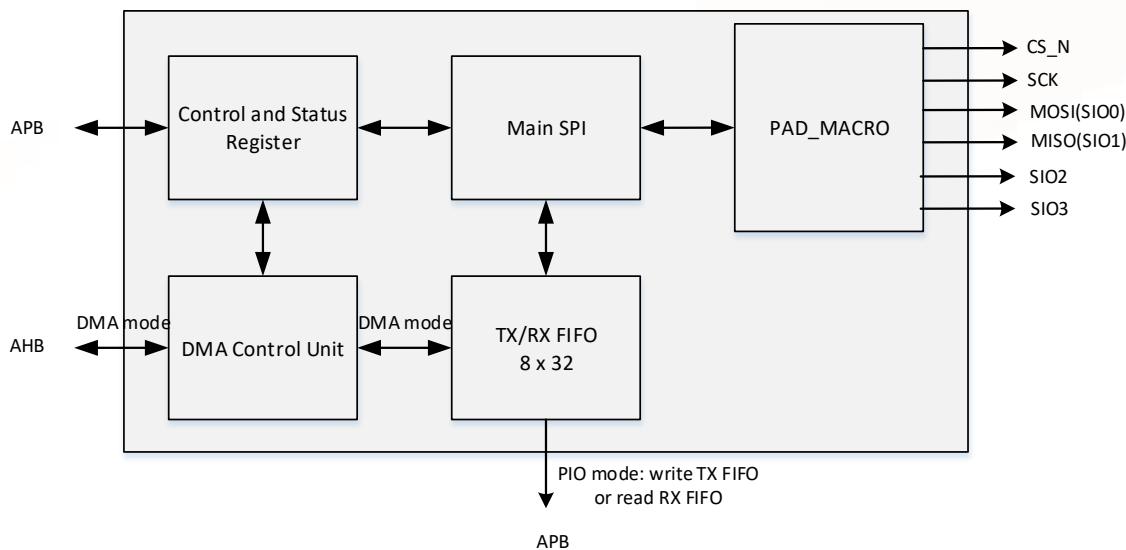

#### 1.1.1 Functional Block Diagram

Figure 1-1. MT7981B functional block diagram

## 1.2 Features

### 1.2.1 Platform Features

- AP MCU Subsystem

- Dual-core Arm® Cortex-A53 MPCore™ operating at 1.3 GHz

- NEON processing engine with advanced SIMD and floating-point extension

- 32KB L1 I-cache and 32KB L1 D-cache

- 256KB unified L2 cache

- Cryptography extension

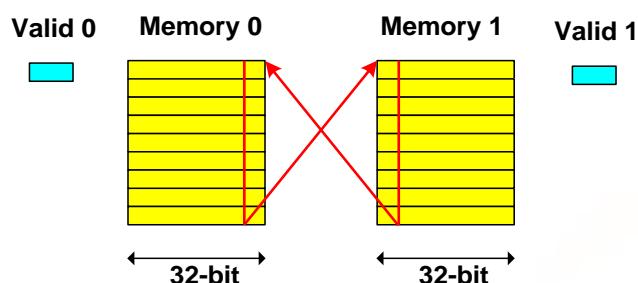

- Memory Interface

- 16-bit data bus width

- Memory clock up to DDR3/DDR4-2133

- Supports self-refresh/partial self-refresh mode

- Programmable slew rate for memory controller's IO pads

- Advanced bandwidth arbitration control

- Peripherals

- 1 USB3.0/USB2.0 (host)

- 1 PCIe Gen2 1-Lane interface

- UART for external devices and debugging interfaces

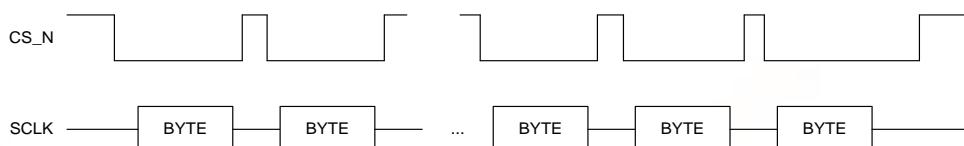

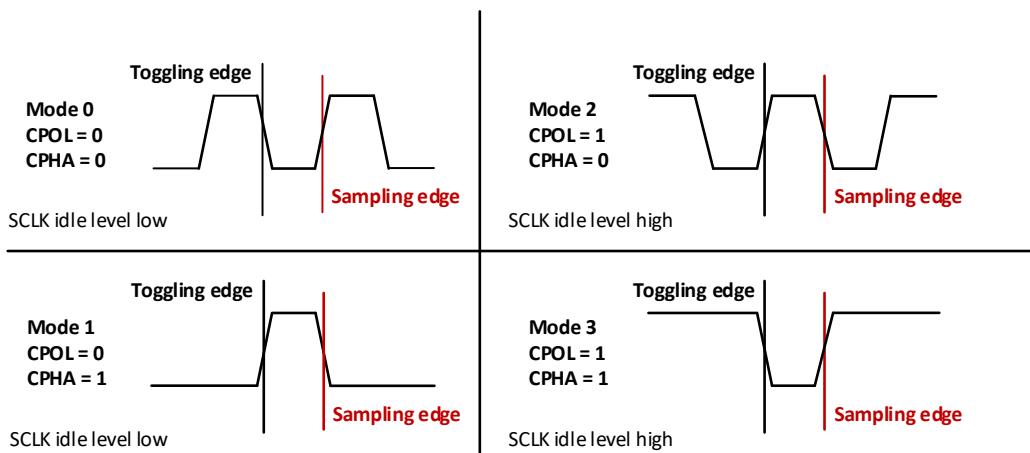

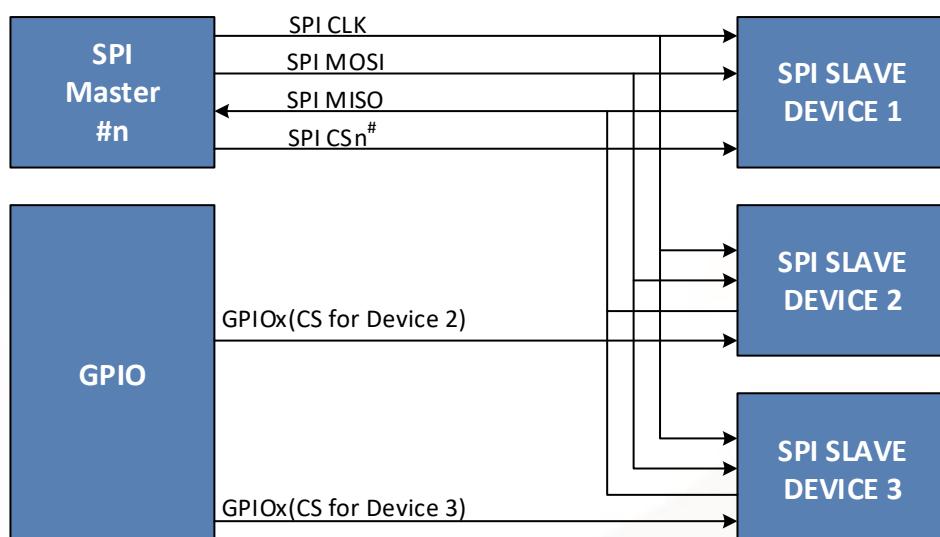

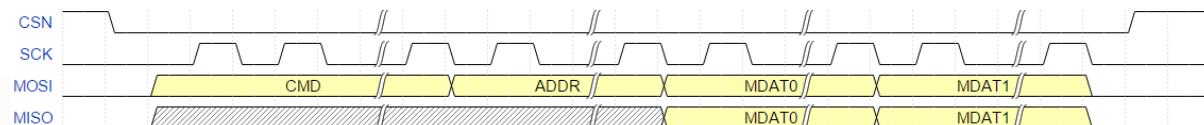

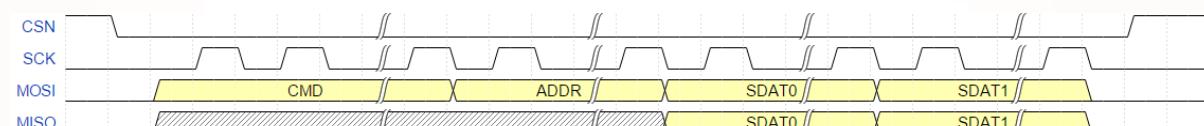

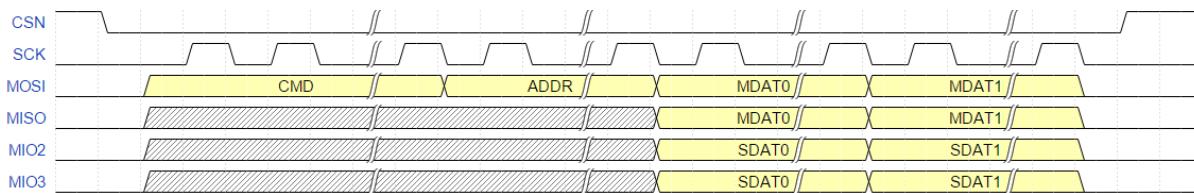

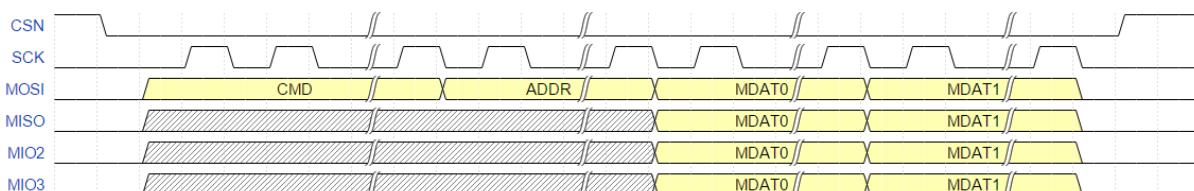

- SPI master for external devices

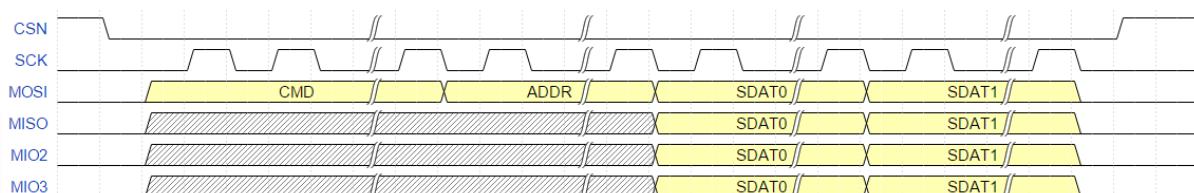

- SPI NOR flash interface

- SPI NAND flash interface

- eMMC4.5/SD interface

- I2C to control peripheral devices

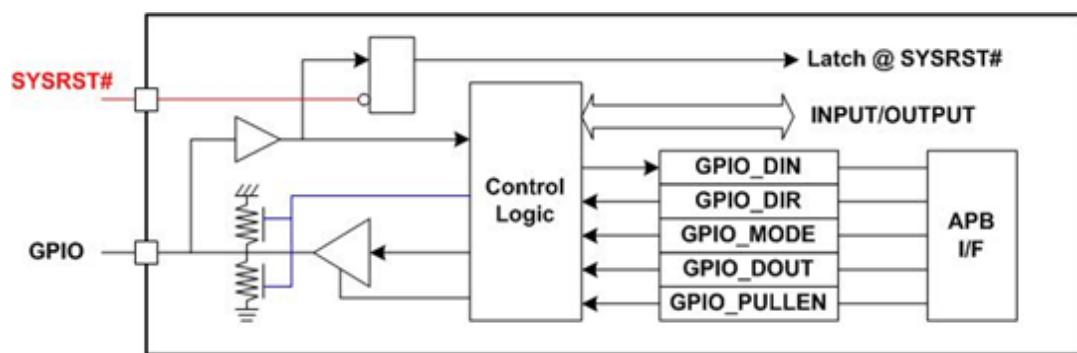

- General-Purpose Input/Output

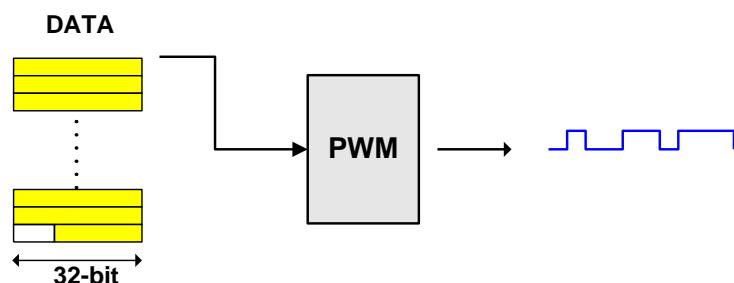

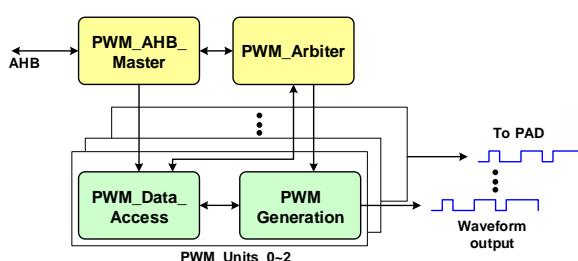

- PWM (Pulse Width Modulation)

- Operating conditions

- Core voltage: 0.87V

- I/O voltage: 1.8V/3.3V

- Package

- TFBGA 13.0 mm x 11.7 mm

- Ball pitch: 0.65 mm

## 1.2.2 Wireless Connectivity Features

### 1.2.2.1 Wi-Fi MAC Features

Wi-Fi MAC supports the following features:

- Support Dual-band Dual Concurrent

- Support all data rates of 802.11a/b/g/n/ac/ax

- Support short GI and all data rates of 802.11n including MCS0 to MCS7

- Support 802.11ac MCS0 to MCS11

- Support 802.11ax MCS0 to MCS11

- A-MPDU/A-MSDU RX (de-aggregation) and TX (aggregation) support

- TX beamformer and RX beamformee

- TX rate adaptation

- TX power control

- Security

- 64-bit WEP (WEP-40) and 128-bit WEP (WEP-104) encryption with hardware TKIP processing

- AES-CCMP hardware processing

- GCMP hardware processing

- Management/control frame filtering

### 1.2.2.2 WLAN Baseband Features

Wi-Fi baseband supports the following features:

- Support Dual band Dual Concurrent

- 20/40/80/160 MHz channels

- HE MCS0-11 BW20/40/80/160 MHz with  $N_{ss} = 1\sim 2$

- Short Guard Interval

- Space-Time Block Code (STBC)

- Low Density Parity Check (LDPC)

- Support digital pre-distortion to enhance PA performance

- Smoothing (channel estimation) extension to MIMO case

- Support radar detection

- Beamformer (explicit/implicit)

- Encoded BW20/40/80/160 up to 2x2 BF matrix apply

- Beamformee

- Decoded BW20/40/80/160 up to 4x2 MU matrix feedback

- UL OFDMA/MU-MIMO

- DL OFDMA/MU-MIMO

- Max RU number in 2G band is 8

- Max RU number in 5G band is 16

- Max user number is 512 (use DDR 512MB)

### 1.2.3 Wired Ethernet Features

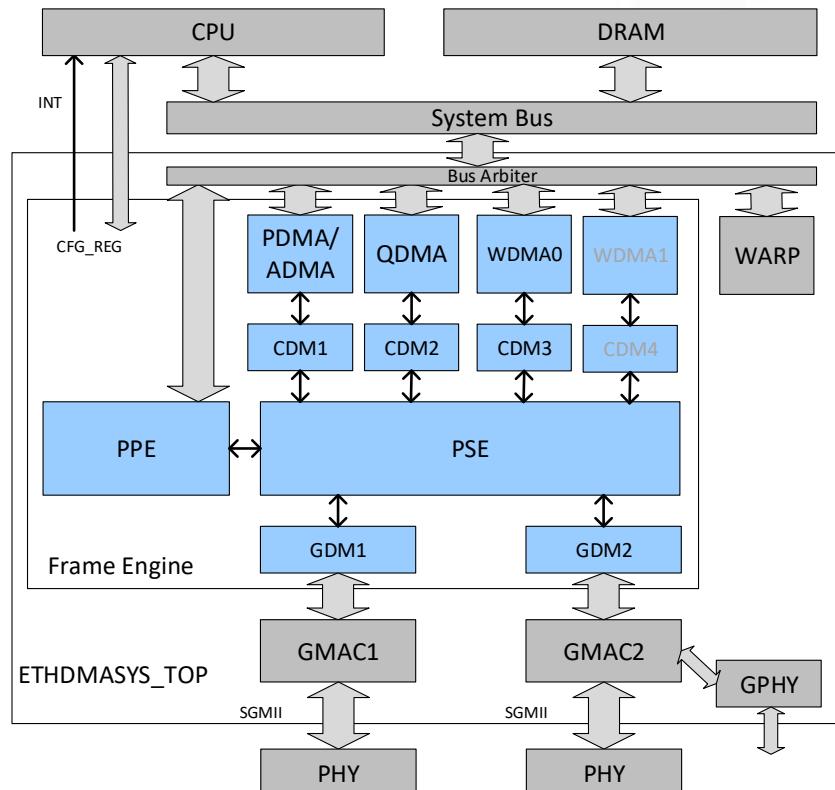

- Frame Engine

- Packet DMA (PDMA)

- 4 Tx descriptor and 4 Rx descriptor rings

- Scatter/Gather DMA

- Configurable 4/8/16/32 32-bit burst length and delayed interrupt

- Support TSO

- QoS DMA (QDMA)

- Supports 64 Tx physical queues and 4 sets of scheduler

- Per Tx queue forward/drop packet accounting

- Per Tx queue forward byte accounting

- Supports Tx queue min/max rate control and SP/WFQ egress scheduler

- Supports up to 1024 virtual queues for 8 sets of SFQ

- Packet Switch Engine (PSE)

- Wire-speed NAT/NAPT routing

- Egress rate limiting/shaping

- IP/TCP/UDP checksum offload

- IP/TCP/UDP checksum generation

- VLAN & PPPoE header insertion

- TCP segmentation offload

- Packet Process Engine (PPE)

- IPv4 NAP/NAPT, IPv6 Routing and Tunnel IP (DS-Lite, 6RD, 464XLAT, MAP-E/T)

- 1/2/4/8/16/32K session/flow

- Flow offloading technology for flexible/high performance packet L3/L4 packet processing

- Support NAT/NAPT wire-speed within 128 flows for any packet size

- Wi-Fi WARP

- Ethernet/Wi-Fi offload, forwarding packets directly

- Dynamic buffer allocate and release

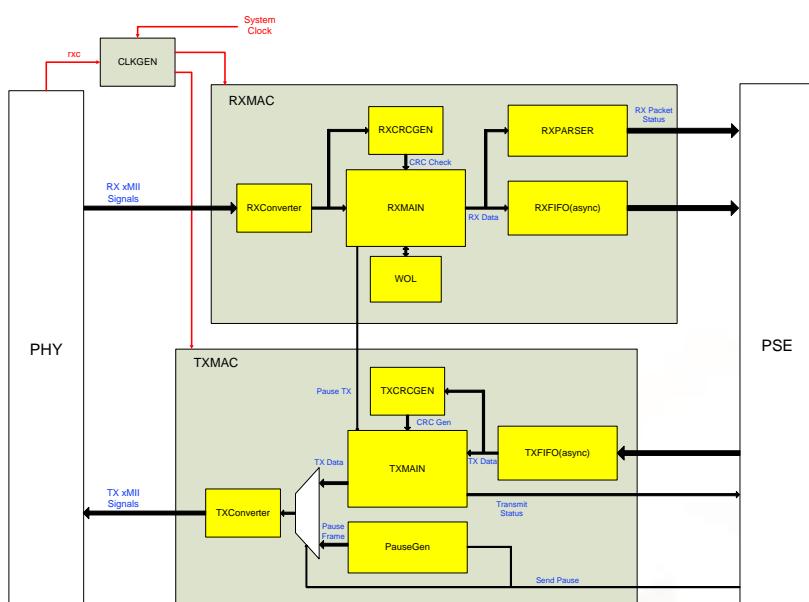

- Giga MAC (GMAC)

- Support IEEE 802.3x full duplex flow control

- Integrate 1G PHY for extender

- Only support SGMII-1 or internal-GBE due to their MAC sharing

- Support HSGMII interface

- HSGMII supports 10/100/1000Mbps speed change through auto negotiation and configurable 2.5Gbps SerDes links

## 2 Terms and Abbreviations

### 2.1 Terms

Table 2-1 describes the terms in Chapter 3 Pin Information.

**Table 2-1. Terms**

| Abbreviation | Description             |

|--------------|-------------------------|

| I            | Input                   |

| OH           | Output high             |

| OL           | Output low              |

| A            | Analog                  |

| P            | Power                   |

| G            | Ground                  |

| NC           | No connection           |

| PD           | Internal pull-down      |

| PU           | Internal pull-up        |

| NP           | No pull-down or pull-up |

## 2.2 Abbreviations

**Table 2-2. Abbreviations**

| Abbreviation | Description                                   |

|--------------|-----------------------------------------------|

| 6RD          | IPv6 Rapid Deployment                         |

| AHB          | Advanced Microcontroller Bus                  |

| AXI          | Advanced eXtensible Interface                 |

| DDR          | Double Data Rate                              |

| DMA          | Direct Memory Access                          |

| ECC          | Error Correction Code                         |

| EINTC        | External Interrupt Controller                 |

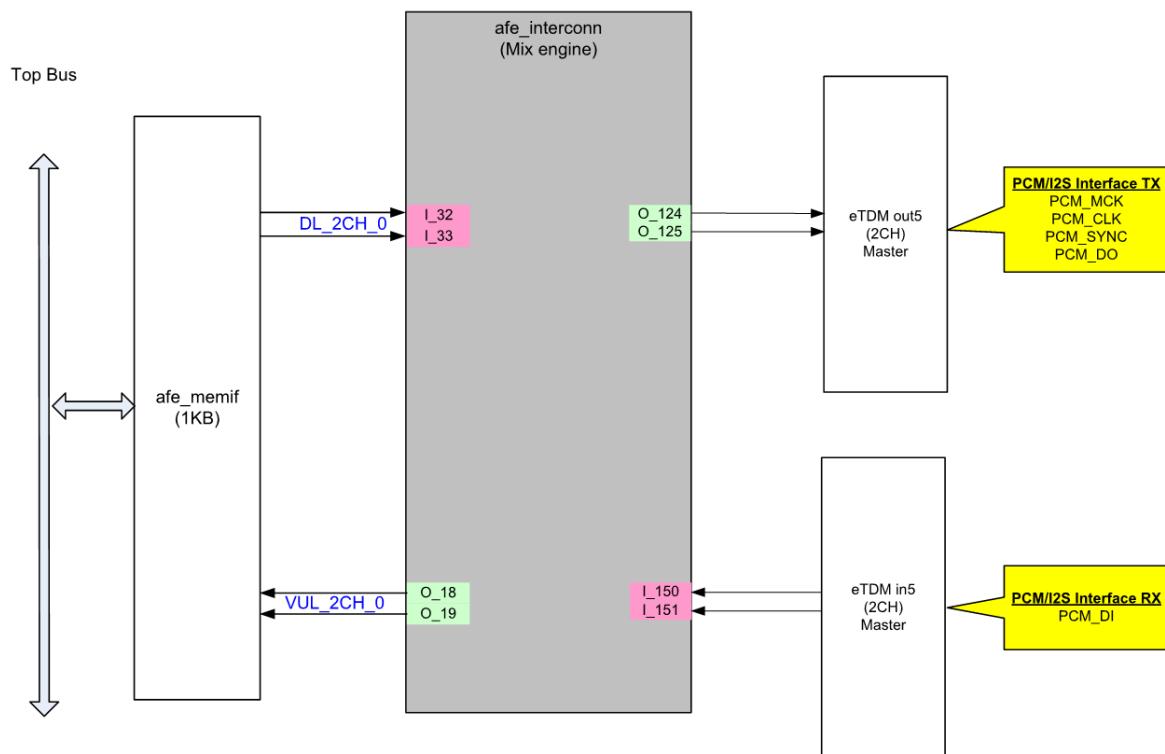

| eTDM         | Enhanced-Time-Division-Multiplexer            |

| FE           | Frame Engine                                  |

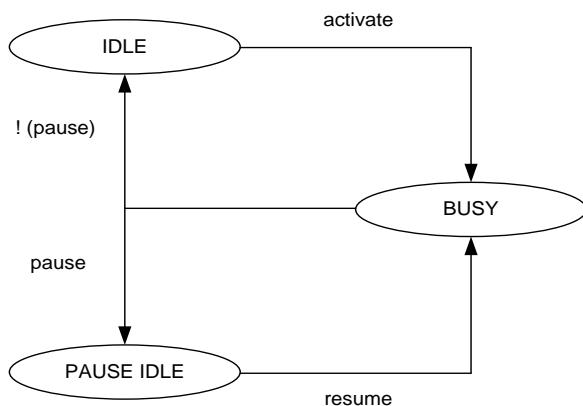

| FSM          | Finite State Machine                          |

| GIC          | Generic Interrupt Controller                  |

| GMII         | Gigabit Media-Independent Interface           |

| GPHY         | Gigabit Ethernet PHY                          |

| GPIO         | General-Purpose Input/Output                  |

| GPT          | General-Purpose Timer                         |

| HIF          | Host Interface                                |

| HW           | Hardware                                      |

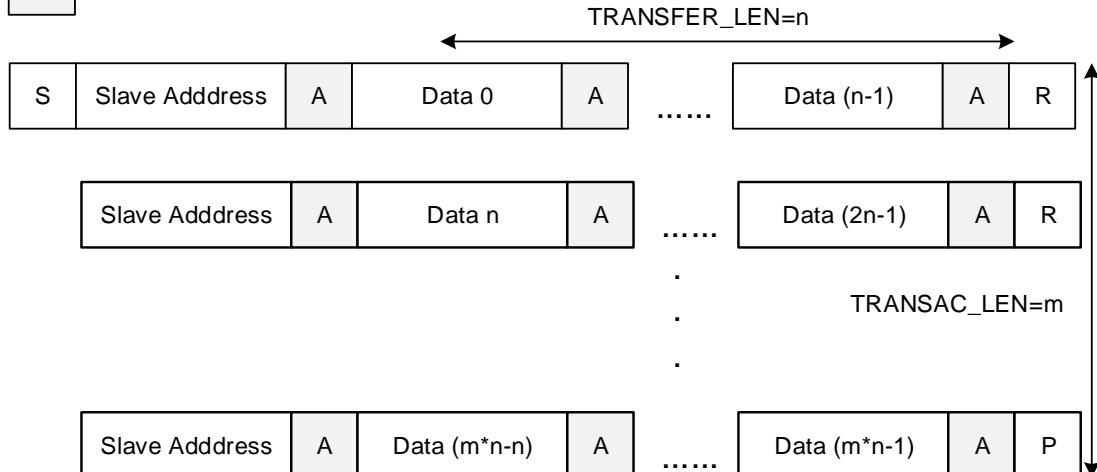

| I2C          | Inter-Integrated Circuit                      |

| I2S          | Inter-IC Sound                                |

| IRQ          | Interrupt Request                             |

| LDPC         | Low Density Parity Check                      |

| MII          | Media-Independent Interface                   |

| NAPT         | Network Address and Port Translation          |

| NAT          | Network Address Translation                   |

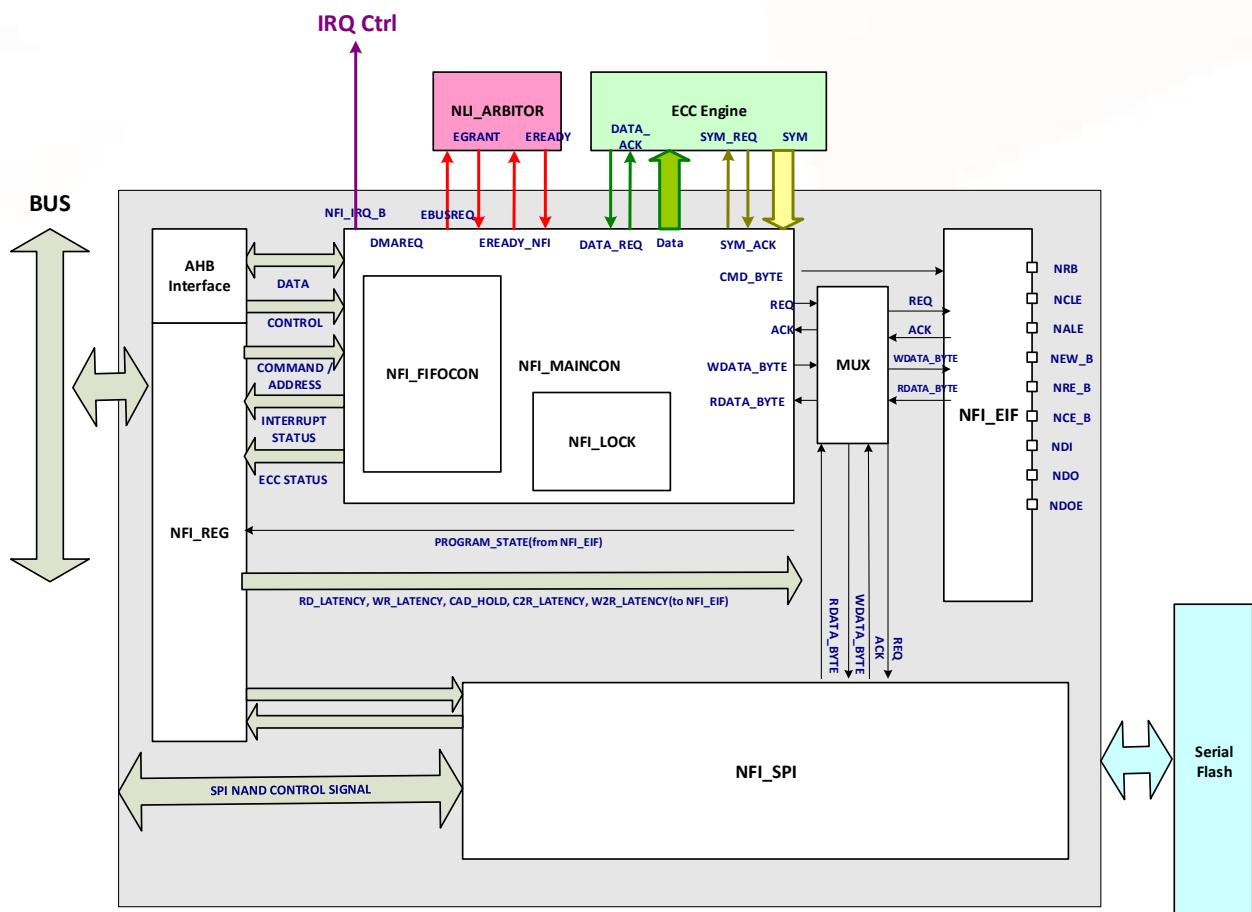

| NFI          | NAND Flash Interface                          |

| OCC          | On-Chip Clock                                 |

| PCIe         | Peripheral Component Interconnect Express     |

| PCM          | Pulse Code Modulation                         |

| PCS          | Physical Coding Sublayer                      |

| PLL          | Phase-Locked Loop                             |

| PWM          | Pulse Width Modulator; Pulse Width Modulation |

| RR           | Round-Robin                                   |

| SerDes       | Serializer/Deserializer                       |

| SGMII        | Serial Gigabit Media-Independent Interface    |

| SoC          | System-on-Chip                                |

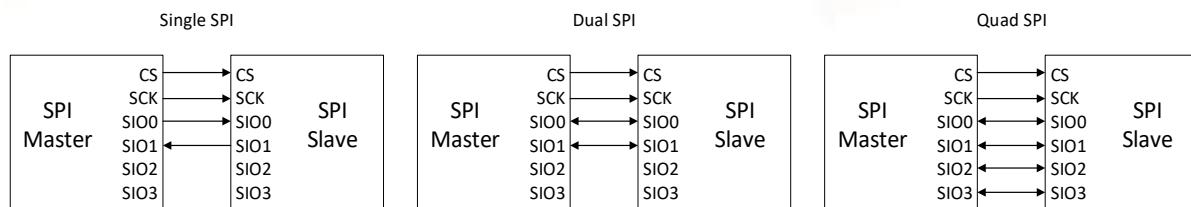

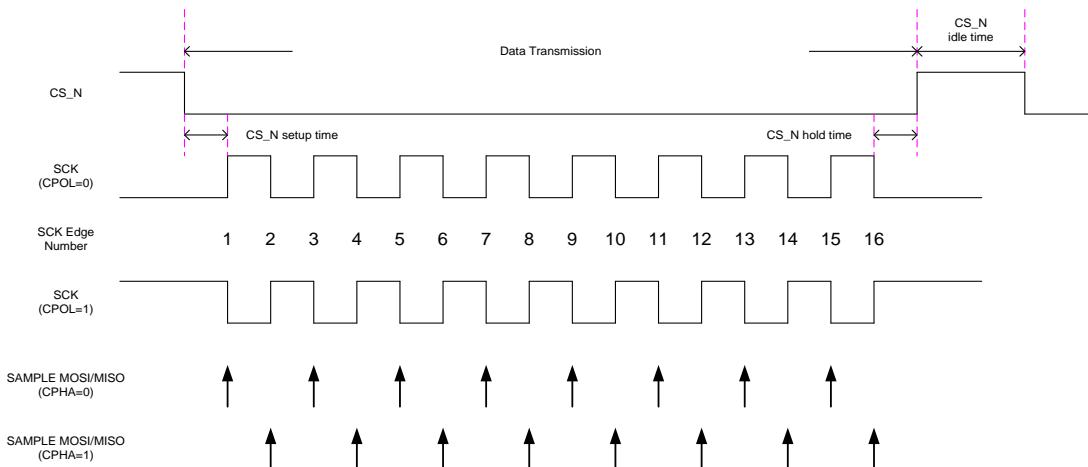

| SPI          | Serial Peripheral Interface                   |

| STBC         | Space-Time Block Code                         |

| SW           | Software                                      |

| UART         | Universal Asynchronous Receiver/Transmitter   |

| WDT          | Watchdog Timer                                |

### 3 Pin Information

#### 3.1 Pin Description

Table 3-1. Pin description

| Pin                                 | Name            | Reset <sup>(1)</sup> |                     | After Reset <sup>(1)</sup> |     |                     | Pull <sup>(1) (3)</sup> | Voltage (V) | Driving (mA) | Description |

|-------------------------------------|-----------------|----------------------|---------------------|----------------------------|-----|---------------------|-------------------------|-------------|--------------|-------------|

|                                     |                 | State <sup>(2)</sup> | Pull <sup>(3)</sup> | State <sup>(2)</sup>       | Aux | Pull <sup>(3)</sup> |                         |             |              |             |

| <b>GPIO</b>                         |                 |                      |                     |                            |     |                     |                         |             |              |             |

| F17                                 | GPIO_WPS        | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| E18                                 | GPIO_RESET      | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| L3                                  | USB_VBUS        | I                    | PD                  | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| N3                                  | PCIE_PERESET_N  | O                    | H-Z                 | OL                         | 1   | NP                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| M4                                  | JTAG_JTRST_N    | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| L4                                  | JTAG_JTDI       | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| L5                                  | JTAG_JTMS       | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| N4                                  | JTAG_JTCLK      | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| M3                                  | JTAG_JTDO       | O                    | H-Z                 | OL                         | 1   | NP                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| R3                                  | WO_JTAG_JTDO    | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| P3                                  | WO_JTAG_JTCLK   | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| P2                                  | WO_JTAG_JTMS    | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| R4                                  | WO_JTAG_JTDI    | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| R2                                  | WO_JTAG_JTRST_N | I                    | PD                  | I                          | 0   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| <b>UART</b>                         |                 |                      |                     |                            |     |                     |                         |             |              |             |

| G16                                 | UART0_RXD       | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| G17                                 | UART0_TXD       | O                    | H-Z                 | OH                         | 1   | NP                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| <b>Pulse-Width Modulation (PWM)</b> |                 |                      |                     |                            |     |                     |                         |             |              |             |

| D20                                 | PWM0            | I                    | PD                  | OL                         | 0   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| <b>Serial Flash</b>                 |                 |                      |                     |                            |     |                     |                         |             |              |             |

| D19                                 | SPI0_CLK        | O                    | H-Z                 | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| B20                                 | SPI0_CS         | O                    | H-Z                 | OH                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| D18                                 | SPI0_MOSI       | O                    | H-Z                 | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| C18                                 | SPI0_MISO       | I                    | PD                  | I                          | 1   | PD                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| C19                                 | SPI0_WP         | I                    | PU                  | I                          | 1   | PD                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| B19                                 | SPI0_HOLD       | I                    | PU                  | I                          | 1   | PU                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| A19                                 | SPI1_CLK        | O                    | H-Z                 | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| C17                                 | SPI1_CS         | O                    | H-Z                 | OH                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| B18                                 | SPI1_MOSI       | O                    | H-Z                 | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| A18                                 | SPI1_MISO       | I                    | PD                  | I                          | 1   | PD                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| T2                                  | SPI2_CLK        | I                    | PD                  | OL                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| V2                                  | SPI2_CS         | O                    | H-Z                 | OH                         | 1   | NP                  | 4                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| T3                                  | SPI2_MOSI       | O                    | H-Z                 | OL                         | 1   | NP                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| T1                                  | SPI2_MISO       | I                    | PD                  | I                          | 1   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| U1                                  | SPI2_WP         | I                    | PU                  | I                          | 1   | PD                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| U2                                  | SPI2_HOLD       | I                    | PU                  | I                          | 1   | PU                  | 2                       | PU/PD       | 3.3          | 2/4/8/12/16 |

| <b>DRAM</b>                         |                 |                      |                     |                            |     |                     |                         |             |              |             |

| U19                                 | EMI_EXTR        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| R15                                 | EMI_RESET_N     | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| T14                                 | EMI0_A0         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| U12                                 | EMI0_A1         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| R13                                 | EMI0_A10        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| T13                                 | EMI0_A11        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| V14                                 | EMI0_A12        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| U16                                 | EMI0_A13        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| U13                                 | EMI0_A14        | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| V16                                 | EMI0_A2         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| T16                                 | EMI0_A3         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| T11                                 | EMI0_A4         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

| U17                                 | EMI0_A5         | A                    | -                   | A                          | -   | -                   | -                       | -           | 1.5          | -           |

Table 3-1. Pin description

| Pin                                      | Name         | Reset (1) |          | After Reset (1) |     |          | Pull (1) (3) | Voltage (V) | Driving (mA) | Description                         |

|------------------------------------------|--------------|-----------|----------|-----------------|-----|----------|--------------|-------------|--------------|-------------------------------------|

|                                          |              | State (2) | Pull (3) | State (2)       | Aux | Pull (3) |              |             |              |                                     |

| V13                                      | EMIO_A6      | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V17                                      | EMIO_A7      | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T12                                      | EMIO_A8      | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T15                                      | EMIO_A9      | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V18                                      | EMIO_BA0     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R11                                      | EMIO_BA1     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R16                                      | EMIO_BA2     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R14                                      | EMIO_CAS_N   | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V11                                      | EMIO_CK_C    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U10                                      | EMIO_CK_T    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U11                                      | EMIO_CKE0    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V19                                      | EMIO_CS0_N   | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U7                                       | EMIO_DM0     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T5                                       | EMIO_DM1     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U5                                       | EMIO_DQ0     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V8                                       | EMIO_DQ1     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R10                                      | EMIO_DQ10    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R6                                       | EMIO_DQ11    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T10                                      | EMIO_DQ12    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T6                                       | EMIO_DQ13    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R9                                       | EMIO_DQ14    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R7                                       | EMIO_DQ15    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V5                                       | EMIO_DQ2     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U8                                       | EMIO_DQ3     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V4                                       | EMIO_DQ4     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V10                                      | EMIO_DQ5     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U4                                       | EMIO_DQ6     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U9                                       | EMIO_DQ7     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T9                                       | EMIO_DQ8     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T7                                       | EMIO_DQ9     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| V7                                       | EMIO_DQS0_C  | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U6                                       | EMIO_DQS0_T  | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| T8                                       | EMIO_DQS1_C  | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| R8                                       | EMIO_DQS1_T  | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U15                                      | EMIO_ODT     | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U14                                      | EMIO_RAS_N   | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| U18                                      | EMIO_WE_N    | A         | -        | A               | -   | -        | -            | 1.5         | -            | DRAM signal                         |

| <b>(SSUSB, SGMII1 or PCIe)/USB</b>       |              |           |          |                 |     |          |              |             |              |                                     |

| H2                                       | PCIE_CKP     | A         | -        | A               | -   | -        | -            | 0.9         | -            | PCIe CLK pin CK +                   |

| H3                                       | PCIE_CKN     | A         | -        | A               | -   | -        | -            | 0.9         | -            | PCIe CLK pin CK -                   |

| G1                                       | PCIE_LNO_RXP | A         | -        | A               | -   | -        | -            | 0.9         | -            | SSUSB/SGMII1 data pin RX +          |

| G2                                       | PCIE_LNO_RXN | A         | -        | A               | -   | -        | -            | 0.9         | -            | SSUSB/SGMII1 data pin RX -          |

| F2                                       | PCIE_LNO_TXP | A         | -        | A               | -   | -        | -            | 0.9         | -            | SSUSB/SGMII1 data pin TX +          |

| F1                                       | PCIE_LNO_TXN | A         | -        | A               | -   | -        | -            | 0.9         | -            | SSUSB/SGMII1 data pin TX -          |

| K3                                       | USB_DM       | A         | -        | A               | -   | -        | -            | 3.3         | -            | USB HS/FS/LS data pin data -        |

| K2                                       | USB_DP       | A         | -        | A               | -   | -        | -            | 3.3         | -            | USB HS/FS/LS data pin data +        |

| <b>Serial Management Interface (SMI)</b> |              |           |          |                 |     |          |              |             |              |                                     |

| L17                                      | SMI_MDC      | O         | H-Z      | OL              | 1   | PU       | 2            | PU/PD       | 3.3          | 2/4/8/12/16 Serial management clock |

| K17                                      | SMI_MDIO     | I         | PU       | I               | 1   | PU       | 2            | PU/PD       | 3.3          | 2/4/8/12/16 Serial management data  |

| <b>GBE Interface</b>                     |              |           |          |                 |     |          |              |             |              |                                     |

| M18                                      | GBE_RESET    | I         | PD       | I               | 0   | PD       | 2            | PU/PD       | 3.3          | 2/4/8/12/16 GBE_RESET               |

| M17                                      | GBE_INT      | I         | PD       | I               | 1   | PD       | 2            | PU/PD       | 3.3          | 2/4/8/12/16 GBE_INT                 |

| <b>Thermal Sensor Interface (TSAUX)</b>  |              |           |          |                 |     |          |              |             |              |                                     |

| F19                                      | AUXINO       | A         | -        | A               | -   | -        | -            | 1.8         | -            | Aux ADC input 0                     |

| F20                                      | AUXIN1       | A         | -        | A               | -   | -        | -            | 1.8         | -            | Aux ADC input 1                     |

| E20                                      | AUXIN2       | A         | -        | A               | -   | -        | -            | 1.8         | -            | Aux ADC input 2                     |

| E19                                      | TSAUX_MD     | A         | -        | A               | -   | -        | -            | 1.8         | -            | TSAUX_MD                            |

| G19                                      | TSAUX_REFP   | A         | -        | A               | -   | -        | -            | 1.8         | -            | TSAUX_REFP                          |

Table 3-1. Pin description

| Pin                              | Name          | Reset (1) |          | After Reset (1) |     |          | Pull (1)(3) | Voltage (V) | Driving (mA) | Description                              |

|----------------------------------|---------------|-----------|----------|-----------------|-----|----------|-------------|-------------|--------------|------------------------------------------|

|                                  |               | State (2) | Pull (3) | State (2)       | Aux | Pull (3) |             |             |              |                                          |

| <b>SGMII</b>                     |               |           |          |                 |     |          |             |             |              |                                          |

| J20                              | SGMII_LNO_RXN | A         | -        | A               | -   | -        | -           | 0.9         | -            | SGMII 0 data pin RX -                    |

| J19                              | SGMII_LNO_RXP | A         | -        | A               | -   | -        | -           | 0.9         | -            | SGMII 0 data pin RX +                    |

| K20                              | SGMII_LNO_TXN | A         | -        | A               | -   | -        | -           | 0.9         | -            | SGMII 0 data pin TX -                    |

| K19                              | SGMII_LNO_TXP | A         | -        | A               | -   | -        | -           | 0.9         | -            | SGMII 0 data pin TX +                    |

| <b>GPHY/GBE interface</b>        |               |           |          |                 |     |          |             |             |              |                                          |

| T19                              | REXT          | A         | -        | A               | -   | -        | -           | 1.8         | -            | REXT                                     |

| T20                              | GBE_TXVP_A_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY A_Channel differential P node       |

| R20                              | GBE_TXVN_A_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY A_Channel differential N node       |

| R19                              | GBE_TXVP_B_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY B_Channel differential P node       |

| P19                              | GBE_TXVN_B_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY B_Channel differential N node       |

| N19                              | GBE_TXVP_C_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY C_Channel differential P node       |

| N20                              | GBE_TXVN_C_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY C_Channel differential N node       |

| M20                              | GBE_TXVP_D_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY D_Channel differential P node       |

| M19                              | GBE_TXVN_D_PO | A         | -        | A               | -   | -        | -           | 3.3         | -            | GPHY D_Channel differential N node       |

| <b>OSC Clock</b>                 |               |           |          |                 |     |          |             |             |              |                                          |

| D16                              | MAIN_X40M_XIN | A         | -        | A               | -   | -        | -           | 1.8         | -            | OSC clock input                          |

| <b>Wi-Fi interface (2.4G/5G)</b> |               |           |          |                 |     |          |             |             |              |                                          |

| E3                               | WF_TOP_CLK    | I         | PD       | OH              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 SPI clock                    |

| C1                               | WF_TOP_DATA   | I         | PD       | OH              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 SPI data                     |

| A2                               | WF_HB0        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI clock                    |

| D5                               | WF_HB0_B      | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI clock                    |

| C3                               | WF_HB1        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf0 data[0]              |

| B1                               | WF_HB2        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf1 data[1]              |

| B2                               | WF_HB3        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf1 data[0]              |

| B3                               | WF_HB4        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf1 data[1]              |

| C5                               | WF_HB5        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf2 data[0]              |

| D6                               | WF_HB6        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf2 data[1]              |

| E6                               | WF_HB7        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf3 data[0]              |

| D7                               | WF_HB8        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf3 data[1]              |

| E7                               | WF_HB9        | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf4 data[0]              |

| E8                               | WF_HB10       | I         | PD       | OL              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 WRI wf4 data[1]              |

| C2                               | WF_XO_REQ     | I         | PD       | OH              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 OSC clock request to RF chip |

| D3                               | WF_DIG_RESETB | I         | PD       | OH              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 Reset RF chip digital        |

| D2                               | WF_CBA_RESETB | I         | PD       | OH              | 1   | NP       | 4           | PU/PD       | 1.8          | 2/4/8/12/16 Reset RF chip analog         |

| M1                               | WF2G_LED      | O         | H-Z      | I               | 0   | PD       | 2           | PU/PD       | 3.3          | 2/4/8/12/16 2G LED                       |

| M2                               | WF5G_LED      | O         | H-Z      | I               | 0   | PD       | 2           | PU/PD       | 3.3          | 2/4/8/12/16 5G LED                       |

| A17                              | WF4_IP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF4 I_Channel differential P node        |

| B17                              | WF4_IN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF4 I_Channel differential N node        |

| B16                              | WF4_QP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF4 Q_Channel differential P node        |

| C15                              | WF4_QN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF4 Q_Channel differential N node        |

| C14                              | WF3_IP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF3 I_Channel differential P node        |

| B14                              | WF3_IN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF3 I_Channel differential N node        |

| C13                              | WF3_QP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF3 Q_Channel differential P node        |

| B13                              | WF3_QN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF3 Q_Channel differential N node        |

| C12                              | WF2_IP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF2 I_Channel differential P node        |

| C11                              | WF2_IN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF2 I_Channel differential N node        |

| B11                              | WF2_QP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF2 Q_Channel differential P node        |

| B10                              | WF2_QN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF2 Q_Channel differential N node        |

| C10                              | WF1_IP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF1 I_Channel differential P node        |

| C9                               | WF1_IN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF1 I_Channel differential N node        |

| B8                               | WF1_QP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF1 Q_Channel differential P node        |

| C8                               | WF1_QN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF1 Q_Channel differential N node        |

| B7                               | WF0_IP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF0 I_Channel differential P node        |

| C7                               | WF0_IN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF0 I_Channel differential N node        |

| B5                               | WF0_QP        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF0 Q_Channel differential P node        |

| A5                               | WF0_QN        | A         | -        | A               | -   | -        | -           | 1.8         | -            | WF0 Q_Channel differential N node        |

Table 3-1. Pin description

| Pin                                                                                       | Name                                                                                                      | Reset (1) |          | After Reset (1) |     |          | Pull (1) (3) | Voltage (V) | Driving (mA) | Description                   |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------|----------|-----------------|-----|----------|--------------|-------------|--------------|-------------------------------|

|                                                                                           |                                                                                                           | State (2) | Pull (3) | State (2)       | Aux | Pull (3) |              |             |              |                               |

| <b>POR</b>                                                                                |                                                                                                           |           |          |                 |     |          |              |             |              |                               |

| B4                                                                                        | POR_RSTB                                                                                                  | A         | -        | A               | -   | -        | -            | 1.8         | -            | PMU_RSTB                      |

| A4                                                                                        | POR_BG_OUT                                                                                                | A         | -        | A               | -   | -        | -            | 1.8         | -            | BG_OUT                        |

| <b>PLLGP</b>                                                                              |                                                                                                           |           |          |                 |     |          |              |             |              |                               |

| L1                                                                                        | PLLGP_TP                                                                                                  | A         | -        | A               | -   | -        | -            | 1.8         | -            | PLLGP_TP test point           |

| L2                                                                                        | PLLGP_TN                                                                                                  | A         | -        | A               | -   | -        | -            | 1.8         | -            | PLLGP_TN test point           |

| <b>Misc.</b>                                                                              |                                                                                                           |           |          |                 |     |          |              |             |              |                               |

| R1                                                                                        | SYS_WATCHDOG                                                                                              | OL        | -        | OH              | -   | -        | -            | 3.3         | -            | Watchdog reset                |

| N2                                                                                        | SYSRSTB                                                                                                   | I         | PU       | I               | -   | PU       | -            | 3.3         | -            | Power on reset                |

| F16                                                                                       | TESTMODE                                                                                                  | I         | PD       | I               | -   | PD       | -            | 3.3         | -            | Test mode                     |

| <b>Power</b>                                                                              |                                                                                                           |           |          |                 |     |          |              |             |              |                               |

| F8, F9, F10, F13, F14, G6, G7, G13, H6, H14, J6, J15, K14, L8, L9, L10, L14, M7, M14, M15 | VCCK                                                                                                      | P         | -        | P               | -   | -        | -            | 0.85        | -            | Core power supply (DVDD_CORE) |

| F7<br>F6<br>K6<br>L6<br>L16<br>G15<br>F15                                                 | DVDD18IO_TL<br>DVDD18IO_LT<br>DVDD18IO_LB<br>DVDD18IO_BL<br>DVDD18IO_RB<br>DVDD18IO_RTC0<br>DVDD18IO_RTC1 | P         | -        | P               | -   | -        | -            | 1.8         | -            | IO power supply               |

| M6<br>L7<br>L15<br>H15<br>G14                                                             | DVDD33IO_LB<br>DVDD33IO_BL<br>DVDD33IO_RB<br>DVDD33IO_RTC0<br>DVDD33IO_RTC1                               | P         | -        | P               | -   | -        | -            | 3.3         | -            | IO power supply               |

| G4                                                                                        | AVDD09_PCIE                                                                                               | P         | -        | P               | -   | -        | -            | 0.9         | -            | SGMII1/PCIe power supply      |

| J18                                                                                       | AVDD09_SGMII                                                                                              | P         | -        | P               | -   | -        | -            | 0.9         | -            | SGMII power supply            |

| F4                                                                                        | AVDD18_PCIE                                                                                               | P         | -        | P               | -   | -        | -            | 1.8         | -            | SGMII1/PCIe power supply      |

| H19                                                                                       | AVDD18_SGMII                                                                                              | P         | -        | P               | -   | -        | -            | 1.8         | -            | SGMII power supply            |

| A3                                                                                        | AVDD15_POR                                                                                                | P         | -        | P               | -   | -        | -            | 1.5         | -            | POR power supply              |

| C4                                                                                        | AVDD18_POR                                                                                                | P         | -        | P               | -   | -        | -            | 1.8         | -            | POR power supply              |

| E15                                                                                       | AVDD12_CKSQ                                                                                               | P         | -        | P               | -   | -        | -            | 1.2         | -            | CKSQ power supply             |

| E14                                                                                       | AVDD18_CKSQ                                                                                               | P         | -        | P               | -   | -        | -            | 1.8         | -            | CKSQ power supply             |

| G20                                                                                       | AVDD18_AUXADC                                                                                             | P         | -        | P               | -   | -        | -            | 1.8         | -            | TSAUX power supply            |

| J5                                                                                        | AVDD18_PLLGP                                                                                              | P         | -        | P               | -   | -        | -            | 1.8         | -            | PLLGP power supply            |

| R17                                                                                       | AVDD18_RDDR                                                                                               | P         | -        | P               | -   | -        | -            | 1.8         | -            | DDR power supply              |

| M11                                                                                       | VDDIO_DDR_R                                                                                               | P         | -        | P               | -   | -        | -            | 1.5         | -            | DDR power supply              |

| M12                                                                                       | VDDIO_DDR_CA                                                                                              | P         | -        | P               | -   | -        | -            | 1.5         | -            | DDR power supply              |

| N8                                                                                        | VDDIO_DDR_DQ                                                                                              | P         | -        | P               | -   | -        | -            | 1.5         | -            | DDR power supply              |

| N9                                                                                        | VDDIO_DDR_DQ                                                                                              | P         | -        | P               | -   | -        | -            | 1.5         | -            | DDR power supply              |

| N10                                                                                       | VDDIO_DDR_MCLK                                                                                            | P         | -        | P               | -   | -        | -            | 1.5         | -            | DDR power supply              |

| L11                                                                                       | DVDD_DDR_TX                                                                                               | P         | -        | P               | -   | -        | -            | 0.87        | -            | DDR core power supply         |

| L12                                                                                       | DVDD_DDR_RX                                                                                               | P         | -        | P               | -   | -        | -            | 0.87        | -            | DDR core power supply         |

| J4                                                                                        | AVDD18_USB                                                                                                | P         | -        | P               | -   | -        | -            | 1.8         | -            | USB power supply              |

| K4                                                                                        | AVDD33_USB                                                                                                | P         | -        | P               | -   | -        | -            | 3.3         | -            | USB power supply              |

| E11                                                                                       | AVDD12_WBG                                                                                                | P         | -        | P               | -   | -        | -            | 1.2         | -            | AFE power supply              |

| E12                                                                                       | AVDD18_WBG                                                                                                | P         | -        | P               | -   | -        | -            | 1.8         | -            | AFE power supply              |

| R18                                                                                       | AVDD18_COM                                                                                                | P         | -        | P               | -   | -        | -            | 1.8         | -            | GPHY power supply             |

| P18                                                                                       | AVDD33_LD_P0                                                                                              | P         | -        | P               | -   | -        | -            | 3.3         | -            | GPHY power supply             |

| E5                                                                                        | DVDD18_VQPS                                                                                               | P         | -        | P               | -   | -        | -            | 1.8         | -            | eFuse blow power supply       |

Table 3-1. Pin description

| Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Name                               | Reset <sup>(1)</sup> |                     | After Reset <sup>(1)</sup> |     |                     | Pull <sup>(1) (3)</sup> | Voltage (V) | Driving (mA) | Description   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------------|---------------------|----------------------------|-----|---------------------|-------------------------|-------------|--------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    | State <sup>(2)</sup> | Pull <sup>(3)</sup> | State <sup>(2)</sup>       | Aux | Pull <sup>(3)</sup> |                         |             |              |               |

| <b>Ground</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                      |                     |                            |     |                     |                         |             |              |               |

| D4, D17, E1, E2, E4, E16, E17, F3, F5, F11, F12, F18, G3, G5, G8, G9, G10, G11, G12, G18, H1, H4, H5, H7, H8, H9, H10, H11, H12, H13, H16, H17, H18, J2, J3, J7, J8, J9, J10, J11, J12, J13, J14, J16, J17, K5, K7, K8, K9, K10, K11, K12, K13, K15, K16, K18, L13, L18, L19, L20, M5, M13, M16, N5, N6, N7, N11, N12, N13, N14, N15, N16, N17, N18, P4, P5, P6, P7, P8, P9, P10, P11, P12, P13, P14, P15, P16, P17, R5, T4, T17, T18, U3, U20, V3, V6, V9, V12, V15 | GNDK                               | G                    | -                   | G                          | -   | -                   | -                       | -           | -            | Ground (DVSS) |

| A7, A11, A14, B6, B15, C6, C16, D8, D9, D10, D11, D12, D13, D14, D15, E9, E10, E13                                                                                                                                                                                                                                                                                                                                                                                   | AVSS18_WBG                         | G                    | -                   | G                          | -   | -                   | -                       | -           | -            | Ground        |

| A1<br>A20<br>V1<br>V20                                                                                                                                                                                                                                                                                                                                                                                                                                               | NC_A1<br>NC_A20<br>NC_V1<br>NC_V20 | -                    | -                   | -                          | -   | -                   | -                       | -           | -            | NC ball       |

(1) See Table 2-1 for definitions of I, OH, OL, A, P, G, NC, PD, PU and NP.

(2) The internal pull resistance range: 10 kΩ to 75 kΩ, depending on IO configurations.

(3) While IO is set as GPIO mode, the IO driving strength can be either one of 2/4/6/8/10/12/14/16 mA and the default is [ ] mA.

### 3.1.1 Constantly Tied Pin

Table 3-2. Constantly tied pin

| Pin Name | Description            |

|----------|------------------------|

| TESTMODE | Test mode (tie to GND) |

## 3.2 Pin Sharing Schemes

Some pins are shared with GPIO to provide maximum flexibility for system designers. You can configure the register to specify pin function.

**Table 3-3. Pin sharing scheme**

| Pin Name        | Aux Func.0 | Aux Func.1          | Aux Func.2            | Aux Func.3         | Aux Func.4                | Aux Func.5     | Aux Func.6 |

|-----------------|------------|---------------------|-----------------------|--------------------|---------------------------|----------------|------------|

| GPIO_WPS        | B:GPIO00   | -                   | I0:WA_AICE_TCKC       | I0:WM_AICE_TCKC    | -                         | O:WM_UART_TXD  | -          |

| GPIO_RESET      | B:GPIO1    | -                   | B0:WA_AICE_TMSC       | B0:WM_AICE_TMSC    | -                         | O:WA_UART_TXD  | -          |

| SYS_WATCHDOG    | B:GPIO2    | O:SYS_WATCHDOG      | -                     | -                  | -                         | -              | -          |

| PCIE_PERESET_N  | B:GPIO3    | O:PCIE_PERESET_N    | -                     | -                  | -                         | -              | -          |

| JTAG_JTDO       | B:GPIO4    | O:JTAG_JTDO         | O:WM_JTAG_JTDO        | I1:UART2_RXD       | I0:PTA_EXT_ACT            | O:SPI1_CLK     | -          |

| JTAG_JTDI       | B:GPIO5    | I1:JTAG_JTDI        | I1:WM_JTAG_JTDI       | O:UART2_TXD        | I0:PTA_EXT_PRI            | O:SPI1_MOSI    | -          |

| JTAG_JTMS       | B:GPIO6    | B1:JTAG_JTMS        | I1:WM_JTAG_JTMS       | I1:UART2_CTS       | O:PTA_EXT_WLAN_ACT        | I0:SPI1_MISO   | B1:I2C_SCL |

| JTAG_JTCLK      | B:GPIO7    | I1:JTAG_JTCLK       | I1:WM_JTAG_JTCLK      | O:UART2_RTS        | O:PWM2                    | O:SPI1_CS      | B1:I2C_SDA |

| JTAG_JTRST_N    | B:GPIO8    | I0:JTAG_JTRST_N     | I0:WM_JTAG_JTRST_N    | O:GGE_LED0         | O:NET_WOO_UART_TXD        | -              | -          |

| WO_JTAG_JTDO    | B:GPIO9    | O:WOO_JTAG_JTDO     | I0:WM_AICE_TCKC       | -                  | O:PCM_DTX <sup>(1)</sup>  | -              | -          |

| WO_JTAG_JTDI    | B:GPIO10   | I1:WOO_JTAG_JTDI    | B0:WM_AICE_TMSC       | -                  | I0:PCM_DRX <sup>(1)</sup> | -              | -          |

| WO_JTAG_JTMS    | B:GPIO11   | B1:WOO_JTAG_JTMS    | -                     | -                  | O:PCM_CLK <sup>(1)</sup>  | -              | -          |

| WO_JTAG_JTCLK   | B:GPIO12   | I1:WOO_JTAG_JTCLK   | -                     | -                  | O:PCM_FS <sup>(1)</sup>   | -              | -          |

| WO_JTAG_JTRST_N | B:GPIO13   | I0:WOO_JTAG_JTRST_N | O:PWM0                | O:GGE_LED1         | O:PCM_MCK <sup>(1)</sup>  | O:SYS_WATCHDOG | -          |

| USB_VBUS        | B:GPIO14   | O:DRV_VBUS          | O:PWM1                | O:NET_WOO_UART_TXD | -                         | -              | -          |

| PWM0            | B:GPIO15   | O:PWM0              | O:EMMC_RSTB           | O:PWM1             | O:NET_WOO_UART_TXD        | -              | -          |

| SPI0_CLK        | B:GPIO16   | O:SPI0_CLK          | B1:EMMC_DAT0          | O:SNFI_CLK         | I1:UART1_RXD              | -              | -          |

| SPI0_MOSI       | B:GPIO17   | B0:SPI0_MOSI        | B1:EMMC_DAT1          | B0:SNFI_MOSI       | O:UART1_TXD               | -              | -          |

| SPI0_MISO       | B:GPIO18   | B0:SPI0_MISO        | B1:EMMC_DAT2          | B0:SNFI_MISO       | I1:UART1_CTS              | -              | -          |

| SPI0_CS         | B:GPIO19   | O:SPI0_CS           | B1:EMMC_DAT3          | O:SNFI_CS          | O:UART1_RTS               | -              | -          |

| SPI0_HOLD       | B:GPIO20   | B0:SPI0_HOLD        | B1:EMMC_DAT4          | B0:SNFI_HOLD       | O:WM_UART_TXD             | -              | -          |

| SPI0_WP         | B:GPIO21   | B0:SPI0_WP          | B1:EMMC_DAT5          | B0:SNFI_WP         | O:WA_UART_TXD             | -              | -          |

| SPI1_CLK        | B:GPIO22   | O:SPI1_CLK          | B1:EMMC_DAT6          | I1:UART2_RXD       | I0:PTA_EXT_ACT            | -              | -          |

| SPI1_MOSI       | B:GPIO23   | O:SPI1_MOSI         | B1:EMMC_DAT7          | I0:UART2_RXD       | I0:PTA_EXT_PRI            | -              | -          |

| SPI1_MISO       | B:GPIO24   | I0:SPI1_MISO        | B1:EMMC_CMD           | I1:UART2_CTS       | O:PTA_EXT_WLAN_ACT        | -              | -          |

| SPI1_CS         | B:GPIO25   | O:SPI1_CS           | B1:EMMC_CLK           | O:UART2_RTS        | O:PCM_MCK <sup>(1)</sup>  | -              | -          |

| SPI2_CLK        | B:GPIO26   | O:SPI2_CLK          | I1:UART1_RXD          | -                  | -                         | -              | -          |

| SPI2_MOSI       | B:GPIO27   | B0:SPI2_MOSI        | O:UART1_RXD           | -                  | -                         | -              | -          |

| SPI2_MISO       | B:GPIO28   | B0:SPI2_MISO        | I1:UART1_CTS          | O:WA_AICE_TCKC     | -                         | -              | -          |

| SPI2_CS         | B:GPIO29   | O:SPI2_CS           | O:UART1_RTS           | B0:WA_AICE_TMSC    | -                         | -              | -          |

| SPI2_HOLD       | B:GPIO30   | B0:SPI2_HOLD        | O:WF2G_LED            | O:WM_UART_TXD      | B1:I2C_SCL                | -              | -          |

| SPI2_WP         | B:GPIO31   | B0:SPI2_WP          | O:WF5G_LED            | O:WA_UART_TXD      | B1:I2C_SDA                | -              | -          |

| UART0_RXD       | B:GPIO32   | I1:UART0_RXD        | B1:SGMII1_PHY_I2C_SCL | B1:U3_PHY_I2C_SCL  | -                         | -              | -          |

| UART0_TXD       | B:GPIO33   | O:UART0_RXD         | B1:SGMII1_PHY_I2C_SDA | B1:U3_PHY_I2C_SDA  | -                         | -              | -          |

| WF2G_LED        | B:GPIO34   | O:WF2G_LED          | B1:PCIE_CLK_REQ       | -                  | -                         | -              | -          |

| WF5G_LED        | B:GPIO35   | O:WF5G_LED          | I1:PCIE_WAKE_N        | -                  | -                         | -              | -          |

| SMI_MDC         | B:GPIO36   | O:SMI_MDC           | B1:I2C_SCL            | I1:GGE_EXT_MDC     | -                         | -              | -          |

| SMI_MDIO        | B:GPIO37   | B0:SMI_MDIO         | B1:I2C_SDA            | B1:GGE_EXT_MDIO    | -                         | -              | -          |

| GBE_INT         | B:GPIO38   | I0:MT7531_INT       | -                     | -                  | -                         | -              | -          |

| GBE_RESET       | B:GPIO39   | -                   | -                     | -                  | -                         | -              | -          |

| WF_DIG_RESETB   | B:GPIO40   | O:WF0_DIG_RESETB    | -                     | -                  | -                         | -              | -          |

| WF_CBA_RESETB   | B:GPIO41   | O:WF0_CBA_RESETB    | -                     | -                  | -                         | -              | -          |

| WF_XO_REQ       | B:GPIO42   | O:WF0_XO_REQ        | -                     | -                  | -                         | -              | -          |

| WF_TOP_CLK      | B:GPIO43   | O:WF0_TOP_CLK       | -                     | -                  | -                         | -              | -          |

| WF_TOP_DATA     | B:GPIO44   | B0:WF0_TOP_DATA     | -                     | -                  | -                         | -              | -          |

| WF_HB1          | B:GPIO45   | B0:WF_HB1           | O:WF0_MODE_SEL_1      | -                  | -                         | -              | -          |

| WF_HB2          | B:GPIO46   | B0:WF_HB2           | O:WF0_MODE_SEL_2      | -                  | -                         | -              | -          |

| WF_HB3          | B:GPIO47   | B0:WF_HB3           | O:WF0_XTAL_SEL_0      | -                  | -                         | -              | -          |

| WF_HB4          | B:GPIO48   | B0:WF_HB4           | O:WF0_XTAL_SEL_1      | -                  | -                         | -              | -          |

| WF_HB0          | B:GPIO49   | O:WF_O_HB0          | O:WF0_MODE_SEL_0      | -                  | -                         | -              | -          |

| WF_HB0_B        | B:GPIO50   | O:WF_O_HB0_B        | -                     | -                  | -                         | -              | -          |

| WF_HB5          | B:GPIO51   | B0:WF_HB5           | O:WF0_XTAL_SEL_2      | -                  | -                         | -              | -          |

| WF_HB6          | B:GPIO52   | B0:WF_HB6           | -                     | -                  | -                         | -              | -          |

| WF_HB7          | B:GPIO53   | B0:WF_HB7           | -                     | -                  | -                         | -              | -          |

| WF_HB8          | B:GPIO54   | B0:WF_HB8           | -                     | -                  | -                         | -              | -          |

| WF_HB9          | B:GPIO55   | B0:WF_HB9           | -                     | -                  | -                         | -              | -          |

| WF_HB10         | B:GPIO56   | B0:WF_HB10          | -                     | -                  | -                         | -              | -          |

**(1) Pin sharing:**

PCM\_DTX: I2S Data Out

PCM\_DRX: I2S Data In

PCM\_CLK: I2S BCLK/SCK

PCM\_FS: I2S WS/LRCK

PCM\_MCK: I2S MCLK

### 3.3 Strapping Options

*Table 3-4. Strapping*

| Pin Name | Strapping Name | Description                                                                               |

|----------|----------------|-------------------------------------------------------------------------------------------|

| USB_VBUS | Boot Mode      | {PWM0, USB_VBUS}<br>00: SPI-NOR<br>01: SPI-NAND → SD<br>10: eMMC<br>11: SNAND (SNFI) → SD |

| PWM0     |                |                                                                                           |

| SPI2_CLK | A-die Crystal  | 0: 80 MHz<br>1: 40 MHz (supported)                                                        |

## 4 Electrical Characteristics

### 4.1 Absolute Maximum Ratings

Table 4-1. Absolute maximum ratings

| Symbol or Pin Name                                                                                                                                  | Description          | Min  | Max   | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-------|------|

| VCCK (DVDD_CORE)<br>DVDD_DDR_TX<br>DVDD_DDR_RX                                                                                                      | 0.87V supply voltage | -0.3 | 0.95  | V    |

| DVDD18IO_TL<br>DVDD18IO_LT<br>DVDD18IO_LB<br>DVDD18IO_BL<br>DVDD18IO_RB<br>DVDD18IO_RTC0<br>DVDD18IO_RTC1                                           | 1.8V supply voltage  | -0.3 | 1.98  | V    |

| DVDD33IO_LB<br>DVDD33IO_BL<br>DVDD33IO_RB<br>DVDD33IO_RTC0<br>DVDD33IO_RTC1                                                                         | 3.3V supply voltage  | -0.3 | 3.6   | V    |

| AVDD33_USB<br>AVDD33_LD_P0                                                                                                                          | 3.3V supply voltage  | -0.3 | 3.6   | V    |

| AVDD12_CKSQ<br>AVDD12_WBG                                                                                                                           | 1.2V supply voltage  | -0.3 | 1.32  | V    |

| AVDD09_PCIE<br>AVDD09_SGMII                                                                                                                         | 0.9V supply voltage  | -0.3 | 0.99  | V    |

| AVDD18_PCIE<br>AVDD18_SGMII<br>AVDD18_COM<br>AVDD18_POR<br>AVDD18_AUXADC<br>AVDD18_PLLGP<br>AVDD18_CKSQ<br>AVDD18_USB<br>AVDD18_WBG<br>AVDD18_RADDR | 1.8V supply voltage  | -0.3 | 1.98  | V    |

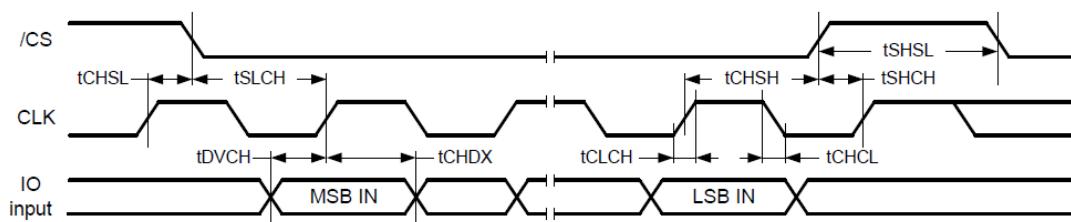

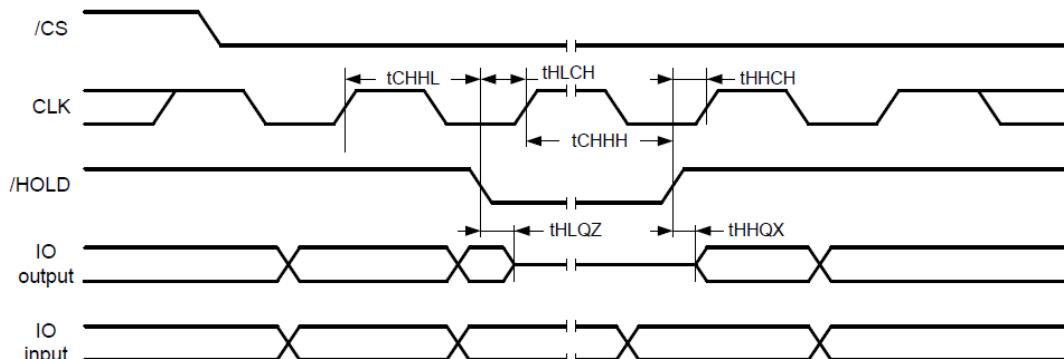

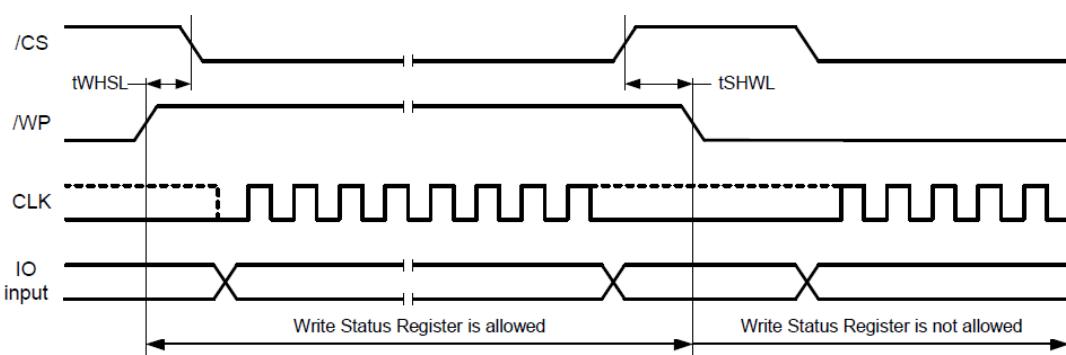

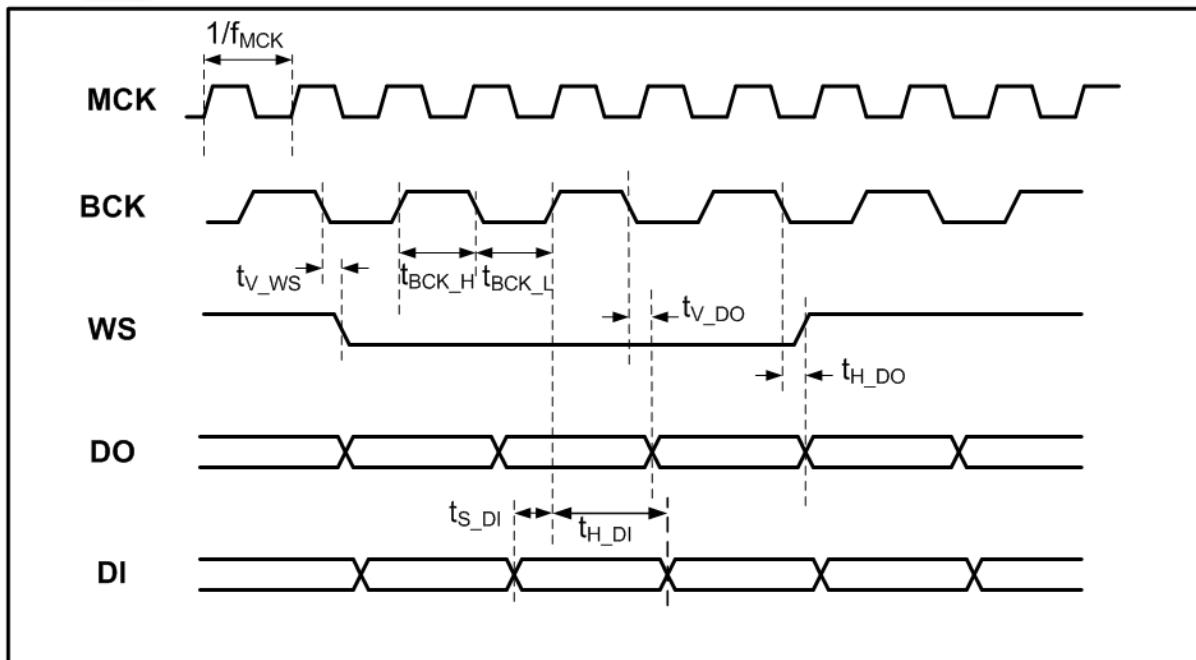

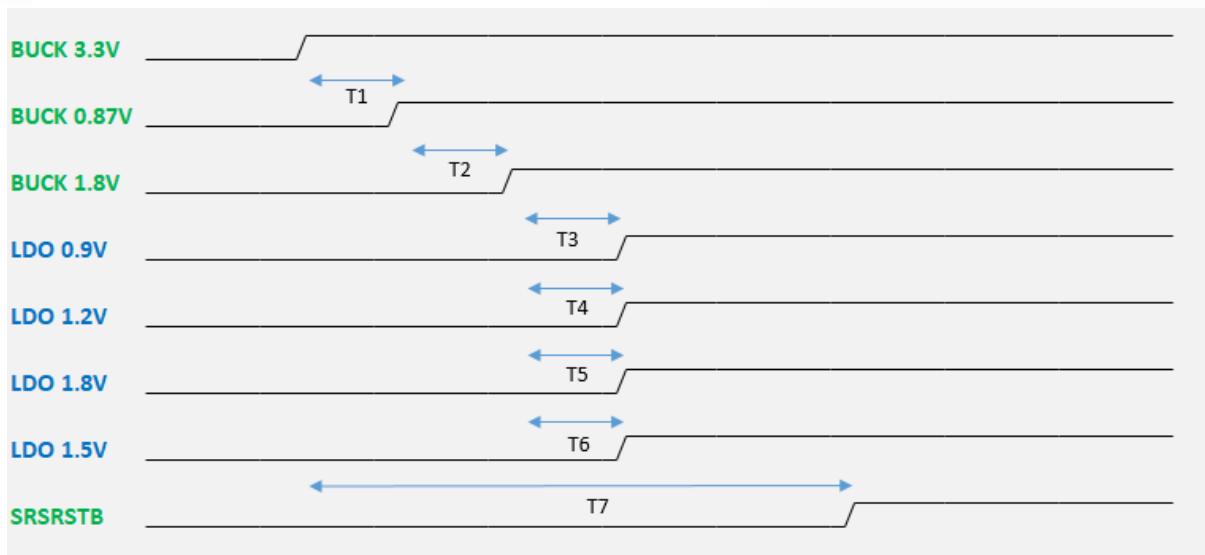

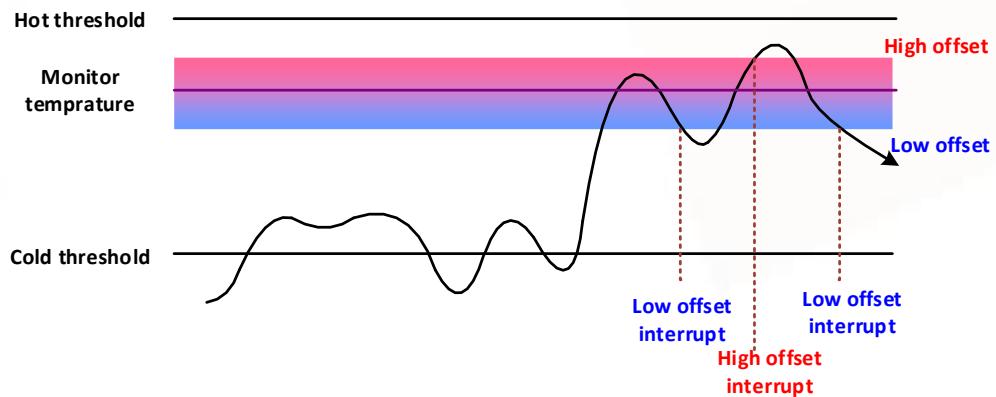

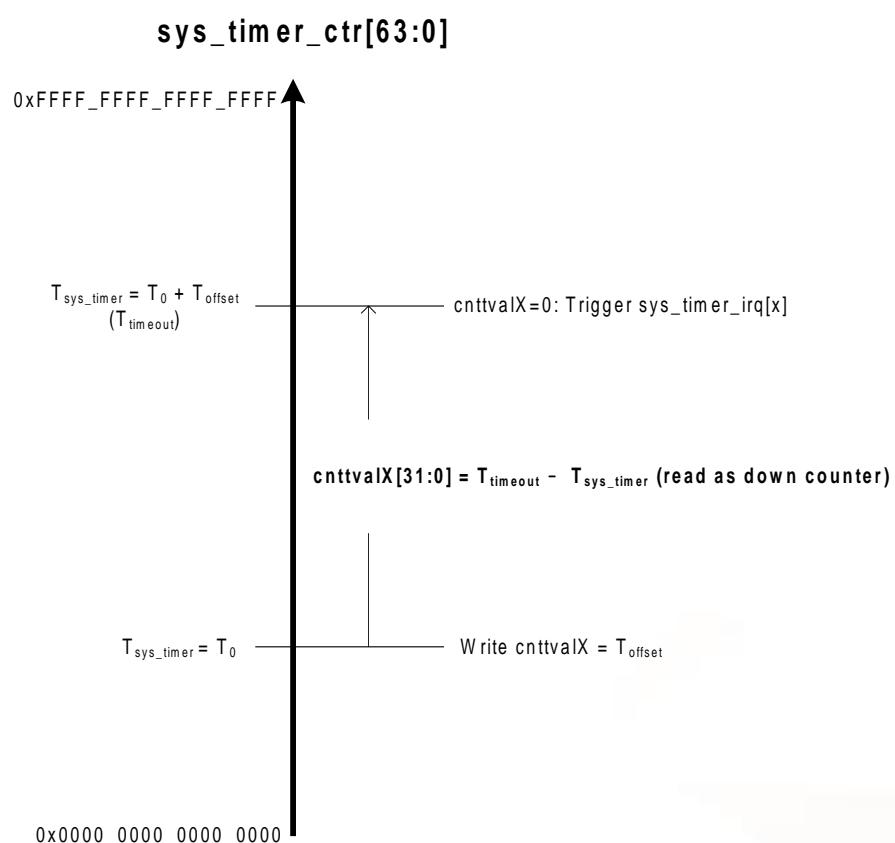

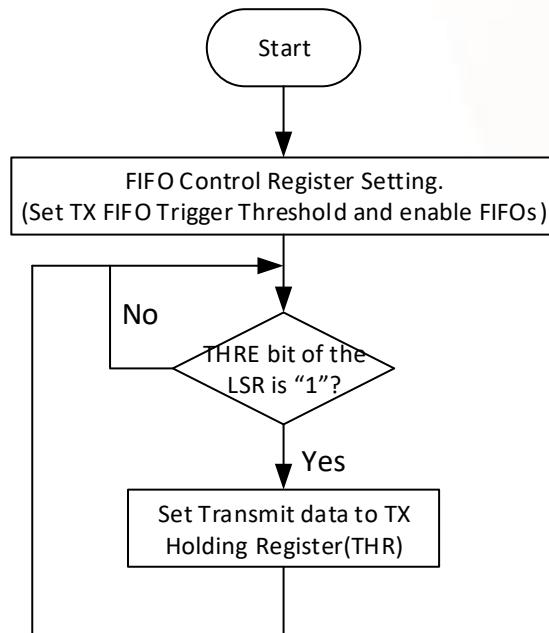

| VDDIO_DDR_DQ<br>VDDIO_DDR_MCLK<br>VDDIO_DDR_R<br>VDDIO_DDR_CA<br>AVDD15_POR                                                                         | 1.5V supply voltage  | -0.3 | 1.575 | V    |