# 1/5-Inch System-On-A-Chip (SOC) CMOS Digital Image Sensor

# MT9D113 Data Sheet

For the latest data sheet, refer to Aptina's Web site: www.aptina.com

## **Features**

- 2Mp resolution (1600H x 1200V)

- 1/5-inch optical format

- Same or better image quality compared to MT9D112

- Individual module ID support through one-time programmable (OTP) memory

- Surface fit lens correction (LC) to compensate for lens/small pixel vignetting and corner color variations

- Automatic functions: Exposure, white balance, black level offset correction, flicker detection and avoidance, color saturation control, defect identification and correction, aperture correction, and GPIO

- Programmable controls: Exposure, white balance, horizontal and vertical blanking, color, sharpness, gamma, lens shading correction, horizontal and vertical image flip, zoom, windowing, sampling rates, and GPIO

- 15 frames per second (fps) at 1600H x 1200V with moderate pixel clock frequency ( $\leq$  65 MHz) to minimize baseband reception interference and 30 fps at 800H x 600V

- 2 x 2 pixel binning to improve low-light image quality

- Support for external LED or xenon flash

- On-chip phase-locked loop (PLL) to minimize the number of system clocks

- Low power modes to prolong battery life of portable devices

- Fail-safe I/Os with programmable output slew rate

- Industry standard two-wire serial interface for controls

- 10-bit parallel or MIPI serial interfaces for image data

# **Applications**

- Cellular phones

- · PC cameras

- PDAs

# **Ordering Information**

Table 1: Available Part Numbers

| Part Number         | Description |

|---------------------|-------------|

| MT9D113D00STCK25AC1 | Bare Die    |

## Table 2: Key Performance Parameters

| Parameter             | Value                                         |

|-----------------------|-----------------------------------------------|

| Pixel size            | Symmetric 1.75μm pixel                        |

| Optical format        | 1/5-inch                                      |

| Targeted module size  | 6.5mm x 6.5mm x 5mm                           |

| (estimated)           |                                               |

| Targeted die size     | 5.06mm x 5.24mm                               |

| Array format (active) | 1600H x 1200V (4:3 aspect ratio)              |

| Imaging area          | 2.8mm x 2.10mm: 3.50mm diagonal (4:3          |

|                       | aspect ratio)                                 |

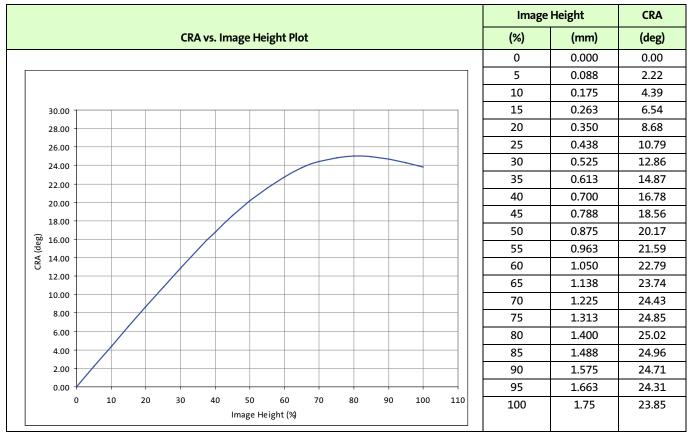

| CRA                   | 25° (MAX at 90% image height)                 |

| Color filter array    | RGB color filters                             |

| Frame rate            | 15 fps (full resolution), 30 fps (video mode) |

| Scan mode             | Progressive                                   |

| Shutter               | Electronic rolling shutter (ERS)              |

| Windowing             | Programmable                                  |

| Output Interfaces     | MIPI single-lane or parallel 10-bit           |

| Data rate             | MIPI: Up to 640 Mb/s and up to 85 MHz         |

|                       | parallel data                                 |

|                       | Parallel: 80 MB/s (parallel no FIFO),         |

|                       | 63 MB/s (parallel with FIFO)                  |

| Responsivity          | 0.2 V/Lux-sec (550nm)                         |

| Signal-to-noise ratio | >37dB (MAX)                                   |

| Dynamic range         | >60dB (pixel)                                 |

| Full well             | >6900e- (linear)                              |

| Read noise            | 4e- (8x Gain)                                 |

| Supply voltage        | Analog: 2.8V (nominal)                        |

|                       | Digital: 1.8V (nominal)                       |

|                       | I/O: 1.8V or 2.8V (nominal)                   |

|                       | OTP: 8V (nominal)                             |

| Operating temperature | –30°C to 70°C (at junction)                   |

| range                 |                                               |

| Package               | Bare die (in wafer form)                      |

# **Table of Contents**

| Features                                                        |     |

|-----------------------------------------------------------------|-----|

| Applications                                                    |     |

| Ordering Information                                            |     |

| Overview                                                        |     |

| Гypical Connections                                             |     |

| Decoupling Capacitor Recommendations                            |     |

| Signal Descriptions                                             |     |

| Architecture                                                    |     |

| Firmware                                                        |     |

| External Host Interface (Two-Wire Slave-Only Interface)         |     |

| Always-On Power Domain                                          |     |

| Sensor Core                                                     |     |

| Pixel Array                                                     |     |

| Analog Processing                                               |     |

| PLL-Generated Master Clock                                      | .16 |

| PLL Setup                                                       | .17 |

| Digital Processing                                              | .17 |

| Readout Options                                                 | .17 |

| Readout Modes                                                   | .17 |

| Input Interface to Image Flow Processor                         | .25 |

| Image Flow Processor                                            | .26 |

| Pixel Reconstruction (Lens Shading Correction)                  |     |

| Color Rendering/Statistics Collection (Color Correction)        |     |

| Digital Scaling/Output Format                                   | .29 |

| YUV-to-RGB/YUV Conversion and Output Formatting                 |     |

| Output Interface from IFP                                       |     |

| Parallel and MIPI Output                                        |     |

| Output Format and Timing                                        |     |

| Control Functions                                               |     |

| Sequencer: Camera Operating System                              |     |

| Mode: Context Information                                       |     |

| Camera Functions                                                |     |

| Simple Rule-based Auto Exposure                                 |     |

| AE Driver                                                       |     |

| Evaluative Algorithm                                            |     |

| Accelerated Settling During Overexposure                        |     |

| Exposure Control.                                               |     |

| Flicker Detection and Avoidance                                 |     |

| Auto White Balance                                              |     |

| Flash                                                           |     |

| Histogram: Dark Level Adjustments, Low Light and Tonal Controls |     |

| Optics                                                          |     |

| Power Modes                                                     |     |

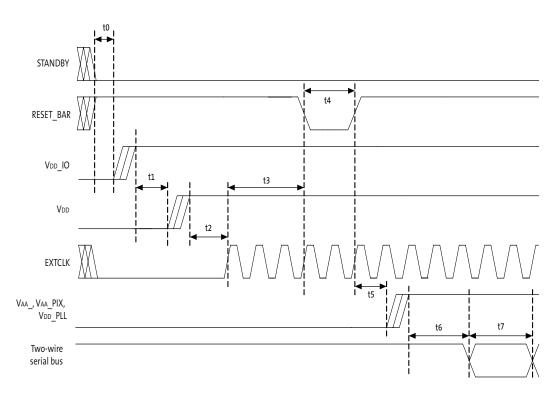

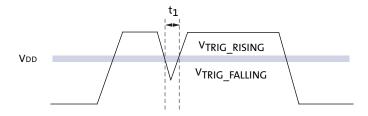

| Power Application Sequence                                      |     |

| Power-On Reset                                                  |     |

|                                                                 |     |

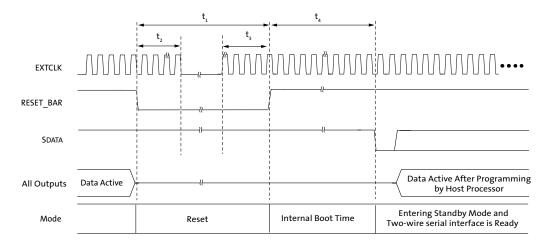

| Hard Reset                                                      |     |

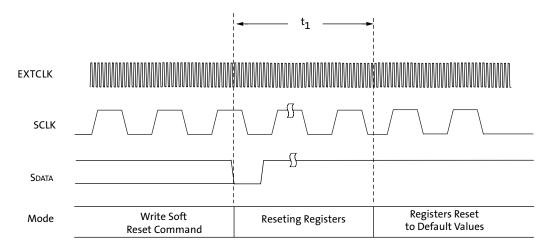

| Soft Reset                                                      |     |

| Power Removal Sequence                                          |     |

| Standby Modes                                                   |     |

| Soft Standby                                                    |     |

| Low Leakage Hard Standby                                        | .45 |

# MT9D113: 1/5-Inch SOC Digital Image Sensor Table of Contents

|                                                                                | www.DataSheet4U.co |

|--------------------------------------------------------------------------------|--------------------|

| Hard Standby Mode                                                              | 46                 |

| Entering Standby Mode                                                          | 46                 |

| Exiting Standby Mode                                                           |                    |

| Soft Standby Mode                                                              |                    |

| Entering Standby Mode                                                          |                    |

| Exiting Standby Mode                                                           |                    |

| Other Features                                                                 | 49                 |

| One-time Programmable (OTP) Memory                                             |                    |

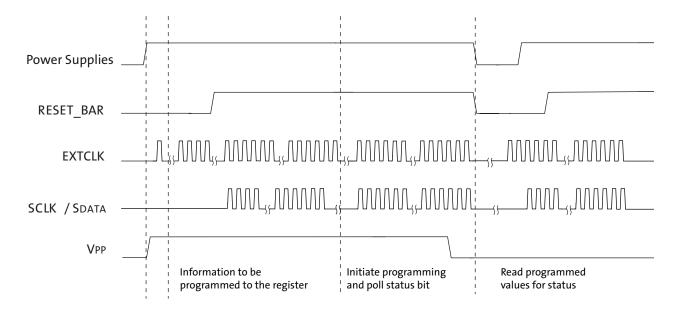

| Programming the OTP Memory                                                     | 49                 |

| Sequence of Signals for OTP Memory Operation                                   | 49                 |

| Reading the OTP Memory                                                         | 49                 |

| GPIO and Output Enable Controls                                                | 50                 |

| General Purpose I/Os                                                           | 50                 |

| Output Enable Control                                                          | 50                 |

| GPIO Control                                                                   |                    |

| Overview of GPIO Signals                                                       | 51                 |

| Electrical Specifications                                                      | 52                 |

| Absolute Maximum Rating                                                        |                    |

| I/O Parameters                                                                 |                    |

| AC Electricals                                                                 | 53                 |

| Appendix A - VDD_IO Current Addition                                           | 56                 |

| Introduction                                                                   |                    |

| VDD_IO Current                                                                 |                    |

| IO Pin States                                                                  |                    |

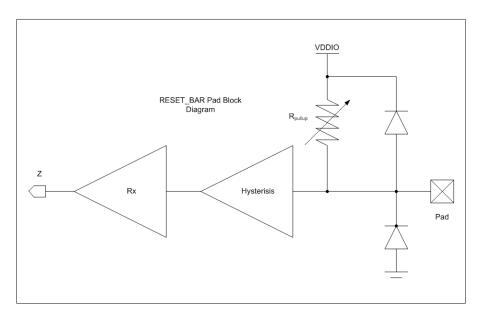

| RESET_BAR with Internal Pull-UP                                                | 58                 |

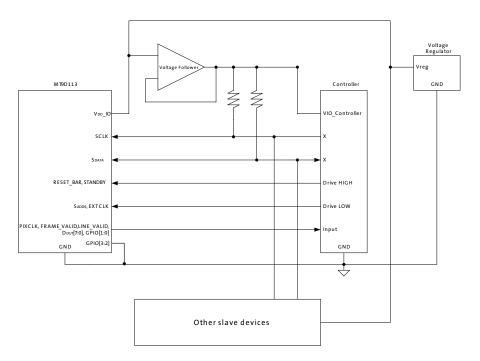

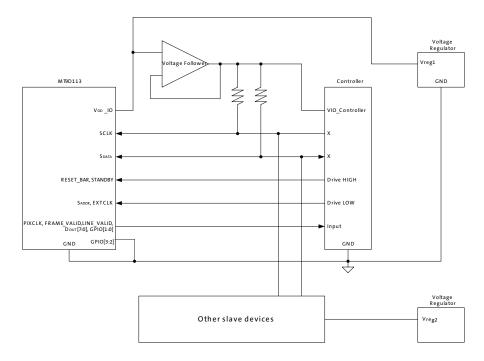

| Recommended System and Test Setup with Multiple Serial Interface Slave Devices | 59                 |

| Test Sequence for Measuring VDD_IO Current at Hard Standby Mode                | 62                 |

| Conclusion                                                                     | 62                 |

| Pavision History                                                               | 63                 |

# **List of Figures**

| Figure 1:  | Typical Configuration (connection)                                                                     |

|------------|--------------------------------------------------------------------------------------------------------|

| Figure 2:  | SOC Block Diagram9                                                                                     |

| Figure 3:  | Firmware Architecture                                                                                  |

| Figure 4:  | External Host Register Map11                                                                           |

| Figure 5:  | Two-Wire Serial Control Bus Timing                                                                     |

| Figure 6:  | Sensor Core Block Diagram14                                                                            |

| Figure 7:  | Pixel Color Pattern Detail (Top Right Corner)14                                                        |

| Figure 8:  | Imaging a Scene                                                                                        |

| Figure 9:  | 6 Pixels in Normal and Column Mirror Readout Modes17                                                   |

| Figure 10: | Six Rows in Normal and Row Mirror Readout Modes                                                        |

| Figure 11: | Eight Pixels in Normal and Column Skip 2X Readout Modes18                                              |

| Figure 12: | Pixel Readout (no skipping)                                                                            |

| Figure 13: | Pixel Readout (x_odd_inc = 3, y_odd_inc = 1)19                                                         |

| Figure 14: | Pixel Readout (x_odd_inc = 1, y_odd_inc = 3)20                                                         |

| Figure 15: | Pixel Readout (x_odd_inc = 3, y_odd_inc = 3)20                                                         |

| Figure 16: | Pixel Readout (x_odd_inc = 3, y_odd_inc = 1, x_bin = 1)                                                |

| Figure 17: | Pixel Readout (x_odd_inc = 3, y_odd_inc = 3, x_ybin = 1)                                               |

| Figure 18: | Valid Image Data24                                                                                     |

| Figure 19: | Pixel Data Timing Example24                                                                            |

| Figure 20: | Available Test Patterns                                                                                |

|            | IFP Block Diagram                                                                                      |

| Figure 22: | Gamma Correction Curve29                                                                               |

| Figure 23: | Timing of Full Frame Data or Scaled Data Passing Through the FIFO                                      |

| Figure 24: | Sequencer Finite State Machine                                                                         |

| Figure 25: | CRA vs. Image Height39                                                                                 |

| Figure 26: | Power Application Sequence Timing                                                                      |

|            | Internal Power-On Reset                                                                                |

| Figure 28: | Hard Reset Operation                                                                                   |

| Figure 29: | Soft Reset Operation                                                                                   |

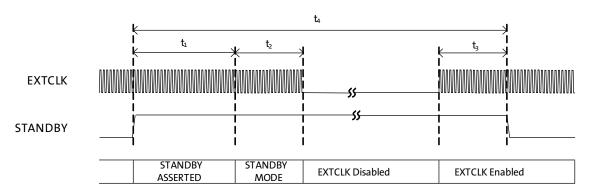

| Figure 30: | Hard Standby Mode Operation                                                                            |

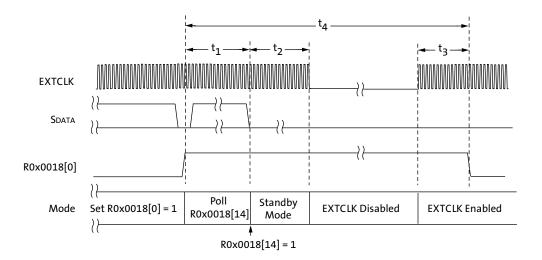

| Figure 31: | Soft Standby Mode Operation                                                                            |

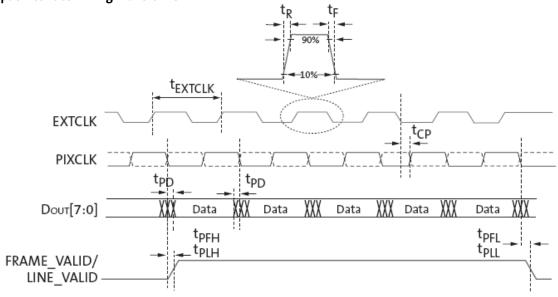

| Figure 32: | Output Interface Timing Waveforms                                                                      |

| Figure 33: | Recommended System and Test Setup for Minimum VDD_IO Power Consumption                                 |

| Figure 34: | RESET_BAR Pad Architecture                                                                             |

| Figure 35: | Recommended System and Test Setup for Minimum $\mbox{\sc Vdd}\xspace$ Power Consumption in the MT9D113 |

|            | Multiple Two-wire Serial Interface Devices59                                                           |

| Figure 36: | Recommended System and Test Setup for Minimum VDD_IO Power Consumption in the MT9D113                  |

|            | Multiple Two-wire Serial Interface Devices at Different IO Levels60                                    |

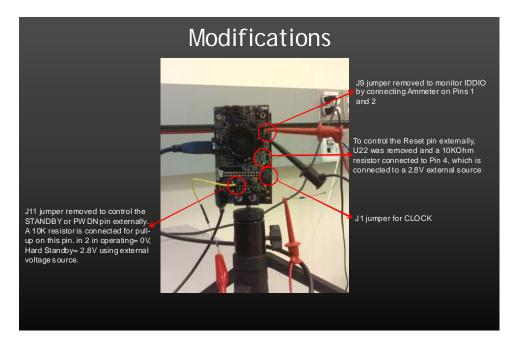

| Figure 37: | System Setup with Independent Voltage Sources for MT9D113 and Controller Chip                          |

| Figure 38: | Modifications to the Demo2 Sensor Head Board for VDD IO Current Measurement                            |

# **List of Tables**

| Table 1:  | Available Part Numbers                                                                   | 1  |

|-----------|------------------------------------------------------------------------------------------|----|

| Table 2:  | Key Performance Parameters                                                               | 1  |

| Table 3:  | Signal Description and Direction                                                         | 8  |

| Table 4:  | List of Drivers                                                                          | 10 |

| Table 5:  | Two-Wire Serial Control Bus Timing Parameters                                            | 13 |

| Table 6:  | Row Address Sequencing (Sampling)                                                        | 22 |

| Table 7:  | Row Address Sequencing (Binning)                                                         | 23 |

| Table 8:  | Data Formats Supported by MIPI Interface                                                 | 31 |

| Table 9:  | YCbCr Output Data Ordering                                                               | 32 |

| Table 10: | RGB Ordering in Default Mode                                                             | 32 |

| Table 11: | 2-Byte RGB Format                                                                        | 33 |

| Table 12: | Power Application Sequence Timing                                                        | 41 |

| Table 13: | POR Parameters                                                                           | 42 |

| Table 14: | Hard Reset                                                                               | 43 |

| Table 15: | Soft Reset Signal Timing                                                                 | 44 |

| Table 16: | Hard Standby Signal Timing                                                               | 46 |

| Table 17: | Soft Standby Signal Timing                                                               | 47 |

| Table 18: | Status of Signals During Different States                                                | 48 |

| Table 19: | GPIO Related Registers and Variables                                                     | 51 |

| Table 20: | Maximum Rating                                                                           | 52 |

| Table 21: | I/O Parameters                                                                           | 52 |

| Table 22: | AC Electricals                                                                           |    |

| Table 23: | DC Electricals                                                                           | 54 |

| Table 24: | Status of Signals During Standby State                                                   | 57 |

| Table 25: | Typical Mismatch Current in VDD_IO Due to Mismatch in RESET_BAR level and VDD_IO Level . | 58 |

|           |                                                                                          |    |

## Overview

The MT9D113 from Aptina is a complete camera system-on-a-chip (SOC) image sensor. The MT9D113 outputs sharp, clear, progressive scan images while extending the battery life of an application. It provides near-CCD image quality while maintaining a small form factor.

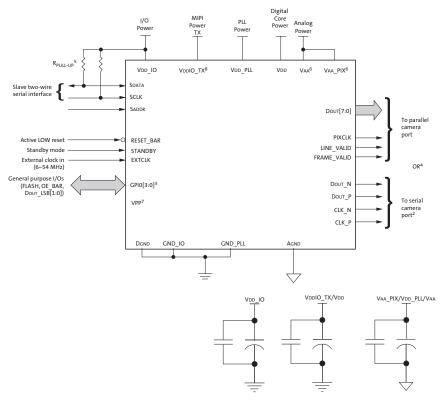

# **Typical Connections**

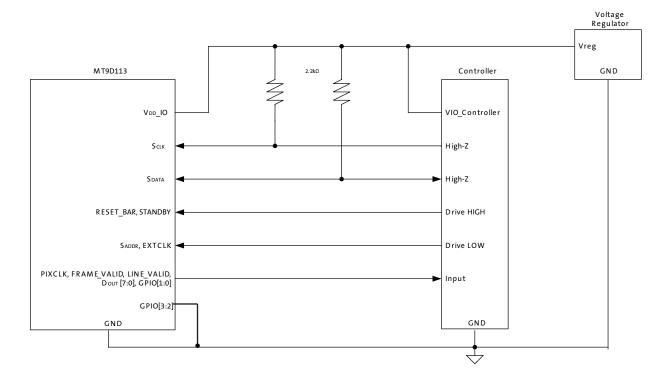

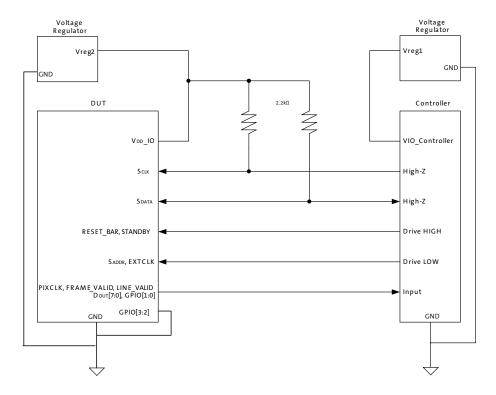

Figure 1: Typical Configuration (connection)

Notes:

- 1. This typical configuration shows only one scenario out of multiple possible variations for this sensor.

- 2. If a MIPI Interface is not required, the following pads must be left floating: DOUT\_P, DOUT\_N, CLK\_P, and CLK\_N.

- 3. The GPIO pads can serve multiple features that can be reconfigured. The function and direction will vary by applications.

- 4. Only one output mode (serial or parallel) can be used at any time.

- 5. Aptina recommends a resistor value of 1.5K $\Omega$  to VDD\_IO for the two-wire serial interface RPULL-UP; Higher values can be used for slower transmission speed.

- 6. VAA and VAA\_PIX can be tied together. Although separate decoupling capacitors are recommended for VAA and VAA\_PIX, decoupling capacitors can be shared if one would like to reduce module size.

- 7. VPP is the OTP memory programming voltage and should be left floating during normal operation.

- 8. 1.8V supply is shared by MIPI interface and VDD to reduce the number of decoupling caps, and, subsequently, the module size. VDDIO\_TX must be connected to a 1.8V power supply source, even though MIPI interface is not used.

- 9. Aptina recommends that  $0.1\mu F$  and  $1\mu F$  decoupling capacitors for each power supply are mounted as close as possible to the pad and that a  $10\mu F$  capacitor be placed nearby off-module. Actual values and results can vary depending on layout and design considerations.

- 10. VDD\_PLL and VAA can share the same power source, in which case GND\_PLL must be connected to GND.

- 11. Internal pull-up in RESET\_BAR pin and can be left floating when not connected.

# **Decoupling Capacitor Recommendations**

It is important to provide clean, well-regulated power to each power supply. The customer is ultimately responsible for ensuring that clean power is provided for their own designs because hardware design is influenced by many factors, including layout, operating conditions, and component selection.

The recommendations for capacitor placement and values listed below are based on the Aptina internal demo camera design and verified in hardware.

Aptina recommends the following, in order of preference:

- 1. Mount  $0.1\mu F$  and  $1\mu F$  decoupling capacitors for each power supply as close as possible to the pad and place a  $10\mu F$  capacitor nearby off-module.

- 2. If module limitations allow for only six decoupling capacitors for a three-regulator design (VDD1V2 tied to external regulator), use a  $0.1\mu F$  and  $1\mu F$  capacitor for each of the three regulated supplies. Aptina also recommends placing a  $10\mu F$  capacitor for each supply off-module, but close to each supply.

- 3. If module limitations allow for only three decoupling capacitors, use a  $1\mu F$  capacitor (preferred) or a  $0.1\mu F$  capacitor for each of the three regulated supplies. Aptina also recommends placing a  $10\mu F$  capacitor for each supply off-module but close to each supply.

- 4. Give priority to the VAA supply for additional decoupling capacitors.

Aptina does not recommend inductive filtering components.

Follow best practices when performing physical layout. Refer to technical note TN-09-131.

# **Signal Descriptions**

Table 1: Signal Description and Direction

| Name               | Туре                 | Description                                                         | Note |

|--------------------|----------------------|---------------------------------------------------------------------|------|

| STANDBY            | Input                | Hardware standby                                                    | 3    |

| EXTCLK             | Input                | External clock input                                                |      |

| SADDR              | Input                | Two-wire interface device select address                            |      |

| SCLK               | Input                | Two-wire interface serial clock                                     |      |

| RESET_BAR          | Input                | Hardware reset                                                      | 4    |

| CLK_N              | Output               | MIPI differential clock N                                           | 5    |

| CLK_P              | Output               | MIPI differential clock P                                           | 5    |

| Dout_N             | Output               | MIPI differential data N                                            | 5    |

| Dout_P             | Output               | MIPI differential data P                                            | 5    |

| Dout[7:0]          | Output               | Parallel image data                                                 | 1    |

| FRAME_VALID        | Output               | Parallel pixel bus frame valid                                      | 1    |

| LINE_VALID         | Output               | Parallel pixel bus line valid                                       | 1    |

| PIXCLK             | Output               | Parallel pixel bus pixel clock                                      | 1    |

| SDATA              | Bidirectional        | Two-wire interface serial data                                      |      |

| GPIO_0/Dout_LSB[0] | Bidirectional/Output | General-purpose I/O or LSB for Raw 10 data output during SOC Bypass | 2    |

| GPIO_1/Dout_LSB[1] | Bidirectional/Output | General-purpose I/O or LSB for Raw 10 data output during SOC Bypass | 2    |

| GPIO_3/OE_BAR      | Bidirectional/Output | General-purpose I/O or output enable                                | 2    |

| GPIO_2/FLASH       | Bidirectional/Output | General-purpose I/O or flash control                                | 2    |

| VAA                | Supply               | Analog core power source 2.8V nominal                               |      |

| VAA_PIX            | Supply               | Analog core power source 2.8V nominal                               |      |

| VDD                | Supply               | Digital core power source 1.8V nominal                              |      |

| VDD_IO             | Supply               | Digital IO power source 1.8V or 2.8V nominal                        |      |

| VDD_PLL            | Supply               | Digital PLL power source 2.8V nominal                               |      |

| VDDIO_TX           | Supply               | Digital MIPI IO power source 1.8V nominal.                          | 6    |

Notes

- 1. In serial only mode, Dout[7:0], PIXCLK, and GPIO[3:0] can be left floating by setting R0x0026[1] =1. If GPIO signals are required, Dout[7:0] and PIXCLK must be tied to DGND and OE\_BAR must be tied to VDD\_IO. GPIO\_3 should be configured as an input for OE\_BAR function and set R0x001A[8] = 1.

- 2. GPIO can be left floating if not used and must be programmed as outputs.

- 3. Can be left floating because of the internal pull-up resistor.

- 4. Must be connected to VDD\_IO, internal 100k ohms typical at 2.8V VDDIO used.

- 5. Can be left floating if not used.

- 6. Must be connected to VDD, even in designs where the MIPI interface is not used.

# **Architecture**

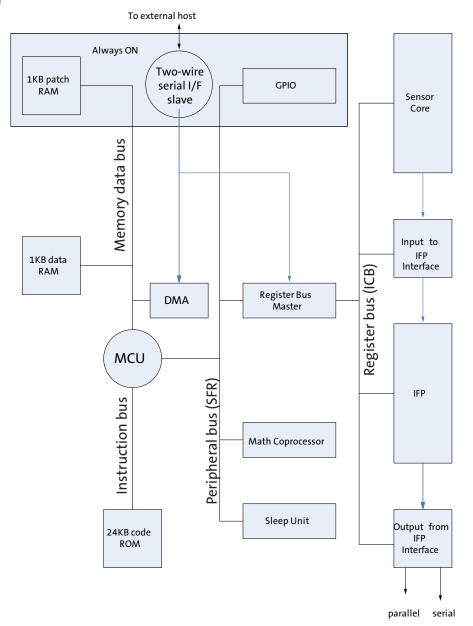

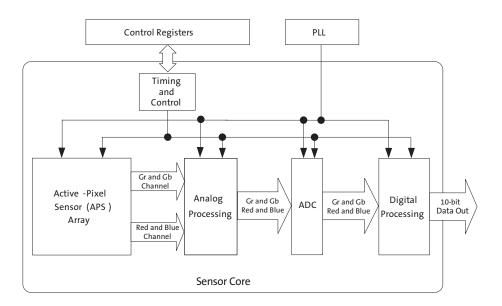

The MT9D113 from Aptina is the third-generation, two-megapixel camera SOC. It is a microprocessor-based camera system that combines a sensor core with an image flow processor (IFP) to form a standalone solution that includes image acquisition and processing. Both the sensor core and IFP have internal registers that can be accessed by an external host. In normal operation, the integrated system microprocessor autonomously controls most aspects of operation. The image data is transmitted to the external host system either through a parallel bus or a serial MIPI interface (see Figure 2).

Figure 2: SOC Block Diagram

The external host and the integrated microprocessor (MCU) can both access all the internal resources (RAM and registers). The external host always has higher priority. The following sections briefly describe the functionality of each key component of the system.

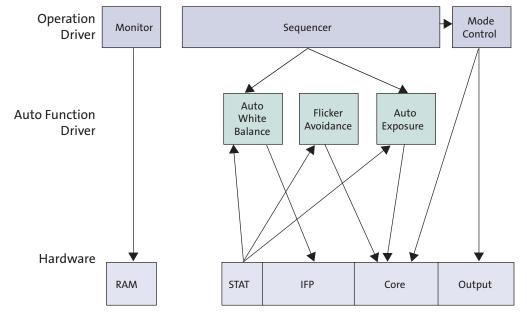

# **Firmware**

The firmware implements all automatic camera functions, such as auto exposure (AE), auto white balance (AWB), and flicker detection/avoidance (FD), as well as control functions such as sequencer, mode/context, and histogram (see Table 2). The firmware consists of drivers, generally one driver for each major automatic or control function (see Figure 3).

Table 2: List of Drivers

| ID      | Driver Name       | Description                                    |  |

|---------|-------------------|------------------------------------------------|--|

| ID = 1  | Sequencer         | Controls of camera main function               |  |

| ID = 2  | AE                | Auto exposure                                  |  |

| ID = 3  | AWB               | Auto white balance                             |  |

| ID = 4  | Flicker Detection | Flicker detection and avoidance                |  |

| ID = 7  | Mode/Context      | Context variables                              |  |

| ID = 11 | Histogram         | Reduce image flare and analyze image histogram |  |

Figure 3: Firmware Architecture

# **External Host Interface (Two-Wire Slave-Only Interface)**

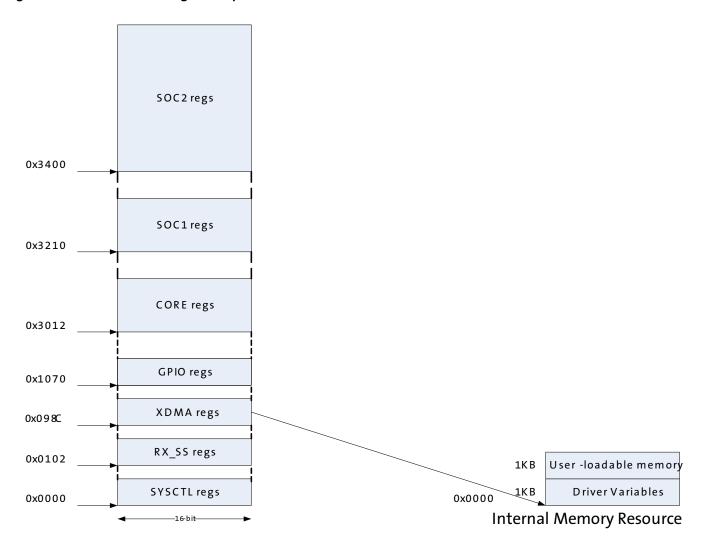

The MT9D113 will appear as a two-wire serial interface slave to the external host. Its base address is selectable by the external SADDR pin input (when SADDR = 0 then base address = 0x78; when SADDR = 1 then base address = 0x7A). There are 32K addressable 16-bit registers (that is, the starting address of each register always falls into even addresses) within the MT9D113 but not all of them are being used (see Figure 4).

Figure 4: External Host Register Map

"Appendix A - Registers" on page 56 provides detailed register explanations. Although most registers are self-explanatory, the next paragraphs contain enhanced information about XDMA registers are worth explaining here.

The XDMA registers allow the external host to indirectly access the internal memory resources of the MT9D113, which include the firmware driver variables. To access the variables that are described in "Appendix B - Driver Variables" on page 94, use logical accesses provided by the XDMA registers.

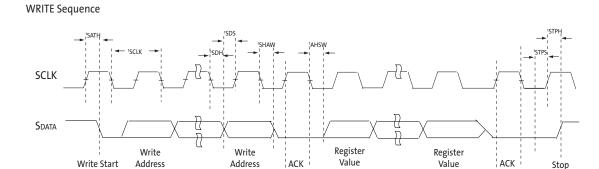

The external host interface is implemented through a two-wire interface that enables direct read/write access to hardware registers and indirect access to firmware variables within the MT9D113. The interface is designed to be compatible with the MIPI alliance standard for Camera Serial Interface 2 (CSI-2) 1.0, which uses the electrical characteristics and transfer protocols of the two-wire serial interface specifications.

The interface protocol uses a master/slave model in which a master controls one or more slave devices. The sensor acts as a slave device to the external host which acts as a master device. The master generates a clock (SCLK) that is an input to the sensor and used to synchronize the transactions at the interface.

Data is transferred between the master and the slave on a bidirectional serial data bus (SDATA). Both SCLK and SDATA are pulled up to VDD\_IO off-chip by a  $1.5 \mathrm{K}\Omega$  resistor. Either the slave or master device can drive SDATA to LOW—the interface determines which device is allowed to drive SDATA at any given time.

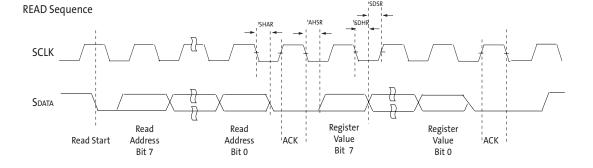

Figure 5: Two-Wire Serial Control Bus Timing

Bit 7

Bit 7

Bit 0

Bit 0

Table 3: Two-Wire Serial Control Bus Timing Parameters

| Symbol            | Definition              | Condition  | Min | Тур | Max      | Unit |

|-------------------|-------------------------|------------|-----|-----|----------|------|

| <sup>f</sup> SCLK | Serial clock frequency  | -          | 0   | _   | 400      | KHz  |

| <sup>t</sup> SCLK | Serial clock period     | -          | 2.5 | -   | $\infty$ | μs   |

| DCsclk            | Serial clock duty cycle | -          | 45  | 50  | 55       | %    |

| <sup>t</sup> SRTH | Start hold time         | Write/Read | 300 | -   | _        | ns   |

| <sup>t</sup> STPH | Stop hold time          | Write/Read | 600 | -   | _        | ns   |

| <sup>t</sup> SDH  | Sdata hold              | Write      | 300 | -   | _        | ns   |

| <sup>t</sup> SDS  | SDATA setup             | Write      | 300 | -   | _        | ns   |

| <sup>t</sup> SHAW | SDATA hold to Ack       | Write      | 300 | -   | _        | ns   |

| <sup>t</sup> AHSW | ACK hold to SDATA       | Write      | 400 | -   | _        | ns   |

| <sup>t</sup> SDHR | Sdata hold              | Read       | 300 | -   | _        | ns   |

| <sup>t</sup> SFSR | SDATA setup             | Read       | 300 | -   | _        | ns   |

| <sup>t</sup> shar | SDATA hold to ACK       | Read       | 300 | -   | -        | ns   |

| <sup>t</sup> AHSR | ACK hold to SDATA       | Read       | 300 | _   | _        | ns   |

| <sup>t</sup> R    | Rise time               | Write/Read | _   | _   | 300      | ns   |

| <sup>t</sup> F    | Fall time               | Write/Read | _   | -   | 300      | ns   |

Note:

<sup>t</sup>R and <sup>t</sup>F are dependent on system-level parameters such as the value of pull-up resistor used, how the two-wire serial bus is routed, whether there are other devices on the serial bus, and the strength of the supply used to pull-up the serial bus.

# **Always-On Power Domain**

The always-on power domain (AOPD) provides an area of functionality that will always be active while power is applied to the MT9D113. The external host interface is located in the AOPD. The domain also includes miscellaneous clock and reset controls as well as configuration registers for the sensor core, processor core, clock configuration, and clock reset control. The user-loadable patch memory is also included in this domain. This memory will remain powered when the main core power is shut down using the standby command.

### **Sensor Core**

The sensor core of the MT9D113 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate, qualified by LINE\_VALID (LV) and FRAME\_VALID (FV). The maximum pixel rate is 30 Mp/s, corresponding to a pixel clock rate of 63.25 MHz. See Figure 6 on page 14 for a block diagram of the sensor core. It includes a 2.0Mp active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. After a row is read, data from the columns are sequenced through an analog signal chain that provides offset correction and gain, and then through an ADC. The output from the ADC is a 10-bit value for each pixel in the array.

The pixel array contains optically active and light-shielded (dark) pixels. The dark pixels provide data for the offset-correction algorithms (black level control).

The sensor core contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain settings. These registers are controlled by the firmware and can be accessed through a two-wire serial interface. Register values written to the sensor core can be overwritten by firmware.

The output from the core is a Bayer pattern, where alternate rows are a sequence of either green and red pixels or blue and green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

A flash strobe output signal is provided to allow an external xenon or LED light source to synchronize with the sensor exposure time.

Figure 6: Sensor Core Block Diagram

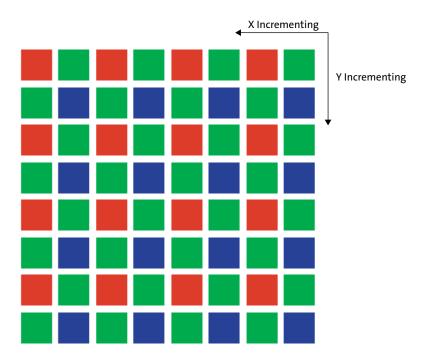

# **Pixel Array**

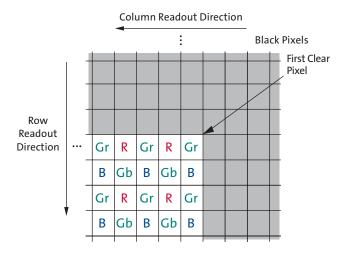

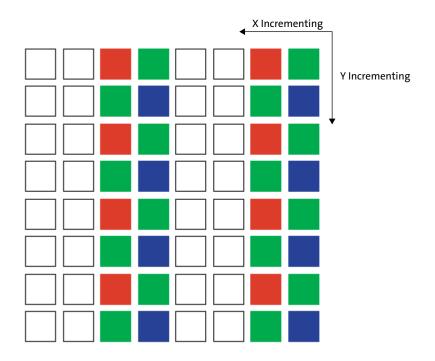

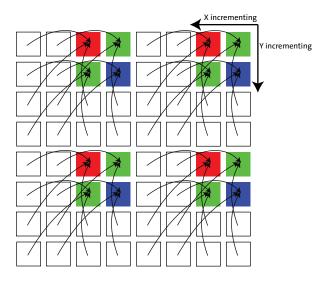

The sensor core uses a Bayer color pattern (see Figure 7). The even-numbered rows contain green and red pixels. The odd-numbered rows contain blue and green pixels. Even-numbered columns contain green and blue pixels. Odd-numbered columns contain red and green pixels.

Figure 7: Pixel Color Pattern Detail (Top Right Corner)

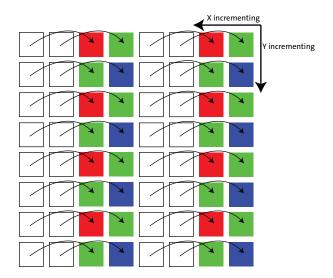

## **Default Readout Order**

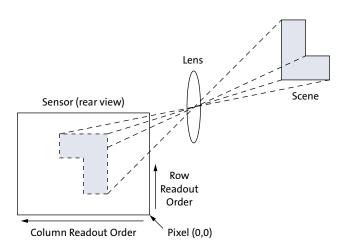

By convention, the sensor core pixel array is shown with pixel (0,0) in the top right corner. This reflects the actual layout of the array on the die. When the sensor is operating in a system, the active surface of the sensor faces the scene (see Figure 8).

When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced. By convention, data from the sensor is shown with the first pixel read out in the case of the sensor core in the top left corner.

Figure 8: Imaging a Scene

# **Analog Processing**

# **Analog Readout Channel**

The sensor core features an analog readout channel, (see Figure 6 on page 14). The readout channel consists of a gain stage, a sample-and-hold stage with black level calibration capability, and a 10-bit ADC.

## **Gain Options**

The MT9D113 provides per-color gain control as well as the option of global gain control. The per-color and global gain control can be used interchangeably. A WRITE to a global gain register is aliased as a WRITE of the same data to the four associated color-dependent gain registers.

Integer digital gains in the range 0–7 can be programmed. A digital gain of 0 sets all pixel values to 0 (the pixel data will simply represent the value applied by the pedestal block). Gain settings are updated in every frame by the MCU auto functions such as AWB, AE, and FD. To make manual adjustments to gain settings, the MCU automatic exposure and automatic white balance adjustment features must be disabled.

## **Integration Time**

The integration time (exposure) of the MT9D113 is controlled by variables. While coarse integration time controls the integration duration in terms of row times, fine integration time allows for sub-row times accuracy in terms of pixel clocks. Integration time is updated in every frame by the MCU auto feature. Disable the MCU auto features to make manual adjustments to integration time.

Because of the basic operation of the Electronic Roller Shutter (ERS), it is not advisable to set an integration time that is greater than the frame time.

It is not necessary to reprogram the frame time on the MT9D113 to make longer integration times available because the frame time adjusts automatically. However, long integration times increase the likelihood of image degradation because of increased accumulation of dark current.

If the integration time is changed while FV is asserted for frame n, the first frame output using the new integration time is frame (n + 2). The sequence is as follows:

- 1. During frame *n*, the new integration time is held in the pending register.

- 2. At the start of frame (n + 1), the new integration time is transferred to the live register. Integration for each row of frame (n + 1) has been completed using the old integration time.

- 3. The earliest time that a row can start integrating using the new integration time is immediately after that row has been read for frame (n + 1).

- 4. When frame (n + 2) is read out, it will have been integrated using the new integration time

If the integration time is changed on successive frames, each value written will be applied for a single frame; the latency between writing a value and it affecting the frame readout remains at two frames.

When the integration time and the gain are changed at the same time, the gain update is held off by one frame so that the first frame output with the new integration time also has the new gain applied.

#### **PLL-Generated Master Clock**

The PLL can generate a master clock signal whose frequency is up to 85 MHz (input clock from 6 MHz through 54 MHz).

## **PLL Setup**

Because the input clock frequency is unknown, the sensor starts up with the PLL disabled. The PLL takes time to power up. During this time, the behavior of its output clock signal is not guaranteed. The PLL output frequency is determined by two constants, M and N, and the input clock frequency.

$$VCO = \frac{Fin \times 2 \times M}{N+1}$$

$$PLL \ output \ frequency = \frac{VCO}{P1+1}$$

(EQ 1)

# **Digital Processing**

# **Readout Options**

The sensor core supports different readout options to modify the image before it is sent to the IFP. The readout can be limited to a specific window of the original pixel array.

For preview modes, the sensor core supports both skipping and pixel averaging in x and y directions.

By changing the readout direction the image can be flipped in the vertical direction and/or mirrored in the horizontal direction.

### Window Size

The image output size is set with registers x\_addr\_start, x\_addr\_end, y\_addr\_start, and y\_addr\_end. The edge pixels in the 1600 x 1200 array are present to avoid edge defects and should not be included in the visible window. Binning will change the image output size

### **Readout Modes**

## **Horizontal Mirror**

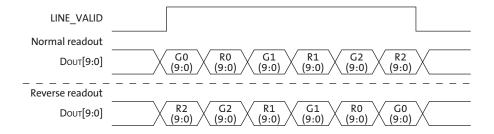

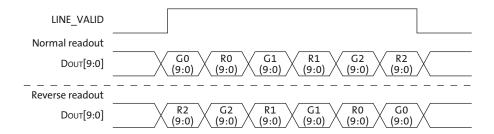

When the sensor is configured to mirror the image horizontally, the order of pixel readout within a row is reversed, so that readout starts from  $x_addr_end$  and ends at  $x_addr_start$ . Figure 9 shows a sequence of 6 pixels being read out with normal readout and reverse readout. The SOC corrects for this change in sensor core output.

Figure 9: 6 Pixels in Normal and Column Mirror Readout Modes

## **Vertical Flip**

When the sensor is configured to flip the image vertically, the order in which pixel rows are read out is reversed, so that row readout starts from y\_addr\_end and ends at y\_addr\_start. Figure 10 shows a sequence of six rows being read out with normal readout and reverse readout. The SOC corrects for this change in sensor core output.

Figure 10: Six Rows in Normal and Row Mirror Readout Modes

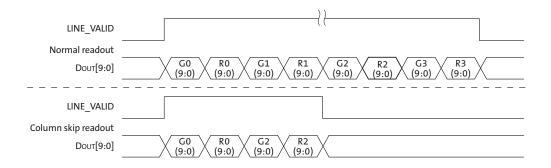

## Column and Row Skip

The sensor core supports subsampling. Subsampling reduces the amount of data processed by the analog signal chain in the sensor and thereby allows the frame rate to be increased. This reduces the amount of row and column data processed and is equivalent to the skip2 readout mode provided by earlier Aptina image sensors. Set the proper image output and crop sizes before enabling subsampling.

Figure 11: Eight Pixels in Normal and Column Skip 2X Readout Modes

#### **Pixel Readouts**

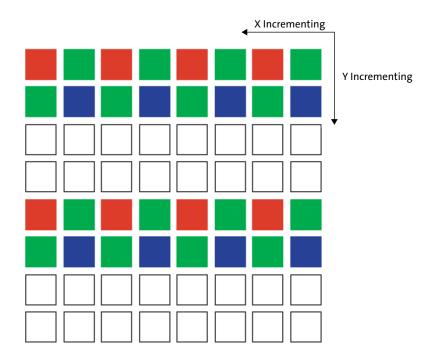

Figures 12 through Figure 15 on page 20 show a sequence of data being read out with no skipping, with  $x\_odd\_inc = 3$  and  $y\_odd\_inc = 1$ , with  $x\_odd\_inc = 1$  and  $y\_odd\_inc = 3$ , and with  $x\_odd\_inc = 3$  and  $y\_odd\_inc = 3$ .

Figure 12: Pixel Readout (no skipping)

Figure 13: Pixel Readout (x\_odd\_inc = 3, y\_odd\_inc = 1)

Figure 14: Pixel Readout (x\_odd\_inc = 1, y\_odd\_inc = 3)

Figure 15: Pixel Readout (x\_odd\_inc = 3, y\_odd\_inc = 3)

## **Programming Restrictions when Skipping**

When skipping is enabled as a viewfinder mode, and the sensor is switched back and forth between full resolution and skipping, keep *line\_length\_pck* constant. This allows the same integration times to be used in each mode.

When subsampling is enabled, it might be necessary to adjust the  $x_addr_end$  and  $y_addr_end$  settings. The values for these registers must correspond with rows/ columns that form part of the subsampling sequence. Use the following rules to make the adjustment.

$$remainder = (addr\_end - addr\_start + 1) AND 4$$

(EQ 2)

$$if (remainder == 0) \ addr\_end = addr\_end - 2$$

(EQ 3)

Table 4 shows the row address sequencing for normal and subsampled (with  $y\_odd\_inc = 3$ ) readout. The same sequencing applies to column addresses for subsampled readout. Because the subsampling sequence only reads half of the rows and columns, there are two possible subsampling sequences, depending upon the alignment of the start address.

Table 4: Row Address Sequencing (Sampling)

| Normal | Subsampled Sequence 1 | Subsampled Sequence 2 |

|--------|-----------------------|-----------------------|

| 0      | 0                     | No data               |

| 1      | 1                     | No data               |

| 2      | No data               | 2                     |

| 3      | No data               | 3                     |

| 4      | 4                     | No data               |

| 5      | 5                     | No data               |

| 6      | No data               | 6                     |

| 7      | No data               | 7                     |

## **Binning**

The MT9D113 sensor core supports 2 x 1 and 2 x 2 analog binning (column binning, also called x-binning and row/column binning, also called xy-binning). Binning has many of the same characteristics as subsampling. However, because binning gathers image data from all pixels in the active window, rather than from a subset of pixels, it achieves superior image quality and avoids the aliasing artifacts that can be a characteristic side effect of subsampling.

Enable binning by selecting the appropriate subsampling settings ( $x\_odd\_inc = 3$  and  $y\_odd\_inc = 1$  for x-binning,  $x\_odd\_inc = 3$  and  $y\_odd\_inc = 3$  for xy-binning) and setting the appropriate binning bit in read\_mode register. As for subsampling,  $x\_addr\_end$  and  $y\_addr\_end$  might require adjustment when binning is enabled.

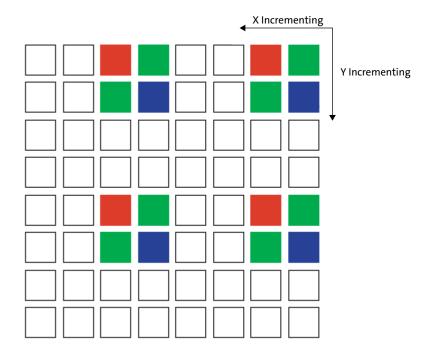

The effect of the different subsampling settings is shown in Figure 16 and in Figure 17 on page 23.

Figure 16: Pixel Readout (x\_odd\_inc = 3, y\_odd\_inc = 1, x\_bin = 1)

Figure 17: Pixel Readout (x\_odd\_inc = 3, y\_odd\_inc = 3, x\_ybin = 1)

## **Binning Limitations**

Binning requires a different sequencing of the pixel array and imposes different timing limits on the operation of the sensor. In particular, xy-binning requires two READ operations from the pixel array for each line of output data, which has the effect of increasing the minimum line blanking time.

As a result, when xy-binning is enabled, some of the programming limits declared in the parameter limit registers are no longer valid. In addition, the default values for some of the manufacturer-specific registers need to be reprogrammed. None of these adjustments are required for x-binning. The sensor must be taken out of streaming mode before switching between binned and non-binned operation. The row addresses for various binning modes are shown in Table 5.

Table 5: Row Address Sequencing (Binning)

| Normal | Binning Sequence 1 | Binning Sequence 2 |

|--------|--------------------|--------------------|

| 0      | 0, 2               | No data            |

| 1      | 1, 3               | No data            |

| 2      | No data            | 2, 4               |

| 3      | No data            | 3, 5               |

| 4      | 4, 6               | No data            |

| 5      | 5, 7               | No data            |

| 6      | No data            | 6, 8               |

| 7      | No data            | 7, 9               |

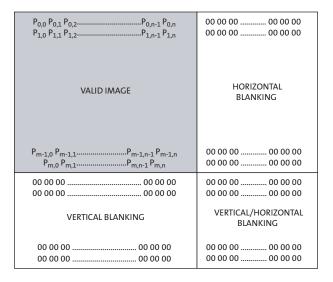

## **Raw Data Format**

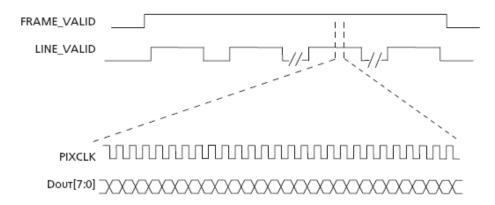

The sensor core image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking, (see Figure 18). The amount of horizontal blanking and vertical blanking is programmable. LV is HIGH during the shaded region of the figure.

Figure 18: Valid Image Data

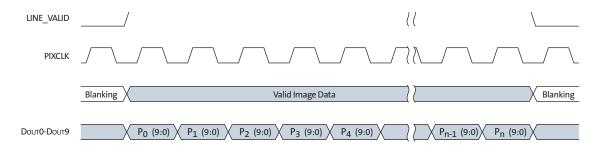

## **Raw Data Timing**

The sensor core output data is synchronized with the PIXCLK output. When LV is HIGH, one pixel's data is output on the 10-bit DOUT output bus every PIXCLK period. By default, the PIXCLK signal runs at the same frequency as the master clock, and its falling edges occur one-half of a master clock period after transitions on LV, FV, and DOUT[9:0] (see Figure 19). This allows PIXCLK to be used as a clock to sample the data. PIXCLK is continuously enabled, even during the blanking period.

Figure 19: Pixel Data Timing Example

# Input Interface to Image Flow Processor

The input interface to the IFP is the front end of the IFP, in which it will choose between the sensor core output or a test pattern generator output. During normal operation, a stream of raw Bayer image data from the sensor is continuously fed into the IFP. For testing purposes, the test generator output is selected. The generator provides a selection of test patterns sufficient for basic testing of the IFP. Program variable (ID=7, Offset=0x66) followed by REFRESH command to the sequencer in order to access different test patterns (see Figure 20).

Depending on which test pattern has been selected, the user might need to program additional registers in order to see the intended effects.

Figure 20: Available Test Patterns

| Test Pattern       | Registers/Variables                                                                                                                                                                                                                | Example |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Flat Field         | mode_common<br>settings_test_mode<br>(ID=7, Offset=0x66)=1<br>test_pxl_red (R0x0102) = 0x1ff<br>test_pxl_g2 (R0x0106) = 0x1ff<br>test_pxl_g2 (R0x0106) = 0x1ff<br>test_pxl_g2 (R0x0106) = 0x1ff<br>test_pxl_blue (R0x0108) = 0x1ff |         |

| Vertical Ramp      | mode_common_<br>mode_settings<br>test_mode<br>(ID=7, Offset=0x66)=2                                                                                                                                                                |         |

| Color Bar          | mode_common_<br>mode_settings<br>test_mode<br>(ID=7, Offset=0x66)=3                                                                                                                                                                |         |

| Vertical Stripes   | mode_common<br>settings_test_mode<br>([D=7, Offset_mode)=0.4]ff<br>test_pxl_red (R0x0104) = 0x17d<br>test_pxl_g1 (R0x0104) = 0x104<br>test_pxl_g2 (R0x0106) = 0x000<br>test_pxl_blue (R0x0108) = 0x000                             |         |

| Pseudo-Random      | mode_common_mode<br>settings_test_mode<br>(ID=7, Offset=0x66)=5                                                                                                                                                                    |         |

| Horizontal Stripes | mode_common settings_test_mode ((l0=7,0ffset=0x69)=6 test_pxi_red (R0x0102) = 0x1ff test_pxi_g1 (R0x0104) = 0x17d test_pxi_g2 (R0x0106) = 0x000 test_pxi_blue (R0x0108) = 0x000                                                    |         |

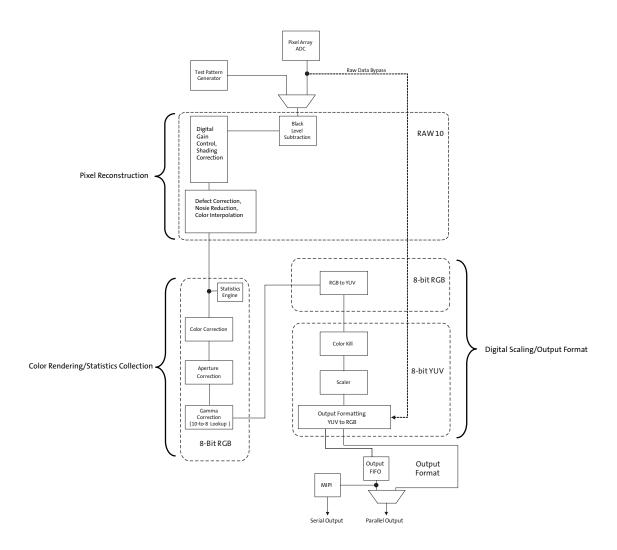

# **Image Flow Processor**

Most IFP functions can be controlled directly by the MCU. The external host will control it indirectly through the driver variables. IFP processing can be broken into three different phases: pixel reconstruction, color rendering/statistics collection, and digital scaling/output format. Figure 21 shows a simplified IFP block diagram and the operating color space at each processing phase.

Figure 21: IFP Block Diagram

## **Pixel Reconstruction (Lens Shading Correction)**

## First Black Level Subtraction and Digital Gain

Image stream processing starts with black level subtraction and multiplication of all pixel values by a programmable digital gain. Both operations can be independently set to separate values for each color channel (R, Gr, Gb, B). Independent color channel digital gain can be adjusted with registers. Independent color channel black level adjustments can also be made. If the black level subtraction produces a negative result for a particular pixel, the value of this pixel is set to "0."

## **Shading Correction (SC)**

Lenses tend to produce images whose brightness is significantly attenuated near the edges. Other factors also cause fixed pattern signal gradients in images captured by image sensors. The cumulative result of all factors is known as image shading. The MT9D113 has an embedded shading correction module that can be programmed to counter the shading effects on each individual R, Gb, Gr, and B color signal.

#### The Correction Function

Color-dependent solutions are calibrated using the sensor, lens system, and an image of an evenly illuminated, featureless grey calibration field. The color correction functions can be derived from the resulting image.

The correction functions can then be applied to each pixel value to equalize the response across the image as follows:

$$P_{corrected}(row,col) = P_{sensor}(row,col) * f(row,col)$$

(EQ 4)

where *P* are the pixel values and *f* is the color dependent correction functions for each color channel.

#### **Defect Correction**

The IFP performs continuous defect correction that can mask pixel array defects such as high dark-current (hot) pixels and pixels that are darker or brighter than their neighbors due to photoresponse nonuniformity. The module is edge-aware with exposure that is based on configurable thresholds. The thresholds are changed continuously based on the brightness of the current scene.

#### Noise Reduction

Noise reduction can be enabled or disabled. Thresholds can be set through register settings.

# Color Interpolation and Edge Detection

In the raw data stream fed by the sensor core to the IFP, each pixel is represented by a 10-bit integer number, which can be considered proportional to the pixel's response to a one-color light stimulus, red, green, or blue, depending on the pixel's position under the color filter array. Initial data processing steps—up to and including the defect correction—preserve the one-color-per-pixel nature of the data stream. After the defect correction, the data stream must be converted to a three-colors-per-pixel stream appropriate for standard color processing. The conversion is done by an edge-sensitive color interpolation module. The module pads the incomplete color information available for each pixel with information extracted from an appropriate set of neighboring pixels. The algorithm used to select this set and extract the information seeks the best compromise between preserving edges and filtering out high frequency noise in flat field areas. The edge threshold can be set through register settings.

## **Aperture Correction**

To increase image sharpness, a programmable 2D aperture correction (sharpening filter) is applied to color-corrected image data. The gain and threshold for 2D correction can be defined through variable settings.

## **Color Rendering/Statistics Collection (Color Correction)**

#### **Color Correction**

To achieve good color fidelity of the IFP output, interpolated RGB values of all pixels are subjected to color correction. The IFP multiplies each vector of three pixel colors by a 3 x 3 color correction matrix. The three components of the resulting color vector are all sums of three 10-bit numbers. Because such sums can have up to 12 significant bits, the bit width of the image data stream is widened to 12 bits per color (36 bits per pixel). The color correction matrix can be programmed by the user or automatically selected by the AWB algorithm implemented in the IFP. Ideally, color correction should produce output colors that are independent of the spectral sensitivity and color crosstalk characteristics of the image sensor. The optimal values of the color correction matrix elements depend on those sensor characteristics and on the spectrum of light incident on the sensor. The color correction variables can be adjusted through register settings.

## **Image Cropping**

By configuring the cropped and output windows to various sizes, different zooming levels (for example 4X, 2X, and 1X) can be achieved. The location of the cropped window is also configurable so that panning is also supported. A separate cropped window is defined for context A and context B. In both contexts, the height and width definitions for the output window must be equal to or smaller than the cropped image.

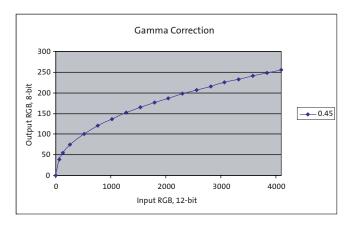

### **Gamma Correction**

The gamma correction curve (see Figure 22 on page 29) is implemented as a piecewise linear function with 19 knee points, taking 12-bit arguments and mapping them to 8-bit output. The abscissas of the knee points are fixed at 0, 64, 128, 256, 512, 768, 1024, 1280, 1536, 1792, 2048, 2304, 2560, 2816, 3072, 3328, 3584, 3840, and 4096. The 8-bit ordinates are programmable through IFP registers.

The MT9D113 IFP includes a block for gamma correction that can adjust its shape based on brightness to enhance the performance under certain lighting conditions. Two custom gamma correction tables can be uploaded, one corresponding to a brighter lighting condition, the other corresponding to a darker lighting condition. At power-up, the IFP loads the two tables with default values. The final gamma correction table used depends on the brightness of the scene and can take the form of either uploaded tables or an interpolated version of the two tables. A single (non-adjusting) table for all conditions can also be used.

Figure 22: Gamma Correction Curve

Color Kill

A color kill circuit is included to remove high or low light color artifacts. It affects only pixels whose luminance exceeds a certain preprogrammed threshold. The U and V values of those pixels are attenuated proportionally to the difference between their luminance and the threshold.

## **Digital Scaling/Output Format**

**Special Effects**

Special effects like negative image, sepia, or black and white can be applied to the data stream at this point. These effects can be enabled and selected by registers.

**RGB to YUV Conversion**

For further processing, the data is converted from RGB color space to YUV color space.

**YUV Color Filter**

As an optional processing step, noise suppression by one-dimensional low-pass filtering of Y and/or UV signals is possible. A 3- or 5-tap filter can be selected for each signal.

**Image Scaling**

The IFP includes a scaler module to ensure that the size of images output by the MT9D113 can be tailored to the needs of all users. When enabled, this module performs rescaling of incoming images—shrinks them to arbitrarily selected width and height without reducing the field of view and without discarding any pixel values.

The scaler performs pixel binning—divides each input image into rectangular bins corresponding to individual pixels of the desired output image, averages pixel values in these bins, and assembles the output image from the bin averages. Pixels lying on bin boundaries contribute to more than one bin average; their values are added to bin-wide sums of pixel values with fractional weights. The entire procedure preserves all image information that can be included in the downsized output image and filters out high frequency features that could cause aliasing.

Use the image cropping and scaler module together to implement a digital zoom and pan. If the scaler is programmed to output images smaller than images coming from the sensor core, zoom effect can be produced by cropping the latter from their maximum

size down to the size of the output images. The ratio of these two sizes determines the maximum attainable zoom factor. For example, a  $1600 \times 1200$  image rendered on a  $250 \times 150$  display can be zoomed up to eight times, because 1280/160 = 1024/128 = 8. A panning effect can be achieved by fixing the size of the crop-

1280/160 = 1024/128 = 8. A panning effect can be achieved by fixing the size of the cropping window and moving it around the pixel array.

# YUV-to-RGB/YUV Conversion and Output Formatting

The YUV data stream emerging from the scaling module can either exit the color pipeline as-is or be converted before exit to an alternative YUV or RGB data format.

#### **Color Conversion Formulas**

Y'U'V'

This conversion is ITU-R BT.601 scaled to make YUV range from 0 through 255. This setting is recommended for JPEG encoding and is the most popular.

$$Y' = 0.299 \times R' + 0.587 \times G' + 0.114 \times B'$$

(EQ 5)

$$U' = 0.564 \times (B' - Y') + 128$$

(EQ 6)

$$V' = 0.713 \times (R' - Y') + 128$$

(EQ 7)

There is an option where 128 is not added to U'V'.

# Y'Cb'Cr' Using sRGB Formulas

The MT9D113 implements the sRGB standard. This option provides YCbCr coefficients for a correct 4:2:2 transmission.

**Note:** 16 < Y' < 235; 16 < Cb < 240; 16 < Cr < 240; and  $0 \ge RGB \ge 255$

$$Y' = (0.2126 \times R' + 0.7152 \times G' + 0.0722 \times B') \times (219/256) + 16$$

(EQ 8)

$$Cb' = 0.5389 \times (B' - Y') \times (224/256) + 128$$

(EO 9)

$$Cr' = 0.635 \times (R' - Y') \times (224/256) + 128$$

(EQ 10)

### Y'U'V' Using sRGB Formulas

Similar to the previous set of formulas, but has YUV spanning a range of 0 through 255.

$$Y' = 0.2126 \times R' + 0.7152 \times G' + 0.0722 \times B'$$

(EQ 11)

$$U' = 0.5389 \times (B' - Y') + 128 = -0.1146 \times R - 0.3854 \times G + 0.5 \times B$$

(EQ 12)

$$V' = 0.635 \times (R' - Y') + 128 = 0.5 \times R - 0.4542 \times G - 0.0458 \times B$$

(EQ 13)

There is an option to disable adding 128 to U'V'. The reverse transform is as follows:

$$R' = Y + 1.5748 \times V$$

(EQ 14)

$$G' = Y - 0.1873 \times (U - 128) - 0.4681 \times (V - 128)$$

(EQ 15)

$$B' = Y + 1.8556 \times (U - 128)$$

(EQ 16)

# **Output Interface from IFP**

The output interface contains parallel image bus, MIPI serial bus interfaces, and walking 1s connectivity test generator.

## **Parallel and MIPI Output**

The user can select to use either the serial MIPI output or the 10-bit parallel output to transmit the data. Only one of the output modes can be used at any time.

The parallel output can be used with an output FIFO whose memory is shared with the MIPI output FIFO to retain a constant pixel output clock independent from the scaling factor.

When scaling the image or skipping lines, the data would be generated in bursts and the pixel clock would turn on and off in intervals, which might lead to EMI problems. The output FIFO will group all active pixel data together so the pixel clock can be run at a constant speed.

The MIPI output transmitter implements a serial differential sub-LVDS transmitter capable of up to 640~Mb/s. It supports multiple formats, error checking, and custom short packets.

The virtual channel could be used by host MIPI RX circuits to differentiate between preview and capture image data if the FW changes the channel number when switching between contexts. The host cannot adequately time this switching of contexts and so cannot use channel number in this way without FW support.

The hardware supports a configurable MIPI virtual channel in the MIPI Control register (R0x3400). Firmware provides two variables that allow the MIPI virtual channel to be changed according to context (preview/A, capture/B). The host can specify what channel is used for which context through these variables.

Table 6: Data Formats Supported by MIPI Interface

| Data Format   | Data Type |

|---------------|-----------|

| YUV 422 8-bit | 0x1E      |

| 565RGB        | 0x22      |

| 555RGB        | 0x21      |

| 444RGB        | 0x20      |

| RAW8          | 0x2A      |

| RAW10         | 0x2B      |

Note: Data will be packed as RAW8 if the data type specified does not match any of the above data types.

## **Output Format and Timing**

## YUV/RGB Output

YUV or RGB data can be output either directly from the output formatting block or through a FIFO buffer with a capacity of 1024 bytes. This size is large enough to hold one-fourth of a scan line at full resolution. Buffering of data is a way to equalize the data output rate when image scaling is used. Scaling produces an intermittent data stream consisting of short high-rate bursts separated by idle periods. High pixel clock frequency during bursts may be undesirable due to EMI concerns.

Figure 23 shows the output timing of a YUV/RGB scan line when a scaled data stream is equalized by buffering or when no scaling takes place. The pixel clock frequency remains constant during each LV high period. Scaled data is output at a lower frequency than full size frames, which helps to reduce EMI.

Figure 23: Timing of Full Frame Data or Scaled Data Passing Through the FIFO

## YUV/RGB Data Ordering

The MT9D113 supports swapping YCbCr mode (see Table 7).

Table 7: YCbCr Output Data Ordering

| Mode              | Data Sequence   |                 |                  |                  |

|-------------------|-----------------|-----------------|------------------|------------------|

| Default (no swap) | Cb <sub>i</sub> | Yi              | Cri              | Y <sub>i+1</sub> |

| Swapped CrCb      | Cr <sub>i</sub> | Yi              | Cb <sub>i</sub>  | Y <sub>i+1</sub> |

| Swapped YC        | Yi              | Cb <sub>i</sub> | Y <sub>i+1</sub> | Cr <sub>i</sub>  |

| Swapped CrCb, YC  | Yi              | Cr <sub>i</sub> | Y <sub>i+1</sub> | Cb <sub>i</sub>  |

The RGB output data ordering in default mode is shown in Table 8. The odd and even bytes are swapped when luma/chroma swap is enabled. R and B channels are bitwise swapped when chroma swap is enabled.

Table 8: RGB Ordering in Default Mode

| Mode (Swap Disabled) | Byte | $D_7D_6D_5D_4D_3D_2D_1D_0$ |

|----------------------|------|----------------------------|

| 565RGB               | Odd  | $R_7R_6R_5R_4R_3G_7G_6G_5$ |

|                      | Even | $G_4G_3G_2B_7B_6B_5B_4B_3$ |

## Table 8: RGB Ordering in Default Mode (continued)

| Mode (Swap Disabled) | Byte | $D_7D_6D_5D_4D_3D_2D_1D_0$                                                                                 |

|----------------------|------|------------------------------------------------------------------------------------------------------------|

| 555RGB               | Odd  | 0 R <sub>7</sub> R <sub>6</sub> R <sub>5</sub> R <sub>4</sub> R <sub>3</sub> G <sub>7</sub> G <sub>6</sub> |

|                      | Even | $G_4G_3G_2B_7B_6B_5B_4B_3$                                                                                 |

| 444xRGB              | Odd  | $R_7R_6R_5R_4G_7G_6G_5G_4$                                                                                 |

|                      | Even | B <sub>7</sub> B <sub>6</sub> B <sub>5</sub> B <sub>4</sub> 0 0 0 0                                        |

| x444RGB              | Odd  | 0 0 0 0 R <sub>7</sub> R6 <sub>6</sub> R <sub>5</sub> R <sub>4</sub>                                       |

|                      | Even | $G_7G_6G_5G_4B_7B_6B_5B_4$                                                                                 |

## 10-Bit Bypass Output

Raw 10-bit Bayer data from the sensor core can be output in bypass mode in two ways:

- 1. Using eight data output signals (DOUT[7:0]) and GPIO[1:0]. The GPIO signals are the lowest two bits of data.

- 2. Using only eight signals (DOUT[7:0]) and a special 8 + 2 data format, shown in Table 9.

# Table 9: 2-Byte RGB Format

| Byte       | Bits Used                   | Bit Sequence                       |

|------------|-----------------------------|------------------------------------|

| Odd bytes  | 8 data bits                 | $D_9D_8D_7D_6D_5D_4D_3D_2$         |

| Even bytes | 2 data bits + 6 unused bits | 00000D <sub>1</sub> D <sub>0</sub> |

**FIFO**

During normal pipeline operation, the output data rate is determined by a number of factors: input image size, degree of scaling, and sensor operation mode. As these parameters change during normal sensor operation, output frequency changes. This output frequency may generate RF noise, interfering with the mobile device. By using an output FIFO to maintain a constant output clock frequency, noise is easily filtered out.

The FIFO accumulates data and after a certain number of bytes are stored, it will output them in a single burst, making sure that the data rate within the burst remains constant. This approach utilizes a free-running clock, thus making possible minimal RF interference.

# **Control Functions**

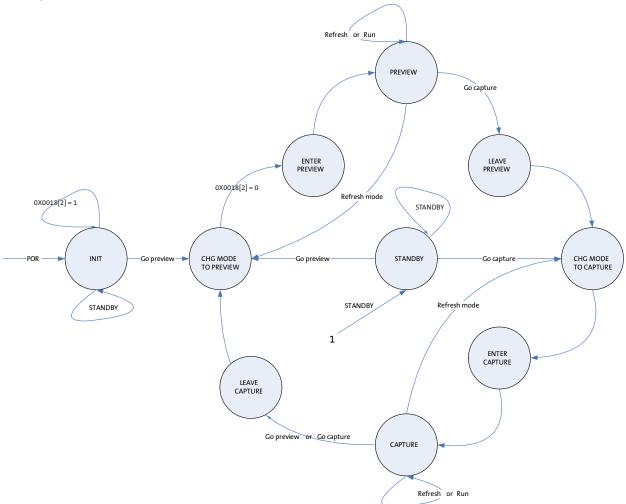

# **Sequencer: Camera Operating System**

The sequencer is a finite state machine that controls the general operations of the camera and switching between operating modes. Camera operation is organized in states such as enter preview, preview, leave preview, enter capture, and capture. The sequencer carries out a number of commands such as run, go preview, go capture, refresh, and refresh mode. The current state of the sequencer is indicated in a variable seqr.state. To execute a command, the user must set a particular command number in the variable *seqr.cmd*. Aptina recommends that the external host monitor *seqr.state* to know when to change resolution or capture frames.

Each state has its configuration; therefore, the user should set up the state configuration to customize the camera configuration before executing the corresponding program such as GO TO CAPTURE. A typical camera operating scenario is:

- 1. Configure mode variables after hardware reset.

- 2. Configure preview mode.

- 3. Execute sensor REFRESH program.

- 4. Run in preview until shutter button is pressed.

- 5. Capture a frame.

Figure 24: Sequencer Finite State Machine

Note: Any state except INIT can transition to Standby state by either hard standby or soft standby.

### **Mode: Context Information**

The mode driver reduces integration efforts by managing most aspects of switching the two contexts. It remembers vital register values for each image acquisition context and loads these values to the appropriate registers in the IFP upon context switching.

For the mode driver variables to take effect, the user changes the variable values in the mode driver (ID = 7). Upon the next mode change or sequencer's REFRESH command, these driver variable values will be loaded to the appropriate physical sensor core and IFP registers. The image processing will take the new values at the beginning of the next frame acquired.

To control the output image size, the user can modify the mode driver variables such as <code>output\_width\_A</code>, <code>output\_height\_A</code>, <code>output\_width\_B</code>, and <code>output\_height\_B</code>. The mode driver will automatically apply any appropriate downscaling filter to achieve this output image size as well as update the watermark of the output FIFO. It is important to set up the sensor core to output an image equal to or larger than the crop window size, which in turn is equal to or larger than the desired output image size.

## **Camera Functions**

# **Simple Rule-based Auto Exposure**

The AE algorithm performs automatic adjustments of the image brightness by controlling exposure time and analog gains of the sensor core as well as digital gains applied to the image.

Auto exposure is implemented by a firmware (FW) driver that analyzes image statistics collected by the exposure measurement engine, makes a decision, and programs the sensor core and color pipeline to achieve the desired exposure. The measurement engine subdivides the image into 16 windows organized as a 4 x 4 grid.

An AE algorithm mode is available: average brightness tracking (ABT).

The ABT AE uses a constant average tracking algorithm where a target brightness value is compared to a current brightness value, and the gain and integration time are adjusted accordingly to meet the target requirement.

## **AE Driver**

DRT exposure mode is activated during preview. This mode can also be enabled during video capture mode. The DRT exposure mode relies on the statistics engine to track speed and amplitude of the change of the overall luminance in the selected windows of the image.

Backlight compensation is achieved by weighting the luminance in the center of the image higher than the luminance on the periphery. Other algorithm features include the rejection of fast fluctuations in illumination (time averaging), control of speed of response, and control of the sensitivity to the small changes. While the default settings are adequate in most situations, the user can program target brightness, measurement window, and other parameters.

The driver calculates image brightness based on average luma values received from 16 programmable equal-size rectangular windows forming a  $4 \times 4$  grid. In preview mode, 16 windows are combined in two segments: central and peripheral. The central segment includes four central windows. All remaining windows belong to the peripheral segment. Scene brightness is calculated as average luma in each segment taken with certain weights.

The driver changes AE parameters (integration time, gains, and so on) to drive brightness to the programmable target. The value of the single step approach to the target value can be controlled.

To avoid unwanted reaction of AE on small fluctuations of scene brightness or momentary scene changes, the AE driver uses a temporal filter for luma and a threshold around the AE luma target. The driver changes AE parameters only if the filtered luma is larger than the AE target step and pushes the luma beyond the threshold.

# **Evaluative Algorithm**

A scene-evaluative AE algorithm is available for use in snapshot mode. The algorithm performs scene analysis and classification with respect to its brightness, contrast, and composure and then decides to increase, decrease, or keep the original exposure target. It makes the most difference for backlight and bright outdoor conditions.

### **Accelerated Settling During Overexposure**

The AE speed is direction-dependent. Transitioning from overexposure to target can take more time than transitioning from underexposure. The AE driver has a mode that speeds up AE for overexposed scenes.

The AE driver counts the number of AE windows whose average brightness is equal to or greater than some value, 250 by default. For a scene that has saturated regions, the average luma is underestimated because of signal clipping. The driver compensates underestimation by a factor that can be defined.

### **Exposure Control**

To achieve the required amount of exposure, the AE driver adjusts the sensor integration time, gains, ADC reference, and IFP digital gains. In addition, ae\_base\_target (ID = 2, offset = 0x4F) is available for the user to adjust the overall brightness of the scene.

#### Flicker Detection and Avoidance

Flicker occurs when the integration time is not an integer multiple of the period of the light intensity. The automatic flicker detection block does not compensate for the flicker, but rather avoids it by detecting the flicker frequency and adjusting the integration time.

To reject flicker, integration time is typically adjusted in increments of steps. The incremental step specifies the duration in row times equal to one flicker period. Thus, flicker is rejected if integration time is kept to an integral factor of the flicker period.

Flicker cannot be avoided for integration times below the light intensity period (10ms for 50Hz environment).

Flicker shows up in the image as horizontal bars that roll up or down. The MCU looks for these rolling bars using a thin horizontal window, which outputs luma average and is applied to 48 points in the upper half of the image. The MCU repeats the same sampling on the next frame; 48 samples from the previous frame are subtracted from corresponding samples from the current frame. Skipping more frames between subtraction can be set by a variable. The MCU then smooths the 48 sampling points, applies an amplitude threshold to avoid false detection, and looks at the resulting waveform. If flicker is present, the waveform should have a frequency within the search range. Assuming the flicker power is a sine wave, subtracting two frames results in:

$$sin(wt) - sin(wt + a) = 2 \times sin(a/2) \times cos(wt + (a/2))$$

(EQ 17)

which is a cosine wave of the original frequency.

#### **Auto White Balance**

The MT9D113 has a built-in AWB algorithm designed to compensate for the effects of changing spectra of the scene illumination on the quality of the color rendition. The algorithm consists of two major parts: a measurement engine performing statistical analysis of the image and a driver performing the selection of the optimal color correction matrix, digital gains, and sensor core analog gains. While default settings of these algorithms are adequate in most situations, the user can reprogram the base color correction matrices, place limits on color channel gains, and control the speed of both matrix and gain adjustments.

#### Flash

To take a snapshot, the user must send a command that changes the context from preview to snapshot. The typical sequence of events after this command is:

- 1. The camera might turn on its LED flash, if it has one and is required to use it. With the flash on, the camera exposure and white balance are automatically adjusted to the changed illumination of the scene.