### MOTOROLA SEMICONDUCTOR TECHNICAL DATA

Designer's Data Sheet

# TMOS IV Power Field Effect Transistors N-Channel Enhancement-Mode Silicon Gate

This advanced "E" series of TMOS power MOSFETs is designed to withstand high energy in the avalanche and commutation modes. These new energy efficient devices also offer drain-to-source diodes with fast recovery times. Designed for low voltage, high speed switching applications in power supplies, converters and PWM motor controls, these devices are particularly well suited for bridge circuits where diode speed and commutating safe operating area are critical, and offer additional safety margin against unexpected voltage transients.

- Internal Source-to-Drain Diode Designed to Replace External Zener Transient Suppressor — Absorbs High Energy in the Avalanche Mode — Unclamped Inductive Switching (UIS) Energy Capability Specified at 100°C.

- Commutating Safe Operating Area (CSOA) Specified for Use in Half and Full Bridge Circuits

- Source-to-Drain Diode Recovery Time Comparable to a Discrete Fast Recovery Diode

- Diode is Characterized for Use in Bridge Circuits

- DC Equivalent to BUZ11

#### MAXIMUM RATINGS ( $T_J = 25^{\circ}C$ unless otherwise noted)

| Rating                                                                        | Symbol                              | Value      | Unit          |

|-------------------------------------------------------------------------------|-------------------------------------|------------|---------------|

| Drain-Source Voltage                                                          | V <sub>DSS</sub>                    | 50         | Vdc           |

| Drain-Gate Voltage (R <sub>GS</sub> = 1 MΩ)                                   | VDGR                                | 50         | Vdc           |

| Gate-Source Voltage — Continuous<br>— Non-repetitive (t <sub>p</sub> ≤ 50 μs) | V <sub>GS</sub><br>V <sub>GSM</sub> | ±20<br>±40 | Vdc<br>Vpk    |

| Drain Current — Continuous (T <sub>C</sub> = 25°C) — Pulsed                   | I <sub>D</sub>                      | 45<br>145  | Adc           |

| Total Power Dissipation @ T <sub>C</sub> = 25°C Derate above 25°C             | PD                                  | 125<br>1   | Watts<br>W/°C |

| Operating and Storage Temperature Range                                       | Tj, T <sub>sta</sub>                | -65 to 150 | °C            |

#### THERMAL CHARACTERISTICS

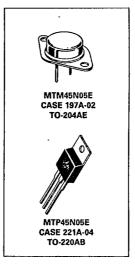

| Thermal Resistance<br>Junction to Case<br>Junction to Ambient                    | MTM45N05E<br>MTP45N05E | R <sub>Ø</sub> JC<br>R <sub>Ø</sub> JA | 1.0<br>30<br>62.5 | °C/W |

|----------------------------------------------------------------------------------|------------------------|----------------------------------------|-------------------|------|

| Maximum Lead Temperature for Soldering<br>Purposes, 1/8" from case for 5 seconds |                        | τ <sub>L</sub>                         | 275               | . ℃  |

TMOS POWER FETS

45 AMPERES

rDS(on) = 0.035 OHM

50 VOLTS

Designer's Data for "Worst Case" Conditions — The Designer's Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit curves — representing boundaries on device characteristics — are given to facilitate "worst case" design.

## MOTOROLA SC XSTRS/R F 7-39-13 14E D 6367254 0090106 0

| ELECTRICAL CHARACTERISTICS (T                                                                                                                    |                                                                                                  | <del></del>         |                        |                                       |             |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------|------------------------|---------------------------------------|-------------|--|

| Charac                                                                                                                                           | teristic                                                                                         | Symbol              | Min                    | Max                                   | Unit        |  |

| OFF CHARACTERISTICS                                                                                                                              | ·                                                                                                |                     | , ······               |                                       |             |  |

| Drain-Source Breakdown Voltage<br>(VGS = 0, ID = 0.25 mA)                                                                                        |                                                                                                  | V(BR)DSS            | 50                     | _                                     | Vdc         |  |

| Zero Gate Voltage Drain Current (VDS = Rated VDSS, VGS = 0) (VDS = Rated VDSS, VGS = 0, TJ = 125°C)                                              |                                                                                                  | IDSS                | _                      | 10<br>100                             | μΑ          |  |

| Gate-Body Leakage Current, Forward (VGSF = 20 Vdc, VDS = 0)                                                                                      |                                                                                                  | IGSSF               | _                      | 100                                   | nAdc        |  |

| Gate-Body Leakage Current, Reverse (VGSR = 20 Vdc, VDS = 0)                                                                                      |                                                                                                  | IGSSR               |                        | 100                                   | nAdc        |  |

| ON CHARACTERISTICS*                                                                                                                              |                                                                                                  |                     |                        | ····· · · · · · · · · · · · · · · · · | L           |  |

| Gate Threshold Voltage (VDS = VGS, ID = 250 $\mu$ A) TJ = 100°C                                                                                  |                                                                                                  | V <sub>GS(th)</sub> | 2.0<br>1.5             | 4<br>3.5                              | Vdc         |  |

| Static Drain-Source On-Resistance (V                                                                                                             | 3S = 10 Vdc, ID = 29 Adc)                                                                        | rDS(on)             |                        | 0.035                                 | Ohm         |  |

| Drain-Source On-Voltage (V <sub>GS</sub> = 10 (I <sub>D</sub> = 45 Adc)<br>(I <sub>D</sub> = 22.5 Adc, T <sub>J</sub> = 100°C)                   |                                                                                                  | V <sub>DS(on)</sub> | =                      | 1.5<br>0.9                            | Vdc         |  |

| Forward Transconductance (VDS = 1                                                                                                                | 5 V, I <sub>D</sub> = 29 A)                                                                      | g <sub>FS</sub>     | 17                     | _                                     | mhos        |  |

| DRAIN-TO-SOURCE AVALANCHE CHAR                                                                                                                   | ACTERISTICS                                                                                      |                     |                        |                                       |             |  |

| Unclamped Inductive Switching Energ<br>(ID = 145 A, VDD = 25 V, TC = 25<br>(ID = 45 A, VDD = 25 V, TC = 25°(<br>(ID = 18 A, VDD = 25 V, TC = 100 | C. P.W. ≤ 45 μs. Duty Cycle ≤ 1%)                                                                | WDSR                | =                      | 50<br>110<br>40                       | mJ          |  |

| DYNAMIC CHARACTERISTICS                                                                                                                          |                                                                                                  |                     |                        |                                       |             |  |

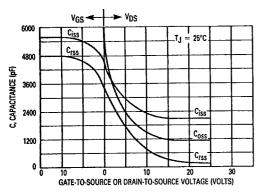

| Input Capacitance                                                                                                                                | (Vpc = 25 V Vcc = 0                                                                              | C <sub>iss</sub>    |                        | 3000                                  | pF          |  |

| Output Capacitance                                                                                                                               | $(V_{DS} = 25 \text{ V}, V_{GS} = 0, \\ f = 1 \text{ MHz})$                                      | Coss                | _                      | 1500                                  |             |  |

| Reverse Transfer Capacitance                                                                                                                     | See Figure 16                                                                                    | Crss                |                        | 400                                   |             |  |

| SWITCHING CHARACTERISTICS* (TJ =                                                                                                                 | 100°C)                                                                                           | · <del></del>       |                        |                                       |             |  |

| Turn-On Delay Time                                                                                                                               |                                                                                                  | td(on)              | _                      | 25                                    | ns          |  |

| Rise Time                                                                                                                                        | (V <sub>DD</sub> = 25 V, I <sub>D</sub> = 29 A<br>R <sub>gen</sub> = 4.7 ohms)                   | tr                  |                        | 60                                    |             |  |

| Turn-Off Delay Time                                                                                                                              | See Figure 9                                                                                     | td(off)             | _                      | 70                                    |             |  |

| Fall Time                                                                                                                                        | 555 / <b>.g</b> 4.5 5                                                                            | tf                  |                        | 25                                    |             |  |

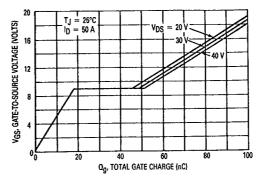

| Total Gate Charge                                                                                                                                | (Voc = 0.8 Rated Vocc                                                                            | Qg                  | 55 (Typ)               | 60                                    | nC          |  |

| Gate-Source Charge                                                                                                                               | $(V_{DS} = 0.8 \text{ Rated } V_{DSS},$<br>$I_{D} = \text{Rated } I_{D}, V_{GS} = 10 \text{ V})$ | Ωgs                 | 30 (Typ)               | _                                     | -<br>-<br>- |  |

| Gate-Drain Charge                                                                                                                                | See Figures 17 and 18                                                                            | Q <sub>gd</sub>     | 25 (Typ)               |                                       |             |  |

| SOURCE DRAIN DIODE CHARACTERIST                                                                                                                  | ics*                                                                                             |                     | <u> </u>               |                                       |             |  |

| Forward On-Voltage                                                                                                                               | (Ic = 46 A                                                                                       | V <sub>SD</sub>     | 1.8 (Typ)              | 2.2                                   | Vdc         |  |

| Forward Turn-On Time                                                                                                                             | (IS = 46 A<br>VGS = 0                                                                            | ton                 | Limited                | by stray ind                          | luctance    |  |

| Reverse Recovery Time                                                                                                                            | dig/dt = 100 A/μs)                                                                               | t <sub>rr</sub>     | 200 (Typ)              |                                       | пѕ          |  |

| NTERNAL PACKAGE INDUCTANCE (TO                                                                                                                   | -204)                                                                                            |                     |                        |                                       |             |  |

| Internal Drain Inductance<br>(Measured from the contact screw of<br>to the source pin and the center of                                          |                                                                                                  | Ld                  | 5 (Typ)                |                                       | nH          |  |

| Internal Source Inductance<br>(Measured from the source pin, 0.2<br>to the source bond pad)                                                      | 5" from the package                                                                              | Ls                  | 12.5 (Typ)             | _                                     |             |  |

| NTERNAL PACKAGE INDUCTANCE (TO                                                                                                                   | -220)                                                                                            |                     |                        |                                       |             |  |

| Internal Drain Inductance<br>(Measured from the contact screw (<br>(Measured from the drain lead 0.25                                            |                                                                                                  | Ld                  | 3.5 (Typ)<br>4.5 (Typ) |                                       | nH          |  |

| Internal Source Inductance<br>(Measured from the source lead 0.2                                                                                 | 5" from package to source bond pad.)                                                             | L <sub>S</sub>      | 7.5 (Typ)              |                                       |             |  |

<sup>\*</sup>Pulse Test: Pulse Width  $\leq$  300  $\mu$ s, Duty Cycle  $\leq$  2%.

#### TYPICAL ELECTRICAL CHARACTERISTICS

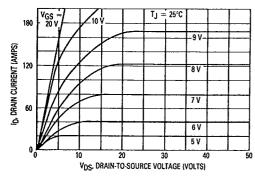

Figure 1. On-Region Characteristics

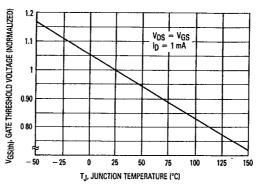

Figure 2. Gate-Threshold Voltage Variation With Temperature

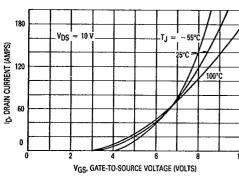

Figure 3. Transfer Characteristics

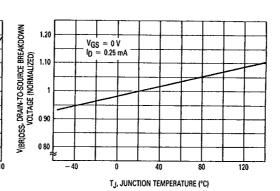

Figure 4. Breakdown Voltage Variation With Temperature

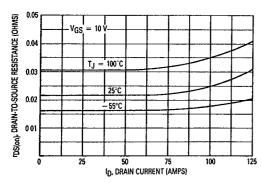

Figure 5. On-Resistance versus Drain Current

Figure 6. On-Resistance Variation With Temperature

#### SAFE OPERATING AREA INFORMATION

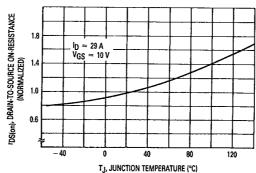

Figure 7. Maximum Rated Forward Bias Safe Operating Area

# 180 150 150 160 17J < 150°C 30 0 10 20 30 40 50 60 VDS, DRAIN-TO-SOURCE VOLTAGE (VOLTS)

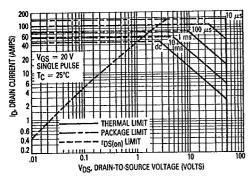

Figure 8. Maximum Rated Switching Safe Operating Area

#### FORWARD BIASED SAFE OPERATING AREA

The FBSOA curves define the maximum drain-to-source voltage and drain current that a device can safely handle when it is forward biased, or when it is on, or being turned on. Because these curves include the limitations of simultaneous high voltage and high current, up to the rating of the device, they are especially useful to designers of linear systems. The curves are based on a case temperature of 25°C and a maximum junction temperature of 150°C. Limitations for repetitive pulses at various case temperatures can be determined by using the thermal response curves. Motorola Application Note, AN569, "Transient Thermal Resistance-General Data and Its Use" provides detailed instructions.

#### **SWITCHING SAFE OPERATING AREA**

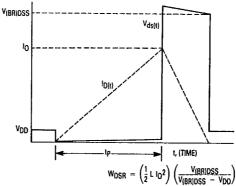

The switching safe operating area (SOA) of Figure 8 is the boundary that the load line may traverse without incurring damage to the MOSFET. The fundamental limits are the peak current,  $I_{\mbox{\footnotesize DM}}$  and the breakdown voltage,  $V_{\mbox{\footnotesize (BR)DSS}}$ . The switching SOA shown in Figure 8 is applicable for both turn-on and turn-off of the devices for switching times less than one microsecond.

The power averaged over a complete switching cycle must be less than:

Figure 9. Resistive Switching Time Variation versus Gate Resistance

RG, GATE RESISTANCE (OHMS)

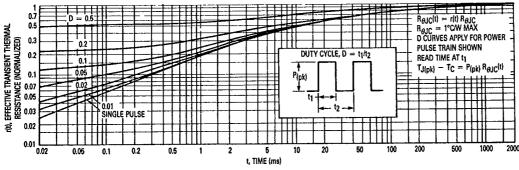

Figure 10. Thermal Response

#### MTM/MTP45N05E

#### **COMMUTATING SAFE OPERATING AREA (CSOA)**

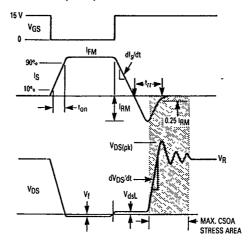

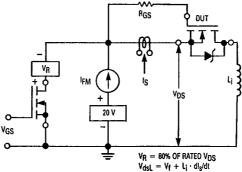

The Commutating Safe Operating Area (CSOA) of Figure 12 defines the limits of safe operation for commutated source-drain current versus re-applied drain voltage when the source-drain diode has undergone forward bias. The curve shows the limitations of IFM and peak VDS for a given rate of change of source current. It is applicable when waveforms similar to those of Figure 11 are present. Full or half-bridge PWM DC motor controllers are common applications requiring CSOA data.

Device stresses increase with increasing rate of change of source current so dls/dt is specified with a maximum value. Higher values of dl<sub>s</sub>/dt require an appropriate derating of I<sub>FM</sub>, peak V<sub>DS</sub> or both. Ultimately dl<sub>s</sub>/dt is limited primarily by device, package, and circuit impedances. Maximum device stress occurs during trr as the diode goes from conduction to reverse blocking.

VDS(pk) is the peak drain-to-source voltage that the device must sustain during commutation; IFM is the maximum forward source-drain diode current just prior to the onset of commutation.

V<sub>R</sub> is specified at 80% of V<sub>(BR)DSS</sub> to ensure that the CSOA stress is maximized as I<sub>S</sub> decays from I<sub>RM</sub> to zero.

RGS should be minimized during commutation. TJ has only a second order effect on CSOA.

Stray inductances in Motorola's test circuit are assumed to be practical minimums. dVDS/dt in excess of 10 V/ns was attained with dl<sub>S</sub>/dt of 400 A/μs.

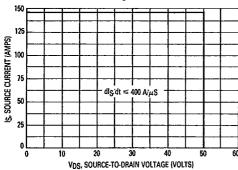

Figure 12. Commutating Safe Operating Area (CSOA)

Figure 14. Unclamped Inductive Switching **Test Circuit**

Figure 11. Commutating Waveforms

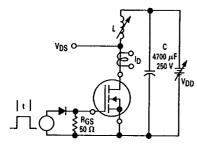

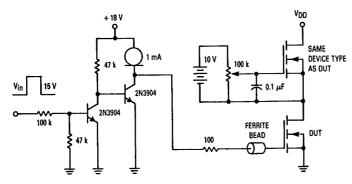

Figure 13. Commutating Safe Operating Area **Test Circuit**

Figure 15. Unclamped Inductive Switching Waveforms

Figure 16. Capacitance Variation

Figure 17. Gate Charge versus Gate-to-Source Voltage

$m V_{in} = 15 \, V_{pk}$ ; PULSE WIDTH  $m \leqslant 100 \; \mu s$ , DUTY CYCLE  $m \leqslant 10\%$

Figure 18. Gate Charge Test Circuit