This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

GEC PLESSEY

# MV1471

# HDB3/AMI ENCODER/DECODER

The MV1471, along with other devices in the GPS 2Mbit PCM signalling series comprise a group of circuits which will perform the common channel signalling and error detection functions for a 2.048Mbit PCM transmission link operating in accordance with the appropriate CCITT Recommendations. The MV1471 is also capable of operating at clock rates up to 10MHz. The MV1471 circuit is fabricated in CMOS and operates from a single +5V supply with all inputs and outputs being TTL compatible.

The MV1471 is an encoder/decoder for pseudo-ternary transmission codes. The code can be selected as either true Alternate Mark Inversion (AMI) code or AMI modified according to the HDB3 coding laws specified in Annex A of CCITT Recommendation G. 703. The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of the HDB3 coding and all ones detection. In addition a loop back function is provided for terminal testing.

#### FEATURES

- Single +5V supply

- All Inputs and Outputs TTL compatible

- Selectable HDB3 or AMI coding

- HDB3 Encoding and Decoding to CCITT Recommendation G. 703

- Simultaneous Encoding and Decoding

- Clock Recovery Signal allows Clock Regeneration from Incoming PCM data

- Loop Back Control

- HDB3 error monitor

- Alarm Indication Signal Monitor

- Low Power Operation

- 2.048MHz or 8.448MHz Operation

#### ABSOLUTE MAXIMUM RATINGS

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

| Supply Voltage           | –0.5V to +7V                   |

|--------------------------|--------------------------------|

| Supply Voltage           | –0.5V to +7V                   |

| Input Voltage            | 0.5V to V <sub>DD</sub> +0.5V  |

| Output Voltage           | -0.5V to V <sub>DD</sub> +0.5V |

| Storage temperature (DP) | -55 to +150°C                  |

| Storage temperature (DG) | –65 to +150°C                  |

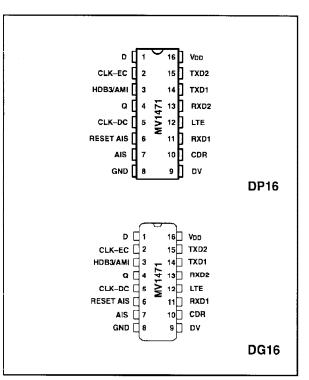

Fig. 1 Pin connections top view

#### **ORDERING INFORMATION**

MV1471/CG/DPAS MV1471/CG/DGAS

#### **Functional Description**

High density bipolar 3 (HDB3) is a ternary transmission code in which the number of consecutive zeros which may occur is restricted to three, to ensure adequate clock recovery at the receiver. In any sequence of four consecutive binary zero's, the last zero is substituted by a mark of the same polarity as the previous mark, thus breaking the Alternate Mark Inversion (AMI) code. This mark is termed a violation. In addition, the first zero may also be substituted by a mark if the last mark and last violation are of the same polarity. This mark does not violate the AMI code and ensures that successive violations alternate in polarity and as such introduce no DC components to the HDB3 signal.

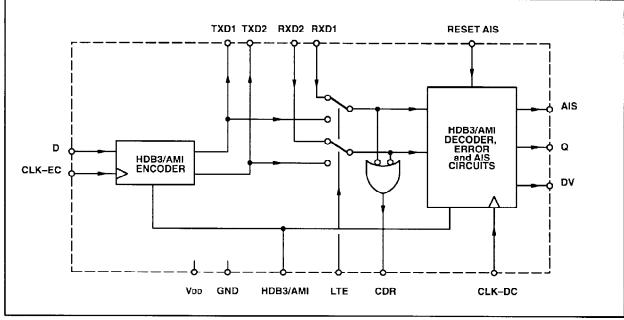

The MV1471 consists of two main blocks, the HDB3/AMI Encoder and the HDB3/AMI Decoder, with the block diagram being shown in Fig. 2. The function of each block is now described separately.

#### HDB3/AMI Encoder

The HDB3/AMI Encoder is responsible for converting the incoming NRZ data into pseudo-ternary form for transmission over a 2.048Mbit/8.448Mbit PCM link according to either the true AMI rules or AMI modified according to the HDB3 encoding rules. In HDB3 mode, this conversion is carried out in accordance with the HDB3 coding laws specified in CCITT Recommendation G. 703, Annex A. Selection between the two encoding schemes is controlled by the HDB3/AMI control input. A logic high on this pin will configure the device in HDB3 mode.

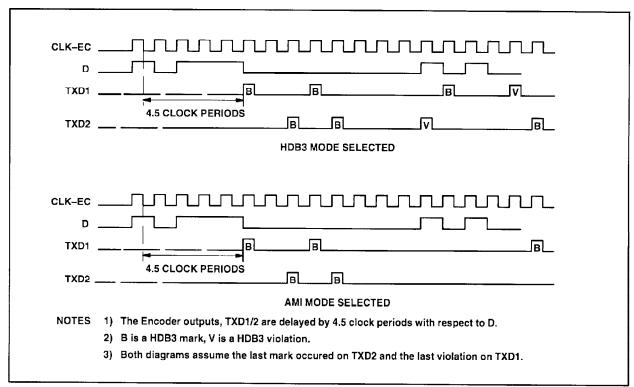

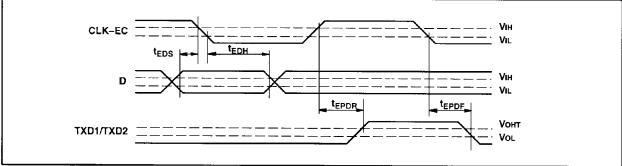

The data to be encoded is input on the D input pin and the encoding process is synchronised to the 2.048/8.448MHz clock signal being input on the CLK–EC pin. The HDB3/AMI Encoder has two outputs, TXD1 and TXD2, which represent the encoded PCM data stream in pseudo-ternary form. If a mark or HDB3 violation is to be transmitted the output pulses high after the rising edge of the clock, with the length of the pulse set by the clock high pulse width. The timing diagram of the HDB3/AMI Encoder is shown in Fig. 3.

#### HDB3/AMI Decoder

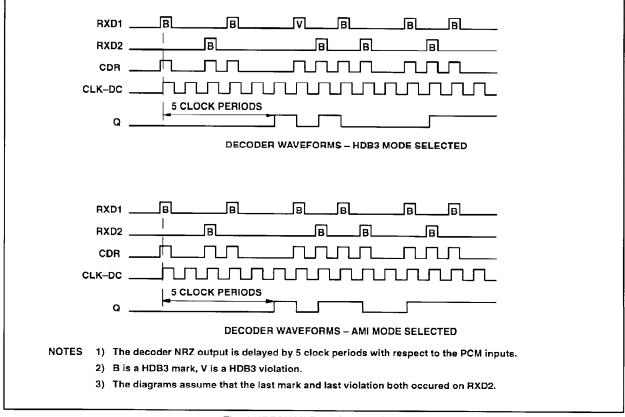

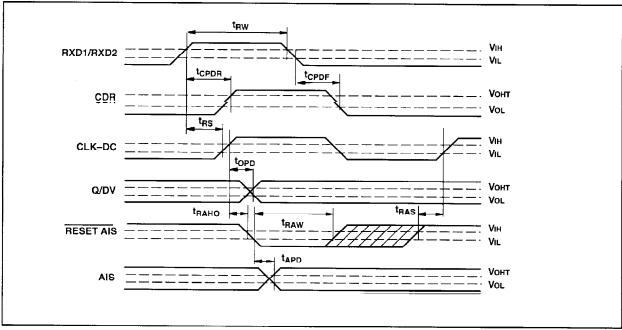

The HDB3/AMI Decoder circuit is responsible for converting the 2.048Mbit/8.448Mbit HDB3/AMI encoded pseudo-ternary PCM data stream on its inputs, RXD1 and RXD2, into NRZ binary form to be output on the Q output pin. In HDB3 mode this conversion is carried out in accordance with the HDB3 coding laws specified in CCITT Recommendation G. 703, Annex A. The HDB3/AMI decoder synchronously decodes the data on its RXD input pins into NRZ form under control of the 2.048MHz/8.448MHz clock being input on its CLK-DC pin. There is a 5 clock period delay between the encoded data being clocked in from the RXD inputs and the NRZ data appearing on the Q output. The Decoder clock must be externally regenerated from the incoming PCM data streams and in order to aid this clock recovery a logical 'OR' function of the decoder inputs is output on the CDR pin.

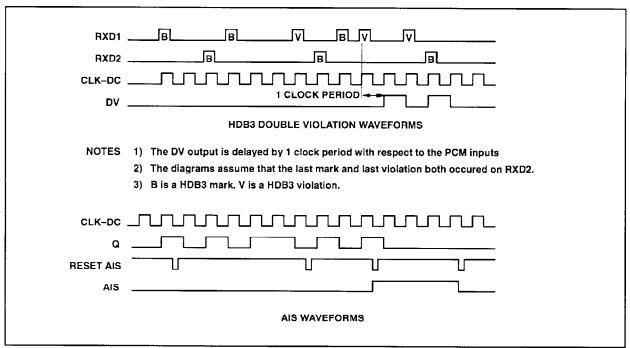

In addition to the HDB3/AMI decoding the circuit also provides two alarm outputs. The first of these alarms is DV (Double Violation) and a logic high on this output denotes that two successive violations have been received with the same polarity, thus violating the HDB3 decoding laws. The second alarm output is AIS (Alarm Indication Signal). This output will go high if less than 3 decoded zero's have been detected in the preceding two RESET AIS=1 periods (i.e. between two RESET AIS=0 pulses) and as such this alarm can be used to detect the CCITT Alarm Indication Signal. All the alarm circuit as well as the decoding process is synchronised to the clock signal being input on the CLK-DC pin. The clock signal may by asynchronous with the CLK-EC signal. The timing diagrams of the HDB3/AMI Decoder circuit are shown in Fig.4. In addition to the normal mode of operation, a loop test mode is available for terminal testing. This mode is selected by taking the LTE (Loop Test Enable) input high. In this mode, the HDB3/AMI encoded pseudo-ternary data outputs of the encoder block are fed back as the inputs to the decoder block, which in turn decodes this data and outputs it in NRZ form.

Fig. 2 Block diagram

Fig. 3 HDB3/AMI Encoder waveforms

Fig. 4 HDB3/AMI Decoder waveforms

Fig. 4 HDB3/AMI Decoder waveforms (continued)

#### **PIN DESCRIPTION**

| Pin Name  | Pin No | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D         | 1      | NRZ Data Input pin to HDB3/AMI Encoder. The NRZ binary data on this pin is input to the HDB3/AMI Encoder for conversion to HDB3/AMI pseudo-ternary form under control of the CLK-EC signal. The D input is latched into the encoder block by the falling edge of CLK-EC.                                                                                                                                                                                                    |  |  |  |  |  |

| CLK-EC    | 2      | 2.048MHz Clock Input to HDB3 Encoder. The clock signal on this input is used for the encoding of data on pin 1.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| HDB3/AMI  | 3      | HDB3/AMI Mode Select Input. A logic high on this pin selects HDB3 operation. A logic low selects AMI mode.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Q         | 4      | NRZ Data Output from HDB3/AMI Decoder. This output represents the HDB3/AMI input data decoded back into NRZ binary form, with a 5 clock period delay from the PCM inputs to the NRZ output. This decoding process is carried out under control of the CLK-DC signal.                                                                                                                                                                                                        |  |  |  |  |  |

| CLK-DC    | 5      | 2.048MHz Clock Input to HDB3/AMI Decoder. The clock signal on this pin is used for decoding of data on the RXD input pins, or the TXD pins in Loop Test Mode. This pin is used to input the externally regenerated clock signal recovered from the incoming HDB3/AMI waveforms back to the decoder block.                                                                                                                                                                   |  |  |  |  |  |

| RESET AIS | 6      | Reset AIS Input to HDB3/AMI Decoder. A logic '0' on this input resets a decoded zeros counter in the HDB3/AMI decoder. It will also reset the AIS output to '0' provided 3 or more zeros have been decoded in the preceding RESET AIS=1 period, or set AIS to '1' if less than 3 zeros have been decoded in the preceding two RESET AIS=1 periods. This may be used to detect the CCITT Alarm Indication Signal. A logic '1' on this pin enables the decoded zeros counter. |  |  |  |  |  |

| AIS       | 7      | Alarm Indicator Signal Output from HDB3/AMI Decoder. See description for RESET AIS pin.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GND       | 8      | Digital Ground. 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| DV        | 9      | Double Violation Alarm Output from HDB3/AMI Decoder. This output goes high for one period of CLK–DC, one period after the detection of a HDB3 violation of the same polarity as the previous HDB3 violation.                                                                                                                                                                                                                                                                |  |  |  |  |  |

| CDR       | 10     | Clock Recovery Output from HDB3/AMI Decoder. This pin is used to output the logical 'OR' function of the PCM inputs for the use of the external clock recovery circuit.                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| RXD1 | 11 | HDB3/AMI Encoded Input 1 to HDB3/AMI Decoder. This is one of the pair of 2.048Mbit/8.448Mbit pseudo-ternary PCM data stream inputs to the HDB3/AMI Decoder. This input asynchronously latches the incoming HDB3/AMI data and is rising edge sensitive. Since the input is asynchronously latched it is not necessary for the RXD pulse to straddle a rising clock edge.                                       |

|------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTE  | 12 | Loop Test Enable Control Input. A logic low on this pin selects normal operation, with<br>encoding and decoding being independent and asynchronous. A logic high on this<br>pin internally connects TXD1 to RXD1 and TXD2 to RXD2. Note that in loop back<br>mode, a decoder clock must be supplied.                                                                                                          |

| RXD2 | 13 | HDB3/AMI Encoded Input 2 to HDB3/AMI Decoder. See description for pin RXD1.                                                                                                                                                                                                                                                                                                                                   |

| TXD1 | 14 | HDB3/AMI Encoded Pseudo-Ternary Output 1 from HDB3/AMI Encoder. The NRZ<br>PCM data stream being input on the D pin is HDB3/AMI encoded and output on this<br>pin and pin TXD2. This output is always low during the low half cycle of clock and is<br>only high during the high half cycle of clock if a mark is to be output. There is a 4.5<br>clock period delay from the falling edge of CLK-EC to TXD1. |

| TXD2 | 15 | HDB3/AMI Encoded Pseudo-Ternary Output 1 from HDB3/AMI Encoder. See Pin TXD1 description.                                                                                                                                                                                                                                                                                                                     |

| VDD  | 16 | Digital Supply Voltage. 5V.                                                                                                                                                                                                                                                                                                                                                                                   |

NOTES

1. All inputs except HDB3/AMI have 100K on-chip pull down resistors. HDB3/AMI has a 100K on-chip pull-up resistor.

## **ELECTRICAL CHARACTERISTICS**

Test Conditions Supply Voltage V<sub>DD</sub> = 5V  $\pm$ 0.5V Ambient Temperature T<sub>amb</sub> = 0°C to + 70°C

#### STATIC CHARACTERISTICS

| Characteristics           | Oh.a.l           | Value                |     |                 |       |                            |

|---------------------------|------------------|----------------------|-----|-----------------|-------|----------------------------|

|                           | Symbol           | Min                  | Тур | Max             | Units | Conditions                 |

| Low level input voltage   | VIL              | 0.0                  |     | 0.8             | v     |                            |

| High level input voltage  | VIH              | 2.0                  |     | V <sub>DD</sub> | v     |                            |

| Low level output voltage  | V <sub>OL</sub>  |                      |     | 0.4             | V V   | I <sub>sink</sub> = 2mA    |

| High level output voltage | V <sub>OHT</sub> | 2.4                  |     |                 | v     | I <sub>source</sub> = 2mA  |

|                           | V <sub>онс</sub> | V <sub>DD</sub> -1.0 |     |                 | v     | I <sub>source</sub> = 1mA  |

| Input leakage current     | hι               | -10                  |     | 200             | μΑ    | $V_{in} = V_{DD}$ or GND   |

| Supply current            | I <sub>S</sub>   |                      |     | 5               | mA    | 2.048MHz operation Note 1. |

|                           |                  |                      |     | 15              | mA    | 8.448MHz operation Note 1. |

| Input capacitance         | C <sub>IN</sub>  |                      | 5   |                 | pF    | All inputs                 |

| Output capacitance        | C <sub>OUT</sub> |                      | 5   |                 | pF    | All outputs                |

NOTES

1. All supply currents measured with outputs unloaded. These currents are not tested but are guaranteed by characterisation and a static current test.

#### **DYNAMIC CHARACTERISTICS**

| Characteristics      | Cumula al                        | Value |     |     |       | <b>•</b>   |

|----------------------|----------------------------------|-------|-----|-----|-------|------------|

|                      | Symbol                           | Min   | Тур | Max | Units | Conditions |

| CLOCK                |                                  |       |     |     |       |            |

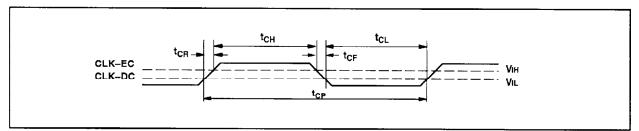

| Clock period         | t <sub>CP</sub>                  | 100   |     |     | ns    | See Fig. 5 |

| Clock rise/fall time | t <sub>CR/</sub> t <sub>CF</sub> |       |     | 20  | ns    | See Fig. 5 |

| Clock high/low time  | t <sub>CH</sub> /t <sub>CL</sub> | 30    |     |     | ns    | See Fig. 5 |

### (cont.)DYNAMIC CHARACTERISTICS

|                                       |                                          | Value |     |     | [     |                           |

|---------------------------------------|------------------------------------------|-------|-----|-----|-------|---------------------------|

| Characteristics                       | Symbol                                   | Min   | Тур | Max | Units | Conditions                |

| ENCODER                               |                                          |       |     |     |       |                           |

| Encoder data setup time               | t <sub>EDS</sub>                         | 15    |     |     | ns    | See Fig. 6                |

| Encoder data hold time                | t <sub>EDH</sub>                         | 15    |     |     | ns    | See Fig. 6                |

| TXD1/TXD2 output<br>propagation delay | t <sub>EPDR</sub><br>t <sub>EPDF</sub>   |       |     | 45  | ns    | See Fig. 6, Note 1.       |

| DECODER                               |                                          |       |     |     |       |                           |

| RXD1/2 data setup time                | t <sub>AS</sub>                          | 20    |     |     | ns    | See Fig. 7                |

| RXD1/2 pulse width                    | t <sub>RW</sub>                          | 20    |     |     | ns    | See Fig. 7                |

| CDR propagation delay                 | t <sub>CPDR</sub> /<br>t <sub>CPDF</sub> |       |     | 45  | ns    | See Fig. 7, Note 1.       |

| Decoder output<br>propagation delay   | topd                                     |       |     | 45  | ns    | See Fig. 7, Note 1.and 2. |

| RESET AIS hold-off time               | t <sub>RAHO</sub>                        | 15    |     |     | ns    | See Fig. 7                |

| RESET AIS pulse width                 | t <sub>RAW</sub>                         | 15    |     |     | ns    | See Fig. 7                |

| Reset AIS setup time                  | t <sub>RAS</sub>                         | 10    |     |     | ns    | See Fig. 7                |

| AIS propagation delay                 | t <sub>APD</sub>                         |       |     | 55  | ns    | See Fig. 7, Note 1.       |

NOTES

1. All output propagation delays are measured with a 50pF load.

2. The  $t_{\mbox{\scriptsize OPD}}$  parameter applies to outputs Q, and DV, but does not apply to AIS.

Fig. 5 Clock timing parameters

Fig. 6 Encoder timing parameters

Fig. 7 Decoder timing parameters

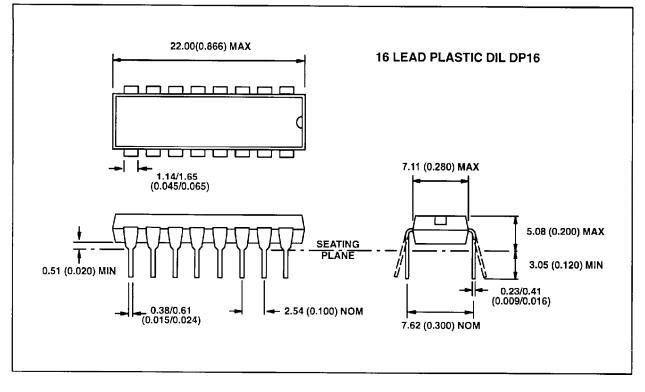

#### **PACKAGE DETAILS**

Dimensions are shown thus: mm (in). For further package information please contact your local Customer Service Centre.

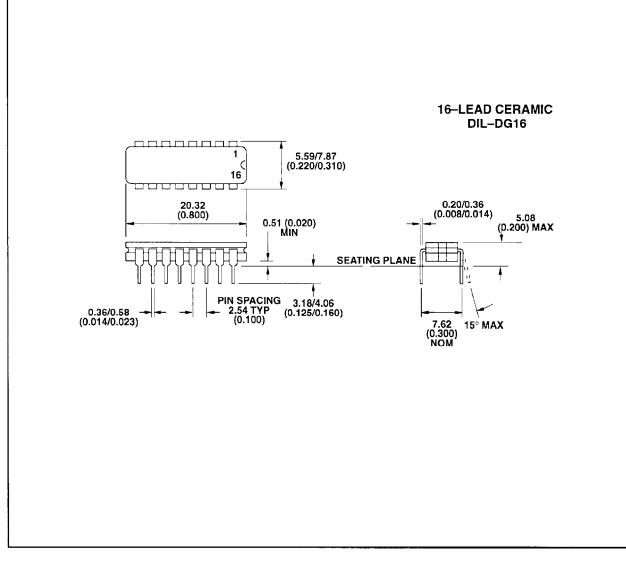

#### PACKAGE DETAILS

Dimensions are shown thus: mm (in). For further package information please contact your local Customer Service Centre.

## IIII GEC PLESSEY SEMICONDUCTORS

HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Fax: (0793) 518411

GEC PLESSEY SEMICONDUCTORS P.O. box 660017 1500 Green Hills Road, Scotts Valley, California 95067–0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

- CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Tx: 602858F • 64 46 06 07 Fax: (1

- .

- Fax: (1) 64 46 06 07 GERMANY Munich Tel: (089) 3609 06 0 Tx: 523980 Fax: (089) 3609 06 55 ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993 JAPAN Tokyo Tel: (03) 3296–0281 Fax: (03) 3296–0228 NORTH AMERICA Integrated Circuits and Microwave Products, Scotts Valley, USA Tel: (408) 438 2900 Fax: (408) 438 7023 Hybrid Products, Farmingdale, USA Tel: (516) 293 8686 Fax: (516) 293 0061 Fax: (516) 293 0061

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872 SWEDEN Stockholm Tel: 46 8 7029770 Fax: 46 8 6404736 UNITED KINGDOM & SCANDINAVIA Swindon Tel: (0793) 518510 Tx: 444410 Fax: (0793) 518582

- .

- .

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1993 Publication No. D.S. 3780 Issue No. 1.6 November 1993

.

This publication is issued to provide information only, which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without proir knowledge the specification, design, price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.