This product is obsolete.

This information is available for your convenience only.

For more information on Zarlink's obsolete products and replacement product lists, please visit

http://products.zarlink.com/obsolete\_products/

.

.

# MV1815

# T-77-07-05

## SINGLE CHIP TELETEXT DECODER FOR 625 LINE OPERATION

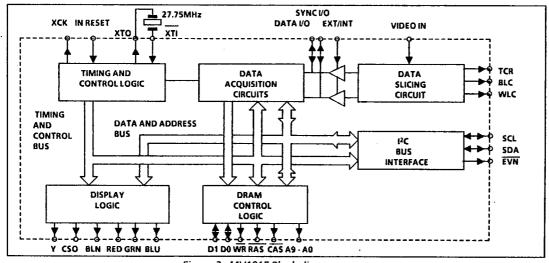

The MV1815 is an advanced CMOS single chip Teletext decoder for 625 line World Standard Teletext Systems. The MV1815 has an on board data slicer circuit, dual page acquisition circuits, and direct memory addressing, which allow a low cost Teletext decoder to be built with a minimum number of additional components.

### **FEATURES**

- On-Chip data slicing.

- Up to 254 display pages, using two low cost 200ns DRAMs.

- Low external component count.

- I<sup>2</sup>C Bus for low cost interfacing .

- Multi-language capability for fourteen European languages.

- Pinout to suit single sided PCB layout.

Non-display packets stored for linked page operation, video programming, and other advanced uses.

- High resolution characters 16 by 10 dot matrix

- Advanced CMOS technology gives low power dissipation and high reliability.

| GND       | ٢,          | 40          | V <sub>DD</sub>      |

|-----------|-------------|-------------|----------------------|

| хто       | ٢, D        | 39          | EVENT                |

| XTI       | Ľ,          | 38          | I <sup>2</sup> C SDA |

| XCK       | Ū₄          | 37          | I2C SCL              |

| A7        | []s         | 36          | A1                   |

| A5        | [6          | 35          | A2                   |

| A4        | Į,          | 34          | AO                   |

| A3        | C ه         | D           | RAS                  |

| A6        | Ľ,          | 32          | WB                   |

| D1        | [] 10       | "D          | CAS                  |

| D0        | Q           | 10 P        | TEST                 |

| A8        | [] 12       | 29 🛛        | A9                   |

| RESET     | [] 13       | 28          | CSO                  |

| SYNC VO   | Q 14        | 27          | Y OUTPUT             |

| DATA I/O  | Q 15        | 26          | BLUE OUTPUT          |

| EXT / INT | L 16        | 25 <b>D</b> | GREEN OUTPUT         |

| BLC       | Q 17        | 24 🛛        | RED OUTPUT           |

| WLC       | <b>G</b> 18 | 23 🛛        | BLANK OUTPUT         |

| VIDEO IN  | [] 19       | 22 🛛        | TCR                  |

| GND       | Q 20        | 21          | V <sub>DD</sub>      |

|           |             |             |                      |

|           |             |             | DP40                 |

Figure 1. Pin Connections (top view)

Figure 2. MV1815 Block diagram

| Section                                 | Specification T-77-07-0                                    |

|-----------------------------------------|------------------------------------------------------------|

| Data Acquisition Logic                  |                                                            |

|                                         | 625 Lines 50 Fields / second.                              |

| Teletext data rate                      | 6.9375 Mbits / sec ± 25ppm.                                |

| Data line content                       | 360 bits as 45 bytes of 8 bits each.                       |

| TV lines used VBI                       | Lines 6 to 22 and 319 to 335.                              |

| TV lines used full field                | Lines 6 to310 and 319 to 622.                              |

|                                         | (display is interrupted during data acquistion).           |

| Packets accepted                        | X/0 to X/25, X/26, X/27, X/28, X/29, 8/30 (formats 1 & 2), |

|                                         | X/31.                                                      |

| Page numbers                            | 00 to FF                                                   |

| Pages subcodes                          | 0000 to 3F7F                                               |

|                                         |                                                            |

| Display Logic                           | 40, occupying 46.126µs of the 52µs display time            |

| Characters per row                      | 1 to 24 and 25 and 26 software switchable                  |

| Teletext rows displayed                 | Rows Start Finish                                          |

| TV lines used                           | 24 48 288                                                  |

|                                         | 26 38 298                                                  |

|                                         | 16 x 10 dot matrix                                         |

| Character definition                    | English, German, Swedish, Italian,Belgian,Spanish,         |

| Character Sets                          | Czechoslovakian, Polish, Rumanian, Hungarian,              |

|                                         | Serbo Croat, Danish and American                           |

| a statute and a statute                 | Standard Level One Range                                   |

| Spacing control characters              | Page Number - Row 1 characters 1 to 8                      |

| Data boxing into picture                | Page Header - Row 1 characters 9 to 32                     |

|                                         | Clock Time - Row 1 characters 33 to 40                     |

|                                         | Rows 25 and 26                                             |

|                                         | 14 to 254 each of 1K bytes, depending on the size of the   |

| Displayable page stores                 | DRAM being used                                            |

|                                         | Picture, Text                                              |

| Display options                         | Mix of text foreground and picture background              |

|                                         | Three part magnify - display rows 1 to 12                  |

|                                         | rows 7 to 18                                               |

|                                         | rows 13 to 24                                              |

|                                         | Boxing of Newsflash and Subtitles into picture             |

|                                         | Boxing of picture into text.                               |

|                                         |                                                            |

| Dynamic RAM Control Logic               |                                                            |

| Device Type                             | 2 off 1M x 1 or,                                           |

|                                         | 2 off 256K x 1 or,                                         |

|                                         | 2 of 64K x 1 with page or nibble mode operation.           |

| Maximum access time (t <sub>RAC</sub> ) | 200ns.                                                     |

| Refresh period for complete memory      | 2.048ms.                                                   |

|                                         | Refresh occurs during the line flyback period. Contents of |

|                                         | any memory location may be accessed by the                 |

|                                         | microprocessor via the I <sup>2</sup> C Bus interface.     |

|                                         | Standard implementation of a slave transmitter / receiver. |

| I <sup>2</sup> C Bus Interface          | Control of the MV 1815 is via 31 on - chip registers.      |

|                                         |                                                            |

Table 1 MV1815 System Specification

100

■ 7220513 0009421 3

# Device Description

# T-77-07-05

The MV1815 is a single chip teletext decoder using an on chip data slicing circuit capable of receiving Teletext services broadcast to the WST Level 1 + standard, for display on 625 line TV receivers.

The device is controlled using a low cost I<sup>2</sup>C interface allowing easy interface to microprocessors. The register structure of the MV1815 allows the microprocessor to quickly read the Event and Page Receive registers, which hold information on the page being currently received. The chip requires only a single 27.75MHz crystal for all system clocks, this clock is internally divided by two to generate an external clock capable of driving the host microprocessor at 13.875MHz.

The MV1815 has dual acquisition circuits to ensure that the viewed page can always be kept live while the second acquisition circuit stores linked or other pages. It is possible for many linked page numbers to be transmitted in extra packet 27's. As the MV1815 has the capacity to store up to 254 different pages, it can store a complete magazine of linked pages.

The display memory uses two very low cost DRAMs. The DRAMs are controlled by the MV1815, including all the necessary refresh cycles. Refresh occurs during the flyback period on all ten address lines. The two DRAMs may be either:  $64K \times 1$ ,  $256K \times 1$ , or  $1M \times 1$  giving 14, 62, or 254 displayable pages in memory, plus two pages of store for nondisplay packets. These two pages will store two versions of packet 30 and two versions of packet 29 leaving the rest of the two pages to store any mix of packets 26, 27, or 28 up to a total maximum of 23 per acquistion circuit. It will be possible for the MV1815 to use two 4Mbyte DRAMs if the extra address lines are externally controlled.

Rows 25 & 26 can be displayed under software control. The contents of these lines will be optionally written by packets X/24 and X/25 dependent on the status of a register bit. A row zero write inhibit bit in a register will prevent the transmitted data in the header packet writing to memory, so that the microprocessor may process packet 8/30 data and write its own header line at the top of the screen. The displayed page can be enlarged into three overlapping half pages for ease of reading.

The on board character ROM holds 192 different characters with a resolution of 16 x 10 dots . This allows selective interlacing with high resolution characters, and a seven language capability.

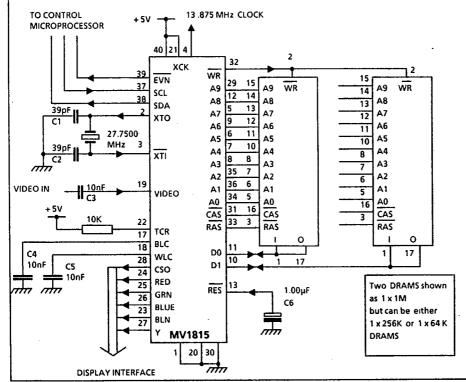

Figure 3. MV1815 applications circuit

### **APPLICATION NOTES**

The following notes assume that the MV1815 is to operate in a system which conforms to the principles of the teletext transmissions as described in the "World System Teletext Specifications".

The design of the MV1815 enables it to be incorporated in a system, using a minimum of external components, figure 3 shows a typical application circuit. It can be seen from this circuit that to produce a complete multi-page teletext system requires only three ICs and eight discrete components.

The video signal required is typically 1V (peak to peak) coupled by a 10nF capacitor in series.

The pin-out on the MV1815 has been specially designed to allow the circuit to be constructed easily on a single sided PCB when using either 64K x 1 or 256K x 1 DRAMs. It is required that two DRAMS are always included in the circuit rather than a single large DRAM, as the MV1815 expects to access a two deep memory field.

The reset input must be held low for about 250ms from power up to avoid erroneous clocking. A 1µF capacitor is all that is required.

If the on-chip data slicer is not required, by holding EXT/INT high, an external data stream and sync pulses may be input to the MV1815 on pins SYNC and DATA.

#### **Pin Descriptions**

Vdd and Vss (pins 21 & 40 and 1 & 20 respectively).

The  $5 \pm 0.5$  volt supply is applied to any convenient pair of these pins. It is however recommended that all four supply pins are used.

#### Video input (pin 19).

The video input is connected to this pin coupled via a 10nF capacitor. A video signal between 0.5V and 2.5V peak to peak is required.

#### BLC (pin 17).

Black level capacitor. A 10nF capacitor connected to ground is required.

#### WLC (pin 18).

White level capacitor. A 10nF capacitor connected to ground is required.

#### TCR(pin22)

Time constant resistor. A 10K resistor is required to  $V_{DD}$ .

DATA I/O and SYNC I/O (pins 15 and 14 respectively).

The two outputs from the internal data slicer are fed via two tri-state buffers to the inputs of the data acquisition logic circuits. These two pins can be used to inject an external data and sync pulse train into the data acquisition circuits or to use the output of the internal data-slicer, depending on the state of EXT/INT.

EXT/INT (pin 16).

### T-77-07-05

■ 7220513 0009422 5 **■**

When this pin is held low the data acquisition circuits use the data and sync pulse trains from the internal data slicer. When high it permits external data and sync signals to be fed directly into the data acquisition circuits.

#### XTI & XTO (pins 3 and 4).

This pair of pins are designed to drive a 27.75000 MHz fundamental or third overtone quartz crystal. If a third overtone type is used, two external components are required to ensure operation at the correct frequency. Typical external components are, a 33nF capacitor and a 1 $\mu$ H. inductor in series and in parallel with the crystal. A 1M $\Omega$  resistor is included on chip between XTI and XTO to bias the input to its correct operating region. The crystal should be within ± 100 p.p.m. of the nominal frequency over the operating temperature range.

#### XCK (pin 4).

This pin is a clock output running at 13.875 MHz. It can be used as a stable clock for other components.

A0-A9(pins 34, 36, 35, 8, 7, 6, 9, 5, 12, 29 respectively).

DRAM address lines.

D0 (pin 11). DRAM data line to bank 0

D1 (pin 10). DRAM data line to bank 1

CAS (pin31). DRAM column address strobe

RAS (pin 33). DRAM row address strobe

WR (pin 32). DRAM read/not write signal

#### TEST(pin 30).

This pin is used for internal testing and should be held low for the normal operation of the chip.

#### EVENT (pin 39).

An active low open drain output intended to interrupt a microprocessor when an important event occurs on either data acquisition circuit. The EVENT/A /B register bits uniquely describe which type of event has occured.

# CSO OUT, BLUE, GREEN RED, BLANK (pins 28, 26,25,24,23).

These pins are high power RGB outputs allowing direct connection to display circuits without further buffering.

### Y (pin 27).

This pin is a logical OR of the R.G.B. ouputs

#### SCL & SDA (pins 37 & 38 respectively)

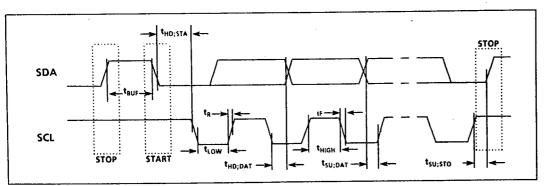

Standard connection to I<sup>2</sup>C bus. The MV1815 can work at frequencies to a maximum of 1 MHz.

#### RESET (pin 13).

The active low reset input. This input has a nominal 150 K $\Omega$  resistor coupled to V<sub>DD</sub> and a schmitt input buffer, allowing a simple external circuit consisting of a 1µF capacitor to ground to perform a power - on reset pulse of sufficient duration to allow the crystal oscillator to stabilize. When held low this input resets all registers to default setting and initalises counters.

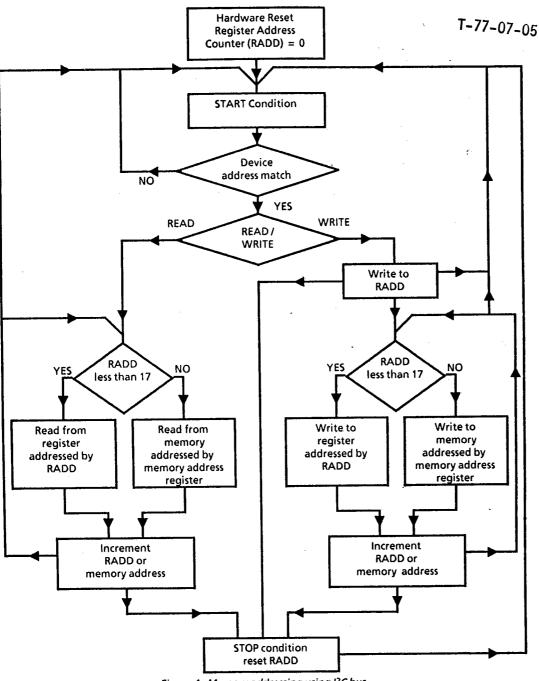

### MV1815 REGISTER ACCESSING VIA 12C

The MV1815 has twelve read registers and nineteen write registers. The I<sup>2</sup>C - bus slave address is "001001W/R".

When the MV1815 is addressed on the I<sup>2</sup>C bus as a slave transmitter, i.e. the eighth data bit is high, it will acknowledge the address byte, then transmit the contents of register address #0 to #10 in numerical order, if the master receiver continues to issue clock and acknowledge pulses. After transmitting register 10 contents, the register address will be set to #17, the RAM data register. The contents of RAM will be transmitted from the starting address set in the memory address registers. Each further transmitted byte increments the memory address by one, rather than the register address.

When addressed as a slave receiver, i.e. the eighth data bit is low, the MV1815 will acknowledge the address byte. The first data byte received by the MV1815 sets the register address counter. This defines the address of the register that will be written to by the following byte. Subsequent transmitted bytes will increment the register address by one each time, and the data will thus be written to all numerically higher registers, until the address reaches #17, the RAM data register. All subsequent received bytes will increment the memory address by one and be written to RAM. Whenever a stop condition occurs while the MV1815 is addressed as either a receiver or transmitter, the register address counter will be reset to zero.

# T-77-07-05 READ REGISTERS

EVENT A/B - Event Registers (register numbers 0 & 1).

These are interrupt registers, designed to quickly notify the controlling microprocessor about the major acquisition events, so that the microprocessor is relieved of the task of polling memory for information regarding the reception of data. The EVENT output is set low when any one of six major events occurs in either of the acquisition circuits. Multiple events will set multiple bits in the registers, which will be cleared when the appropriate registers have been read, as will the EVENT output.

The events that are notified using this register are:- New page received, Valid header received, receipt of non-display packets and control bits C8 and C10, though these bits do not set the EVENT output.

**CBITS A/B - Control Bit Registers** (register numbers 2 & 6).

These registers display the remaining eight control bits, C5, C6, C7, C9, C11, C12, C13 and C14 received in the last valid header for each acquisition circuit.

# PGR 1/2/3 A/B - Page Received Registers. (register numbers 3,4,5,7,8 & 9).

These registers show the exact page number and sub code of the received page.

HAMMC - Hamming Correction Counter. (register number 10).

To aid correct tuning of the receiver, each Hamming protected character received with other than exactly correct Hamming protection, will increment this counter. Thus by regularly reading this count, and monitoring its rate of increase, a good indication is given of the signal quality.

**RDATA - RAM Contents Register.** (register number 17).

RD7 to RD0 - The video RAM data at the address set by HADD and LADD registers, can be read from this register.

Figure 4. Memory addressing using I<sup>2</sup>C bus

7220513 0009425 0

### WRITE REGISTERS

RADD - Register Address Counter.

The first data byte transmitted in any write sequence is the address of the first register to be written to, ( see figure 4). Bits 0 to 4 define the register address. An Auto Increment Inhibit bit, disables the auto incrementing of the register or RAM address. The other two bits set the quadrant in which the memory address registers work.

ACON A/B - Acquisition control registers for A and B acquisition circuits (register numbers 1 & 5)

These two registers control the acquisition of data. They control which acquisition circuits are on and which of the magazine, page number or subcode digits are of "don't care" status during reception of Teletext.

**STOR A/B - Acquisition Store Select Registers** (register numbers 1 & 6).

The eight bits in each register select which of the 254 page stores will be written to by each acquisition circuit The controlling microprocessor must ensure that the two registers are not written with the same value.

PGS A/B - Page Select Registers (register numbers 2,3,4,7,8 and 9)

These registers define the magazine, page and sub-page that each acquisition circuit will search for, depending on the information set in the ACON registers.

**RECON - Receive Control Register** (register number 10).

This register controls the data format of the teletext being received including the:-

Writing of Packet 0 to memory; Writing of Packet 24 to memory; Writing of Packet 25 to memory; Parity check enable; Accuracy of the framing code; Full field or normal teletext data; Rolling headers.

DISCON 1,2,3,4 - Display control registers (register numbers 11,12,13 and 14)

These four registers control the actual display of the teletext and picture. The features controlled include :-

Which acquisition circuit is displayed; Language displayed; Control of the display of the header; Display of TEXT, PICTURE, or MIX; Display of boxes of either text or picture; Reveal of text hidden by "conceal" control

codes; Cursor control;

Control of separated graphics;

The display of lines 25 and 26; Double height display of,

Top half of text, Middle half of text, Bottom half of text.

T-77-07-05

Double height of any area will be true double height, i.e. giving quad height characters if double height control characters are present. Double height control characters have no effect when on the bottom row of any displayed region.

HADD - High Address Word Register. (register number 15)

A8 to A15 - The high order address bits selecting one of the 256 sections of 256 bytes to be read through the data register.

LADD - Low Address Byte Register (register number 16)

A0 to A7 - The lower order address bits selecting one of 256 bytes in a given section. This register auto-increments after every read or write operation of the DATA registers if the AII bit is low. Auto incrementing of this register from FF to 00 will increment the HADD register, and overflow of HADD increments A16 & A17 in the RADD register.

WDATA - RAM contents Register. (register 17)

The video RAM data at the address set by HADD and LADD registers can be written via this register.

## **MEMORY ORGANISATION.**

The display memory addresses as seen by the microprocessor via the I<sup>2</sup>C registers 'HADD' and 'LADD' bear little resemblance to the actual memory addresses that are used to store the data in the DRAMs, in conjunction with RAS and CAS strobes. This is of little consequence though to the system designer, unless he wishes to access the display DRAM data directly, which is inadvisable since the MV1815 needs access to the DRAMs during all TV lines.

The data address in HADD and LADD have been arranged as logically and as simply as possible, to allow a processor system easy access to the display (and non-display) data. Irrespective of the size of memory devices used, the lowest 2K (2048 bytes) of DRAM addresses, referred to as Store 0 and Store 1 contain all the non-display packets associated with the pages being acquired by both acquisition circuits. Space is reserved in Store 0 and Store 1 for up to 23 versions of packets X/26, X/27 or X/28. The only restriction is the total number of the. three packets. These packets are stored in the same sequence as they are received. Reception of the same page will overwrite the memory space with new packets X/26, X/27 or X/28.

T-77-07-05

The first byte of rows 1 to 23 inclusive in both Store 0 and Store 1 can be read by the microprocessor to identify which non-display packet is stored in the particular row. This byte is made up of the 3 least significant bits of the packet number and the designation code value. In addition, packet 29's are stored in both stores and the two versions of packet 8/30 are stored, one in each of the two stores.

The lowest 24 bytes of store 0 (address 0000 to 0017 HEX) are allocated as follows. The first eight (0000 - 0007) are never written to by the MV1815 acquisition circuits. They are however read by the display circuits for display as the first eight characters in the top display row of the teletext page. This is normally where the requested page number is shown. There is no fixed format for this however and the MV1815 puts no constraints on what data is written to this part of the screen. When headers are 'rolling', MV1815 does not write any colour control characters to these locations. It is the responsibility of the control software to do this if it is required. It is therefore perfectly feasible to have red, yellow or cyan rolling headers to signify different states if so desired, or of course white, as the headers are actually transmitted. Allowing access to all eight characters allows a system to write e.g. "123-0001", or "432-XXXX", to show the magazine, page number and sub-code selected by the user, not just the page number as with previous systems. This address in store 1 is not used and may be used by the system for other purposes.

15E

Address 0008 - 000F are written by the MV1815 acquisition circuit that is currently selected for display, with the last eight bytes from every header (packet 0) received by the MV1815 (or every header of the relevant parallel magazine). The only exception are 'out of sequence' headers, or if the 'WI0' bit is set, then no data will be written to these eight bytes. The microprocessor may then write them as required with, for instance, the time derived from packet 8/30. These eight bytes are displayed by the MV1815 as the last eight characters on the top display row, irrespective of which store is selected for display. Addresses 0010 -0017 are used by the MV1815 to output packet 31 at receiver rate.

The display stores, 2 to 15 (63 or 255 if larger DRAMs are used), start at address 0800, the boundaries being in multiples of 1024 bytes, at 0C00, 1000 etc. (HEX). In each store, the first 24 bytes are nos. 14 to 37 inc. from the header for the requested page The further 1000 bytes per store are used by packets 1 though to 25 (40 bytes per packet), in that order, irrespective of the order of the transmission.

| TABLE<br>POSITION | ENGLISH           | GERMAN | SWEDISH<br>FINNISH | ITALIAN | FRENCH<br>(BELGIAN) | SPANISH | CZECH |

|-------------------|-------------------|--------|--------------------|---------|---------------------|---------|-------|

| 2/3               | £                 | #      | #                  | £       | é                   | ç       | #     |

| 2/4               | \$                | \$     | X                  | \$      | ï                   | \$      | ů     |

| 4/0               | @                 | §      | É                  | é       | à                   | i       | č     |

| 5/11              | <                 | Ä      | Ä                  | o       | ë                   | á       | ť     |

| 5/12              | 1 <u>2</u>        | Ö      | Ö                  | ç       | ê                   | é       | ž     |

| 5/13              | >                 | Ü      | Å                  | >       | ù                   | í       | ý     |

| 5/14              | <b>↑</b>          | ^      | Ü                  | ^       | î                   | Ó       | í     |

| 5/15              | #                 |        | _                  | #       | #                   | ú       | ř     |

| 6/0               |                   | •      | é                  | ù       | è                   | ż       | é     |

| 7/11              | 1                 | ä      | ä                  | à       | â                   | ü       | á     |

| 7/12              |                   | ö      | ö                  | ò       | Ô                   | ñ       | ě     |

| 7/13              | <del>3</del><br>4 | ü      | å                  | è       | û                   | è       | ú     |

| 7/14              | ÷                 | ß      | ü                  | ì       | ç                   | à       | Š     |

Table 2. International Character set

T-77-07-05

|    |                  |                        | τοι | UMN | (bits | 5,6,7 | & 8) | ·         |   | / ]<br> | /-0 | 7-05 |

|----|------------------|------------------------|-----|-----|-------|-------|------|-----------|---|---------|-----|------|

| ow | 0                | . 1                    | 2   |     | 3     | 3     | 4    | 5         | ( | 5       |     | 7    |

| 0  | Alpha<br>Black   | Graphic<br>Black       |     |     | 0     |       | @    | P         |   |         | р   |      |

| ١  | Aipha<br>Red     | Graphics<br>Red        | l   |     | 1     |       | A    | Q         | а |         | q   |      |

| 2  | Alpha<br>Green   | Graphics<br>Green      | "   |     | 2     |       | B    | R         | b |         | r   |      |

| 3  | Alpha<br>Yellow  | Graphics<br>Yellow     | £   |     | 3     |       | C    | S         | C |         | S   |      |

| 4  | Alpha<br>Blue    | Graphics<br>Blue       | \$  |     | 4     |       | D    | T         | d |         | t   |      |

| 5  | Alpha<br>Magenta | Graphics<br>Magenta    | %   |     | 5     |       | E    | U         | e |         | u   |      |

| 6  | Alpha<br>Cyan    | Graphics<br>Cyan       | &   |     | 6     |       | F    | V         | f |         | V   |      |

| 7  | Alpha<br>White   | Graphics<br>White      | •   |     | 7     |       | G    | W         | g |         | W   |      |

| 8  | Flash            | Conceal<br>Display     | (   |     | 8     |       | H    | X         | h |         | X   |      |

| 9  | Steady           | Contiguous<br>Graphics |     |     | 9     |       |      | Y         |   |         | У   |      |

| 10 | End Box          | Separate<br>Graphics   | *   |     |       |       | J    | Z         | j |         | Z   |      |

| 11 | Start Box        | No action              | +   |     |       |       | K    | <b> ←</b> | k |         | 14  |      |

| 12 | Normal<br>Height | Black<br>Background    |     |     |       |       |      | 1<br>2    |   |         |     |      |

| 13 | Double<br>Height | Néw<br>Background      | -   |     |       |       | M    |           | m |         | 34  |      |

| 14 | No action        | Hold<br>Graphics       |     |     |       |       | N    | 1         | n |         | ÷   |      |

| 15 | No action        | Release<br>Graphics    | 1   |     |       | ?     | 0    | ) #       | 0 |         |     |      |

Table 3. Control Characters, Primary Character Set G0 and Mosaic Graphics Set G1

# MV1815 PLESSEY SEMICONDUCTORS LZE D

# TIMING CHARACTERISTICS

Test conditions (unless otherwise stated) T<sub>amb</sub> = 0°C to 70°C, V<sub>DD</sub> = + 5V ± 0.5V T-77-07-05

.

|                                                                                        |                     |     | Value |      | Units | Conditions                              |

|----------------------------------------------------------------------------------------|---------------------|-----|-------|------|-------|-----------------------------------------|

| Characteristic                                                                         |                     | Min | Тур   | Max  | Units | Conditions                              |

| SCL Clock frequency                                                                    | f <sub>SCL</sub>    | 0   | 100   | 1000 | kHz   |                                         |

| Time the bus must be free<br>before a new transision can<br>start                      | t <sub>BUF</sub>    | 4.7 |       |      | μs    |                                         |

| Hold time start<br>condition.After this<br>periodthe first clock pulse is<br>generated | t <sub>HD;STA</sub> | 4.0 |       |      | μs    |                                         |

| Low period of clock                                                                    | t <sub>LOW</sub>    | 470 |       |      | nś    | All values refer to V <sub>IH</sub> and |

| High period of clock                                                                   | t <sub>HIGH</sub>   | 400 |       |      | ns    | V <sub>IL</sub> levels                  |

| Set up time DATA                                                                       | t <sub>SU;DAT</sub> | 25  |       |      | ns    |                                         |

| Rise time of SDA and SCL signals                                                       | t <sub>R</sub>      |     |       | 1    | μs    |                                         |

| Fall time of SDA and SCL signals                                                       | t <sub>F</sub>      |     |       | 300  | ns    |                                         |

| Set up time for STOP condition                                                         | t <sub>su;sto</sub> | 4   |       |      | μs    |                                         |

Table 4 I<sup>2</sup>C Parameters

Figure 5 I<sup>2</sup>C bus timing diagram

# PLESSEY SEMICONDUCTORS

## **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated)  $T_{amb} = 0^{\circ}C \text{ to } 70^{\circ}C, V_{DD} = + 5V \pm 0.5V$

# T-77-07-05

7220513 0009429 8 🔳

| Characteristic                          | Pin   |      | Value  | _    | Units | Conditions                                   |

|-----------------------------------------|-------|------|--------|------|-------|----------------------------------------------|

|                                         | Pin   | Min  | Тур    | Max  | Units | Conditions                                   |

| All Inputs (except XTI and              |       |      |        |      |       |                                              |

| TEST)                                   |       |      |        |      |       | All inputs have $150K\Omega$                 |

| Input low current (source)              |       | -10  | -33    | -100 | μА    | pull-up resistor to V <sub>DD</sub>          |

| Input high current (sink)               |       |      |        | 10   | μA    | except test                                  |

| XTI and TEST inputs                     | 3     |      |        |      |       |                                              |

| Input low current (source)              | 30    |      |        | -10  | μA    |                                              |

| Input high current (sink)               |       |      |        | + 10 | μΑ    |                                              |

| SYNC and DATA inputs                    | 14,15 |      |        |      |       |                                              |

| Input low voltage                       |       | -0.3 | ·.     | 0.8  | v     |                                              |

| Input high voltage                      |       | 2.0  |        | 5.3  | V V   | $V_{\rm IH_{MAX}} = V_{\rm DD} + 0.3V$       |

| RESET, SDA, SCL input                   |       |      |        |      |       |                                              |

| (Schmitt input)                         | 13    |      |        |      |       |                                              |

| Input low voltage                       | 38    | -0.3 |        | 1.0  | V     |                                              |

| Input high voltage                      | 37    | 2.0  |        | 5.3  | V     | $V_{\rm IH_{MAX}} = V_{\rm DD} + 0.3V$       |

| Threshold voltage (rising)              |       |      | 1.85   |      | V     | $V_{DD} = 5\dot{V}$                          |

| (falling)                               |       |      | 1.05   |      | V     | V <sub>DD</sub> = 5V                         |

| All other inputs                        |       |      |        |      |       |                                              |

| Input low voltage                       |       | -0.3 |        | 1.5  | V     |                                              |

| Input high voltage                      |       | 3.5  |        | 5.3  | v     | V <sub>IH MAX</sub> = V <sub>dd</sub> + 0.3V |

| Outputs (A0 to A9,D0, D1,               |       |      |        |      |       |                                              |

| WE,CAS,RAS,EVENT)                       |       |      |        |      |       |                                              |

| Output low (sink)                       |       | 13   | 26     |      | mA    | V <sub>OL</sub> = 0.4V                       |

| Output high (source)                    |       | 21   | 45     |      | mA    | V <sub>OH</sub> = 2.4V                       |

| хск                                     | 4     |      |        |      |       |                                              |

| Output low(sink)                        |       | 6.9  | 13     |      | mA    | $V_{OL} = 0.4V$                              |

| Output high(source)                     |       | 10   | 22     |      | mA    | V <sub>OH</sub> = 2.4V                       |

| Frequency                               |       |      | 13.875 |      | MHz   |                                              |

| хто                                     | 2,    |      |        |      |       |                                              |

| Output low (sink)                       |       | 6.9  | 13     |      | mA    | V <sub>OL</sub> = 0.4V                       |

| (source)                                |       | 10   | 22     |      | mA    |                                              |

| Max Input Frequency, F <sub>INMAX</sub> | 3     |      | 27.75  |      | MHz   |                                              |

75E D

Table 5

## **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated)  $T_{amb} = 0^{\circ}C$  to 70°C,  $V_{DD} = +5V \pm 0.5V$  T-77-07-05

|                                  |            | T     |         | Value |     | Units      | Conditions   |  |

|----------------------------------|------------|-------|---------|-------|-----|------------|--------------|--|

| Characteristic                   |            | Pin   | Min Typ |       | Max | Units      | Conditions   |  |

| R, G, B & Blanking               | outputs    | 23,24 | •       |       |     |            |              |  |

|                                  | IOL        | 25,26 | 23      | 43    |     | mA         |              |  |

|                                  | юн         | 27    | 36      | 76    |     | mA         | Vol = 0.4V   |  |

| Composite sync                   | <b>IOL</b> |       | 13      | 26    |     | mA         | VoH = 2.4V   |  |

| output                           | юн         | 28    | 21      | 45    |     | mA         |              |  |

| Video Input pin<br>Input voltage |            | 19    | 0.5     |       | 2.5 | v          | peak to peak |  |

| Operating tempe                  | rature     |       | 0       |       | 70  | °⊂         |              |  |

| Storage tempera                  |            |       | -65     |       | 150 | <b>°</b> ℃ |              |  |

| Relative Humidit                 | У          |       |         |       | 85  | %          |              |  |

| Absolute Max D                   | C supply   | 21    | -0.3    |       | 7.0 | V          |              |  |

|                                  |            | 40    |         |       |     |            |              |  |

15E D

Table 6

## **TIMING CHARACTERISTICS of DRAMS**

Test conditions (unless otherwise stated)  $T_{amb} = 0^{\circ}C$  to 70°C,  $V_{DD} = + 5V \pm 0.5V$

| <b>6</b> 1               |                  |             | Value |       | Units      | Conditions               |  |

|--------------------------|------------------|-------------|-------|-------|------------|--------------------------|--|

| Characteristic           |                  | Min Typ Max |       | Units | Conditions |                          |  |

| Access time from RAS     | t <sub>RAC</sub> |             |       | 232   | nS         | DRAM timing              |  |

| Access time from CAS     | tCAC             |             |       | 124   | nS         | characteristics required |  |

| RAS Precharge Time       | t <sub>RP</sub>  |             |       | 144   | nS         | by the MV1815            |  |

| RAS Pulse Width          | t <sub>RAS</sub> |             |       | 432   | nS         |                          |  |

| CAS Pulse Width          | tCAS             |             |       | 144   | nS         |                          |  |

| Row Address Hold Time    | t <sub>RAH</sub> |             | 1     | 36    | nS         |                          |  |

| Column Address Hold Time | tCAH             | 72          |       |       | nS         |                          |  |

| Data-inSet Time          | t <sub>DS</sub>  | 36          |       |       | nS         |                          |  |

| Data-in Hold Time        | t <sub>DH</sub>  | 72          |       |       | nS         |                          |  |

|                          | t <sub>CP</sub>  | 108         |       | ł     | nS         |                          |  |

|                          | tPC              | 252         |       |       | nS         |                          |  |

| Ramdon R/W Cycle Time    | t <sub>RC</sub>  | 576         | l     | 1     | nS         |                          |  |

**Table 7 DRAM Parameters**