# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

# MV3506 A-LAW FILTER/CODEC MV3507 $\mu$ -LAW FILTER/CODEC MV3508 A-LAW FILTER/CODEC WITH OPTIONAL SQUELCH

These devices are silicon gate CMOS Companding Encoder/Decoder integrated circuits designed to implement the per channel voice frequency Codecs used in PCM systems. They contain the band-limiting filters and the analog to digital conversion circuits that conform to the desired transfer characteristic. The MV3506 and MV3508 provide the European A-Law companding and the MV3507 provides the North American  $\mu\text{-Law}$  companding characteristic. The MV3508 has programmable squelch circuitry to reduce idle channel noise.

These circuits provide the interface between the analog signals of the subscriber loop and digital signals of the PCM highway in a digital telephone switching system. The devices operate from dual power supplies of  $\pm 5$ V.

#### **FEATURES**

- Low Power CMOS 80mW (Operating) 10mW (Standby)

- Meets or Exceeds AT & T3, and CCITT G.711, G.712 and G.733 Specifications

- Input Analog Filter Eliminates Need for External Antialiasing Prefilter

- Uncommitted Input and Output Op. Amps for Programming Gain

- Output Op. Amp Provides ±3.1V into a 1200 Ohms Load or can be Switched Off for Reduced Power (70mW)

- Encoder has Dual-speed Auto-zero Loop for Fast Acquisition on Power-up

- Low Absolute Group Delay = 410 microseconds at 1 kHz

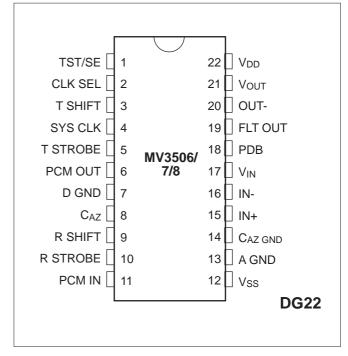

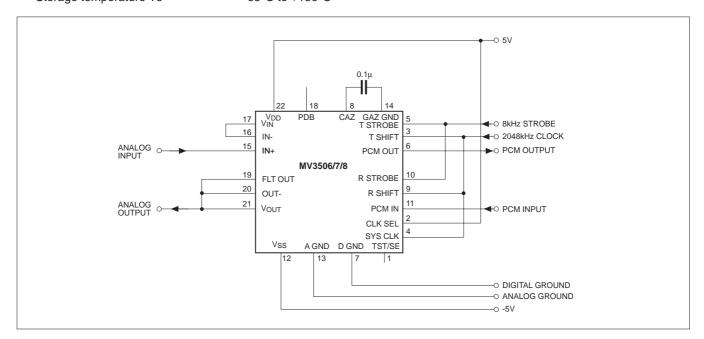

Figure 1: Pin connection - top view

#### **FUNCTIONAL DESCRIPTION**

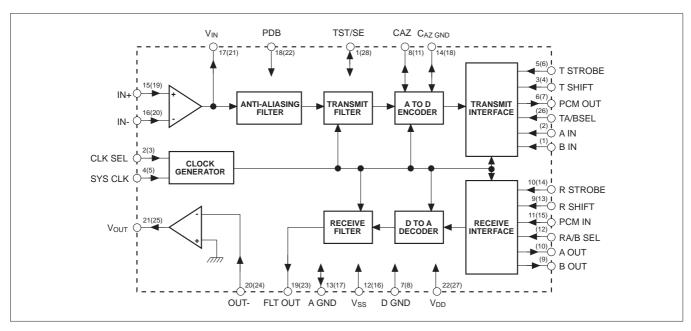

Fig.2 shows the simplified block diagram of the devices. They contain independent circuitry for processing transmit and receive signals. Switched capacitor filters provide the necessary bandwidth limiting of voice signals in both directions. Circuitry for coding and decoding operates on the principle of successive approximation, using charge redistribution in a binary weighted capacitor array to define segments and a resistor chain to define steps.

#### TRANSMIT SECTION

Input analog signals first enter the chip at the uncommitted op.amp. terminals (IN+ and IN- pins). This allows for the gain in the system to be trimmed. From the  $V_{\rm IN}$  pin the signal enters a second-order analog anti-aliasing filter. This filter eliminates the need for any off-chip filtering as it provides attenuation of 34dB (typically) at 256kHz and 44dB (typically) at 512kHz.

The signal next enters the transmit filter, which is a fifth order low-pass filter clocked at 256kHz, followed by a third order high-pass filter clocked at 64kHz. The resulting bandpass characteristics meet the CCITT specifications G.711, G.712 and G.733. Some representative attenuations are better than 26dB from 0 to 60Hz and better than 35dB from 4.6kHz to 100kHz.

The output of the transmit filter is sampled at the analog to digital encoder by a capacitor array at the sampling rate of 8kHz. The successive approximation conversion process requires about 72µsec.

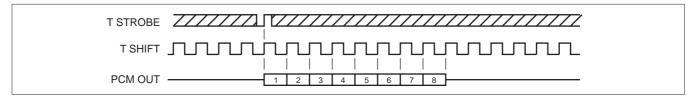

The 8-bit PCM data is clocked out by the transmit shift clock which can vary from 64kHz to 2.048MHz in 8kHz steps (see Figs. 3 and 4). A switched capacitor dual-speed, autozero loop using a small non-critical external capacitor (0.1 $\mu F$ ) provides DC offset cancellation by integrating the sign bit of the PCM data and feeding it back to the noninverting input of the comparator.

Included in the circuitry of the MV3507 is 'All Zero' code suppression so that negative input signal values between decision values numbers 127 and 128 are encoded as 00000010. This prevents loss of repeater synchronisation by

DS1 (T1) line clock recovery circuitry as there are never more than 15 consecutive zeros.

An additional feature of the MV3506/7 is a special circuit to eliminate any transmitted idle channel noise during quiet periods. When the input of these chips is-such that for 250ms the only code words generated were +0, -0, +1 or -1, the output word will be a +0. The steady +0 state prevents alternating sign bits or LSB from toggling and thus results in a quieter signal at the decoder. Upon detection of a different value, the output resumes normal operation resetting the 250ms timer. This feature is a form of idle Channel Noise 'Squelch' or 'Crosstalk Suppression'. It is of particular importance in the MV3506 A-Law version because the A-Law transfer characteristic has 'mid-riser' bias which enhances low level signals from crosstalk.

#### **RECEIVE SECTION**

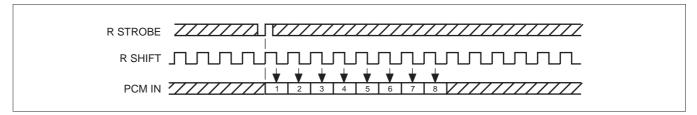

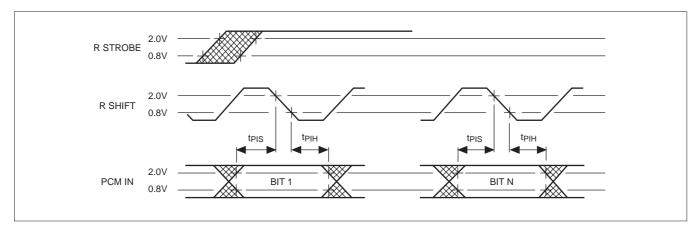

A receive shift clock, variable between the frequencies of 64kHz and 2.048MHz clocks the PCM data into the input buffer register once every sampling period (see Figs.5 and 6). A charge proportional to the received PCM data word appears on the decoder capacitor array of the digital to analog converter. A sample and hold circuit, initialised to zro by a narrow pulse at the beginning of each sampling period, integrates the charge and holds it for the rest of the sampling period .

The receive filter, consisting of a switched-capacitor filhhorder low-pass filter clocked at 256kHz, smooths the sampled and held signal. It also performs the loss equalisation to compensate for the sin(x)/x distortion due to the sampling.

The filter output (FLT OUT pin) is available for driving electronic hybrids directly as long as the impedance is greater than  $20k\Omega.$  When used in this fashion the low impedance output amp can be switched off for a considerable saving in power consumption. When it is required to drive a  $600\Omega$  load the output amp allows gain trimming as well as impedance matching.

Figure 2: Functional block diagram (pin numbers for the MV3507A are in brackets)

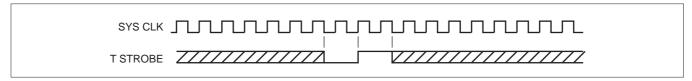

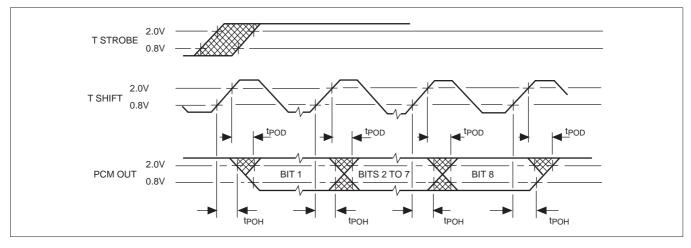

Figure 3: Transmit strobe alignment

Figure 4: Transmit alignment

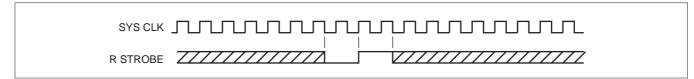

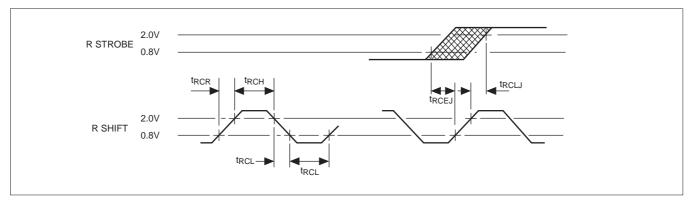

Figure 5: Receive strobe alignment

Figure 6: Receive alignment

#### **TIMING REQUIREMENTS**

The internal design of the devices paid careful attention to the timing requirements of various systems. In North America, central office and channel bank designs often follow the American Telephone and Telegraph Company's T1 (DS1) Carrier PCM format to multiplex 24 voice channels at a data rate of 1.544M b/s. PABX designs, on the other hand, may use their own multiplexing formats with different data rates. Nevertheless, in digital telephone designs, Codecs may be used in a non-multiplexed form with data rate as low as 64kbit/s. The  $\mu\text{-Law}$  Codecs fulfil these requirements.

In Europe, telephone exchange and channel bank designs often follow the CCITT carrier PCM format to multiplex 30 telephony channels at a data rate of 2.048Mbit/s. The A-Law Codecs are designed for this market and will also handle PABX and digital telephone applications.

The timing format chosen for the devices allows operation in both multiplexed or non-multiplexed form with data rates variable from 64kbit/s to 2.048Mbit/s. Use of separate internal clocks for filters and for shifting of PCM input/output data allows for this variation.

The devices do not require that the 8kHz transmit and receive sampling strobes be exactly 8 bit periods wide. The device has an internal bit counter that counts the number of

data bits shifted. It is reset on the leading (+ve) edges of the strobe, forcing the PCM output into its high impedance state after the 8th bit is shifted out. This allows the width of the strobe signal to vary as long as its repetition rate is 8kHz and the transmit and receive shift clocks are synchronised to it.

#### SYSTEM CLOCK

The basic timing is provided by the system clock which is divided down internally to provide the various filter clocks and the timing for the conversions. The transmit and receive strobes and clocks must be locked to this clock so that the PCM data matches the sample rates.

# **PIN DESCRIPTIONS**

| Symbol          | Pin No   | Pin name and description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | 3506/7/8 |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TST/SE          | 1        | Test/Squelch Enable (Internal Connection/Digital Input). This pin is an internal test connection on the MV3506, MV3507 and it is the squelch enable input on the MV3508.  On the MV3506/7 it should be left unconnected or connected to the A GND pin via a capacitor for normal operation.  On the MV3508 it should be tied high to enable the squelch feature and it should be left unconnected otherwise.                                  |

| CLK SEL         | 2        | Clock Select (Three Level Input). This pin selects the proper divide ratios for a 256kHz, 1.544MHz or 2.048MHz system clock. The pin is tied to $V_{DD}$ (+5V) for 2.048MHz operation, to D GND (0V) for 256kHz operation, and to $V_{SS}$ (-5V) for 1.544MHz operation.                                                                                                                                                                      |

| T SHIFT         | 3        | <b>Transmit Shift Clock (Digital Input).</b> This TTL compatible input shifts PCM data out of the coder on the positive going edges after receiving a positive edge on the T STROBE input. The clocking rate can vary from 64kHz to 2.048MHz.                                                                                                                                                                                                 |

| SYS CLK         | 4        | <b>System Clock (Digital Input).</b> This pin is a TTL compatible input for either a 256kHz, 1.544MHz or a 2.048MHz clock that is divided down to provide the filter clocks. The status of the CLK SEL pin must correspond to the provided clock frequency.                                                                                                                                                                                   |

| T STROBE        | 5        | <b>Transmit Strobe (Digital Input with Pull-up).</b> This TTL compatible pulse input (typically 8kHz) is used for analog sampling and initiating the PCM output from the coder. It must be synchronised with the T SHIFT and SYS CLK clocks with its positive going edges occurring after the falling edges of these clocks. The width of this signal is not critical. An internal bit counter generates the necessary timing for PCM output. |

| PCM OUT         | 6        | <b>PCM Out (Pull-down Output).</b> This is a LS TTL compatible open-drain output. It is active only during transmission of PCM output for 8-bit periods of the T SHIFT clock signal following positive edge on the T STROBE input. Data is clocked out by the positive edge on the T SHIFT clock into one $510\Omega$ pull-up per system plus 2 LS TTL inputs.                                                                                |

| D GND           | 7        | Digital Ground (Power Input). 0V.                                                                                                                                                                                                                                                                                                                                                                                                             |

| CAZ             | 8        | Auto Zero Capacitor (Reterence Node). A capacitor of $0.1\mu F$ ( $\pm 20\%$ ) should be connected between this pin and CAZ GND for coder auto zero operation. The sign bi of the PCM data is integrated and fed back to the comparator for DC offset cancellation.                                                                                                                                                                           |

| R SHIFT         | 9        | Receive Shift Clock (Digital Input). This TTL compatible input shifts PCM data into the decoder on the negative going edges after receiving a positive edge on the R STROBE input. The clocking rate can vary from 64kHz to 2.048MHz.                                                                                                                                                                                                         |

| R STROBE        | 10       | Receive Strobe (Digital Input with Pull-up). This TTL compatible pulse input (typically 8kHz) initiates clocking of PCM input data into the decoder. It must be synchronised with the R SHIFT and SYS CLK clocks with its positive going edges occurring after the falling edges of these clocks. The width of the signal is not critical. An internal bit counter generates necessary timing for PCM input.                                  |

| PCM IN          | 11       | <b>PCM In (Digital Input).</b> This is a TTL compatible input for supplying PCM input data to the decoder. Data is clocked in by the negative edge of the R SHIFT clock.                                                                                                                                                                                                                                                                      |

| V <sub>ss</sub> | 12       | Negative Supply (Power Input)5V.                                                                                                                                                                                                                                                                                                                                                                                                              |

| A GND           | 13       | Analog Ground (Reference Node). This is the ground reference node for analog signals.                                                                                                                                                                                                                                                                                                                                                         |

# PIN DESCRIPTIONS (continued)

| Symbol              | Pin No   | Pin name and description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 3506/7/8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| C <sub>AZ GND</sub> | 14       | Auto Zero Capacitor Ground (Reterence Node). A capacitor of $0.1\mu F$ ( $\pm 20\%$ ) should be connected between this pin and $C_{AZ}$ for coder auto zero operation. The sign bit of the PCM data is integrated and fed back to the comparator for DC offset cancellation.                                                                                                                                                                                                                                                     |

| IN +, IN-           | 15,16    | In Positive and Negative (Analog Voltage Inputs). These are the differential inputs of a high input impedance op amp whose output is connected to the $V_{\rm IN}$ pin. These three pins allow the user complete control over the input stage so that it can be connected as a fixed gain amplifier, as an amplifier with adjustable gain, or as a differential input amplifier The adjustable gain configuration will facilitate calibration of the transmit channel.                                                           |

| V <sub>IN</sub>     | 17       | Input Voltage (Analog High-impedance Voltage Output). This is the output of a high input impedance op amp whose differential inputs are the IN + and IN- pins. This node feeds the rest of the analog input section.                                                                                                                                                                                                                                                                                                             |

| PDB                 | 18       | <b>Power Down Bar (Digital Input with Pull-up).</b> This TTL compatible input, when held low, puts the chip into the powered down mode regardless of strobes. The chip will also power down if the strobes stop. The strobes can be high, low or floating, but as long as they are static, the powered down mode is in effect.                                                                                                                                                                                                   |

| FLT OUT             | 19       | Filter Out (Analog High-impedance Voltage Output). This is the output of the low pass filter which represents the recreated analog signal from the received PCM data words. The filter sample frequency of 256kHz is down 37dB at this point. This is a high impedance output which can be used by itself or connected to the output amplifier stage which has a low output impedance. It should not be loaded by less than $20k\Omega$ .                                                                                        |

| OUT-                | 20       | Out Negative (Analog Voltage Input). This is the inverting input of the uncommitted output amplifier stage, which has its non-inverting input connected internally to ground and its output connected to VOUT. The signal at the FLT OUT pin can be connected to this pin to realise a low output impedance with unity, increased or reduced gain. This allows easy calibration of the receive channel. If OUT- is connected directly to Vss then the op amp will be powered down, reducing power consumption by 10mW typically. |

| V <sub>OUT</sub>    | 21       | Output Voltage (Analog Voltage Output). This is the output of the uncommitted output amplifier stage, which has its inverting input connected to the OUT- pin and its non-inverting input connected internally to ground. The signal at the FLT OUT pin can be connected to OUT- to realise a low output impedance with unity, increased or reduced gain. This allows easy calibration of the receive channel. The $V_{OUT}$ pin has the capability of driving 0dBm into a $600\Omega$ load (see Fig.4) .                        |

| $V_{DD}$            | 22       | Positive Supply (Power Input). 5V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **ELECTRICAL CHARACTERISTICS**

Test conditions - Voltages are with respect to digital ground ( $V_{\text{DGND}}$ )

| Characteristic                           | Symbol              | Value                  |         |                        | Units |

|------------------------------------------|---------------------|------------------------|---------|------------------------|-------|

|                                          |                     | Min.                   | Typ.(1) | Max.                   |       |

| Digital supply voltage                   | $V_{DD}$            | 4.75                   | 5       | 5.25                   | V     |

| Negative supply voltage                  | V <sub>SS</sub>     | -5.25                  | -5      | -4.75                  | V     |

| Analog ground voltage                    | $V_{AGND}$          | -0.1                   | 0       | 0.1                    | V     |

| Ambient temperature                      | $V_{AMB}$           | 0                      |         | 70                     | °C    |

| Input low voltage - digital inputs       | V <sub>IL</sub>     | 0                      | 0.4     | 0.8                    | V     |

| Input high voltage - digital inputs      | V <sub>IH</sub>     | 2.0                    | 2.4     | $V_{DD}$               | V     |

| System clock frequency                   |                     |                        |         |                        |       |

| CLK SEL tied to V <sub>DD</sub>          | f <sub>S</sub>      | 2047.90                | 2048    | 2048.10                | kHz   |

| CLK SEL tied to D GND                    |                     | 255.99                 | 256     | 256.01                 |       |

| CLK SEL tied to V <sub>SS</sub>          |                     | 1549.92                | 1544    | 1544.08                |       |

| Capacitive loading - digital outputs     | $C_{LD}$            | 0                      |         | 100                    | pF    |

| Pull-up resistance for PCM OUT pin       | R <sub>PU</sub>     | 510                    |         |                        | Ω     |

| Analog input voltage                     | $V_{IA}$            | V <sub>AGND</sub> —3.1 |         | V <sub>AGND</sub> +3.1 | V     |

| Capacitive loading - analog outputs      | $C_{LA}$            |                        |         | 50                     | pF    |

| Resistive loading - V <sub>OUT</sub> pin | $R_{VOUT}$          | 1200                   |         |                        | Ω     |

| Resistive loading - V <sub>IN</sub> pin  | R <sub>VIN</sub>    | 10                     |         |                        | kΩ    |

| Resistive loading - FLT OUT pin          | R <sub>RLTOUT</sub> | 20                     |         |                        | kΩ    |

# POWER SUPPLY REQUIREMENTS - $V_{DD} = 5V$ , $V_{SS} = -5V$

| Characteristic                          | Symbol          |      | Value | Units | Conditions |          |

|-----------------------------------------|-----------------|------|-------|-------|------------|----------|

|                                         |                 | Min. | Тур.  | Max.  |            |          |

| Power dissipation - normal              | P <sub>IN</sub> |      | 80    | 110   | mW         | Unloaded |

| Power dissipation - without output amp. | P <sub>WA</sub> |      | 70    |       | mW         | Unloaded |

| Power dissipation - standby             | Ps              |      | 10    | 20    | mW         | Unloaded |

# STATIC CHARACTERISTICS - VOLTAGES ARE WITH RESPECT TO DIGITAL GROUND ( $V_{DGND}$ )

| Characteristic                                                                                              | Symbol                                                                                      | Value                                        |          |                                               | Units                   | Conditions                                                           |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------|----------|-----------------------------------------------|-------------------------|----------------------------------------------------------------------|

|                                                                                                             | •                                                                                           | Min.                                         | Тур. (1) | Max.                                          |                         |                                                                      |

| Pin capacitance<br>Input leakage current                                                                    | C <sub>PIN</sub><br>I <sub>IL</sub>                                                         |                                              | 7        | 15<br>1                                       | pF<br>μA                | 0 < V < V <sub>DD</sub>                                              |

| Input source current - inputs<br>with pull-ups                                                              | I <sub>IS</sub>                                                                             |                                              |          | 600                                           | μΑ                      | 0 < V < V <sub>DD</sub>                                              |

| Output high voltage Output low voltage Output leakage current Analog input resistance Analog output voltage | V <sub>OH</sub><br>V <sub>OL</sub><br>I <sub>OL</sub><br>R <sub>IA</sub><br>V <sub>OA</sub> | 2.4<br>0<br>100<br>V <sub>AGND</sub><br>-3.1 |          | VDD<br>0.4<br>10<br>V <sub>AGND</sub><br>+3.1 | V<br>V<br>μΑ<br>kΩ<br>V | $I_{OH} (Source) = 40\mu A$ $I_{OL} (Sink) = 1.6mA$ $0 < V < V_{DD}$ |

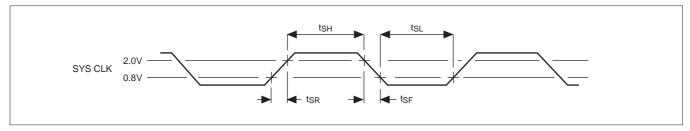

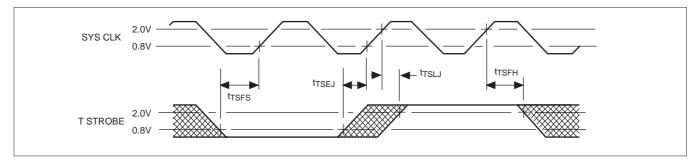

# DIGITAL SWITCHING CHARACTERISTICS - SYSTEM CLOCK (SEE FIG.7)

|                          |                 | Value  |      |        |       |            |

|--------------------------|-----------------|--------|------|--------|-------|------------|

| Characteristic           | Symbol          | Min.   | Тур. | Max.   | Units | Conditions |

|                          |                 |        |      |        |       |            |

| System clock rise time   | t <sub>SR</sub> |        | 50   |        | ns    |            |

| System clock high period | t <sub>SH</sub> | 0.4/fs |      | 0.6/fs | s     |            |

| System clock fall time   | t <sub>SF</sub> |        | 50   |        | ns    |            |

| System clock low period  | t <sub>SL</sub> | 0.4/fs |      | 0.6/fs | S     |            |

Figure 7: Timing - system clock

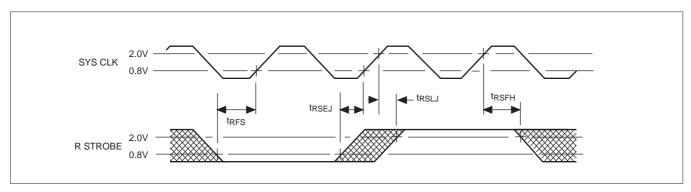

#### DIGITAL SWITCHING CHARACTERISTICS - RECEIVE STROBE AND CLOCK (SEE FIGS. 8 AND 9)

| Characteristic                     | Symbol            |                     | Value    |          | Units | Conditions                     |

|------------------------------------|-------------------|---------------------|----------|----------|-------|--------------------------------|

|                                    |                   | Min.                | Typ.(1 ) | Max.     |       |                                |

| Receive strobe frequency           | f <sub>RS</sub>   | 7.99996             |          | 8.00004  | kHz   | Phase-locked with system clock |

| Receive strobe falling set-up time | t <sub>RSFS</sub> | 120                 |          |          | ns    |                                |

| Receive strobe early jitter        | $t_{RSEJ}$        |                     |          | 200      | ns    |                                |

| Receive strobe late jitter         | $t_{RSLJ}$        |                     |          | 100      | ns    |                                |

| Receive strobe falling hold time   | t <sub>RSFH</sub> | 220                 |          |          | ns    |                                |

| Receive clock frequency            | $f_{RC}$          | 63.9997             |          | 2048.01  | kHz   | Phase-locked with              |

|                                    |                   |                     |          |          |       | receive strobe                 |

| Receive clock rise time            | $t_{RCR}$         |                     |          | 100      | ns    |                                |

| Receive clock high period          | $t_{RCH}$         | 0.4/f <sub>RC</sub> |          | 0.6/f RC | S     |                                |

| Receive clock fall time            | $t_{RCF}$         |                     |          | 100      | ns    |                                |

| Receive clock low period           | t <sub>RCL</sub>  | 0.4/f <sub>RC</sub> |          | 0.6/f RC | S     |                                |

| Receive clock early jitter         | $t_{RCEJ}$        |                     |          | 200      | ns    |                                |

| Receive clock late jitter          | $t_{RSLJ}$        |                     |          | 100      | ns    |                                |

Figure 8: Timing - receive strobe

Figure 9: Timing - receive clock

# DIGITAL SWITCHING CHARACTERISTICS - RECEIVE DATA (SEE FIG.10)

|                                           |                  | Value    |          |      |          |            |

|-------------------------------------------|------------------|----------|----------|------|----------|------------|

| Characteristic                            | Symbol           | Min.     | Typ. (1) | Max. | Units    | Conditions |

| PCM input set-up time PCM input hold time | t <sub>PIS</sub> | 60<br>60 |          |      | ns<br>ns |            |

Figure 10: Timing - receive data

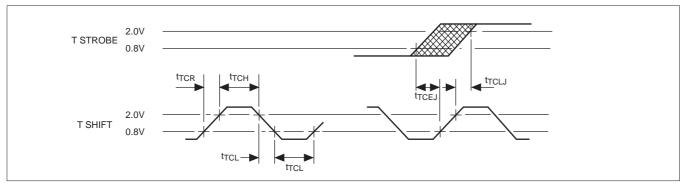

# DIGITAL SWITCHING CHARACTERISTICS - TRANSMIT STROBE AND CLOCK (SEE FIGS.11 AND 12)

| Characteristic                                                                             | racteristic Symbol Value                              |                     |          | Units                             | Conditions     |                                   |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------|----------|-----------------------------------|----------------|-----------------------------------|

|                                                                                            |                                                       | Min.                | Typ. (1) | Max.                              |                |                                   |

| Transmit strobe frequency                                                                  | f <sub>TS</sub>                                       | 7.99996             | 8        | 8.00004                           | kHz            | Phase-locked with system clock    |

| Transmit strobe falling set-up time                                                        | t <sub>TSFS</sub>                                     | 120                 |          |                                   | ns             |                                   |

| Transmit strobe early jitter Transmit strobe late jitter Transmit strobe falling hold time | t <sub>TSEJ</sub> t <sub>TSLJ</sub> t <sub>TSFH</sub> | 220                 |          | 200<br>100                        | ns<br>ns<br>ns |                                   |

| Transmit clock frequency                                                                   | f <sub>TC</sub>                                       | 63.9997             |          | 2048.01                           | kHz            | Phase-locked with transmit strobe |

| Transmit clock rise time Transmit clock high period Transmit clock fall time               | t <sub>TCR</sub> t <sub>TCH</sub> t <sub>TCF</sub>    | 0.4/f <sub>TC</sub> |          | 100<br>0.6/ <sub>TC</sub><br>100  | ns<br>s<br>ns  |                                   |

| Transmit clock low period Transmit clock early jitter Transmit clock late jitter           | t <sub>TCL</sub> t <sub>TCEJ</sub> t <sub>TCLJ</sub>  | 0.4/f <sub>TC</sub> |          | 0.6/f <sub>TC</sub><br>200<br>100 | s<br>ns<br>ns  |                                   |

Figure 11: Timing - receive strobe

Figure 12: Timing - receive clock

# DIGITAL SWITCHING CHARACTERISTICS - TRANSMIT DATA (SEE FIG.13)

|                                       |                  | Value |           |     |          |            |

|---------------------------------------|------------------|-------|-----------|-----|----------|------------|

| Characteristic                        | Symbol           | Min   | Typ (1)   | Max | Units    | Conditions |

| PCM output holt time PCM output delay | t <sub>POH</sub> | 0     | 50<br>100 | 150 | ns<br>ns |            |

Figure 13: Timing - transmit data

#### **ANALOG CHANNEL CHARACTERISTICS - FILTER DELAYS**

|                                            |                  |     | Value   |            |          |              |

|--------------------------------------------|------------------|-----|---------|------------|----------|--------------|

| Characteristic                             | Symbol           | Min | Typ.(1) | Max.       | Units    | Conditions   |

| Transmit filter delay Receive filter delay | t <sub>TFD</sub> |     |         | 182<br>110 | μs<br>μs | 1kHz<br>1kHz |

#### **ANALOG CHANNEL CHARACTERISTICS - A-LAW**

| Characteristic                                                                                             | Symbol                                    |             | Value    |                          | Units                        | Conditions                                                                      |

|------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------|----------|--------------------------|------------------------------|---------------------------------------------------------------------------------|

|                                                                                                            |                                           | Min.        | Typ. (1) | Max.                     |                              |                                                                                 |

| 0dBm0 level (see Note 2)<br>Variation in 0dBm0 level                                                       | 0dBM0 $\Delta_{\mathrm{0dBm0}}$           | 5.3<br>-0.3 | 5.8<br>0 | 6.3<br>0.3               | dBm<br>dB                    | ±5V, 25°C<br>Over test conditions                                               |

| Weighted idle channel noise                                                                                | ICN <sub>W</sub>                          |             | -85      | -73                      | dBm0p                        | CCITT G.712, §5.1 (see Note 3)                                                  |

| Single frequency idle channel noise                                                                        | ICN <sub>SF</sub>                         |             |          | -60                      | dBm0                         | CCITT G.712, §5.2                                                               |

| Weighted receive idle channel noise                                                                        | ICN <sub>WR</sub>                         |             |          | -78                      | dBm0p                        | CCITT G.712, §5.3                                                               |

| Spurious out-band noise Spurious in-band noise Two tone interdemodulation Tone + power inter- demodulation | $N_{SOB}$ $N_{SIB}$ $IMD_{2T}$ $IMD_{TP}$ |             |          | -30<br>-40<br>-35<br>-49 | dBm0<br>dBm0<br>dBm0<br>dBm0 | CCITT G.712, §7.1<br>CCITT G.712, §10<br>CCITT G.712, §8.1<br>CCITT G.712, §8.2 |

| Crosstalk attenuation between $V_{\mathrm{IN}}$ and $V_{\mathrm{OUT}}$                                     | Ax                                        | 75          | 80       |                          | dB                           | CCITT G.712, §12                                                                |

#### ANALOG CHANNEL CHARACTERISTICS - $\mu$ -LAW

| Characteristic                                                                  | Symbol                                                    | Value       |               |                   | Units                | Conditions                                                   |

|---------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|---------------|-------------------|----------------------|--------------------------------------------------------------|

|                                                                                 |                                                           | MIn.        | Тур. (1)      | Max.              |                      |                                                              |

| 0dBm0 level (see Note 2) Variation in 0dBm0 level Weighted idle channel noise   | 0dBm0 $\Delta_{\rm dBm0}$ ICN $_{\rm W}$                  | 5.3<br>-0.3 | 5.8<br>0<br>5 | 6.3<br>0.3<br>17  | dBm<br>dB<br>dBrnc0  | ±5V, 25°C<br>Over test conditions<br>AT&T D3<br>(see Note 3) |

| Single frequency idle channel noise                                             | ICN <sub>SF</sub>                                         |             |               | -60               | dBm0                 | AT&T D3                                                      |

| Weighted receive idle channel noise                                             | ICN <sub>WR</sub>                                         |             |               | 15                | dBrnc0               | AT&T D3                                                      |

| Spurious out-band noise<br>Spurious in-band noise<br>Two tone interdemodulation | N <sub>SOB</sub><br>N <sub>SIB</sub><br>IMD <sub>2T</sub> |             |               | -28<br>-40<br>-35 | dBm0<br>dBm0<br>dBm0 | AT&T D3<br>AT&T D3<br>AT&T D3                                |

| Tone + power inter-<br>demodulation                                             | $IMD_TP$                                                  |             |               | -49               | dBm0                 | AT&T D3                                                      |

| Crosstalk attenuation between V <sub>IN</sub> and V <sub>OUT</sub>              | Ax                                                        | 75          | 80            |                   | dB                   | AT&T D3                                                      |

#### **NOTES**

- 1. Typical figures are for design aid only They are not guaranteed and not subject to production testing

- 2. The typical 0dBm0 level of 58dBm corresponds to an RMS voltage of 1.51V and a maximum coding level of 3.1V

- 3. The maximum value reduces to -68dBm0p without squelch (MV3508 with TST/SE pin unconnected)

#### **ABSOLUTE MAXIMUM RATINGS**

Exceeding these ratings may cause permanent damage. Functional operation under these conditions is not implied.

Figure 14: Simple application circuit

HEADQUARTERS OPERATIONS

GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000 Fax: (0793) 518411

GEC PLESSEY SEMICONDUCTORS

P.O.Box 660017, 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel (408) 438 2900 Fax: (408) 438 5576 CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax: (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (3) 5276-5501 Fax: (3) 5276-5510

- NORTH AMERICA Integrated Circuits and Microwave Products, Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

- SOUTH EAST ASIA Singapore Tel: 2919291 Fax: 2916455

- **SWEDEN** Johanneshov Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- UK, EIRE, DENMARK, FINLAND & NORWAY Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1993 Publication No. DS 3133 Issue No. 2.1 September 1993

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior knowledge the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

http://www.zarlink.com

World Headquarters - Canada

Tel: +1 (613) 592 0200 Fax: +1 (613) 592 1010

**North America - West Coast**

Tel: (858) 675-3400 Fax: (858) 675-3450

**Asia/Pacific** Tel: +65 333 6193 Fax: +65 333 6192 Tel: (978) 322-4800 Fax: (978) 322-4888

**North America - East Coast**

Europe, Middle East, and Africa (EMEA)

Tel: +44 (0) 1793 518528 Fax: +44 (0) 1793 518581

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink Semiconductor's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips

Zarlink and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2001, Zarlink Semiconductor Inc. All rights reserved.