# Sequential 4G-Bits XtraROM for Amusement

## **1. FEATURES**

- Organization

- 256M x 16bit

- Page Size : 512words(support sequential read)

- Memory Area: Please refer to "7. MEMORY AREA"

- Read Operation

- Latency : 15us

- Read Cycle Time : 40ns

- Voltage Supply : 3.0V ~ 3.6V

- Current

- Read : 120mA

- Stand-by : 200uA

- Command/Address/Data Multiplexed Port

- Package : 70-pin SSOP

- · All devices are RoHS compliant

## 4. PIN CONFIGURATIONS

#### 70 SSOP

|        |    |    | -     |

|--------|----|----|-------|

| IO15 🗆 | 1  | 70 | 1014  |

| NC 🗆   | 2  | 69 | 1013  |

| NC 🗆   | 3  | 68 | 1012  |

| NC 🗆   | 4  | 67 |       |

| NC 🗆   | 5  | 66 | GND2  |

| NC 🗆   | 6  | 65 | 1011  |

| NC 🗆   | 7  | 64 | 1010  |

| NC 🗆   | 8  | 63 | L 109 |

| NC 🗆   | 9  | 62 | 108   |

| NC 🗆   | 10 | 61 | TEST  |

| NC 🗆   | 11 | 60 | D NC  |

| NC 🗆   | 12 | 59 |       |

| CE 🗆   | 13 | 58 | GND1  |

| RES -  | 14 | 57 |       |

| VCC1   | 15 | 56 | □ R/B |

| GND1   | 16 | 55 | D NC  |

| NC 🗆   | 17 | 54 | D NC  |

| NC 🗆   | 18 | 53 | D NC  |

| NC 🗆   | 19 | 52 | D NC  |

| NC 🗆   | 20 | 51 | GND1  |

| R/B □  | 21 | 50 | VCC1  |

| RE 🗆   | 22 | 49 | RES   |

| GND1   | 23 | 48 |       |

| VCC1   | 24 | 47 | D NC  |

| NC 🗆   | 25 | 46 | D NC  |

| test 🗆 | 26 | 45 | D NC  |

| 100 🗆  | 27 | 44 | D NC  |

| 101 🗆  | 28 | 43 | D NC  |

| 102 🗆  | 29 | 42 | D NC  |

| 103 🗆  | 30 | 41 | D NC  |

| GND2   | 31 | 40 | D NC  |

| VCC2   | 32 | 39 | D NC  |

| 104 🗆  | 33 | 38 | D NC  |

| 105 🗆  | 34 | 37 | D NC  |

| IO6 🗆  | 35 | 36 | □ 107 |

|        |    |    |       |

## 2. GENERAL DESCRIPTION

The MX23J4G76 is a single 3.3V XtraROM, density 4Gbit, factory pre-programmed ROM with Macronix NBit technology.

It utilizes the 16 bit multiplexed I/O bus for command, address, and data inputs/outputs.

Simple design structure makes the cost of the device and competitive over the other types of code-storage memory IC.

# 3. ORDER INFORMATION

| Part No.        | Read Cycle Time | Package |

|-----------------|-----------------|---------|

| MX23J4G76MC-40G | 40ns            | 70 SSOP |

## **5. PIN DESCRIPTION**

| Symbol   | Туре | Pin Function                                     |

|----------|------|--------------------------------------------------|

| CE       | I    | Chip Enable                                      |

| IO0~IO15 | I/O  | Command / Address / Data<br>Multiplexed I/O Port |

| RE       | I    | Read Clock                                       |

| VCC1     | I    | Power (3.3V)                                     |

| VCC2     | I    | Power (3.3V, for I/O)                            |

| GND1     | I    | Ground                                           |

| GND2     | I    | Ground (for I/O)                                 |

| NC       |      | All pins = Connected to Floating                 |

| (Note 3) |      | All pins = Connected to GND                      |

| R/B      | OD   | Ready/Busy output pin (Note 1)                   |

| RES      | I    | RESET (Low Active)                               |

| TEST     | I    | Test Pin (Note 2)                                |

- Note 1 :  $R/\overline{B}$  (2 pins)=connected in PC board. R/B open drain.

- Note 2 : TEST pin can be connected to GND, VCC or Open.

- Note 3 : All NC pins = Connected to Floating or All NC pins = Connected to GND

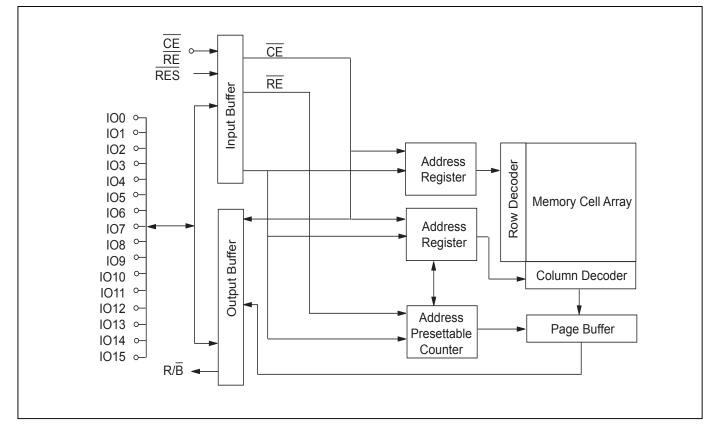

# 6. BLOCK DIAGRAM

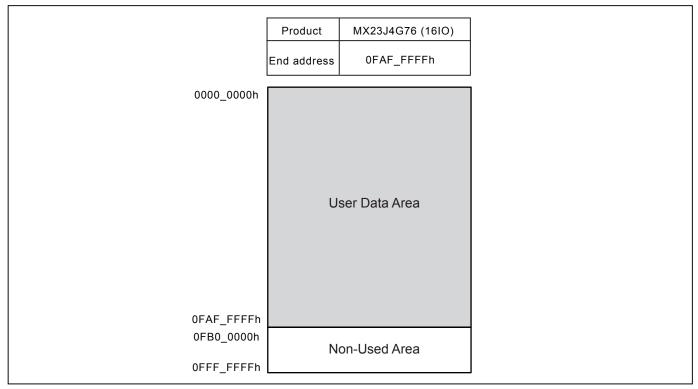

## 7. MEMORY AREA

## **8. ABSOLUTE MAXIMUM RATINGS**

| Item                               | Symbol          | Ratings        |

|------------------------------------|-----------------|----------------|

| Voltage on any Pin Relative to VSS | V <sub>IN</sub> | -0.5V to 4.6V  |

| Ambient Operating Temperature      | Topr            | 0°C to 85°C    |

| Storage Temperature                | Tstg            | -55°C to 125°C |

## 9. DC CHARACTERISTICS

# Table 1. DC Characteristics ( $T_{opr} = 0 \sim 85^{\circ}C$ , VCC = 3.0~3.6V )

| Item                   | Symbol           | Test Conditions                                                                                                                                                                                                                                                                                                                     | Min. | Max.                  | Unit |

|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------|

| Input High Voltage     | V <sub>IH</sub>  | -                                                                                                                                                                                                                                                                                                                                   | 2    | V <sub>cc</sub> +0.5V | V    |

| Input Low Voltage      | V <sub>IL</sub>  | -                                                                                                                                                                                                                                                                                                                                   | -0.5 | 0.8                   | V    |

| Output High Voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -400uA                                                                                                                                                                                                                                                                                                            | 2.4  | -                     | V    |

| Output Low Voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.6mA                                                                                                                                                                                                                                                                                                             | -    | 0.4                   | V    |

| Operating Current *    | I <sub>cc</sub>  | $\label{eq:CE} \begin{array}{l} \overline{\text{CE}} \ = \text{V}_{\text{IL}}, \ \text{I}_{\text{OUT}} = 0\text{mA}, \\ t_{\text{CS}} = 100\text{ns}, \ t_{\text{CH}} = 100\text{ns}, \\ t_{\text{CEPH}} = 100\text{ns}, \ t_{\text{CYC}} = 50\text{ns}, \\ t_{\text{WH}} = 25\text{ns}, \ t_{\text{WL}} = 25\text{ns} \end{array}$ | -    | 120                   | mA   |

| Standby Current (CMOS) | I <sub>STB</sub> | $\overline{CE} = V_{cc} - 0.2V, IO=Hi-z,$<br>$\overline{RE} = V_{cc} - 0.2V$                                                                                                                                                                                                                                                        | -    | 200                   | uA   |

| Input Leakage Current  | ILI              | $V_{IN} = 0$ to $V_{CC}(max)$                                                                                                                                                                                                                                                                                                       | -    | ±10                   | uA   |

| Output Leakage Current | I <sub>LO</sub>  | $V_{OUT} = 0$ to $V_{CC}(max)$                                                                                                                                                                                                                                                                                                      | -    | ±10                   | uA   |

\* note: output load : 30pF \* Recommended Operation Condition, Vcc Rise Time 30mV/mS

# **10. AC CHARACTERISTICS**

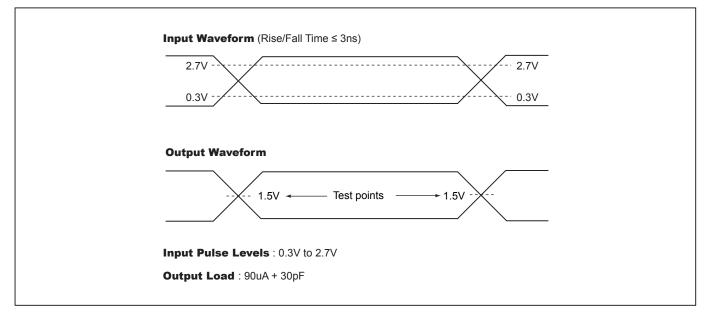

#### Table 2. AC TEST CONDITION

| Parameter                 | Test Condition |

|---------------------------|----------------|

| Input Pulse Level         | 0.3V to 2.7V   |

| Input Rise and Fall Times | 3ns            |

| Output Timing Levels      | 1.5V/1.5V      |

| Output Load               | 90uA + 30pF    |

## **AC Test Conditions**

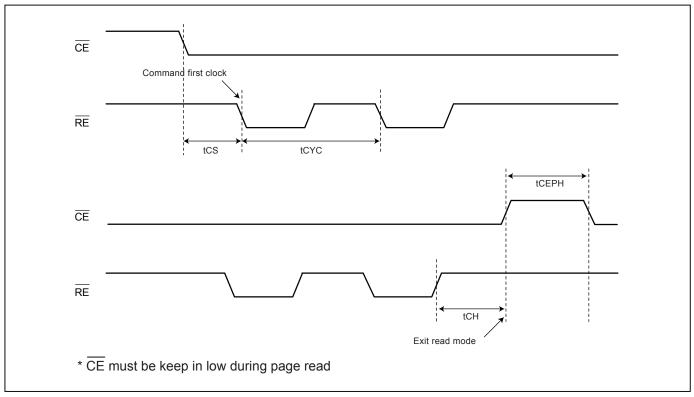

# Table 3. AC Characteristics for Command Input ( $T_{opr} = 0 \sim 85^{\circ}C$ , VCC = 3.0~3.6V)

| Parameter                 | Symbol            | Min. | Unit |

|---------------------------|-------------------|------|------|

| CE Setup Time             | t <sub>cs</sub>   | 50   | ns   |

| CE Hold Time              | t <sub>cH</sub>   | 50   | ns   |

| CE High Pulse Width       | t <sub>CEPH</sub> | 100  | ns   |

| Data-in Setup Time        | t <sub>DIS</sub>  | 5    | ns   |

| Data-in Hold Time         | t <sub>DIH</sub>  | 5    | ns   |

| Data-out Hold Time *      | t <sub>DOH</sub>  | 10   | ns   |

| Read cycle time           | t <sub>cyc</sub>  | 40   | ns   |

| RE High Pulse Width       | t <sub>wH</sub>   | 16   | ns   |

| RE Low Pulse Width        | t <sub>wL</sub>   | 20   | ns   |

| Ready to RE low           | t <sub>RR</sub>   | 20   | ns   |

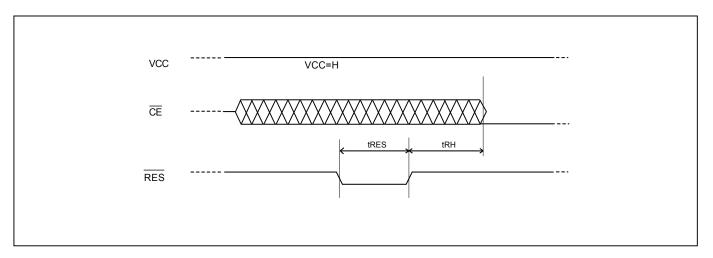

| RES Low Pulse Width       | t <sub>RES</sub>  | 100  | ns   |

| RES High Time Before Read | t <sub>RH</sub>   | 1    | ms   |

\*  $\overline{\text{RES}}$  filter glitch which pulse width is less than 5ns.

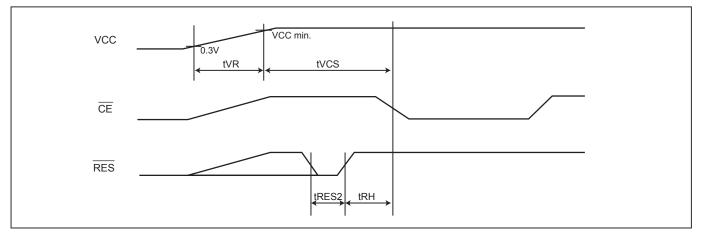

# POR SEQUENCE

# POR Timing Waveform

| Symbol | Parameter                 | Min. | Max.   | Unit |

|--------|---------------------------|------|--------|------|

| tVR    | VCC Rise Time             | 50   | 500000 | us/V |

| tR     | Input Signal Rise Time    |      | 20     | us/V |

| tF     | Input Signal Fall Time    |      | 20     | us/V |

| tVCS   | VCC Setup Time            | 2    |        | ms   |

| tRES2  | RES Low Time 2            | 100  |        | ns   |

| tRH    | RES High Time Before Read | 1    |        | ms   |

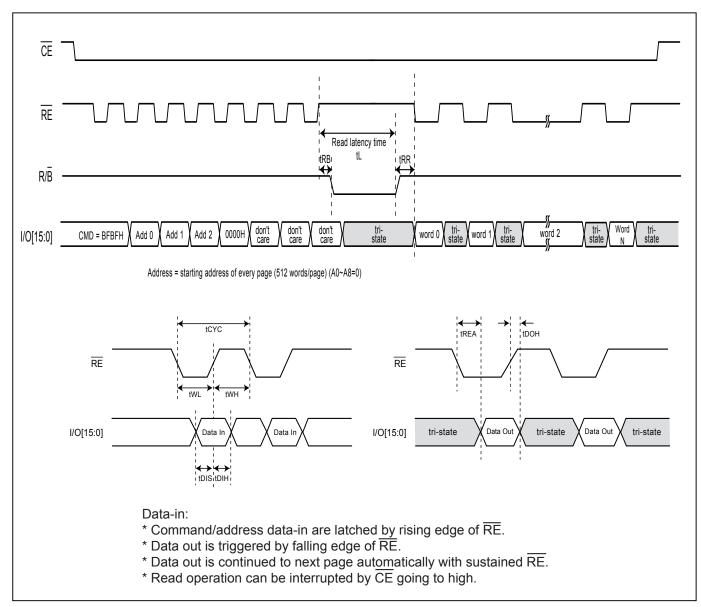

# Table 4. AC Characteristics for Data Output ( $T_{opr} = 0 \sim 85^{\circ}C$ , VCC = 3.0~3.6V)

| Parameter            | Symbol           | Min. | Max.              | Unit |

|----------------------|------------------|------|-------------------|------|

| Read Latency Time *1 | tL               | -    | 15                | us   |

| RE Access Time       | t <sub>REA</sub> | -    | 18                | ns   |

| RE High to Busy      | t <sub>RB</sub>  | -    | 250* <sup>2</sup> | ns   |

\*<sup>1</sup> The read latency will only be needed at the first page read.

\*<sup>2</sup> tRB=250ns max. including Tf at 10Kohm pull-up condition. Note:

**AC Timing Condition**

#### Command Input and Data Output Timing Waveform

#### **Table 5. Read Command Definitions**

| Command Bus cycles |         | 1st<br>bus cycle | 2nd<br>bus cycle | 3rd<br>bus cycle | 4th<br>bus cycle | 5th<br>bus cycle | 6th<br>bus cycle | 7th<br>bus cycle | 8th<br>bus cycle |

|--------------------|---------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

|                    | command | address          |                  |

| Read Mode          | 8       | BFBFH            | Addr0            | Addr1            | Addr2            | 0000H            | don't care       | don't care       | don't care       |

Addr0 : A24~A27 (IO0/8=A24, IO1/9=A25, IO2/10=A26, IO3/11=A27)

Addr1 : A16~A23 (IO0/8=A16, IO1/9=A17, IO2/10=A18, IO3/11=A19, IO4/12=A20, IO5/13=A21, IO6/14=A22, IO7/15=A23)

Addr2 : A8~A15 (IO0/8=A8, IO1/9=A9, IO2/10=A10, IO3/11=A11, IO4/12=A12, IO5/13=A13, IO6/14=A14, IO7/15=A15)

Note : The starting address of every page (A8~A0) is 0, Each page has 512 words

**RES** Timing Waveform

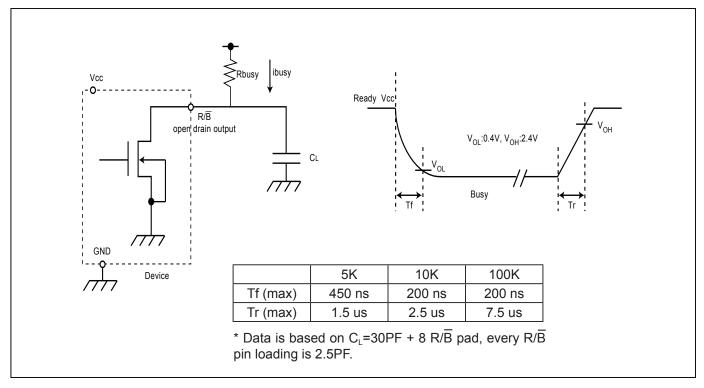

# READY/BUSY

The device has a  $R/\overline{B}$  output that provides a hardware method of indicating the device is ready for read. The  $R/\overline{B}$  is normally high but transitions to low after read command is issued. It returns to high when the internal controller has finish the read operation.

The pin is an open-drain driver thereby allowing two or more  $R/\overline{B}$  outputs to be Or-tied. A5K $\Omega \sim 50K\Omega$  pull-up resistor is required to allow  $R/\overline{B}$  to transition high indicating the device is ready for read.

Note:

1. Rbusy must be higher than 5K $\Omega$ .

2. A schmitt trigger is suggested to provide on the user input port due to the slow slew rate of the tr and tf.

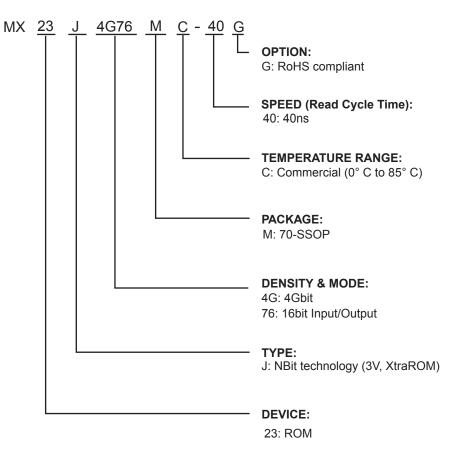

# **11. PART NAME DESCRIPTION**

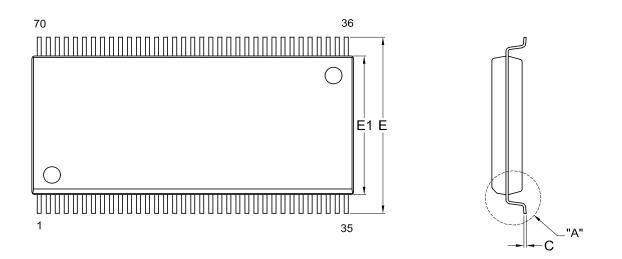

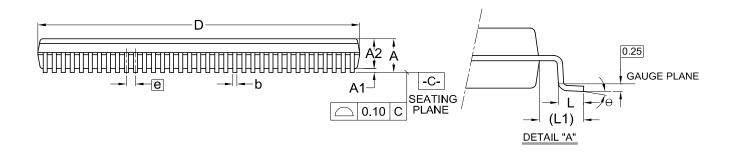

# **12. PACKAGE INFORMATION**

Doc. Title: Package Outline for SSOP 70L (500MIL)

Dimensions (inch dimensions are derived from the original mm dimensions)

| SY<br>UNIT | MBOL | Α     | A1    | A2    | b     | С     | D     | Е     | E1    | е     | L     | L1    | Θ  |

|------------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----|

|            | Min. |       | 0.10  | 2.56  | 0.30  | 0.17  | 28.37 | 15.73 | 12.47 |       | 0.61  | 1.51  | 0  |

| mm         | Nom. |       | 0.15  | 2.69  | 0.35  | 0.20  | 28.50 | 16.03 | 12.60 | 0.80  | 0.81  | 1.71  | 5  |

|            | Max. | 3.05  | 0.23  | 2.82  | 0.43  | 0.25  | 28.63 | 16.33 | 12.73 | -     | 1.01  | 1.91  | 10 |

|            | Min. |       | 0.004 | 0.101 | 0.012 | 0.007 | 1.117 | 0.619 | 0.491 | -     | 0.024 | 0.060 | 0  |

| Inch       | Nom. |       | 0.006 | 0.106 | 0.014 | 0.008 | 1.122 | 0.631 | 0.496 | 0.031 | 0.032 | 0.068 | 5  |

|            | Max. | 0.120 | 0.009 | 0.111 | 0.017 | 0.010 | 1.127 | 0.643 | 0.501 |       | 0.040 | 0.075 | 10 |

| Dura No   | Revision |                 | Reference |  |  |  |  |

|-----------|----------|-----------------|-----------|--|--|--|--|

| Dwg. No.  | Kevision | JEDEC           | EIAJ      |  |  |  |  |

| 6110-1503 | 8        | MO <b>-</b> 174 |           |  |  |  |  |

# **REVISION HISTORY**

| <b>Revision No.</b> | Description                                                  | Page | Date        |

|---------------------|--------------------------------------------------------------|------|-------------|

| 0.01                | 1. Modified Addr0 of Table 5. Read Command Definitions       | P6   | NOV/18/2010 |

| 0.02                | 1. Added "MEMORY AREA"                                       | P2   | MAR/11/2011 |

| 0.03                | 1. Modified PIN CONFIGURATIONS of 70SSOP                     | P1   | MAY/16/2011 |

| 1.0                 | 1. Removed "ADVANCED INFORMATION"                            | P1   | NOV/01/2011 |

| 1.1                 | 1. Added POR SEQUENCE                                        | P5   | MAY/08/2012 |

|                     | 2. Added Part Name Description                               | P10  |             |

|                     | 3. Modified NC1 pin (pin 26, 61) as TEST pin                 | P1   |             |

|                     | NC1 pin (pin 20, 55) as NC pin                               |      |             |

|                     | 4. Modified AC Test Conditions                               | P4   |             |

|                     | 5. Modified table 2 from "Input and Output Timing Levels" to | P4   |             |

|                     | "Output Timing Levels"                                       |      |             |

|                     | 6. Added note *2 for tRB                                     | P6   |             |

Except for customized products which has been expressly identified in the applicable agreement, Macronix's products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only, and not for use in any applications which may, directly or indirectly, cause death, personal injury, or severe property damages. In the event Macronix products are used in contradicted to their target usage above, the buyer shall take any and all actions to ensure said Macronix's product qualified for its actual use in accordance with the applicable laws and regulations; and Macronix as well as it's suppliers and/or distributors shall be released from any and all liability arisen therefrom.

Copyright© Macronix International Co., Ltd. 2010~2012. All rights reserved, including the trademarks and tradename thereof, such as Macronix, MXIC, MXIC Logo, MX Logo, Integrated Solutions Provider, NBit, Nbit, NBiit, Macronix NBit, eLiteFlash, XtraROM, Phines, KH Logo, BE-SONOS, KSMC, Kingtech, MXSMIO, Macronix vEE, Macronix MAP, Rich Audio, Rich Book, Rich TV, and FitCAM. The names and brands of other companies are for identification purposes only and may be claimed as the property of the respective companies.

For the contact and order information, please visit Macronix's Web site at: http://www.macronix.com

MACRONIX INTERNATIONAL CO., LTD. reserves the right to change product and specifications without notice.